# **ADN4680E**

# 250 Mbps, Half-Duplex, Quad M-LVDS Transceivers

## **FEATURES**

- Four M-LVDS transceivers (driver and receiver pairs)

- Switching rate: 250 Mbps (125 MHz)

- ▶ Independent pin select for each receiver, two modes:

- ► Type 1: input hysteresis of 15 mV typical

- Type 2: differential input threshold voltage offset by 100 mV to support open-circuit, short-circuit, and bus idle fail-safe

- Compatible with the TIA/EIA-899 standard for M-LVDS

- ▶ Glitch free power-up/power-down on the M-LVDS bus

- Controlled transition times on the driver output

- ▶ Common-mode range: -1 V to +3.4 V, allowing communication with ±2 V of ground noise

- Driver outputs high-Z when disabled or powered off

- ► Independent enable pins for each driver and receiver

- Enhanced ESD protection on bus pins

- ▶ ≥±15 kV HBM, air discharge

- ► ≥±8 kV HBM, contact discharge

- ▶ ≥±10 kV IEC 61000-4-2, air discharge

- ≥±8 kV IEC 61000-4-2, contact discharge

- Enhanced ±8 kV HBM ESD protection for all pins, contact discharge

- Operating temperature range: -40°C to +105°C

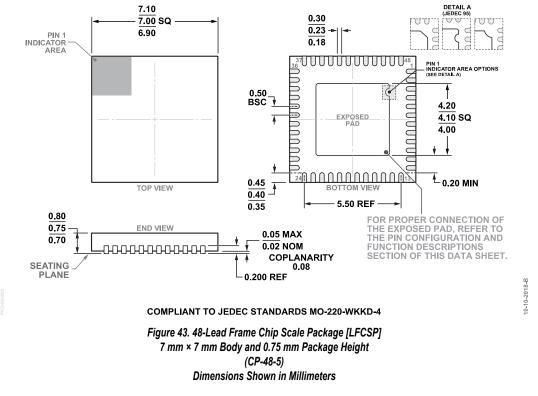

- Available in 48-lead, 7 mm x 7 mm LFCSP

## **APPLICATIONS**

- Backplane and cable multipoint data transmission

- Multipoint clock distribution

- Low power, high speed alternative to shorter RS-485 links

- Networking and wireless base station infrastructure

- ▶ Grid infrastructure and relay protection systems

- Differential extension of SPI networks

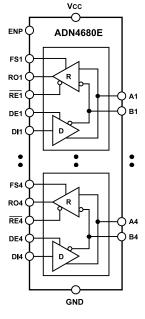

## FUNCTIONAL BLOCK DIAGRAM

50

# **GENERAL DESCRIPTION**

The ADN4680E comprises four multipoint, low voltage differential signaling (M-LVDS) transceivers (driver and receiver pairs) that can operate at up to 125 MHz, or 250 Mbps nonreturn to zero (NRZ). The driver and receiver of each transceiver are connected in half-duplex configuration, which allows each transceiver to be configured via independent enable pins for either sending or receiving data. Electrostatic discharge (ESD) protection of up to ±15 kV is implemented on the bus pins. The transceivers are optimized for low dynamic power consumption for use in high density applications. The ADN4680E is designed to the TIA/EIA-899 standard for use in M-LVDS networks and complement TIA/EIA-644 LVDS devices with additional multipoint capabilities.

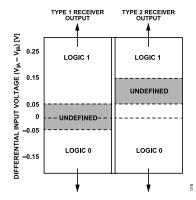

The receivers detect the bus state with a differential input of as little as  $\pm 50 \text{ mV}$  over a common-mode voltage range of -1 V to +3.4 V. Each receiver can be independently pin selectable as a Type 1 or Type 2 receiver. Type 1 receivers have 15 mV of hysteresis so that slow changing signals or loss of input does not lead to output oscillations. Type 2 receivers exhibit an offset threshold, guaranteeing the output state when the inputs are open (open circuit fail-safe), the bus is idle (bus idle or terminated fail-safe), or when the inputs are hard short circuited.

The device is available in a compact 48-lead, 7 mm × 7 mm LFCSP and operates over a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

Rev. 0

DOCUMENT FEEDBACK

**TECHNICAL SUPPORT**

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     | 1   |

|----------------------------------------------|-----|

| Applications                                 | 1   |

| Functional Block Diagram                     | 1   |

| General Description                          | 1   |

| Specifications                               | 3   |

| Receiver Input Threshold Test Voltages       | 4   |

| Timing Specifications                        | 5   |

| Absolute Maximum Ratings                     | 7   |

| Thermal Resistance                           | 7   |

| Electrostatic Discharge (ESD) Ratings        | 7   |

| ESD Caution                                  | 7   |

| Pin Configurations and Function Descriptions | 8   |

| Typical Performance Characteristics          | 9   |

| Test Circuits and Switching Characteristics  | .13 |

| Driver Voltage and Current Measurements      | .13 |

| Driver Timing Measurements                   | 14  |

|                                              |     |

# **REVISION HISTORY**

9/2021—Revision 0: Initial Version

| Receiver Timing Measurements            | 15 |

|-----------------------------------------|----|

| Theory of Operation                     | 16 |

| Three-State Bus Connection              | 16 |

| Truth Tables                            | 16 |

| Glitch Free Powering Up and Powering    |    |

| Down                                    | 17 |

| Fault Conditions                        | 17 |

| Receiver Input Thresholds and Fail-Safe | 17 |

| Sixty-Four Transceivers on a Network    | 17 |

| Applications Information                | 18 |

| PCB Layout                              | 19 |

| M-LVDS Design Considerations            | 19 |

| Extending the SPI over M-LVDS           | 19 |

| Outline Dimensions                      | 21 |

| Ordering Guide                          | 21 |

| Evaluation Boards                       | 21 |

|                                         |    |

$V_{CC}$  = 3.0 V to 3.6 V, load resistance (R<sub>L</sub>) = 50  $\Omega$ , and T<sub>A</sub> = -40°C to +105°C, unless otherwise noted. All typical values are given for V<sub>CC</sub> = 3.3 V and T<sub>A</sub> = 25°C.

| Parameter                                           | Symbol                    | Min                  | Тур | Max                 | Unit | Test Conditions/Comments                                                                                                     |

|-----------------------------------------------------|---------------------------|----------------------|-----|---------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                                        |                           |                      |     |                     |      |                                                                                                                              |

| Supply Current                                      | I <sub>CC</sub>           |                      |     |                     |      | 125 MHz clock on DI1 to DI4 or A1 to A4<br>and B1 to B4, ENP high, and other pins<br>open, unless stated otherwise           |

| Only Driver Enabled                                 |                           |                      | 65  | 75                  | mA   | DE1 to DE4, $\overline{\text{RE1}}$ to $\overline{\text{RE4}}$ = V <sub>CC</sub> , R <sub>L</sub> = 50 $\Omega$              |

| Both Driver and Receiver Disabled                   |                           |                      | 8   | 10                  | mA   | DE1 to DE4 = 0 V, $\overline{RE1}$ to $\overline{RE4}$ = V <sub>CC</sub>                                                     |

| Both Driver and Receiver Enabled                    |                           |                      | 115 | 140                 | mA   | DE1 to DE4 = $V_{CC}$ , $\overline{RE1}$ to $\overline{RE4}$ = 0 V, $R_L$ = 50 $\Omega$ , load capacitance ( $C_L$ ) = 15 pF |

| Only Receiver Enabled                               |                           |                      | 60  | 75                  | mA   | DE1 to DE4, $\overline{RE1}$ to $\overline{RE4}$ = 0 V, C <sub>L</sub> = 15 pF                                               |

| Power-Down Supply Current                           | ICCPD                     |                      |     | 4.5                 | mA   | ENP low                                                                                                                      |

| DRIVER                                              |                           |                      |     |                     |      |                                                                                                                              |

| Differential Outputs                                |                           |                      |     |                     |      |                                                                                                                              |

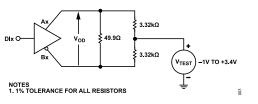

| Differential Output Voltage Magnitude               | V <sub>OD</sub>           | 450                  | 550 | 650                 | mV   | See Figure 24                                                                                                                |

| $\Delta  V_{OD} $ for Complementary Output States   | $\Delta  V_{OD} $         | -50                  | 0   | +50                 | mV   | See Figure 24                                                                                                                |

| Common-Mode Output Voltage (Steady State)           | V <sub>OS(SS)</sub>       | 0.7                  | 0.9 | 1.1                 | V    | See Figure 25 and Figure 28                                                                                                  |

| $\Delta V_{OS(SS)}$ for Complementary Output States | $\Delta V_{OS(SS)}$       | -50                  | 0   | +50                 | mV   | See Figure 25 and Figure 28                                                                                                  |

| Peak-to-Peak V <sub>OS</sub>                        | V <sub>OS(PP)</sub>       |                      | 100 |                     | mV   | See Figure 25 and Figure 28                                                                                                  |

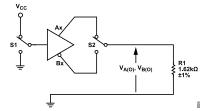

| Maximum Steady-State Open-Circuit Output Voltage    | $V_{A(O)}$ and $V_{B(O)}$ | 0                    |     | 2.4                 | V    | See Figure 26                                                                                                                |

| Voltage Overshoot <sup>1</sup>                      |                           |                      |     |                     |      |                                                                                                                              |

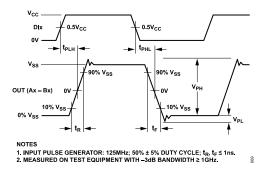

| Low to High                                         | V <sub>PH</sub>           |                      |     | 1.2 V <sub>SS</sub> | V    | See Figure 29 and Figure 30                                                                                                  |

| High to Low                                         | V <sub>PL</sub>           | -0.2 V <sub>SS</sub> |     |                     | V    | See Figure 29 and Figure 30                                                                                                  |

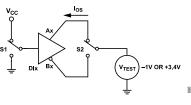

| Output Current, Short-Circuit                       | I <sub>OS</sub>           |                      |     | 24                  | mA   | See Figure 27                                                                                                                |

| Logic Inputs (DIx, DEx, and ENP)                    |                           |                      |     |                     |      |                                                                                                                              |

| Input High Voltage                                  | VIH                       | 2                    |     | V <sub>CC</sub>     | V    |                                                                                                                              |

| Input Low Voltage                                   | VIL                       | GND                  |     | 0.8                 | V    |                                                                                                                              |

| Input Current                                       | lı                        | 0                    |     | 10                  | μA   | Input voltage (VI) = GND to V <sub>CC</sub>                                                                                  |

| Input Capacitance                                   | CIN                       |                      | 5   |                     |      | $V_{I} = 0.4 \sin(30 \times 10^{6} \pi t) V + 0.5 V^{2}$                                                                     |

| RECEIVER                                            |                           |                      |     |                     |      |                                                                                                                              |

| Differential Inputs                                 |                           |                      |     |                     |      |                                                                                                                              |

| Differential Input Threshold Voltage                |                           |                      |     |                     |      | See Table 2 and Figure 39                                                                                                    |

| Type 1 Receiver                                     | V <sub>TH</sub>           | -50                  |     | +50                 | mV   | FSx = GND                                                                                                                    |

| Type 2 Receiver                                     | V <sub>TH</sub>           | 50                   |     | 150                 | mV   | FSx = V <sub>CC</sub>                                                                                                        |

| Input Hysteresis                                    |                           |                      |     |                     |      |                                                                                                                              |

| Type 1 Receiver                                     | V <sub>HYS</sub>          |                      | 15  |                     | mV   | FSx = GND                                                                                                                    |

| Type 2 Receiver                                     | V <sub>HYS</sub>          |                      | 0   |                     | mV   | FSx = V <sub>CC</sub>                                                                                                        |

| Differential Input Voltage Magnitude                | V <sub>ID</sub>           | 0.05                 |     | V <sub>CC</sub>     | V    |                                                                                                                              |

| Logic Output ROx                                    |                           |                      |     |                     |      |                                                                                                                              |

| Short-Circuit Current                               | I <sub>OS</sub>           | -65                  |     | +65                 | mA   | $\overline{REx}$ = GND, ROx = V <sub>CC</sub> or GND                                                                         |

| Output Voltage                                      |                           |                      |     |                     |      |                                                                                                                              |

| High                                                | V <sub>OH</sub>           | 2.4                  |     |                     | V    | Output high current (I <sub>OH</sub> ) = -8 mA                                                                               |

| Low                                                 | V <sub>OL</sub>           |                      |     | 0.4                 | V    | Output low current (I <sub>OL</sub> ) = 8 mA                                                                                 |

| High Impedance Output Current                       | I <sub>OZ</sub>           | -10                  |     | +15                 | μA   | Output voltage ( $V_O$ ) = 0 V or 3.6 V                                                                                      |

| Logic Input (REx) and FSx)                          |                           |                      |     |                     |      |                                                                                                                              |

| Input Voltage                                       |                           |                      |     |                     |      |                                                                                                                              |

| High                                                | VIH                       | 2                    |     | V <sub>CC</sub>     | V    |                                                                                                                              |

|--|

| Parameter                                                                | Symbol                           | Min | Тур      | Max | Unit | Test Conditions/Comments                                                                                     |

|--------------------------------------------------------------------------|----------------------------------|-----|----------|-----|------|--------------------------------------------------------------------------------------------------------------|

| Low                                                                      | V <sub>IL</sub>                  | GND |          | 0.8 | V    |                                                                                                              |

| Input Current                                                            | lı -                             | -10 |          | 0   | μA   | $V_{I} = GND$ to $V_{CC}$                                                                                    |

| BUS INPUT AND OUTPUT                                                     |                                  |     |          |     |      |                                                                                                              |

| Input Current                                                            |                                  |     |          |     |      |                                                                                                              |

| Ax (Receiver or Transceiver with Driver Disabled)                        | I <sub>A</sub>                   | 0   |          | 16  | μA   | Bx voltage (V <sub>B</sub> ) = 1.2 V and Ax voltage (V <sub>A</sub> = 3.8 V                                  |

|                                                                          |                                  | -10 |          | +10 | μA   | $V_B$ = 1.2 V and $V_A$ = 0 V or 2.4 V                                                                       |

|                                                                          |                                  | -16 |          | 0   | μA   | $V_B = 1.2 \text{ V}$ and $V_A = -1.4 \text{ V}$                                                             |

| Bx (Receiver or Transceiver with Driver Disabled)                        | I <sub>B</sub>                   | 0   |          | 16  | μA   | $V_A$ = 1.2 V and $V_B$ = 3.8 V                                                                              |

|                                                                          |                                  | -10 |          | +10 | μA   | $V_A$ = 1.2 V and $V_B$ = 0 V or 2.4 V                                                                       |

|                                                                          |                                  | -16 |          | 0   | μA   | $V_A = 1.2 V$ and $V_B = -1.4 V$                                                                             |

| Differential (Receiver or Transceiver with Driver Disabled)              | I <sub>AB</sub>                  | -4  |          | +4  | μA   | $V_A = V_B$ and 1.4 V $\leq V_A \leq 3.8$ V                                                                  |

| Power-Off Input Current                                                  |                                  |     |          |     |      | $0 \text{ V} \le \text{V}_{\text{CC}} \le 1.5 \text{ V}$                                                     |

| Ax                                                                       | I <sub>A(OFF)</sub>              | 0   |          | 16  | μA   | $V_B = 1.2 \text{ V} \text{ and } V_A = 3.8 \text{ V}$                                                       |

|                                                                          |                                  | -10 |          | +10 | μA   | $V_B = 1.2 V$ and $V_A = 0 V$ or 2.4 V                                                                       |

|                                                                          |                                  | -16 |          | 0   | μA   | $V_B = 1.2 \text{ V}$ and $V_A = -1.4 \text{ V}$                                                             |

| Bx                                                                       | I <sub>B(OFF)</sub>              | 0   |          | 16  | μA   | $V_A$ = 1.2 V and $V_B$ = 3.8 V                                                                              |

|                                                                          |                                  | -10 |          | +10 | μA   | $V_A$ = 1.2 V and $V_B$ = 0 V or 2.4 V                                                                       |

|                                                                          |                                  | -16 |          | 0   | μA   | $V_A = 1.2 V$ and $V_B = -1.4 V$                                                                             |

| Differential                                                             | I <sub>AB(OFF)</sub>             | -4  |          | +4  | μA   | $V_A = V_B$ and $1.4 \le V_A \le 3.8$ V                                                                      |

| Input Capacitance (Transceiver with Driver Disabled)                     | C <sub>A</sub> or C <sub>B</sub> |     | 13       |     | pF   | $V_A \text{ or } V_B = 0.4 \sin(30e^6\pi t) \text{ V} + 0.5 \text{ V}, ^2$<br>other input = 1.2 V, DEx = 0 V |

| Differential Input Capacitance (Transceiver with Driver<br>Disabled)     | C <sub>AB</sub>                  |     | 6.5      |     | pF   | Ax – Bx voltage (V <sub>AB</sub> ) =<br>0.4 sin(30× $10^{6}\pi$ t) V, <sup>2</sup> DEx = 0 V                 |

| Input Capacitance Balance $(C_A/C_B)$ (Transceiver with Driver Disabled) | C <sub>A/B</sub>                 |     | 1 ± 0.01 |     |      | DEx = 0 V                                                                                                    |

<sup>1</sup> These specifications are guaranteed by design and characterization

<sup>2</sup> HP4194A impedance analyzer (or equivalent).

# **RECEIVER INPUT THRESHOLD TEST VOLTAGES**

$\overline{\text{REx}} = 0 \text{ V}.$

# Table 2. Test Voltages for Type 1 Receiver (FSx = GND)

| Α              | pplied Voltages (V) |                               | Input Voltage (V)            |         |

|----------------|---------------------|-------------------------------|------------------------------|---------|

| V <sub>A</sub> | V <sub>B</sub>      | Differential, V <sub>ID</sub> | Common-Mode, V <sub>IC</sub> | ROx (V) |

| +2.4           | 0                   | +2.4                          | +1.2                         | High    |

| 0              | +2.4                | -2.4                          | +1.2                         | Low     |

| +3.4           | +3.35               | +0.05                         | +3.375                       | High    |

| +3.35          | +3.4                | -0.05                         | +3.375                       | Low     |

| -1.35          | -1.4                | +0.05                         | -1.375                       | High    |

| -1.4           | -1.35               | -0.05                         | -1.375                       | Low     |

## Table 3. Test Voltages for Type 2 Receiver (FSx = V<sub>CC</sub>)

| Applied Voltages (V) |                |                               | Input Voltage (V)           |         |

|----------------------|----------------|-------------------------------|-----------------------------|---------|

| V <sub>A</sub>       | V <sub>B</sub> | Differential, V <sub>ID</sub> | Common-Mode V <sub>IC</sub> | ROx (V) |

| +2.4                 | 0              | +2.4                          | +1.2                        | High    |

| 0                    | +2.4           | -2.4                          | +1.2                        | Low     |

| +3.4                 | +3.25          | +0.15                         | +3.325                      | High    |

## Table 3. Test Voltages for Type 2 Receiver (FSx = V<sub>CC</sub>)

|                | Applied Voltages (V) |                               | Input Voltage (V)           |         |

|----------------|----------------------|-------------------------------|-----------------------------|---------|

| V <sub>A</sub> | V <sub>B</sub>       | Differential, V <sub>ID</sub> | Common-Mode V <sub>IC</sub> | ROx (V) |

| +3.4           | +3.35                | +0.05                         | +3.375                      | Low     |

| -1.25          | -1.4                 | +0.15                         | -1.325                      | High    |

| -1.35          | -1.4                 | +0.05                         | -1.375                      | Low     |

# TIMING SPECIFICATIONS

$V_{CC}$  = 3.0 V to 3.6 V and  $T_A$  = -40°C to +105°C, unless otherwise noted. All typical specifications are given for  $V_{CC}$  = 3.3 V and  $T_A$  = 25°C.

| Parameter                                                      | Symbol                              | Min  | Тур | Max | Unit | Test Conditions/Comments                                                   |

|----------------------------------------------------------------|-------------------------------------|------|-----|-----|------|----------------------------------------------------------------------------|

| DRIVER                                                         |                                     |      |     |     |      |                                                                            |

| Maximum Data Rate <sup>1</sup>                                 |                                     | 250  |     |     | Mbps | $T_A = -40^{\circ}C$ to +85°C                                              |

|                                                                |                                     | 100  |     |     | Mbps | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C$                           |

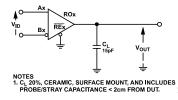

| Propagation Delay <sup>1</sup>                                 | t <sub>PLH</sub> , t <sub>PHL</sub> | 1.5  | 1.9 | 2.4 | ns   | See Figure 29 and Figure 30                                                |

| Differential Output Rise and Fall Time <sup>1</sup>            | t <sub>R</sub> , t <sub>F</sub>     | 1    | 1.3 | 1.6 | ns   | See Figure 29 and Figure 30                                                |

| Output Skew (Channel to Channel) <sup>1, 2</sup>               | t <sub>SK(O)</sub>                  |      |     | 100 | ps   | See Figure 29 and Figure 30                                                |

| Pulse Skew  t <sub>PHL</sub> – t <sub>PLH</sub>   <sup>1</sup> | t <sub>SK</sub>                     |      | 0   | 135 | ps   | See Figure 29 and Figure 30                                                |

| Part to Part Skew <sup>1, 3</sup>                              | t <sub>SK(PP)</sub>                 |      |     | 350 | ps   | See Figure 29 and Figure 30                                                |

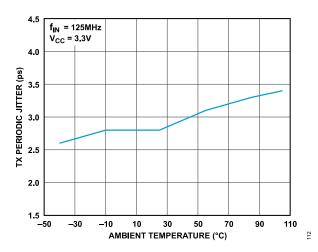

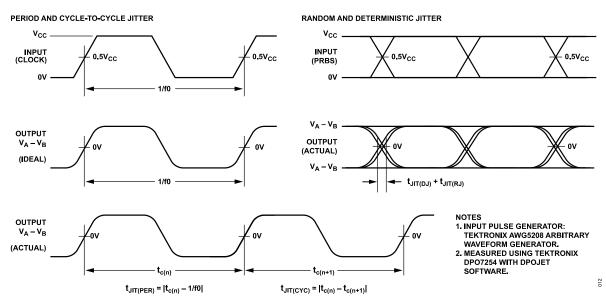

| Period Jitter, RMS (1 Standard Deviation)                      | t <sub>JIT(PER)</sub>               |      | 3   |     | ps   | 125 MHz clock input <sup>4, 5</sup> (see Figure 33)                        |

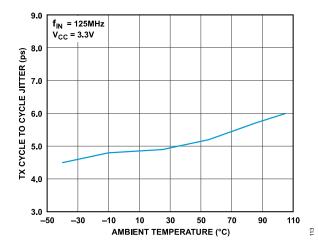

| Cycle to Cycle Jitter, RMS                                     | t <sub>JIT(CYC)</sub>               |      | 5   |     | ps   | 125 MHz clock input <sup>4, 5</sup> (see Figure 33)                        |

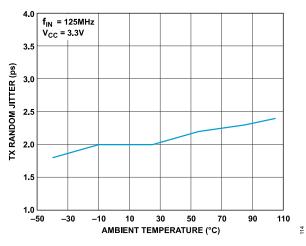

| Random Jitter, RMS                                             | t <sub>JIT(RJ)</sub>                |      | 2   |     | ps   | 250 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>4</sup> (see Figure 33)       |

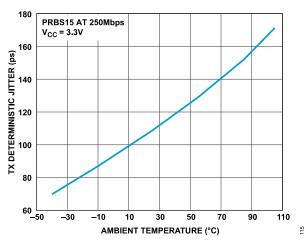

| Deterministic Jitter <sup>6</sup>                              | t <sub>JIT(DJ)</sub>                |      | 110 |     | ps   | 250 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>4</sup> (see Figure 33)       |

| Disable Time <sup>1</sup>                                      |                                     |      |     |     |      |                                                                            |

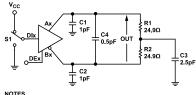

| From High Level                                                | t <sub>PHZ</sub>                    |      |     | 7   | ns   | See Figure 31 and Figure 32                                                |

| From Low Level                                                 | t <sub>PLZ</sub>                    |      |     | 7   | ns   | See Figure 31 and Figure 32                                                |

| Enable Time <sup>1</sup>                                       |                                     |      |     |     |      |                                                                            |

| To High Level                                                  | t <sub>PZH</sub>                    |      |     | 6   | ns   | See Figure 31 and Figure 32                                                |

| To Low Level                                                   | t <sub>PZL</sub>                    |      |     | 6   | ns   | See Figure 31 and Figure 32                                                |

| RECEIVER                                                       |                                     |      |     |     |      |                                                                            |

| Maximum Data Rate <sup>1</sup>                                 |                                     | 250  |     |     | Mbps | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                            |

|                                                                |                                     | 100  |     |     | Mbps | $T_{A} = -40^{\circ}C$ to +105°C                                           |

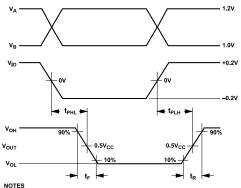

| Propagation Delay <sup>1</sup>                                 | t <sub>PLH</sub> , t <sub>PHL</sub> | 3    | 4   | 5   | ns   | C <sub>L</sub> = 15 pF (see Figure 34 and Figure 35)                       |

| Rise and Fall Time <sup>1</sup>                                | t <sub>R</sub> , t <sub>F</sub>     | 0.65 |     | 2.3 | ns   | C <sub>L</sub> = 15 pF (see Figure 34 and Figure 35)                       |

| Output Skew (Channel to Channel) <sup>1, 2</sup>               | t <sub>SK(O)</sub>                  |      |     | 300 | ps   | C <sub>L</sub> = 15 pF (see Figure 34 and Figure 35)                       |

| Pulse Skew  t <sub>PHL</sub> – t <sub>PLH</sub>   <sup>1</sup> | t <sub>SK</sub>                     |      |     |     |      | C <sub>L</sub> = 15 pF (see Figure 34 and Figure 35)                       |

| Type 1 Receiver                                                |                                     |      | 100 | 350 | ps   | FSx = GND                                                                  |

| Type 2 Receiver                                                |                                     |      | 300 | 500 | ps   | FSx = V <sub>CC</sub>                                                      |

| Part to Part Skew <sup>1, 3</sup>                              | t <sub>SK(PP)</sub>                 |      |     | 820 | ps   | C <sub>L</sub> = 15 pF (see Figure 34 and Figure 35)                       |

| Period Jitter, RMS (1 Standard Deviation)                      | t <sub>JIT(PER)</sub>               |      | 4   |     | ps   | 125 MHz clock input <sup>4, 5</sup> (see Figure 38)                        |

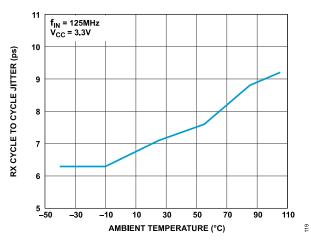

| Cycle to Cycle Jitter, RMS                                     | t <sub>JIT(CYC)</sub>               |      | 7   |     | ps   | 125 MHz clock input <sup>4, 5</sup> (see Figure 38)                        |

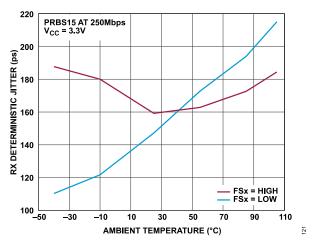

| Deterministic Jitter <sup>6</sup>                              | t <sub>JIT(DJ)</sub>                |      |     |     |      | 250 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>4</sup> (see Figure 38)       |

| Type 1 Receiver                                                | ()                                  |      | 150 |     | ps   | FSx = GND,  V <sub>ID</sub>   = 400 mV, V <sub>IC</sub> = 1 V              |

| Type 2 Receiver                                                |                                     |      | 150 |     | ps   | FSx = V <sub>CC</sub> ,  V <sub>ID</sub>   = 400 mV, V <sub>IC</sub> = 1 V |

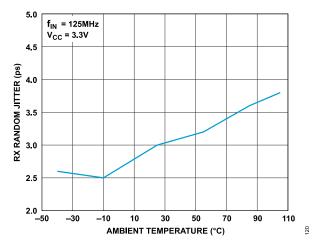

| Random Jitter, RMS                                             | t <sub>JIT(RJ)</sub>                |      |     |     |      | 250 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>4</sup> (see Figure 38)       |

| Type 1 Receiver                                                |                                     |      | 3   |     |      | FSx = GND,  V <sub>ID</sub>   = 400 mV, V <sub>IC</sub> = 1 V              |

| Type 2 Receiver                                                |                                     |      | 3   |     |      | $FSx = V_{CC}$ , $ V_{ID}  = 400 \text{ mV}$ , $V_{IC} = 1 \text{ V}$      |

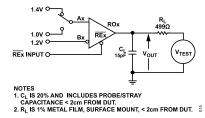

| Disable Time <sup>1</sup>                                      |                                     |      |     |     |      |                                                                            |

| From High Level                                                | t <sub>PHZ</sub>                    |      |     | 10  | ns   | See Figure 36 and Figure 37                                                |

## Table 4.

| Parameter                                  | Symbol           | Min | Тур | Max | Unit | Test Conditions/Comments    |

|--------------------------------------------|------------------|-----|-----|-----|------|-----------------------------|

| From Low Level<br>Enable Time <sup>1</sup> | t <sub>PLZ</sub> |     |     | 10  | ns   | See Figure 36 and Figure 37 |

| To High Level                              | t <sub>PZH</sub> |     |     | 15  | ns   | See Figure 36 and Figure 37 |

| To Low Level                               | t <sub>PZL</sub> |     |     | 15  | ns   | See Figure 36 and Figure 37 |

<sup>1</sup> Timing parameters are guaranteed by design and characterization. Values do not include stimulus jitter.

$^2$  t<sub>SK(O)</sub> is defined as the difference in propagation delay between the fastest and slowest channel on the same device.

<sup>3</sup> t<sub>SK(PP)</sub> is defined as the difference between the propagation delays of two devices between any specified terminals. This specification applies to devices at the same V<sub>CC</sub> and temperature and with identical packages and test circuits.

<sup>4</sup>  $t_{R} = t_{F} = 0.5 \text{ ns} (10\% \text{ to } 90\%)$

$^5$  50 ± 1% duty cycle, measured over 30,000 samples.

$^{\rm 6}$  Deterministic jitter includes jitter due to pulse skew (t\_{SK}).

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 5.

| Rating           |

|------------------|

| -0.5 V to +4 V   |

| -0.5 V to +4 V   |

| -0.5 V to +4.5 V |

| -1.8 V to +4 V   |

| -0.3 V to +4 V   |

| -40°C to +105°C  |

| -65°C to +150°C  |

|                  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operation environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

## Table 6. Thermal Resistance

| Package Type         | θ <sub>JA</sub> | Unit |

|----------------------|-----------------|------|

| CP-48-5 <sup>1</sup> | 30.2            | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with no bias. See JEDEC JESD-51.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JE-DEC JS-002.

International Electrotechnical Commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2

# ESD Ratings for ADN4680E

#### Table 7. ADN4680E, 48-Lead LFCSP

| ESD Model | Withstand Threshold (V)     | Class                |

|-----------|-----------------------------|----------------------|

| HBM       | ≥±8,000 (contact discharge) | 3B <sup>1</sup>      |

|           | ≥±15,000 (air discharge)    | 3B <sup>2</sup>      |

| FICDM     | ≥±1,250                     | C5 <sup>1</sup>      |

| IEC       | ≥±8,000 (contact discharge) | Level 4 <sup>2</sup> |

|           | ≥±10,000 (air discharge)    | Level 3 <sup>2</sup> |

<sup>1</sup> This class is for all pins.

<sup>2</sup> This class is for the A1 to A4 and B1 to B4 pins only.

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

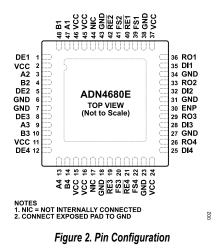

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

### Table 8. Pin Function Descriptions

| Pin No.                             | Mnemonic               | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 8, 12                         | DE1 to DE4             | Driver Output Enable. A logic high on the DE1 to DE4 pins enables the corresponding driver differential outputs. A logic low on the DE1 to DE4 pins places the corresponding driver differential outputs in a high impedance state. If left floating, the DE1 to DE4 pins are internally pulled to logic low.                                                          |

| 2, 11, 15, 16, 24,<br>37, 45, 46    | V <sub>CC</sub>        | Power Supply (3.3 V $\pm$ 0.3 V). All V <sub>CC</sub> pins must be connected externally to the supply. Decouple the V <sub>CC</sub> pins to GND with 0.1 $\mu$ F capacitors.                                                                                                                                                                                           |

| 3, 9, 13, 47                        | A2, A3, A4, A1         | Noninverting Receiver Input A and Noninverting Driver Output A for Each Transceiver.                                                                                                                                                                                                                                                                                   |

| 4, 10, 14, 48                       | B2, B3, B4, B1         | Inverting Receiver Input B and Inverting Driver Output B for Each Transceiver.                                                                                                                                                                                                                                                                                         |

| 6, 7, 18, 23, 27,<br>31, 34, 38, 43 | GND                    | Ground. All GND pins must be externally connected to ground.                                                                                                                                                                                                                                                                                                           |

| 17, 44                              | NIC                    | Not Internally Connected. The NIC pins are not internally connected.                                                                                                                                                                                                                                                                                                   |

| 19, 21, 40, 42                      | RE3 , RE4,<br>RE1, RE2 | Receiver Output Enable. A logic low on the $\overline{RE1}$ to $\overline{RE4}$ pins enables the corresponding receiver output. A logic high on the $\overline{RE1}$ to $\overline{RE4}$ pins places the corresponding receiver output in a high impedance state. If left floating, the $\overline{RE1}$ to $\overline{RE4}$ pins are internally pulled to logic high. |

| 20, 22, 39, 41                      | FS3, FS4, FS1,<br>FS2  | Receiver Fail-Safe Enable. A logic high on the FS1 to FS4 pins enables Type 2 receiver functionality for the corresponding receiver inputs (offset threshold). A logic low on the FS1 to FS4 pins enables Type 1 receiver functionality (symmetrical thresholds). If left floating, the FS1 to FS4 pins are internally pulled to logic high.                           |

| 25, 28, 32, 35                      | DI4, DI3, DI2,         | Driver Inputs. When enabled (the corresponding DE1 to DE4 pins are logic high, and ENP is logic high):                                                                                                                                                                                                                                                                 |

|                                     | DI1                    | A logic low on the DI1 to DI4 pins forces the corresponding noninverting driver output low and inverting output high, whereas a logic high on the DI1 to DI4 pins forces the noninverting output high and inverting output low. If left floating, the DI1 to DI4 pins are internally pulled to logic low.                                                              |

| 26, 29, 33, 36                      | RO4, RO3,<br>RO2, RO1  | Receiver Outputs. When the receiver is enabled (the corresponding RE1 to RE4 pins are logic low, and ENP is logic high), the following results:                                                                                                                                                                                                                        |

|                                     |                        | In Type 1 receiver mode (the corresponding FS1 to FS4 pins are logic low), if $Ax - Bx \ge +50$ mV, the output is logic high, and if $Ax - Bx \le -50$ mV, the output is logic low.                                                                                                                                                                                    |

|                                     |                        | In Type 2 receiver mode (the corresponding FS1 to FS4 pins are logic high), if $Ax - Bx \ge +150$ mV, the output is logic high, and if $Ax - Bx \le +50$ mV, the output is logic low.                                                                                                                                                                                  |

|                                     |                        | The receiver outputs are undefined outside of these conditions.                                                                                                                                                                                                                                                                                                        |

| 30                                  | ENP                    | Global Device Power Enable Pin. The device is active when logic high is applied to the ENP pin. Power-down mode when logic low is applied (overrides all other enable pins for the global device low power shutdown). If left floating, the ENP pin is internally pulled to logic low.                                                                                 |

|                                     | EPAD                   | Exposed Pad. The exposed pad must be connected to ground for proper operation.                                                                                                                                                                                                                                                                                         |

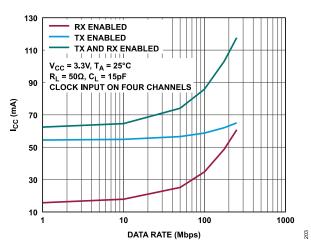

Figure 3.  $I_{CC}$  vs. Data Rate (Receiver  $V_{ID}$  = 400 mV and  $V_{IC}$  = 1 V)

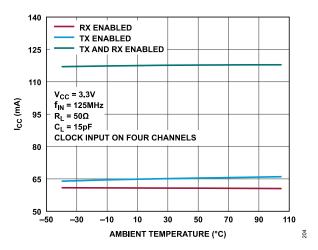

Figure 4.  $I_{CC}$  vs. Ambient Temperature (Receiver  $V_{ID}$  = 400 mV and  $V_{IC}$  = 1 V)

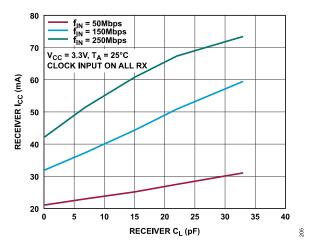

Figure 5. Receiver  $I_{CC}$  vs. Receiver  $C_L$  (Receiver  $V_{ID}$  = 400 mV and  $V_{IC}$  = 1 V)

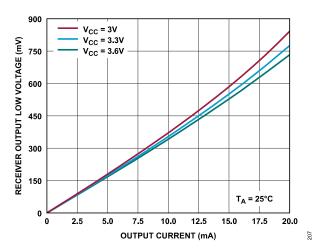

Figure 6. Receiver Output Low Voltage vs. Output Current

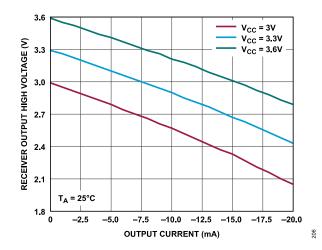

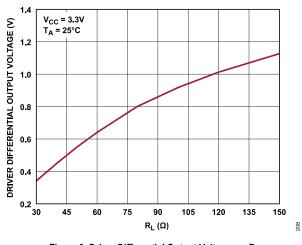

Figure 8. Driver Differential Output Voltage vs. RL

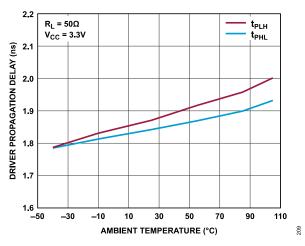

Figure 9. Driver Propagation Delay vs. Ambient Temperature

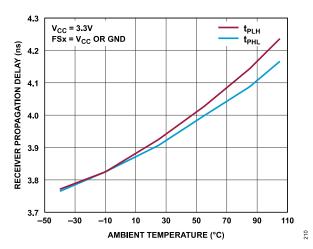

Figure 10. Receiver Propagation Delay vs. Ambient Temperature  $(V_{ID} = 400 \text{ mV} \text{ and } V_{IC} = 1.1 \text{ V})$

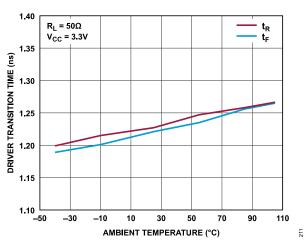

Figure 11. Driver Transition Time vs. Ambient Temperature

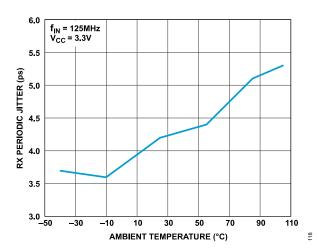

Figure 12. Transmitter Periodic Jitter, RMS vs. Ambient Temperature

Figure 13. Transmitter Cycle to Cycle Jitter, RMS vs. Ambient Temperature

Figure 14. Transmitter Random Jitter, RMS vs. Ambient Temperature

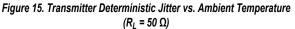

Figure 16. Transmitter Deterministic Jitter vs. Data Rate ( $R_L$  = 50  $\Omega$ )

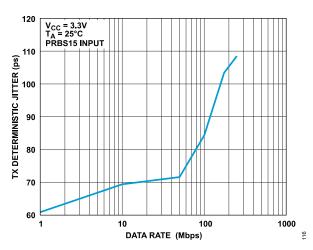

Figure 17. Driver Output Eye Pattern ( $V_{CC}$ = 3.3 V,  $T_A$ = 25 °C, Data Rate = 250 Mbps, PRBS15 Input, and  $R_L$  = 50  $\Omega$ )

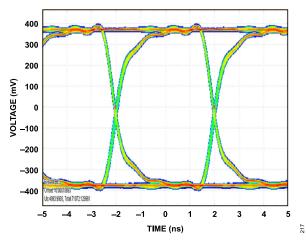

Figure 18. Receiver Periodic Jitter, RMS vs. Ambient Temperature  $(V_{ID} = 400 \text{ mV} \text{ and } V_{IC} = 1.1 \text{ V})$

Figure 19. Receiver Cycle to Cycle Jitter, RMS vs. Ambient Temperature  $(V_{ID} = 400 \text{ mV} \text{ and } V_{IC} = 1.1 \text{ V})$

Figure 20. Receiver Random Jitter, RMS vs. Ambient Temperature  $(V_{ID} = 400 \text{ mV} \text{ and } V_{IC} = 1.1 \text{ V})$

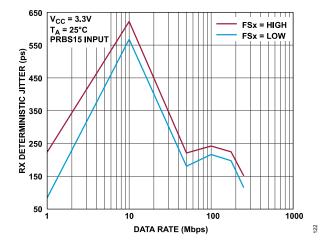

Figure 22. Receiver Deterministic Jitter vs. Data Rate ( $V_{ID}$  = 400 mV and  $V_{IC}$  = 1.1 V)

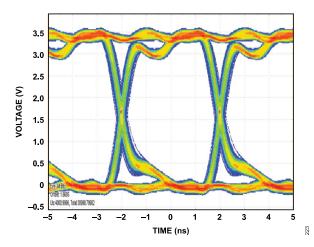

Figure 23. Receiver Output Eye Pattern ( $V_{CC}$ = 3.3 V,  $T_A$ = 25 °C, Data Rate = 200 Mbps, PRBS15 Input, and  $C_L$  = 15 pF)

# **TEST CIRCUITS AND SWITCHING CHARACTERISTICS**

# DRIVER VOLTAGE AND CURRENT MEASUREMENTS

Figure 25. Driver Common-Mode Output Voltage Measurement

Figure 27. Driver Short Circuit

Figure 28. Driver Common-Mode Output Voltage (Steady State)

Figure 26. Maximum Steady-State Output Voltage Measurement (S1 Is Switch 1)

10

11

# **TEST CIRCUITS AND SWITCHING CHARACTERISTICS**

## **DRIVER TIMING MEASUREMENTS**

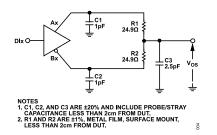

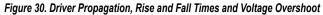

Figure 29. Driver Timing Measurement Circuit

NOTES 1. C1, C2, C3, AND C4 INCLUDE PROBE/STRAY CAPACITANCE. 2. R1 AND R2 ARE METAL FILM, SURFACE MOUNT.

Figure 31. Driver Enable and Disable Time Circuit

NOTES 1. INPUT PULSE GENERATOR: 2MHz; 50% ±5% DUTY CYCLE;  $t_R, t_F \le 1$ ns. 2. MEASURED ON TEST EQUIPMENT WITH –3dB BANDWIDTH ≥ 1GHz.

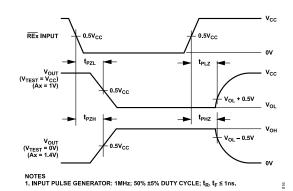

Figure 32. Driver Enable and Disable Times

Figure 33. Driver Period, Cycle to Cycle, Random and Deterministic Jitter Characteristics

# **TEST CIRCUITS AND SWITCHING CHARACTERISTICS**

# **RECEIVER TIMING MEASUREMENTS**

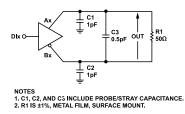

Figure 34. Receiver Timing Measurement Circuit

NOTES 1. INPUT PULSE GENERATOR: 1MHz; 50% ±5% DUTY CYCLE;  $t_R, t_F \le 1ns.$  2. MEASURED ON TEST EQUIPMENT WITH –3dB BANDWDTH  $\ge 1$ GHz.

Figure 35. Receiver Propagation and Rise and Fall Times

Figure 36. Receiver Enable and Disable Time Circuit

Figure 37. Receiver Enable and Disable Times

PERIOD AND CYCLE-TO-CYCLE JITTER RANDOM AND DETERMINISTIC JITTER VA INPUT  $V_A - V_B$ INPLIT (PRBS) (CLOCK) v, 1/f0 VOH VOH OUTPUT OUTPUT 0.5V<sub>CC</sub> 0.5V<sub>CC</sub> 0.5V<sub>CC</sub> 0.5V<sub>CC</sub> (IDEAL) (ACTUAL) VoL VoL 1/f0  $t_{JIT(DJ)} + t_{JIT(RJ)}$ v<sub>он</sub> NOTES 1. INPUT PULSE GENERATOR: OUTPUT TEKTRONIX AWG5208 ARBITRARY WAVEFORM GENERATOR 0.5V<sub>CC</sub> 0.5V<sub>CC</sub> 0.5V<sub>CC</sub> (ACTUAL) 2. MEASURED USING TEKTRONIX VOL DPO7254 WITH TAP3500 PROBE AND DPOJET SOFTWARE. t<sub>c(n)</sub>  $\mathbf{t}_{c(n+1)}$  $\mathbf{t}_{\mathsf{JIT}(\mathsf{PER})} = |\mathbf{t}_{\mathsf{c}(n)} - 1/f0|$  $\mathbf{t}_{\mathsf{JIT}(\mathsf{CYC})} = |\mathbf{t}_{\mathsf{c}(n)} - \mathbf{t}_{\mathsf{c}(n+1)}|$ 017

14

Figure 38. Receiver Period, Cycle to Cycle, Deterministic and Random Jitter Characteristics

# THEORY OF OPERATION

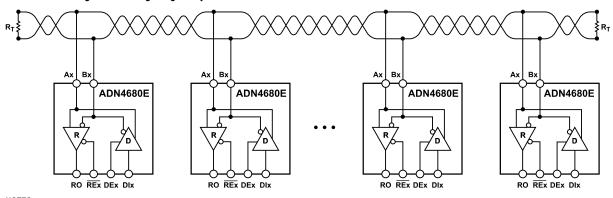

The ADN4680E comprises four transceivers for transmitting and receiving M-LVDS at high data rates of up to 250 Mbps NRZ. Each device has a differential line driver and a differential line receiver, allowing each device to send and receive data. The drivers and receivers are connected in half-duplex configuration, allowing a transceiver to transmit or to receive but not simultaneously. Figure 40 shows a typical half-duplex bus topology for M-LVDS.

M-LVDS expands on the established LVDS method by allowing bidirectional communication between more than two nodes. Up to 32 nodes can connect to a standard M-LVDS bus. The ADN4680E is optimized for low dynamic power consumption in applications that utilize multiple high speed M-LVDS lanes.

# THREE-STATE BUS CONNECTION

The outputs of the device can be placed in a high impedance state by disabling the driver or the receiver. Placing the driver in a high impedance state allows several driver outputs to connect to a single M-LVDS bus. Note that, on each bus line, only one driver can be enabled at a time, but many receivers can be enabled simultaneously.

Each driver can be enabled or disabled using the driver enable pins (DE1 to DE4). The DEx pins enable the driver outputs when driven logic high. When driven logic low, the DEx pins put the driver outputs into a high impedance state. Similarly, active low receiver enable pins ( $\overline{RE1}$  to  $\overline{RE4}$ ) control each receiver. Driving an  $\overline{REx}$ pin low enables the corresponding receiver output, whereas driving

Table 11. Each Receiver (see Table 9 for the Abbreviation Definitions)

an REx pin high puts the corresponding receiver output into a high impedance state. The M-LVDS driver outputs remain in a high impedance state while the transceiver is not powered.

Truth tables for driver and receiver output states under various conditions are shown in Table 10 and Table 11.

# TRUTH TABLES

### Table 9. Truth Table Abbreviation Definitions

| Abbreviation | Description           |

|--------------|-----------------------|

| н            | High level            |

| L            | Low level             |

| Х            | Don't care            |

| I            | Indeterminate         |

| Z            | High impedance (off)  |

| NC           | Disconnected/no input |

Table 10. Each Driver (See Table 9 for the Abbreviation Definitions)

|                 |         | Inputs  |     | Outputs |    |  |

|-----------------|---------|---------|-----|---------|----|--|

| V <sub>cc</sub> | ENP     | DEx     | Dix | Ax      | Bx |  |

| On              | Н       | Н       | Н   | Н       | L  |  |

| On              | Н       | Н       | L   | L       | Н  |  |

| On              | Н       | н       | NC  | L       | Н  |  |

| On              | Х       | L or NC | X   | Z       | Z  |  |

| On              | L or NC | Х       | X   | Z       | Z  |  |

| Off             | X       | Х       | Х   | Z       | Z  |  |

|                 | Inputs  |         |         |                         |               |     |

|-----------------|---------|---------|---------|-------------------------|---------------|-----|

| V <sub>cc</sub> | ENP     | REx     | FSx     | Ax – Bx                 | Receiver Mode | ROx |

| On              | Н       | L       | L       | ≥+50 mV                 | Туре 1        | Н   |

| On              | Н       | L       | L       | ≤-50 mV                 | Type 1        | L   |

| On              | Н       | L       | L       | −50 mV < A − B < +50 mV | Type 1        | I   |

| On              | Н       | L       | L       | NC                      | Type 1        | I   |

| On              | н       | L       | L       | Short circuit           | Type 1        | I   |

| On              | Н       | L       | H or NC | ≥+150 mV                | Type 2        | Н   |

| On              | Н       | L       | H or NC | ≤+50 mV                 | Type 2        | L   |

| On              | н       | L       | H or NC | 50 mV < A – B < 150 mV  | Type 2        | I   |

| On              | Н       | L       | H or NC | NC                      | Type 2        | L   |

| On              | Н       | L       | H or NC | Short circuit           | Type 2        | L   |

| On              | Х       | H or NC | Х       | X                       | x             | Z   |

| On              | L or NC | X       | Х       | X                       | x             | Z   |

| Off             | Х       | X       | Х       | X                       | X             | l   |

# THEORY OF OPERATION

# GLITCH FREE POWERING UP AND POWERING DOWN

To minimize disruption to the bus when adding or removing nodes from the network, the M-LVDS outputs of the device are kept glitch free when the device is powering up or powering down. This feature allows insertion of a device onto a live M-LVDS bus because the bus outputs are not switched on before the device is fully powered. In addition, all outputs are placed in a high impedance state when the device is powered off.

# FAULT CONDITIONS

The ADN4680E contains short-circuit current protection that protects the device under fault conditions in case of short circuits on the bus. This protection limits the transmitter output current in a fault condition to 24 mA for short-circuit faults between -1 V and +3.4 V. Any network fault must be cleared to avoid data transmission errors and to ensure reliable operation of the data network and of any devices that are connected to the network.

# RECEIVER INPUT THRESHOLDS AND FAIL-SAFE

Two receiver types are pin-selectable using the FSx pins for each receiver. Protection against short circuits is integrated into each receiver.

Type 1 receivers (configured with FSx low) incorporate 15 mV of hysteresis to ensure that slow changing signals or a loss of input does not result in the oscillation of the receiver output. Type 1 receiver thresholds are  $\pm$ 50 mV. Therefore, the state of the receiver output is indeterminate if the differential between Ax and Bx is approximately 0 V. This state occurs if the bus is idle (approximately 0 V on both Ax and Bx), with no drivers enabled on the attached nodes.

Type 2 receivers (configured with FSx high or open) have an open-circuit, short-circuit, and bus idle (terminated) fail-safe. The

input threshold is offset by 100 mV to ensure that a logic low is present on the receiver output during the bus idle or receiver open-circuit conditions.

The different receiver thresholds for the two receiver types are illustrated in Figure 39. See Table 11 for the receiver output states under various conditions.

Figure 39. Input Threshold Voltages ( $V_{IA}$  Is the Voltage Input on Pin Ax, and  $V_{IB}$  Is the Voltage Input on Pin Bx.)

# SIXTY-FOUR TRANSCEIVERS ON A NETWORK

The TIA/EIA-899 standard specifies a maximum of 32 M-LVDS transceivers connected to the same differential pair. The ADN4680E receiver exceeds these requirements by a factor of two, with a reduced input current allowing more devices to be connected to the network without excessively loading a transmitter. Up to 64 transceivers from the ADN4680E can be connected to a single network. The ac loading effects of any M-LVDS transceivers on the network must also be considered. See the M-LVDS Design Considerations section for more details.

019

# **APPLICATIONS INFORMATION**

M-LVDS extends the low power, high speed, differential signaling of LVDS to multipoint systems where multiple nodes are connected over short distances in a bus topology network.

With M-LVDS, a transmitting node drives a differential signal across a transmission medium such as a twisted pair cable. The transmitted differential signal allows other receiving nodes that are connected along the bus to detect a differential voltage that can then be converted back into a single-ended logic signal by the receiver.

The communication line is typically terminated at both ends by resistors ( $R_T$ ), the value of which is chosen to match the characteristic impedance of the medium (typically 100  $\Omega$ ). For half-duplex multipoint applications such as the one shown in Figure 40, only one driver can be enabled at any time.

NOTES 1.  $R_{\rm T}$  IS EQUAL TO THE CHARACTERISTIC IMPEDANCE OF THE COMMUNICATION MEDIUM.

Figure 40. Typical Half-Duplex M-LVDS Network

# **APPLICATIONS INFORMATION**

# PCB LAYOUT

The ADN4680E must be adequately decoupled with 0.1  $\mu F$  capacitors between the  $V_{CC}$  and GND pins.

The RO1 to RO4 pins of the ADN4680E output a 3.3 V singleended signal with fast switching edges of approximately 1 ns. Keep these traces short and routed over a continuous reference plane to minimize radiated emissions. Edge coupling to the reference plane helps minimize fringing electric fields.

The RO1 to RO4 trace capacitance affects the switching supply current drawn from the  $V_{CC}$  supply. In applications where the low power consumption is desired, minimize the RO1 to RO4 trace length and capacitance (see Figure 5).

For optimum thermal performance, the exposed pad of the LFCSP must be connected to GND and connected to a solid reference plane through an array of 16 vias with diameter of 0.3 mm, or similar.

# **M-LVDS DESIGN CONSIDERATIONS**

In a backplane or cabled M-LVDS network, the signal integrity is dependent on good design practices. Follow these guidelines to minimize adverse effects on noise margin caused by reflections:

- Route the M-LVDS signals as an impedance controlled differential pair, as either an edge-coupled microstrip or an embedded edge-coupled stripline. The stripline is the preferred method.

- A differential characteristic impedance of between 100 Ω and 130 Ω is recommended. In heavily loaded M-LVDS networks, a larger characteristic impedance gives the best noise margin.

- Maintain a uniform impedance across the M-LVDS network where possible. Avoid unnecessary discontinuities, such as vias or large test points, along the M-LVDS signals.

- Place M-LVDS transceiver modules at uniform distances across the transmission line where possible.

- Place termination resistors within 2.5 cm of the end of the cable or backplane.

- Keep any stub lengths off the main cable or backplane to less than 2.5 cm.

- ▶ Minimize connector capacitance where possible.

- Note that Type 2 receivers include fail-safe functionality but have reduced noise margin when receiving data. Configure receivers as Type 1 where receiver fail-safe functionality is not required.

- ► In heavily loaded M-LVDS networks with multiple devices, match the termination resistors to the effective impedance (Z<sub>EFF</sub>) of the network. The effective impedance of the network is determined by the capacitance of the network, the capacitance of each transceiver module, and the distance between them as follows:

$$Z_{EFF} = \sqrt{\frac{L_0}{C_0 + \frac{C_L}{D}}} = Z_0 \sqrt{\frac{1}{1 + \frac{C_L}{C_0 D}}}$$

(1)

where:

Z<sub>EFF</sub> is the effective characteristic impedance.

$Z_0^{-}$  is the characteristic impedance of the M-LVDS signals.

$L_0$  is the inductance per unit length of the M-LVDS signals.

$C_0$  is the differential capacitance per unit length of the M-LVDS signals.

$C_{L}^{\tilde{}}$  is the differential capacitance of the load (the transceiver module).

D is the distance between the loads.

# **EXTENDING THE SPI OVER M-LVDS**

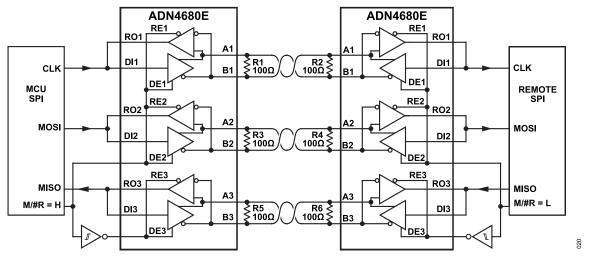

The ADN4680E can extend the reach and reliability of a serial peripheral interface (SPI). At a high clock rate and transmission distance, the single-ended signals used in the SPI suffer from poor electromagnetic compatibility (EMC). Differential extenders are commonly used to allow the reliable transmission of the SPI over longer distances. The ADN4680E has several features that make it well suited for this:

- A data rate of up to 125 MHz supports the highest SPI clock rates with minimal added skew and jitter.

- ► A quad channel transceiver that allows a single device to extend the CLK, MOSI, MISO, and SS signals of the SPI.

- A half-duplex configuration allows for configurable channel directionality.

- The low propagation delay of the transceiver minimizes the impact on transmission distance at higher SPI clock frequencies.

- The robust EMC protection on the M-LVDS input and output pins is suitable for operation in harsh environments.

- The M-LVDS common-mode range allows communication in the presence of up to ±2 V of ground offset.

In Figure 41, the CLK, MOSI, and MISO signals of the SPI are extended over several meters between a processor and a remote device. The same schematic can function as either a master or a remote interface, selectable via a single logic pin (M/#R). The fourth transceiver of the ADN4680E is not shown and can be used to extend the other SPI signals, such as the chip select line or an interrupt from the remote device to the microcontroller unit (MCU).

# **APPLICATIONS INFORMATION**

Figure 41. SPI over M-LVDS with ADN4680E

A requirement of the SPI is that the round-trip time delay between the master and the peripheral is less than half the SPI clock period. This requirement places a restriction on the allowed latency, which in turn, limits the maximum cable distance between the master and the peripheral. Devices placed within the signal path, such as transceivers, digital isolators, and level translators, add further propagation delay, which reduces the maximum cable length. The ADN4680E features 10× lower propagation delay than similar RS-485-based solutions, allowing a 10 MHz SPI to operate over several meters of Category 5e (Cat 5e) cabling.

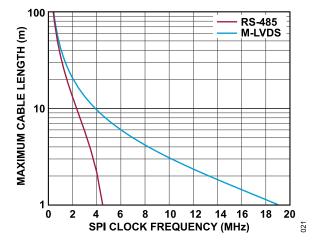

Figure 42. Maximum Cable Length vs. SPI Clock Frequency

# **OUTLINE DIMENSIONS**

Updated: September 09, 2021

# **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                   | Packing Quantity | Package<br>Option |

|--------------------|-------------------|---------------------------------------|------------------|-------------------|

| ADN4680EBCPZ       | –40°C to +105°C   | 48-Lead LFCSP (7 mm × 7 mm with EPAD) | Tray, O          | CP-48-5           |

| ADN4680EBCPZ-RL    | –40°C to +105°C   | 48-Lead LFCSP (7 mm × 7 mm with EPAD) | Reel, 2500       | CP-48-5           |

<sup>1</sup> Z = RoHS Compliant Part.

# **EVALUATION BOARDS**

| Model                         | Description               |

|-------------------------------|---------------------------|

| EVAL-ADN4680EEBZ <sup>1</sup> | ADN4680E Evaluation Board |

<sup>1</sup> Z = RoHS Compliant Part.