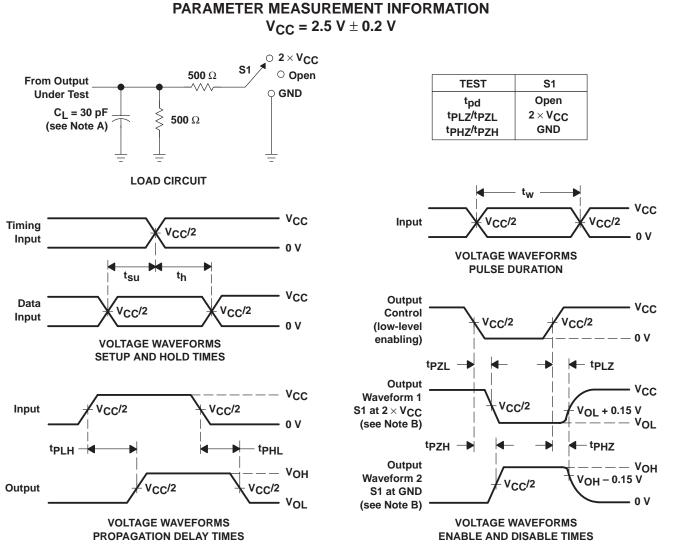

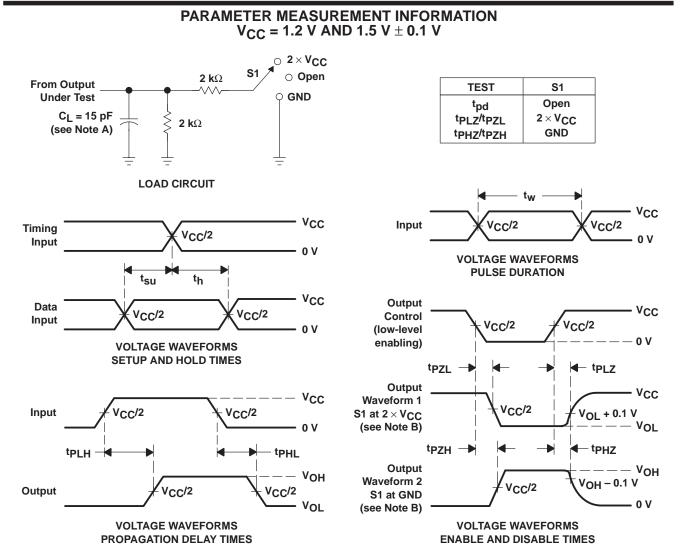

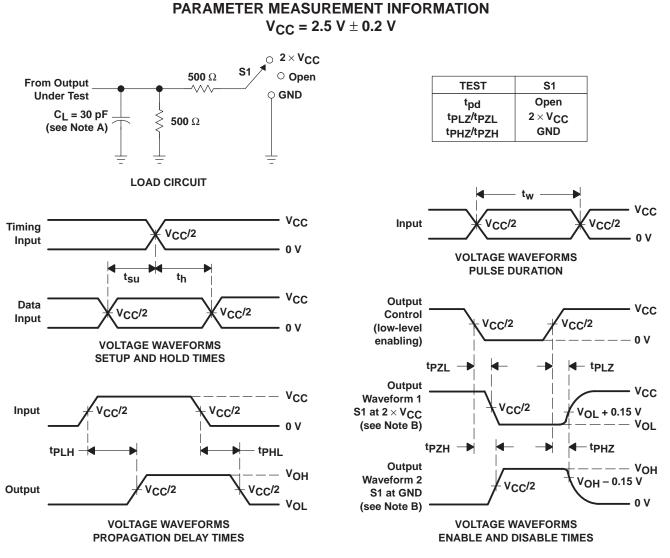

- NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

All input pulses are supplied by generators begins the following characteristics: PBP < 10 MHz, 7a = 50.0 t < 2 no. t < 2 no.</li>

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2 ns, t<sub>f</sub>  $\leq$  2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

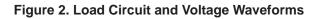

#### Figure 4. Load Circuit and Voltage Waveforms

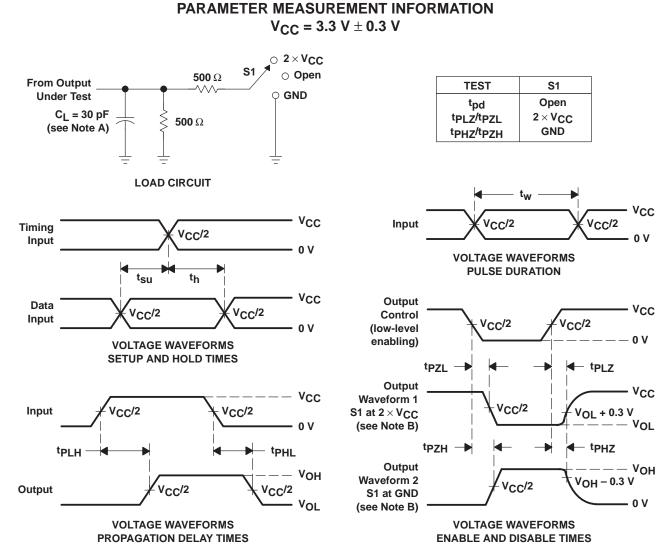

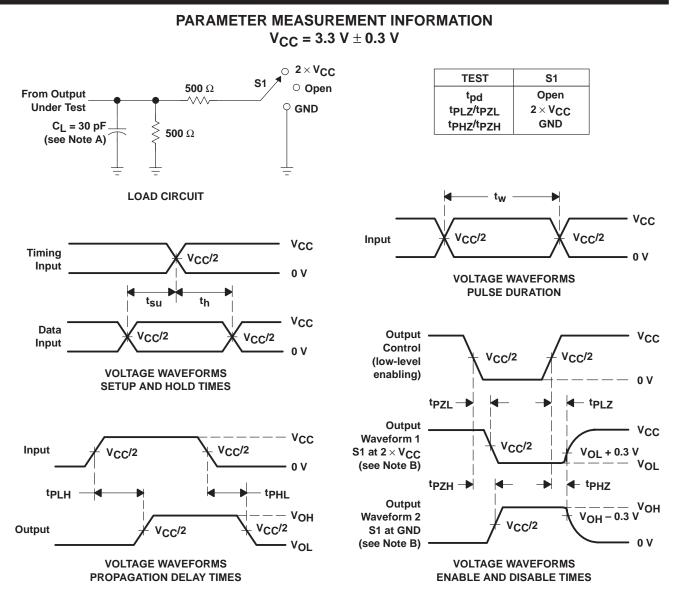

#### NOTES: A. Cl includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> ≤ 2 ns, t<sub>f</sub> ≤ 2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tPLZ and tPHZ are the same as tdis.

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G. t<sub>PLH</sub> and t<sub>PHL</sub> are the same as t<sub>pd</sub>.

#### Figure 5. Load Circuit and Voltage Waveforms

- Member of the Texas Instruments *Widebus™* Family

- *EPIC*<sup>™</sup> (Enhanced-Performance Implanted CMOS) Submicron Process

- DOC<sup>™</sup> (Dynamic Output Control) Circuit Dynamically Changes Output Impedance, Resulting in Noise Reduction Without Speed Degradation

- Less Than 2-ns Maximum Propagation Delay at 2.5-V and 3.3-V V<sub>CC</sub>

- Dynamic Drive Capability Is Equivalent to Standard Outputs With I<sub>OH</sub> and I<sub>OL</sub> of ±24 mA at 2.5-V V<sub>CC</sub>

- Overvoltage-Tolerant Inputs/Outputs Allow Mixed-Voltage-Mode Data Communications

- I<sub>off</sub> Supports Partial-Power-Down Mode Operation

- Package Options Include Plastic Thin Shrink Small-Outline (DGG) and Thin Very Small-Outline (DGV) Packages

## description

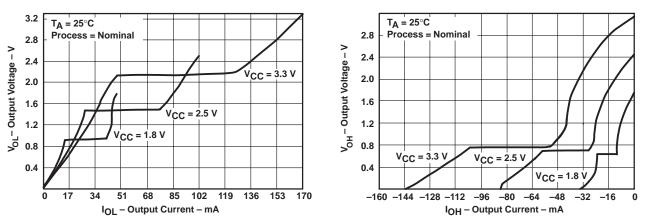

A Dynamic Output Control (DOC) circuit is implemented, which, during the transition, initially lowers the output impedance to effectively drive the load and, subsequently, raises the impedance to reduce noise. Figure 1 shows typical  $V_{OL}$  vs  $I_{OL}$  and  $V_{OH}$  vs  $I_{OH}$  curves to illustrate the output impedance and drive capability of the circuit. At the beginning of the signal transition, the DOC circuit provides a maximum dynamic drive that is equivalent to a high-drive standard-output device. For more information, refer to the TI application reports, *AVC Logic Family Technology and Applications*, literature number SCEA006, and *Dynamic Output Control (DOC<sup>TM</sup>) Circuitry Technology and Applications*, literature number SCEA009.

Figure 1. Output Voltage vs Output Current

This 20-bit non-inverting buffer/driver is operational at 1.2-V to 3.6-V  $V_{CC}$ , but is designed specifically for 1.65-V to 3.6-V  $V_{CC}$  operation.

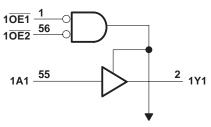

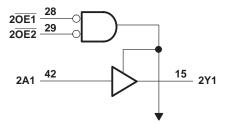

The SN74AVC16827 is composed of two 10-bit sections with separate output-enable signals. For either 10-bit buffer section, the two output-enable ( $1\overline{OE1}$  and  $1\overline{OE2}$  or  $2\overline{OE1}$  and  $2\overline{OE2}$ ) inputs must both be low for the corresponding Y outputs to be active. If either output-enable input is high, the outputs of that 10-bit buffer section are in the high-impedance state.

To ensure the high-impedance state during power up or power down,  $\overline{OE}$  should be tied to V<sub>CC</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

This device is fully specified for partial-power-down applications using  $I_{off}$ . The  $I_{off}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

DOC, EPIC, and Widebus are trademarks of Texas Instruments Incorporated.

## SN74AVC16827 20-BIT BUFFER/DRIVER WITH 3-STATE OUTPUTS SCES176F – DECEMBER 1998 – REVISED FEBRUARY 2000

## description (continued)

The SN74AVC16827 is characterized for operation from -40°C to 85°C.

#### terminal assignments

| DGG OR DGV PACKAGE<br>(TOP VIEW)                                                                                           |                                                                                                                                                                                                                            |                                                           |                                                                                                                            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10E1<br>1Y1<br>1Y2<br>GND<br>1Y3<br>1Y4<br>V <sub>CC</sub><br>1Y5<br>1Y6<br>1Y7<br>GND<br>1Y8<br>1Y9<br>1Y10<br>2Y1<br>2Y2 | (TOP)<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>15<br>16<br>10<br>11<br>12<br>13<br>14<br>15<br>10<br>11<br>12<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | <b>/IEW)</b> 56 55 54 53 52 51 50 49 48 47 46 43 43 42 41 | 10E2<br>1A1<br>1A2<br>GND<br>1A3<br>1A4<br>V <sub>CC</sub><br>1A5<br>1A6<br>1A7<br>GND<br>1A8<br>1A9<br>1A10<br>2A1<br>2A2 |  |  |  |  |

| 2Y1                                                                                                                        |                                                                                                                                                                                                                            | E                                                         |                                                                                                                            |  |  |  |  |

| 20E1                                                                                                                       | 28                                                                                                                                                                                                                         | 29                                                        | 20E2                                                                                                                       |  |  |  |  |

#### FUNCTION TABLE (each 10-bit buffer/driver)

| (••• |        |        |   |  |  |  |  |  |  |  |

|------|--------|--------|---|--|--|--|--|--|--|--|

|      | INPUTS | OUTPUT |   |  |  |  |  |  |  |  |

| OE1  | OE2    | Α      | Y |  |  |  |  |  |  |  |

| L    | L      | L      | L |  |  |  |  |  |  |  |

| L    | L      | Н      | н |  |  |  |  |  |  |  |

| н    | Х      | Х      | Z |  |  |  |  |  |  |  |

| Х    | н      | Х      | Z |  |  |  |  |  |  |  |

### SN74AVC16827 **20-BIT BUFFER/DRIVER** WITH 3-STATE OUTPUTS SCES176F - DECEMBER 1998 - REVISED FEBRUARY 2000

# logic symbol<sup>†</sup>

|            |    | 1 |   |              | 1  |       |

|------------|----|---|---|--------------|----|-------|

| 10E1       | 1  |   | & |              |    |       |

| 10E2       | 56 |   |   | EN1          |    |       |

| 20E1       | 28 | Ν | & |              |    |       |

|            | 29 | 2 |   | EN2          |    |       |

| 20E2       |    |   | L | ᆝᅟᆮ          |    |       |

| 1A1        | 55 |   |   | <br>1 1⊽     | 2  | 1Y1   |

| 1A2        | 54 |   |   |              | 3  | 1Y2   |

| 1A3        | 52 |   |   |              | 5  | 1Y3   |

| 1A3        | 51 |   |   |              | 6  | · 1Y4 |

| 1A4<br>1A5 | 49 |   |   |              | 8  | 1Y5   |

| 1A5        | 48 |   |   |              | 9  | 1Y6   |

| 1A0        | 47 |   |   |              | 10 | 1Y7   |

|            | 45 |   |   |              | 12 |       |

| 1A8        | 44 |   |   |              | 13 | 1Y8   |

| 1A9        | 43 |   |   |              | 14 | 1Y9   |

| 1A10       | 42 |   |   |              | 15 | 1Y10  |

| 2A1        | 41 |   |   | <b>1 2</b> ∇ | 16 | 2Y1   |

| 2A2        | 40 |   |   |              | 17 | 2Y2   |

| 2A3        | 38 |   |   |              | 19 | 2Y3   |

| 2A4        | 37 |   |   |              | 20 | 2Y4   |

| 2A5        | 36 |   |   |              | 21 | 2Y5   |

| 2A6        | 34 |   |   |              | 23 | 2Y6   |

| 2A7        | 33 |   |   |              | 24 | 2Y7   |

| 2A8        | 31 |   |   |              | 24 | 2Y8   |

| 2A9        | 30 |   |   |              | 20 | 2Y9   |

| 2A10       | 30 |   |   |              | 21 | 2Y10  |

|            |    |   |   |              | -  |       |

#### <sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

# logic diagram (positive logic)

**To Nine Other Channels**

**To Nine Other Channels**

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> 0.5 V to 4.6 V<br>Input voltage range, V <sub>I</sub> (see Note 1)0.5 V to 4.6 V<br>Voltage range applied to any output in the high-impedance or power-off state, V <sub>O</sub> |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (see Note 1)                                                                                                                                                                                                           |  |

| Voltage range applied to any output in the high or low state, VO                                                                                                                                                       |  |

| (see Notes 1 and 2)                                                                                                                                                                                                    |  |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                                                                                                                                                              |  |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0) –50 mA                                                                                                                                                      |  |

| Continuous output current, I <sub>O</sub> ±50 mA                                                                                                                                                                       |  |

| Continuous current through each V <sub>CC</sub> or GND ±100 mA                                                                                                                                                         |  |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): DGG package                                                                                                                                                   |  |

| DGV package 48°C/W                                                                                                                                                                                                     |  |

| Storage temperature range, T <sub>stg</sub>                                                                                                                                                                            |  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. This value is limited to 4.6 V maximum.

3. The package thermal impedance is calculated in accordance with JESD 51.

# SN74AVC16827 **20-BIT BUFFER/DRIVER** WITH 3-STATE OUTPUTS

SCES176F - DECEMBER 1998 - REVISED FEBRUARY 2000

## recommended operating conditions (see Note 4)

|                         |                                               |                                            | MIN                    | MAX                  | UNI            |  |

|-------------------------|-----------------------------------------------|--------------------------------------------|------------------------|----------------------|----------------|--|

| Vee                     | Supply yeltogo                                | Operating                                  | 1.4                    | 3.6                  | V              |  |

| VCC                     | Supply voltage                                | Data retention only                        | 1.2                    |                      | V              |  |

|                         |                                               | V <sub>CC</sub> = 1.2 V                    | V <sub>CC</sub>        |                      |                |  |

|                         |                                               | $V_{CC} = 1.4 \text{ V to } 1.6 \text{ V}$ | $0.65 \times V_{CC}$   |                      |                |  |

| √ін                     | High-level input voltage                      | V <sub>CC</sub> = 1.65 V to 1.95 V         | 0.65 × V <sub>CC</sub> |                      | V              |  |

|                         |                                               | $V_{CC}$ = 2.3 V to 2.7 V                  | 1.7                    |                      |                |  |

|                         |                                               | $V_{CC} = 3 V \text{ to } 3.6 V$           | 2                      |                      |                |  |

| V <sub>IL</sub> Low-lev |                                               | V <sub>CC</sub> = 1.2 V                    |                        | GND                  |                |  |

|                         |                                               | $V_{CC} = 1.4 V \text{ to } 1.6 V$         |                        | $0.35 \times V_{CC}$ |                |  |

|                         | Low-level input voltage                       | V <sub>CC</sub> = 1.65 V to 1.95 V         |                        | $0.35 \times V_{CC}$ | V              |  |

|                         |                                               | $V_{CC}$ = 2.3 V to 2.7 V                  |                        | 0.7                  |                |  |

|                         |                                               | $V_{CC} = 3 V \text{ to } 3.6 V$           |                        | 0.8                  |                |  |

| VI                      | Input voltage                                 |                                            | 0                      | 3.6                  | V              |  |

| Va                      | Output veltogo                                | Active state                               | 0                      | VCC                  | V              |  |

| VO                      | Output voltage                                | 3-state                                    | 0                      | 3.6                  | 1 <sup>v</sup> |  |

|                         |                                               | V <sub>CC</sub> = 1.4 V to 1.6 V           |                        | -2                   |                |  |

|                         | a da biak la sala sala sala sala sala         | V <sub>CC</sub> = 1.65 V to 1.95 V         |                        | -4                   | mA             |  |

| IOHS                    | Static high-level output current <sup>†</sup> | $V_{CC}$ = 2.3 V to 2.7 V                  |                        | -8                   |                |  |

|                         |                                               | $V_{CC} = 3 V \text{ to } 3.6 V$           |                        | -12                  |                |  |

|                         |                                               | V <sub>CC</sub> = 1.4 V to 1.6 V           |                        | 2                    |                |  |

|                         |                                               | V <sub>CC</sub> = 1.65 V to 1.95 V         |                        | 4                    | mA             |  |

| I <sub>OLS</sub> S      | Static low-level output current <sup>†</sup>  | $V_{CC}$ = 2.3 V to 2.7 V                  |                        | 8                    |                |  |

|                         |                                               | $V_{CC} = 3 V \text{ to } 3.6 V$           |                        | 12                   |                |  |

| Δt/Δv                   | Input transition rise or fall rate            | V <sub>CC</sub> = 1.4 V to 3.6 V           |                        | 5                    | ns/            |  |

| TA                      | Operating free-air temperature                | •                                          | -40                    | 85                   | °C             |  |

<sup>†</sup> Dynamic drive capability is equivalent to standard outputs with IOH and IOL of ±24 mA at 2.5-V VCC. See Figure 1 for VOL vs IOL and VOH vs IOH characteristics. Refer to the TI application reports, AVC Logic Family Technology and Applications, literature number SCEA006, and Dynamic Output Control (DOC<sup>TM</sup>) Circuitry Technology and Applications, literature number SCEA009.

NOTE 4: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

### SN74AVC16827 20-BIT BUFFER/DRIVER WITH 3-STATE OUTPUTS SCES176F – DECEMBER 1998 – REVISED FEBRUARY 2000

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                       | TEST                                     | CONDITIONS               | Vcc            | MIN                  | TYP† | MAX  | UNIT |  |

|-----------------|---------------------------------|------------------------------------------|--------------------------|----------------|----------------------|------|------|------|--|

|                 |                                 | I <sub>OHS</sub> = -100 μA               |                          | 1.4 V to 3.6 V | V <sub>CC</sub> -0.2 | 2    |      |      |  |

|                 |                                 | $I_{OHS} = -2 \text{ mA},$               | V <sub>IH</sub> = 0.91 V | 1.4 V          | 1.05                 |      |      |      |  |

| VOH             |                                 | $I_{OHS} = -4 \text{ mA},$               | V <sub>IH</sub> = 1.07 V | 1.65 V         | 1.2                  |      |      | V    |  |

|                 |                                 | $I_{OHS} = -8 \text{ mA},$               | VIH = 1.7 V              | 2.3 V          | 1.75                 |      |      |      |  |

|                 |                                 | $I_{OHS} = -12 \text{ mA},$              | V <sub>IH</sub> = 2 V    | 3 V            | 2.3                  |      |      |      |  |

|                 |                                 | I <sub>OLS</sub> = 100 μA                |                          | 1.4 V to 3.6 V |                      |      | 0.2  |      |  |

|                 |                                 | $I_{OLS} = 2 \text{ mA},$                | V <sub>IL</sub> = 0.49 V | 1.4 V          |                      |      | 0.4  |      |  |

| V <sub>OL</sub> |                                 | I <sub>OLS</sub> = 4 mA,                 | V <sub>IL</sub> = 0.57 V | 1.65 V         |                      |      | 0.45 | V    |  |

|                 |                                 | I <sub>OLS</sub> = 8 mA,                 | V <sub>IL</sub> = 0.7 V  | 2.3 V          |                      |      | 0.55 |      |  |

|                 |                                 | I <sub>OLS</sub> = 12 mA,                | V <sub>IL</sub> = 0.8 V  | 3 V            |                      |      | 0.7  |      |  |

| lj              | Control inputs                  | V <sub>I</sub> = V <sub>CC</sub> or GND  |                          | 3.6 V          |                      |      | ±2.5 | μA   |  |

| loff            |                                 | VI or VO = 3.6 V                         |                          | 0              |                      |      | ±10  | μA   |  |

| loz             |                                 | $V_{O} = V_{CC} \text{ or } GND$         |                          | 3.6 V          |                      |      | ±10  | μΑ   |  |

| ICC             |                                 | V <sub>I</sub> = V <sub>CC</sub> or GND, | IO = 0                   | 3.6 V          |                      |      | 40   | μA   |  |

|                 | Control in nuto                 |                                          |                          | 2.5 V          |                      |      |      |      |  |

| c <sub>i</sub>  | Control inputs                  |                                          |                          | 3.3 V          |                      |      |      | - 5  |  |

|                 | $V_{I} = V_{CC} \text{ or } GN$ | vI = vCC or GND                          |                          | 2.5 V          |                      |      |      | pF   |  |

|                 | Data inputs                     |                                          |                          |                |                      |      |      | 1    |  |

| ~               | Quitauta                        |                                          |                          | 2.5 V          |                      |      |      |      |  |

| Co              | Outputs                         | $V_{O} = V_{CC} \text{ or } GND$         |                          | 3.3 V          |                      |      |      | pF   |  |

<sup>†</sup> Typical values are measured at  $T_A = 25^{\circ}C$ .

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figures 2 through 5)

| PARAMETER        | FROM TO<br>(INPUT) (OUTPUT) |          | V <sub>CC</sub> = 1.2 V | V <sub>CC</sub> =<br>± 0. | 1.5 V<br>1 V | V <sub>CC</sub> =<br>± 0.1 |     | V <sub>CC</sub> =<br>± 0.2 |     | V <sub>CC</sub> =<br>± 0.3 |     | UNIT |

|------------------|-----------------------------|----------|-------------------------|---------------------------|--------------|----------------------------|-----|----------------------------|-----|----------------------------|-----|------|

|                  |                             | (001701) | TYP                     | MIN                       | MAX          | MIN                        | MAX | MIN                        | MAX | MIN                        | MAX |      |

| <sup>t</sup> pd  | A                           | Y        |                         |                           |              |                            |     |                            |     |                            |     | ns   |

| ten              | OE                          | Y        |                         |                           |              |                            |     |                            |     |                            |     | ns   |

| <sup>t</sup> dis | OE                          | Y        |                         |                           |              |                            |     |                            |     |                            |     | ns   |

# switching characteristics, $T_A = 0^{\circ}C$ to $85^{\circ}C$ , $C_L = 0 \text{ pF}^{\ddagger}$

| PARAMETER       | FROM<br>(INPUT) | TO<br>(OUTPUT) | V <sub>CC</sub> = 3.3 V<br>± 0.15 V | UNIT |

|-----------------|-----------------|----------------|-------------------------------------|------|

|                 |                 | (001101)       | MIN MAX                             |      |

| <sup>t</sup> pd | A               | Y              |                                     | ns   |

<sup>‡</sup> Texas Instruments SPICE simulation data

### SN74AVC16827 20-BIT BUFFER/DRIVER WITH 3-STATE OUTPUTS SCES176F – DECEMBER 1998 – REVISED FEBRUARY 2000

### operating characteristics, T<sub>A</sub> = 25°C

| PARAMETER       |                   | TEST CONDITIONS  | ± 0.15 V                         | V <sub>CC</sub> = 2.5 V<br>± 0.2 V<br>TVD |     | UNIT |    |

|-----------------|-------------------|------------------|----------------------------------|-------------------------------------------|-----|------|----|

|                 |                   |                  |                                  | TYP                                       | TYP | TYP  |    |

| C .             | Power dissipation | Outputs enabled  | $C_1 = 0$ , $f = 10 \text{ MHz}$ |                                           |     |      | ٥F |

| C <sub>pd</sub> | capacitance       | Outputs disabled | $C_L = 0$ , $f = 10 \text{ MHz}$ |                                           |     |      | μr |

- NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2 ns, t<sub>f</sub>  $\leq$  2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tpl 7 and tpH7 are the same as tdis.

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G. tpLH and tpHL are the same as  $t_{pd}$ .

- NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>O</sub> = 50 Ω, t<sub>f</sub> ≤ 2 ns, t<sub>f</sub> ≤ 2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tPLZ and tPHZ are the same as tdis.

- F. tpzL and tpzH are the same as ten.

- G. tPLH and tPHL are the same as tpd.

#### Figure 3. Load Circuit and Voltage Waveforms

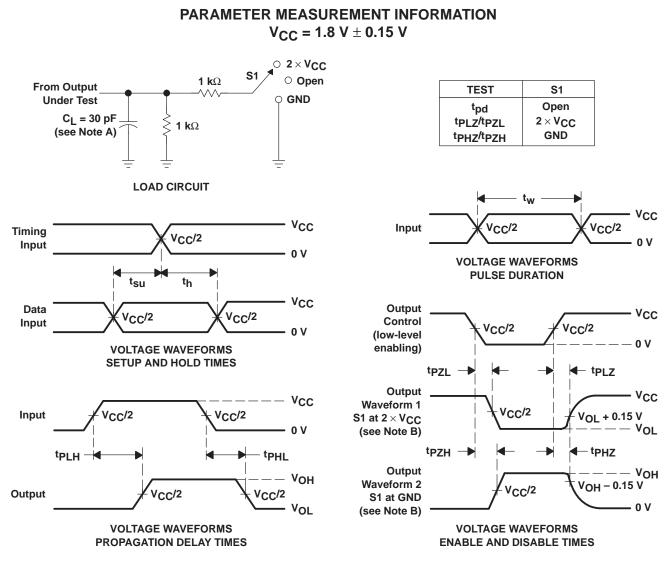

- NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>Q</sub> = 50 Ω, t<sub>f</sub> ≤ 2 ns, t<sub>f</sub> ≤ 2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G. tpLH and tpHL are the same as  $t_{pd}$ .

#### Figure 4. Load Circuit and Voltage Waveforms

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2 ns, t<sub>f</sub>  $\leq$  2 ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{P7I}$  and  $t_{P7H}$  are the same as  $t_{en}$ .

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

Figure 5. Load Circuit and Voltage Waveforms