October 1994

### PC87410 PCI-IDE Interface Controller

#### **General Description**

The PCI-IDE Interface Controller is designed to interface the IDE drive directly onto the PCI bus. It provides write posting and read pre-fetches, allowing the CPU to run concurrently with IDE cycles. It connects IDE drives "gluelessly" into the PCI bus and supports faster ATA devices using modes 1, 2 and 3 through PIO accesses. It supports dual IDE channels for up to four drives, and works seamlessly with the National Semiconductor's SuperI/OTM family of products.

A full suite of software drives included with device are fully tested with DOS 5.0-6.x, Windows 3.x-4.x, Windows NT, OS/2 2.x, Novell Netware 3.1x-4.x, and SCO UNIX 3.x.

#### **Key Features**

- Fully compatible with PCI specifications rev 2.0 (April, 1993)

- Programmable Base Address registers

- Interfaces with the 32 bits PCI local bus to IDE drives

- Support IDE PIO timing mode 0, 1, 2 of ANSI ATA specifications

- Support Mode 3 (11 MB/s) timing proposal on enhanced IDE (IDE-2 or ATA-2) specifications

- Two IDE-2 channel supported (each channel supports 2 devices)

- Supports primary IDE or secondary IDE address

- 16-Byte FIFO provide 4-level Posted Write and Read ahead buffers per channel for concurrent system operation

- Programmable command and recovery timing for reads and writes per channel

- Independent timings for command registers and data registers

- Slew rate controlled output directly interface with IDE devices

- Supports either IRQ14/15 or INTA#/B#

- Hardware and Software chip enable/disable capability

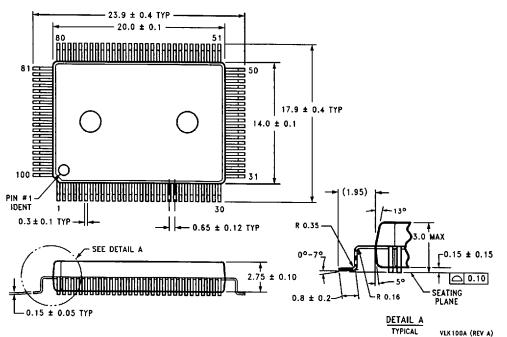

- 100 pin PQFP package, NO other glue logic needed and 12 mA transceivers are built in

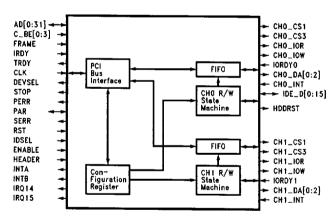

### **Block Diagram**

TL/F/12073-1

TRI-STATE® is a registered trademark of National Semiconductor Corporation SuperI/O™ is a trademark of National Semiconductor Corporation

© 1995 National Semiconductor Corporation TL/F/12073

RRD-B30M75/Printed in U. S. A.

#### Absolute Maximum Ratings 5V ± 10%

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>DD</sub>)

-0.5V to +7.0V

Input Voltage (V<sub>I</sub>)

-0.5V to  $V_{DD} + 0.5V$

Output Voltage (VO)

-0.5V to  $V_{DD} + 0.5V$

Storage Temperature (TSTG)

-65°C to +165°C

Lead Temperature (TL)

(Soldering, 10 seconds)

+260°C

### **Recommended Operating Conditions**

Supply Voltage Operating Temperature (T<sub>A</sub>) 0

Min Typ Max Units 4.5 5.0 5.5

+70 °C

#### **DC Electrical Characteristics**

| Symbol          | Parameter                                 | Conditions                                              | Min                 | Тур         | Max                | Units    |

|-----------------|-------------------------------------------|---------------------------------------------------------|---------------------|-------------|--------------------|----------|

| V <sub>IL</sub> | Input Low Voltage                         |                                                         |                     |             |                    | <u> </u> |

|                 | CMOS                                      |                                                         |                     | ***         | 0.3V <sub>DD</sub> | V        |

|                 | TTL                                       |                                                         |                     |             | 0.8                | V        |

| ViH             | Input High Voltage                        |                                                         |                     | <del></del> |                    |          |

|                 | смоѕ                                      |                                                         | 0.7 V <sub>DD</sub> |             |                    | V        |

|                 | TTL                                       |                                                         | 2.0                 |             |                    | V        |

| l <sub>IH</sub> | Input High Current                        | $V_{IN} = V_{DD}$                                       | -10                 |             | 10                 | μА       |

|                 | Input with Pull-Down                      | $V_{IN} = V_{DD}$                                       | 10                  |             | 200                | μА       |

| I <sub>IL</sub> | Input Low Current                         | VIN = VSS                                               | -10                 |             | 10                 | μА       |

|                 | Input with Pull-Down                      | V <sub>IN</sub> = V <sub>SS</sub>                       | -200                |             | -10                | μА       |

| $V_{OH}$        | Type B8                                   | I <sub>OH</sub> = 8 mA                                  | 2.4                 |             |                    | v        |

|                 | Type B12                                  | I <sub>OH</sub> = 12 mA                                 | 2.4                 |             |                    | V        |

| VOL             | Type B8                                   | I <sub>OL</sub> = 8 mA                                  |                     | ·           | 0.4                | V        |

|                 | Type B12                                  | I <sub>OL</sub> = 12 mA                                 |                     |             | 0.4                | V        |

| loz             | Output TRI-STATE<br>Leakage Current       | V <sub>OH</sub> = V <sub>SS</sub><br>or V <sub>DD</sub> | -10                 |             | 10                 | μΑ       |

| I <sub>DD</sub> | V <sub>DD</sub> Average Supply<br>Current | No Load                                                 |                     |             | 10                 | mA       |

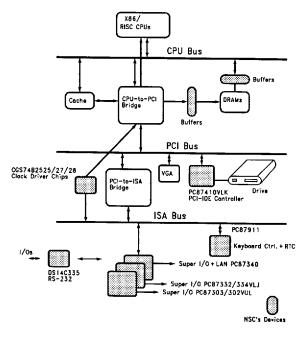

### PCI\_Based System

TL/F/12073-2

TL/F/12073-3

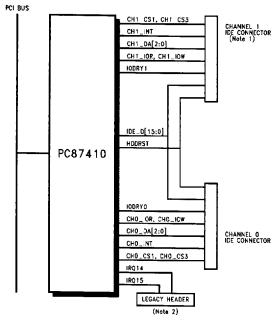

#### **Basic Configuration**

The following diagram shows how the PCI-IDE Interface Controller is used in a system.

Note 1. Second IDE connector is optional

Note 2. Legacy header is needed under the following conditions:

a. The device is on a PCI adapter card.

b. IDE compatibility is required.

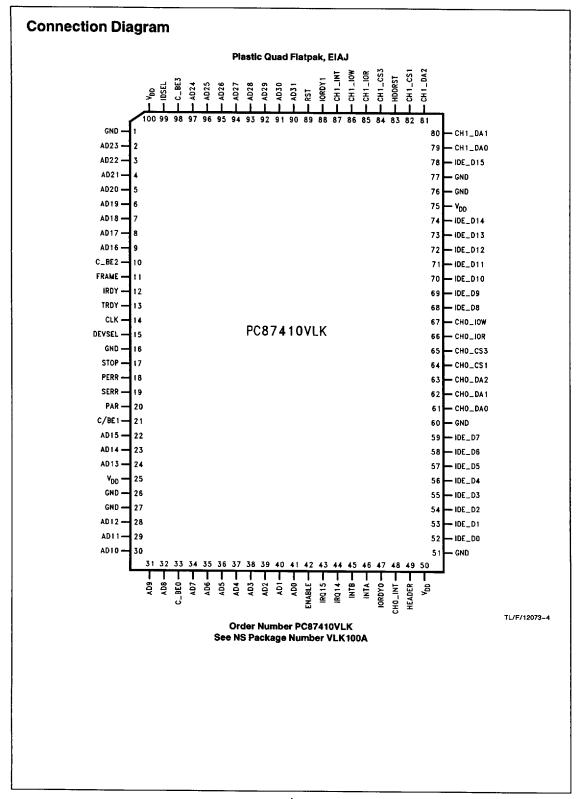

## **Pin Description**

#### PCI Interface

| Name       | Туре         | l <sub>OL</sub>            | Description                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------|--------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD[31:0]   | 1/0          | 8 mA                       | MULTIPLEXED ADDRESS AND DATA. The direction of these pins are defined below: Phase                                                                                                                                                                                                                                                                                 |  |  |

|            |              |                            | Address Phase input Data Phase Read output Write input                                                                                                                                                                                                                                                                                                             |  |  |

| C/BE [3:0] | 1            |                            | COMMAND/BYTE ENABLE are multiplexed Bus command and Byte enables.                                                                                                                                                                                                                                                                                                  |  |  |

| PAR        | 1/0          | 8 mA                       | PARITY is even parity across AD[31:0] and C/BE[3:0]. PAR is an input during writes and an output during reads.                                                                                                                                                                                                                                                     |  |  |

| FRAME#     | l            |                            | CYCLE FRAME is driven by the initiator to indicate the beginning and duration of an access.                                                                                                                                                                                                                                                                        |  |  |

| TRDY#      | O/TRI-STATE® | 12 mA                      | TARGET READY indicates that the current data phase of the transaction is ready to be completed.                                                                                                                                                                                                                                                                    |  |  |

| IRDY#      | l            |                            | INITIATOR READY indicates that the initiator is ready to complete the current data phase of the transaction.                                                                                                                                                                                                                                                       |  |  |

| STOP#      | O/TRI-STATE  | 8 mA                       | STOP indicates that the current target is requesting the initiator to stop the current transaction.                                                                                                                                                                                                                                                                |  |  |

| DEVSEL#    | O/TRI-STATE  | 8 mA                       | <b>DEVICE SELECT,</b> when actively drive, indicates the driving device has decoded its adderss as the target of the current access.                                                                                                                                                                                                                               |  |  |

| IDSEL      | l            |                            | INITIALIZATION DEVICE SELECT is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                            |  |  |

| PERR#      | O/TRI-STATE  | 8 mA                       | PARITY ERROR is used for reporting data parity errors during all PCI transactions except a Special Cycle. PERR * is an output during writes and an input during reads.                                                                                                                                                                                             |  |  |

| SERR#      | O/TRI-STATE  | 8 mA                       | SYSTEM ERROR is used for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be castrophic. When reporting address parity errors, SERR # is an output. When reporting data parity errors for the Special Cycle command, SERR # is an output during writes and an input during needs. |  |  |

| INTA#,B#   | O/TRI-STATE  | 8 mA, Slew<br>Rate Control | INTERRUPT. Interrupt request A and B                                                                                                                                                                                                                                                                                                                               |  |  |

| CLK        | I            |                            | CLOCK. Up to 33 MHz PCI Clock                                                                                                                                                                                                                                                                                                                                      |  |  |

| RST#       | _            |                            | RESET, PCI Reset                                                                                                                                                                                                                                                                                                                                                   |  |  |

### **Power and Ground**

| Name            | Туре | Description                                                         |

|-----------------|------|---------------------------------------------------------------------|

| GND             | 1    | V <sub>SS</sub> or GROUND                                           |

| v <sub>cc</sub> | ı    | V <sub>DD</sub> or +5V. Power to PCI buffers, core and IDE buffers. |

Note: All signals are TTL except CH0\_INT (Pin 48) and CH1\_INT (Pin 87) are CMOS.

### Pin Description (Continued)

#### IDE Interface

| Name                  | Type        | l <sub>OL</sub>             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------------------|-------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IDED[15:0]            | 1/0         | 12 mA, Slew<br>Rate Control | DRIVE DATA BUS. This is an 8- or 16-bit bi-direction data between the PCI-IDE chip and the drive. The lower 8 bits are used for 8-bit transfers (e.g. command registers, ECC bytes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CH0_DA[2:0]           | 0           | 12 mA, Slew<br>Rate Control | CHANNEL 0 ADDRESS LINES. This is the 3-bit binary coded address asserted by the host to access a register or data port in the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CH1_DA [2:0]          | 0           | 12 mA, Siew<br>Rate Control | CHANNEL 1 ADDRESS LINES. This is the 3-bit binary coded address asserted by the host to access a register or data port in the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| IORDY0                | ı           |                             | CHANNEL 0 I/O CHANNEL READY. This signal is negated to extend the disk transfer cycle of any register access (read or write) when the drive is not ready to respond to a data transfer request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| IORDY1                | . I         |                             | CHANNEL 1 I/O CHANNEL READY. This signal is negated to extend the disk transfer cycle of any register access (read or write) when the drive is not ready to respond to a data transfer request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CH0IOR#               | 0           | 12 mA, Slew<br>Rate Control | CHANNEL 0 I/O READ. This is the read strobe signal. The falling edge of CH0_IOR # enables data from a register or the data port of the drive onto the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CH0_IOW#              | 0           | 12 mA, Slew<br>Rate Control | Channel 0 I/O Read. This is the write strobe signal. The rising edge of CH0_IOW # clocks data from the PCI-IDE chip into the register or the data port of the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CH1_IOR#              | 0           | 12 mA, Slew<br>Rate Control | CHANNEL 1 I/O READ. This is the read strobe signal. The falling edge of th CH1IOR # enables data from a register or the data port of the drive onto the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| CH1_IOW#              | О           | 12 mA, Slew<br>Rate Control | CHANNEL 1 I/O WRITE. This is the write strobe signal. The rising edge of CH1_IOW # clocks data from the PCI-IDE chip into the register or the data p of the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| HDDRST#               | 0           | 12 mA, Slew<br>Rate Control | The state of the s |  |

| CH0CS1#,<br>CH0CS3#   | 0           | 12 mA, Slew<br>Rate Control | CHANNEL 0 CHIP SELECT 1 AND 3. CH0CS1 # is the chip select signal to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CH1_CS1#,<br>CH1_CS3# | 0           | 12 mA, Siew<br>Rate Control | CHANNEL 1 CHIP SELECT 1 AND 3. CH1CS1 # is the chip select signal to select the Command Block Registers. CH1CS3 # is the chip select to select the Control Block Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CH0_INT<br>CH1_INT    | l           |                             | CHANNEL INTERRUPTS. These signals are used to interrupt the host system. CHO_INT is asserted only when the drive(s) on channel 0 has a pending interrupt, and the host has cleared nIEN in the Device Control Register. CH1_INT is asserted only when the drive(s) on channel 1 has a pending interrupt, and the host has cleared nIEN in the Device Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| ENABLE                | ı           |                             | CHIP ENABLE PIN. Logic low will disable this chip. If this pin is tied to Logic High or not connected then the chip is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| HEADER                | I           |                             | HEADER PIN. See page 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| IRQ14                 | O/TRI-STATE | 8 mA, Slew<br>Rate Control  | The output of this pin is equivalent to ISA IRQ14 if HEADER is "not connected" or Logic High. However, this pin will go to TRI-STATE if HEADER is tied to Logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| IRQ15                 | O/TRI-STATE | 8 mA, Slew<br>Rate Control  | The output of this pin is equivalent to ISA IRQ15 if HEADER is "Not connected" or Logic High. However, this pin will go to TRI-STATE If HEADER is tied to Logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

## Configuration Registers The configuration register map is shown in Table I.

#### TABLE I

| Reg. #<br>(in HEX) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                 | R   | VENDOR ID (100Bh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 02-3               | R   | DEVICE ID (D001h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 04-5               | R/W | COMMAND REGISTER. The command register provides coarse control over a device's ability to generate and respond to PCI cycles.  bit 0—controls the response to the I/O space accesses specified in the Base Address Register. Default value is determined by the ENABLE pin.  1: Chip enable  0: Chip enable  bit 6— allows the controller to detect parity errors on the PCI bus and report these errors to the system.  1: enable parity checking  0: disable parity checking (default)  bit 8—allows the controller to detect system errors on the PCI bus and report these errors to the system.  1: enable system error checking  0: disable system error checking (default)                                                                                                                                                                             |

| 06                 | R/W | STATUS REGISTER. This register is used to record status information for PCI bus related events. "Reads" from this register behaves normally. However, "write" to this register is slightly different respect to the ordinary register. This register can be reset but not set. In order to reset this register, a logical High need to write to the corresponding bit. For details, please check P.156 of the PCI specification 2.0 (April 30, 1993). bit 9–10: These bit encode the timing of DEVSEL #. (read only)  00: fast  01: medium, Default  bit 14: 1 means system error  bit 15: This bit will be set by a device whenever that device detects a data parity error. This bit is disabled when parity error handling is disabled. A logical one means detection of parity error. Please check P. 157 of the PCI specification 2.0 (April 30, 1993). |

| Reg. #<br>(In HEX) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 08                 | R   | REV. ID (00h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 09                 | R   | PROGRAMMING INTERFACE, default is 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0A                 | R   | SUB-CLASS CODE, default is 01h (means IDE controller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0B                 | R   | BASIC CLASS CODE, default is 01h (means mass storage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0C-0D              |     | Not Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0E                 | R   | HEADER TYPE, default is 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10-13              | R/W | BASE ADDRESS REGISTERS 0. For Primary IDE Data Control Ports (Default: 000001F0h-000001F7h) bit0: fixed to 1 bit1: fixed to 0 bit2: fixed to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14-17              | R/W | BASE ADDRESS REGISTERS 1. For Primary IDE Control Status Ports (Default: 000003F6h) Note: only "3F6" byte is accessible bit0: fixed to 1 bit1: fixed to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18-1B              | R/W | BASE ADDRESS REGISTER 2. For Secondary IDE Data Control Ports. (Default: 00000170h-0000177h) bit0: fixed to 1 bit1: fixed to 0 bit2: fixed to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1C-1F              | R/W | BASE ADDRESS REGISTER 3. For Secondary IDE Control Status Ports. (Default: 00000376h) Note: only "376" byte is accessible bit0: fixed to 1 bit1: fixed to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Configuration Registers The configuration register map is shown in Table I. (Continued)

### TABLE I (Continued)

| Reg. #<br>(in HEX) | R/W      |                                                             | Description                                       |                                       |

|--------------------|----------|-------------------------------------------------------------|---------------------------------------------------|---------------------------------------|

| 20-27              |          | Not used.                                                   |                                                   |                                       |

| 3C                 | R/W      | INTERRUPT LINE, de                                          | fault is 0Eh                                      |                                       |

| 3D                 | R        | INTERRUPT PIN Default is 00h if HEAD Default is 01h if HEAD |                                                   |                                       |

| 3E-3F              |          | Not used                                                    |                                                   |                                       |

| 40                 |          | IDE CHANNEL 0 TIMI<br>Default is set at B5H. (              | NG CONTROL REGISTER. This register is the Note 1) | cycle control register for 1F0h port. |

|                    |          | bit 7, 6:                                                   | address/chip select setup ti                      | ime                                   |

|                    |          | 00                                                          | 1 PCI clk                                         |                                       |

|                    |          | 0.1                                                         | 2 PCI clk                                         |                                       |

|                    |          | 10                                                          | 3 PCI clk                                         | (default)                             |

|                    |          | 11                                                          | 4 PCI clk                                         |                                       |

|                    |          | bit 5 4 3:                                                  | address/chip select/write d                       | ata hold time                         |

|                    |          | 000                                                         | 1 PCI clk                                         |                                       |

|                    |          | 001                                                         | 2 PCI clk                                         |                                       |

|                    |          | 010                                                         | 3 PCI clk                                         |                                       |

|                    |          | 011                                                         | 4 PCI clk                                         |                                       |

|                    |          | 101                                                         | 5 PCI clk                                         |                                       |

|                    |          | 110                                                         | 6 PCl clk                                         |                                       |

| İ                  |          | 111                                                         | 8 PCI clk                                         | (default)                             |

|                    |          | bit 2 1 0:                                                  | 12 PCI clk                                        |                                       |

|                    |          | 000                                                         | Command active time 2 PCI clk                     | (3.5)                                 |

|                    |          | 001                                                         | 3 PCI clk                                         | (Note 3)                              |

|                    |          | 010                                                         | 4 PCI clk                                         |                                       |

|                    |          | 011                                                         | 5 PCI clk                                         |                                       |

|                    |          | 100                                                         | 6 PCI clk                                         |                                       |

| ľ                  |          | 101                                                         | 8 PCI clk                                         | (default)                             |

|                    |          | 110                                                         | 12 PCI clk                                        | (delauit)                             |

|                    |          | 111                                                         | 16 PCl clk                                        |                                       |

| 41                 | W/O      | IDE CHANNEL O REA                                           | D-AHEAD COUNTER, LOW BYTE.                        |                                       |

|                    |          |                                                             | pading bit0-bit7 of read—ahead counter.           |                                       |

| i                  |          |                                                             | d—ahead counter                                   |                                       |

|                    |          |                                                             | d—ahead counter                                   |                                       |

| i                  |          |                                                             | d—ahead counter                                   |                                       |

|                    |          |                                                             | d—ahead counter                                   |                                       |

|                    |          |                                                             | d—ahead counter                                   |                                       |

| Į                  |          |                                                             | d—ahead counter                                   |                                       |

| [                  |          |                                                             | d—ahead counter                                   |                                       |

| 42                 | Bit 7 is | IDE CHANNEL 9 REA                                           | AHEAD COUNTER, HIGH BYTE.                         |                                       |

|                    | R/W,     | It provides values for lo                                   | ading bit8-bit9 read_ahead counter.               |                                       |

|                    | others   | bit0: bit8 of the rea                                       | d-ahead counter                                   |                                       |

|                    | are W/O  | <b>!</b>                                                    | d—ahead counter                                   |                                       |

|                    |          |                                                             | unction control                                   |                                       |

|                    |          | 1: enable                                                   |                                                   |                                       |

|                    |          | 0: disable (def                                             | ault)                                             |                                       |

## Configuration Registers The configuration register map is shown in Table I. (Continued)

### TABLE I (Continued)

| Reg. #<br>(In HEX) | R/W | Description                      |                                                               |                                                            |  |  |

|--------------------|-----|----------------------------------|---------------------------------------------------------------|------------------------------------------------------------|--|--|

| 43                 |     | IDE CHANNEL 0 FUNCTION REGISTER. |                                                               |                                                            |  |  |

|                    |     | bit3:                            | channel 0 I/O decode enable bit                               |                                                            |  |  |

|                    |     |                                  | 1: enable (default)                                           |                                                            |  |  |

|                    |     |                                  | 0: disable                                                    |                                                            |  |  |

|                    |     | bit2:                            | IORDY0 function control                                       |                                                            |  |  |

|                    |     |                                  | 1: enable                                                     |                                                            |  |  |

|                    |     |                                  | 0: disable (default)                                          |                                                            |  |  |

|                    |     | bit1:                            | CH0_INT status (read only)                                    |                                                            |  |  |

|                    |     |                                  | 1: interrupt pending                                          |                                                            |  |  |

|                    |     |                                  | 0: no interrupt pending                                       |                                                            |  |  |

|                    |     | bitQ:                            | CH0_INT request to be masked or no                            | t                                                          |  |  |

|                    |     |                                  | 1: be masked                                                  |                                                            |  |  |

|                    |     |                                  | 0: not be masked (default)                                    |                                                            |  |  |

| 44                 |     | IDE CHA                          | NNEL 1 TIMING CONTROL REGISTER.                               | This register is the cycle control register for 170h port. |  |  |