## SN74BCT2425 MCP NuBus™ ADDRESS/DATA REGISTERED TRANSCEIVER

SDIS011B D3361, FEBRUARY 1990-REVISED JANUARY 1991

- Designed to Support Apple Computer

MacIntosh Coprocessor Platform (MCP)

Interface Applications

- Designed to Operate with the SN74ACT2441

MCP NuBus™ Interface Controller

- Includes NuBus™ Address and Data Path Circuitry Along with Memory Address Drivers

- Conforms to Apple Computer MacIntosh II Family NuBus™ Interface Specifications

- BiCMOS Design Substantially Reduces Standby Current

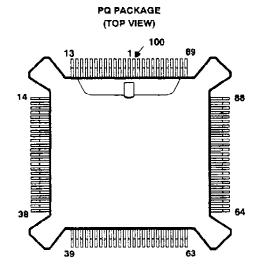

- Available in 100-pin Plastic Quad Flat Package

## description

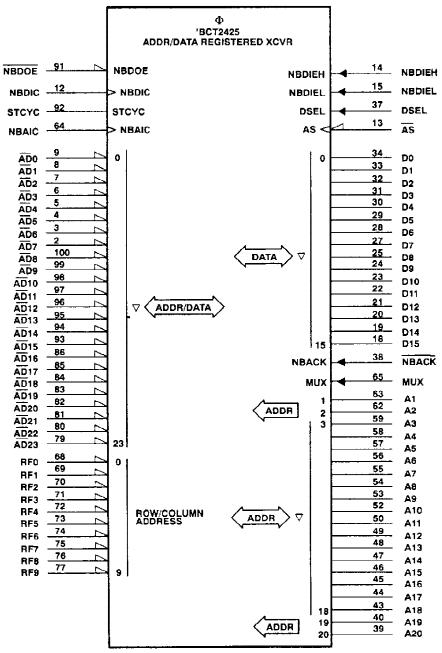

The SN74BCT2425 consists of bus transceiver circuits, D-type flip-flops, memory drivers, and control circuitry arranged for multiplexed transmission of address and data information in MacIntosh Coprocessor Platform (MCP) applications.

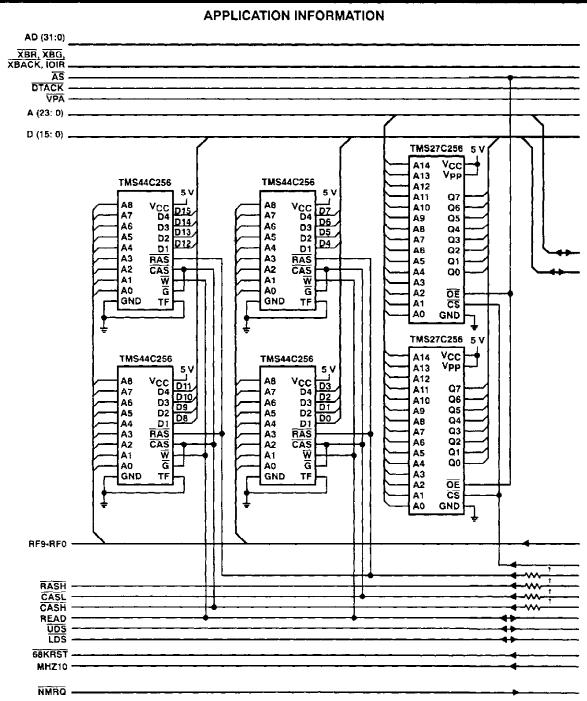

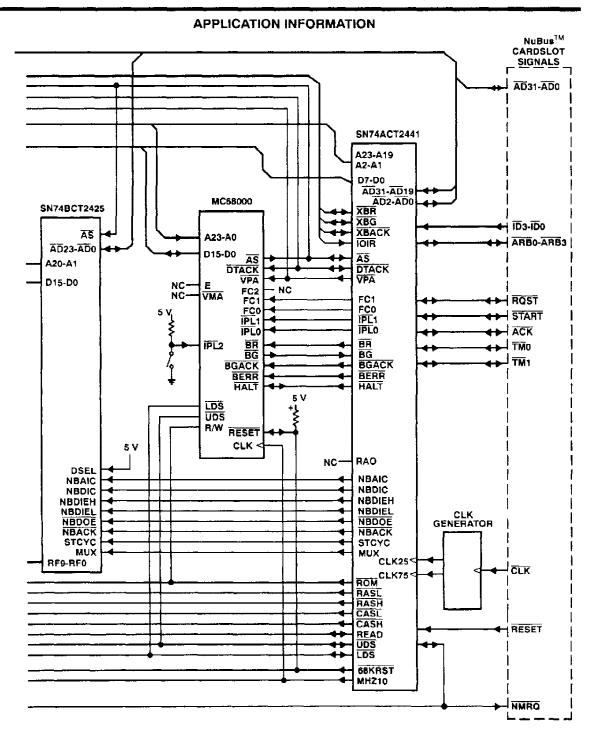

The MCP is a generic software and hardware foundation developed by Apple Computer and may be used in the development of add-in cards and software applications for the MacIntosh II computer.

The MCP provides an intelligent NuBus™ interface that includes hardware support for an MC68000 processor, an application specific I/O processor, ROM, and dynamic memory. Software support for the MCP architecture consists of the A/ROSE operating system (Apple Real-time Operating System Environment). A/ROSE is downloaded onto the MacIntosh II I/O card for execution by the on-board MC68000.

For a complete description of the Apple MacIntosh NuBus<sup>™</sup> implementation, see *Designing Cards and Drivers* for MacIntosh II and MacIntosh SE published by Addison Wesley, or contact the Apple Programmers and Developers Association (APDA). For additional information on MCP or A/ROSE, contact Apple Computer directly.

The SN74BCT2425 is characterized for operation from 0°C to 70°C.

NuBus is a trademark of Texas Instruments Incorporated.

# SN74BCT2425 MCP NuBus™ ADDRESS/DATA REGISTERED TRANSCEIVER

**NBACK**

A20

A19

38

39

40

D15

D14

D13

18

19

20

| Pin Assignments |            |     |            |     |            |     |       |     |       |

|-----------------|------------|-----|------------|-----|------------|-----|-------|-----|-------|

|                 | PIN        |     | PIN        |     | PIN        | 1   | PIN   |     | PIN   |

| NO.             | NAME       | NO. | NAME       | NO. | NAME       | NO. | NAME  | NO. | NAME  |

| 1               | GND        | 21  | D12        | 41  | Vçc        | 61  | Vcc   | 81  | AD21  |

| 2               | AD7        | 22  | D11        | 42  | GND        | 62  | A2    | 82  | AD20  |

| 3               | AD6        | 23  | D10        | 43  | A18        | 63  | A1    | 83  | AD19  |

| 4               | AD5        | 24  | D9         | 44  | A17        | 64  | NBAIC | 84  | AD18  |

| 5               | AD4        | 25  | D8         | 45  | A16        | 65  | MUX   | 85  | AD17  |

| 6               | AD3        | 26  | GND        | 46  | A15        | 66  | Vcc   | 86  | AD16  |

| 7               | AD2        | 27  | D7         | 47  | A14        | 67  | GND   | 87  | GND   |

| 8               | ĀD1        | 28  | D6         | 48  | A13        | 66  | AF0   | 88  | VCC   |

| 9               | AD0        | 29  | <b>D</b> 5 | 49  | A12        | 69  | RF1   | 89  | Vcc   |

| 10              | GND        | 30  | D4         | 50  | A11        | 70  | RF2   | 90  | GND   |

| 11              | Vcc        | 31  | D3         | 51  | GND        | 71  | RF3   | 91  | NBDOE |

| 12              | NBDIC      | 32  | D2         | 52  | A10        | 72  | RF4   | 92  | STCYC |

| 13              | <b>⊼</b> Ş | 33  | D1         | 53  | A9         | 73  | RF5   | 93  | AD15  |

| 14              | NBDIEH     | 34  | D0         | 54  | A8         | 74  | RF6   | 94  | ĀD14  |

| 15              | NBDIEL     | 35  | GND        | 55  | <b>A</b> 7 | 75  | RF7   | 95  | AD13  |

| 16              | Vcc.       | 36  | Vcc        | 56  | A6         | 76  | RF8   | 96  | AD12  |

| 17              | GND        | 37  | DSEL       | 57  | A5         | 77  | RF9   | 97  | AD11  |

A4

ΑЗ

GND

58

59

GND

AD23

AD22

78

79

80

98

99

100

AD10

AD9

AD8

## logic symbol†

<sup>\*</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984.

#### logic diagram ΕN NBDOE <del>√8 X 1</del> 8 DSEL - NBDIEH G1 NBDIC -ΕN 8 1 8X MUX D15-D8 8 X 1 AS AD23-AD16 EN > C1 8X AD7-AD0 8 ∤ AD15-AD8 8 8/ 8 AD23-AD0 - NBDIEL G1 ΕN > C1 8 X 1 ▽ **BX MUX** D7-D0 16 8 D15-D8 D15-D0 AD7-AD0 AD15-AD8 ΕN STCYC -AD18-AD3 16X 16 - NBACK 16 ΕN NBAIC 1 2 C1 16X <sub>▽</sub> 16X A18-A3 16 A1,A2,A19,A20 A18-A3 G1 MUX -45 Ω 10 A19,A17, ... A3,A1 10X MUX1 RF9-RF0 -10, A20,A18, ... A2

## SN74BCT2425 MCP NuBus™ ADDRESS/DATA REGISTERED TRANCEIVER

## TERMINAL FUNCTIONS

| PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20-A1   | Local Address Bus. This 20-bit I/O port directly interfaces to the local address bus A23-A0.                                                                                                                                                                                                                                                       |

| AD23-AD0 | Address/Data Port. This 24-bit active low I/O port directly interfaces to the NuBus" address/data lines. These lines are multiplexed to carry address at the beginning of a NuBus" cycle, and data information in the last portion of the NuBus" cycle.                                                                                            |

| ĀŠ       | Address Strobe. This input is used for saving data information on the low-to-high transition of AS. The AS input is typically connected to both the 'ACT2441 and the MC6800.                                                                                                                                                                       |

| D15-D0   | Data Address Bus. This 16-bit I/O port directly interfaces to the local data bus.                                                                                                                                                                                                                                                                  |

| DSEL     | Data Select. This input controls the data multiplexer for the local data bus, When this input is driven low, the NuBus <sup>™</sup> addresses AD23-AD0 are selected as inputs to the output data buffer. When DSEL is driven high, the NuBus <sup>™</sup> data saved in the data input registers are selected as inputs to the output data buffer. |

| MUX      | Multiplex Row/Column Addresses. This input is used to select between row and column addresses when reading or writing to memory. This signal is driven by the 'ACT2441.                                                                                                                                                                            |

| NBACK    | NuBus <sup>**</sup> Acknowledge. This active-low input is used to enable NuBus <sup>**</sup> address information, saved via the NBAIC input, onto the local A20-A1 address lines.                                                                                                                                                                  |

| NBAIC    | NuBus ** Address Input Clock. This input is used for saving the address portion of NuBus** read or write cycles. Data present at the AD18-AD3 I/O port is clocked into the address register on the low-to-high transition of NBAIC.                                                                                                                |

| NBDIC    | NuBus <sup>®</sup> Data Input Clock. This input is used for saving the data portion of NuBus <sup>®</sup> read or write cycles. Data present at the AD23-AD0 I/O port is clocked into the data registers on the low-to-high transition of NBDIC.                                                                                                   |

| NBDIEL   | NuBus <sup>™</sup> Data Input Enable Low. This active-high input is used to enable NuBus <sup>™</sup> data information onto the local bus (D15-D0) for the lower 16-bits corresponding to AD15-AD0.                                                                                                                                                |

| NBDIEH   | NuBus™ Data Input Enable High. This active-high input is used to enable NuBus™ data information onto the local bus (D15-D8) for the upper 8-bits corresponding to AD23-AD16. The remaining 8-bits D7-D0, corresponding to AD31-AD24, are supplied by the 'ACT2441.                                                                                 |

| NBDOE    | NuBus™ Data Output Enable. This active-low input is used to enable the AD23-AD0 outputs. When NBDOE is taken inactive (high), the AD23-AD0 outputs are at high impedance (assuming STCYC is also inactive).                                                                                                                                        |

| RF0-RF9  | Memory Row/Column Addresses. These outputs are used for driving row and column address information onto the DRAM address bus. Each output has an internal 45-Ω resistor in series with the output pin for the purpose of supressing signal overshoot and undershoot.                                                                               |

| STCYC    | Start Cycle Active. This active-high input is used to enable the local bus address lines A18-A3 onto the NuBus™ AD18-AD3 bus lines. The remainder of the 24-bit address lines are driven directly from the 'ACT2441 MCP NuBus™ controller. When STCYC is taken inactive (low), the AD18-AD3 outputs are at high impedance.                         |

#### **Function Tables**

#### DATA BUS PORT MODE

|      | CONTRO | LINPUTS |        |                           | DATA INPUTS |                     | OUT    | PUTS  |   |

|------|--------|---------|--------|---------------------------|-------------|---------------------|--------|-------|---|

| DSEL | NBDIC  | NBDIEL  | NBDIEH | AD23-AD16                 | AD15-AD8    | AD7-AD0             | D15-D8 | D7-D0 |   |

| X    | Х      | L       | L      | ×                         | X           | Х                   | Z      | Z     |   |

|      | .,     | i .     |        | L                         | X           | Х                   | н      | Z     |   |

| L    | X      | £       | Н      | Н                         | ×           | ×                   | L      | Z     |   |

|      |        | 1       |        | X                         | Н           | L                   | н      | L     |   |

| L    | X      | н       | H      | X                         | L           | н                   | L      | Н     |   |

| L    | Х      | Н       | н      |                           | Unaliov     | ved input condition | on     |       |   |

|      |        |         |        |                           | L           | Х                   | Х      | Н     | Z |

| н    | !      | L       | H      | H                         | х           | ×                   | L      | Z     |   |

|      | Not    |         |        | X                         | X           | X                   | NC     | Z     |   |

| - "  |        |         |        | Х                         | н           | L                   | Н      | L     |   |

| н    | į t    | н       | L      | X                         | L           | Н                   | L      | Н     |   |

|      | Not    | 1       |        | X                         | Х           | X                   | NC     | NC    |   |

| Н    | ×      | Н       | н      | Unallowed input condition |             |                     |        |       |   |

Inputs  $\overline{AD}$ 15- $\overline{AD}$ 8 map to outputs D7-D0, and inputs  $\overline{AD}$ 7- $\overline{AD}$ 0 map to outputs D15-D8, respectively, in the applicable mode. Inputs  $\overline{AD}$ 23- $\overline{AD}$ 16 map to outputs D15-D8, respectively, in the applicable mode.

#### NuBus™ PORT OUTPUT MODE

|    | CONTROL INPUTS |       |       | D                         | ATA INPUT | S        | OUTPUTS        |             |          |         |

|----|----------------|-------|-------|---------------------------|-----------|----------|----------------|-------------|----------|---------|

| A1 | ĀS             | NBDOE | STCYC | A18-A3                    | D15-D8    | D7-D0    | AD23-AD19      | AD18-AD16   | AD15-AD3 | AD2-AD0 |

| X  | Х              | Н     | L     | Х                         | Х         | Х        | Z              | Z           | Z        | Z       |

|    | . х н          |       | L     | Х                         | Х         | Z        | Н              | н           | Z        |         |

| L  |                | H     | Н     | Н                         | Х         | Х        | Z              | L           | L        | Z       |

|    | T              | L L   | 1 .   | X                         | Ĺ         | L        | Н              | н           | н        | Н       |

| L  | ×              |       | -     | Х                         | Н         | Н        | L              | Ĺ           | L        | L       |

| L  | X              | L     | н     |                           |           | <u>'</u> | Unallowed inpu | t condition | ·        |         |

|    |                |       | ·     | L                         | Х         | Х        | Z              | Н           | н        | Z       |

| Н  | X              | н     | Н     | Н                         | X         | Х        | Z              | L           | L        | Z       |

|    |                |       |       | X                         | L         | L        | Н              | Н           | Н        | н       |

| H  | ı              | _     | ļ L   | X                         | Н         | H        | L              | L           | L        | Ł       |

|    | 1              |       | 1     | ×                         | L         | L        | H              | н           | NC       | NC      |

| Н  | No†            | L     | L     | X                         | Н         | Н        | L              | L           | NC       | NC      |

| Н  | X              | L     | н     | Unallowed input condition |           |          |                |             |          |         |

Inputs A18-A3 map to outputs AD18-AD3, respectively in the applicable mode.

Inputs D15-D8 map to outputs AD23-AD16, respectively in the applicable mode.

Inputs D7-D0 map to outputs  $\overline{AD}15$ - $\overline{AD}8$ , and inputs D15-D8 map to outputs  $\overline{AD}7$ - $\overline{AD}0$ , respectively in the applicable mode

Hidenotes a high level, Lidenotes a low level, Z denotes a high-impedance state, † denotes a low-to-high logic level transition, NC denotes no change, and X denotes a level that does not affect the result.

# SN74BCT2425 MCP NuBus™ ADDRESS/DATA REGISTERED TRANCEIVER

#### **Function Tables**

#### MEMORY DRIVER PORT

| CONTROL | DATA INPUTS                                  |                                             |              |  |  |  |  |

|---------|----------------------------------------------|---------------------------------------------|--------------|--|--|--|--|

| MUX     | A20, A18, A16, A14, A12, A10, A8, A6, A4, A2 | A19, A17, A15, A13, A11, A9, A7, A5, A3, A1 | , A1 RF9-RF0 |  |  |  |  |

|         | L                                            | X                                           | Н            |  |  |  |  |

| L       | Н                                            | X                                           | L            |  |  |  |  |

|         | X                                            | L                                           | н            |  |  |  |  |

| н       | ×                                            | н                                           | L            |  |  |  |  |

Inputs A20, A18, A16, A14, A12, A10, A8, A6, A4, A2 map to outputs RF9-RF0, respectively. Inputs A19, A17, A15, A13, A11, A9, A7, A5, A3, A1 map to outputs RF9-RF0, respectively.

#### ADDRESS PORT OUTPUT MODE

| CON   | TROL  | DATA INPUTS | OUTPUTS |  |

|-------|-------|-------------|---------|--|

| NBAIC | NBACK | AD18-AD3    | A18-A3  |  |

| Х     | Н     | X           | Z       |  |

| t     |       | L           | Н       |  |

| t     | L     | Н           | L       |  |

| No †  | 1     | X           | NC      |  |

Inputs AD18-AD3 map to A18-A3, respectively.

H denotes a high level, L denotes a low level, Z denotes a high-impedance state, \* denotes a low-to-high logic level transition, NC denotes no change, and X denotes a level that does not affect the result.

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)               |

|------------------------------------------------------------|

| Input voltage range, V <sub>I</sub> 5.5 V                  |

| Operating free-air temperature, T <sub>A</sub> 0°C to 70°C |

| Storage temperature range – 65°C to 150°C                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to the GND terminal.

#### recommended operating conditions

|                 |                              |                      | MIN  | NOM | MAX | UNIT |

|-----------------|------------------------------|----------------------|------|-----|-----|------|

| Vcc             | Supply voltage               |                      | 4.5  | 5   | 5.5 | V    |

| ViH             | High-level input voltage     |                      | 2    |     |     | ٧    |

| VIL             | Low-level input voltage      |                      |      |     | 8.0 | V    |

| IOH             | High-level output current    |                      |      |     | 15  | mA   |

| lot             | Low-level output current     | Ax, Dx, ADx, outputs |      |     | 24  | mA   |

| UL              | zon iere oatpat aanen        | RFx outputs          |      |     | 12  |      |

| ,               | Pulse duration               | Clocks high          | 12.5 |     |     | ns   |

| I <sub>W</sub>  | , also detailer              | 12.5                 | ·    |     |     |      |

| t <sub>SU</sub> | Setup time                   |                      | 10   |     | _   | ns   |

| th              | Hold time                    |                      | 3    |     |     | ns   |

| ŤΑ              | Operating free-air temperatu | 70                   | 0    |     | 70  | °C   |

## SN74BCT2425 MCP Nubus™ ADDRESS/DATA REGISTERED TRANSCEIVER

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER VIK |                              | 1                                              | EST CONDITIONS                | MIN  | TYP  | MAX   | UNIT |

|---------------|------------------------------|------------------------------------------------|-------------------------------|------|------|-------|------|

|               |                              | V <sub>CC</sub> = 4.5 V,                       | lį = ~ 18 mA                  |      |      | - 1.2 | V    |

|               |                              | V <sub>CC</sub> = 4.5 to 5.5 V,                | I <sub>OH</sub> = - 400 μA    | Vcc- | 1.5  |       |      |

| ∨он           |                              | V <sub>CC</sub> = 4.5 V,                       | I <sub>OH</sub> = - 3 mA      | 2.B  | 3.6  | }     | V    |

|               |                              | VCC = 4.5 V.                                   | IOH = 15 mA                   | 2    |      |       |      |

|               | Ax, Dx, ADx                  | V <sub>CC</sub> = 4.5 V,                       | l <sub>OL</sub> = 12 mA       |      | 0.25 | 0.4   | -    |

|               | Ax, Dx, ADx                  | V <sub>CC</sub> = 4.5 V,                       | IOL = 24 mA                   |      | 0.35 | 0.5   | V    |

| VOL           | RF                           | V <sub>CC</sub> = 4.5 V,                       | IOL = 1 mA                    |      | 0.2  | 0.4   | •    |

|               | RF                           | V <sub>CC</sub> = 4.5 V.                       | 1 <sub>OL</sub> = 12 mA       |      | 0.8  | 1     |      |

| Βį            |                              | V <sub>CC</sub> = 5.5 V <sub>1</sub>           | V <sub>1</sub> = 5.5 V        |      |      | 100   | 14A  |

| IOL           | RF                           | V <sub>CC</sub> = 4.5 V,                       | V <sub>O</sub> = 2 V          | 15   |      |       | mA   |

| 1114          | NBACK, NBDIEL, NBDOE         | V <sub>CC</sub> = 5.5 V,                       | V <sub>1</sub> = 2.7 V        |      |      | 20    | μА   |

| чнт           | All other inputs             | V <sub>CC</sub> = 5.5 V.                       | V <sub>1</sub> = 2.7 V        | - 10 |      | - 100 | μΛ   |

| llÇ           | NBDIEL, NBDIEH, NBDOE, STCYC | V <sub>CC</sub> = 5.5 V,                       | V <sub>I</sub> = 0.4 V        |      |      | - 300 | μΑ   |

| ηL.           | All other inputs             | V <sub>CC</sub> = 5.5 V.                       | V <sub>I</sub> = 0.4 V        |      | _    | - 200 | μη   |

| IO§           | Ax, Dx, ADx                  | V <sub>CC</sub> = 5.5 V,                       | V <sub>Q</sub> = 2.25 V       | - 30 |      | - 112 |      |

| ''.           | RF                           | V <sub>CC</sub> = 5.5 V,                       | V <sub>O</sub> = 2.25 V       | - 20 |      | - 50  | mA   |

|               |                              | V <sub>CC</sub> = 5.5 V,                       |                               |      |      | 172   |      |

|               |                              | V <sub>IH</sub> = 3 V.                         | Maximum number of outputs low |      | 111  |       | mA   |

| 1CC           |                              | V <sub>IL</sub> = 0. Maximum number of outputs |                               | 40   |      | 68    | HIM  |

|               |                              | Outputs open                                   | disabled (high-Z)             |      | 40   | 00    |      |

TAll typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the off-state output current.

The output conditions have been selected to produce a current that closely approximates one half of the true short-circuit current I<sub>OS</sub>.

# SN74BCT2425 MCP NuBus™ ADDRESS/DATA REGISTERED TRANCEIVER

switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)  $^\dagger$

|                  | FDOU            | 70              | TI                | EST CO     | NDITION |       |          | UNIT |     |

|------------------|-----------------|-----------------|-------------------|------------|---------|-------|----------|------|-----|

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT)† | V <sub>L</sub> B1 |            | R2      | CL    | MIN TYP‡ |      | MAX |

|                  | (···· •··)      | (000.,          | (V)               | <b>(Ω)</b> | (Q)     | (pF)  |          |      |     |

| <sup>t</sup> pd  | A3-A18          | AD3-AD18        | 1                 |            |         |       | 11       | 18   | ns  |

| <sup>†</sup> pd  | D0-D15          | AD0-AD15        |                   |            | İ       |       | 11       | 18   | ns  |

| t <sub>pd</sub>  | D8-D15          | AD16-AD23       | Vcc               | 270        | 470     | 130   | 11       | 18   | ns  |

| tpd              | ĀS†             | AD0-AD15        |                   |            |         |       | 14       | 22   | ns  |

| <sup>t</sup> pd  | A1              | AD0-AD15        |                   |            |         |       | 14       | 22   | ns  |

| t <sub>pd</sub>  | AD0-AD23        | D0-D15          |                   |            |         |       | 9        | 16   | ns  |

| t <sub>pd</sub>  | NBDIC†          | D0-D15          |                   | open       | en 500  |       | 12       | 21   | ns  |

| <sup>†</sup> pd  | DSEL            | D0-D15          | open              |            |         | 50    | 15       | 23   | n\$ |

| t <sub>pd</sub>  | NBAIC†          | A3-A18          | 7                 |            | İ       |       | 10       | 18   | ns  |

| <sup>t</sup> pd  | A1-A20          | RF0-RF9         |                   | ореп       |         |       | 9        | 16   | ns  |

| <sup>t</sup> pď  | MUX             | RF0-RF9         | open              |            | 2 k     | 50    | 9        | 16   | ns  |

| t <sub>en</sub>  | NBDOE           | AD0-AD23        | V.                |            | 470     | 100   | 12       | 20   | ns  |

| t <sub>en</sub>  | STCYC           | AD3-AD18        | → vcc             | 270        | 470     | 130   | 14       | 22   | ns  |

| t <sub>en</sub>  | NBDIEL          | D0-D15          |                   |            |         |       | 11       | 22   | ns  |

| t <sub>en</sub>  | NBDIEH          | D8-D15          | 7                 | 500        | 500     | 50    | 11       | 22   | ns  |

| ten              | NBACK           | A3-A18          |                   |            | į       |       | 10       | 20   | пз  |

| t <sub>dis</sub> | NBDOE           | AD0-AD23        | .,                | 570        | 170     |       | 6        | 10   | ns  |

| t <sub>dis</sub> | STCYC           | AD3-AD18        | ─ Vcc             | 270        | 470     | 50    | 6        | 10   | ns  |

| <sup>t</sup> dis | NBDIEL          | D0-D15          |                   |            |         |       | 6        | 10   | ns  |

| t <sub>dis</sub> | NBDIEH          | D8-D15          | 7                 | 500        | 0 500   | 00 50 | 6        | 10   | ns  |

| <sup>t</sup> dis | NBACK           | A3-A18          | 7                 |            |         |       | 6        | 1D   | ns  |

<sup>†</sup> The outputs are measured one at a time with one transition per measurement or in the PAD mode two outputs switching at one time.

$<sup>^{\</sup>mbox{$\frac{1}{2}$}}$  All typical values are at VCC = 5 V, TA = 25°C.

<sup>†</sup> Series damping resistors are recommended but may not be required depending on system environment.

Figure 1. MacIntosh Coprocessor Platform (MCP) Architecture (configured with 1 row of 245K x 4 DRAMs)

Figure 1. Macintosh Coprocessor Platform (MCP) Architecture (Continued) (configured with 1 row of 245K x 4 DRAMs)

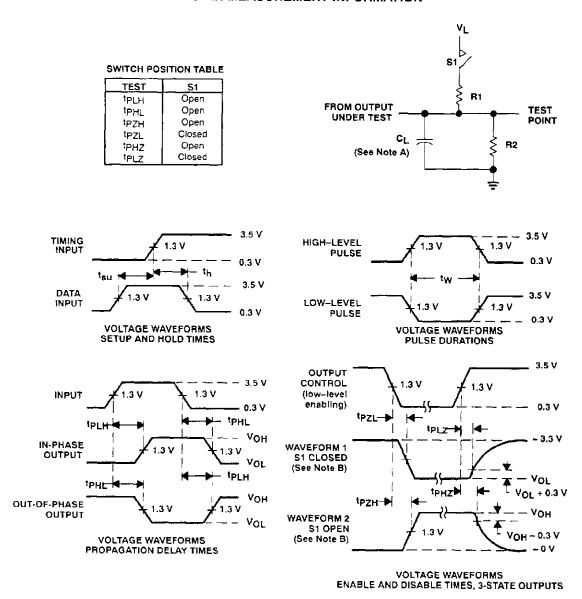

#### PARAMETER MEASUREMENT INFORMATION

NOTES. A Cy includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_f = t_f = 2$  ns, duty cycle = 50%.

- D. The outputs are measured one at a time with one transition per measurement.

Figure 2

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

ti.com 24-Jun-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3) |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|-------------------|

| SN74BCT2425PQ    | OBSOLETE              | BQFP            | PQ                 | 100                 | TBD                     | Call TI          | Call TI           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated