National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

# CR16MES5/CR16MES9/CR16MFS5/CR16MFS9/ CR16MHS5/CR16MHS9/CR16MNS5/CR16MNS9/ CR16M9S5/CR16MUS5/CR16MUS9/ Family of CompactRISC 16-Bit Microcontrollers

#### 1.0 **General Description**

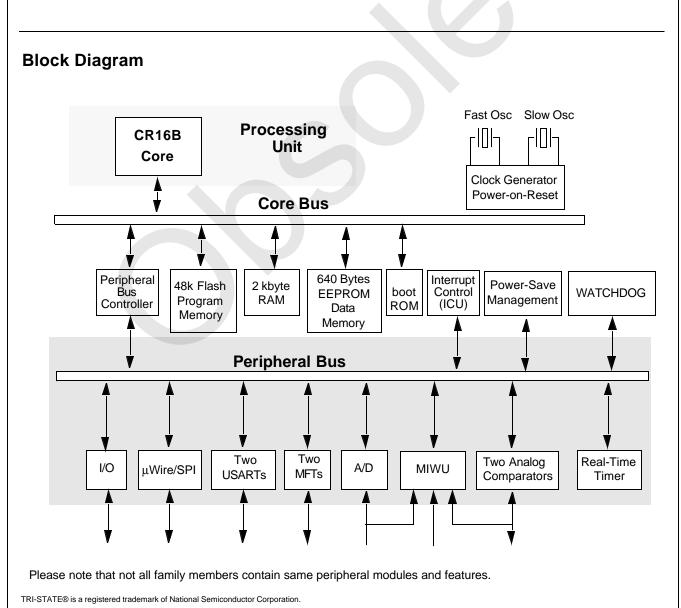

The family of CompactRISC™ microcontrollers are general-purpose 16-bit microcontrollers based on a Reduced Instruction Set Computer (RISC) architecture. The device operates as a complete microcomputer with all system timing, interrupt logic, flash program memory or ROM memory, RAM, EEPROM data memory, and I/O ports included on-chip. It is ideally suited to a wide range of embedded controller applications because of its high performance, on-chip integrated features and low power consumption, resulting in decreased system cost.

The family of CompactRISC 16-bit microcontrollers offer the high performance of a RISC architecture while retaining the advantages of a traditional Complex Instruction Set Computer (CISC): compact code, on-chip memory and I/O, and reduced cost. The CPU uses a three-stage instruction pipeline that allows execution of up to one instruction per clock cycle, or up to 20 million instructions per second (MI-PS) at a clock rate of 20 MHz.

<sup>2001</sup> National Comisandustar Corneration

December 2001

# **Table of Contents**

| 1.0  | Gene       | ral Description                      |

|------|------------|--------------------------------------|

| 2.0  | Featu      | ıres                                 |

| 3.0  | Devic      | e Overview5                          |

|      | 3.1        | CR16B CPU Core5                      |

|      | 3.2        | Memory                               |

|      | 3.3        | Input/Output Ports5                  |

|      | 3.4        | Bus Interface Unit5                  |

|      | 3.5        | Interrupts                           |

|      | 3.6        | Multi-Input Wake-up6                 |

|      | 3.7        | Dual Clock and Reset6                |

|      | 3.8        | Power Management6                    |

|      | 3.9        | Multi-Function Timer6                |

|      | 3.10       | Real-Time TIMER and Watchdog6        |

|      | 3.11       | USART                                |

|      | 3.12       | MICROWIRE/SPI6                       |

|      | 3.13       | A/D Converter6                       |

|      | 3.14       | Analog Comparators7                  |

|      | 3.15       | Development Support7                 |

|      | 3.16       | Pin Description                      |

| 4.0  | Syste      | em Configuration                     |

|      | 4.1        | ENV0 and ENV1 Pins                   |

|      | 4.2        | Module Configuration (MCFG) Register |

|      | 4.3        | Module Status (MSTAT) Register       |

| 5.0  | Input      | /Output Ports                        |

|      | 5.1        | Port Registers                       |

|      | 5.2        | Open-Drain Operation                 |

| 6.0  | CPU a      | and Core Registers                   |

|      | 6.1        | General-Purpose Registers            |

|      | 6.2        | Dedicated Address Registers          |

|      | 6.3        | Processor Status Register            |

|      | 6.4        | Configuration Register               |

|      | 6.5        | Addressing Modes                     |

|      | 6.6        | Stacks                               |

|      | 6.7        | Instruction Set                      |

| 7.0  |            | nterface Unit                        |

|      | 7.1        | Bus Cycles                           |

|      | 7.2        | BIU Control Registers                |

|      | 7.3        | Wait and Hold States Used            |

| 8.0  |            | ory                                  |

| 0.0  | 8.1        | Flash Program Memory                 |

|      | 8.2        | RAM Memory                           |

|      | 8.3        | EEPROM Data Memory                   |

|      | 8.4        | ISP Memory                           |

| 9.0  |            | upts                                 |

| 5.0  | 9.1        | Interrupt Operation                  |

|      | 9.2        | Non-Maskable Interrupt               |

|      | 9.3        | Maskable Interrupts                  |

|      | 9.4        | Interrupt Registers                  |

|      | 9.4<br>9.5 | Interrupt Programming Procedures     |

| 10.0 |            | memory Programming Procedures        |

| 10.0 | 10.1       | Active Mode                          |

|      | 10.1       | Power Save Mode                      |

|      | 10.2       | Idle Mode                            |

|      | 10.3       | Halt Mode                            |

|      | 10.4       | Switching Between Power Modes        |

|      | 10.5       |                                      |

| 11.0  | Dual Clock and Reset                                                                                           | 36         |

|-------|----------------------------------------------------------------------------------------------------------------|------------|

|       | 11.1 External Crystal Network                                                                                  | 36         |

|       | 11.2 Main System Clock                                                                                         | 37         |

|       | 11.3 Slow System Clock                                                                                         |            |

|       | 11.4 Power-On Reset                                                                                            |            |

|       | 11.5 External Reset                                                                                            |            |

|       | 11.6 Dual Clock and Reset Registers                                                                            | 38         |

|       | 11.7 Slow Clock Prescaler Register (PRSSC)                                                                     |            |

| 12.0  | Multi-Input Wake-Up                                                                                            |            |

|       | 12.1 Wake-Up Edge Detection Register (WKEDG)                                                                   |            |

|       | 12.2 Wake-Up Enable Register (WKENA)                                                                           |            |

|       | 12.3 Wake-Up Source Select Register (WKCTRL)4                                                                  |            |

|       | 12.4 Wake-Up Pending Register (WKPND)                                                                          |            |

|       | 12.5 Wake-Up Pending Clear Register (WKPCL)4                                                                   |            |

| 42.0  | 12.6 Programming Procedures                                                                                    |            |

| 13.0  | Real-Time Timer and WATCHDOG         4           13.1         TWM Structure         4                          |            |

|       | 13.2         Timer T0 Operation         4                                                                      |            |

|       | 13.3 WATCHDOG Operation                                                                                        |            |

|       | 13.4 TWM Registers                                                                                             |            |

|       | 13.5 WATCHDOG Programming Procedure                                                                            |            |

| 14.0  | Multi-Function Timer                                                                                           |            |

|       | 14.1 Timer Structure                                                                                           | 45         |

|       | 14.2 Timer Operating Modes                                                                                     | 47         |

|       | 14.3 Timer Interrupts5                                                                                         | 50         |

|       | 14.4 Timer I/O Functions5                                                                                      | 50         |

|       | 14.5 Timer Registers                                                                                           | 51         |

| 15.0  | MICROWIRE/SPI                                                                                                  |            |

|       | 15.1 MICROWIRE Operation                                                                                       |            |

|       | 15.2 Master Mode                                                                                               |            |

|       | 15.3         Slave Mode         5           15.4         Interrupt Generation         5                        |            |

|       | 15.4         Interrupt Generation         5.5           15.5         MICROWIRE Interface Registers         5.5 |            |

| 16.0  |                                                                                                                |            |

| 10.0  | 16.1 Functional Overview                                                                                       |            |

|       | 16.2 USART Operation                                                                                           |            |

|       | 16.3 USART Registers                                                                                           |            |

|       | 16.4 Baud Rate Calculations                                                                                    |            |

| 17.0  | Analog Comparators                                                                                             |            |

|       | 17.1 Analog Comparator Control/Status Register                                                                 |            |

|       | (CMPCTRL)68                                                                                                    |            |

|       | 17.2 Analog Comparator Usage6                                                                                  |            |

| 18.0  | A/D Converter                                                                                                  |            |

|       | 18.1 Operating Modes                                                                                           |            |

|       | 18.2 A/D Converter Registers                                                                                   |            |

| 40.0  | 18.3 A/D Converter Programming                                                                                 |            |

| 19.0  | Memory Map                                                                                                     |            |

| 20.0  | Register Layouts         7           20.1         Register layout         7                                    |            |

| 21.0  | ELECTRICAL CHARACTERISTICS                                                                                     |            |

| 2.1.0 | Comparator AC and DC Characteristics                                                                           |            |

|       | Output Signal Levels                                                                                           |            |

| 22.0  | Appendix                                                                                                       |            |

|       | 22.1 8-bit MICROWIRE/SPI (MWSPI)                                                                               | 95         |

|       | 22.2 Timing and watchdog module                                                                                |            |

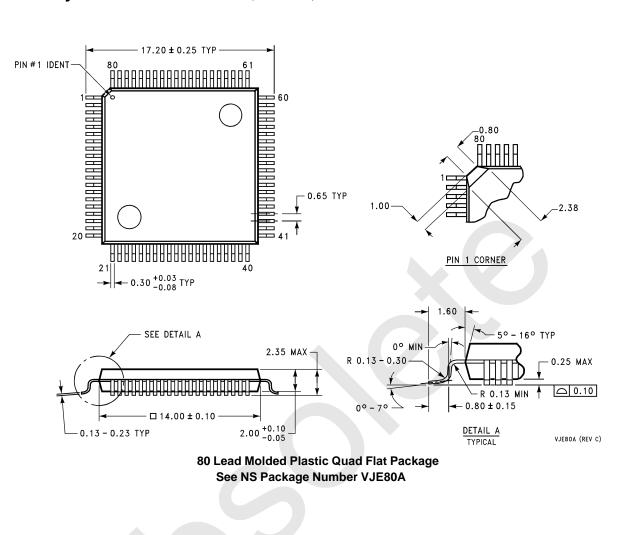

| 23.0  | Physical Dimension                                                                                             | <b>9</b> 7 |

# 1.0 General Description (Continued)

In the following text, device is alsays refered to the family of CompactRISC 16-bit microcontrollers. For the exact feature set, check individual datasheets.

The device is available in a variety of package sizes and types. All devices have 48 kbytes of reprogrammable flash program memory, 1.5 kbytes of ISP memory, 2 kbytes of static RAM, and 640 bytes of non-volatile EEPROM data memory. The 80-pin device has two USARTs, two 16-bit multifunction timers, one SPI/MICROWIRE-PLUS<sup>™</sup> serial interface, an 8-channel A/D converter, two analog comparators, WATCHDOG<sup>™</sup> protection mechanism, and up to 48 general-purpose I/O pins. The 44-pin devices offer the same basic features as the 80-pin device, but with fewer I/O ports and peripheral modules due to the smaller number of available pins.

All devices operate with a high-frequency crystal as the main clock source. Some packages allow the device to operate with either the main clock source or with a slow (32.768 KHz) oscillator in Power Save mode. The device supports several Power Save modes which are combined with multi-source interrupt and wake-up capabilities.

Powerful cross-development tools are available from National Semiconductor and third party suppliers to support the development and debugging of application software for the device. These tools let you program the application software in C and are designed to take full advantage of the CompactRISC architecture.

# 2.0 Features

- CPU Features

- Fully static core, capable of operating at any rate from 0 to 20 MHz (4 MHz minimum in active mode)

- 50 ns instruction cycle time with a 20 MHz external clock frequency

- Multi-source vectored interrupts (internal, external, and on-chip peripheral)

- On-chip power-on reset

- On-Chip Memory

- 48 kbytes of flash program memory or ROM memory (100K cycle)

- 1.5 kbytes of ISP memory (100K cycle)

- 2 kbytes of static RAM data memory

- 640 bytes of non-volatile EEPROM data memory, word-programmable (100K cycle)

- On-Chip Peripherals

- Up to two Universal Synchronous/Asynchronous Receiver/Transmitter (USART) devices

- Programmable Idle Timer and real-time clock (T0)

- Up to two dual 16-bit multi-function timers (MFT1 and MFT2)

- SPI/MICROWIRE-PLUS serial interface

- 8-channel, 8-bit Analog-to-Digital (A/D) converter with external voltage reference, programmable sampleand-hold delay, and programmable conversion frequency

- Up to two analog comparators

- Integrated WATCHDOG logic

- I/O Features

- Up to 48 general-purpose I/O pins (shared with on-chip peripheral I/O pins)

- Programmable I/O pin characteristics: TRI-STATE output, push-pull output, weak pull-up input, high-impedance input

- Software-configurable Schmitt triggers on inputs

- Power Supply

- 4.5V to 5.5V single-supply operation

- Temperature Range

- $-0^{\circ}$ C to +70 $^{\circ}$ C

- $-40^{\circ}$ C to +85°C

- -40°C to +125°C Development Support

- Real-time emulation and full program debug capabilities available

- CompactRISC tools provide C programming and debugging support

# CR16 CompactRISC microcontroller Family Selection Guide

## Programmable devices

| NSID         | Speed<br>(MHz) | Flash/<br>ROM<br>(kByte) | EEPROM<br>Data<br>Memory<br>(Bytes) | SRAM<br>(kBytes) | USART | Timer |    | Temp.<br>Range | Peripherals         | Package<br>Type |

|--------------|----------------|--------------------------|-------------------------------------|------------------|-------|-------|----|----------------|---------------------|-----------------|

| CR16MHS9VJEx | 20             | 48                       | 640                                 | 2                | 2     | 2     | 48 | E, I           | ADC,<br>Comparators | 80PQFP          |

| CR16MFS944Vx | 20             | 48                       | 640                                 | 2                | 2     | 1     | 33 | E, I           | ADC                 | 44PLCC          |

| CR16MES944Vx | 20             | 48                       | 640                                 | 2                | 1     | 2     | 33 | E, I           | ADC                 | 44PLCC          |

| CR16MNS944Vx | 20             | 48                       | None                                | 2                | 1     | 2     | 33 | C, I           | None                | 44PLCC          |

| CR16MUS944Vx | 8              | 48                       | None                                | 2                | 1     | 2     | 33 | С              | None                | 44PLCC          |

#### **ROM devices**

| NSID          | Speed<br>(MHz) | Flash/<br>ROM<br>(kByte) | EEPROM<br>Data<br>Memory<br>(Bytes) | SRAM<br>(kBytes) | USART | Timer | I/Os | Temp.<br>Range | Peripherals         | Package<br>Type |

|---------------|----------------|--------------------------|-------------------------------------|------------------|-------|-------|------|----------------|---------------------|-----------------|

| CR16MHS5VJExy | 20             | 48                       | 640                                 | 2                | 2     | 2     | 48   | Е, І           | ADC,<br>Comparators | 80PQFP          |

| CR16MFS544Vxy | 20             | 48                       | 640                                 | 2                | 2     | 1     | 33   | E, I           | ADC                 | 44PLCC          |

| CR16MES544Vxy | 20             | 48                       | 640                                 | 2                | 1     | 2     | 33   | E, I           | ADC                 | 44PLCC          |

| CR16MPS544Vxy | 20             | 48                       | None                                | 2                | 1     | 2     | 33   | C, I           | ADC                 | 44PLCC          |

| CR16MNS544Vxy | 20             | 48                       | None                                | 2                | 1     | 2     | 33   | C, I           | None                | 44PLCC          |

| CR16MUS544Vxy | 8              | 48                       | None                                | 2                | 1     | 2     | 33   | С              | None                | 44PLCC          |

Note:

• Suffix x in the NSID is defined below:

Temperature Ranges:

E = Extended I = Industrial C = Commercial -40 °C to +125 °C is represented when x is 7 -40 °C to +85 °C is represented when x is 8 0 °C to +70 °C is represented when x is 9

• Suffix y in the NSID defines the ROM code.

**Note:** All devices contains Clock and Reset, MICROWIRE/ API, Multi-Input Wake-Up (MIWU), Power Management (PMM), and the Real-Time Timer and Watchdog (TWM) modules.

## 44-Pin PLCC versus 80-Pin PQFP

For 44PLCC packages, MICROWIRE/SPI slave mode, the first 4 MIWU channels and the Vref pin are not available. 80-pin PQFP packages provide the MICROWIRE/SPI master and slave modes, 8 MIWU channels, Vref pin, and two US-ARTs and two MFTs.

# 3.0 Device Overview

The family of CompactRISC 16-bit microcontrollers are complete microcomputers with all system timing, interrupt logic, program memory, data memory, and I/O ports included onchip, making it well-suited to a wide range of embedded controller applications.

# 3.1 CR16B CPU CORE

The device uses the CR16B CPU core module. This is the same core used in other CompactRISC family members.

The high performance of the CPU core results from the implementation of a pipelined architecture with a two-bytes-percycle pipelined system bus. As a result, the CPU can support a peak execution rate of one instruction per clock cycle.

Compared with conventional RISC processors, the device differs in the following ways:

- The CPU core uses on-chip rather than external memory. This eliminates the need for large and complex bus interface units.

- Most instructions are 16 bits, so all basic instructions are just two bytes long. (Additional bytes are sometimes required for immediate values, so instructions can be two or four bytes long.)

- Non-aligned word access is allowed. Each instruction can operate on 8-bit or 16-bit.

- The device is designed to operate with a clock rate in the 10 to 25 MHz range rather than 100 MHz or more. Most embedded systems face EMI and noise constraints that limit clock speed to these lower ranges. A lower clock speed means a simpler, less costly silicon implementation.

- The instruction pipeline uses three stages. A smaller pipeline eliminates the need for costly branch prediction mechanisms and bypass registers, while maintaining adequate performance for typical embedded controller applications.

# 3.2 MEMORY

The CompactRISC architecture supports a uniform linear address space of 2 megabytes. The device implementation of this architecture uses only the lowest 64 kbytes of address space. Four types of on-chip memory occupy specific intervals within this address space: 48 kbytes of flash program memory, 1.5 kbytes of ISP memory, 2 kbytes of static RAM, and 640 bytes of EEPROM data memory.

The 48 kbytes of flash program memory are used to store the application program. It has security features to prevent unintentional programming and to prevent unauthorized access to the program code. This memory can be programmed either with the device plugged into an EPROM programmer unit (external programming) or with the device installed in the application system (in-system programming).

The 2 kbytes of static RAM are used for temporary storage of data and for the program stack and interrupt stack. Read and write operations can be byte-wide or word-wide, depending on the instruction executed by the CPU. Each memory access requires one clock cycle; no wait cycles or hold cycles are required.

The 640 bytes of EEPROM data memory are used for nonvolatile storage of data, such as configuration settings entered by the end-user. The CPU reads or writes this memory by using ordinary byte-wide or word-wide memory access commands. After the CPU performs a write to this memory, the on-chip hardware completes the EEPROM programming in the background. A register status bit indicates the status of the EEPROM programming operation.

There is a factory programmed boot memory used to store In-System-Programming (ISP) code. (this code allows programming of the program memory via one of the USART interfaces in the final application.)

For the flash program memory, the device internally generates the necessary voltages for programming. No additional power supply is required.

# 3.3 INPUT/OUTPUT PORTS

Each device has 48 software-configurable I/O pins, organized into six 8-pin ports called Port B, Port C, Port F, Port G, Port L, and Port I. Each pin can be configured to operate as a general-purpose input or general-purpose output. In addition, many I/O pins can be configured to operate as a designated input or output for an on-chip peripheral module such as the USART, timer, A/D converter, or MICROWIRE/SPI interface.

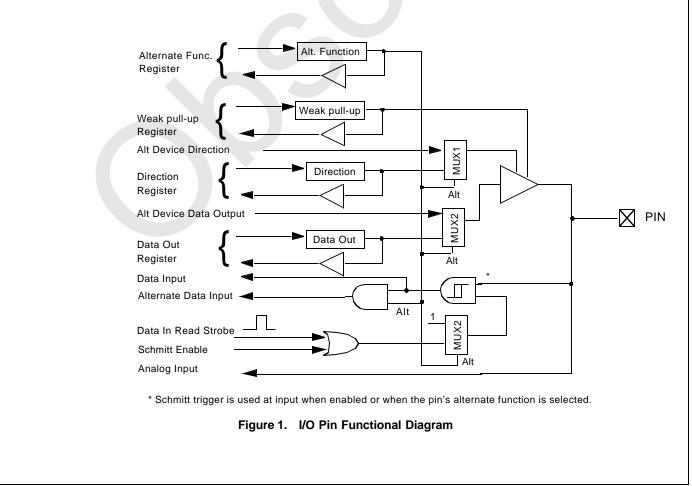

The I/O pin characteristics are fully programmable. Each pin can be configured to operate as a TRI-STATE output, pushpull output, weak pull-up input, or high-impedance input. Input pins can be software-configured to use Schmitt triggers for noise resistance.

Each 44-pin device has a subset of the pins available in the 80-pin device. This results in the loss of some features that are available in the larger-package device:

- One of the two USARTs or one of the two multi-function timers (depending on package selection)

- Synchronous mode in the remaining USART(s)

- Slave mode operation for the MICROWIRE/SPI interface

- Separate external V<sub>REF</sub> for the A/D converter

- Comparators

- · Four of the eight Multi-Input Wakeup pins

- NMI interrupt input pin

# 3.4 BUS INTERFACE UNIT

The Bus Interface Unit (BIU) controls the interface between the on-chip modules to the internal core bus. It determines the configured parameters for bus access (such as the number of wait states for memory access) and issues the appropriate bus signals for each requested access.

The BIU uses a set of control registers to determine how many wait states and hold states are to be used when accessing EEPROM memory. Upon start-up of the device, these registers must be programmed with appropriate values so that the minimum allowable number states is used. This number varies with the clock frequency and the type of onchip device being accessed.

# 3.5 INTERRUPTS

The Interrupt Control Unit (ICU) receives interrupt requests from internal and external sources and generates interrupts to the CPU. An interrupt is an event that temporarily stops the normal flow of program execution and causes a separate interrupt service routine to be executed. After the interrupt is serviced, CPU execution continues with the next instruction in the program following the point of interruption.

Interrupts from the timers, USARTs, MICROWIRE/SPI interface, multi-input wake-up, and A/D converter are all maskable interrupts; they can be enabled or disabled by the software. There are 16 of these maskable interrupts, organized into 16 predetermined levels of priority.

The highest-priority interrupt is the Non-Maskable Interrupt  $(\overline{\text{NMI}})$ , which is generated by a signal received on the  $\overline{\text{NMI}}$  input pin. This interrupt is not available in the 44-pin packages.

# 3.6 MULTI-INPUT WAKE-UP

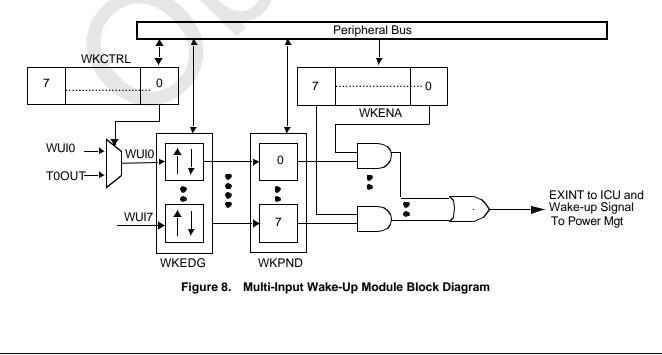

The Multi-Input Wake-up (MIWU) module can be used for either of two purposes: to provide inputs for waking up (exiting) from the HALT, IDLE, or Power Save mode; or to provide general-purpose edge-triggered maskable interrupts from external sources. This eight-channel module generates one combined interrupt to the CPU based on the signals received on its eight input channels. Channels can be individually enabled or disabled, and programmed to respond to positive or negative edges.

# 3.7 DUAL CLOCK AND RESET

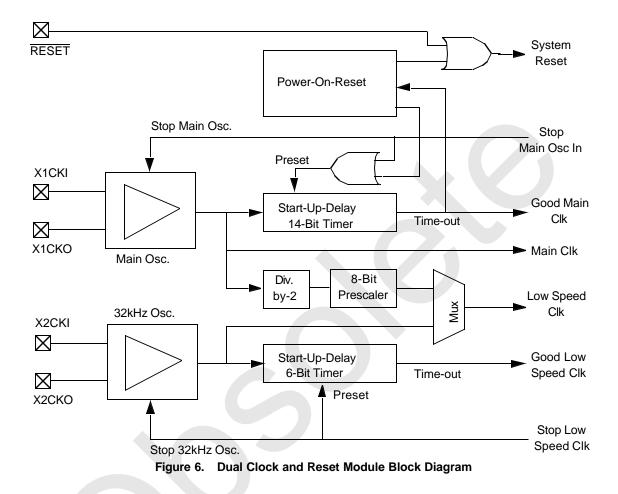

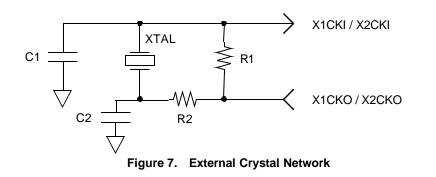

The Dual Clock and Reset (CLK2RES) module generates a high-speed main system clock from an external crystal network. It also provides the main system reset signal and a power-on reset function.

In the 80-pin package, the module also generates a slow system clock (32.768 KHz) from another external crystal network. The slow clock is used for operating the device in power-save mode. For the 44-pin devices and for devices not using a secondary crystal network, the slow clock can be generated by dividing the high-speed main clock by a prescaler factor.

# 3.8 POWER MANAGEMENT

The Power Management Module (PMM) improves the efficiency of the device by changing the operating mode (and therefore the power consumption) according to the current level of activity.

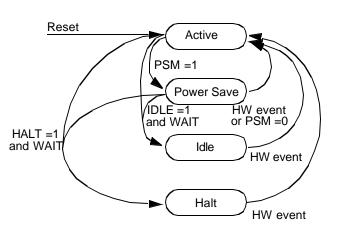

The device can operate in any of four power modes:

- Active: The device operates at full speed using the high-frequency clock. All device functions are fully operational.

- Power Save: The device operates at reduced speed using the slow clock. The CPU and some modules can continue to operate at this low speed.

- IDLE: The device is inactive except for the Power Management Module and Timing and Watchdog Module, which continue to operate using the slow clock.

- HALT: The device is inactive but still retains its internal state (RAM and register contents).

# 3.9 MULTI-FUNCTION TIMER

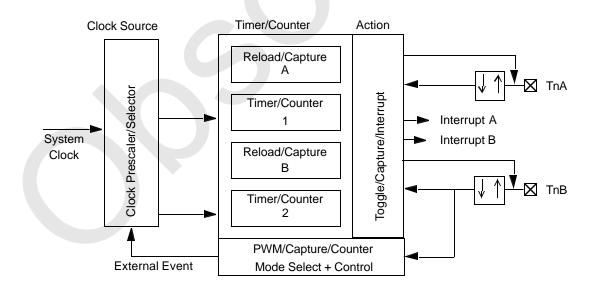

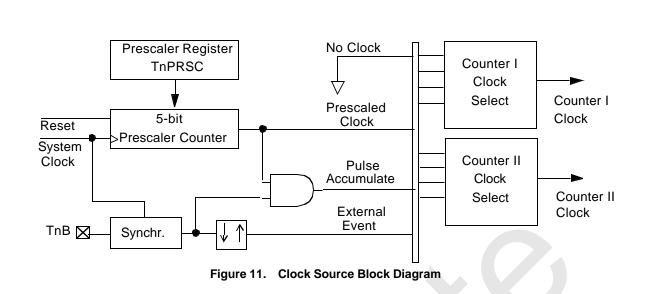

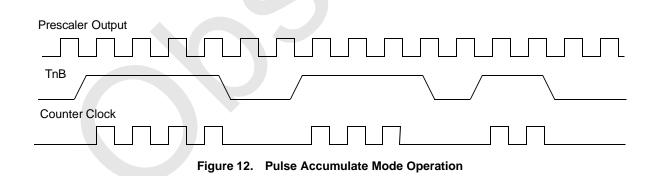

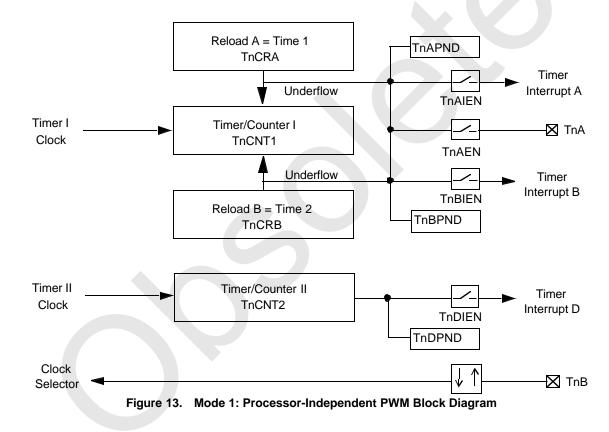

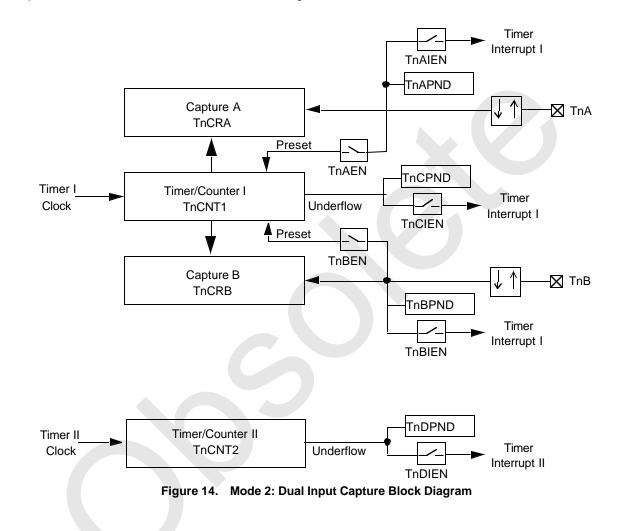

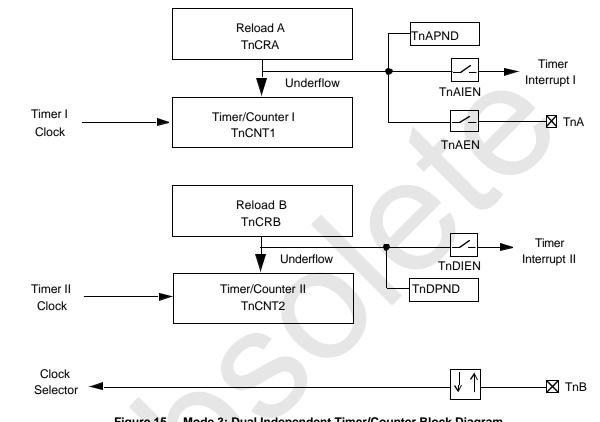

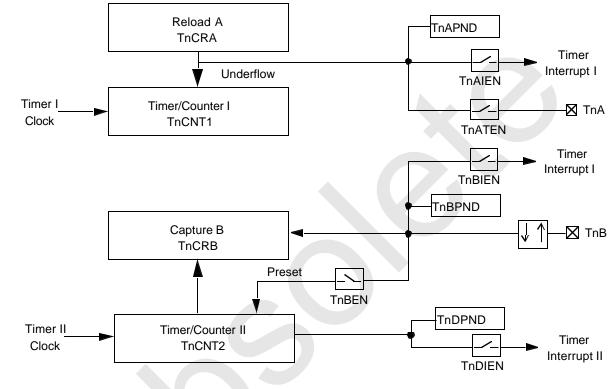

The Multi-Function Timer (MFT16) module contains two independent timer/counter units called MFT1 and MFT2, each containing a pair of 16-bit timer/counter registers. Each timer/ counter unit can be configured to operate in any of the following modes:

- Processor-Independent Pulse Width Modulation (PWM) mode, which generates pulses of a specified width and duty cycle, and which also provides a general-purpose timer/counter

- Dual Input Capture mode, which measures the elapsed time between occurrences of external events, and which also provides a general-purpose timer/counter

- Dual Independent Timer mode, which generates system timing signals or counts occurrences of external events

- Single Input Capture and Single Timer mode, which provides one external event counter and one system timer

# 3.10 REAL-TIME TIMER AND WATCHDOG

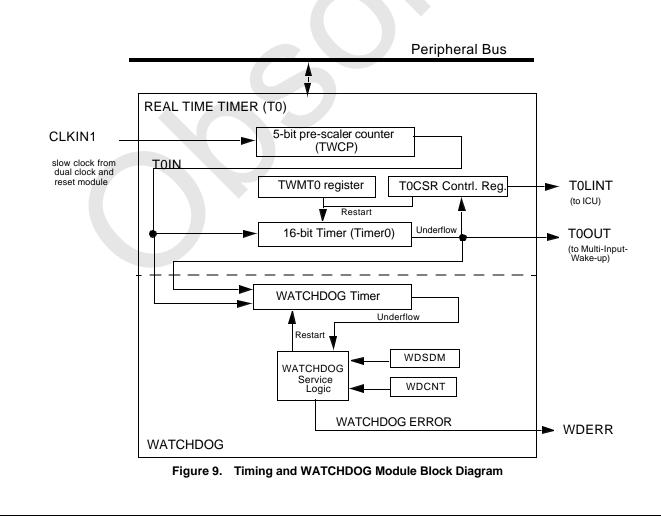

The Timing and Watchdog Module (TWM) generates the clocks and interrupts used for timing periodic functions in the system. It also provides Watchdog protection against software errors. The module operates on the slow (32.768 KHz) clock.

The real-time timer generates a periodic interrupt to the CPU at a software-programmed interval. This can be used for real-time functions such as a time-of-day clock.

The Watchdog is designed to detect program execution errors such as an infinite loop or a "runaway" program. Once Watchdog operation is initiated, the application program must periodically write a specific value to a Watchdog register, within specific time intervals. If the software fails to do so, a Watchdog error is triggered, which resets the device.

# 3.11 USART

The USART is a Universal Synchronous/Asynchronous Receiver-Transmitter, a device used for serial communications. It supports a wide range of programmable baud rates and data formats, and handles parity generation and several error detection schemes. The baud rate is generated on-chip, under software control.

The synchronous mode of operation is not available in the 44-pin devices.

# 3.12 MICROWIRE/SPI

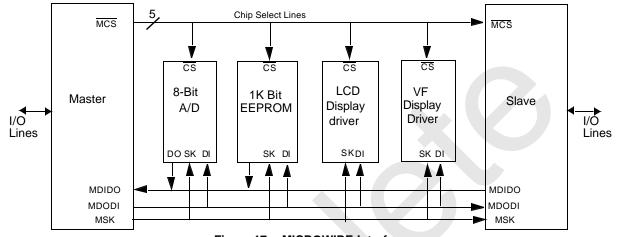

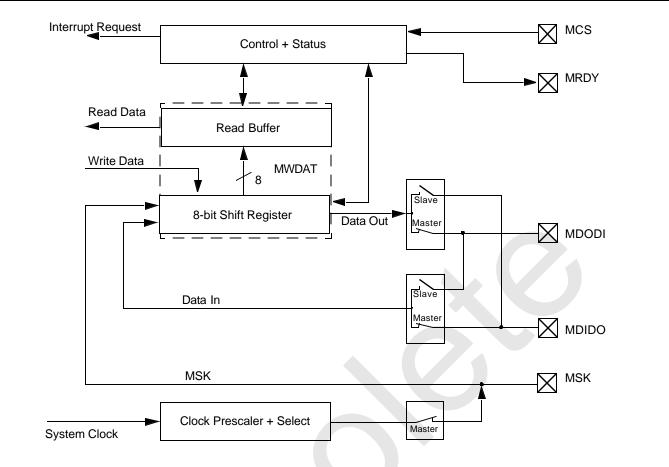

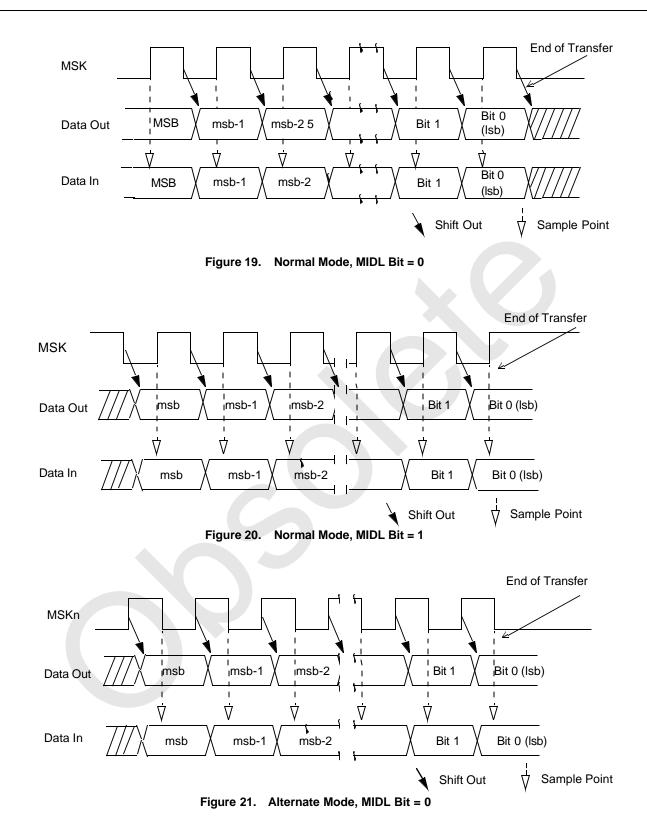

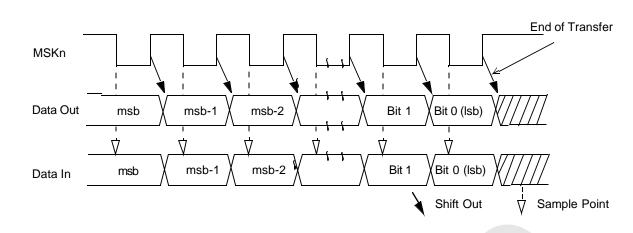

The MICROWIRE/SPI (MWSPI) interface module supports asynchronous serial communications with other devices that conform to MICROWIRE or Serial Peripheral Interface (SPI) specifications.

The MICROWIRE interface allows several devices to communicate over a single system consisting of three wires: serial in, serial out, and shift clock. At any given time, one device on the MICROWIRE interface operates as the master, while all other devices operate as slaves. An 80-pin device supports the full set of slave select and Ready lines for multislave implementation, while a 44-pin device has only the basic Data-in/Data-out/Clock lines, limiting its implementation to master mode.

# 3.13 A/D CONVERTER

The A/D Converter (ADC) module is an 8-channel multiplexed-input analog-to-digital converter. The A/D Converter receives an analog voltage signal on an input pin and converts the analog signal into an 8-bit digital value using successive approximation. The CPU can then read the result from a memory-mapped register. The module supports four automated operating modes, providing single-channel or scanned 4-channel operation in single or continuous mode.

The 80-pin device has a separate pin, Vref, for the A/D reference voltage. The 44-pin devices use the AVCC (analog VCC) power supply pin as the reference voltage.

# 3.14 ANALOG COMPARATORS

The Dual Analog Comparator (ACMP2) module contains two independent analog comparators with all necessary control logic. Each comparator unit compares the analog input voltages applied to two input pins and determines which voltage is higher. The CPU uses a memory-mapped register to control the comparator and to obtain the comparison results. The comparison result can also be applied to comparator output pins.

# 3.15 DEVELOPMENT SUPPORT

A powerful cross-development tool set is available from National Semiconductor and third parties to support the development and debugging of application software for the device. The tool set lets you program the application software in C and is designed to take full advantage of the CompactRISC architecture.

There are In-System Emulation (ISE) devices available for the device from iSYSTEM<sup>™</sup>, as well as lower-cost evaluation boards. See your National Semiconductor sales representative for current information on availability of various features of emulation equipment and evaluation boards.

| GND<br>Vcc<br>GND<br>ENV0-44/SLCLK <sup>a</sup><br>PC0<br>PC1 |       | 44<br>1<br>N/A | 13<br>14 | PWR |

|---------------------------------------------------------------|-------|----------------|----------|-----|

| GND<br>ENV0-44/SLCLK <sup>a</sup><br>PC0                      |       |                | 14       |     |

| ENV0-44/SLCLK <sup>a</sup><br>PC0                             |       | N/A            |          | PWR |

| PC0                                                           |       |                | 15       | PWR |

|                                                               |       | 2              | N/A      | I/O |

| PC1                                                           |       | 3              | 17       | I/O |

|                                                               |       | 4              | 18       | I/O |

| PC2                                                           |       | 5              | 19       | I/O |

| PC3                                                           |       | 6              | 20       | I/O |

| PC4                                                           |       | 7              | 21       | I/O |

| PC5                                                           |       | 8              | 22       | I/O |

| PC6                                                           |       | 9              | 23       | I/O |

| PC7                                                           |       | 10             | 24       | I/O |

| ENV0-80/SLCLK <sup>a</sup>                                    |       | N/A            | 26       | I/O |

| CLKOUT2 <sup>b</sup>                                          |       | 11             | 27       | I/O |

| ENV1/CLK <sup>a</sup>                                         |       | 11             | 28       | I/O |

| PG7                                                           | CKX1  | N/A            | 29       | I/O |

| PG6                                                           | TDX1  | 12             | 30       | I/O |

| PG5                                                           | RDX1  | 13             | 31       | I/O |

| PG4                                                           | MRDY  | N/A            | 32       | I/O |

| PG3                                                           | MCS   | N/A            | 33       | I/O |

| PG2                                                           | MSK   | 14             | 34       | I/O |

| PG1                                                           | MDODI | 15             | 35       | I/O |

| PG0                                                           | MDIDO | 16             | 36       | I/O |

| PF7                                                           |       | N/A            | 38       | I/O |

| PF6                                                           | CKX2  | N/A            | 39       | I/O |

| PF5                                                           | T2B   | 17             | 40       | I/O |

| PF4                                                           | T2A   | 18             | 41       | I/O |

| PF3°                                                          | TDX2  | 19 or N/A *    | 42       | I/O |

| PF2 <sup>c</sup>                                              | RDX2  | 20 or N/A *    | 43       | I/O |

| PF1 <sup>c</sup>                                              | T1B   | N/A or 19 *    | 44       | I/O |

| PF0°                                                          | T1A   | N/A or 20 *    | 45       | I/O |

| NMI                                                           |       | N/A            | 46       | I   |

| X1CKO                                                         |       | 21             | 48       | 0   |

| X1CKI                                                         |       | 22             | 49       | I   |

| GND                                                           |       | N/A            | 50       | PWR |

| Pin Name           | Alternate Function(s)       | 44-pin PLCC<br>Package<br>Pin Number | 80-pin PQFP<br>Package<br>Pin Number | Туре |

|--------------------|-----------------------------|--------------------------------------|--------------------------------------|------|

| GND                |                             | 24                                   | 52                                   | PWR  |

| X2CKO              |                             | N/A                                  | 53                                   | 0    |

| X2CKI              |                             | N/A                                  | 54                                   | I    |

| PI0                | ACH0 <sup>e,f</sup>         | 25                                   | 57                                   | I/O  |

| PI1                | ACH1 <sup>e,f</sup>         | 26                                   | 58                                   | I/O  |

| Pl2                | ACH2 <sup>e,f</sup>         | 27                                   | 59                                   | I/O  |

| PI3                | ACH3 <sup>e,f</sup>         | 28                                   | 60                                   | I/O  |

| PI4                | ACH4 <sup>e,f</sup> , MIWU4 | 29                                   | 61                                   | I/O  |

| PI5                | ACH5 <sup>e,f</sup> , MIWU5 | 30                                   | 62                                   | I/O  |

| PI6                | ACH6 <sup>e,f</sup> , MIWU6 | 31                                   | 63                                   | I/O  |

| PI7                | ACH7 <sup>e,f</sup> , MIWU7 | 32                                   | 64                                   | I/O  |

| Vref               |                             | N/A                                  | 66                                   | PWR  |

| AVcc               |                             | 33 <sup>f</sup>                      | 67                                   | PWR  |

| AGND               |                             | 34 <sup>f</sup>                      | 68                                   | PWR  |

| GND                |                             | N/A                                  | 69                                   | PWR  |

| Vcc                |                             | N/A                                  | 70                                   | PWR  |

| GND                |                             | N/A                                  | 71                                   | PWR  |

| RESET <sup>d</sup> |                             | 35                                   | 76                                   | I    |

| PB0                |                             | 36                                   | 77                                   | I/O  |

| PB1                |                             | 37                                   | 78                                   | I/O  |

| PB2                |                             | 38                                   | 79                                   | I/O  |

| PB3                |                             | 39                                   | 80                                   | I/O  |

| PB4                |                             | 40                                   | 1                                    | I/O  |

| PB5                |                             | 41                                   | 2                                    | I/O  |

| PB6                |                             | 42                                   | 3                                    | I/O  |

| PB7                |                             | 43                                   | 4                                    | I/O  |

| PL0                | COMP1N <sup>e</sup>         | N/A                                  | 73                                   | I/O  |

| PL1                | COMP1P <sup>e</sup>         | N/A                                  | 74                                   | I/O  |

| PL2                | COMP10                      | N/A                                  | 5                                    | I/O  |

| PL3                |                             | N/A                                  | 6                                    | I/O  |

| PL4                | COMP2N <sup>e</sup> , MIWU0 | N/A                                  | 8                                    | I/O  |

| PL5                | COMP2P <sup>e</sup> , MIWU1 | N/A                                  | 9                                    | I/O  |

# Table 1 Package Pin Assignments

| Pin Name | Alternate Function(s) | Alternate Function(s) 44-pin PLCC<br>Package<br>Pin Number |    | Туре |

|----------|-----------------------|------------------------------------------------------------|----|------|

| PL6      | COMP2O, MIWU2         | N/A                                                        | 11 | I/O  |

| PL7      | MIWU3                 | N/A                                                        | 12 | I/O  |

Notes:

a. The ENV0 and ENV1 pins each have a weak pullup to keep the input from floating.

b. The CLKOUT2 function is shared with the  $\overline{ENV1}/CLK$  pin in the 44-pin device.

c. In the 44-pin CR16MES, CR16MNS, CR16MPS, and CR16MUS packages, PF1 and PF0 are available; PF3 and PF2 are not available.

In the 44-pin CR16MFS, CR16MOS, CR16MQS, and CR16MVS packages, PF3 and PF2 are available; PF1 and PF0 are not available.

d. The RESET input has a weak pulldown.

e. These functions are always enabled due to the direct low-impedance path to these pins.

f. These functions may not be available on some 44-pin devices.

# 3.16 PIN DESCRIPTION

The following is a brief description of all CR16MHR6 pins.

Some pins have alternate functions which may be enabled. These pins can be individually configured as general purpose pins, even when the module they belong to is enabled.

# Table 2 Input Pins

| Signal  | Туре   | Active | Pin (* for a<br>shared pin) | Function                                                      |

|---------|--------|--------|-----------------------------|---------------------------------------------------------------|

| X1CKI   | OSC    | High   |                             | Main oscillator clock input.                                  |

| X2CKI   | OSC    | High   |                             | 32kHz oscillator clock input.                                 |

| RESET   | CMOS   | Low    |                             | Chip general reset pin. Schmitt trigger input, asynchronous.  |

| ISE     | CMOS   | Low    |                             | Interrupt input for development system.                       |

| T1B     | CMOS   | Prog.  | *                           | Timer 1 input B. Shares pin with I/O port pin PF1.            |

| T2B     | CMOS   | Prog.  | *                           | Timer 2 input B. Shares pin with I/O port pin PF5.            |

| RDX1    | CMOS   | High   | *                           | USART 1 receive data input. Shares pin with I/O port pin PG5. |

| RDX2    | CMOS   | High   | *                           | USART 2 receive data input. Shares pin with I/O port pin PF4. |

| ACH0    | Analog |        | *                           | A2D converter channel 0. Shares pin with I/O port pin PI0     |

| ACH1    | Analog |        | *                           | A2D converter channel 1. Shares pin with I/O port pin PI1     |

| ACH2    | Analog |        | *                           | A2D converter channel 2. Shares pin with I/O port pin PI2     |

| ACH3    | Analog |        | *                           | A2D converter channel 3. Shares pin with I/O port pin PI3     |

| ACH4    | Analog |        | *                           | A2D converter channel 4. Shares pin with I/O port pin PI4     |

| ACH5    | Analog |        | *                           | A2D converter channel 5. Shares pin with I/O port pin PI5     |

| ACH6    | Analog |        | *                           | A2D converter channel 6. Shares pin with I/O port pin PI6     |

| ACH7    | Analog |        | *                           | A2D converter channel 7. Shares pin with I/O port pin PI7     |

| MCS     | CMOS   | Low    | *                           | SPI/MICROWIRE slave select. Shares pin with I/O port pin PG3. |

| NMI     | CMOS   | Low    |                             | External non-maskable interrupt.                              |

| ENV0-44 | CMOS   | Low    | *                           | Strap pin on 44-pin package to select operating environment.  |

| ENV0-80 | CMOS   | Low    | *                           | Strap pin on 80-pin package to select operating environment.  |

| ENV1    | CMOS   | Low    | *                           | Strap pin to select operating environment.                    |

| ENV2    | CMOS   | Low    |                             | Strap pin to select operating environment.                    |

# Table 3 Output Pins

| Signal  | Туре | Active | Pin (* for a shared pin) | Function                                                                                             |

|---------|------|--------|--------------------------|------------------------------------------------------------------------------------------------------|

| X1CKO   | OSC  | High   |                          | Main oscillator clock output.                                                                        |

| X2CKO   | OSC  | High   |                          | 32 kHz oscillator clock output.                                                                      |

| CLK     | CMOS | High   |                          | External reference clock for development environment.                                                |

| TDX1    | CMOS | High   | *                        | USART 1 transmit data output. Shares pin with I/O port pin PG6.                                      |

| TDX2    | CMOS | High   | *                        | USART 2 transmit data output. Shares pin with I/O port pin PF5.                                      |

| MRDY    | CMOS | Low    | *                        | SPI/MICROWIRE slave ready output. Shares pin with I/O port pin PG4                                   |

| CLKOUT2 | OSC  | High   |                          | System clock divided-by-2 output (shared with the $\overline{\text{ENV1}}$ pin in the 44-pin device) |

|         | Table 4   Input/Output Pins |        |                             |                                                                               |  |  |  |  |

|---------|-----------------------------|--------|-----------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| Signal  | Туре                        | Active | Pin (* for a<br>shared pin) | Function                                                                      |  |  |  |  |

| PF[0:7] | CMOS                        | High   | *                           | Generic I/O port. Shared with T1A, T1B, T2A, T2B, RDX2, TDX2, CKX2.           |  |  |  |  |

| PG[0:7] | CMOS                        | High   | *                           | Generic I/O port. Shared with MDIDO, MDODI, MSK, MCS, MRDY, RDX1, TDX1, CKX1. |  |  |  |  |

| PB[0:7] | CMOS                        | High   | *                           | Generic I/O port.                                                             |  |  |  |  |

| PC[0:7] | CMOS                        | High   | *                           | Generic I/O port.                                                             |  |  |  |  |

| PL[0:7] | CMOS                        | High   | *                           | Generic I/O port. Shared with six comparator pins and four MIWU pins.         |  |  |  |  |

| PI[0:7] | CMOS                        | High   | *                           | Generic I/O port. Shared with ADC input channels 0-7 and four MIWU pins.      |  |  |  |  |

| T1A     | CMOS                        | Prog   | *                           | Timer 1 input A. Shared with I/O port pin PF0.                                |  |  |  |  |

| T2A     | CMOS                        | Prog   | *                           | Timer 2 input A. Shared with I/O port pin PF4.                                |  |  |  |  |

| MDIDO   | CMOS                        | High   | *                           | Master In/Slave Out port: SPI/Microwire. Shared with I/O pin PG0.             |  |  |  |  |

| MDODI   | CMOS                        | High   | *                           | Master Out/Slave In port: SPI/Microwire. Shared with I/O pin PG1.             |  |  |  |  |

| MSK     | CMOS                        | High   | *                           | SPI/Microwire clock. Shared with I/O pin PG2.                                 |  |  |  |  |

| CKX1    | CMOS                        | High   | *                           | USART 1 clock signal. Shared with I/O pin PG7.                                |  |  |  |  |

| CKK2    | CMOS                        | High   | *                           | USART 2 clock signal. Shared with I/O pin PF6.                                |  |  |  |  |

# Table 5 Power Supply

| Signal | Function                                                  |  |  |  |

|--------|-----------------------------------------------------------|--|--|--|

| Vcc    | Main digital power supply.                                |  |  |  |

| Vref   | Voltage reference supply for analog to digital converter. |  |  |  |

| AVcc   | Analog power supply for analog/digital converter.         |  |  |  |

| AGND   | Analog reference ground supply.                           |  |  |  |

| GND    | Main digital reference ground.                            |  |  |  |

# 4.0 System Configuration

The CR16MHS9 has two input pins, ENV0 and ENV1, which are used to specify the operating environment of the device upon reset. There are also two system configuration registers, called the Module Configuration (MCFG) register and the Module Status (MSTAT) register.

# 4.1 ENV0 AND ENV1 PINS

Upon reset, the operating mode of the device is determined by the state of the  $\overline{\text{ENV0}}$  and  $\overline{\text{ENV1}}$  input pins, as indicated in Table6.

Table 6 Operating Environment Selection

| ENV1 | ENV0 | Operating Environment                                                                                           |

|------|------|-----------------------------------------------------------------------------------------------------------------|

| 0    | 0    | Test Mode                                                                                                       |

| 0    | 1    | Test Mode                                                                                                       |

| 1    | 0    | In-System Programming mode                                                                                      |

| 1    | 1    | Internal ROM enabled Mode (IRE), if<br>program memory is not empty; or ISP-<br>Mode, if program memory is empty |

In the case where the  $\overline{\text{ENV1}}$  and  $\overline{\text{ENV0}}$  pins are both high, the reset algorithm looks at the FLCTRL2.EMPTY bit to determine whether the program memory is empty, and sets the operating mode accordingly.

The ENV0 and ENV1 pins have on-chip pull-up devices that are enabled during reset while the pins are being sampled. Therefore, if they are left unconnected, the inputs are considered high and the normal operating mode (IRE-Mode) is selected and the CPU starts to execute code at address 0. To enter any other operating mode, the external hardware must drive the appropriate input low.

In the case where the ISP-Mode is selected, the chip starts executing the ISP code residing in the on-chip boot ROM area.

The Test Modes are reserved for factory testing and for external programming of the flash program memory; they should not be invoked otherwise.

# 4.2 MODULE CONFIGURATION (MCFG) REGISTER

The MCFG register is a byte-wide, read/write register that sets the general programmable features of the device.

Upon reset, the non-reserved bits of this register are cleared to zero. The start-up software must write a specific value to this register in order to configure the CLK output pin function.

When the software writes to this register, it must write a zero to each reserved bit for the device to operate properly. The register should be written in active mode only, not in power save, HALT, or IDLE mode. However, the register contents are preserved during all power modes.

The MCFG register format is shown below.

| Reserved CLK2OE SLCOE2 FEEDM SLCLKOE CLKOE Reserved |   | 7    | 6     | 5      | 4      | 3     | 2       | 1     | 0        |

|-----------------------------------------------------|---|------|-------|--------|--------|-------|---------|-------|----------|

|                                                     | ſ | Rese | erved | CLK2OE | SLCOE2 | FEEDM | SLCLKOE | CLKOE | Reserved |

| CLKOE | CPU Clock Output Enable. When this bit is         |

|-------|---------------------------------------------------|

|       | cleared (0), the CLK pin remains in the high-im-  |

|       | pedance state. When this bit is set (1) in normal |

operating mode, the CLK pin operates as a CPU clock output.

- SLCLKOE Slow Clock Output Enable. When cleared (0), the SLCLK pin of the 44-pin package (ENV0-44 pin) remains in the high-impedance state. When set (1), this pin produces the slow clock as an output.

- FEEDM Fast EEPROM Data Memory Access. This bit is set (1) for zero-wait-state access to the EE-PROM data memory, or cleared (0) for onewait-state access to the data ROM. For information on the required number of wait states, see Table8.

- SLCOE2 Slow Clock Output Enable. When cleared (0), the SLCLK pin of the 80-pin package (ENV0-80 pin) remains in the high-impedance state. When set (1), this pin produces the slow clock as an output.

- CLK2OE CPU Clock Divide-by-2 Output Enable. When this bit is cleared (0), the CLKOUT2 pin remains in the high-impedance state. When this bit is set (1) and the CLKOE bit is cleared, the CLKOUT2 pin operates as clock output, with a frequency of one-half that of the CPU clock.

# 4.3 MODULE STATUS (MSTAT) REGISTER

The MSTAT register is a byte-wide, read-only register that indicates the general status of the device.

The MCFG register format is shown below.

|   | 7    | 4    | 3       | 2        | 1     | 0     |

|---|------|------|---------|----------|-------|-------|

| I | Rese | rved | PGMBUSY | Reserved | OENV1 | OENV0 |

- OENV(1:0) Operating Environment. These two bits contain the values applied to the ENV1 and ENV0 pins upon reset. These bit values are controlled by the external hardware upon reset and are held constant in the register until the next reset.

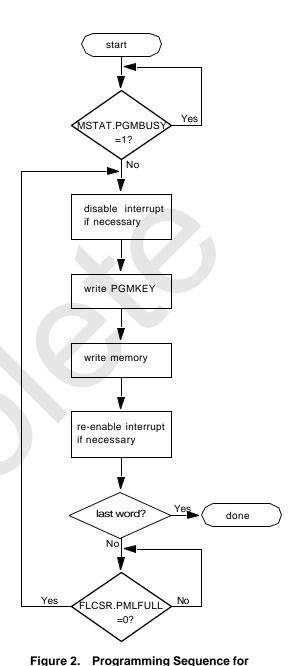

- PGMBUSY Flash Programming Busy. This bit is automatically set to 1 when either the program memory or the data memory is busy being programmed. It is cleared to 0 when neither of the two flash memories are busy being programmed. When this bit is set, the software should not attempt to access either of these two memories.

# 5.0 Input/Output Ports

Each device has up to 48 software-configurable I/O pins, organized into six ports of up to eight pins per port. The exact number of port pins varies with the package type. The ports are named Port B, Port C, Port F, Port G, Port L, and Port I.

Each pin can be configured to operate as a general-purpose input or general-purpose output. In addition, many I/O pins can be configured to operate as a designated input or output for an on-chip peripheral module such as the USART. This is called the pin's "alternate function." The alternate functions of all I/O pins are shown in the pinout diagrams in Table1.

The I/O pin characteristics are fully programmable. Each pin can be configured to operate as a TRI-STATE output, pushpull output, weak pull-up input, or high-impedance input. Different pins within the same port can be individually configured to operate in different modes.

Figure1 is a diagram showing the functional features of an I/ O port pin. The register bits, multiplexers, and buffers allow the port pin to be configured into the various operating modes. The output buffer is a TRI-STATE buffer with weak pull-up capability. The weak pull-up, if used, prevents the port pin from going to an undefined state when it operates as an input.

The input buffer is disabled when it is not needed to prevent leakage current. When enabled, it buffers the input signal and sends the pin's logic level to the appropriate on-chip module where it is latched. A Schmitt trigger, when enabled, minimizes the effects of electrical noise. The electrical characteristics and drive capabilities of the input and output buffers are described in Section21.0.

For some pins, a direct low-impedance path is provided between the pin and an internal analog function. These are the input pins to the A/D converter and the analog comparators

# 5.1 PORT REGISTERS

Each port has an associated set of memory-mapped registers used for controlling the port and for holding the port data. In general, there are six such registers:

- PxALT: Port alternate function register

- PxDIR: Port direction register

- PxDIN: Port data input register

- PxDOUT: Port data output register

- PxWKPU: Port weak pull-up register

- PxSCHEN: Port Schmitt trigger enable register

In the descriptions of the ports and port registers, the lowercase letter "x" represents the port designation, either B, C, F, G, L, or I. For example, "PxDIR register" means any one of the port direction registers: PBDIR, PCDIR, PFDIR, and so on.

All of the port registers are byte-wide read/write registers, except for the port data input registers, which are read-only registers. Each register bit controls the function of the corresponding port pin. For example, PFDIR.2 (bit 2 of the PFDIR register) controls the operation of port pin PF2.

# 5.1.1 Port Alternate Function Register

Each port that supports an alternate function (any port other than Port B or Port C) has an alternate function register (Px-ALT). This register determines whether the port pins are used for general-purpose I/O or for the predetermined alternate function. Each port pin can be controlled independently.

A bit cleared to 0 in the alternate function register causes the corresponding pin to be used for general-purpose I/O. In this configuration, the output buffer is controlled by the direction register and the data output register. The input buffer is routed to the data input register. The input buffer is blocked except when the buffer is actually being read.

A bit set to 1 in the alternate function register causes the corresponding pin to be used for its predetermined peripheral I/ O function. The output buffer data and TRI-STATE configuration are controlled by signals coming from the on-chip peripheral device. The input buffer is enabled continuously in this case. To minimize power consumption, the input signal should be held within 0.2 volts of the VCC or GND voltage.

A reset operation clears the port alternate function registers to 0, which programs the pins to operate as general-purpose I/O ports. This register must be enabled before the corresponding alternate function is enabled.

# 5.1.2 Port Direction Register

The port direction register (PxDIR) determines whether each port pin is used for input or for output. A bit cleared to 0 causes the pin to operate as an input, which puts the output buffer in the high-impedance state. A bit set to 1 causes the pin to operate as an output, which enables the output buffer.

A reset operation clears the port direction registers to 0, which programs the pins to operate as inputs.

# 5.1.3 Port Data Input Register

The data input register (PxDIN) is a read-only register that returns the current state of each port pin. The CPU can read this register at any time even when the pin is configured as an output.

# 5.1.4 Port Data Output Register

The data output register (PxDOUT) holds the data to be driven onto each port pin configured to operate as a general-purpose output. In this configuration, writing to the register changes the output value. Reading the register returns the last value written to the register.

A reset operation leaves the register contents unchanged. Upon power-up, the registers contain unknown values.

# 5.1.5 Port Weak Pull-Up Register

The weak pull-up register (PxWKPU) determines whether each port pin uses a weak pull-up on the output buffer. A bit set to 1 causes the weak pull-up to be used, while a bit cleared to 0 causes the weak pull-up not to be used.

The pull-up device, if enabled by the register bit, operates in the general-purpose I/O mode whenever the port output buffer is in the TRI-STATE mode. In the alternate function mode, the pull-ups are always disabled.

A reset operation clears the port weak pull-up registers to 0, which disables all pull-ups.

# 5.1.6 Port Schmitt Input Enable Register

PxSCHEN registers are byte-wide read/write registers. They enable the Schmitt trigger characteristics on Px input buffers when these pins are used as general purpose I/O ports. When cleared (0) with the pins used as general purpose I/O ports, each bit in PxSCHEN enables the corresponding input buffer only when the port is read, and therefore the input buffer may not exhibit any Schmitt trigger behavior. When set (1), the input buffer is enabled, and will exhibit Schmitt trigger behavior. PxSCHEN registers are cleared upon reset.

# 5.2 OPEN-DRAIN OPERATION

A port pin can be configured to operate as an inverting opendrain output buffer. To do this, the CPU should clear the bit in the data output register (PxDOUT) and then use the port direction register (PxDIR) to set the value of the port pin. With the direction register bit set to 1 (direction=out), the value zero is forced on the pin. With the direction register bit cleared to 0 (direction=in), the pin is placed in the TRI-STATE mode. If desired, the internal weak pull-up can be enabled to pull the signal high when the output buffer is in the TRI-STATE mode.

# 6.0 CPU and Core Registers

The device uses the same CR16B CPU core as other CompactRISC family members. The core's Reduced Instruction Set Computer (RISC) architecture allows a processing rate of up to one instruction per clock cycle.

The CPU core uses the following set of internal registers:

- General-purpose registers (R0-R13, RA, and SP)

- Dedicated address registers (PC, ISP, and INTBASE)

- Processor Status Register (PSR)

- Configuration Register (CFG)

All of these registers are 16 bits wide except for the three address registers, which are 21 bits wide.

Some register bits are designated as "reserved." The CPU must write a zero to each of these bit locations when it writes to the register. Read operations from reserved bit locations return undefined values.

# 6.1 GENERAL-PURPOSE REGISTERS

There are 16 general-purpose registers, designated R0 through R13, RA, and SP. Registers R0 through R13 can be used for any purpose such as holding variables, addresses, or index values. The RA register is usually used to store the return address upon entry into a subroutine. The SP register is usually used as the pointer to the program run-time stack.

If a general-purpose register is used for a byte-wide operation, only the low-order byte is referenced or modified. The high-order byte is not used or affected by a byte-wide operation.

# 6.2 DEDICATED ADDRESS REGISTERS

There are three dedicated address registers: the Program Counter (PC), the Interrupt Stack Pointer (ISP), and the Interrupt Base Register (INTBASE). Each of these registers is 21 bits wide.

# 6.2.1 Program Counter

The PC register contains the address of the first byte of the instruction currently being executed. It is automatically incremented or changed by the appropriate amount each time an instruction is executed.

The five most significant and the least significant bit of this register are always zero. The least significant bit of the PC is always zero, thus instruction must always be aligned to even addresses in the range of 0000 to FFFE hex.

Upon reset, the PC register is initialized to zero and program execution starts at that address. When a reset signal is received, bits 1 through 16 of the PC register (prior to initialization) are stored in register R0. This allows the software to determine the point in the program at which the reset occurred.

# 6.2.2 Interrupt Stack Pointer

The ISP register points to the lowest address of the last item stored on the interrupt stack. This stack is used by the hardware when an interrupt or trap service procedure is invoked.

The five most significant bits and the least significant bit of this register are always zero. The last item stored on the interrupt stack must be at an even address in the range of E000-E7FF hex, which is the range of the RAM memory in which the stack resides.

# 6.2.3 Interrupt Base Register

The INTBASE register holds the address of the Dispatch Table for interrupts and traps. The five most significant bits and the least significant bit of this register are always zero.

# 6.3 PROCESSOR STATUS REGISTER

The Processor Status Register (PSR) holds status information and selects the operating modes for the CPU core. The format of the register is shown below.

| 1 | 15 | 14   | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----|------|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

|   | F  | Rese | erve | d  | -  | Ρ  | Е | 0 | Ν | Ζ | F | 0 | 0 | L | Т | С |

| C bit | The Carry (C) bit indicates whether a carry or<br>borrow has occurred after addition or subtrac-<br>tion. It is set to 1 if a carry or borrow has oc-<br>curred, or cleared to 0 otherwise.                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T bit | The Trace (T) bit, when set, causes a Trace (TRC) trap to be executed after every instruction. This bit is automatically cleared to 0 when                                                                                                                     |

| L bit | a trap or interrupt occurs.<br>The Low (L) bit is set by comparison opera-<br>tions. In a comparison of unsigned integers, the<br>bit is set to 1 if the second operand (Rdest) is<br>less than the first operand (Rsrc). Otherwise, it                        |

| F bit | is cleared to 0.<br>The Flag (F) bit is a general condition flag that<br>is set by various instructions. It may be used to<br>signal exception conditions or to distinguish the                                                                                |

|       | results of an instruction. For example, integer<br>arithmetic instructions use this bit to indicate an<br>overflow condition after an addition or subtrac-<br>tion operation.                                                                                  |

| Z bit | The Zero (Z) bit is set by comparison opera-<br>tions. In a comparison of integers, the bit is set<br>to 1 if the two operands are equal. Otherwise,<br>it is cleared to 0.                                                                                    |

| N bit | The Negative (N) bit is set by comparison oper-<br>ations. In a comparison of signed integers, the<br>bit is set to 1 if the second operand (Rdest) is<br>less than the first operand (Rsrc). Otherwise, it<br>is cleared to 0.                                |

| E bit | The Local Maskable Interrupt Enable (E) bit is<br>used to enable or disable maskable interrupts.<br>If this bit and the Global Maskable Interrupt En-<br>able (I) bit are both set to 1, all maskable inter-<br>rupts are accepted. Otherwise, only non-       |

|       | maskable interrupts are accepted. The E bit is<br>set to 1 by the Enable Interrupts (EI) instruction<br>and cleared to 0 by the Disable Interrupts (DI)<br>instruction.                                                                                        |

| P bit | The Trace Trap Pending (P) bit is used together<br>with the Trace (T) bit to prevent a Trace (TRC)<br>trap from occurring more than once for any in-<br>struction. The P bit may be cleared to 0 (no<br>TRC trap pending) or set to 1 (TRC trap pend-<br>ing). |

I bit The Global Maskable Interrupt Enable (I) bit is used to enable or disable maskable interrupts. If this bit and the Local Maskable Interrupt Enable (E) bit are both set to 1, all maskable interrupts are accepted. Otherwise, only the nonmaskable interrupts are accepted. This bit is automatically cleared to 0 when an interrupt occurs and automatically set to 1 upon completion of an interrupt service routine.

Upon reset, all non-reserved bits of the register are cleared to 0 except for the E bit (bit 9), which is set to 1. When a device reset occurs, the PSR contents prior to the reset are stored into register R1, allowing the initialization software to determine the state of the device prior to the reset operation.

# 6.4 CONFIGURATION REGISTER

The Configuration (CFG) register is a 16-bit core register that determines the size of the INTBASE register. For the device, the CFG register should always be left in its default state (cleared to zero), resulting in a 16-bit INTBASE register.

# 6.5 ADDRESSING MODES

Each instruction operates on one or more operands. An operand can be a register or a memory location.

Most instructions use one, two, or three device registers as operands. The instruction opcode specifies the registers to be operated on. Some instructions may use an immediate value (a value provided in the instruction itself) instead of a register.

Memory locations are accessed only by the Load and Store commands. The memory location to use for a particular instruction can be specified as an absolute, relative, or far-relative address.

The instruction set supports the following addressing modes:

| Register Mode     | The operand is a general-purpose regis-<br>ter: R0 through R13, RA, or SP. For exam-<br>ple:<br>ADDB R1, R2                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Immediate<br>Mode | A constant operand value is specified with-<br>in the instruction. In a branch instruction,<br>the immediate operand is a displacement<br>from the program counter (PC). In the as-<br>sembly language syntax, a dollar sign indi-<br>cates an immediate value. For example:<br>MULW \$4, R4 |

| Relative Mode     | The operand is located in memory. Its ad-<br>dress is obtained by adding the contents of<br>a general purpose register to the constant<br>value encoded into the displacement field<br>of the instruction. For example:<br>LOADW 12(R5), R6                                                  |

| Far-Relative<br>Mode | The operand is located in memory. Its ad-<br>dress is obtained by concatenating a pair<br>of adjacent general-purpose registers to<br>form a 21-bit value, and adding this value<br>to the constant value encoded into the dis-<br>placement field of the instruction. The de-<br>vice implementation only uses the first 64K<br>of the address space, so the relative mode<br>is sufficient to access the entire usable ad-<br>dress opened the for relative mode in pet |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | dress space; the far-relative mode is not used.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Absolute Mode        | The operand is located in memory Its ad-                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Absolute Mode The operand is located in memory. Its address is specified within the instruction. For example:

LOADB 4000, R6

For additional information on the instruction set and instruction encoding, see the CompactRISC CR16B Programmer's Reference manual.

# 6.6 STACKS

A stack is a one-dimensional data buffer in which values are entered and removed one at a time. The last value entered is the first one removed. A register called the stack pointer contains the current address of the last item entered on the stack. In the device, when an item is entered or "pushed" onto the stack, the stack expands downward in memory (the stack pointer is decremented). When an item is removed or "popped" from the stack, the stack shrinks upward in memory (the stack pointer is incremented).

The device uses two type of stacks: the program stack and the interrupt stack.

The program stack is used by the software to save and restore register values upon entry into and exit from a subroutine. The software can also use the program stack to store local and temporary variables. The stack pointer for this stack is the SP register.

The interrupt stack is used to save and restore the program state when an exception occurs (an interrupt or software trap). The on-chip hardware automatically pushes the program state information onto the stack before the exception service procedure is executed. Upon exit from the exception service procedure, the hardware pops this information from the stack and restores the program state. The stack pointer for this stack is the ISP, or Interrupt Stack Pointer.

# 6.7 INSTRUCTION SET

Table7 is a summary list of all instructions in the device instruction set. For each instruction, the table shows the mnemonic with a brief description of the operation performed.

In the Mnemonic column, the lower-case letter "i" is used to indicate the type of integer that the instruction operates on, either "B" for byte or "W" for word. For example, the notation ADDi for the "add" instruction means that there are two forms of this instruction, ADDB and ADDW, which operate on bytes and words, respectively.

Similarly, the lower-case string "cond" is used to indicate the type of condition tested by the instruction. For example, the notation Jcond represents a class of conditional jump instruc-

tions: JEQ for Jump on Equal, JNE for Jump on Not Equal, and so on.

For detailed information on all instructions, see the CompactRISC CR16B Programmer's Reference manual.

#### Table 7 Device Instruction Set Summary

| Mnemonic | Description                              |

|----------|------------------------------------------|

| ADDi     | Add Integer                              |

| ADDUi    | Add Unsigned Integer                     |

| ADDCi    | Add Integer with Carry                   |

| ANDi     | Bitwise Logical AND                      |

| ASHUi    | Arithmetic Shift Unsigned                |

| Bcond    | Conditional Branch                       |

| Bcond0i  | Compare Register to 0 and Branch         |

| Bcond1i  | Compare Register to 1and Branch          |

| BAL      | Branch and Link                          |

| BR       | Unconditional Branch                     |

| CBITi    | Clear Bit in Integer                     |

| CMPi     | Compare Integer                          |

| DI       | Disable Maskable Interrupts              |

| EI       | Enable Maskable Interrupts               |

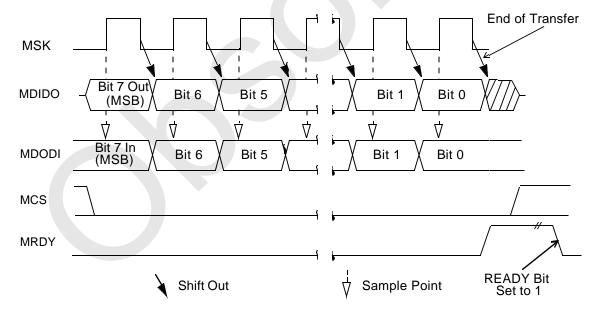

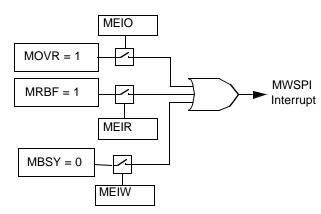

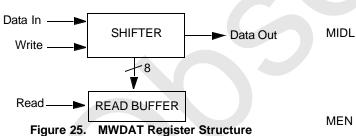

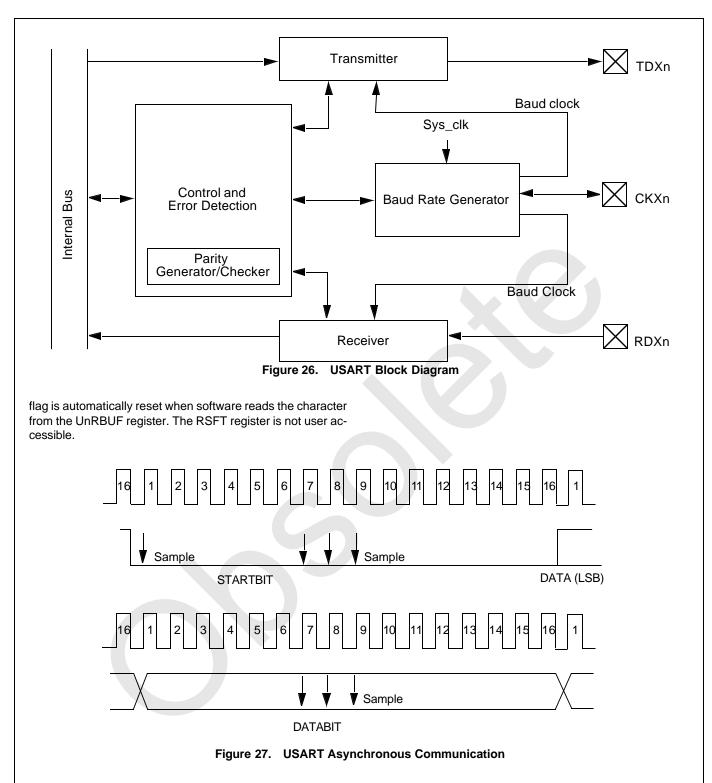

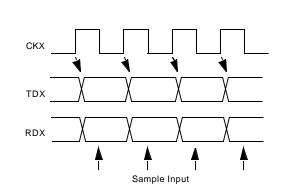

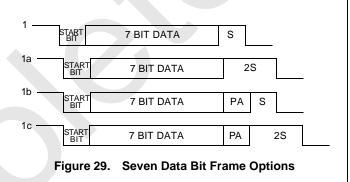

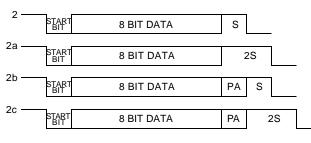

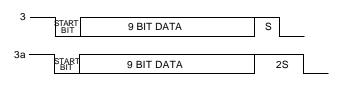

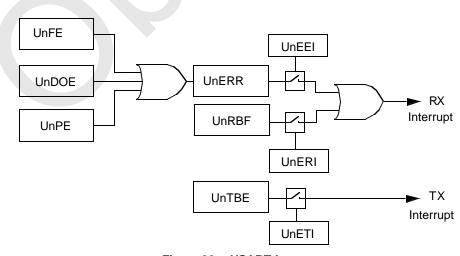

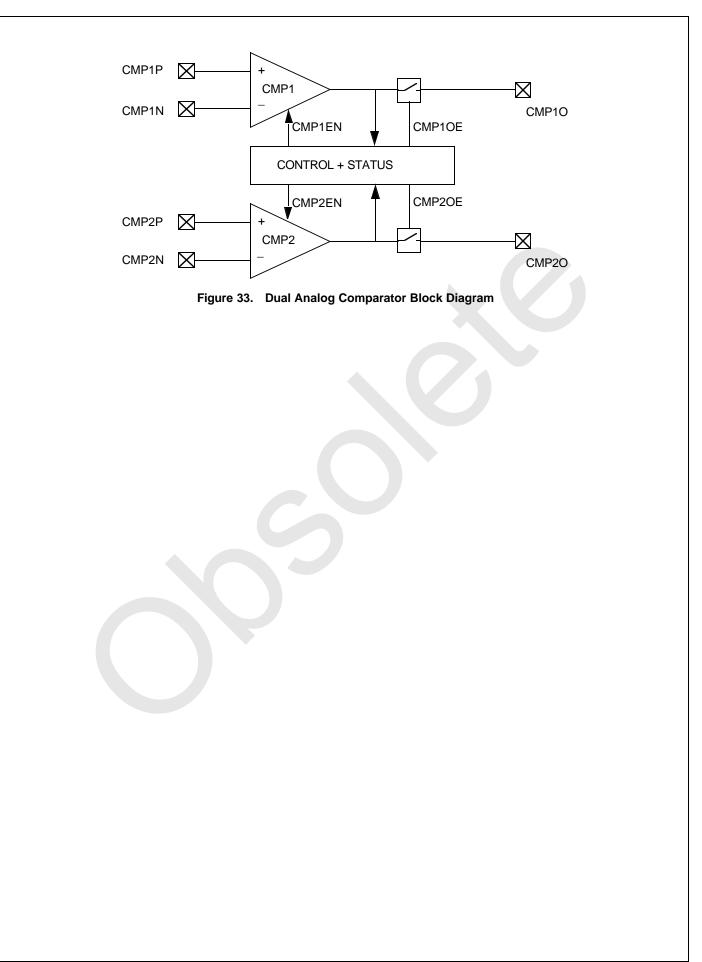

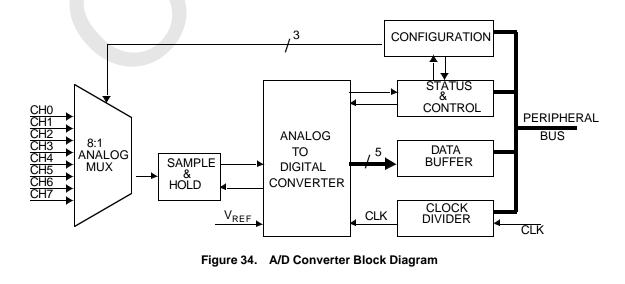

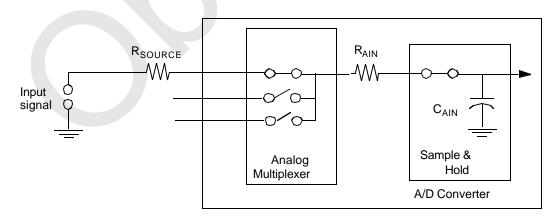

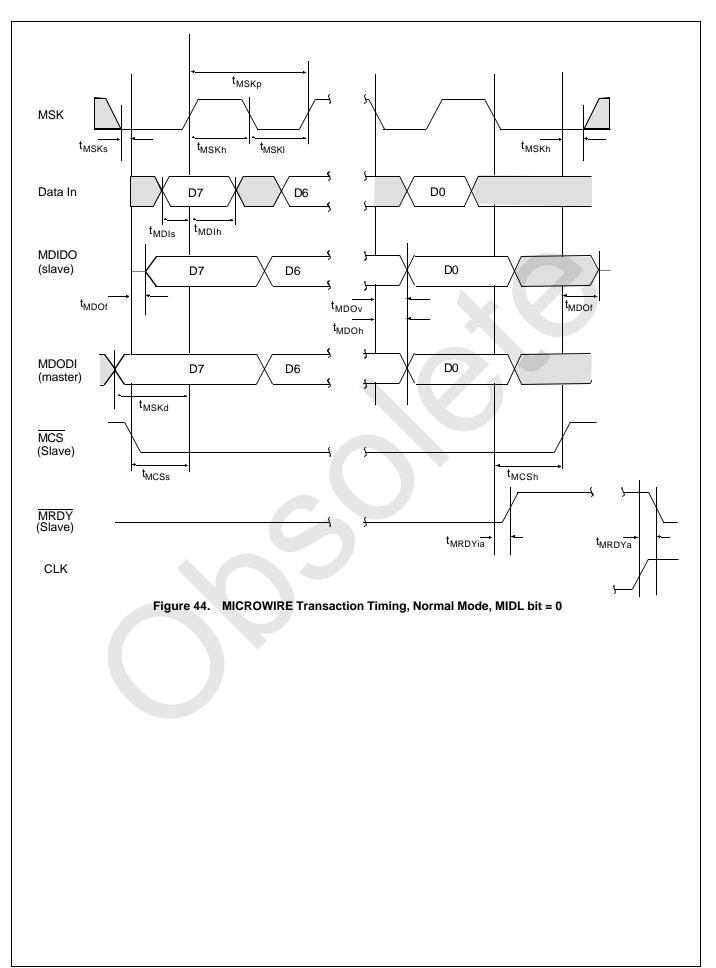

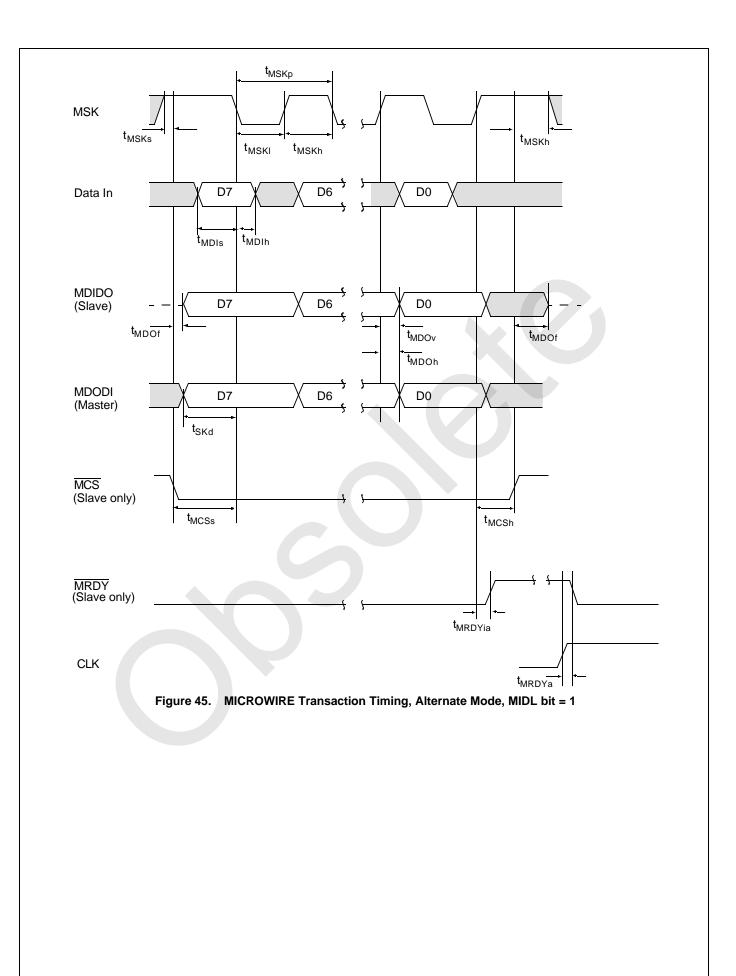

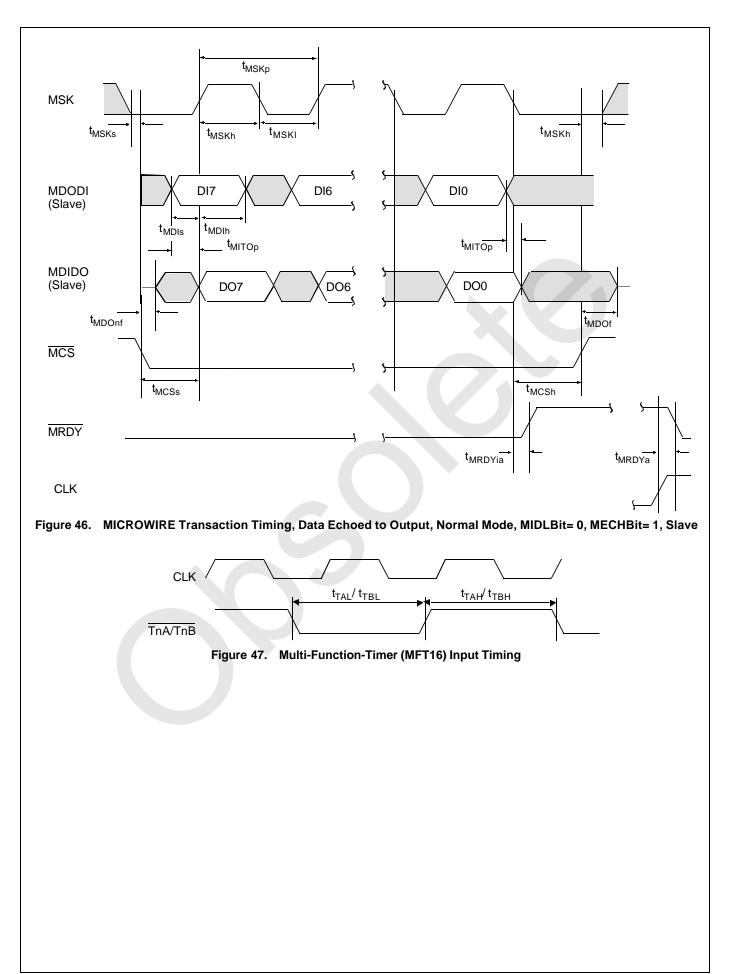

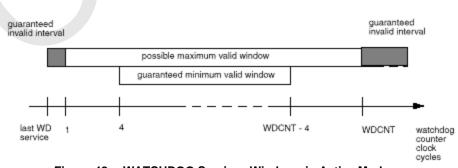

| EIWAIT   | Enable Interrupts and Wait for Interrupt |