- Highly Integrated Single-Chip Shared-Memory Switch

- Provides Eight 10-Mbit/s Ethernet Ports and Two 10-/100-Mbit/s Ethernet Ports

- Collision-Based Flow Control

- Supports Cut-Through and Store-and-Forward Modes of Switching Operation

- All Ports Are Full-Duplex Capable

- 10-/100-Mbit/s Port Capable of Bidirectional Tagging

- Supports On-Chip Per-Port Storage for Etherstat™ and Remote Monitoring (RMON) for Simple-Network Management Protocol (SNMP)

- Provides Direct Connection to Industry-Standard PHY Components:

- 10-Mbit/s Ports Serial Network Interface (SNI)

- 10-/100-Mbit/s Ports SNI for 10-Mbit/s and Media-Independent Interface (MII) for 100-Mbit/s

- Supports Multiple Media-Access Controller (MAC) Address Switching Modes

- Virtual-LAN (VLAN) Capable

- EEPROM Interface for Auto-Configuration, No CPU Needed, Enabling Lowest-Cost Switching Solution

- Provides External Address Match (EAM) Interface

- Packet Memory Utilizes Cost-Effective 60-ns Extended Data Out (EDO) DRAM

- Provides Direct Input/Output (DIO) Interface for Configuration and Statistics Information

- Provides Transmit Pacing

- LED Interface for Link Activity,

Flow-Control Indication, and Port Status

- Fabricated in 3.3-V Low-Voltage Technology

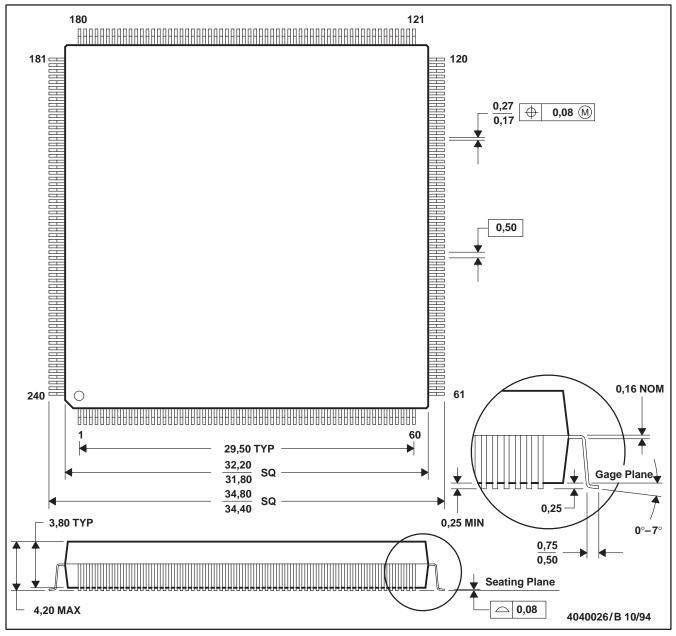

- Packaged in 240-Pin Plastic Quad Flatpack

- 5-V Tolerant I/Os

- JTAG Compliant

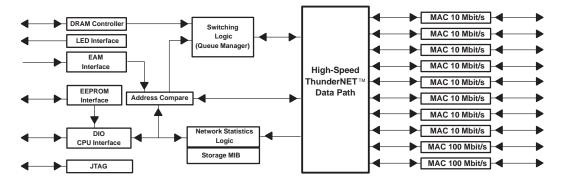

#### description

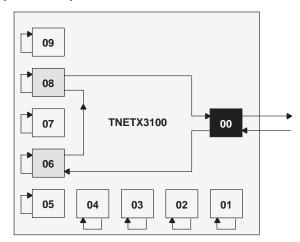

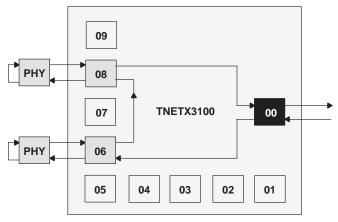

The ThunderSWITCH TNETX3100 is a 10-port 10-/100-Mbit/s Ethernet switch. A low-cost solution is achieved by combining the TNETX3100 with physical interfaces and low-cost packet memory. The TNETX3100 provides 32 internal media access controller (MAC) address registers, collision-based flow control, virtual LAN (VLAN) support, and uplink support.

#### functional block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ThunderSWITCH, ThunderNET, and ThunderPHY are trademarks of Texas Instruments Incorporated. Ethernet and Etherstat are trademarks of Xerox Corporation

# TNETX3100 ThunderSWITCH™ 10-PORT 10-/100-MBIT/S ETHERNET™ SWITCH

SPWS031D - JUNE 1997 - REVISED OCTOBER 1997

#### description (continued)

The TNETX3100 provides two 100-Mbit/s interfaces and eight 10-Mbit/s interfaces. Half-duplex ports support collision-based flow control; the purpose of the flow control is to reduce the risk of data loss for a long burst of activity. With full-duplex capability, ports 02–09 can support 20-Mbit/s connections and ports 00–01 can support 200-Mbit/s connections to desktops or high-speed servers. The uplink (port 00) also can interface to an external routing engine. Besides the ten full-duplex ports, the TNETX3100 has three modes for making forwarding decisions.

The desktop switch internally supports multiple MAC addresses per port (32 total addresses). If more than 32 addresses are required, an external address match (EAM) interface is supplied to support multiple addresses per port. If an external routing engine is used, the uplink port supports frame tagging. The frame tagging provides source port information to an external routing engine. For more flexibility, the TNETX3100 can support VLAN for workgroup and segment-switching applications.

VLAN support is provided in two ways: 1) In the internal address mode, internal VLAN registers are used to configure the destination ports for broadcast/multicast packets. 2) The EAM interface provides a hardware mechanism to control broadcast/multicast packets based on the code provided on that interface. See *EAM interface* and *VLAN support* for more details.

Statistics for the Etherstat and remote monitoring (RMON) management information base are independently collected for each of the ten ports. Access to the statistics counters is provided via the data input/output (DIO) interface. The DIO interface is intended only for configuration and monitoring operations.

The TNETX3100 utilizes an extremely low-cost 60-ns memory solution extended data out (EDO) DRAM. The packet memory has been implemented to effectively support both single-access operation and page-burst-access operation. All DRAM buffer transfers are made within a page boundary, permitting fast-burst accesses. A high-memory bandwidth is maintained, allowing all ports to be active without bottlenecking at the memory buffer.

The TNETX3100 is fabricated with 3.3-V technology. The inputs are 5-V tolerant and the 3.3-V outputs can directly interface to 5-V TTL-logic levels. This provides a broad choice of interfacing-device options.

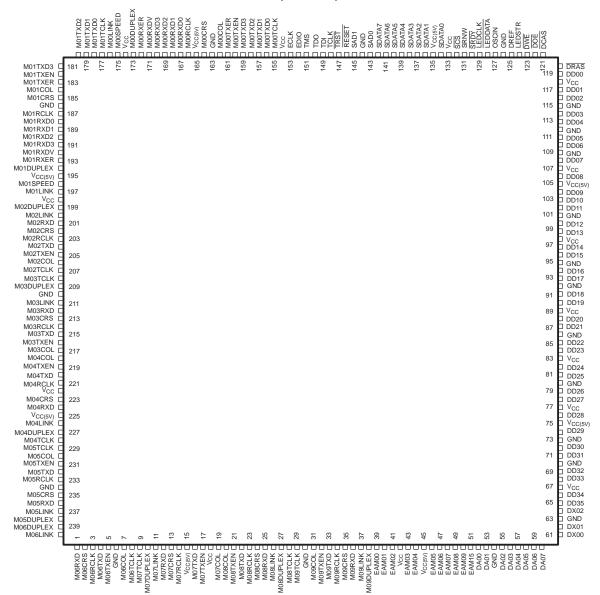

## PGC PACKAGE (TOP VIEW)

## TNETX3100 ThunderSWITCH<sup>™</sup> 10-PORT 10-/100-MBIT/S ETHERNET<sup>™</sup> SWITCH

SPWS031D – JUNE 1997 – REVISED OCTOBER 1997

| Table of                                    | Contents                                              |

|---------------------------------------------|-------------------------------------------------------|

| Terminal Functions                          | DIO Interface (Continued)                             |

| 10-/100-Mbit/s MAC Interface                | DIATST Register                                       |

| DRAM Interface                              | PACTST Register                                       |

| EAM Interface                               | Address Registers                                     |

| DIO and Statistics Interface                | Address Register Description                          |

| EEPROM Interface                            | Port-N Statistics                                     |

| LED Activity Interface                      | Port-N RX Overruns and Collisions                     |

| JTAG Interface                              | DIO Access to Counter Statistics                      |

| Miscellaneous Functions                     | Clearing Statistics Counter Memory                    |

| Power Interface                             | Queue Structures Address Map                          |

| Summary of Signal Terminals by              | EEPROM Interface                                      |

| Signal Group Function                       | EEPROM Auto-Configuration From an                     |

| 10-/100-Mbit/s MAC Interfaces (Ports 00–09) | External x24C02 EEPROM                                |

| Data Reception                              | LED Interface                                         |

| Receive Arbitration                         | LED Functions in Shift-Register Order                 |

| Receive Control                             | Lamp Test                                             |

| TNETX3100 MXXDUPLEX Terminals               | JTAG Interface                                        |

| Flow Control                                | External Pullup Resistors                             |

| Giant (Long) Frames                         | Supported JTAG Instructions                           |

| Short Frames                                | Manufacturing Test Features                           |

| RX Filtering of No-Cut-Through Frames       | Primary Test Access: DIO Testing                      |

| Data Transmission                           | Secondary Test Access                                 |

| Transmit Control                            | FIFO RAM Test Access                                  |

| Transmit Pacing                             | Structure (Statistics) RAM Test Access                |

| Interframe Gap Enforcement                  | Internal Frame-Wrap Test Mode                         |

| Backoff                                     | External Frame-Wrap Test Mode                         |

| 100-Mbit/s MAC Interfaces (Port 00)         | Internal and External Frame-Wrap Example 50           |

| Uplink TX Pretagging                        | Tertiary Test Access                                  |

| Uplink RX Pretagging                        | External DRAM Test Access51                           |

| Using TX Pretagging and RX Posttagging      | Glossary 52                                           |

| Uplink RX Posttagging17                     | Absolute Maximum Ratings                              |

| Uplink Frame RX Routing Via Posttagging     | Recommended Operating Conditions 57                   |

| 100-Mbit/s MAC Interfaces (Port 01)         | Electrical Characteristics                            |

| DRAM and EAM Interfaces                     | Parameter Measurement Information                     |

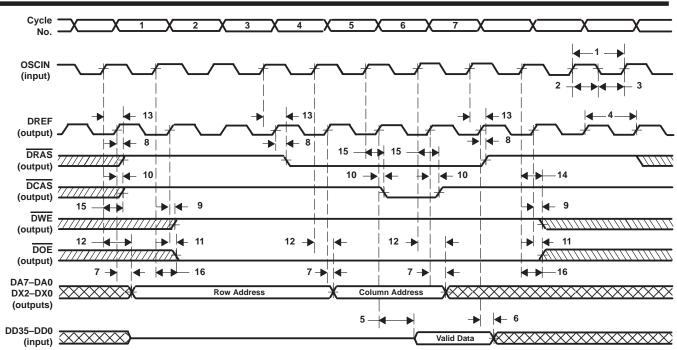

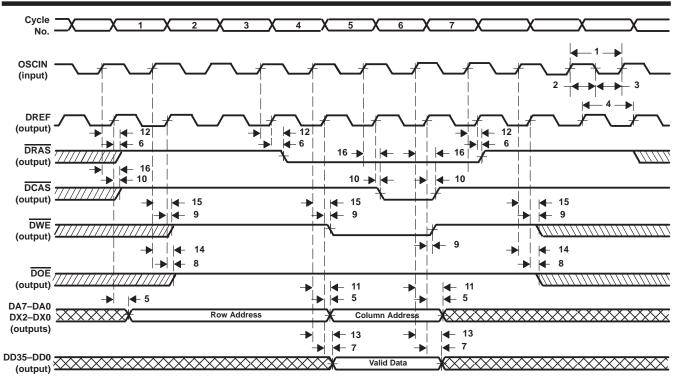

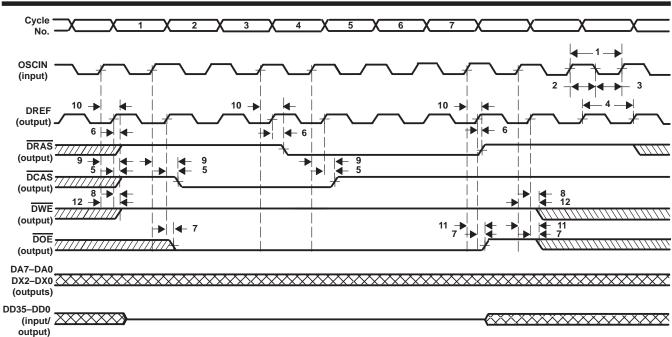

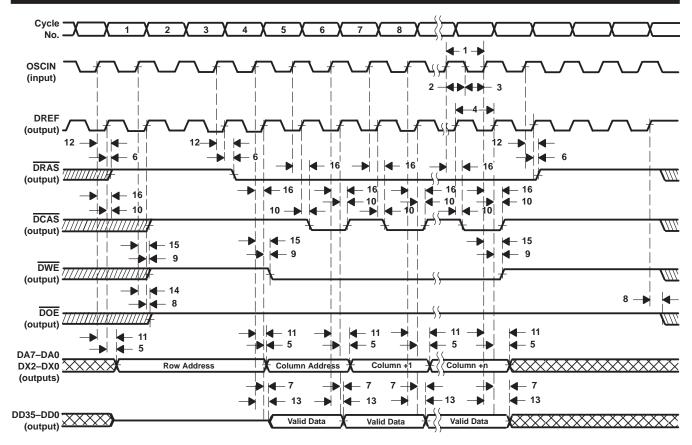

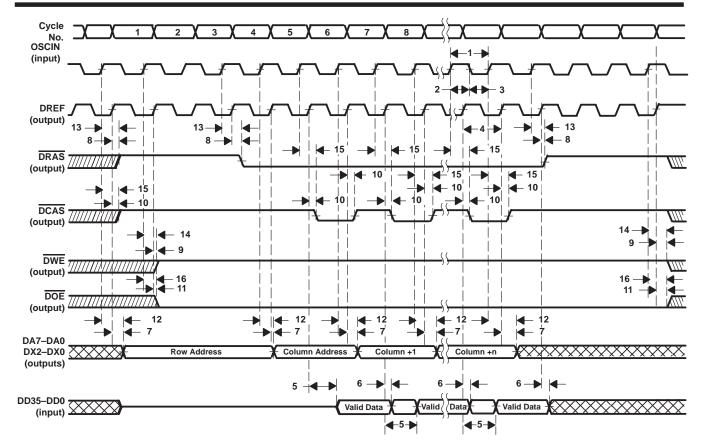

| Flag Byte                                   | Timing Requirements – DRAM Read Cycle59               |

| Unmatched Frames                            | Operating Characteristics – DRAM Read Cycle 59        |

| VLAN Support                                | Timing Requirements – DRAM Write Cycle                |

| DIO Interface                               | Operating Characteristics – DRAM Write Cycle 61       |

| Remote Hardware Reset24                     | Timing Requirements – DRAM CAS Before RAS 63          |

| TNETX3100 Condensed DIO Memory Map24        | Operating Characteristics – DRAM CAS Before RAS 63    |

| Address Registers                           | Timing Requirements – DRAM Burst Write Cycle 65       |

| Address Register Description                | Operating Characteristics – DRAM Burst Write Cycle 65 |

| Secured Address                             | Timing Requirements – DRAM Burst Read Cycle 67        |

| DIO Access to Address Registers             | Operating Characteristics – DRAM Burst Read Cycle 67  |

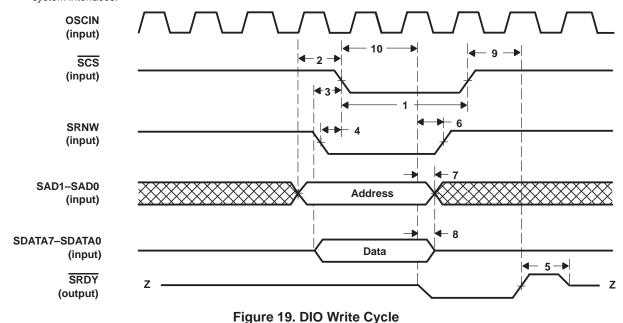

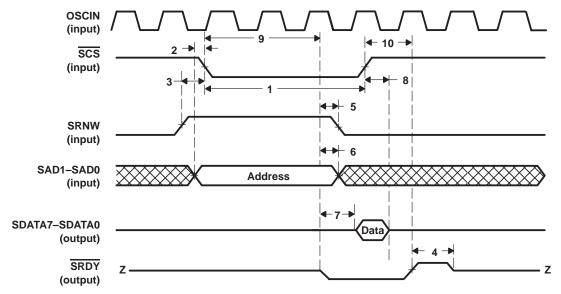

| Port-N Control Register                     | DIO Write Cycle                                       |

| Port-N Status Register                      | Timing Requirements                                   |

| Revision Register                           | Operating Characteristics                             |

| SIO/XCTRL Register                          | DIO Read Cycle70                                      |

| Device Code Register                        | Timing Requirements                                   |

| Transmit Queue-Length Registers             | Operating Characteristics                             |

| Port VLAN Registers                         | Timing Requirements – EAM Interface                   |

| Free Queue-Length Register                  | LED Interface Timing                                  |

| Feature-Configuration Register              | Operating Characteristics – EEPROM Interface          |

| LED Control Register                        | Timing Requirements – MII Receive 100 Mbit/s          |

| RAM Size Register                           | Timing Requirements – MII Receive 10 Mbit/s           |

| System Control Register                     | Operating Characteristics – MII Transmit 10 Mbit/s    |

| DRAM Data Register                          | Timing Requirements – Power-On Reset                  |

| DRAM Flag Register                          | Timing Requirements – RESET Timing                    |

| DRAM Address Register                       | Mechanical Data                                       |

| DRAM Test-Access Operation                  |                                                       |

#### **Terminal Functions**

## 10-Mbit/s MAC interface (ports 02-09)

| TERMINA   | AL  |     | D FOODINTION.                                                                                                                                                                     |

|-----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | I/O | DESCRIPTION                                                                                                                                                                       |

| M02COL    | 206 |     |                                                                                                                                                                                   |

| M03COL    | 217 |     |                                                                                                                                                                                   |

| M04COL    | 218 |     |                                                                                                                                                                                   |

| M05COL    | 230 | ١,  | Callisian again. High maturate callisian and law, no naturate callisian                                                                                                           |

| M06COL    | 7   | 1   | Collision sense. High = network collision and low = no network collision.                                                                                                         |

| M07COL    | 19  |     |                                                                                                                                                                                   |

| M08COL    | 20  |     |                                                                                                                                                                                   |

| M09COL    | 31  |     |                                                                                                                                                                                   |

| M02CRS    | 202 |     |                                                                                                                                                                                   |

| M03CRS    | 213 |     |                                                                                                                                                                                   |

| M04CRS    | 223 |     |                                                                                                                                                                                   |

| M05CRS    | 235 | ١.  | Carrier sense. High = frame carrier signal is received and low = no frame carrier signal is received.                                                                             |

| M06CRS    | 2   | ł   |                                                                                                                                                                                   |

| M07CRS    | 13  |     |                                                                                                                                                                                   |

| M08CRS    | 24  |     |                                                                                                                                                                                   |

| M09CRS    | 35  |     |                                                                                                                                                                                   |

| M02DUPLEX | 199 |     |                                                                                                                                                                                   |

| M03DUPLEX | 209 |     |                                                                                                                                                                                   |

| M04DUPLEX | 227 |     |                                                                                                                                                                                   |

| M05DUPLEX | 238 | 1/0 | Duplex selector. MXXDUPLEX switches the interface between full- and half-duplex operation (low= half duplex, high = full duplex). M02DUPLEX-M09DUPLEX inputs have active pulldown |

| M06DUPLEX | 239 | 1/0 | circuits used to force the inputs low when FORCEHD bit is set.                                                                                                                    |

| M07DUPLEX | 10  |     |                                                                                                                                                                                   |

| M08DUPLEX | 27  |     |                                                                                                                                                                                   |

| M09DUPLEX | 38  |     |                                                                                                                                                                                   |

| M02LINK   | 200 |     |                                                                                                                                                                                   |

| M03LINK   | 211 |     |                                                                                                                                                                                   |

| M04LINK   | 226 |     |                                                                                                                                                                                   |

| M05LINK   | 237 | ,   | Link selector. MXXLINK indicates the condition of the port connection (low = no link, high = link).                                                                               |

| M06LINK   | 240 | '   | = milky might = milky.                                                                                                                                                            |

| M07LINK   | 11  |     |                                                                                                                                                                                   |

| M08LINK   | 26  |     |                                                                                                                                                                                   |

| M09LINK   | 37  |     |                                                                                                                                                                                   |

## 10-Mbit/s MAC interface (ports 02-09) (continued)

| TERMINA | L   | I/O DESCRIPTION |                                                                                                     |

|---------|-----|-----------------|-----------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0             | DESCRIPTION                                                                                         |

| M02RCLK | 203 |                 |                                                                                                     |

| M03RCLK | 214 |                 |                                                                                                     |

| M04RCLK | 221 |                 |                                                                                                     |

| M05RCLK | 233 | ,               | Descrive clock MVVPCLK is the receive clock from the ottophed DLIV                                  |

| M06RCLK | 3   | '               | Receive clock. MXXRCLK is the receive clock from the attached PHY.                                  |

| M07RCLK | 14  |                 |                                                                                                     |

| M08RCLK | 23  |                 |                                                                                                     |

| M09RCLK | 34  |                 |                                                                                                     |

| M02RXD  | 201 |                 |                                                                                                     |

| M03RXD  | 212 |                 |                                                                                                     |

| M04RXD  | 224 |                 |                                                                                                     |

| M05RXD  | 236 | ١. ا            | Receive data. MXXRXD is the receive data from the PMD front end. Data is synchronous to             |

| M06RXD  | 1   | '               | MXXRCLK.                                                                                            |

| M07RXD  | 12  |                 |                                                                                                     |

| M08RXD  | 25  |                 |                                                                                                     |

| M09RXD  | 36  |                 |                                                                                                     |

| M02TCLK | 207 |                 |                                                                                                     |

| M03TCLK | 208 |                 |                                                                                                     |

| M04TCLK | 228 |                 |                                                                                                     |

| M05TCLK | 229 |                 | Transmit clock. MXXTCLK is the transmit clock from the attached PHY.                                |

| M06TCLK | 8   |                 |                                                                                                     |

| M07TCLK | 9   |                 |                                                                                                     |

| M08TCLK | 28  |                 |                                                                                                     |

| M09TCLK | 29  |                 |                                                                                                     |

| M02TXD  | 204 |                 |                                                                                                     |

| M03TXD  | 215 |                 |                                                                                                     |

| M04TXD  | 220 |                 |                                                                                                     |

| M05TXD  | 232 | 0               | Transmit data MVVTVD is the transmit data lequing part by when MVVTVDN is asserted                  |

| M06TXD  | 4   |                 | Transmit data. MXXTXD is the transmit data leaving port xx when MXXTXEN is asserted.                |

| M07TXD  | 16  |                 |                                                                                                     |

| M08TXD  | 22  |                 |                                                                                                     |

| M09TXD  | 33  |                 |                                                                                                     |

| M02TXEN | 205 |                 |                                                                                                     |

| M03TXEN | 216 |                 |                                                                                                     |

| M04TXEN | 219 |                 |                                                                                                     |

| M05TXEN | 231 | 0               | Transmit enable. High = valid transmit data on MXXTXD and low = no valid transmit data on MXXTXD.   |

| M06TXEN | 5   |                 | Transmit Gnable. High = valid transmit data on MAATAD and low = 110 valid transmit data 011 MAATAD. |

| M07TXEN | 17  |                 |                                                                                                     |

| M08TXEN | 21  |                 |                                                                                                     |

| M09TXEN | 32  |                 |                                                                                                     |

## 10-/100-Mbit/s MAC interface (ports 00-01)

| TERMINA   | TERMINAL |          | DESCRIPTION                                                                                                                                                                      |

|-----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.      | I/O      | DESCRIFTION                                                                                                                                                                      |

| M00COL    | 162      | ١,       | Collision sense. High = network collision and low = no network collision.                                                                                                        |

| M01COL    | 184      | <u>'</u> | Collision serise. High = network collision and low = no network collision.                                                                                                       |

| M00CRS    | 164      | ١,       | Carrier sense. High = frame carrier signal is received and low = no frame carrier signal is received.                                                                            |

| M01CRS    | 185      |          | Carrier sense. Fight = frame carrier signal is received and low = no frame carrier signal is received.                                                                           |

| M00DUPLEX | 173      |          | Duplex selector. MXXDUPLEX switches the interface between full- and half-duplex operation                                                                                        |

| M01DUPLEX | 194      | I/O      | (low = half duplex, high = full duplex). The M00DUPLEX and M01DUPLEX inputs have active pulldown circuits used to force the inputs low when FORCEHD bit is set.                  |

| M00LINK   | 176      | ١,       | Link selector. MXXLINK indicates the condition of the port connection ( low = no link, high = link).                                                                             |

| M01LINK   | 197      | <u>'</u> | Link selector. MAALINK indicates the condition of the port connection (low = no link, high = link).                                                                              |

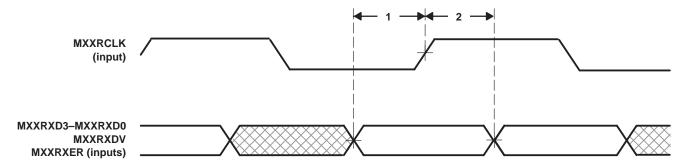

| M00RCLK   | 166      |          | Receive clock, MXXRCLK source is from the external PHY.                                                                                                                          |

| M01RCLK   | 187      | '        | Receive clock. MAARCLA source is from the external PHY.                                                                                                                          |

| M00RXDV   | 171      |          | Descript data valid MAVADADA indicates data on MAVADADA MAVADADA is valid                                                                                                        |

| M01RXDV   | 192      | _ '      | Receive data valid. MXXRXDV indicates data on MXXRXD3–MXXRXD0 is valid.                                                                                                          |

| M00RXER   | 172      |          | Description are MANAPATED indicates asserting of a sedimar area as assisted data                                                                                                 |

| M01RXER   | 193      | _ '      | Receive error. MXXRXER indicates reception of a coding error on received data.                                                                                                   |

| M00RXD0   | 167      |          |                                                                                                                                                                                  |

| M01RXD0   | 188      |          |                                                                                                                                                                                  |

| M00RXD1   | 168      |          |                                                                                                                                                                                  |

| M01RXD1   | 189      | ١,       | Receive data. Nibble receive data MXXRXD3-MXXRXD0 is from the physical media-dependent front end. Data is synchronous to MXXRCLK. If MWIDTH bit in the port control register and |

| M00RXD2   | 169      | '        | M00SPEED terminal are set low, then data is received on M00RXD0 and M01RXD0 terminals.                                                                                           |

| M01RXD2   | 190      |          |                                                                                                                                                                                  |

| M00RXD3   | 170      |          |                                                                                                                                                                                  |

| M01RXD3   | 191      |          |                                                                                                                                                                                  |

| M00SPEED  | 175      |          | Bit-rate selection speed. The speed of the MAC interface is determined by the logic level on                                                                                     |

| M01SPEED  | 196      | <u> </u> | MXXSPEED (low = 10 Mbit/s, high = 100 Mbit/s).                                                                                                                                   |

| M00TCLK   | 155      |          | Transmit clock. Transmit clock source is from the external PHY.                                                                                                                  |

| M01TCLK   | 177      | _ '      | Transmit Clock. Transmit Clock Source is from the external Phy.                                                                                                                  |

## 10-/100-Mbit/s MAC interface (ports 00-01) (continued)

| TERMINA | \L  | 1/0 | DESCRIPTION                                                                                                                                                                            |

|---------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0 | DESCRIPTION                                                                                                                                                                            |

| M00TXD0 | 156 |     |                                                                                                                                                                                        |

| M01TXD0 | 178 |     |                                                                                                                                                                                        |

| M00TXD1 | 157 |     | Transmit data, Nijhbla transmit data is from the TNETV2100, When MVVTVEN is apported these                                                                                             |

| M01TXD1 | 179 | 0   | Transmit data. Nibble transmit data is from the TNETX3100. When MXXTXEN is asserted, these terminals carry transmit data. Data on these terminals is always synchronous to MXXTCLK. If |

| M00TXD2 | 158 |     | MWIDTH bit in the port control register and M00SPEED terminal are set low, then data is transmitted                                                                                    |

| M01TXD2 | 180 |     | on M00TXD0 and M01TXD0.                                                                                                                                                                |

| M00TXD3 | 159 |     |                                                                                                                                                                                        |

| M01TXD3 | 181 |     |                                                                                                                                                                                        |

| M00TXEN | 160 | 0   | Transmit enable. High = valid transmit data on MXXTXD and low = no valid transmit data on                                                                                              |

| M01TXEN | 182 |     | MXXTXD.                                                                                                                                                                                |

| M00TXER | 161 |     | Transmit error. MXXTXER allows coding errors to propagate across the MII. This enables external                                                                                        |

| M01TXER | 183 | 0   | logic to reconstruct and resend the frame. MXXTXER is asserted during an underrunning frame, enabling the TNETX3100 to force a coding error.                                           |

#### **DRAM** interface

| TERMI | NAL | 1/0 | DESCRIPTION                                                                                      |

|-------|-----|-----|--------------------------------------------------------------------------------------------------|

| NAMET | NO. | 1/0 | DESCRIPTION                                                                                      |

| DA00  | 52  |     |                                                                                                  |

| DA01  | 53  |     |                                                                                                  |

| DA02  | 55  |     |                                                                                                  |

| DA03  | 56  | 0   | DDAM address has DAGO DAGO is time multiplead with your and column address attaches              |

| DA04  | 57  |     | DRAM address bus. DA00–DA07 is time multiplexed with row and column address strobes.             |

| DA05  | 58  |     |                                                                                                  |

| DA06  | 59  |     |                                                                                                  |

| DA07  | 60  |     |                                                                                                  |

| DX00  | 61  |     |                                                                                                  |

| DX01  | 62  | 0   | DRAM extended address lines. DX00–DX02 are time multiplexed with row and column address strobes. |

| DX02  | 64  |     |                                                                                                  |

| DCAS  | 121 | 0   | DRAM column address select                                                                       |

| DRAS  | 120 | 0   | DRAM row address select                                                                          |

<sup>†</sup>DD00 is the least-significant bit.

## **DRAM** interface (continued)

| TERMII | NAL |     |                                            |

|--------|-----|-----|--------------------------------------------|

| NAMET  | NO. | 1/0 | DESCRIPTION                                |

| DD35   | 65  |     |                                            |

| DD34   | 66  |     |                                            |

| DD33   | 68  |     |                                            |

| DD32   | 69  |     |                                            |

| DD31   | 71  |     |                                            |

| DD30   | 72  |     |                                            |

| DD29   | 74  |     |                                            |

| DD28   | 76  |     |                                            |

| DD27   | 78  |     |                                            |

| DD26   | 79  |     |                                            |

| DD25   | 81  |     |                                            |

| DD24   | 82  |     |                                            |

| DD23   | 84  |     | DRAM data bus. DD35–DD00 is bidirectional. |

| DD22   | 85  |     |                                            |

| DD21   | 87  |     |                                            |

| DD20   | 88  | I/O |                                            |

| DD19   | 90  |     |                                            |

| DD18   | 91  |     |                                            |

| DD17   | 93  | 1/0 |                                            |

| DD16   | 94  |     |                                            |

| DD15   | 96  |     |                                            |

| DD14   | 97  |     |                                            |

| DD13   | 99  |     |                                            |

| DD12   | 100 |     |                                            |

| DD11   | 102 |     |                                            |

| DD10   | 103 |     |                                            |

| DD09   | 104 |     |                                            |

| DD08   | 106 |     |                                            |

| DD07   | 108 |     |                                            |

| DD06   | 110 |     |                                            |

| DD05   | 111 |     |                                            |

| DD04   | 113 |     |                                            |

| DD03   | 114 |     |                                            |

| DD02   | 116 |     |                                            |

| DD01   | 117 |     |                                            |

| DD00   | 119 |     |                                            |

| DOE    | 122 | 0   | DRAM output enable                         |

| DWE    | 123 | 0   | DRAM write enable                          |

<sup>†</sup> DD00 is the least-significant bit.

## **Terminal Functions (Continued)**

#### **EAM** interface

| TERMIN                 | IAL | 1/0 | DESCRIPTION                                                                                                                                                                   |

|------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                   |

| EAM15<br>(mode select) | 51  | ı   | External address match. When EAM15 is high and EAM04 is low, it indicates that the least-significant nibble EAM03–EAM00 contains a routing code for the single-selected port. |

| EAM00                  | 39  |     |                                                                                                                                                                               |

| EAM01                  | 40  |     |                                                                                                                                                                               |

| EAM02                  | 41  |     |                                                                                                                                                                               |

| EAM03                  | 43  |     | Established the second of Miles FAME is low a bight of FAMO FAMO in the data for the                                                                                          |

| EAM04                  | 44  |     | External address match. When EAM15 is low, a high on EAM00–EAM09 indicates the data frame is transmitted from that single-selected port.                                      |

| EAM05                  | 46  | '   | EAM00 is the least-significant bit and is associated with port 00.                                                                                                            |

| EAM06                  | 47  |     | · · · · · · · · · · · · · · · · · ·                                                                                                                                           |

| EAM07                  | 48  |     |                                                                                                                                                                               |

| EAM08                  | 49  |     |                                                                                                                                                                               |

| EAM09                  | 50  |     |                                                                                                                                                                               |

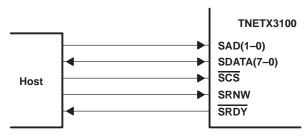

#### DIO and statistics interface

| TERMII | NAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|--------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

| SAD0   | 143 | Ι.  | DIO address SADO SAD1 colocts the TNETV2100 heat registers                                                                                                                                                                                                                                                                                         |

| SAD1   | 145 | '   | DIO address. SAD0–SAD1 selects the TNETX3100 host registers.                                                                                                                                                                                                                                                                                       |

| SCS    | 132 | - 1 | DIO chip select. When low, SCS indicates a port access is valid.                                                                                                                                                                                                                                                                                   |

| SDATA0 | 134 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA1 | 136 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA2 | 137 | 1/0 | DIO data. SDATA0-SDATA7 is bidirectional byte-wide data.                                                                                                                                                                                                                                                                                           |

| SDATA3 | 138 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA4 | 139 | 1/0 |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA5 | 140 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA6 | 141 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SDATA7 | 142 |     |                                                                                                                                                                                                                                                                                                                                                    |

| SRDY   | 130 | 0   | DIO ready. When low, SRDY indicates to the host that data is ready to be read. SRDY also indicates when data has been received for the write cycle. TNETX3100 drives SRDY high for one clock cycle before placing the output in the high-impedance (Z) state after SCS is taken high. SRDY should be pulled high with an external pullup resistor. |

| SRNW   | 131 | I   | DIO read not write. When low, SRNW indicates a write cycle on the DIO port.                                                                                                                                                                                                                                                                        |

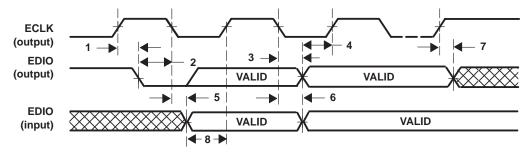

#### **EEPROM** interface

| TERMINA | ۱L  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|---------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. |     | DESCRIFTION                                                                                                                                                                                                                                                                                                                     |

| ECLK    | 153 | 0   | EEPROM data clock. ECLK is the serial EEPROM clock and requires an external pullup resistor.                                                                                                                                                                                                                                    |

| EDIO    | 152 | I/O | EEPROM data input/output. EDIO is the serial EEPROM data I/O signal that requires an external pullup (see EEPROM data sheet) for EEPROM operation. Tying this terminal to ground disables the EEPROM interface and prevents auto-configuration. Reset is asynchronous, therefore, OSCIN needs to operate while RESET is active. |

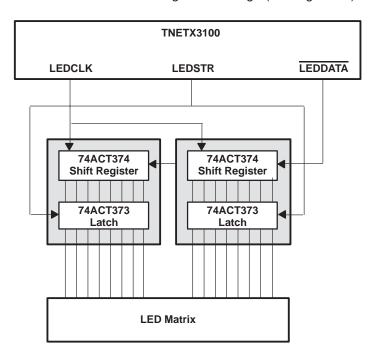

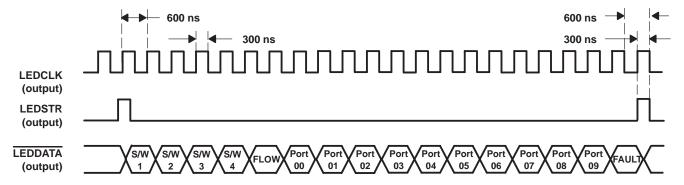

## **LED** activity interface

| TERMINA | \L  | I/O | DESCRIPTION                                                                     |

|---------|-----|-----|---------------------------------------------------------------------------------|

| NAME    | NO. |     | DESCRIPTION                                                                     |

| LEDCLK  | 129 | 0   | LED clock. LEDCLK is the serial-shift clock for the LED-status data.            |

| LEDDATA | 128 | 0   | LED data. LEDDATA is the active-low serial data signal for the LED-status data. |

| LEDSTR  | 124 | 0   | LED strobe. LEDSTR pulses latch the contents of the LED shift registers.        |

#### **JTAG** interface

| TERMINA | \L  | 1/0 | DESCRIPTION                                                                                                             |

|---------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0 | DESCRIPTION                                                                                                             |

| TCLK    | 148 | -   | Test clock. TCLK clocks state information and test data into and out of the device during operation of the test port.   |

| TDI     | 149 | _   | Test data input. TDI serially shifts test data and test instructions into the device during operation of the test port. |

| TDO     | 150 | 0   | Test data out. TDO serially shifts test data and test instructions out of the device during operation of the test port. |

| TMS     | 151 | Ī   | Test mode select. TMS controls the state of the TNETX3100 test-port controller.                                         |

| TRST    | 147 | I   | Test reset. TRST asynchronously resets the test-port controller.                                                        |

#### miscellaneous functions

| TERM  | INAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                    |  |  |  |

|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.  | 1/0 | DESCRIPTION                                                                                                                                                                                                                    |  |  |  |

| DREF  | 125  | 0   | DRAM reference clock.                                                                                                                                                                                                          |  |  |  |

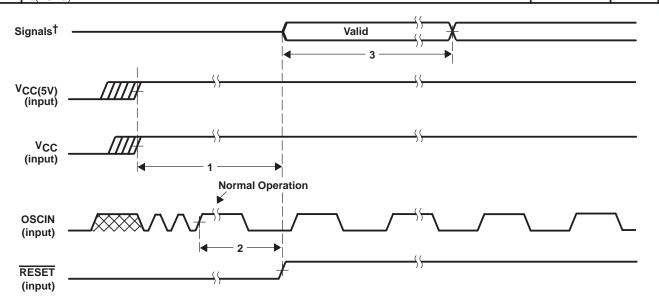

| OSCIN | 127  | -   | Oscillator input. OSCIN is the TNETX3100 clock input (50 MHz).                                                                                                                                                                 |  |  |  |

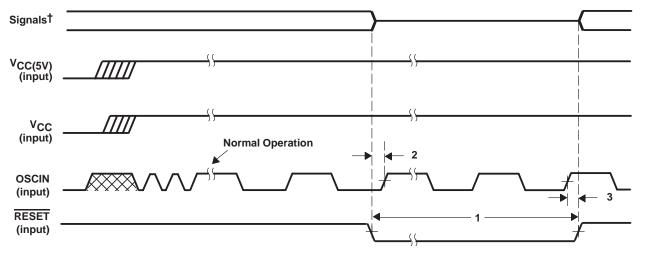

| RESET | 146  | I   | Reset. RESET (active low) resets the TNETX3100. RESET should be held low for 25 ms after the power supplies and clocks have stabilized. This input is synchronous and therefore, the system clock is operational during reset. |  |  |  |

## **Terminal Functions (Continued)**

## power interface

|         | TERMINAL                                                                                | DESCRIPTION                                                                                                                                |  |  |  |

|---------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NO.                                                                                     | DESCRIPTION                                                                                                                                |  |  |  |

| GND     | 6, 30, 54, 63, 70, 73, 80, 86, 92, 95, 101, 109, 112, 115, 126, 144, 163, 186, 210, 234 | Ground. GND is the 0-V reference for the device.                                                                                           |  |  |  |

| VCC     | 18, 42, 67, 77, 83, 89, 98, 107, 118, 133, 154, 174, 198, 222                           | Supply voltage $V_{CC} = 3.3 \pm 0.3 \text{ V}$                                                                                            |  |  |  |

| VCC(5V) | 15, 45, 75, 105, 135, 165, 195, 225                                                     | Supply voltage. $V_{CC(5V)} = 5 \pm 0.5 \text{V}$ . $V_{CC(5V)}$ is only for the I/O periphery and is used for the 5-V tolerant pads only. |  |  |  |

## summary of signal terminals by signal group function

| PORT DESCRIPTION                        | NUMBER OF<br>SIGNALS | MULTIPLIER | TOTAL |  |  |  |  |

|-----------------------------------------|----------------------|------------|-------|--|--|--|--|

| LED                                     | 3                    | 1          | 3     |  |  |  |  |

| 10-Mbit/s port                          | 9                    | 8          | 72    |  |  |  |  |

| 10-/100-Mbit/s port                     | 19                   | 2          | 38    |  |  |  |  |

| DIO                                     | 13                   | 1          | 13    |  |  |  |  |

| EAM port                                | 11                   | 1          | 11    |  |  |  |  |

| EEPROM interface                        | 2                    | 1          | 2     |  |  |  |  |

| DRAM interface                          | 51                   | 1          | 51    |  |  |  |  |

| Miscellaneous                           | 3                    | 1          | 3     |  |  |  |  |

| JTAG                                    | 5                    | 1          | 5     |  |  |  |  |

| Total design                            |                      |            | 198   |  |  |  |  |

|                                         | SUMMARY              |            |       |  |  |  |  |

| Assigned terminals                      |                      |            | 198   |  |  |  |  |

| Power terminals V <sub>CC(5V)</sub> ,   | 8                    |            |       |  |  |  |  |

| Power terminals V <sub>CC</sub> , 3.3 \ | 14                   |            |       |  |  |  |  |

| Power terminals GND                     |                      |            |       |  |  |  |  |

| Total number of terminals               |                      |            | 240   |  |  |  |  |

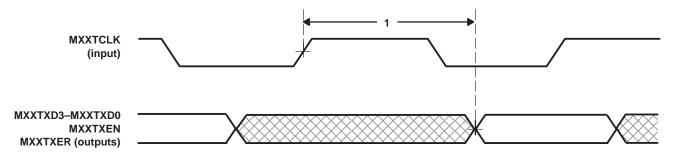

#### 10-Mbit/s and 10-/100-Mbit/s MAC interfaces (ports 00-09)

The following section illustrates the similarities between the 10-Mbit/s and 10-/100-Mbit/s MAC interfaces. All network data flows through either the 10-Mbit/s interface or 10-/100-Mbit/s interface.

#### data reception

#### receive arbitration

Receive arbitration raises the priority of received frames over pending transmit. Active transmissions are given highest priority. This makes it less likely that frames will be lost during heavy traffic load. For correct TNETX3100 operation, the RXARB bit (bit 5) must be set in the SIO register.

#### receive control

Receiver control is partitioned into two blocks:

- 1. The frame control block schedules all receive operations, i.e., detection and removal of the preamble, extraction of the addresses and frame length, data handling, and cyclic redundancy check (CRC) checking. Also included is a jabber-detection timer to detect frames being received on the network that exceed the maximum allowable length.

- 2. The FIFO control block places the received data in the FIFO buffers while also detecting and flagging erroneous data conditions in the flag byte.

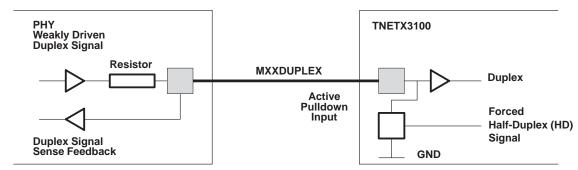

#### **TNETX3100 MXXDUPLEX terminals**

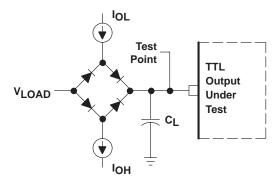

The MXXDUPLEX terminals are implemented as inputs with active pulldown circuitry, producing a pseudo-bidirectional terminal.

An external PHY can weakly drive the DUPLEX line high, indicating an intention for duplex operation. The TNETX3100 can override this DUPLEX terminal input by pulling the line low. This is detected by the PHY, which monitors the sense of the DUPLEX signal, causing it to operate in half-duplex mode. Thus, the TNETX3100 can force the PHY into half-duplex operation when desired (during testing, for example). See Figure 1.

Figure 1. MXXDUPLEX Signal Connection

If the PHY is driven only in half-duplex operation, a pulldown resistor should be permanently attached to the DUPLEX signal. If the PHY is operated in full duplex (with the option of the TNETX3100 forcing half duplex), a pullup resistor should be placed on the DUPLEX signal.

## TNETX3100 ThunderSWITCH<sup>™</sup> 10-PORT 10-/100-MBIT/S ETHERNET<sup>™</sup> SWITCH

SPWS031D - JUNE 1997 - REVISED OCTOBER 1997

#### flow control

The TNETX3100 incorporates a collision-based flow-control mechanism; this mechanism is activated by setting the FLOW bit (bit 5) in the RAM size register to a 1. Flow control affects only the ports that are in half duplex.

The TNETX3100 detects that it is becoming congested by monitoring the size of the free-buffer queue. When there are fewer than 256 buffers on the free queue, the TNETX3100 prevents frames from entering the device by forcing a collision with all frames on all ports (except any frames that the TNETX3100 is transmitting). When the flow control is active, the FLOW LED is illuminated.

When the TNETX3100 has transmitted some of the backlog from the DRAM, and the free-buffer queue increases to 256 or more, forced collisions cease, and frames can again enter the device.

This simplified approach maximizes the use of the DRAM for the mix of port activity. The 256-buffer threshold ensures that all ports can receive and complete a maximum-length frame when there are 256 free buffers.

The purpose of flow control is to reduce the risk of data loss if a long burst of activity causes the TNETX3100 to backlog frames until the DRAM is full. Flow control has no mechanism to allow the TNETX3100 to operate on a sustained basis when the activity level exceeds the device internal bandwidth. Transmit queue length limiting is disabled if FLOW = 1.

#### giant (long) frames

The TNETX3100 can handle frames up to 1531 bytes to support IEEE Std 802.10. All frames longer than 1535 bytes are truncated by the TNETX3100. Frames greater than 1535 bytes received in cut-through mode are passed. Frames greater than 1535 bytes received in store-and-forward mode are discarded and not transmitted. The LONG option bit governs how the statistics for long frames are recorded. The byte count for long frames with good CRCs is recorded in the RX + TX-frames 1024–1518 statistic, which effectively becomes RX + TX-frames 1024–1531 when LONG is set. Long frames received with bad CRCs are recorded as jabbers.

#### short frames

All frames less than 64 bytes received into any port are filtered by the TNETX3100 within the RX FIFOs. They do not appear on the DRAM bus.

#### RX filtering of no-cut-through frames

The TNETX3100 filters RX frames that are in error (CRC, alignment, jabber, etc.) when operating in the store-and-forward mode. A frame that might be cut-through can be non-cut-through if its destination is busy. If it contains any error, it is filtered. The error is recorded in the relevant statistic counter, with all used buffers being recovered and returned to the free queue.

#### data transmission

#### transmit control

Transmit control is partitioned into two blocks:

- 1. The frame control block handles the output of data into the PHYs, and a number of error states are handled. If a collision is detected, the state machine jams the output. If the collision is late (after the first 64-byte buffer has been transmitted) the frame is lost. If it is an early collision, the controller backs off before retrying. While operating in full duplex, both carrier-sense (CRS) mode and collision-sensing modes are disabled.

- 2. The FIFO control block handles the flow of data from the FIFO buffers to the MAC interface for transmission. The data within a FIFO buffer is cleared only after the data has been successfully transmitted without collision (for the half-duplex ports). Transmission recovery also is handled in this state machine. If a collision is detected, frame recovery and retransmission are initiated.

#### transmit pacing

When transmit pacing is enabled, the ThunderSWITCH architecture is capable of altering its transmission routine during times of heavy network activity. The TNETX3100 is intelligent enough to sense heavy network traffic and alter its transmission routing by intentionally inserting an extra amount of delay between transmission attempts. The added delay reduces collision rates, and thus reduces the number of transmission attempts, which helps reduce CPU utilization, lighten overall network traffic, and allows the network time to stabilize before attempting transmission. If the delay was not added, the TNETX3100 would attempt to transmit on an already heavily loaded network, adding to the network traffic's unsuccessful transmission attempts.

Each Ethernet MAC incorporates transmit-pacing logic. This is enabled on an individual basis by setting the TXPACE bit (bit 1) of the port control registers. When set, the MACs use transmit pacing to enhance performance (when connected on networks using other transmit-pacing capable MACs). Transmit pacing introduces delays into the normal transmission of frames, which delays transmission attempts between stations, reducing the probability of collisions occurring during heavy traffic (as indicated by frame deferrals and collisions). This increases the chance of successful transmission.

With pacing enabled, a frame is permitted (after one IPG) to immediately attempt transmission only if the pacing counter is zero. If the pacing counter is nonzero, the frame is delayed by the pacing delay (a delay of approximately four interframe gap delays).

#### interframe gap enforcement

The measurement reference for the interframe gap of 9.6  $\mu$ s (when transmitting at 10 Mbit/s) is changed, depending on frame traffic conditions. If a frame is successfully transmitted (without collision), 9.6  $\mu$ s is measured from MXXTXEN. If the frame suffered a collision, 9.6  $\mu$ s is measured from MXXCRS. The TNETX3100 can receive frames with an interframe gap of less than 9.6  $\mu$ s and it always transmits its frames with an interframe gap of 9.6  $\mu$ s. The 100-Mbit/s ports can receive frames with an interframe gap of less than 0.96  $\mu$ s and always transmit frames with a minimum interframe gap of 0.96  $\mu$ s.

#### backoff

The TNETX3100 implements the IEEE Std 802.3 binary exponential backoff algorithm.

#### 100-Mbit/s MAC interfaces (port 00)

The TNETX3100 allows port 00 to support pretagging and posttagging when forwarding frames to an external routing engine. Posttagging is used by an external routing engine to provide destination port information to the TNETX3100.

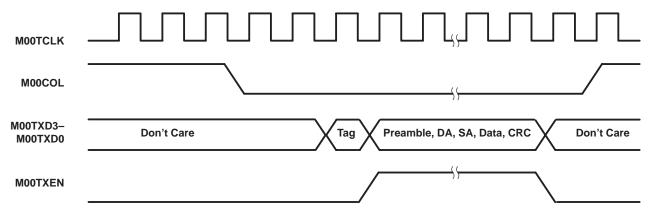

#### uplink TX pretagging to support an external routing engine

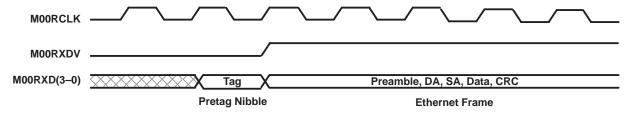

When forwarding frames to a routing engine, it is necessary to know which port received the frame. Multiple TNETX3100 devices can be incorporated into a larger switch fabric that is controlled by one routing engine. The TNETX3100 provides one nibble of information (to identify the source port) on the MII-interface data terminals prior to M00TXEN being asserted. See Figure 2.

Figure 2. Multiplex Operation for Uplink-Port Transmit Frames

Port 00, when operated at 100-Mbit/s mode, provides a tag nibble one cycle prior to M00TXEN being asserted. The nibble format is shown in Table 1.

Table 1. Source Port Number Codes

| SOURCE<br>PORT NUMBER<br>M00TXD3-M00TXD0 | PORT                    |

|------------------------------------------|-------------------------|

| 0000                                     | Reserved                |

| 0001                                     | Port 01 (10/100 Mbit/s) |

| 0010                                     | Port 02 (10/100 Mbit/s) |

| 0011                                     | Port 03 (10 Mbit/s)     |

| 0100                                     | Port 04 (10 Mbit/s)     |

| 0101                                     | Port 05 (10 Mbit/s)     |

| 0110                                     | Port 06 (10 Mbit/s)     |

| 0111                                     | Port 07 (10 Mbit/s)     |

| 1000                                     | Port 08 (10 Mbit/s)     |

| 1001                                     | Port 09 (10 Mbit/s)     |

| 1010                                     | Reserved                |

| 1011                                     | Reserved                |

| 1100                                     | Reserved                |

| 1101                                     | Reserved                |

| 1110                                     | Reserved                |

| 1111                                     | Reserved                |

#### uplink RX pretagging to support an external routing engine

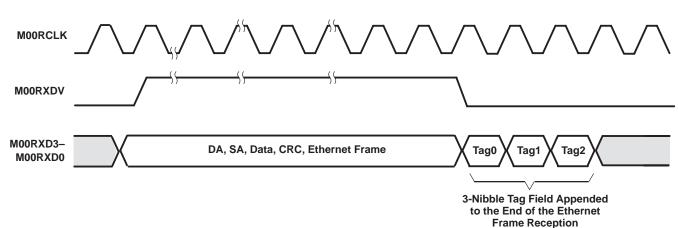

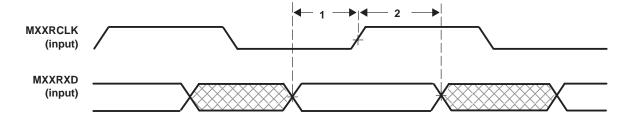

When port 00 (uplink) is operated in 100-Mbit/s mode, a pretag is placed one cycle prior to MRXDV going high for the frame; tag data is applied to M00RXD3–M00RXD0. This pretag is not operated on internally by the TNETX3100 although it is used by an external address-lookup engine. The tag is passed to the DRAM interface, where it appears on bits 31–28 of the forward pointer; this provides the ability for an upstream device, connected to the uplink, to pass information through the TNETX3100 to the DRAM bus where an external address-lookup device (TNETX15VEPGE) operates on that information. The external address-lookup device makes a forwarding decision based on destination address and VLAN register value (see Figure 3).

The pretag is qualified with the port that received the frame. Only pretags received on port 00 are valid. A pretag received on the uplink (port 00) is retained for the duration of the frame.

Figure 3. Data Format for Uplink RX Frames With Pretag

#### using TX pretagging and RX posttagging to support an external routing engine

If the TNETX3100 relies on the external routing engine to make switching decisions, no local switching is performed and port 00 forwards all frames to a routing engine; port 00 also provides a pretag on all forwarded frames. The pretag provides source-port information to the routing engine. The routing engine then makes forwarding decisions and transmits a frame and posttag to port 00; the posttag provides destination port information to the TNETX3100. To allow this, the TAGON bit (bit 4 of RSIZE register 0x00D2) must be a 1.

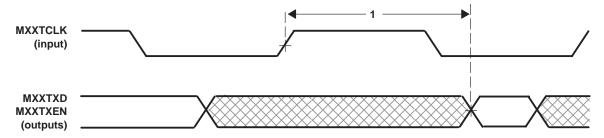

#### uplink RX posttagging to support an external routing engine

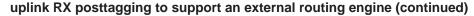

The external routing engine hardware must provide port 00 with an indication of the destination-port information; this information is used by the TNETX3100 to route frames to ports 01–09. This indication consists of three nibbles. When posttagging is enabled, the tag bytes overwrite the value received on the EAM interface (EAM interface has no effect). When posttagging is turned off (designed for local switching), the posttag is ignored, and the EAM interface or the internal address match supplies the routing information.

There is no handshake or flow control for the receive uplink path on the TNETX3100. If required, this must be implemented in upstream devices. No preamble is expected on data received by the uplink at 100 Mbit/s (see Figure 4). If RX posttagging is used, the receive side of port 00 must be configured for store-and-forward mode.

Figure 4. Data Format for Uplink RX Frames

#### uplink frame RX routing via posttagging

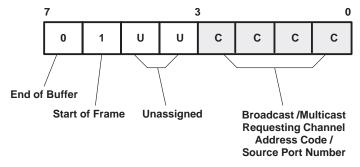

The tag fields are coded as shown in Figure 5:

#### tag 0

| BIT 3                            | BIT 2                            | BIT 1                            | BIT 0                                |  |

|----------------------------------|----------------------------------|----------------------------------|--------------------------------------|--|

| Destination Port 04<br>10 Mbit/s | Destination Port 03<br>10 Mbit/s | Destination Port 02<br>10 Mbit/s | Destination Port 01<br>10/100 Mbit/s |  |

| g 1                              |                                  |                                  |                                      |  |

| BIT 3                            | BIT 2                            | BIT 1                            | BIT 0                                |  |

| Destination Port 08<br>10 Mbit/s | Destination Port 07<br>10 Mbit/s | Destination Port 06<br>10 Mbit/s | Destination Port 05<br>10 Mbit/s     |  |

| g 2                              |                                  |                                  |                                      |  |

| BIT 3                            | BIT 2                            | BIT 1                            | BIT 0                                |  |

| Reserved                         | Reserved                         | Reserved                         | Destination Port 09                  |  |

Figure 5. Tag Field Coding

If only one bit is set in the destination-port field, the packet is a unicast. With tag 0 = 0000, tag 1 = 0100, and tag 2 = 0000, the packet is unicast and destined for port 06.

If more than one bit is set, the packet is VLAN multicast. With tag 0 = 1010, and tag 1 = 1001, and tag 2 = 0001, the packet is transmitted from ports 02, 04, 05, 08, and 09. This allows broadcast and multicast traffic to be limited in supporting external VLANs.

If all bits are clear in the tags, the packet is invalid and is discarded.

#### 100-Mbit/s MAC interfaces (port 01)

This port is identical to the uplink port (port 00) except that it does not support posttagging. The port provides the pretag prior to TXEN going active. The tag is ignored by externally connected PHYs.

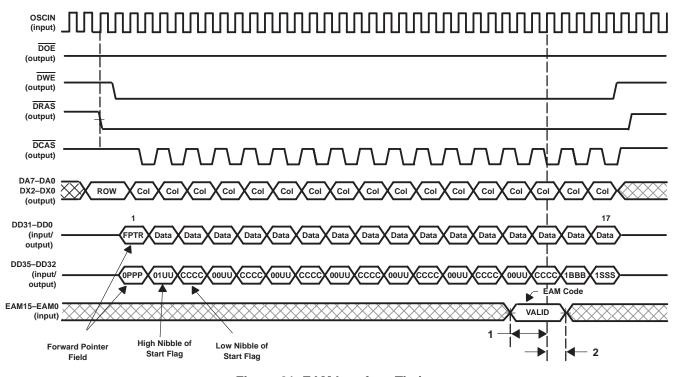

#### **DRAM** and **EAM** interfaces

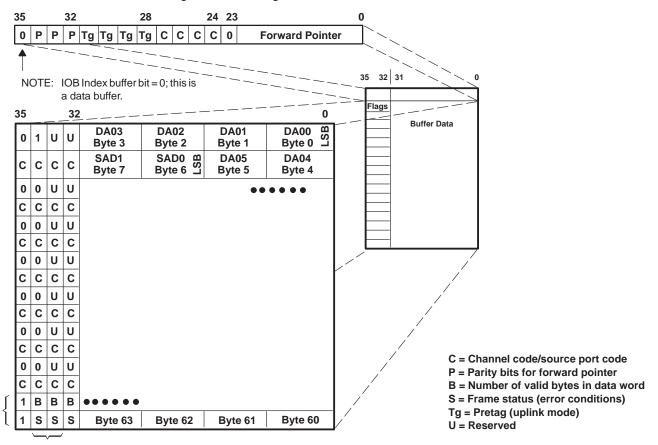

All valid frames are passed across the DRAM interface (see Figure 8). The EAM hardware can detect the start of a new frame from the flag-byte information. The first flag nibble on the DRAM bus (bits 35–32) corresponds to bits 7–4 of the frame flag (see Figure 6). In conjunction with the DRAM column address strobe, external logic accesses the frame addresses and performs external address lookups as detailed in the following:

- Use row-address strobe (DRAS) and column-address strobe (DCAS) to identify the position of the forward pointer, the top nibble of the flag byte, and whether the nibble contains the start of frame code 01XX. Bit 35 of the forward pointer is zero to denote a start of frame. If it is high, the frame is an in-order broadcast (IOB) link buffer and not the start-of-data frame (bits 34, 33, and 32 contain parity information for the three forward pointers or data bytes).

- Bits 31–28 of the forward pointer contain the pre-tag nibble applied to the uplink (when used in uplink mode). See description of port 00 (uplink port).

- Bits 27–24 denote the active port number (port 00 = 0000, port 01 = 0001, etc.).

- Use the DRAM column-address strobe (DCAS) to identify the presence of destination and source address data on the DRAM interface.

- Perform address processing.

- Present the destination-channel bit map not more than 12 memory cycles after the high nibble of the start flag is transmitted on the DRAM interface.

- External address timing is shown in Figure 21.

NOTE: Diagram shows end-of-frame flag format. Multiple buffer frames use this flag format only on the last buffer. (End-of buffer flags are used between a frame's buffers.)

Figure 6. Buffer Diagram Showing Flag Format for a 64-byte Frame

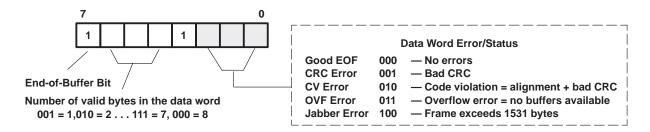

#### flag byte

Flag attributes are assigned to the deserialized data word, identifying key attributes. The flags are used in later data handling. The flag field is assigned to every eight data bytes. The format of the subfields within the flag byte change, depending on the flag information. Previously, the start-of-frame format was described in the address compare text (see Figure 7). The formats shown in Figure 7 are the end-of-buffer and the end-of-frame flag formats. When the most-significant bit (end-of-buffer bit) is set, the remaining bits of the most-significant nibble contain the number of bytes in the data word, while the least-significant nibble contains error/status information.

#### a) START-OF-FRAME (SOF) FORMAT

#### b) END-OF-BUFFER (EOB) FLAG BYTE FORMAT

c) END-OF-FRAME (EOF) FLAG BYTE FORMAT

NOTE A: The EOB bit is asserted after each 64-byte data transfer. Bit 3 of the flag byte is set only at the EOF.

Figure 7. EOB, EOF, and SOF Flag Formats

#### **DRAM** and **EAM** interfaces (continued)

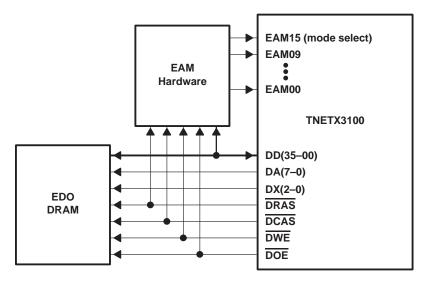

The TNETX3100 gives priority to the external channel address, over the internal-channel address-match information, to route the frame to the appropriate channel. To enable the EAM interface, the EAMON bit in the FEAGFG register must be set to a 1 (see Figure 8).

Figure 8. EAM Interface

Table 2 provides the 4-bit code needed to identify the destination port when using the EAM interface with EAM15 (mode select) bit set.

- With the EAM04 bit and EAM15 bit (mode select) both high, all other EAM bits are ignored (this is a no-operation code) and the frame uses the internal address match information (if enabled). With this code, any external device is signaling that it does not participate in address matching (at least during this cycle). These two bits are hardwired to 1 if no external device is present to disable this interface.

- With the EAM04 bit low and EAM15 bit (mode select) high, EAM03–EAM00 code is used to identify a single destination port.

- When the EAM15 bit (mode select) is low:

- The other bits EAM09-EAM00 represent a mask of the ports to which the frame is forwarded. For example, if the frame is copied to ports 00, 07, and 09, the signal value is 0b1010000001.

- To discard a frame, the external interface provides an all-zero code 0b0000000000).

All internal-address registers are disabled with the not-learn (NLEARN) bit (port-control register, bit 3), if the external device is used.

An external device has two choices of codes with which to forward a frame to a single port. For example, to forward a frame to port 3, one can enter 0x004 (multiport capable with only one port specified), or 0x403 (single-port capable only). While using the first method can make specifying unicast and multicast forwarding more unified, it forces the TNETX3100 to use internal cycles to build a broadcast table with only one entry, and thereby unicast traffic performance is reduced. Unicast forwarding is done with the EAM15 high, and the port specified in the lower four bits.

#### **DRAM and EAM interfaces (continued)**

**Table 2. EAM Port Codes**

| TNETX3100<br>PORT       | EAM15<br>MODE SELECT | EAM09-EAM05 | EAM04              | EAM03-EAM00  |

|-------------------------|----------------------|-------------|--------------------|--------------|

| Port 00 (10/100 Mbit/s) | 1                    | xxxxx       | 0                  | 0000         |

| Port 01 (10/100 Mbit/s) | 1                    | xxxxx       | 0                  | 0001         |

| Port 02 (10 Mbit/s)     | 1                    | xxxxx       | 0                  | 0010         |

| Port 03 (10 Mbit/s)     | 1                    | xxxxx       | 0                  | 0011         |