# 300 mA Adjustable Voltage LDO Regulator

#### Description

The CAT6220 is a 300 mA CMOS low dropout regulator whose output voltage is user adjustable that provides fast response time during load current and line voltage changes.

With 1  $\mu A$  of shutdown current, an internal no–load operating current of only 10  $\mu A$ , and full–load operating current of 40  $\mu A$ , the CAT6220 is ideal for battery–operated devices with supply voltages from 2.3 V to 6.5 V.

The CAT6220 offers 1% initial accuracy and low dropout voltage, 270 mV typical at 300 mA. Stable operation is provided with a small value ceramic capacitor, reducing required board space and component cost.

Other features include current limit and thermal protection.

The device is available in the low profile (1 mm max height) 5–lead TSOT–23 and 6–pad 2 mm x 2 mm TDFN packages.

#### **Features**

- Guaranteed 300 mA Output Current

- Low Dropout Voltage of 270 mV at 300 mA

- Stable with Ceramic Output Capacitor

- No-load Ground Current of 10 μA Typical

- Full-load Ground Current of 40 µA Typical

- ±1.0% Output Voltage Initial Accuracy

- ±2.0% Accuracy over Temperature

- "Zero" Current Shutdown Mode

- Current Limit and Thermal Protection

- 5-lead TSOT-23 and 6-pad TDFN Packages

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Applications**

- Toys

- Consumer Electronics

- Cellular Phones

- Battery-powered Devices

#### ON Semiconductor®

http://onsemi.com

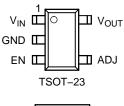

## PIN CONNECTIONS

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

**Table 1. PIN DESCRIPTIONS**

|          | Package Pin # |      |                                                                                                            |  |  |  |

|----------|---------------|------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | TSOT          | TDFN | Function                                                                                                   |  |  |  |

| VIN      | 1             | 3    | Supply voltage input.                                                                                      |  |  |  |

| GND      | 2             | 2    | Ground reference. All GND pins must be grounded.                                                           |  |  |  |

| EN       | 3             | 1    | Enable input (active high)                                                                                 |  |  |  |

| ADJ      | 4             | 6    | Digital programming input                                                                                  |  |  |  |

| NIC      | -             | 5    | No Internal Connection. A voltage or signal applied to this pin will have no effect upon device operation. |  |  |  |

| VOUT     | 5             | 4    | Output Voltage Adjustment.                                                                                 |  |  |  |

| GND      |               | PAD  | Center pad or tab; for heat sinking                                                                        |  |  |  |

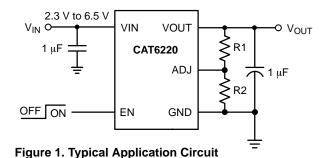

#### Pin Function

**VIN** is the supply pin for the LDO. A small 1  $\mu$ F ceramic bypass capacitor is required between the  $V_{IN}$  pin and ground near the device. When using longer connections to the power supply,  $C_{IN}$  value can be increased without limit. The operating input voltage range is from 2.3 V to 6.5 V.

**EN** is the enable control logic (active high) for the regulator output. Enable is a high impedance input and must not be left unconnected. Floating EN will result in unpredictable action at VOUT.

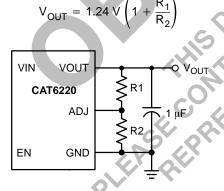

**VOUT** is the LDO regulator's output. Output voltage is set by two external resistors arranged as a voltage divider between VOUT and Ground. The center point of the divider is connected to ADJ as shown in Figure 2. The minimum recommended current through resistors is  $5 \,\mu A$ . The ratio of the resistors is set by the formula:

Figure 2. R1 and R2 Set CAT6220's Output Voltage

A small 1  $\mu F$  ceramic bypass capacitor is required between the VOUT pin and ground. For better transient response, its value can be increased to 2.2  $\mu F$ . This capacitor should be located near the device.

**GND** is the ground reference for the LDO. This pin must be connected to the system ground line or the ground plane of the PCB.

The backside center pad of the TDFN package is internally connected to the GND pin. Any PCB connection to this pad must be either floating or at GND potential.

**ADJ** is the LDO's voltage control input. This pin is connected to the center of the resistor voltage divider R1, R2. A 10 pF capacitor connected in parallel with R1 will improve the transient load regulation for VOUT  $\leq 2$  V.

### **Thermal and Short Circuit Protection**

CAT6220 is equipped with thermal protection and over–current limiting circuitry.

In the event of a short circuit CAT6220 will limit its output current to approximately 400 mA. If the short circuit persists CAT6220's internal temperature will rise and if the chip's temperature reaches 140°C CAT6220 will shut off all current to the load which protects the system and allows the LDO to cool down. When the LDO's internal temperature drops below 130°C the LDO automatically turns ON again. If the short circuit is still present another thermal cycle will ensue. This will continue until either the short circuit is removed or the Enable pin is taken LOW.

For the TSOT23–5 package, a continuous 300 mA output current may turn–on the thermal protection. If this happens the LDO will respond by shutting off power to the load and thermal cycling will begin.

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Parameter                                 | Rating                        | Unit |

|-------------------------------------------|-------------------------------|------|

| V <sub>IN</sub>                           | 0 to 7                        | V    |

| V <sub>EN</sub> , V <sub>OUT</sub>        | −0.3 to V <sub>IN</sub> + 0.3 | V    |

| Junction Temperature, T <sub>J</sub>      | +150                          | °C   |

| Power Dissipation, P <sub>D</sub>         | Internally Limited (Note 1)   | mW   |

| Storage Temperature Range, T <sub>S</sub> | -65 to +150                   | °C   |

| Lead Temperature (soldering, 5 sec.)      | 260                           | °C   |

| ESD Rating (Human Body Model)             | 2                             | kV   |

| ESD Rating (Machine Model)                | 200                           | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 3. RECOMMENDED OPERATING CONDITIONS (Note 2)

| Parameter                                                                                                                  | Range                | Unit |

|----------------------------------------------------------------------------------------------------------------------------|----------------------|------|

| V <sub>IN</sub>                                                                                                            | 2.3 to 6.5           | V    |

| lout                                                                                                                       | 0.005 to 300         | mA   |

| V <sub>EN</sub>                                                                                                            | 0 to V <sub>IN</sub> | V    |

| Junction Temperature Range, T <sub>J</sub>                                                                                 | -40 to +140          | °C   |

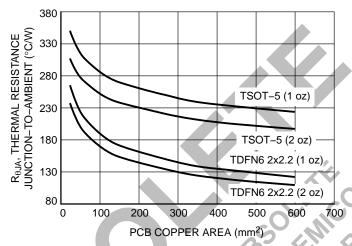

| Package Thermal Resistance (TSOT23–5), θ <sub>JA</sub>                                                                     | 280                  | °C/W |

| Package Thermal Resistance (TDFN–6), θ <sub>JA</sub>                                                                       | 160                  | °C/W |

| Package Thermal Resistance (TDFN–6), θ <sub>JA</sub> 2. The device is not guaranteed to work outside its operating rating. |                      |      |

<sup>2.</sup> The device is not guaranteed to work outside its operating rating.

The maximum allowable power dissipation at any T<sub>A</sub> (ambient temperature) is P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

**Table 4. ELECTRICAL OPERATING CHARACTERISTICS** (Note 3) ( $V_{IN} = V_{OUT} + 1.0 \text{ V}$ ,  $V_{EN} = \text{High}$ ,  $I_{OUT} = 100 \,\mu\text{A}$ ,  $C_{IN} = 1 \,\mu\text{F}$ ,  $C_{OUT} = 1 \,\mu\text{F}$ , ambient temperature of 25°C (over recommended operating conditions unless specified otherwise). **Bold numbers** apply for the entire junction temperature range.)

| Symbol              | Parameter                                     | Conditions                                                                   | Min   | Тур  | Max   | Unit   |

|---------------------|-----------------------------------------------|------------------------------------------------------------------------------|-------|------|-------|--------|

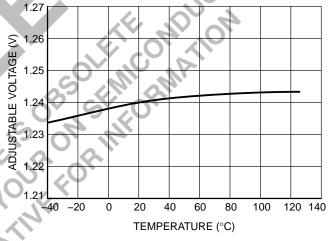

| $V_{ADJ}$           | Adjustable Voltage                            | I <sub>OUT</sub> = 100 μA                                                    |       | 1.24 |       | V      |

| V <sub>ADJ</sub>    | Adjustable Voltage Accuracy                   | Initial accuracy                                                             | -1.5  |      | +1.5  | %      |

|                     |                                               |                                                                              | -2.5  |      | +2.5  |        |

| I <sub>ADJ</sub>    | ADJ pin Input Current                         |                                                                              |       | 1    | 50    | nA     |

| TC <sub>OUT</sub>   | Output Voltage Temp. Coefficient              |                                                                              |       | 40   |       | ppm/°C |

| V <sub>R-LINE</sub> | Line Regulation                               | V <sub>IN</sub> = V <sub>OUT</sub> + 1.0 V to 6.5 V                          | -0.2  | ±0.1 | +0.2  | %/V    |

|                     |                                               |                                                                              | -0.35 |      | +0.35 |        |

| V <sub>R-LOAD</sub> | Load Regulation                               | I <sub>OUT</sub> = 100 μA to 300 mA                                          |       | 0.9  | 1.5   | %      |

|                     |                                               |                                                                              |       |      | 2.2   |        |

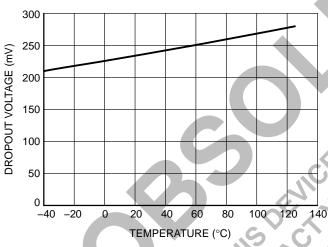

| $V_{DROP}$          | Dropout Voltage (Note 4)                      | I <sub>OUT</sub> = 300 mA                                                    |       | 270  | 350   | mV     |

|                     |                                               |                                                                              |       |      | 500   |        |

| $I_{GND}$           | Ground Current                                | I <sub>OUT</sub> = 5 μA                                                      |       | 10   | 15    | μΑ     |

|                     |                                               |                                                                              |       |      | 20    |        |

|                     |                                               | I <sub>OUT</sub> = 300 mA                                                    |       | 40   | 100   |        |

| I <sub>GND-SD</sub> | Shutdown Ground Current                       | V <sub>EN</sub> < 0.4 V                                                      |       |      | 1     | μΑ     |

|                     |                                               |                                                                              | 0,    | 7    | 2     |        |

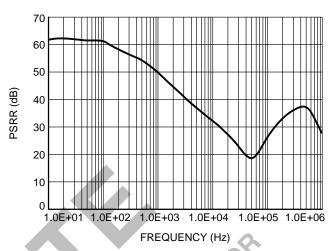

| PSRR                | Power Supply Rejection Ratio                  | f = 100 Hz                                                                   |       | 62   |       | dB     |

|                     |                                               | f = 1 kHz                                                                    | 0,    | 48   |       |        |

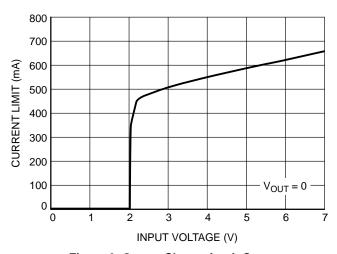

| I <sub>SC</sub>     | Output short circuit current limit            | V <sub>OUT</sub> = 0 V                                                       |       | 500  | 700   | mA     |

| T <sub>ON</sub>     | Turn-On Time                                  | 4,000                                                                        |       | 150  |       | μs     |

| e <sub>N</sub>      | Output Noise Voltage                          | BW = 10 Hz to 100 kHz,<br>V <sub>OUT</sub> = 1.8 V, I <sub>OUT</sub> = 10 mA |       | 150  |       | μVrms  |

| R <sub>OUT-SH</sub> | Shutdown Switch Resistance                    | (V) -4 (V)                                                                   |       | 250  |       | Ω      |

| ESR                 | C <sub>OUT</sub> equivalent series resistance |                                                                              | 5     |      | 500   | mΩ     |

| DIGITAL IN          | IPUT                                          | 0,0                                                                          |       |      |       |        |

| V <sub>HI</sub>     | Logic High Level                              | V <sub>IN</sub> = 2.3 to 6.5 V                                               | 1.8   |      |       | V      |

|                     | CO                                            | V <sub>IN</sub> = 2.3 to 6.5 V, 0°C to +125°C junction temperature           | 1.6   |      |       |        |

| $V_{LO}$            | Logic Low Level                               | V <sub>IN</sub> = 2.3 to 6.5 V                                               |       |      | 0.4   | V      |

| I <sub>IN</sub>     | Input Current                                 | V <sub>LOGIC</sub> = 0.4 V                                                   |       | 0.15 | 1     | μΑ     |

|                     | Input Current                                 | V <sub>LOGIC</sub> = V <sub>IN</sub>                                         |       | 1.5  | 4     |        |

| THERMAL             | PROTECTION                                    |                                                                              |       |      |       |        |

| T <sub>SD</sub>     | Thermal Shutdown                              |                                                                              |       | 140  |       | °C     |

| T <sub>HYS</sub>    | Thermal Hysteresis                            |                                                                              |       | 10   |       | °C     |

<sup>3.</sup> Specification for 2.5 V output version unless specified otherwise.

<sup>4.</sup> Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value measured at 1 V differential. During test, the input voltage stays always above the minimum 2.3 V.

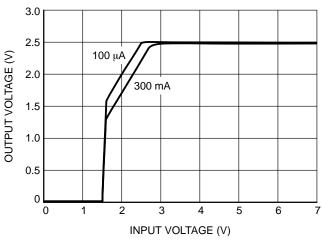

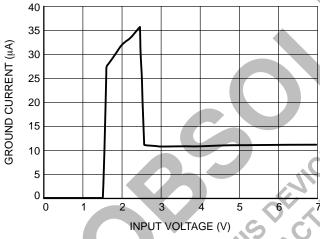

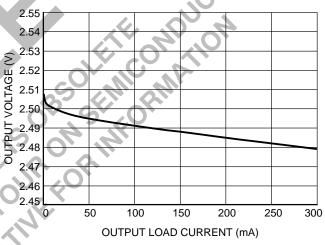

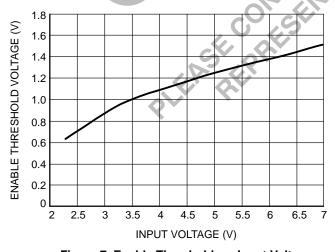

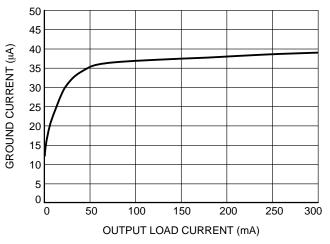

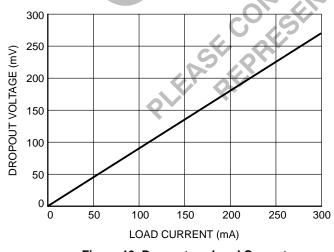

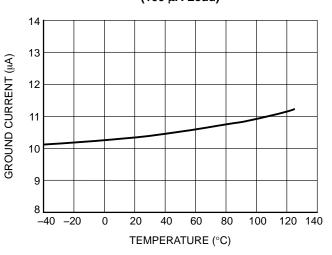

#### TYPICAL CHARACTERISTICS

$(V_{IN}=3.5~V,~R1=R2=250~K\Omega,~I_{OUT}=100~\mu A,~C_{IN}=1~\mu F,~C_{OUT}=1~\mu F,~T_{A}=25^{\circ}C$  unless otherwise specified.)

2.53

2.52

2.51

OUTPUT VOLTAGE (V) 2.50 2.49 2.48 2.47 5 6

Figure 3. Dropout Characteristics

Figure 4. Line Regulation

INPUT VOLTAGE (V)

Figure 5. Ground Current vs. Input Voltage

Figure 6. Load Regulation

Figure 7. Enable Threshold vs. Input Voltage

Figure 8. Ground Current vs. Load Current

#### **TYPICAL CHARACTERISTICS**

$(V_{IN}=3.5~V,~R1=R2=250~K\Omega,~I_{OUT}=100~\mu A,~C_{IN}=1~\mu F,~C_{OUT}=1~\mu F,~T_{A}=25^{\circ}C$  unless otherwise specified.)

Figure 9. Output Short-circuit Current vs. Input Voltage

Figure 10. PSRR vs. Frequency (10 mA Load)

Figure 11. Dropout vs. Temperature (300 mA Load)

Figure 12. Adjustable Voltage vs. Temperature (100 μA Load)

Figure 13. Dropout vs. Load Current

Figure 14. Ground Current vs. Temperature (5 µA Load)

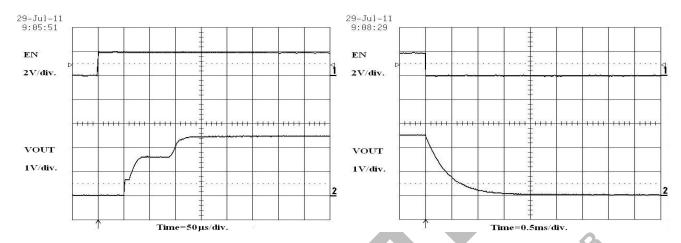

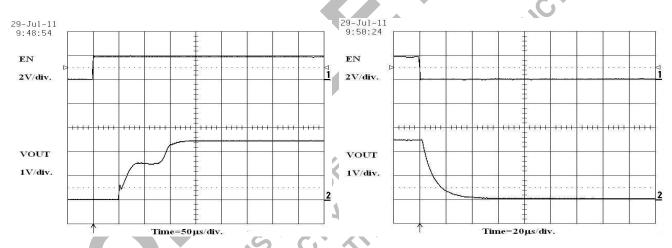

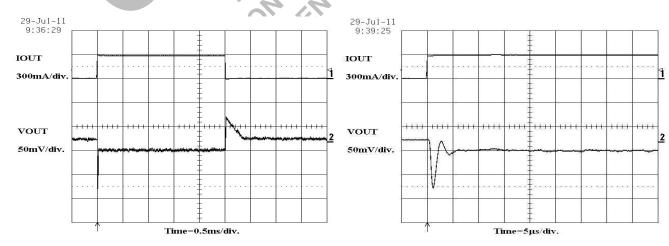

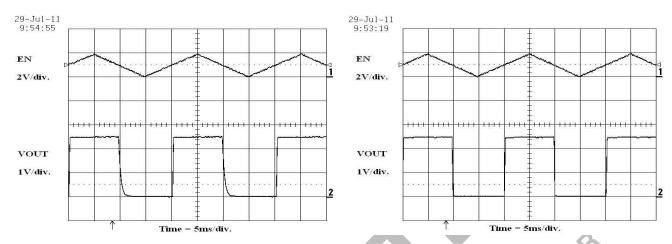

#### TRANSIENT CHARACTERISTICS

$(V_{IN}=3.5~V,~R1=R2=250~K\Omega,~I_{OUT}=100~\mu A,~C_{IN}=1~\mu F,~C_{OUT}=1~\mu F,~T_{A}=25^{\circ}C$  unless otherwise specified.)

Figure 15. Enable Turn-On (100 μA Load)

Figure 16. Enable Turn-Off (100 μA Load)

Figure 17. Enable Turn-On (300 mA Load)

Figure 18. Enable Turn-Off (300 mA Load)

Figure 19. Load Transient Response (0.1 mA to 300 mA)

Figure 20. Load Transient Response - Detail

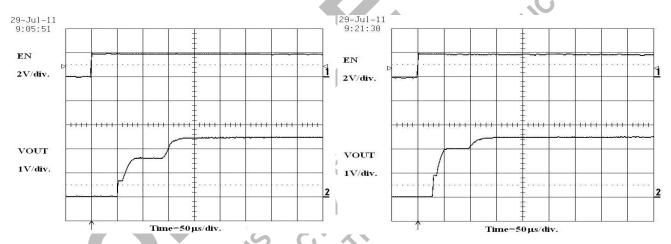

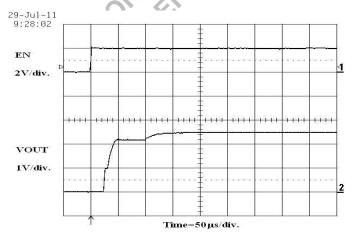

#### TRANSIENT CHARACTERISTICS

$(V_{IN}=3.5~V,~R1=R2=250~K\Omega,~I_{OUT}=100~\mu\text{A},~C_{IN}=1~\mu\text{F},~C_{OUT}=1~\mu\text{F},~T_{A}=25^{\circ}\text{C}~unless~otherwise~specified.})$

Figure 21. Slow–Enable Operation (100 μA Load)

Figure 22. Slow-Enable Operation (300 mA Load)

Figure 23. Enable Turn-On at VIN = 4.5 V (100 μA Load)

Figure 24. Enable Turn-On at VIN = 5.5 V (100 μA Load)

Figure 25. Enable Turn-On at VIN = 6.5 V (100 μA Load)

**Table 5. THERMAL PERFORMANCE**

| Package                                 | Symbol        | Test Conditions                            | Min | Тур | Max | Unit |

|-----------------------------------------|---------------|--------------------------------------------|-----|-----|-----|------|

| PACKAGE THERMAL CONDUCTIVITY COMPARISON |               |                                            |     |     |     |      |

| TSOT-23-5                               | $\theta_{JA}$ | 1 oz Copper Thickness, 100 mm <sup>2</sup> |     | 280 |     | °C/W |

|                                         | θJC           |                                            |     | 68  |     |      |

| TDFN-6                                  | $\theta_{JA}$ | 1 oz Copper Thickness, 100 mm <sup>2</sup> |     | 160 |     | °C/W |

|                                         | θJC           |                                            |     | 35  |     |      |

Figure 26.  $R_{\theta JA}$  vs. PCB Copper Area

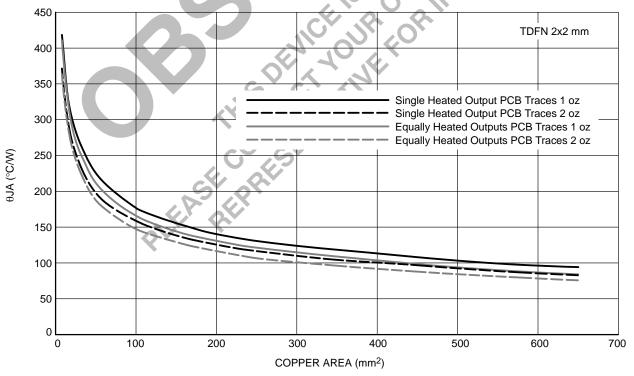

Figure 27. Thermal Characteristic as a Function of Copper Area on the PCB

#### **PACKAGE DIMENSIONS**

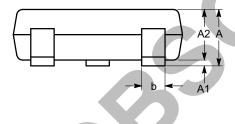

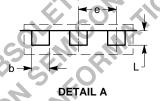

TSOT-23, 5 LEAD CASE 419AE-01 **ISSUE O**

**TOP VIEW**

SIDE VIEW

**END VIEW**

- Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MO-193.

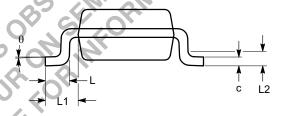

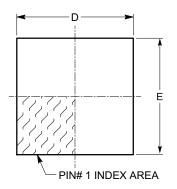

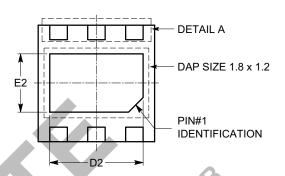

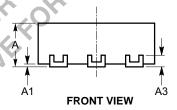

#### **PACKAGE DIMENSIONS**

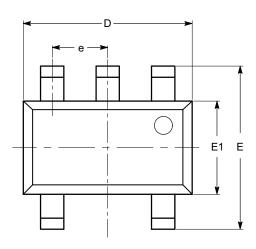

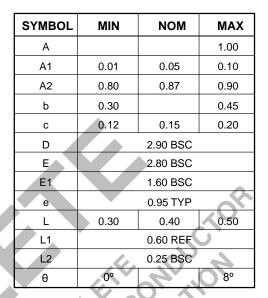

**TDFN6, 2x2** CASE 511AH-01 ISSUE A

**TOP VIEW**

**SIDE VIEW**

**BOTTOM VIEW**

#### ORDERING INFORMATION

| Device Order Number | Specific<br>Device<br>Marking | Package<br>Type | Temperature Range                  | Lead Finish | Shipping (Note 7)                  |

|---------------------|-------------------------------|-----------------|------------------------------------|-------------|------------------------------------|

| CAT6220TDI-GT3      | X2                            | TSOT-23-5       | I = Industrial<br>(-40°C to +85°C) | NiPdAu      | Tape & Reel,<br>3,000 Units / Reel |

| CAT6220VP5I-GT3     | AK                            | TDFN-6          | I = Industrial<br>(-40°C to +85°C) | NiPdAu      | Tape & Reel,<br>3,000 Units / Reel |

- 5. All packages are RoHS-compliant (Lead-free, Halogen-free).

- 6. The standard lead finish is NiPdAu pre-plated (PPF) lead frames.

- For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

- 8. For detailed information and a breakdown of device nomenclature and numbering systems, please see the ON Semiconductor Device Nomenclature document, TND310/D, available at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative