# High-Performance Secure MCUs for Industrial IoT and Metering Applications, Up to 2MB Flash, 512K Dual-Port SRAM, Advanced Crypto and Security Features

# Description

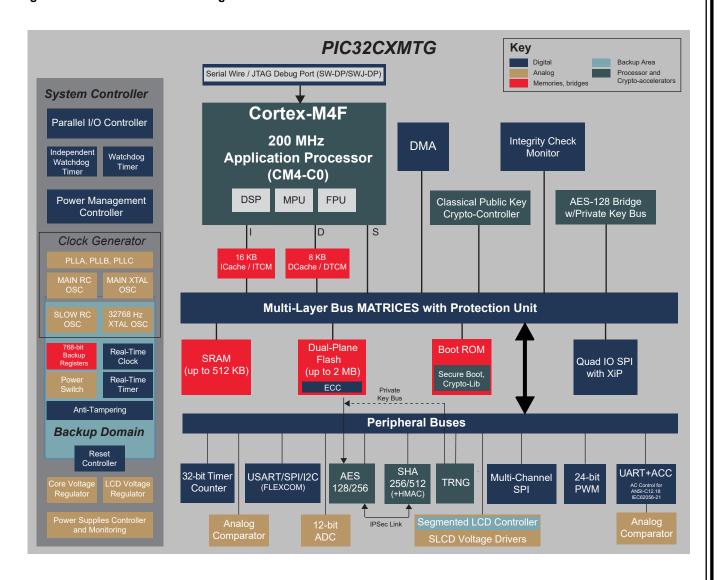

The Microchip PIC32CXMTG series is a family of system-on-chip solutions well suited for smart energy applications such as communication modules and residential split meter systems. Built around a 32-bit Arm® Cortex®-M4F RISC processor, the devices run at a maximum speed of 200 MHz and embed up to 2 Mbytes of embedded Flash, up to 512 Kbytes of SRAM and 16 Kb of Instruction and 8 Kb of Data Cache/Tightly Coupled Memory (TCM) on-chip.

A QSPI interface with eXecute-in-Place (XiP) coupled with on-the-fly AES128 encryption bridge future proofs the devices and ensures platform scalability in case of memory extension needs or changing system requirements.

A Secure Boot and secure key storage coupled with advanced cryptographic/Hash hardware accelerators, such as ECC, RSA, AES128/256 and SHA256/512, support the different encryption and authentication protocols.

The series also features a segmented LCD controller, anti-tampers, Floating Point Unit (FPU), Memory Protection Unit (MPU), FLEXCOM peripherals supporting I2C, SPI, UART/USART interfaces, three PWMs for pulse output functions, 12-channel general-purpose 32-bit timers, 12-bit ADC, analog comparators and a battery backed-up RTC running as low as 1  $\mu$ A.

PIC32CXMTG devices are available in EP-TQFP128-pin exposed pin and VQFN64 packages.

See the table Configuration Summary for device configuration versus packages.

# **Features**

- Core

- Arm<sup>®</sup> Cortex<sup>®</sup>-M4F running at up to 200 MHz

- 16 Kbytes ITCM/I-Cache, 8 Kbytes DTCM/D-Cache

- Memory Protection Unit (MPU)

- IEEE®754-compliant, single-precision Floating Point Unit (FPU), DSP instruction, Thumb®-2 instruction set

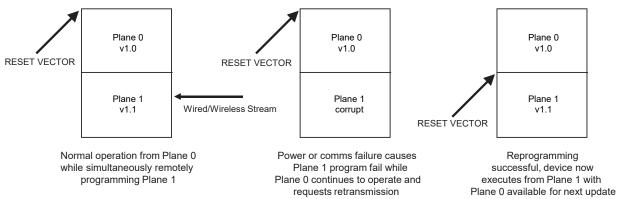

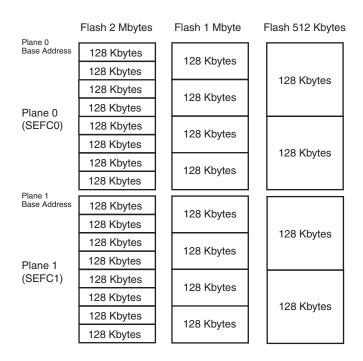

- Up to 2 Mbytes of embedded dual plane/dual boot Flash

- · Built-in ECC, Read-While-Write (RWW) support and Suspend/Resume of write/erase operations

- Endurance of 100K Write/Erase cycles (1M in qualification)

- Up to 512 Kbytes of embedded SRAM

- · Security and Cryptography

- Secure Boot

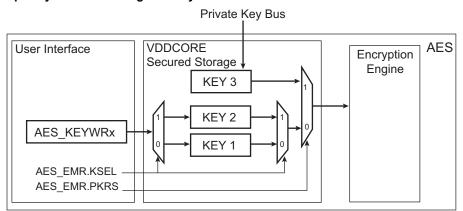

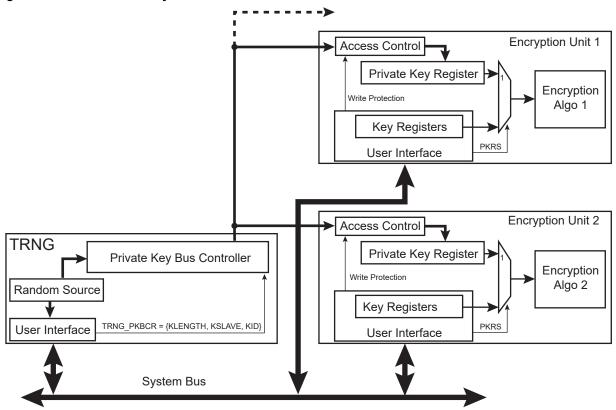

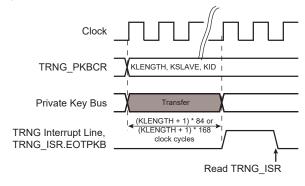

- Secure key storage and transfer to Advanced Encryption Standard (AES) and AES Bridge (AESB) without processor intervention

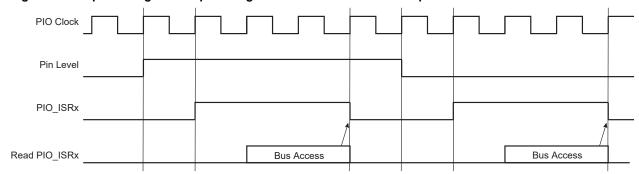

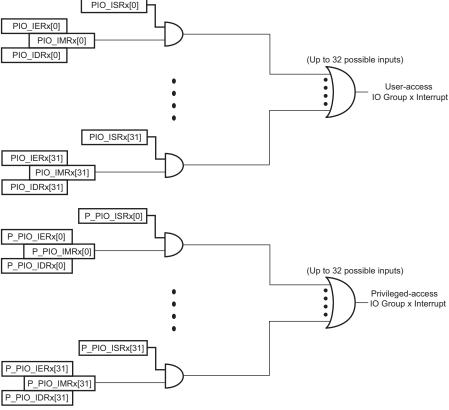

- One-time programmable block for software monotonic counter

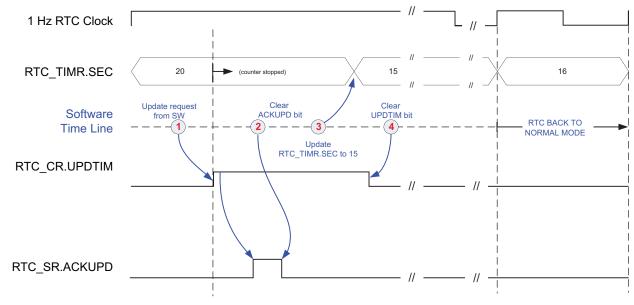

- Security bit to disable debug port access

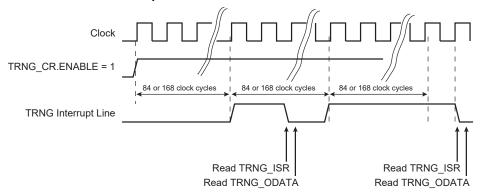

- True Random Number Generator (TRNG)

- Deterministic Random Number Generator (DRNG) support as required by NIST 800-90B

- AES: 256-, 192-, 128-bit key algorithm, compliant with FIPS PUB-197 specifications, ARIA

- AES128 on-the-fly encryption/decryption bridge for QSPI communications

- Secure Hash Algorithm (SHA) supporting SHA1, SHA224, SHA256, SHA384 and SHA512, compliant with FIPS PUB-197 specifications, and associated HMAC

- Classical Public Key Cryptographic Controller (CPKCC) supporting:

- · RSA up to 7168 bits, elliptic curve, DSA, DRNG

- 768 bits of General Purpose Backup registers (GPBR) can be defined as write-once

- Automatic and immediate keys erasing upon detection of Flash erase signal assertion

- · Erase of AES keys, QSPI scrambling keys and GPBR

- Anti-tamper with time-stamping, configurable and immediate actions upon detection

- · Erase of AES, AESB keys, QSPI scrambling keys and General Purpose Backup registers

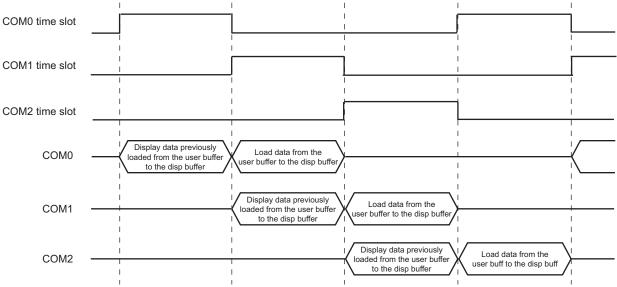

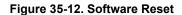

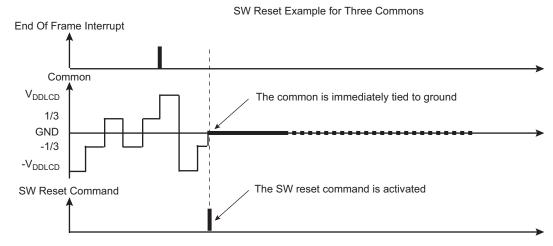

- Integrity Check Module (ICM) based on SHA256, autonomous

- System Controller

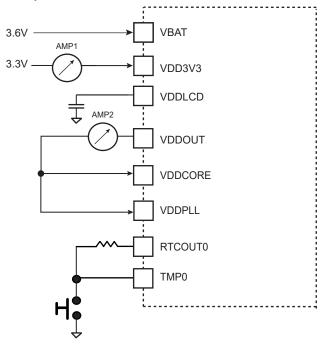

- Power supply

- · Embedded core and LCD voltage regulator for single-supply operation

- Supply monitors

- Ultra-low-power Backup mode

- Clock

- · Programmable PLLs and oscillator clock sources

- · Clock failure detection

- · CPU frequency monitor

- · Main crystal oscillator failure detection

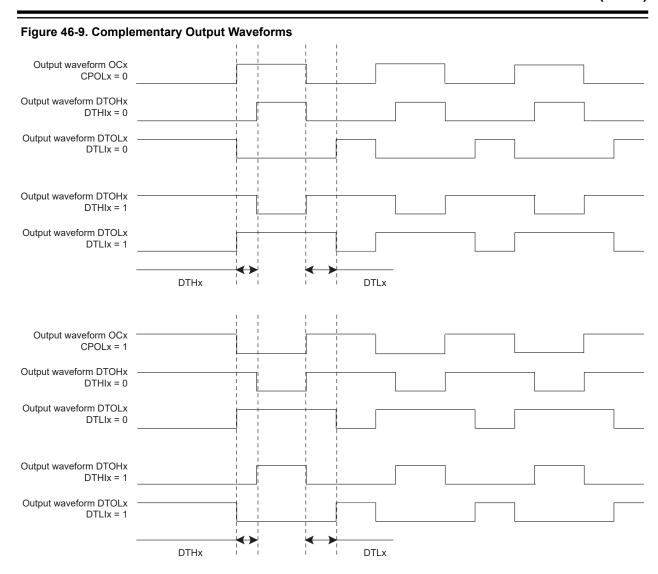

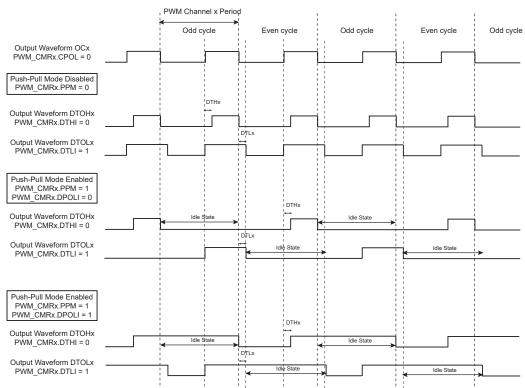

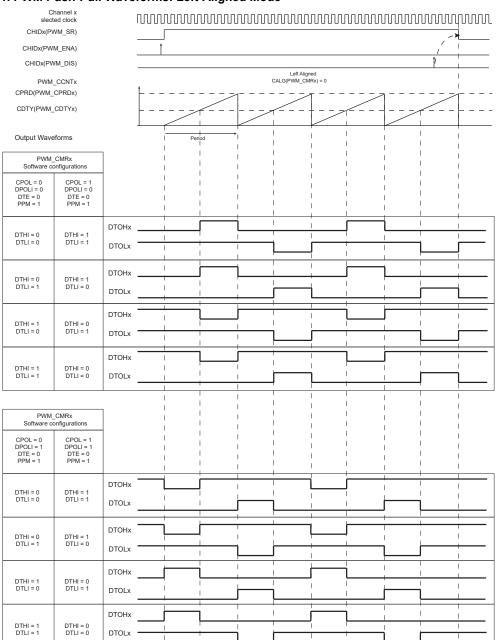

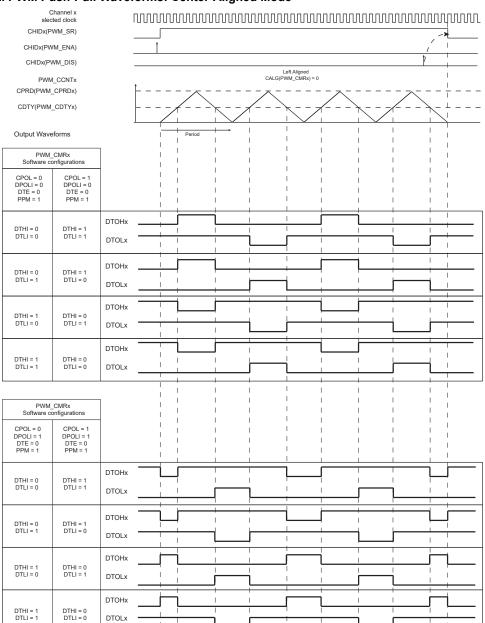

- 32.768 kHz crystal oscillator frequency monitor and failure detection

- Independent Dual Watchdog Timer (DWDT)

- · 12 MHz internal RC oscillator

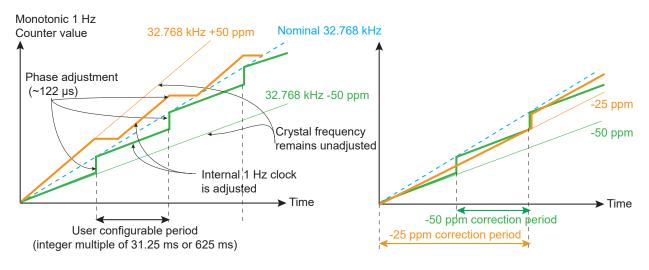

- Ultra-low-power Real-Time Clock (RTC) with Gregorian, Persian calendars and UTC mode, calibration circuitry to compensate the 32.768 kHz crystal drift with observability of compensated clock on output pin

- Peripheral and memory-to-memory DMA channels

- · Shared Peripherals

- Segmented LCD Controller (SLCDC)

- Static, ½, ¼ and ¼ bias

- Software-selectable LCD output voltage (contrast)

- · Can be used in Backup mode

- Communication Interfaces

- FLEXCOMs supporting U(S)ART, SPI, TWI/I2C with FIFOs

- Metrology-specific multi-channel SPI with legacy support

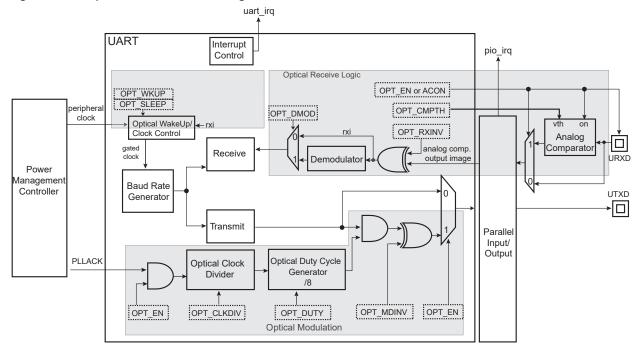

- Metrology-specific two-wire UARTs supporting optical transceiver providing an electrically-isolated serial communication with hand-held equipment, such as calibrators, compliant with ANSI-C12.18 or IEC62056-21 norms

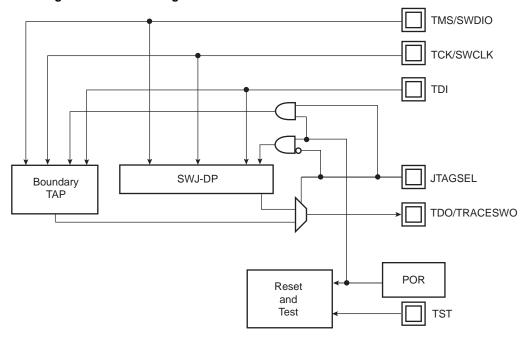

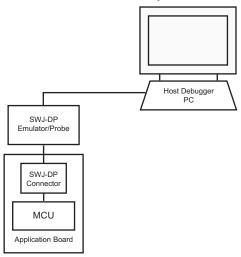

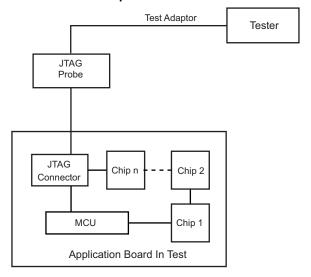

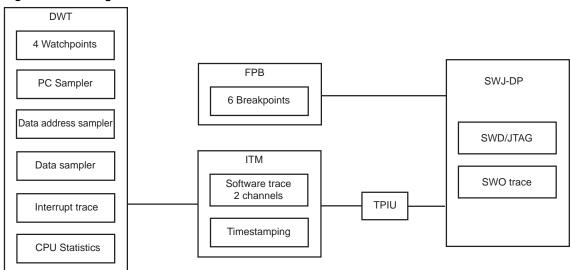

- Debugger Development Support

- Arm CoreSight<sup>™</sup> JTAG-DP or SW-DP debug port

- Wake-up from debug request

- Unlimited software breakpoints

- IEEE 1149.2-compatible (JTAG) boundary scan

- Analog Conversion Block

- 12-bit ADC module

- 1 Msps S/H ADC

- · Up to 8 channels

- Two analog comparators

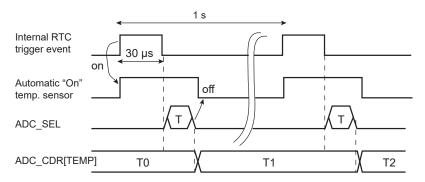

- Temperature sensor

- Closed-Circuit Voltage (CCV) measurement on battery voltage input rail (VBAT)

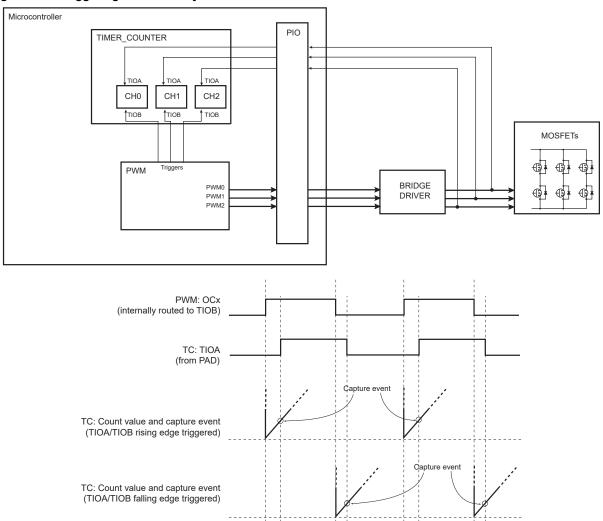

- Timers/Output Compare/Input Capture

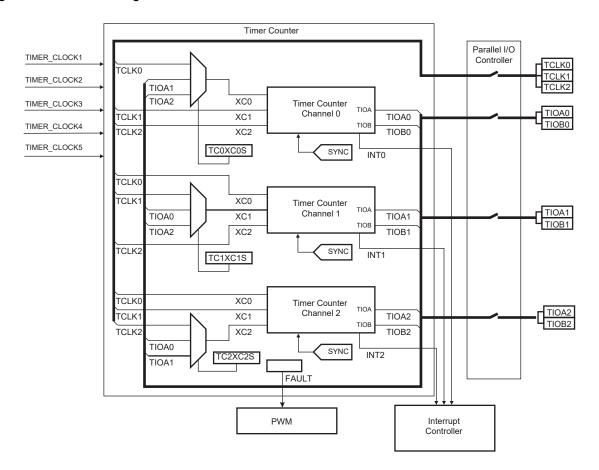

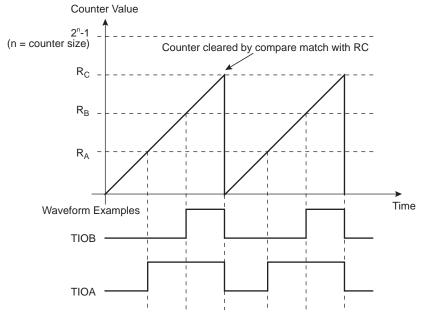

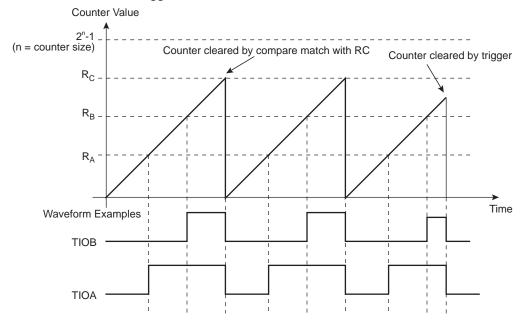

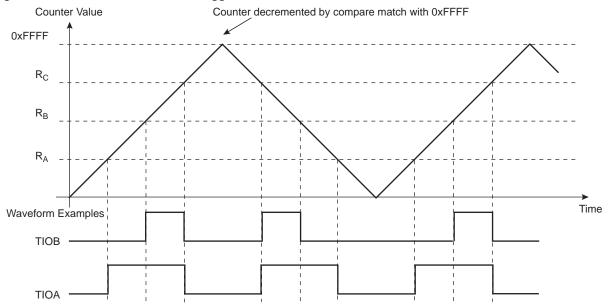

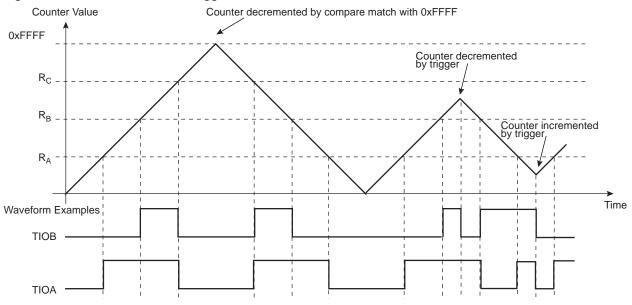

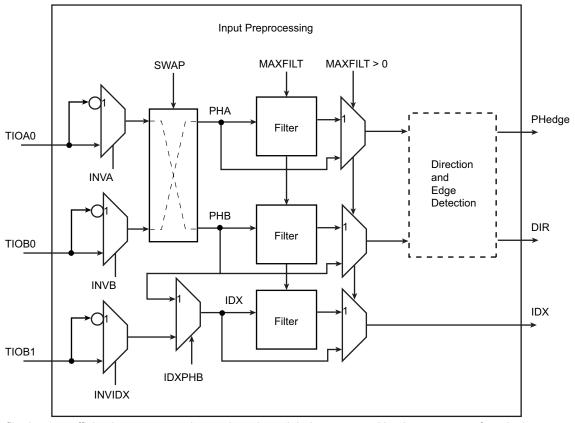

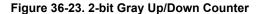

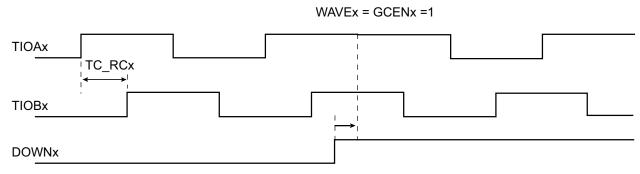

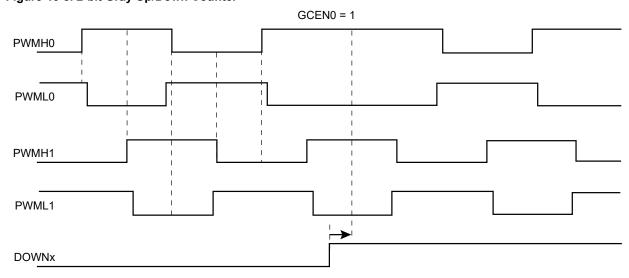

- 12-channel 32-bit Timer Counters (TC) with Capture, Waveform, Compare and basic PWM modes.

Quadrature decoder logic and 2-bit Gray up/down counter

- 3-channel, 24-bit PWM with complementary outputs, dead-time generator and external trigger modes

- I/O

- I/O lines with slew rate control to ease PCB design and EMC compliance, external interrupt capability (edge

or level sensitivity), Schmitt trigger, internal pull-up/pull-down, debouncing, glitch filtering and on-die series

resistor termination

- Software and Tools Support

- Microchip Smart Energy Framework Software Examples

- Microchip G3/PRIME/IEEE PLC Stacks

- Microchip MPLAB®-X & Harmony

- IAR Embedded WorkBench, Keil<sup>®</sup> μVision<sup>®</sup>

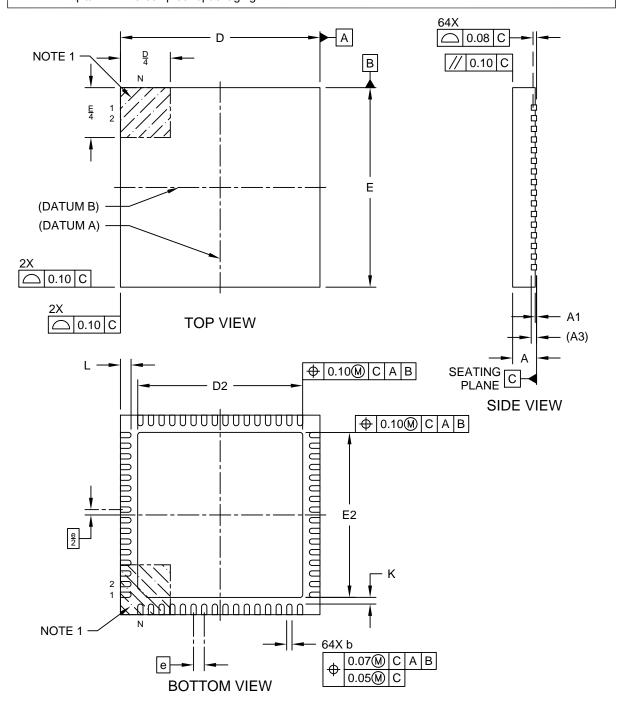

- Packages

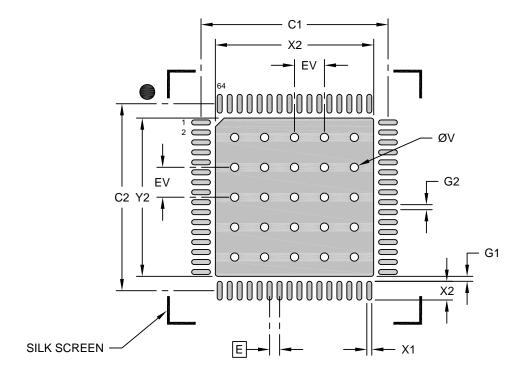

- 64-lead VQFN, 7.5 x 7.5 x 0.9 mm, pitch 0.4 mm

- 128-pin EP-TQFP, 14 x 14 x 1.0 mm, pitch 0.4 mm

- · Operating Conditions

- 2.25V to 3.6V, -40°C to 85°C

Note: Restrictions on range may apply. Refer to section Electrical Characteristics.

# **Table of Contents**

| Des | scription                               | 1  |

|-----|-----------------------------------------|----|

| Fea | atures                                  | 1  |

| 1.  | Block Diagram                           | 0  |

| 2.  | Configuration Summary                   | 13 |

| 3.  | Package and Pinout                      | 14 |

|     | 3.1. Pinout Topology                    | 14 |

|     | 3.2. Pinout and Multiplexing            |    |

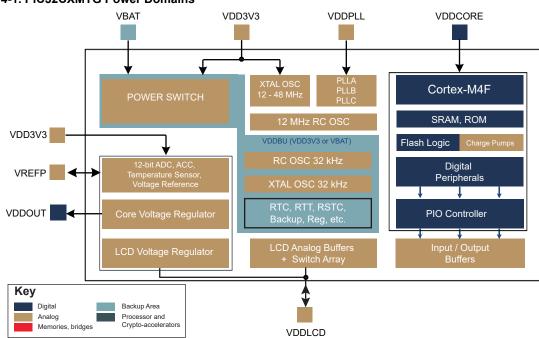

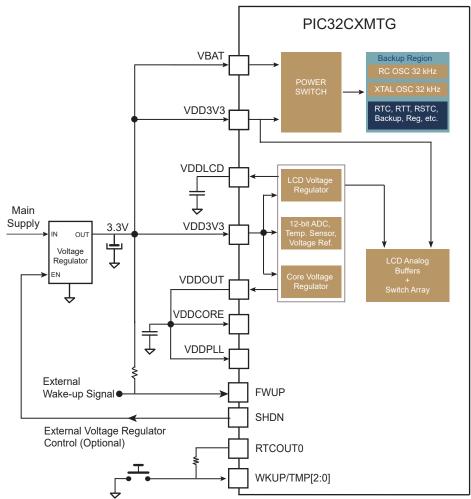

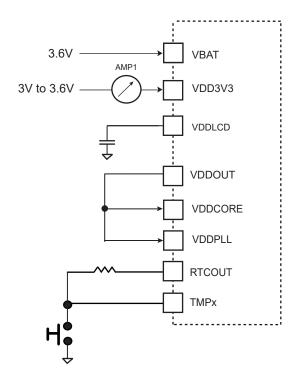

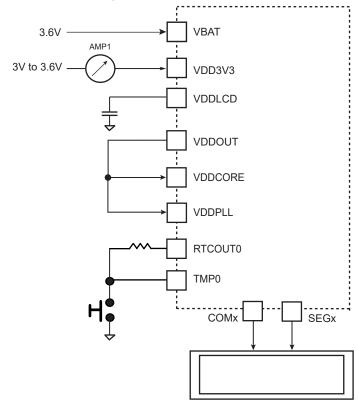

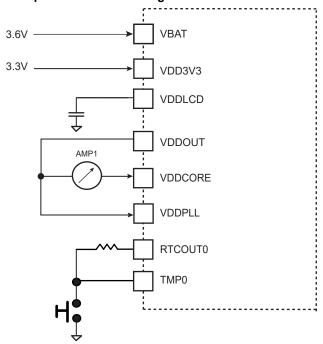

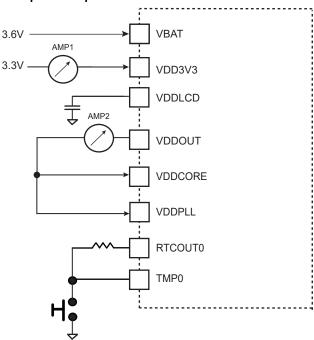

| 4.  | Power Supply and Power Control          | 24 |

|     | 4.1. Power Supplies                     | 24 |

|     | 4.2. System State                       | 28 |

|     | 4.3. Active Mode                        | 28 |

|     | 4.4. Low-Power Modes                    | 29 |

| 5.  | Input/Output Lines                      | 34 |

|     | 5.1. General Purpose I/O Lines          | 34 |

|     | 5.2. TST Pin                            |    |

|     | 5.3. NRST Pin                           | 34 |

|     | 5.4. Anti-Tamper (TMPx) Pins            | 34 |

|     | 5.5. RTCOUTx Pins                       | 34 |

|     | 5.6. Shutdown (SHDN) Pin                | 34 |

|     | 5.7. Force Wake-up (FWUP) Pin           | 35 |

|     | 5.8. Flash Memory Hardware ERASE Signal | 35 |

| 6.  | Core and Interconnect                   | 36 |

|     | 6.1. Cortex-M4 Processor                |    |

| 7.  | Product Mapping and Peripheral Access   | 38 |

| 8.  | Memories                                | 42 |

| ٥.  | 8.1. Embedded Memories                  |    |

|     | 8.2. External Memories                  |    |

| 9.  | Safety and Security Features            | 45 |

|     | 9.1. Design for Safety                  |    |

|     | 9.2. Design for Security                |    |

| 10  | Real-Time Event Management              | 48 |

|     | 10.1. Real-Time Event Mapping List      |    |

| 4.4 |                                         |    |

| 11. | Peripherals                             |    |

|     | 11.1. Peripheral Identifiers            |    |

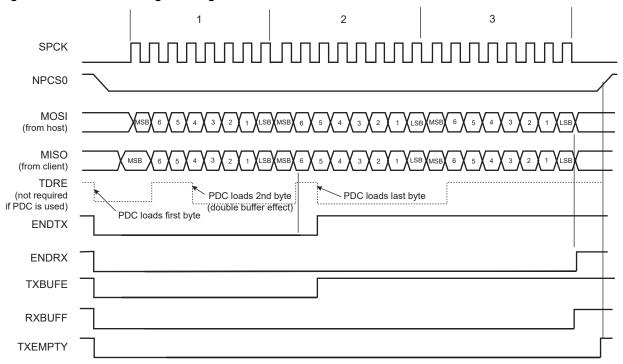

|     | 11.2. Peripheral DMA Controller (PDC)   | 52 |

| 12. | Cortex-M4 Processor (Arm)               | 55 |

|     | 12.1.  | Description                            | 55  |

|-----|--------|----------------------------------------|-----|

|     | 12.2.  | Reference Documents                    | 55  |

|     | 12.3.  | Embedded Characteristics               | 55  |

| 13. | Flash  | Programming, Debug and Test Features   | 57  |

|     | 13.1.  | Flash Programming Sequence             | 57  |

|     |        | Description                            |     |

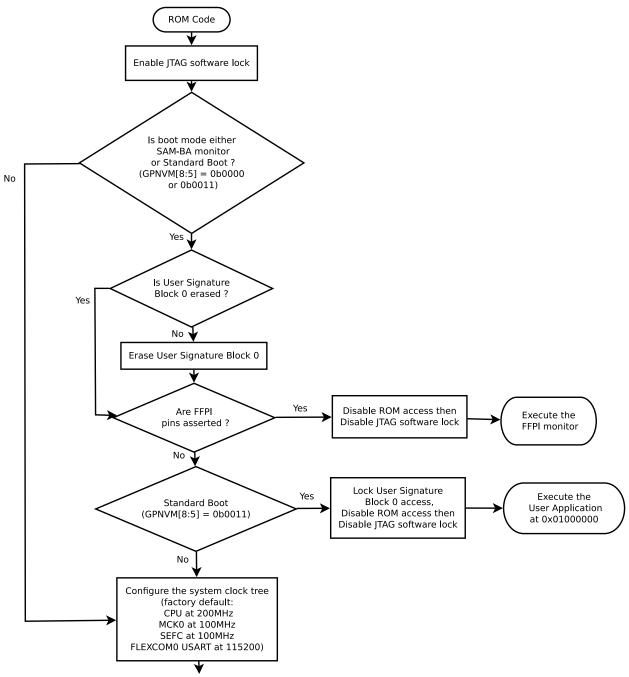

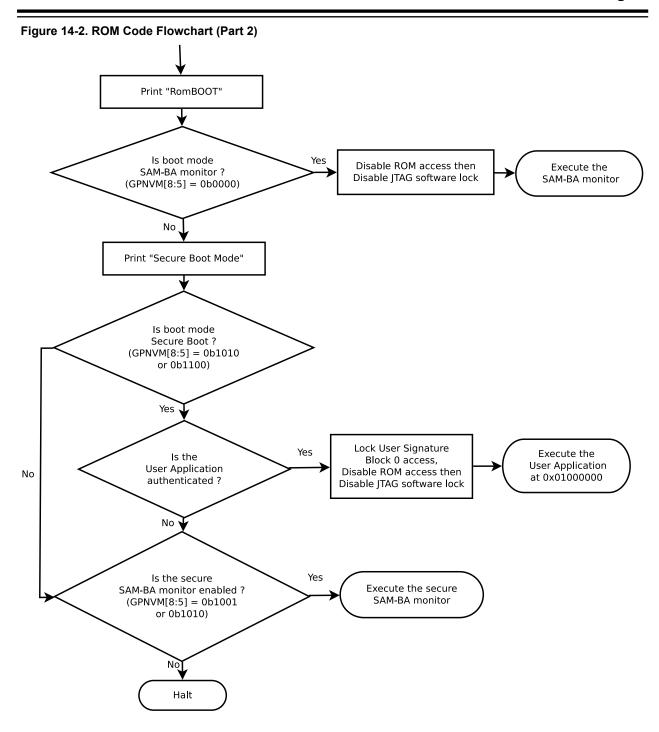

| 14. | ROM    | Code and Boot Strategies               | 65  |

|     |        | Description                            |     |

|     |        | Functional Description                 |     |

|     |        | Secure Boot Mode                       |     |

|     |        | SAM-BA Monitors                        |     |

|     |        | FFPI Monitor                           |     |

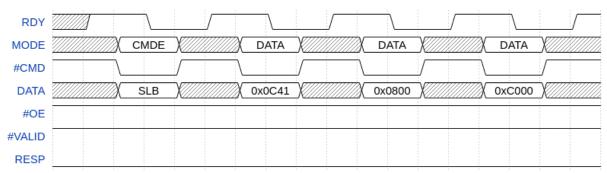

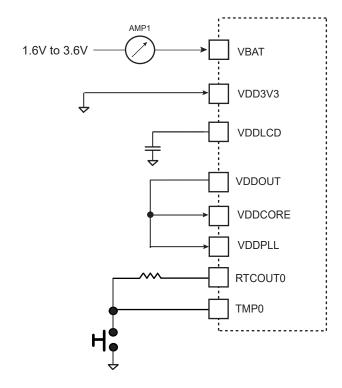

| 15. | Suppl  | ly Controller (SUPC)                   | 90  |

|     | 15.1.  | Description                            | 90  |

|     | 15.2.  | Embedded Characteristics               | 90  |

|     | 15.3.  | Block Diagram                          | 91  |

|     | 15.4.  | Functional Description                 | 92  |

|     | 15.5.  | Register Summary                       | 102 |

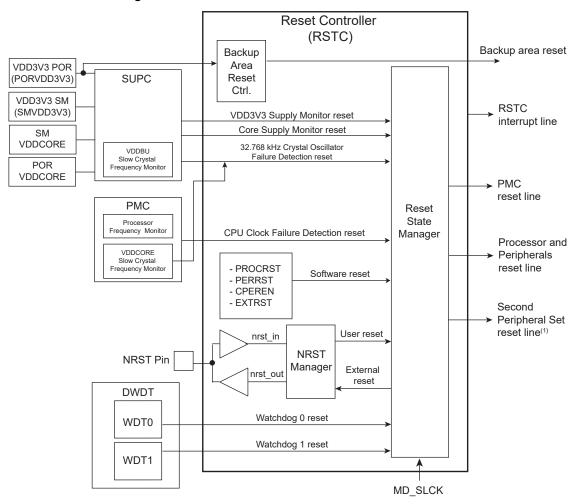

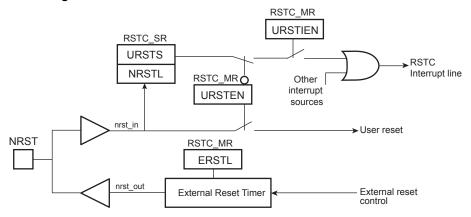

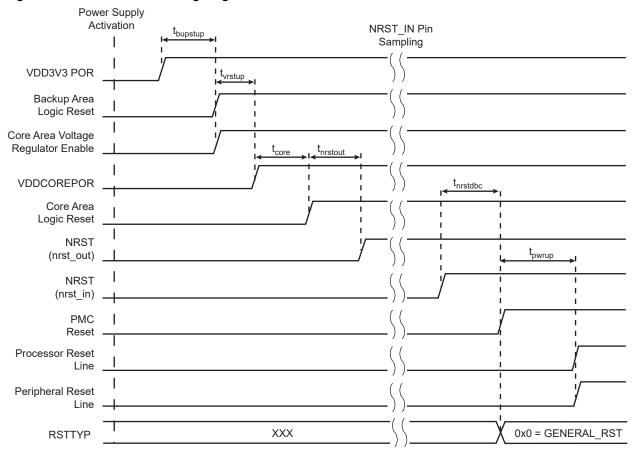

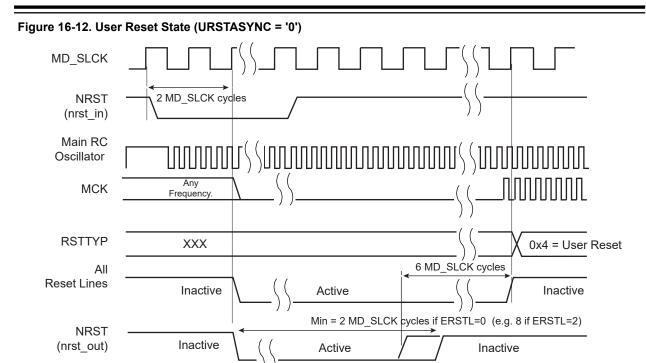

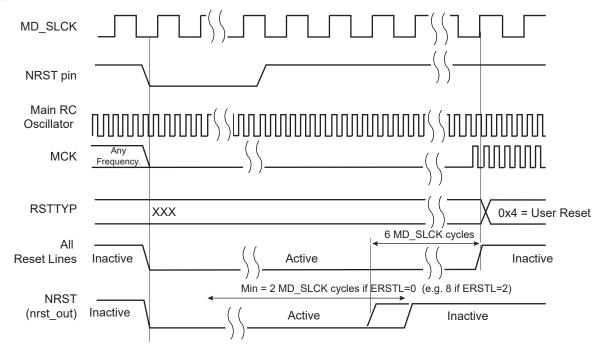

| 16. | Reset  | t Controller (RSTC)                    | 124 |

|     | 16.1.  | Description                            | 124 |

|     | 16.2.  | Embedded Characteristics               | 124 |

|     | 16.3.  | Block Diagram                          | 125 |

|     | 16.4.  | Functional Description                 | 125 |

|     | 16.5.  | Register Summary                       | 137 |

| 17. | Syste  | m Controller Write Protection (SYSCWP) | 143 |

|     | 17.1.  | Functional Description                 | 143 |

|     | 17.2.  | Register Summary                       | 145 |

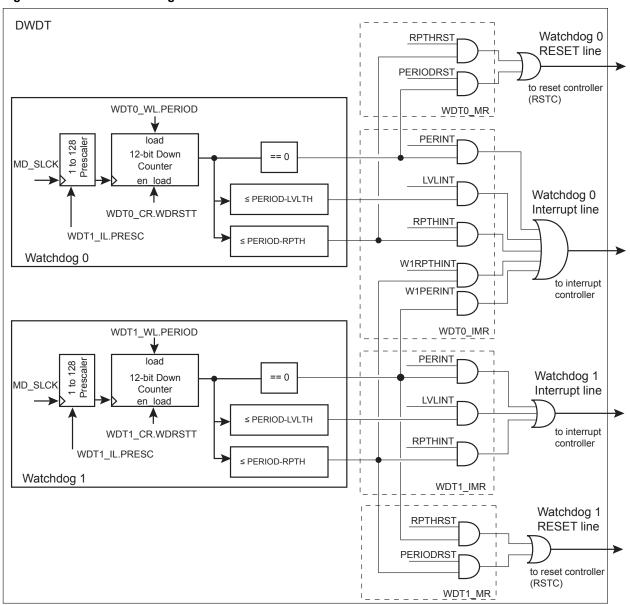

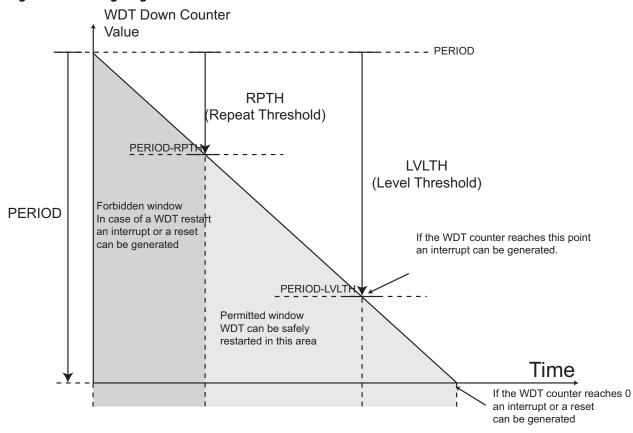

| 18. | Dual \ | Watchdog Timer (DWDT)                  | 148 |

|     | 18.1.  | Description                            | 148 |

|     |        | Embedded Characteristics               | 148 |

|     | 18.3.  | Block Diagram                          | 149 |

|     | 18.4.  | Functional Description                 | 149 |

|     | 18.5.  | Register Summary                       | 152 |

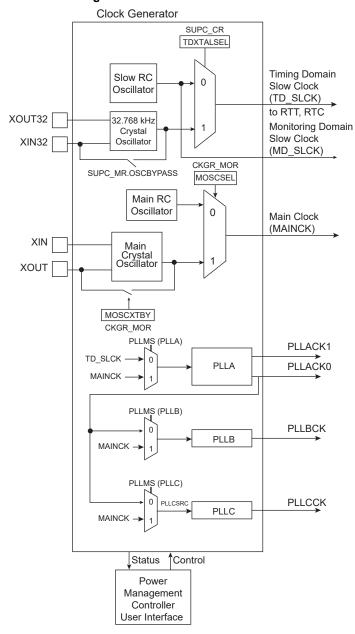

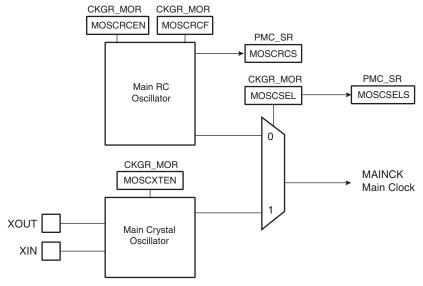

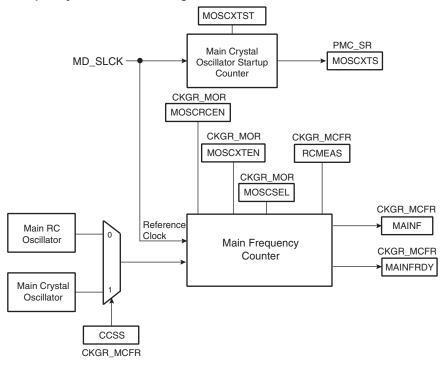

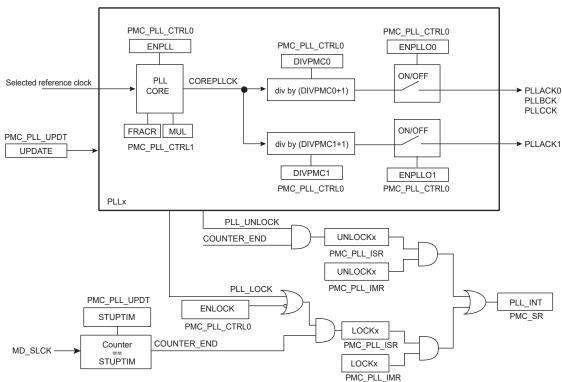

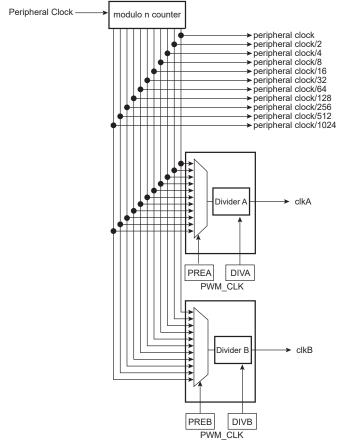

| 19. | Clock  | Generator                              | 181 |

|     | 19.1.  | Description                            | 181 |

|     | 19.2.  | Embedded Characteristics               | 181 |

|     | 19.3.  | Block Diagram                          | 182 |

|     | 19.4.  | Slow Clock                             | 182 |

|     | 19.5.  | Main Clock                             | 183 |

|     |        | PLL Controls                           |     |

| 20. | Powe   | r Management Controller (PMC)          | 190 |

|     | 20.1.  | Description                            | 190 |

|     | 20.2. Embedded Characteristics                         | 190 |

|-----|--------------------------------------------------------|-----|

|     | 20.3. Block Diagram                                    | 191 |

|     | 20.4. Processor Clock Controller                       | 191 |

|     | 20.5. Free-running Processor Clock                     | 192 |

|     | 20.6. Peripheral and Generic Clock Controller          | 192 |

|     | 20.7. SysTick Clock                                    | 192 |

|     | 20.8. Programmable Clock Output Controller             | 193 |

|     | 20.9. Ultra Low Power Modes and Fast Start-up          | 193 |

|     | 20.10. Asynchronous Partial Wake-Up                    | 194 |

|     | 20.11. Start-up from Embedded Flash                    | 196 |

|     | 20.12. Main Crystal Oscillator Failure Detection       | 196 |

|     | 20.13. 32.768 kHz Crystal Oscillator Frequency Monitor | 197 |

|     | 20.14. MCK0 Frequency Monitor                          | 198 |

|     | 20.15. Recommended Programming Sequence                | 198 |

|     | 20.16. Clock Switching Details                         | 199 |

|     | 20.17. Register Write Protection                       | 200 |

|     | 20.18. Register Summary                                | 202 |

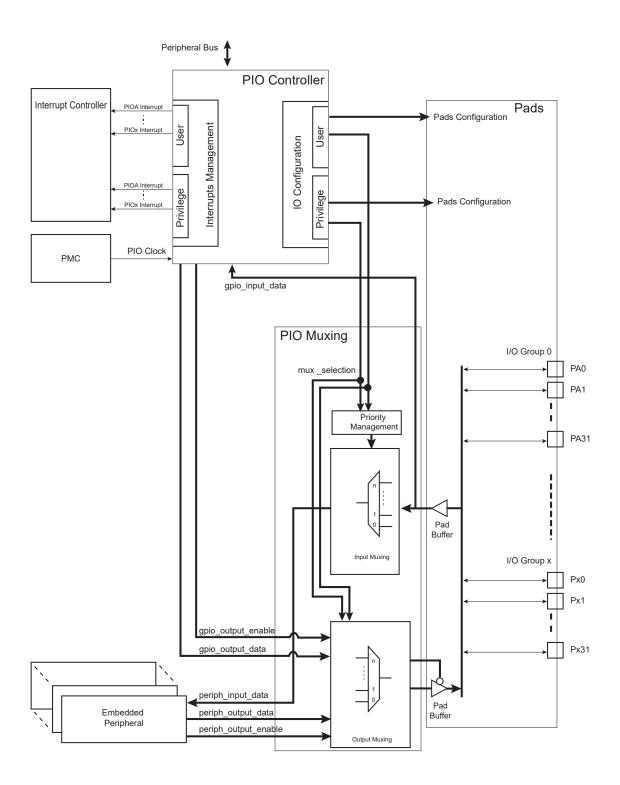

| 21. | Parallel Input/Output Controller (PIO)                 | 253 |

|     | 21.1. Description                                      | 253 |

|     | 21.2. Embedded Characteristics                         |     |

|     | 21.3. Block Diagram                                    |     |

|     | 21.4. Product Dependencies                             |     |

|     | 21.5. Functional Description                           |     |

|     | 21.6. I/O Lines Programming Example                    |     |

|     | 21.7. Register Summary                                 |     |

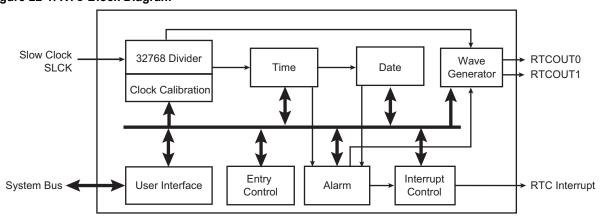

| 22. | Real-Time Clock (RTC)                                  | 313 |

|     | 22.1. Description                                      | 313 |

|     | 22.2. Embedded Characteristics                         |     |

|     | 22.3. Block Diagram                                    |     |

|     | 22.4. Product Dependencies                             |     |

|     | 22.5. Functional Description.                          |     |

|     | 22.6. Register Summary                                 |     |

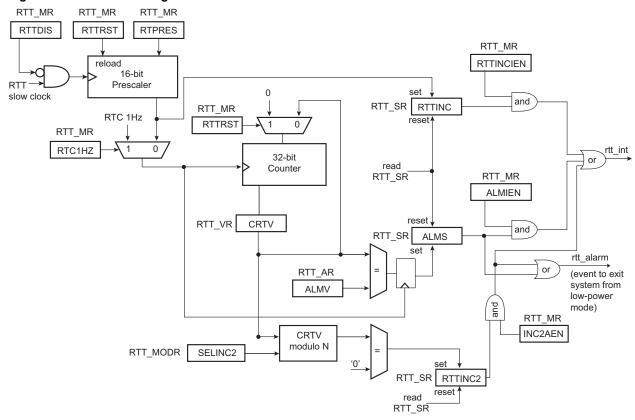

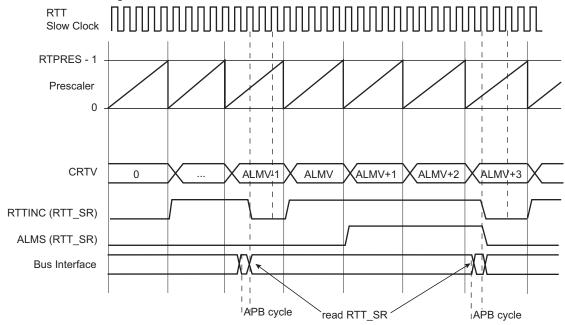

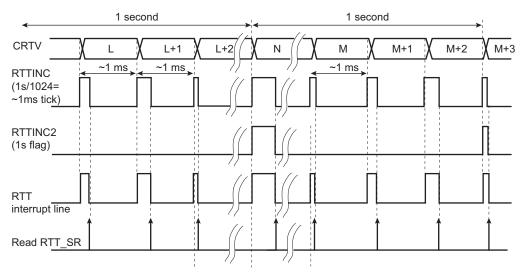

| 23. | Real-time Timer (RTT)                                  | 360 |

|     | 23.1. Description                                      |     |

|     | 23.2. Embedded Characteristics                         |     |

|     | 23.3. Block Diagram                                    |     |

|     | 23.4. Functional Description                           |     |

|     | 23.5. Register Summary                                 |     |

| 24. | General Purpose Backup Registers (GPBR)                | 370 |

|     | 24.1. Description                                      |     |

|     | 24.2. Embedded Characteristics                         |     |

|     | 24.3. Register Summary                                 |     |

| 25  | Special Function Registers (SFR)                       | 374 |

|     | 25.1. Description                                      |     |

|     | 20.1. D00011pti011                                     |     |

|     | 25.2.  | Embedded Characteristics             | 374 |

|-----|--------|--------------------------------------|-----|

|     | 25.3.  | Functional Description               | 374 |

|     | 25.4.  | Register Summary                     | 375 |

| 26. | Specia | al Function Registers Backup (SFRBU) | 382 |

|     | 26.1.  | Description                          | 382 |

|     | 26.2.  | Embedded Characteristics             | 382 |

|     | 26.3.  | Functional Description               | 382 |

|     | 26.4.  | Register Summary                     | 383 |

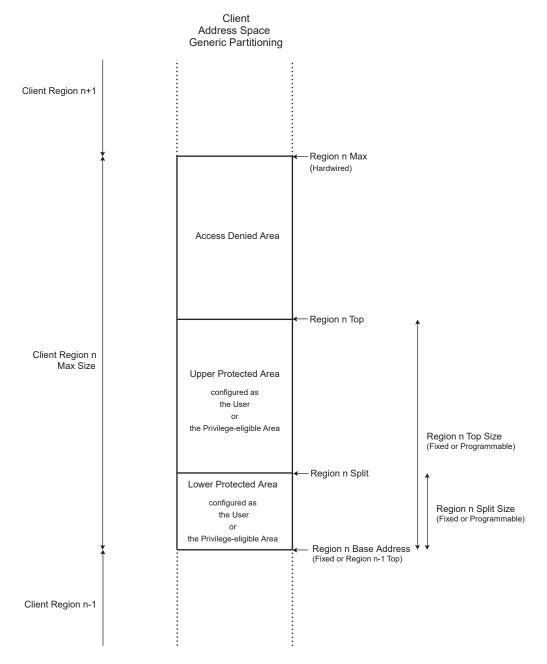

| 27. | Bus M  | latrix (MATRIX)                      | 389 |

|     | 27.1.  | Description                          | 389 |

|     | 27.2.  | Embedded Characteristics             | 392 |

|     | 27.3.  | Memory Mapping                       | 393 |

|     | 27.4.  | Special Bus Granting Techniques      | 393 |

|     |        | No Default Host                      |     |

|     | 27.6.  | Last Access Host                     | 394 |

|     | 27.7.  | Fixed Default Host                   | 394 |

|     | 27.8.  | Arbitration                          | 394 |

|     | 27.9.  | Register Write Protection            | 396 |

|     |        | Privilege Protection of AHB and APB  |     |

|     | 27.11. | Register Summary                     | 406 |

| 28. | Chip I | dentifier (CHIPID)                   | 431 |

|     | 28.1.  | Description                          | 431 |

|     |        | Embedded Characteristics             |     |

|     | 28.3.  | Register Summary                     | 432 |

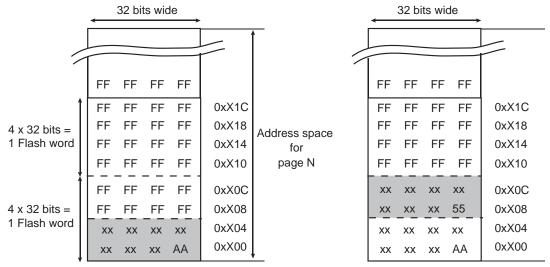

| 29. | Secur  | e Embedded Flash Controller (SEFC)   | 436 |

|     |        | Description                          |     |

|     |        | Embedded Characteristics             |     |

|     |        | Product Dependencies                 |     |

|     |        | Functional Description               |     |

|     |        | Register Summary                     |     |

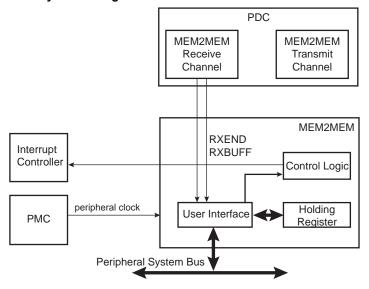

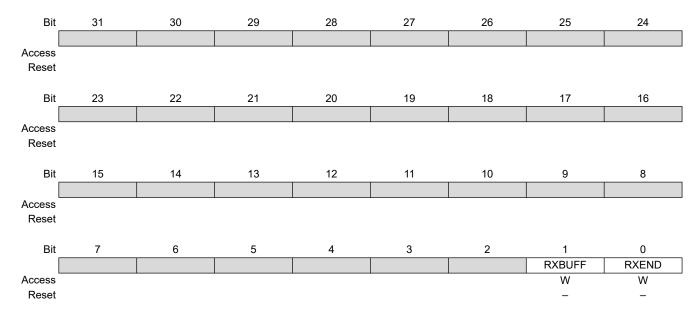

| 30. | Memo   | ry to Memory (MEM2MEM)               | 469 |

|     |        | Description.                         |     |

|     |        | Embedded Characteristics             |     |

|     |        | Block Diagram                        |     |

|     |        | Product Dependencies.                |     |

|     |        | Functional Description               |     |

|     |        | Register Write Protection            |     |

|     |        | Register Summary                     |     |

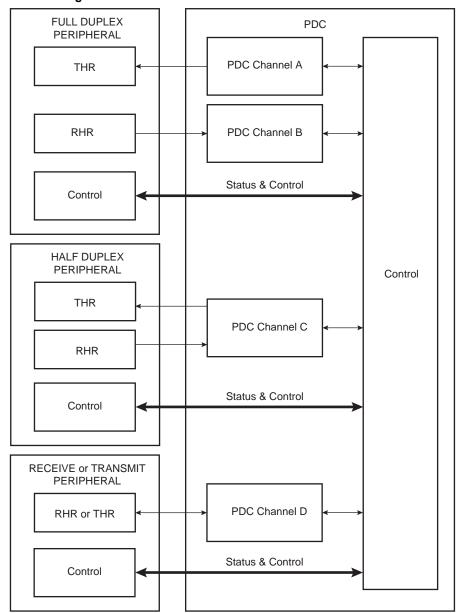

| 31. | Periph | neral DMA Controller (PDC)           | 479 |

|     | -      | Description                          |     |

|     |        | Embedded Characteristics             |     |

|     |        | Block Diagram                        |     |

|     |        | Functional Description               |     |

|     | U 1.4  | 1 UTIVITOTIUT DUJUTUUTI              |     |

|     | 31.5.  | Register Summary                              | 483 |

|-----|--------|-----------------------------------------------|-----|

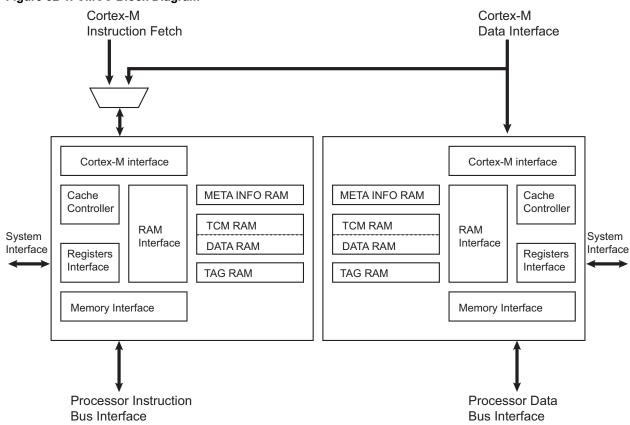

| 32. | Corte  | x-M Cache Controller (CMCC)                   | 496 |

|     | 32.1.  | Description                                   | 496 |

|     | 32.2.  | Embedded Characteristics                      | 496 |

|     | 32.3.  | Block Diagram                                 | 497 |

|     | 32.4.  | Functional Description                        | 497 |

|     | 32.5.  | Register Summary                              | 499 |

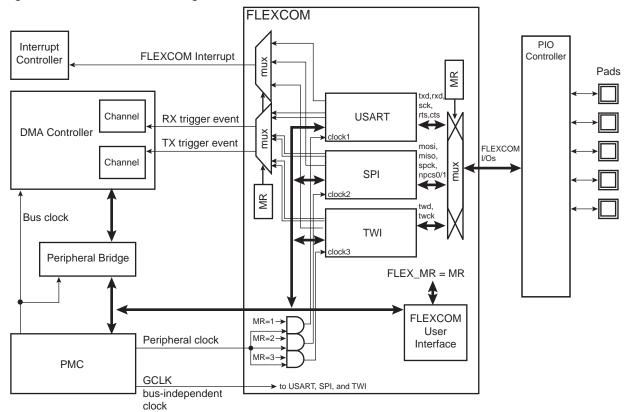

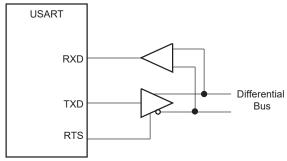

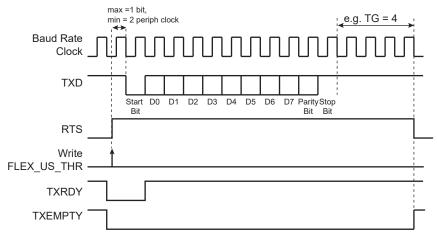

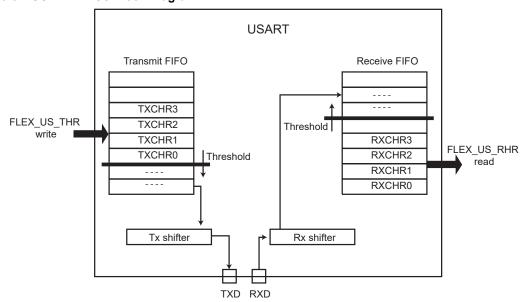

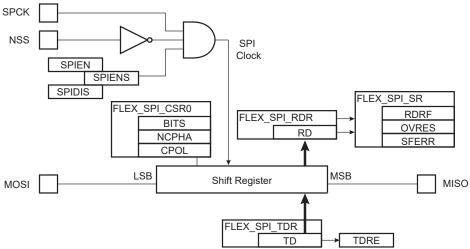

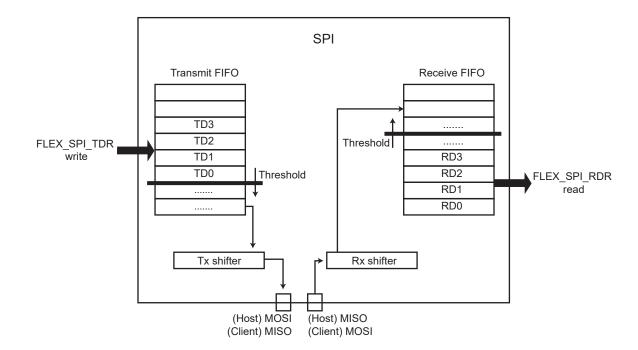

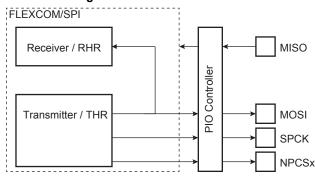

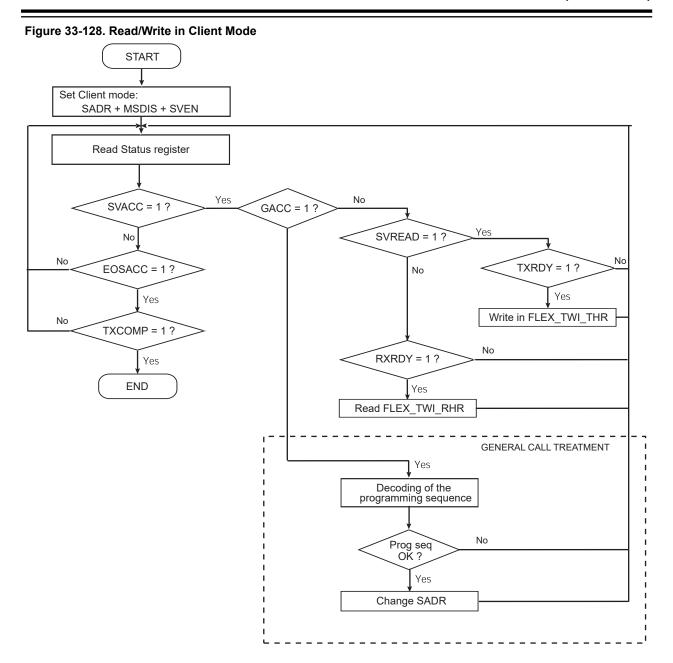

| 33. | Flexib | ole Serial Communication Controller (FLEXCOM) | 513 |

|     | 33.1.  | Description                                   | 513 |

|     | 33.2.  | Embedded Characteristics                      | 514 |

|     | 33.3.  | Block Diagram                                 | 516 |

|     | 33.4.  | I/O Lines Description                         | 516 |

|     | 33.5.  | Product Dependencies                          | 517 |

|     | 33.6.  | Register Accesses                             | 517 |

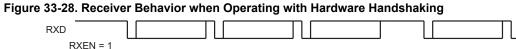

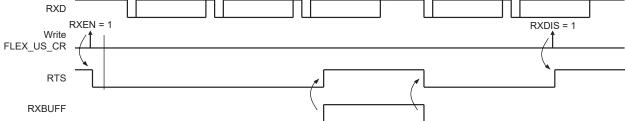

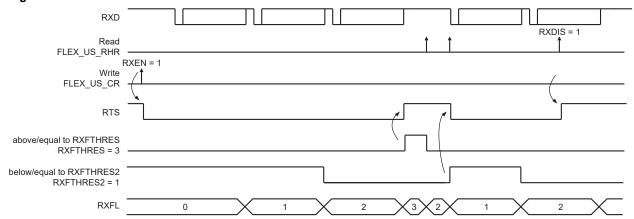

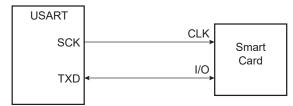

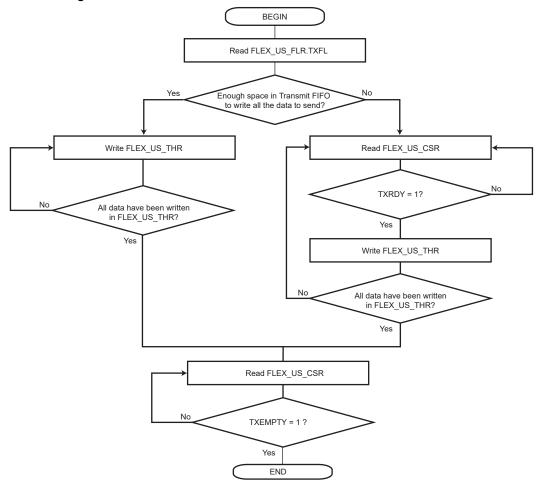

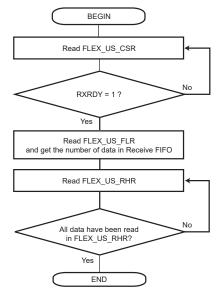

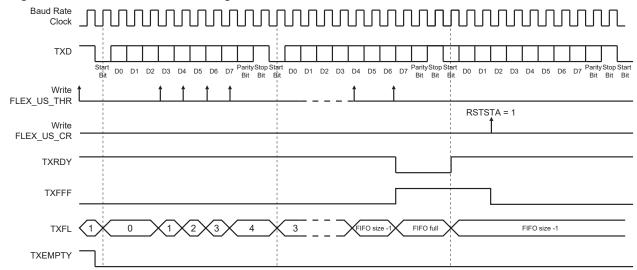

|     | 33.7.  | USART Functional Description                  | 517 |

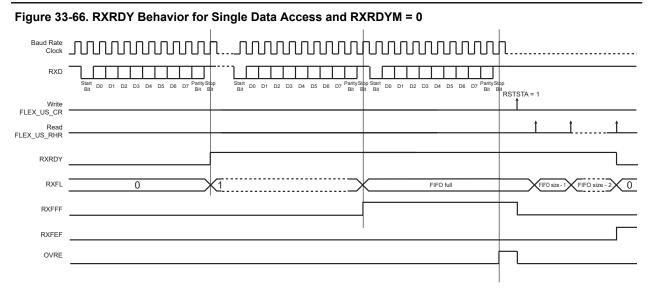

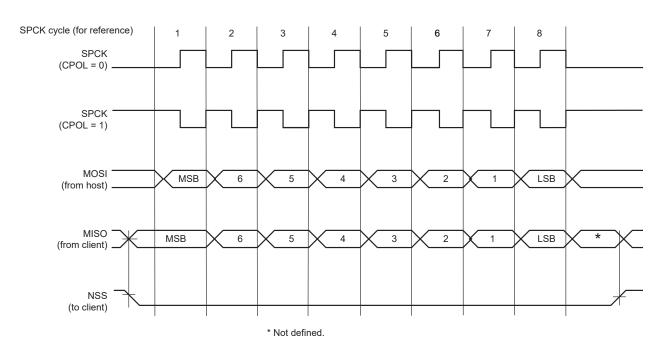

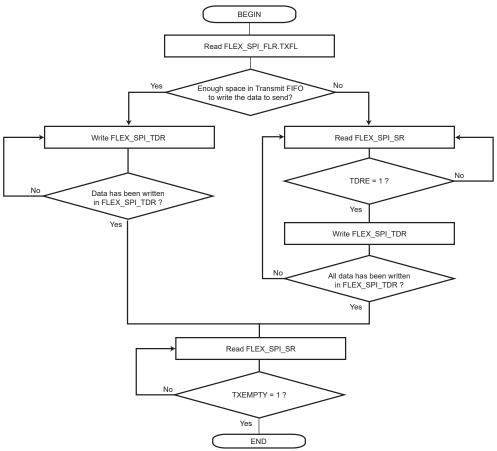

|     | 33.8.  | SPI Functional Description                    | 564 |

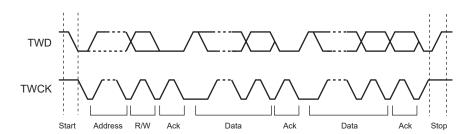

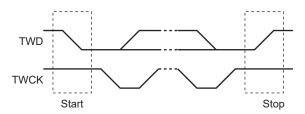

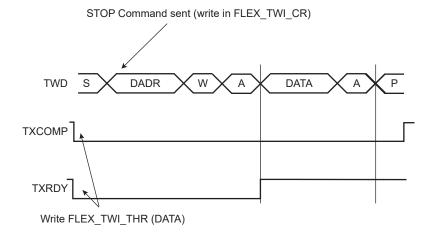

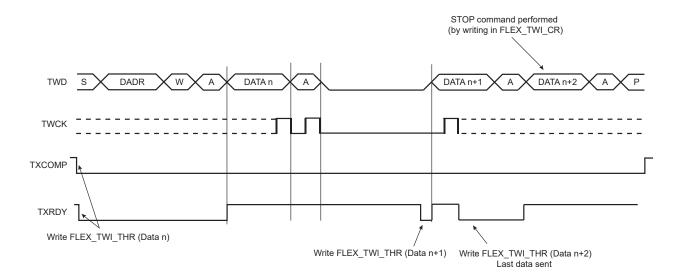

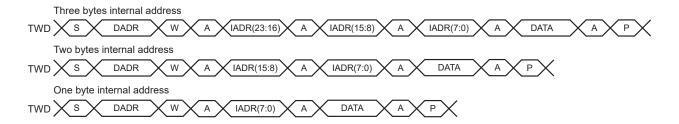

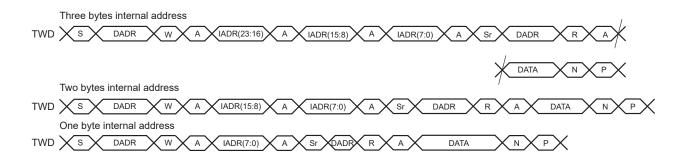

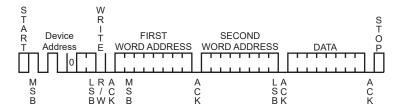

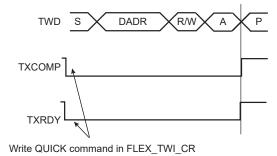

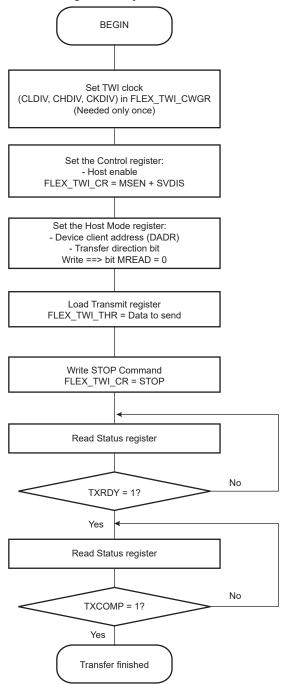

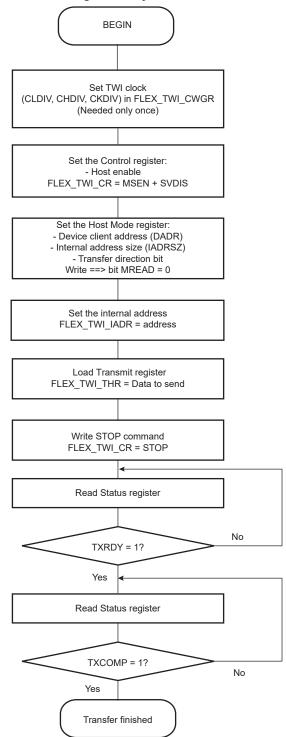

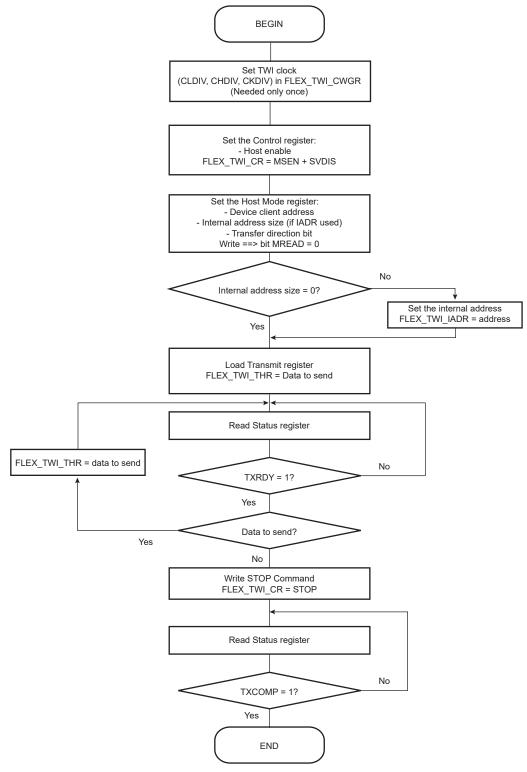

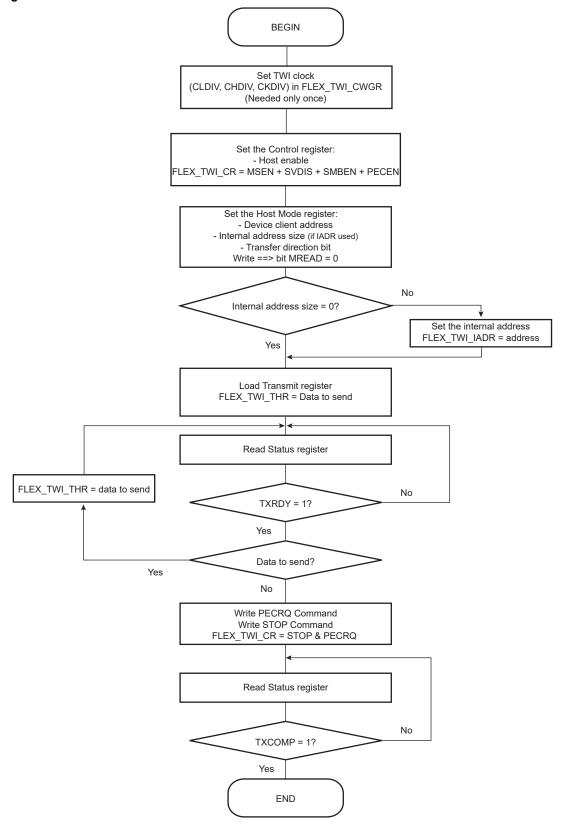

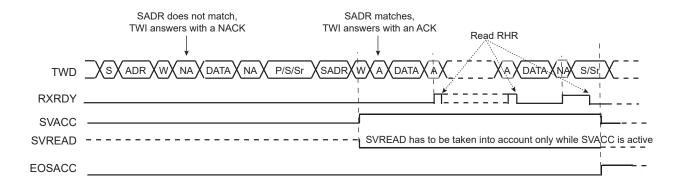

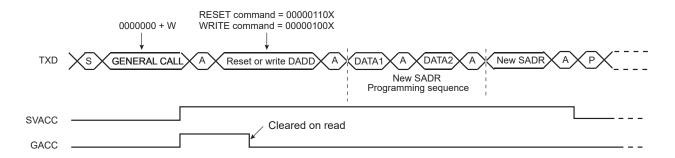

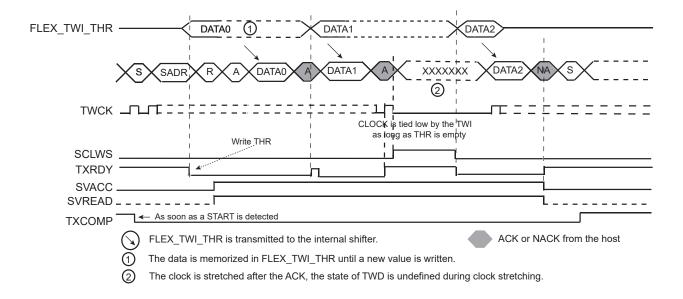

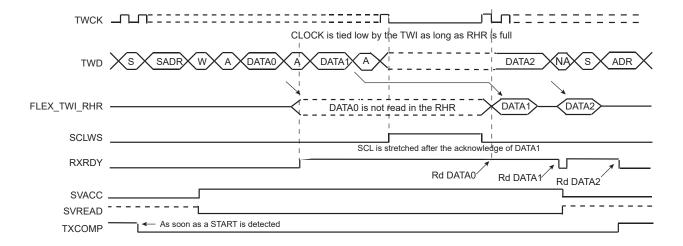

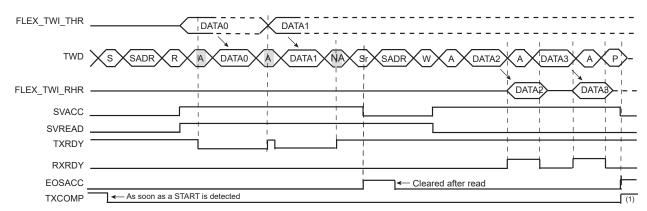

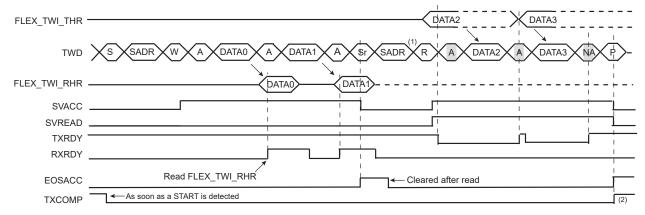

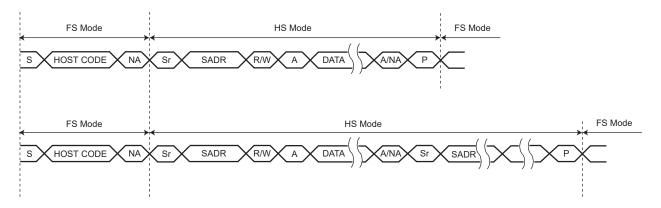

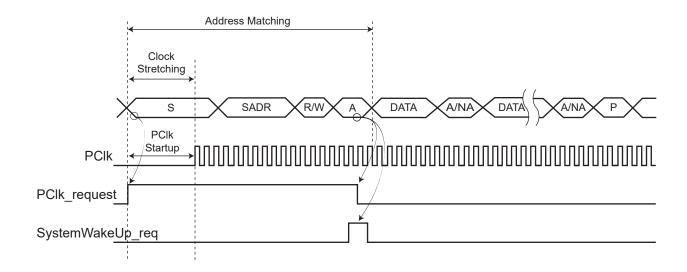

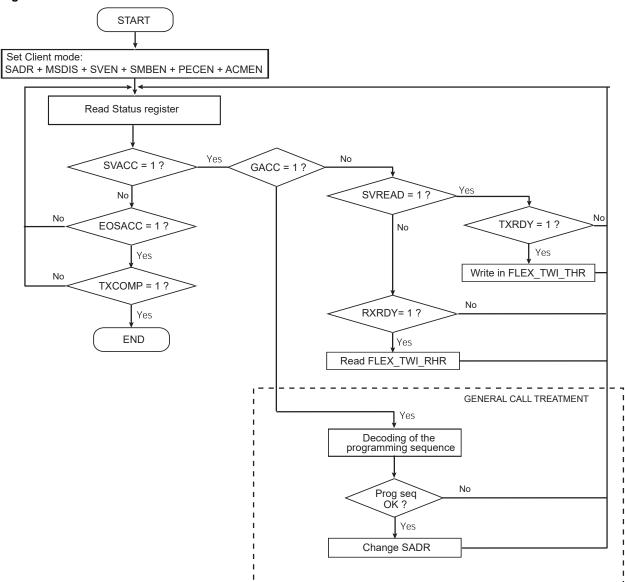

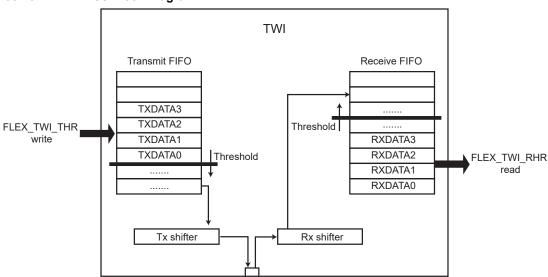

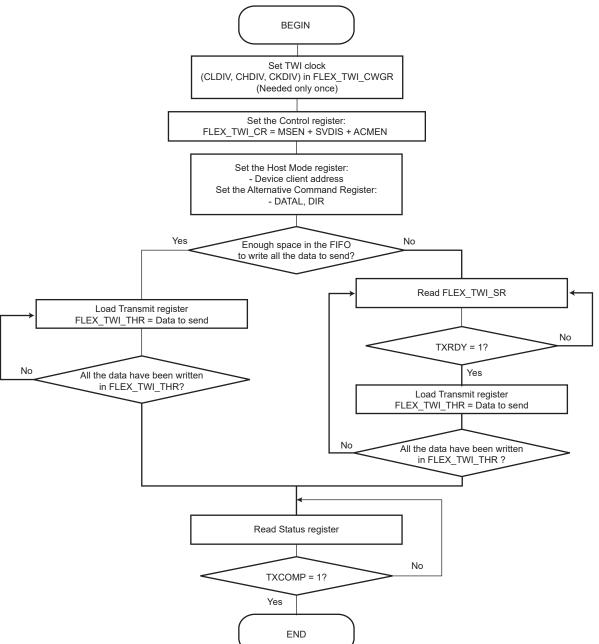

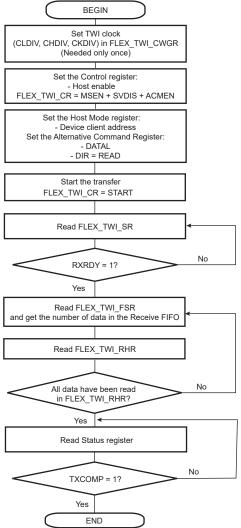

|     | 33.9.  | TWI Functional Description                    | 586 |

|     | 33.10  | . Register Summary                            | 635 |

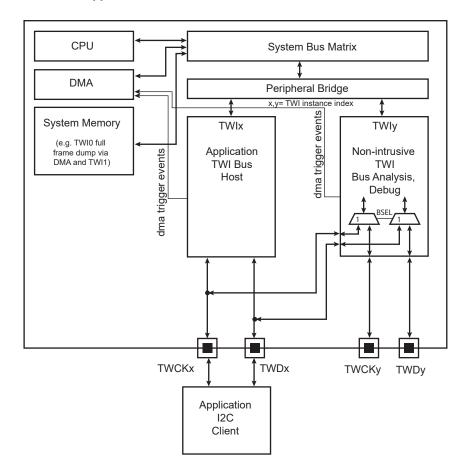

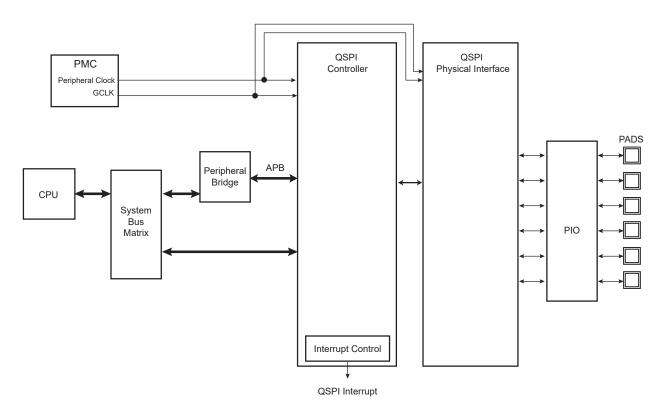

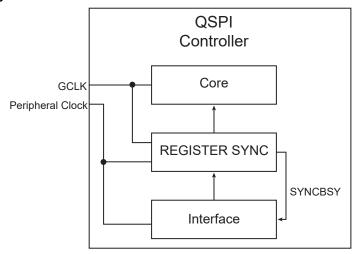

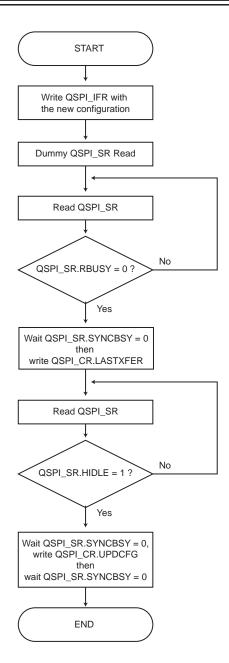

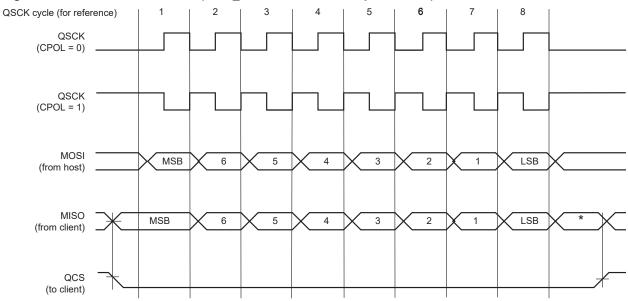

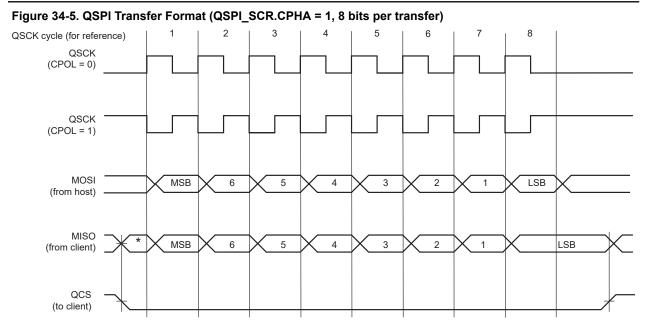

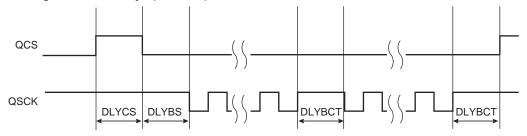

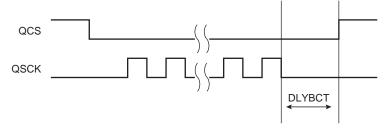

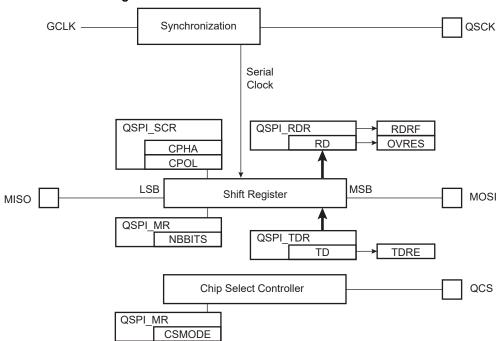

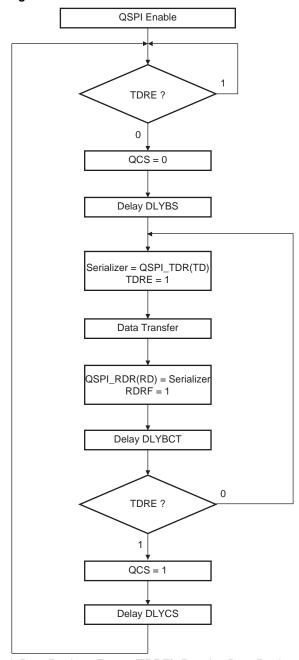

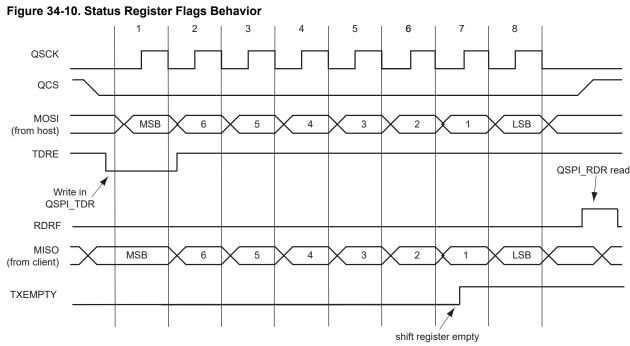

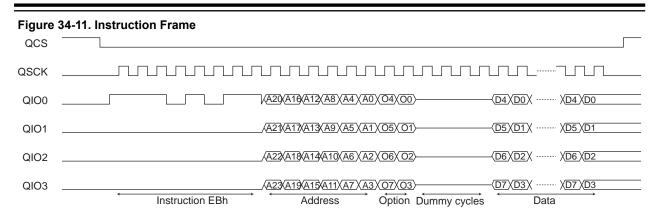

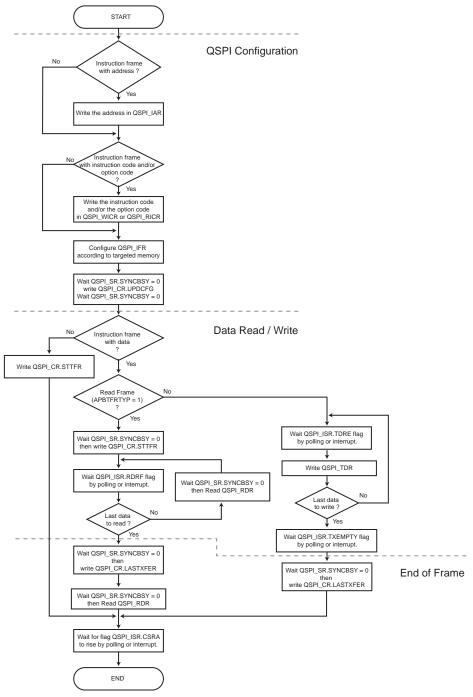

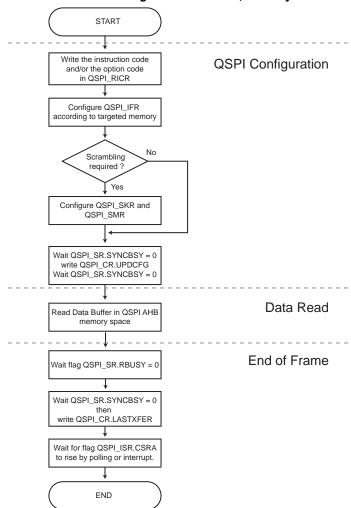

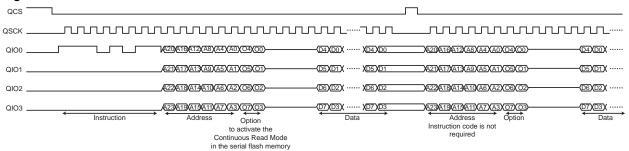

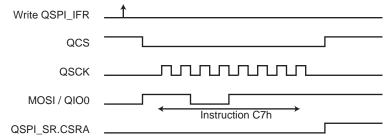

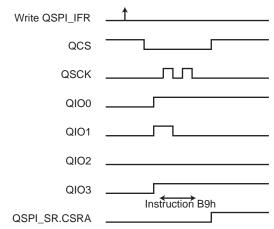

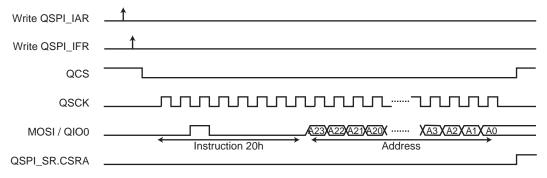

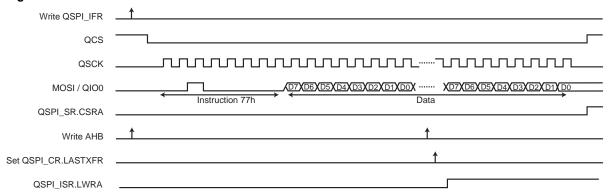

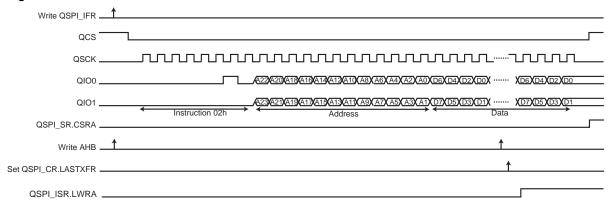

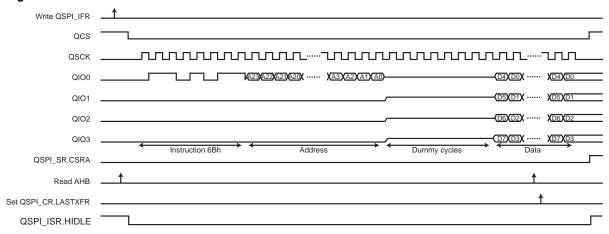

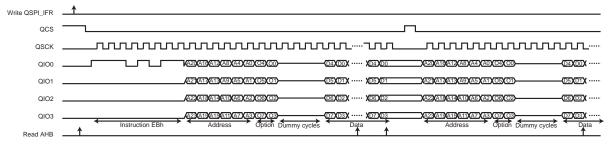

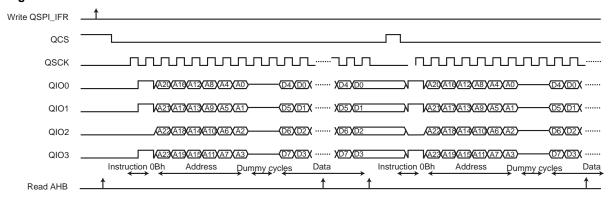

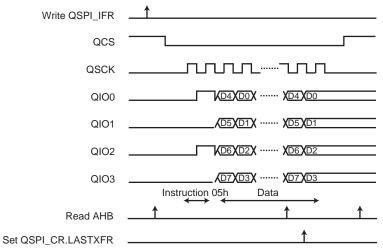

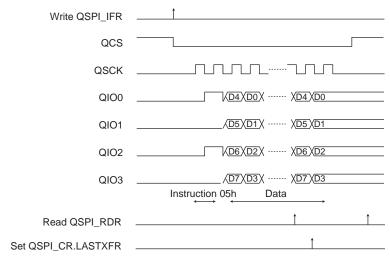

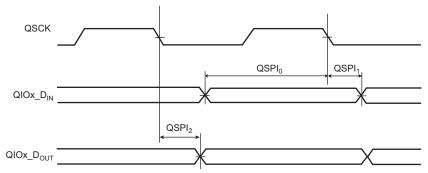

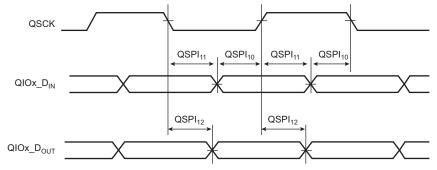

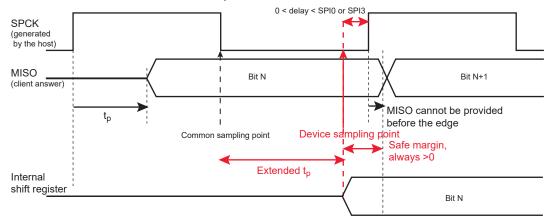

| 34. | Quad   | Serial Peripheral Interface (QSPI)            | 772 |

|     | 34.1.  | Description                                   | 772 |

|     | 34.2.  | Embedded Characteristics                      | 772 |

|     | 34.3.  | Block Diagram                                 | 773 |

|     | 34.4.  | Signal Description                            | 773 |

|     | 34.5.  | Product Dependencies                          | 774 |

|     | 34.6.  | Functional Description                        | 774 |

|     | 34.7.  | Register Summary                              | 799 |

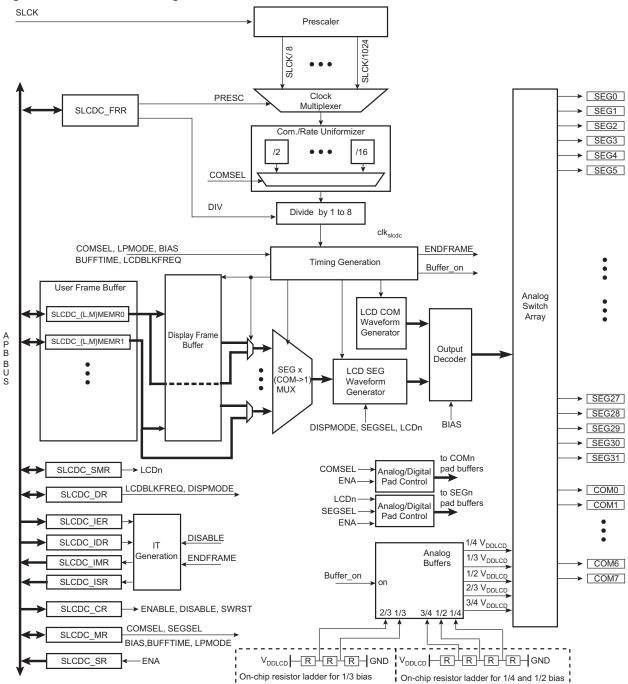

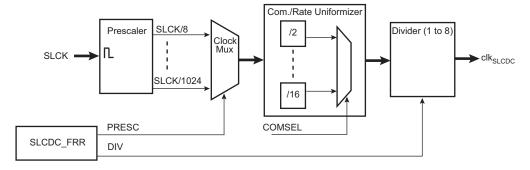

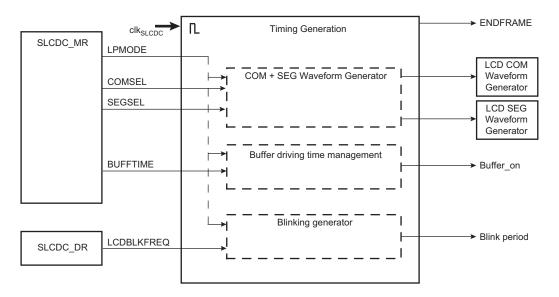

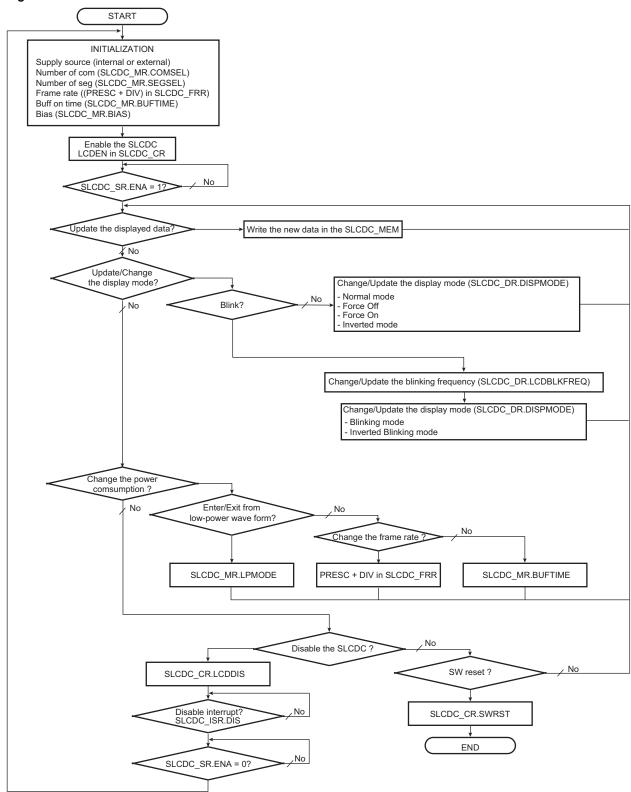

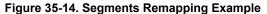

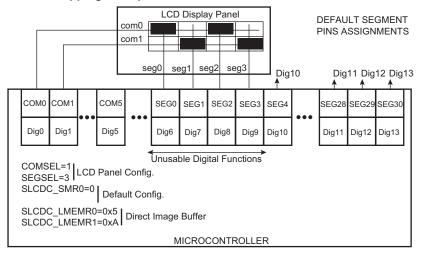

| 35. | Segm   | ent LCD Controller (SLCDC)                    | 830 |

|     | 35.1.  | Description                                   | 830 |

|     | 35.2.  | Embedded Characteristics                      | 830 |

|     | 35.3.  | Block Diagram                                 | 831 |

|     | 35.4.  | I/O Lines Description                         | 832 |

|     | 35.5.  | Product Dependencies                          | 832 |

|     | 35.6.  | Functional Description                        | 832 |

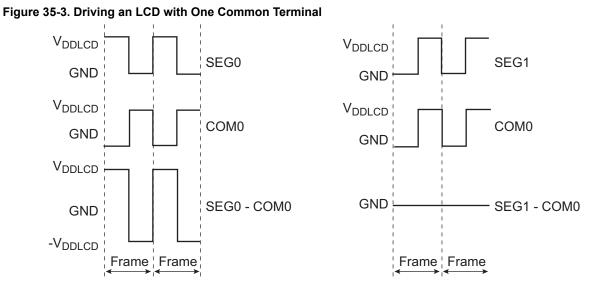

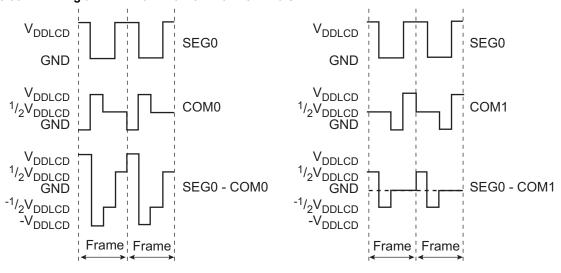

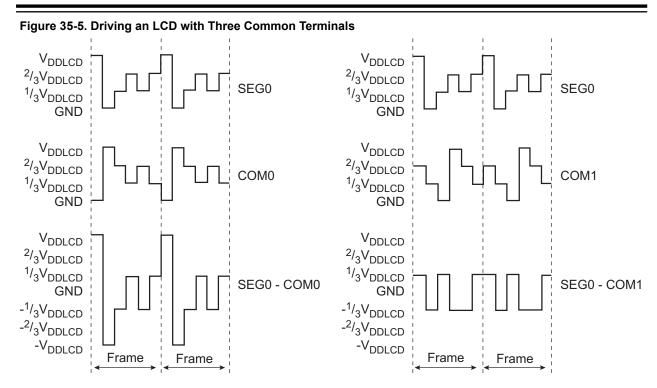

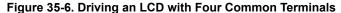

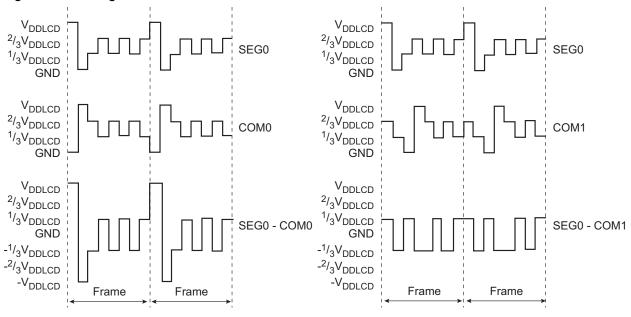

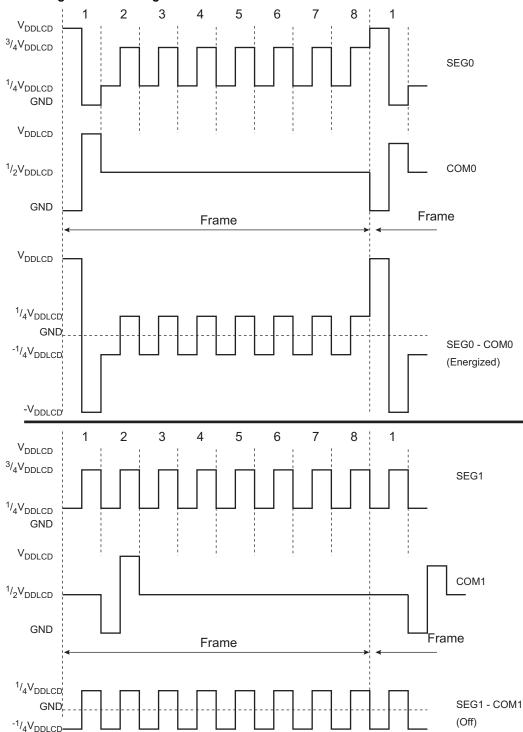

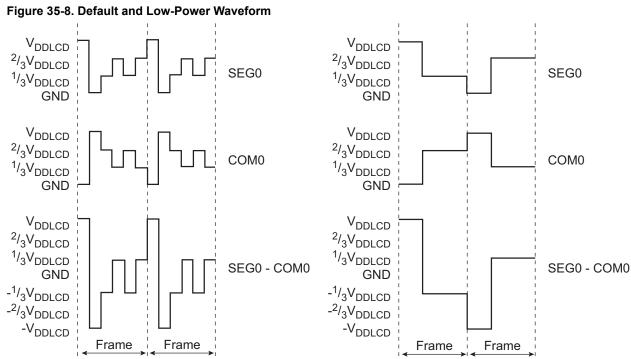

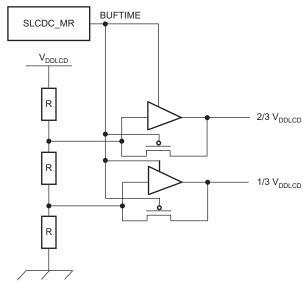

|     | 35.7.  | Waveform Specifications                       | 845 |

|     | 35.8.  | Register Summary                              | 846 |

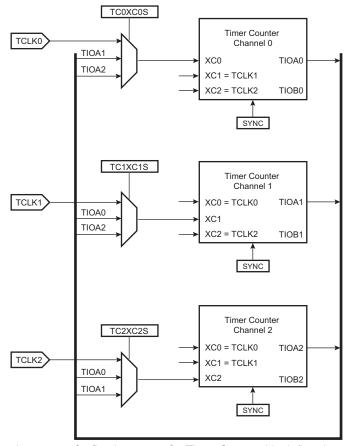

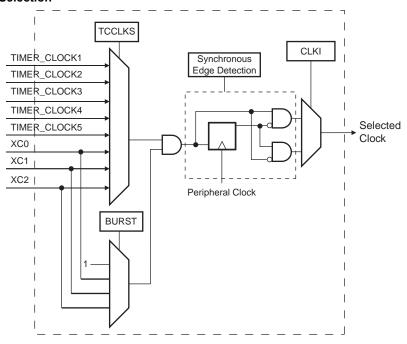

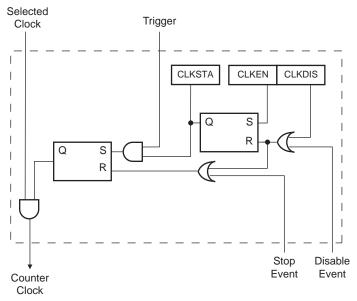

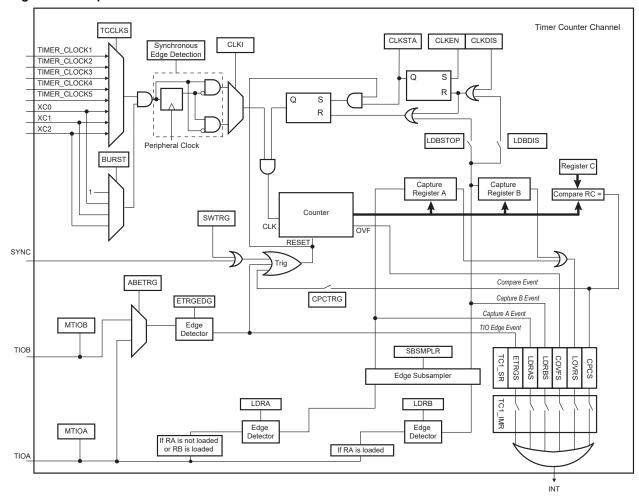

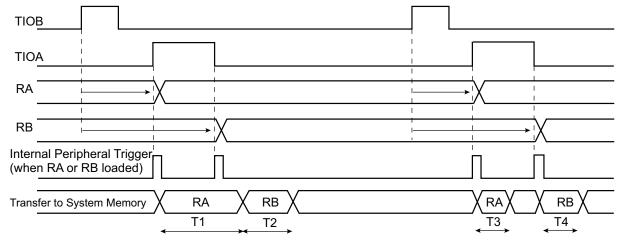

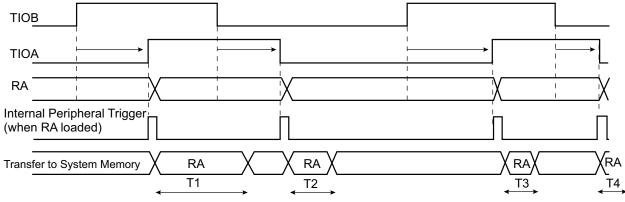

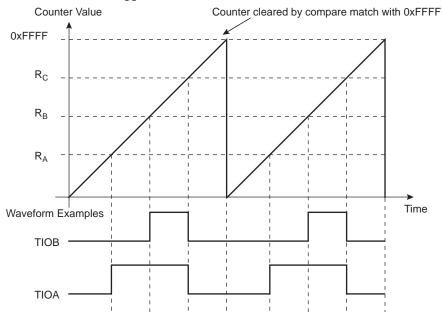

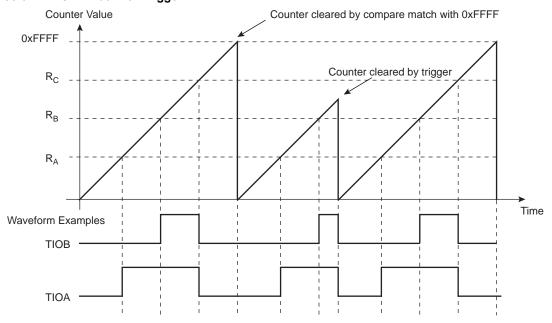

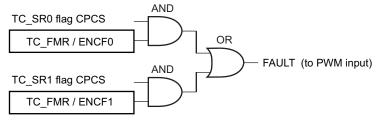

| 36. | Timer  | Counter (TC)                                  | 862 |

|     | 36.1.  | Description                                   | 862 |

|     | 36.2.  | Embedded Characteristics                      | 862 |

|     | 36.3.  | Block Diagram                                 | 863 |

|     | 36.4.  | Pin List                                      | 864 |

|     | 36.5.  | Product Dependencies                          | 864 |

|     | 36.6.  | Functional Description                        | 865 |

|     | 36.7.  | Register Summary                              | 888 |

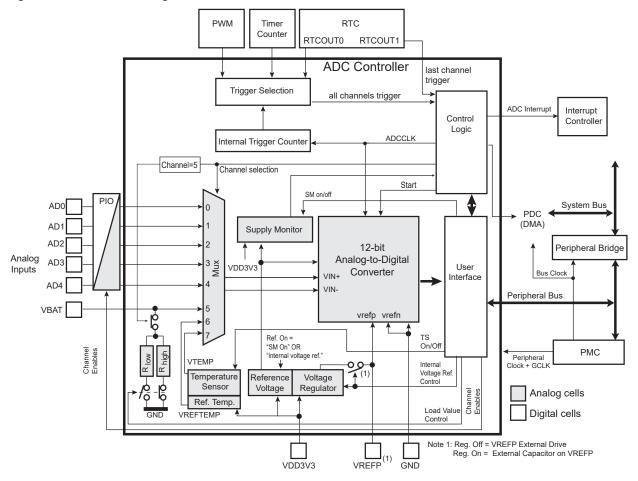

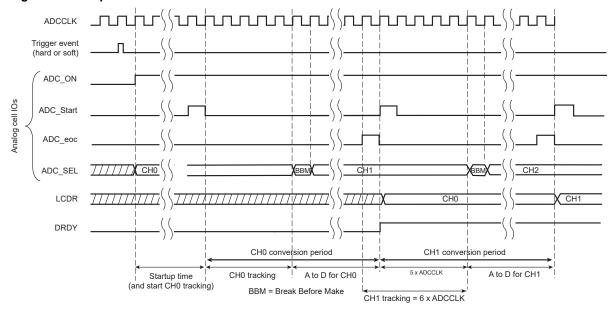

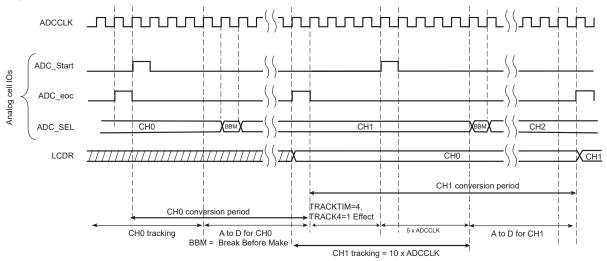

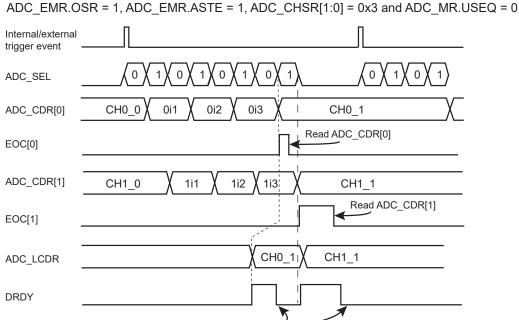

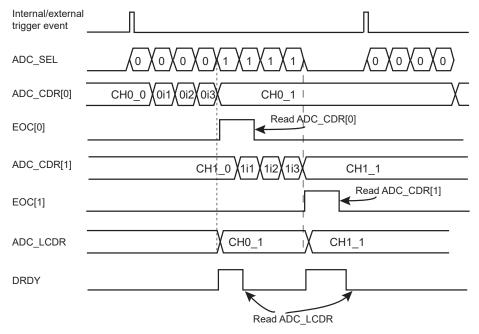

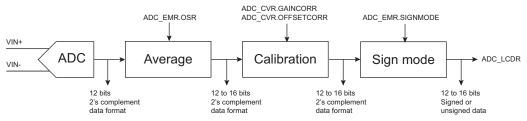

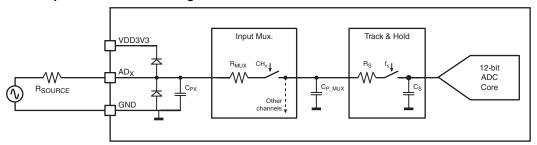

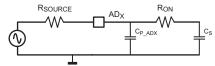

| 37. | Analog-to-Digital Converter (ADC) Controller | 930  |

|-----|----------------------------------------------|------|

|     | 37.1. Description                            | 930  |

|     | 37.2. Embedded Characteristics               | 930  |

|     | 37.3. Block Diagram                          | 931  |

|     | 37.4. Product Dependencies                   | 931  |

|     | 37.5. Functional Description                 | 932  |

|     | 37.6. Register Summary                       | 949  |

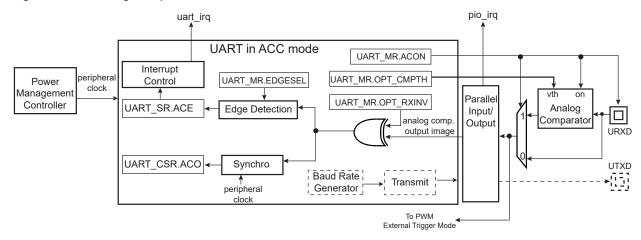

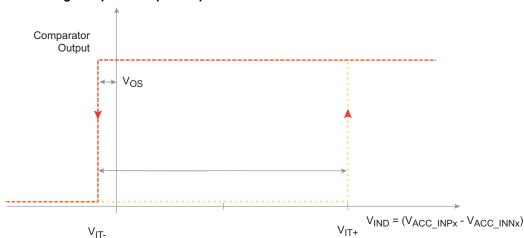

| 38. | Analog Comparator Controller (ACC)           | 991  |

|     | 38.1. Description                            | 991  |

|     | 38.2. Embedded Characteristics               | 991  |

|     | 38.3. Block Diagram                          | 991  |

|     | 38.4. Signal Description                     | 992  |

|     | 38.5. Product Dependencies                   | 992  |

|     | 38.6. Functional Description                 | 992  |

|     | 38.7. Register Summary                       | 994  |

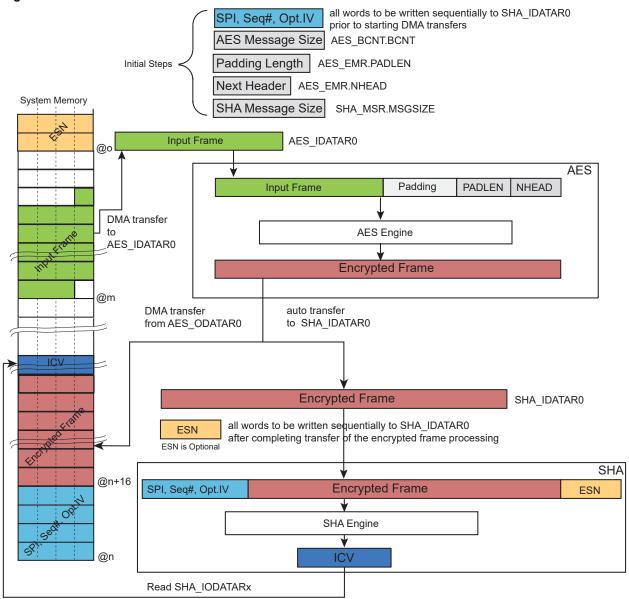

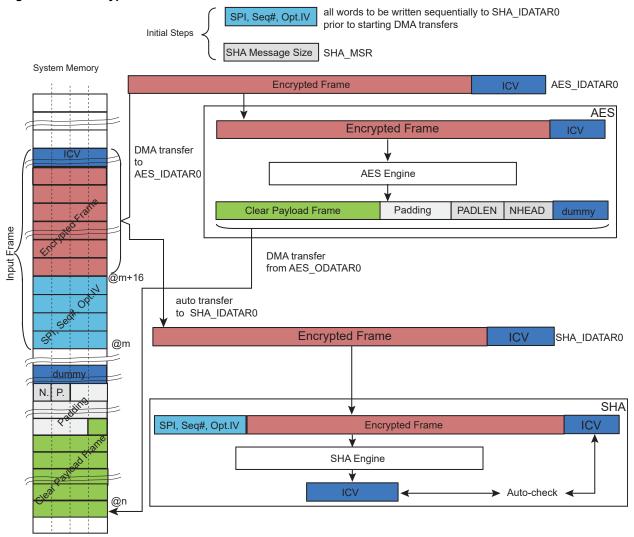

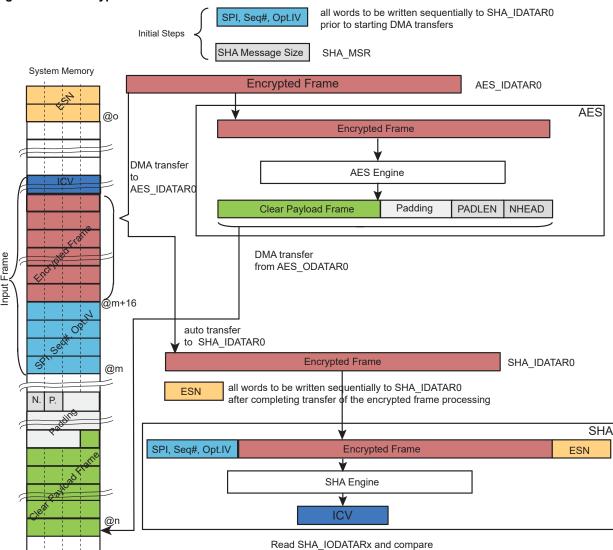

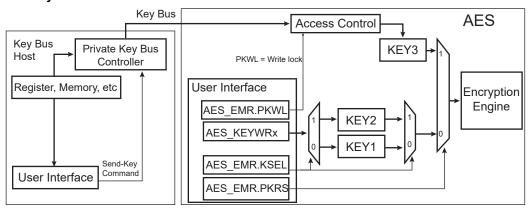

| 39. | Advanced Encryption Standard (AES)           | 1005 |

|     | 39.1. Description                            | 1005 |

|     | 39.2. Embedded Characteristics               | 1005 |

|     | 39.3. Product Dependencies                   | 1006 |

|     | 39.4. Functional Description                 | 1006 |

|     | 39.5. Register Summary                       | 1027 |

| 40. | Advanced Encryption Standard Bridge (AESB)   | 1057 |

|     | 40.1. Description                            | 1057 |

|     | 40.2. Embedded Characteristics               | 1057 |

|     | 40.3. Product Dependencies                   | 1057 |

|     | 40.4. Functional Description                 | 1058 |

|     | 40.5. Register Summary                       | 1063 |

| 41. | Secure Hash Algorithm (SHA)                  |      |

|     | 41.1. Description                            |      |

|     | 41.2. Embedded Characteristics               | 1082 |

|     | 41.3. Product Dependencies                   | 1082 |

|     | 41.4. Functional Description                 | 1083 |

|     | 41.5. Register Summary                       | 1091 |

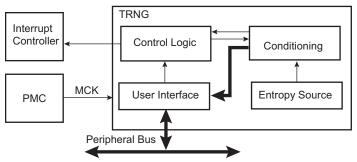

| 42. | True Random Number Generator (TRNG)          | 1111 |

|     | 42.1. Description                            | 1111 |

|     | 42.2. Embedded Characteristics               | 1111 |

|     | 42.3. Block Diagram                          | 1111 |

|     | 42.4. Product Dependencies                   |      |

|     | 42.5. Functional Description                 |      |

|     | 42.6. Register Summary                       |      |

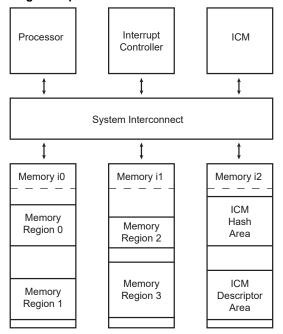

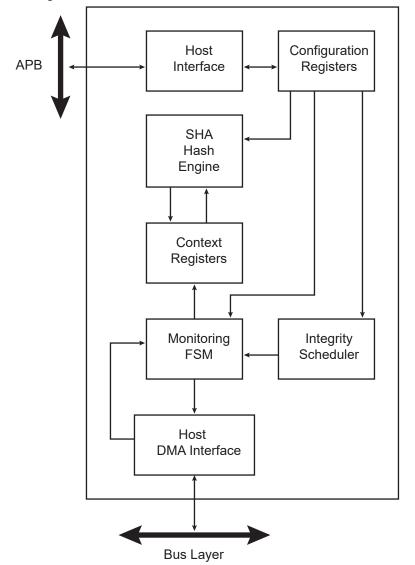

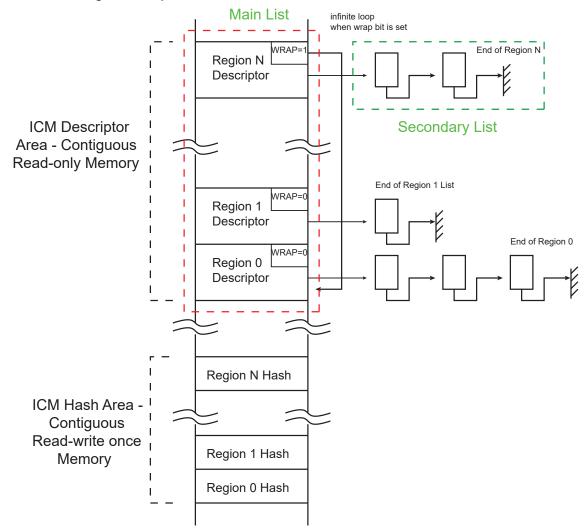

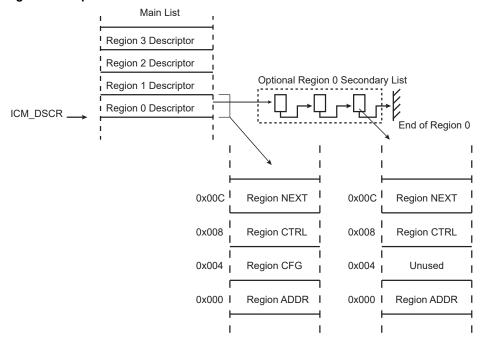

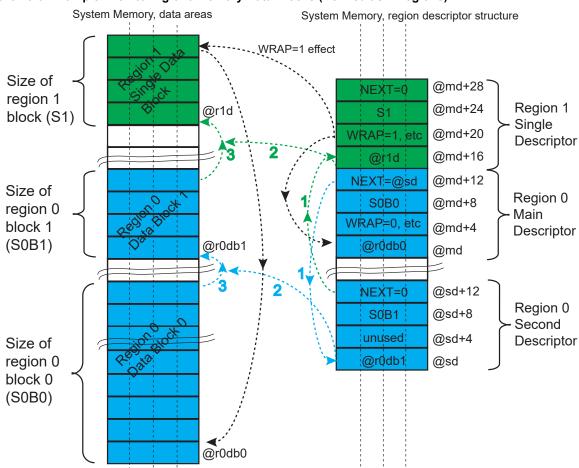

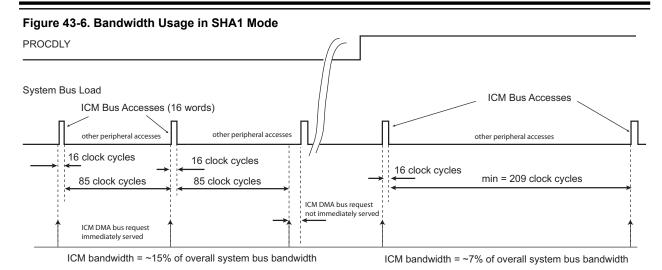

| 43. | Integrity Check Monitor (ICM)                | 1128 |

|     | 43.1. Description                            |      |

|     | 43.2. Embedded Characteristics               |      |

|     | 43.3.   | Block Diagram                                                              | 1129  |

|-----|---------|----------------------------------------------------------------------------|-------|

|     | 43.4.   | Product Dependencies                                                       | 1130  |

|     | 43.5.   | Functional Description                                                     | 1130  |

|     | 43.6.   | Register Summary                                                           | 1143  |

| 44. | Class   | cal Public Key Cryptography Controller (CPKCC)                             | 1162  |

|     | 44.1.   | Description                                                                | 1162  |

|     | 44.2.   | Product Dependencies                                                       | 1162  |

|     | 44.3.   | Functional Description                                                     | 1162  |

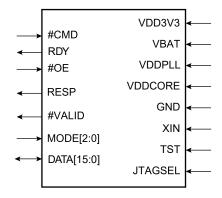

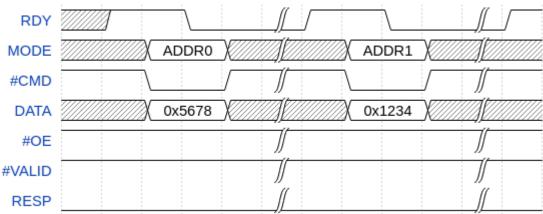

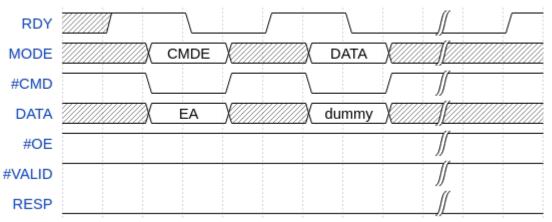

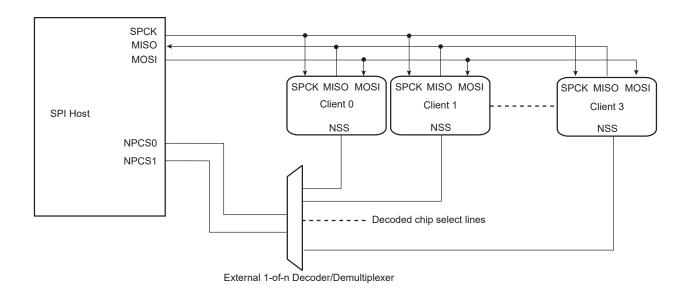

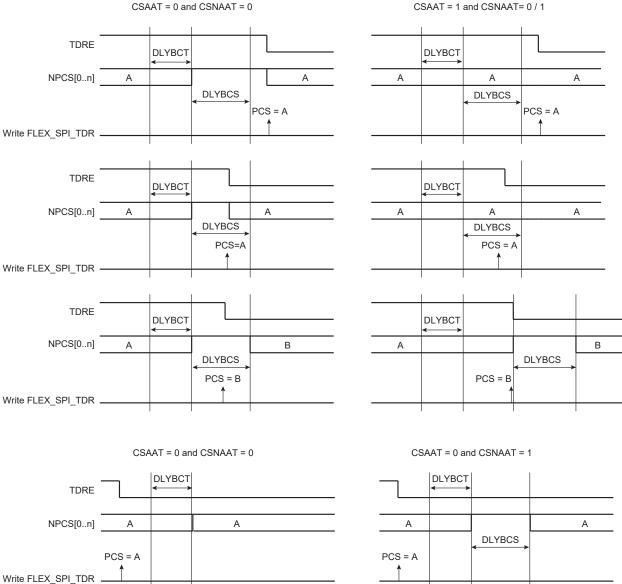

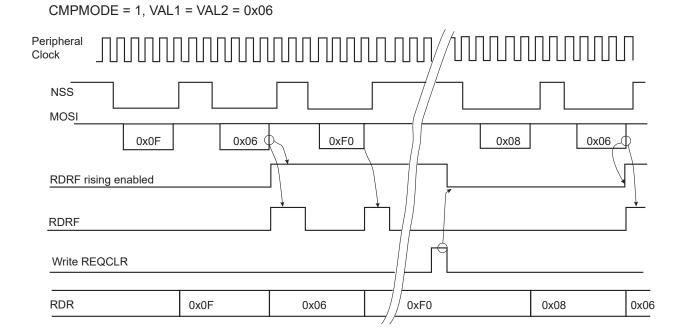

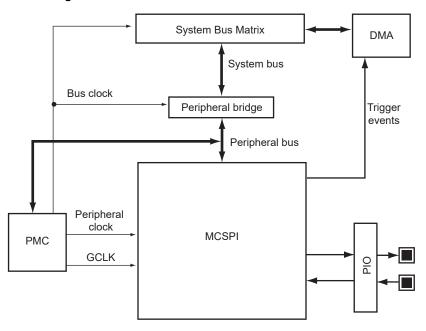

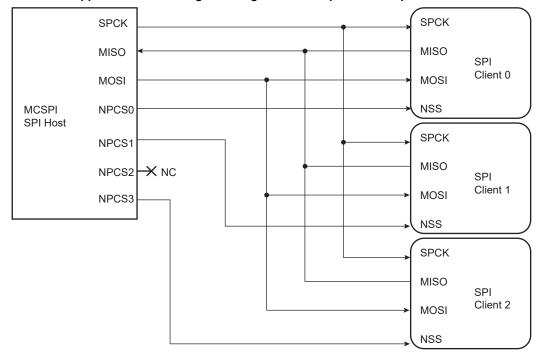

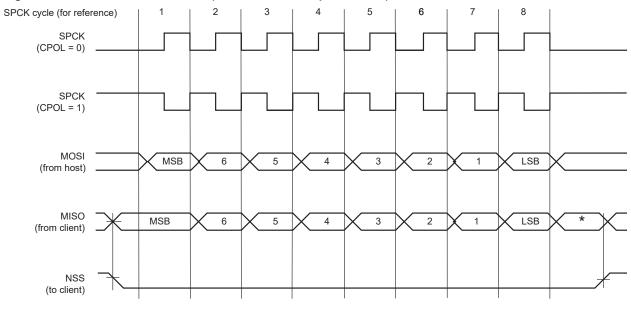

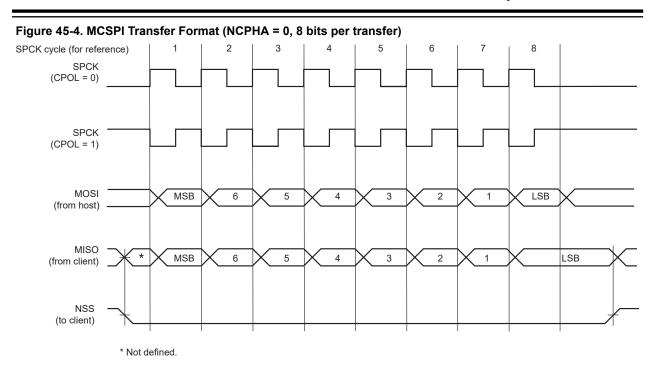

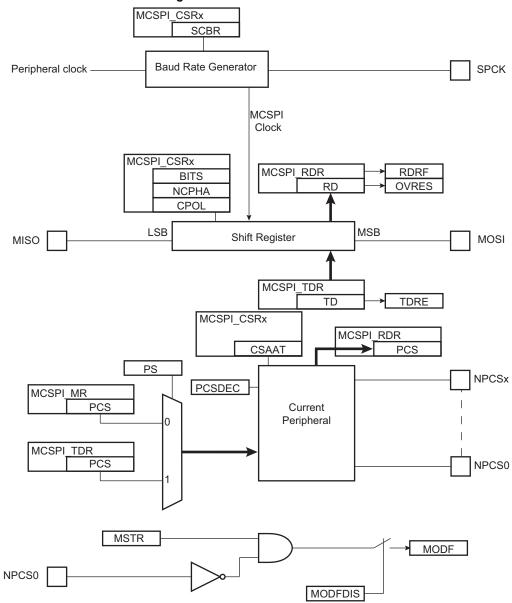

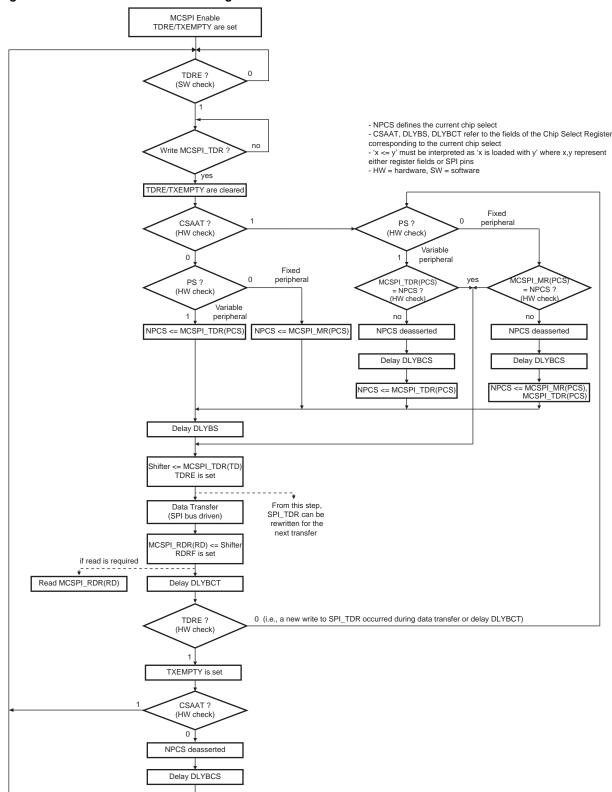

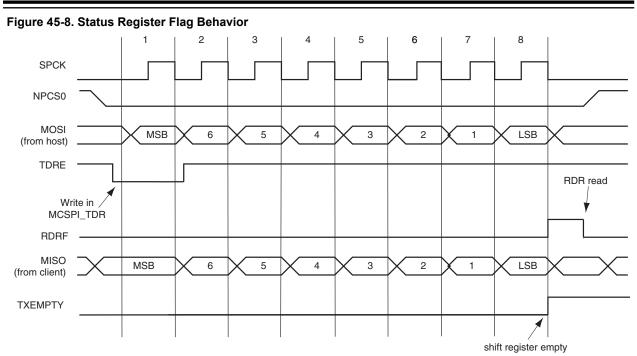

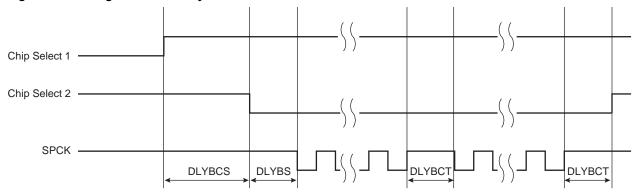

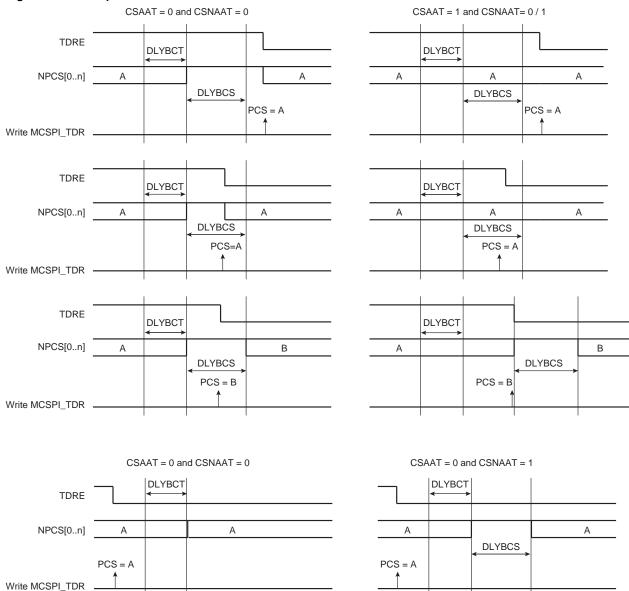

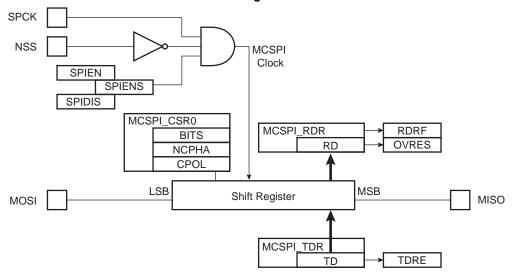

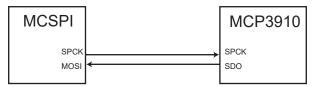

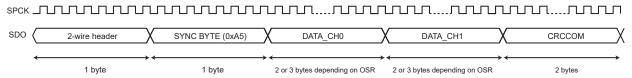

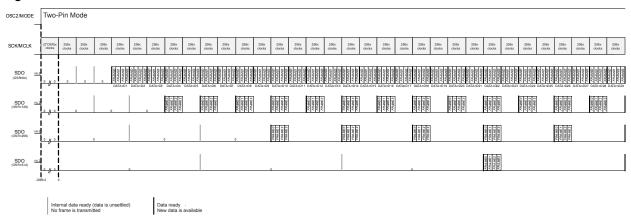

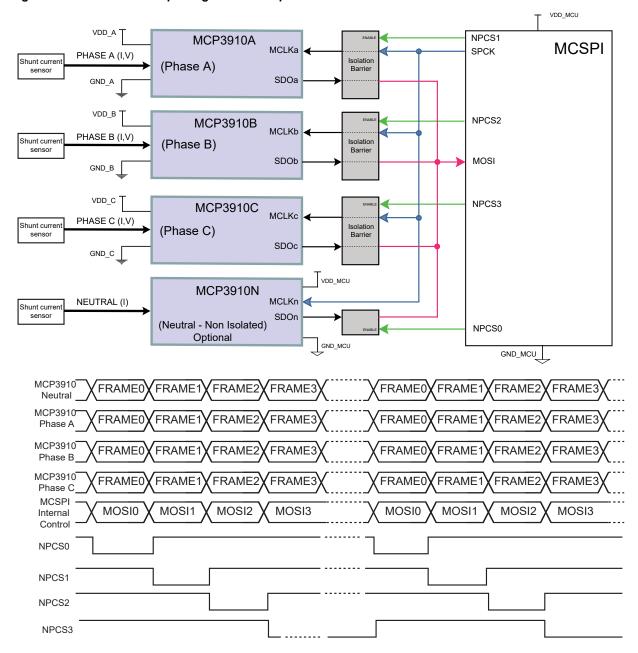

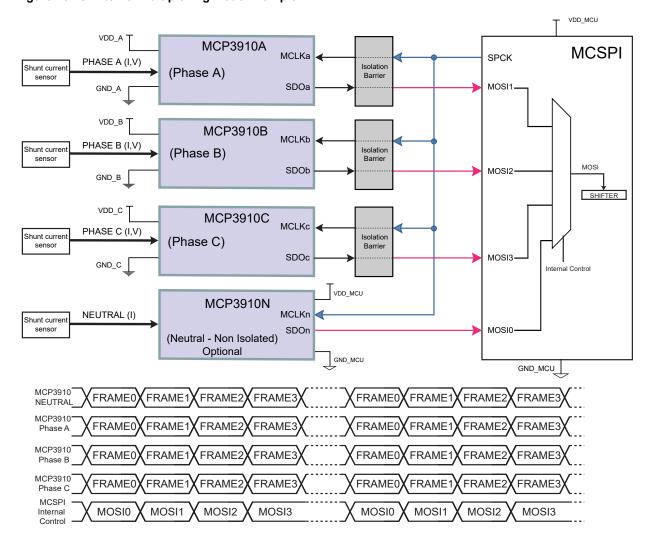

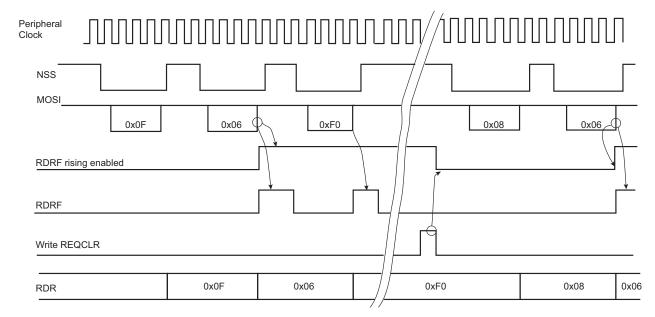

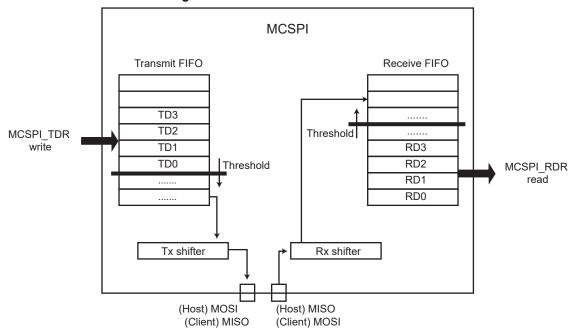

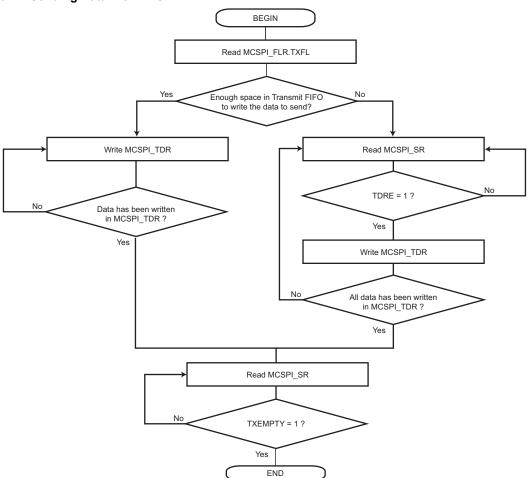

| 45. | Multi ( | Channel Serial Peripheral Interface (MCSPI)                                | 1163  |

|     | 45.1.   | Description                                                                | 1163  |

|     | 45.2.   | Embedded Characteristics                                                   | 1163  |

|     | 45.3.   | Block Diagram                                                              | 1164  |

|     | 45.4.   | Application Block Diagram                                                  | 1164  |

|     | 45.5.   | Signal Description                                                         | 1165  |

|     | 45.6.   | Product Dependencies                                                       | 1165  |

|     | 45.7.   | Functional Description                                                     | 1165  |

|     | 45.8.   | Register Summary                                                           | 1188  |

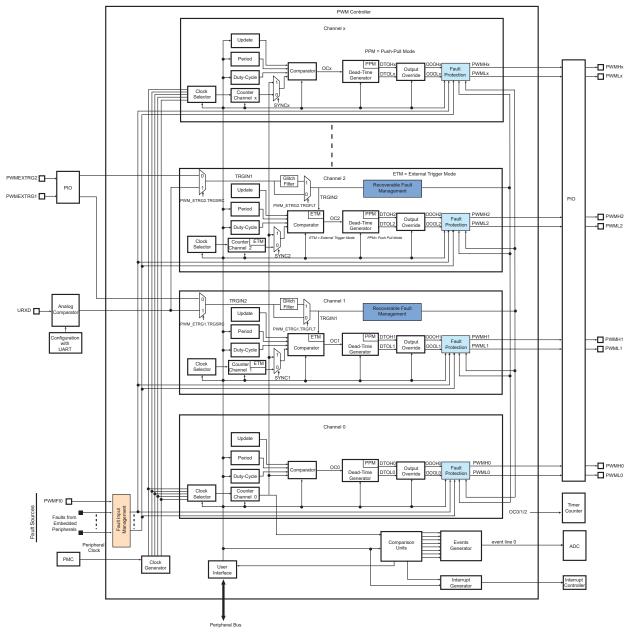

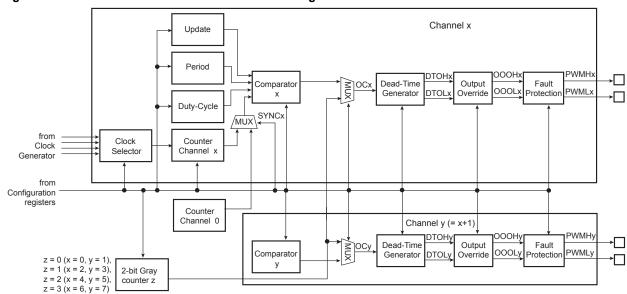

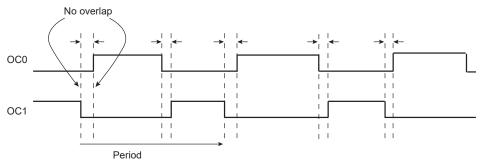

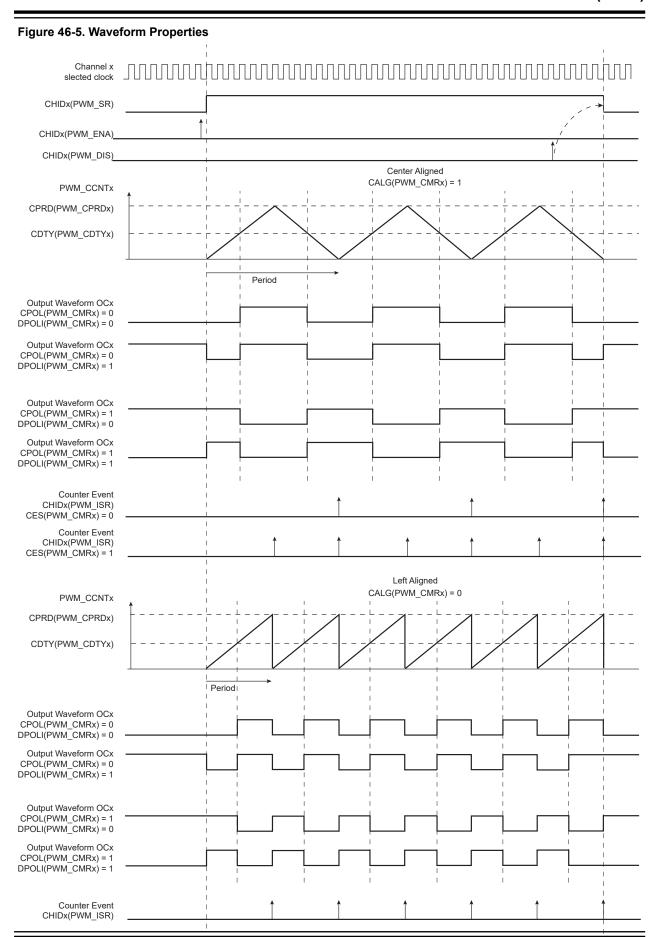

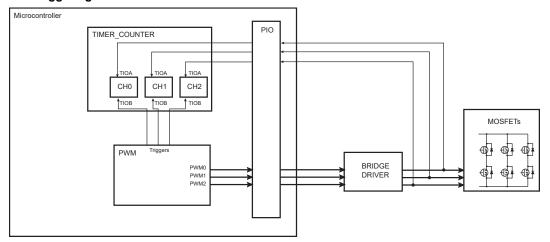

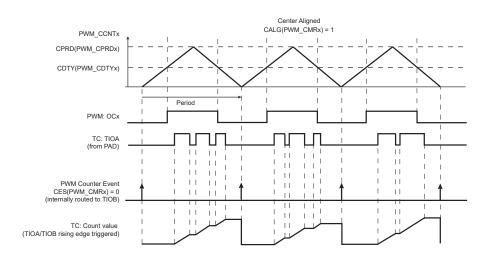

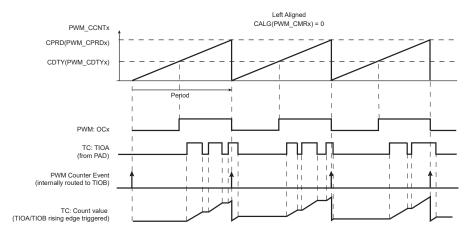

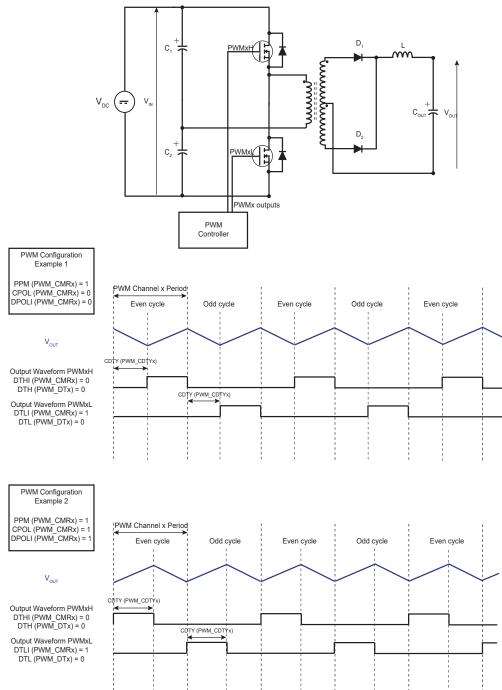

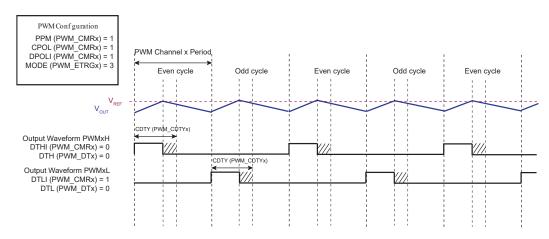

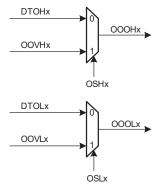

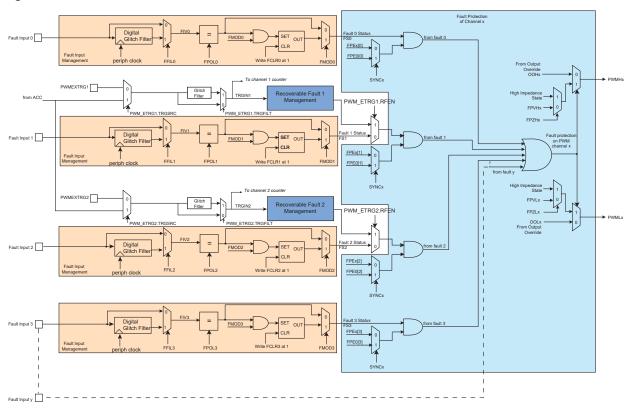

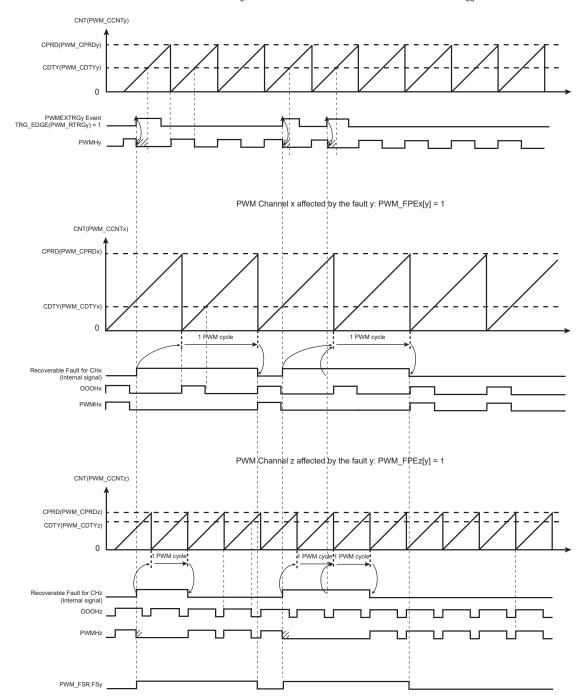

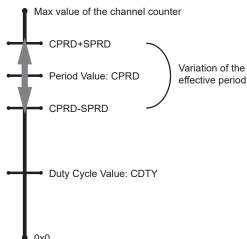

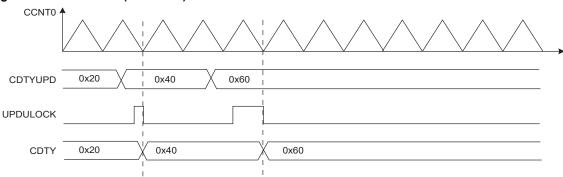

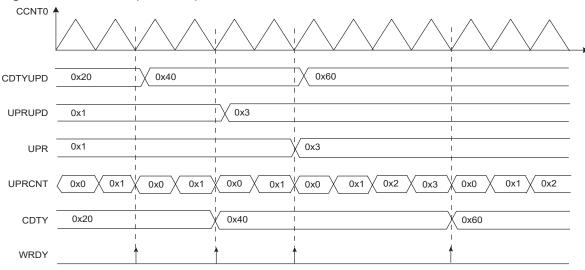

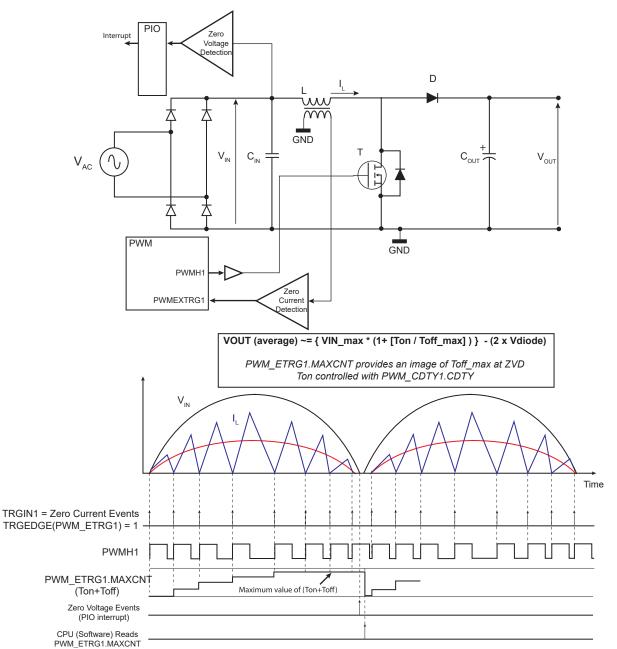

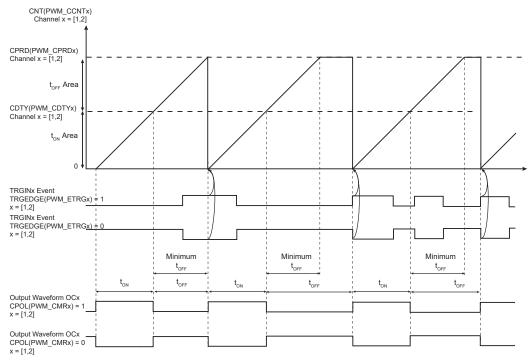

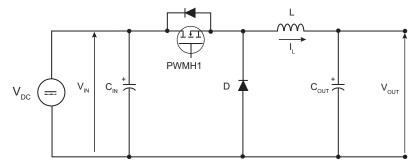

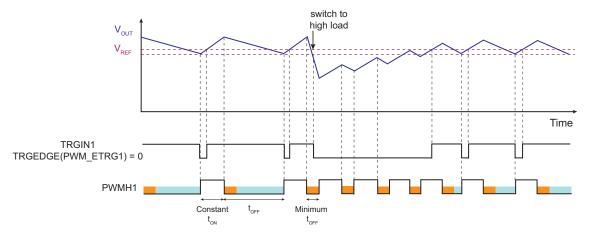

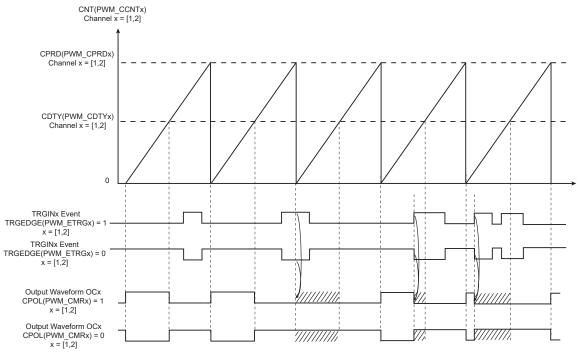

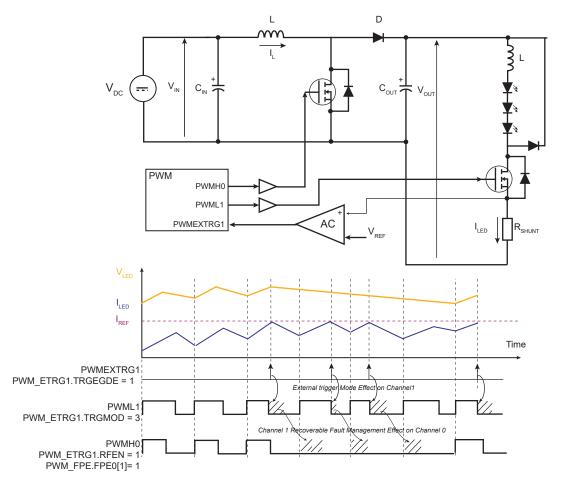

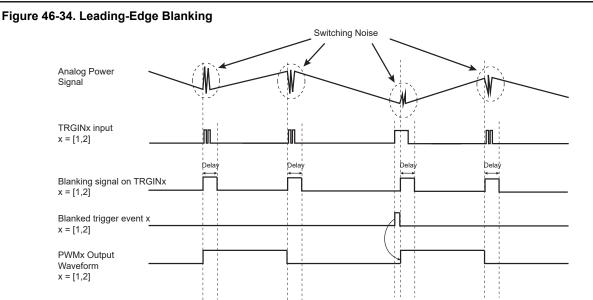

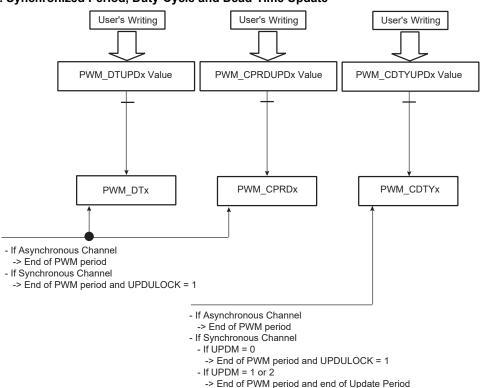

| 46. | Pulse   | Width Modulation Controller (PWM)                                          | 1220  |

|     | 46.1.   | Description                                                                | 1220  |

|     | 46.2.   | Embedded Characteristics                                                   | 1220  |

|     | 46.3.   | Block Diagram                                                              | 1222  |

|     | 46.4.   | I/O Lines Description                                                      | 1222  |

|     | 46.5.   | Product Dependencies                                                       | 1223  |

|     |         | Functional Description                                                     |       |

|     | 46.7.   | Register Summary                                                           | 1263  |

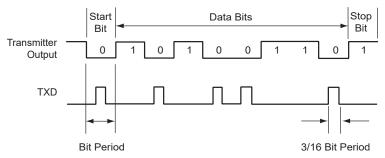

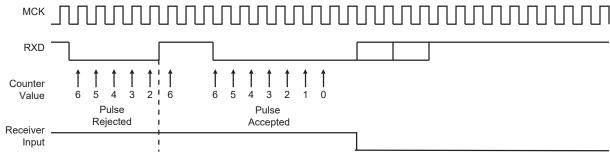

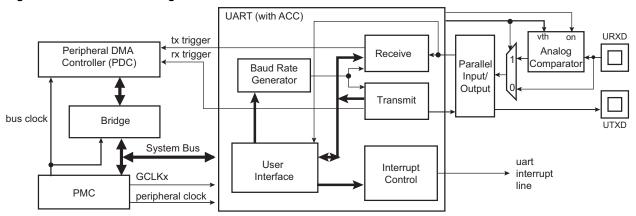

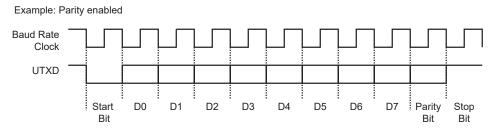

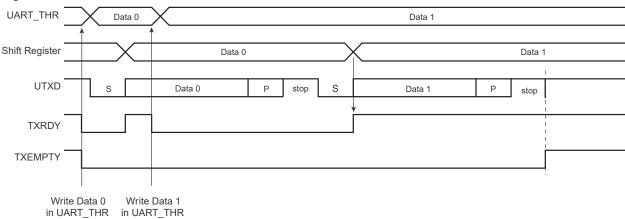

| 47. | Unive   | rsal Asynchronous Receiver Transmitter (UART)                              | 1327  |

|     | 47.1.   | Description                                                                | 1327  |

|     | 47.2.   | Embedded Characteristics                                                   | 1327  |

|     | 47.3.   | Block Diagram                                                              | 1328  |

|     |         | Product Dependencies                                                       |       |

|     |         | Functional Description                                                     |       |

|     |         | Register Summary                                                           |       |

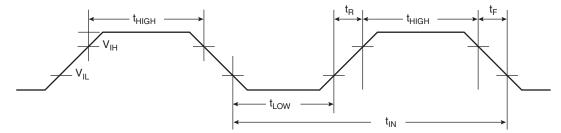

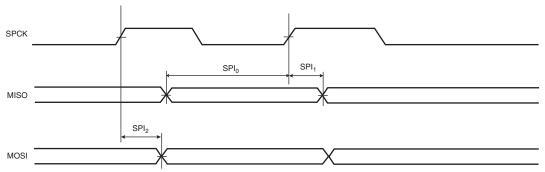

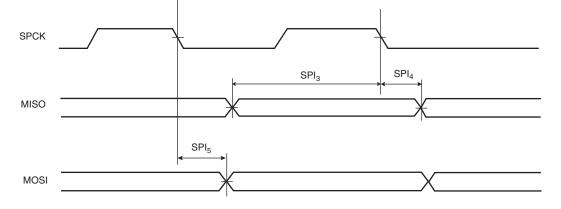

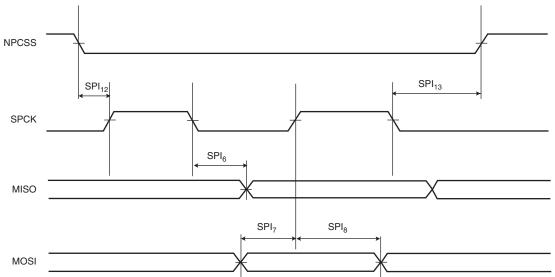

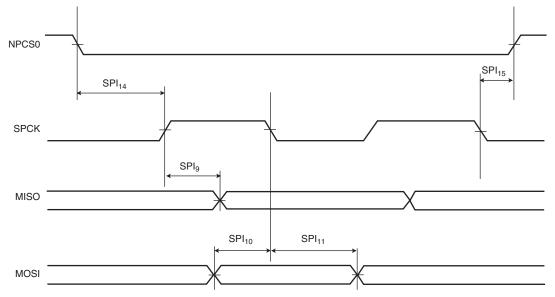

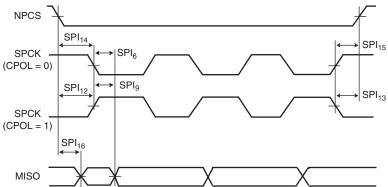

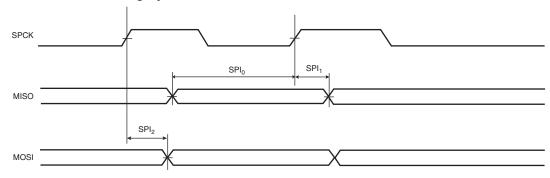

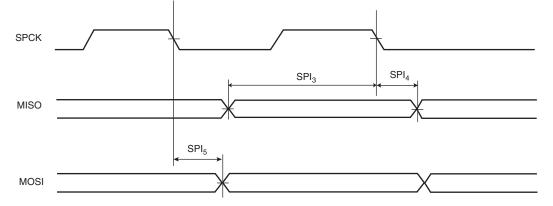

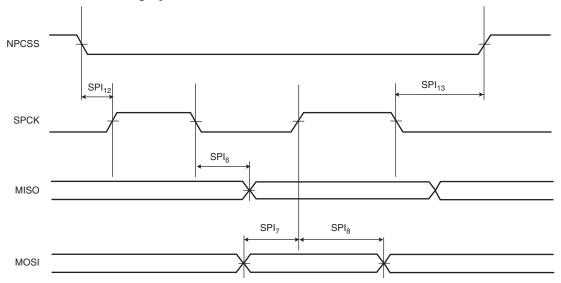

| 48. | Electr  | ical Characteristics                                                       | 1361  |

|     | 48.1.   | Electrical Parameters Usage                                                | 1361  |

|     |         | Absolute Maximum Ratings                                                   |       |

|     |         | Recommended Operating Conditions                                           |       |

|     |         | Recommended Power Supply Sequencing for Externally Supplied VDDCORE/VDDPLL |       |

|     |         | I/O Characteristics                                                        |       |

|     |         | Digital Peripherals Characteristics                                        |       |

|     |         | Embedded Analog Peripherals Characteristics                                |       |

|     |         | Embedded Flash Characteristics.                                            |       |

|     |         | Power Supply Current Consumption                                           |       |

|     |         |                                                                            |       |

| 40  | Mach    | onical Characteristics                                                     | 1/100 |

|     | 49.1. 64-lead VQFN Mechanical Characteristics    | 1401  |

|-----|--------------------------------------------------|-------|

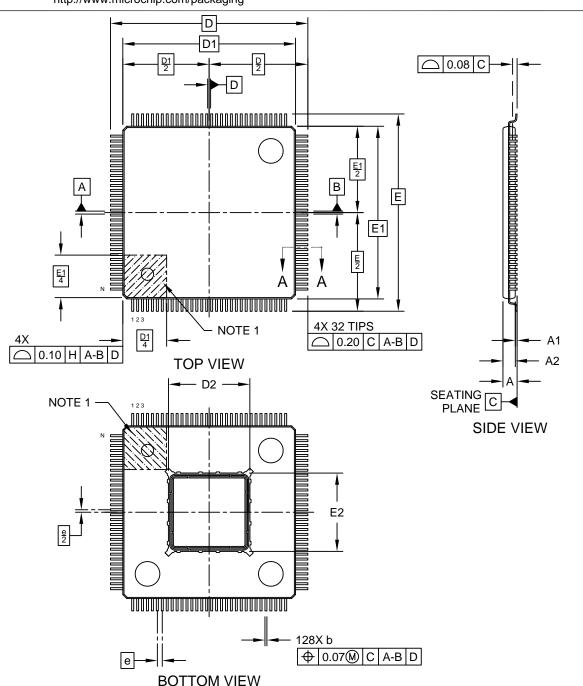

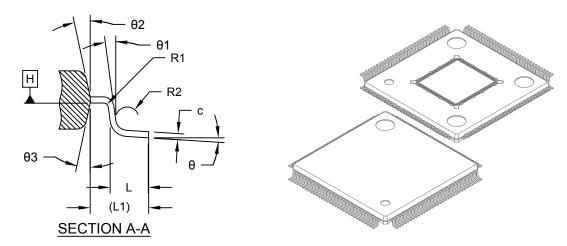

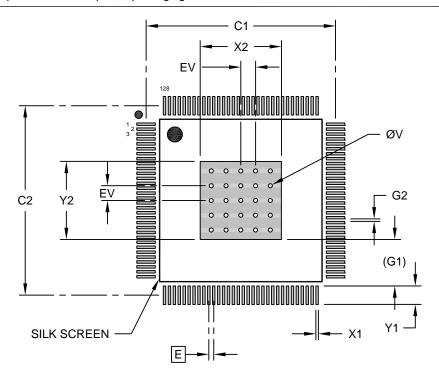

|     | 49.2. 128-pin EP-TQFP Mechanical Characteristics | 1404  |

| 50. | Marking                                          | 1407  |

| 51. | Ordering Information                             | 1408  |

| 52. | Revision History                                 | 1409  |

|     | 52.1. Rev. B - 11/2022                           | 1409  |

|     | 52.2. Rev. A - 06/2022                           | 1409  |

| Mic | crochip Information                              | 1410  |

|     | The Microchip Website                            | 1410  |

|     | Product Change Notification Service              | 1410  |

|     | Customer Support                                 | 1410  |

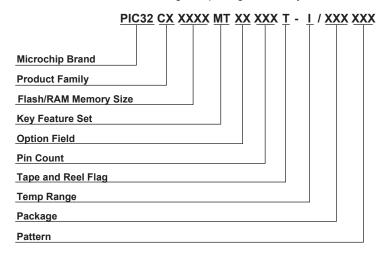

|     | Product Identification System                    | 1411  |

|     | Microchip Devices Code Protection Feature        |       |

|     | Legal Notice                                     |       |

|     | Trademarks                                       | 1412  |

|     | Quality Management System                        | 1413  |

|     | Worldwide Sales and Service                      | 1/1/1 |

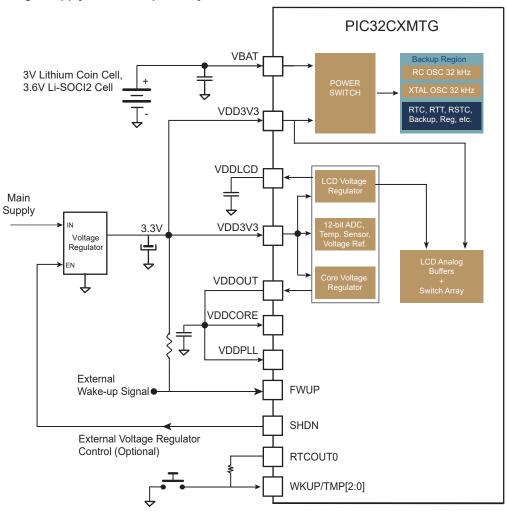

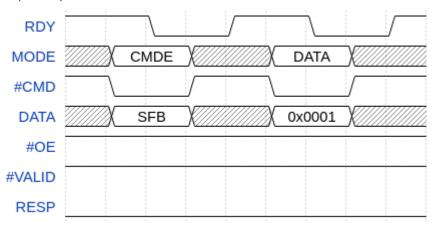

Figure 1-1. PIC32CXMTG Block Diagram

PIC32CXMTG

**Block Diagram**

# 2. Configuration Summary

The devices differ in memory sizes, packages and features. The following table summarizes the different configurations.

Table 2-1. PIC32CXMTG Family Features

|                   |                                                  |                  |                           |         |      |         |                          | Digita                               | ıl Perip               | heral        | ls           |          | Analog                               | Perip                                        | herals             |

|-------------------|--------------------------------------------------|------------------|---------------------------|---------|------|---------|--------------------------|--------------------------------------|------------------------|--------------|--------------|----------|--------------------------------------|----------------------------------------------|--------------------|

| Device            | Flash Memory Size (Kb)/<br>Nb Subsystem x Size/2 | SRAM Memory (Kb) | TCM and Cache Memory (Kb) | FPU/MPU | Pins | Package | FLEXCOM (SPI, UART, TWI) | Quad I/O Serial Peripheral Interface | Timer Counter Channels | PWM Channels | DMA Channels | I/O Pins | Segment LCD Controller<br>(COMs+Seg) | 12-bit ADC (Channels)<br>External / Internal | Analog Comparators |

| PIC32CX2051MTG64  | 2048                                             | 512              |                           |         | 64   | VQFN    | 4x4-wire,<br>3x2-wire    |                                      |                        |              |              | 41       | _                                    | 2 + 3                                        |                    |

| PIC32CX2051MTG128 | (2x1024)                                         |                  |                           |         | 128  | EP-TQFP | 8x4-wire                 |                                      |                        |              |              | 102      | 8x32                                 | 5 + 3                                        |                    |

| PIC32CX1025MTG64  | 1024                                             | 256              | 16 + 8                    | Yes     | 64   | VQFN    | 4x4-wire,<br>3x2-wire    | Υ                                    | 12                     | 3            | 23           | 41       | _                                    | 2 + 3                                        | Yes                |

| PIC32CX1025MTG128 | (2x512)                                          |                  |                           |         | 128  | EP-TQFP | 8x4-wire                 |                                      |                        |              |              | 102      | 8x32                                 | 5 + 3                                        |                    |

| PIC32CX5112MTG128 | 512<br>(2x256)                                   | 128              |                           |         | 128  | EP-TQFP | 8x4-wire                 |                                      |                        |              |              | 102      | 8x32                                 | 5 + 3                                        |                    |

# 3. Package and Pinout

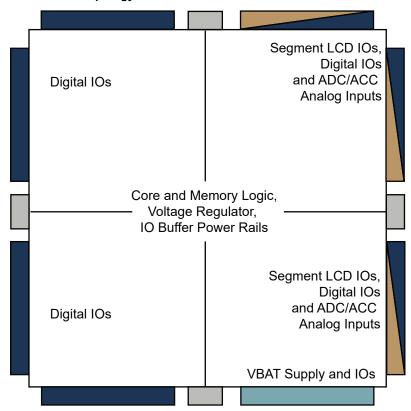

In the following figures, the IO and power supply ring topology are shown for typical use cases of a Smart Energy meter and communication modules.

# 3.1 Pinout Topology

Figure 3-1. PIC32CXMTG Pinout Topology

# 3.2 Pinout and Multiplexing

# 3.2.1 Peripheral Signal Multiplexing on I/O Lines

The multiplexing table that follows defines how the I/O lines of the peripherals A, B, C and D are multiplexed on the PIO Controllers. Refer to the column *PIO Peripheral*, sub-column *Func*.

In the *Primary* and *Alternate* columns, the values in the *Dir* sub-column are applicable to the alternate function only if the primary signal is a PIO line (PAx, PBx, PCx, PDx). If only a primary function is available for a given pin, the value in the sub-column *Dir* applies.

The *IO Set* sub-column in the *PIO Peripheral* column gives IO set numbers per PIO line. For a given set of signals for a given peripheral, only IO peripheral lines which are in the same IO set can be used at the same time.

The column Reset State indicates the Reset state of the line.

- PIO, Alternate or Peripheral signal name Indicates whether the PIO line resets in general purpose I/O mode, in Peripheral mode or in Alternate mode. If "PIO" is mentioned, the PIO line is in I/O mode. If a Peripheral or Alternate signal name is mentioned in the "Reset State" column, the PIO line is assigned to this function.

- I or O Indicates whether the signal is Input or Output state.

- PU or PD Indicates whether Pull-up, Pull-down or nothing is enabled.

- ST— Indicates if Schmitt trigger is enabled.

- All PIO lines feature programmable slew rate control and Lock/Freeze configuration.

For details on FLEXCOM0/1/2/3/4, see FLEXCOM Features and the section Flexible Serial Communication Controller (FLEXCOM).

#### 3.2.1.1 Pinout and Multiplexing

#### Table 3-1. 64-lead VQFN Multiplexing

| VOENCA | Power Rail/          | Primary | Alternate         |     |      | PIO Peripheral |     |        | Reset State                                     |                                                    |

|--------|----------------------|---------|-------------------|-----|------|----------------|-----|--------|-------------------------------------------------|----------------------------------------------------|

| Pin    | Voltage<br>Reference | Signal  | Signal            | Dir | Func | Signal         | Dir | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>SEC, FILTER | Comments                                           |

| 13     | VDD3V3               | PA4     | _                 | -   | Α    | FLEXCOM0_IO0   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

| 14     | VDD3V3               | PA5     | WKUP5             | ı   | Α    | FLEXCOM0_IO1   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

|        |                      |         |                   |     | Α    | FLEXCOM0_IO2   | I/O | 1      |                                                 |                                                    |

| 15     | VDD3V3               | PA6     | _                 | -   | В    | FLEXCOM0_IO4   | 0   | 2      | PIO, I, PU, ST                                  |                                                    |

|        |                      |         |                   |     | С    | TIOA6          | I/O | 1      |                                                 |                                                    |

| 16     | VDD3V3               | PA7     | _                 | _   | Α    | FLEXCOM0_IO3   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

| 10     | VDBOVO               | 170     |                   |     | С    | TIOB6          | I/O | 1      | 1 10, 1, 1 0, 01                                |                                                    |

| 7      | VDD3V3               | PA8     | -                 | -   | Α    | FLEXCOM1_IO0   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

| 8      | VDD3V3               | PA9     | WKUP6             | I   | Α    | FLEXCOM1_IO1   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

| 17     | VDD3V3               | PA12    | -                 | -   | Α    | FLEXCOM2_IO0   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

| 18     | VDD3V3               | PA13    | WKUP7             | I   | Α    | FLEXCOM2_IO1   | I/O | 1,2    | PIO, I, PU, ST                                  |                                                    |

|        |                      |         |                   |     | Α    | COM2           | 0   | 1      |                                                 |                                                    |

| 34     | VDD3V3               | PA23    | _                 | -   | В    | FLEXCOM5_IO1   | I/O | 5,6    | PIO, I, PD, ST                                  |                                                    |

|        |                      |         |                   |     | D    | TCLK0          | I   | 1      |                                                 |                                                    |

|        |                      |         |                   |     | Α    | COM3           | 0   | 1      |                                                 |                                                    |

| 35     | VDD3V3               | PA24    | PA24 –            | -   | В    | FLEXCOM5_IO0   | I/O | 5,6    | PIO, I, PD, ST                                  |                                                    |

|        |                      |         |                   |     | D    | TIOB0          | I/O | 1      |                                                 |                                                    |

|        |                      |         |                   |     | Α    | COM4           | 0   | 1      |                                                 |                                                    |

| 36     | VDD3V3               | PA25    | _                 | -   | В    | FLEXCOM6_IO0   | I/O | 4,5    | PIO, I, PD, ST                                  |                                                    |

|        |                      |         |                   |     | D    | TIOA0          | I/O | 1      |                                                 |                                                    |

|        |                      |         | 450/              |     | Α    | SEG0           | 0   | 1      |                                                 |                                                    |

| 37     | VDD3V3               | PA29    | AD0/<br>ACC_INP0/ | ١,  | В    | FLEXCOM0_IO4   | 0   | 1      | PIO, I, PD, ST                                  | Clock input when oscillator is in Bypass mode      |

| 37     | VDD3V3               | FAZJ    | XIN               | ļ ' | С    | FLEXCOM1_IO4   | 0   | 1      | FIO, 1, FD, 31                                  | Clock input when oscillator is in bypass mode      |

|        |                      |         |                   |     | D    | FLEXCOM2_IO4   | 0   | 1      |                                                 |                                                    |

|        |                      |         | AD3/              |     | Α    | SEG3           | 0   | 1      |                                                 |                                                    |

| 39     | VDD3V3               | PB0     | ACC_INN0/         | I/O | В    | FLEXCOM3_IO4   | 0   | 1      | PIO, I, PD, ST                                  | ADCx/ACCx signals:Pull-down must be disabled       |

|        |                      |         | XOUT              |     | D    | TIOB1          | I/O | 1      |                                                 | in PIO Controller when using these PIO pins as     |

|        |                      |         |                   |     | Α    | SEG5           | 0   | 1      |                                                 | ADC/ACC inputs. XIN/OUT signals:Pull-down must     |

| 40     | VDD3V3               | PB2     | ERASE             |     | В    | FLEXCOM7_IO2   | I/O | 1      |                                                 | be disabled in PIO Controller when using these PIO |

| 40     | VDD3V3               | PD2     | ERASE             | '   | С    | FLEXCOM7_IO4   | 0   | 2      |                                                 | pins as Crystal Oscillator XIN/XOUT signals.       |

|        |                      |         |                   |     | D    | TIOA2          | I/O | 1      |                                                 |                                                    |

|        |                      |         |                   |     | Α    | SEG6           | 0   | 1      |                                                 |                                                    |

| 43     | VDD3V3               | PB3     | -                 | -   | В    | FLEXCOM7_IO1   | I/O | 1,2    | PIO, I, PD, ST                                  |                                                    |

|        |                      |         |                   |     | D    | TIOB2          | I/O | 1      |                                                 |                                                    |

|        |                      |         |                   |     | Α    | SEG7           | 0   | 1      |                                                 |                                                    |

| 44     | VDD3V3               | PB4     | -                 | -   | В    | FLEXCOM7_IO0   | I/O | 1,2    | PIO, I, PD, ST                                  |                                                    |

|        |                      |         |                   |     | D    | TCLK2          | ı   | 1      |                                                 |                                                    |

# **Package and Pinout**

| co            | ntinued       |         |           |     |        |                      |       |        |                                                 |          |  |

|---------------|---------------|---------|-----------|-----|--------|----------------------|-------|--------|-------------------------------------------------|----------|--|

| VOEN64        | Power Rail/   | Primary | Alternate | 1   |        | PIO Peripheral       |       |        | Reset State                                     |          |  |

| Pin<br>Number | Voltage       | Signal  | Signal    | Dir | Func   | Signal               | Dir   | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>SEC, FILTER | Comments |  |

| 45            | VDD3V3        | PB9     | WKUP9     | Ι,  | Α      | SEG12                | 0     | 1      | DIO I DD ST                                     |          |  |

| 45            | VDD3V3        | РВЭ     | WKUP9     | I   | В      | FLEXCOM3_IO0         | I/O   | 3,4    | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | Α      | SEG13                | 0     | 1      |                                                 |          |  |

| 46            | VDD3V3        | PB10    | _         | -   | В      | FLEXCOM3_IO1         | I/O   | 3,4    | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | D      | TRACESWO             | 0     | 1      |                                                 |          |  |

|               |               |         |           |     | Α      | SEG14                | 0     | 1      |                                                 |          |  |

| 47            | VDD3V3        | PB11    | _         | -   | В      | FLEXCOM3_IO2         | I/O   | 3      | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | С      | FLEXCOM3_IO4         | 0     | 4      |                                                 |          |  |

| 48            | VDD3V3        | PB12    | WKUP10    | ı   | Α      | SEG15                | 0     | 1      | PIO, I, PD, ST                                  |          |  |

|               |               |         |           | ļ.  | В      | FLEXCOM3_IO3         | I/O   |        |                                                 |          |  |

|               |               |         |           |     | Α      | SEG27                | 0     | 1      |                                                 |          |  |

| 49            | VDD3V3        | PB24    | _         | -   | В      | FLEXCOM4_IO0         | I/O   |        | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | С      | TIOA5                | I/O   | 2      |                                                 |          |  |

|               |               |         |           |     | Α      | SEG28                | 0     | 1      |                                                 |          |  |

| 50            | VDD3V3        | PB25    | WKUP8     | I   | В      | FLEXCOM4_IO1         | I/O   | 1,2    | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | С      | TIOB5                | I/O   | 2      |                                                 |          |  |

|               |               |         |           |     | Α      | SEG29                | 0     | 1      |                                                 |          |  |

| 51            | VDD3V3        | PB26    | _         | -   | В      | FLEXCOM4_IO2         | I/O   | 1      | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | С      | FLEXCOM4_IO4         | 0     | 2      |                                                 |          |  |

|               | VDD3V3        | PC0     |           |     |        | A                    | SEG30 | 0      | 1                                               |          |  |

| 52            |               |         | _         | _   | В      | FLEXCOM4_IO3         | I/O   |        | PIO, I, PD, ST                                  |          |  |

|               |               |         |           |     | С      | TIOA3                | I/O   | 2      |                                                 |          |  |

|               |               |         |           |     | D      | TDI                  | I     | 1      |                                                 |          |  |

| 55            | VDD3V3        | PC2     | _         | -   | A      | SWCLK                | I     | 1      | SWCLK,ST                                        |          |  |

|               |               |         |           |     | В      | FLEXCOM1_IO0         | 1/0   | 3      |                                                 |          |  |

| 56            | VDD3V3        | PC3     | _         | -   | A      | SWDIO                | 1/0   | 1      | SWDIO,ST                                        |          |  |

|               |               |         |           |     | B<br>A | FLEXCOM1_IO1<br>PCK2 | 0     | 3      |                                                 |          |  |

| 57            | VDD3V3        | PC5     | _         | -   | D      | TCLK5                | ı     | 1,2    | PIO, I, PU, ST                                  |          |  |

| 59            | VDD3V3        | PC10    | _         | -   | A      | QIO3                 | I/O   | 1,2    | PIO, I, PU, ST                                  |          |  |

| 0.0           | V 2 2 2 0 V 0 | . 010   |           |     | A      | QIO2                 | 1/0   | 1      |                                                 |          |  |

| 60            | VDD3V3        | PC11    | -         | -   | В      | FLEXCOM7_IO4         | 0     | 3      | PIO, I, PU, ST                                  |          |  |

|               |               |         |           |     | A      | QIO1                 | 1/0   | 1      |                                                 |          |  |

| 62            | VDD3V3        | PC12    | _         | -   | В      | FLEXCOM7_IO1         | I/O   | 3      | PIO, I, PU, ST                                  |          |  |

|               |               |         |           |     | A      | QIO0                 | I/O   | 1      |                                                 |          |  |

| 63            | VDD3V3        | PC13    | -         | -   | В      | FLEXCOM7_IO0         | I/O   | 3      | PIO, I, PU, ST                                  |          |  |

|               |               |         |           |     | Α      | QCS                  | 0     | 1      |                                                 |          |  |

| 64            | VDD3V3        | PC14    | WKUP13    | ı   | В      | FLEXCOM7_IO3         | I/O   | 3      | PIO, I, PU, ST                                  |          |  |

|               |               | . 014   |           |     | D      | TIOA7                | I/O   | 1      |                                                 |          |  |

|               |               |         |           |     | Α      | QSCK                 | 0     | 1      |                                                 |          |  |

| 1             | VDD3V3        | PC15    | -         | -   | В      | FLEXCOM7_IO2         | I/O   | 3      | PIO, I, PU, ST                                  |          |  |

|               |               |         | . 510     |     | D      | TIOB7                | I/O   | 1      |                                                 |          |  |

|               |               |         |           |     | Α      | FLEXCOM6_IO2         | I/O   | 1      |                                                 |          |  |

| 2             | VDD3V3        | PC18    | -         | _   | В      | FLEXCOM6_IO4         | 0     | 2      | PIO, I, PU, ST                                  |          |  |

|               |               |         |           |     | D      | TIOB8                | I/O   | 1      |                                                 |          |  |

|               |               |         |           |     | D      | HORA                 | 1/0   | I      |                                                 |          |  |

| co                      | ntinued                             |                |           |     |      |                |     |        |                                                 |                                                                   |

|-------------------------|-------------------------------------|----------------|-----------|-----|------|----------------|-----|--------|-------------------------------------------------|-------------------------------------------------------------------|

|                         |                                     | Primary        | Alternate |     |      | PIO Peripheral |     |        | Reset State                                     |                                                                   |

| VQFN64<br>Pin<br>Number | Power Rail/<br>Voltage<br>Reference | Signal         | Signal    | Dir | Func | Signal         |     | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>SEC, FILTER | Comments                                                          |

| 3                       | VDD3V3                              | PC19           | _         | _   | Α    | FLEXCOM6_IO3   | I/O |        | PIO, I, PU, ST                                  |                                                                   |

|                         |                                     |                |           |     | D    | TCLK8          | I   | 1      |                                                 |                                                                   |

| 4                       | VDD3V3                              | PC20           | -         | -   | A    | FLEXCOM7_IO1   | I/O | 4      | PIO, I, PU, ST                                  |                                                                   |

| 5                       | VDD3V3                              | PC21           | WKUP14    | I   | Α    | FLEXCOM7_IO0   | I/O | 4      | PIO, I, PU, ST                                  |                                                                   |

| 6                       | VDD3V3                              | PC22           | RTCOUT1   | 0   | Α    | PCK0           | 0   | 1      | PIO, I, PD, ST                                  |                                                                   |

| 10                      | VDD3V3                              | PD17           | _         | _   | A    | PWML0          | 0   | 1      | PIO, I, PD, ST                                  |                                                                   |

|                         |                                     |                |           |     | C    | TIOA11         | I/O | 1      |                                                 |                                                                   |

|                         |                                     |                |           |     | A    | PWML1          | 0   | 1      |                                                 |                                                                   |

| 11                      | VDD3V3                              | PD18           | _         | -   | В    |                | I/O | 1      | PIO, I, PD, ST                                  |                                                                   |

|                         |                                     |                |           |     | С    | TIOB11         | I/O | 1      |                                                 |                                                                   |

|                         |                                     |                |           |     | Α    | PWML2          | 0   | 1      |                                                 |                                                                   |

| 12                      | VDD3V3                              | PD19           | _         | -   | В    | _              | 0   | 1      | PIO, I, PD, ST                                  |                                                                   |

|                         |                                     |                |           |     | С    | TCLK11         | I   | 1      |                                                 |                                                                   |

| 22                      | VDD3V3                              | NRST           | _         | -   | -    | _              | -   |        | I, PU, ST                                       |                                                                   |

| 28                      | VDDBU                               | FWUP           | -         | 1   | -    | _              | -   | -      | I,ST                                            | Active low, external pull-up needed                               |

| 29                      |                                     | JTAGSEL        | -         | 1   | -    |                | -   | -      | I,PD                                            |                                                                   |

| 33                      |                                     | SHDN           | _         | 0   | -    | -              | _   | -      | 0                                               | The device is in Backup mode     The device is not in Backup mode |

| 32                      |                                     | TST            | _         | I   | _    | -              | -   | -      | I,PD                                            |                                                                   |

| 27                      |                                     | RTCOUT0        | _         | I   | _    | -              | -   | -      | 0                                               |                                                                   |

| 26                      |                                     | WKUP2/<br>TMP2 | _         | ı   | -    | -              | -   | -      | I,ST                                            | External pull-up needed                                           |

| 31                      |                                     | XOUT32         | _         | 0   | -    | _              | -   | -      | -                                               |                                                                   |

| 30                      |                                     | XIN32          | -         | 1   | -    | -              | -   | -      | -                                               | Clock input when oscillator is in Bypass mode                     |

| 9                       | VDD3V3                              |                | -         | -   | -    | -              | -   | -      | -                                               |                                                                   |

| 25                      | VBAT                                |                | _         | -   | -    | -              | -   | -      | -                                               |                                                                   |

| 24                      | VDD3V3                              |                | _         | -   | _    | -              | -   | -      | -                                               |                                                                   |

| 42                      | VDD3V3                              |                | _         | -   | -    | -              | -   | -      | -                                               |                                                                   |

| 54                      | VDD3V3                              |                | -         | -   | -    | -              | -   | -      | -                                               |                                                                   |

| 61                      | VDD3V3                              |                | -         | -   | -    | _              | -   | -      | _                                               |                                                                   |

| 19                      | VDDCORE                             |                | -         | -   | _    | -              | -   | -      | -                                               |                                                                   |

| 23                      | VDDCORE                             | POWER          | -         | -   | -    | -              | -   | -      | -                                               |                                                                   |

| 53                      | VDDCORE                             | . 5.1.2.1      | _         | -   | _    | -              | -   | -      | -                                               |                                                                   |

| 58                      | VDDCORE                             |                | _         | -   | _    | -              | -   | -      | -                                               |                                                                   |

| 41                      | VDDPLL                              |                | _         | -   | _    | _              | -   | -      | _                                               |                                                                   |

| 20                      | VDDOUT                              |                | _         | -   | _    | _              | -   | -      | _                                               |                                                                   |

| 21                      | VDD3V3                              |                | _         | -   | _    | _              | -   | _      | _                                               |                                                                   |

| 38                      | VREFP                               |                | _         | -   | _    | _              | -   | _      | _                                               |                                                                   |

| 65                      | GND                                 |                | _         | -   | _    | _              | -   | _      | _                                               | Digital ground (exposed pad)                                      |

Table 3-2. 128-pin EP-TQFP Multiplexing

| TOED429 | Power Rail/          | Primary | Alternate |     |      | PIO Peripheral |     |        | Reset State                                |          |

|---------|----------------------|---------|-----------|-----|------|----------------|-----|--------|--------------------------------------------|----------|

| Pin     | Voltage<br>Reference | Signal  | Signal [  | Dir | Func | Signal         | Dir | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>FILTER | Comments |

| 16      | VDD3V3               | PA0     | -         | -   | Α    | FLEXCOM6_IO0   | -   | _      | _                                          |          |

|               | 4!al                 |         |            |     |          |                |          |        |                                            |          |

|---------------|----------------------|---------|------------|-----|----------|----------------|----------|--------|--------------------------------------------|----------|

| con           | tinuea               | Duimon  | Alternate  | _   |          | DIO Barinharal | _        |        | Booot State                                |          |

| TQFP128       | Power Rail/          | Primary | Alternate  |     | <u> </u> | PIO Peripheral |          |        | Reset State                                |          |

| Pin<br>Number | Voltage<br>Reference | Signal  | Signal     | Dir | Func     | Signal         | Dir      | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>FILTER | Comments |

| 17            | VDD3V3               | PA1     | -          | -   | Α        | FLEXCOM6_IO1   | -        | -      | _                                          |          |

| 27            | VDD3V3               | PA2     | WKUP3/TMP3 | ı   | A<br>B   | PCK1<br>TIOA0  | 0<br>I/O | 1 2    | PIO, I, PU, ST                             |          |

| 28            | VDD3V3               | PA3     | WKUP4/TMP4 | 1   | Α        | TIOB0          | I/O      | 2      | PIO, I, PU, ST                             |          |

| 29            | VDD3V3               | PA4     | _          | _   | Α        | FLEXCOM0_IO0   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 30            | VDD3V3               | PA5     | WKUP5      | 1   | Α        | FLEXCOM0_IO1   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

|               |                      |         |            |     | Α        | FLEXCOM0_IO2   | I/O      | 1      |                                            |          |

| 31            | VDD3V3               | PA6     | _          | _   | В        | FLEXCOM0_IO4   | 0        | 2      | PIO, I, PU, ST                             |          |

|               |                      |         |            |     | С        | TIOA6          | I/O      | 1      | -,,,,,,                                    |          |

|               |                      |         |            |     | Α        | FLEXCOM0_IO3   | I/O      | 1,2    |                                            |          |

| 32            | VDD3V3               | PA7     | _          | -   | С        | TIOB6          | I/O      | 1      | PIO, I, PU, ST                             |          |

| 5             | VDD3V3               | PA8     | _          | _   | A        | FLEXCOM1_IO0   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 6             | VDD3V3               | PA9     | WKUP6      |     | A        | FLEXCOM1_IO1   | 1/0      | 1,2    | PIO, I, PU, ST                             |          |

| 0             | VDD3V3               | 173     | WINOI O    | _   | A        | FLEXCOM1_IO2   | 1/0      | 1,2    | 1 10, 1, 1 0, 01                           |          |

| 25            | \/DD3\/3             | DA 10   |            |     |          |                | -        |        | DIO I DII ST                               |          |

| 25            | VDD3V3               | PA10    | _          | _   | В        | FLEXCOM1_IO4   | 0        | 2      | PIO, I, PU, ST                             |          |

|               |                      |         |            |     | С        | TCLK6          | 1        | 1      |                                            |          |

| 26            | VDD3V3               | PA11    | _          | _   | Α        | FLEXCOM1_IO3   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 37            | VDD3V3               | PA12    | -          | -   | Α        | FLEXCOM2_IO0   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 38            | VDD3V3               | PA13    | WKUP7      | ı   | Α        | FLEXCOM2_IO1   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 39            | VDD3V3               | PA14    | _          | _   | Α        | FLEXCOM2_IO2   | I/O      | 1      | PIO, I, PU, ST                             |          |

|               | VBB010               | 17411   |            |     | В        | FLEXCOM2_IO4   | 0        | 2      | 1 10, 1, 1 0, 01                           |          |

| 40            | VDD3V3               | PA15    | _          | -   | Α        | FLEXCOM2_IO3   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 33            | VDD3V3               | PA16    | _          | -   | Α        | FLEXCOM3_IO0   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 34            | VDD3V3               | PA17    | _          | -   | Α        | FLEXCOM3_IO1   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 25            | \/DD3\/3             | DA 10   |            |     | Α        | FLEXCOM3_IO2   | I/O      | 1      | DIO I DII ST                               |          |

| 35            | VDD3V3               | PA18    | _          | _   | В        | FLEXCOM3_IO4   | 0        | 2      | PIO, I, PU, ST                             |          |

| 36            | VDD3V3               | PA19    | _          | -   | Α        | FLEXCOM3_IO3   | I/O      | 1,2    | PIO, I, PU, ST                             |          |

| 46            | VDD3V3               | PA20    | _          | -   | Α        | PCK0           | 0        | 2      | PIO, I, PU, ST                             |          |

|               |                      |         |            |     | Α        | COM0           | 0        | 1      |                                            |          |

| 63            | VDD3V3               | PA21    | _          | -   | В        | FLEXCOM5_IO3   | I/O      | 5,6    | PIO, I, PD, ST                             |          |

|               |                      |         |            |     | Α        | COM1           | 0        | 1      |                                            |          |

| 64            | VDD3V3               | PA22    | _          | _   | В        | FLEXCOM5_IO2   | I/O      | 5      | PIO, I, PD, ST                             |          |

|               |                      |         |            |     | С        | FLEXCOM5_IO4   | 0        | 6      |                                            |          |

|               |                      |         |            |     | Α        | COM2           | 0        | 1      |                                            |          |

| 65            | VDD3V3               | PA23    | _          | _   | В        | FLEXCOM5_IO1   | I/O      | 5,6    | PIO, I, PD, ST                             |          |

|               | VBBOVO               | 17120   |            |     | D        | TCLK0          | ı,c      | 1      | 1 10, 1, 1 5, 01                           |          |

|               |                      |         |            |     |          | COM3           |          |        |                                            |          |

| 66            | VDD3V3               | PA24    |            |     | A        |                | 0        | 1      | DIO I DD CT                                |          |

| 00            | VDD3V3               | FMZ4    | _          | -   | В        | FLEXCOM5_IO0   | 1/0      | 5,6    | PIO, I, PD, ST                             |          |

|               |                      |         |            |     | D        | TIOB0          | 1/0      | 1      |                                            |          |

| 07            | \/D50\/2             | D. 4.05 |            |     | A        | COM4           | 0        | 1      | DIO 1 DE 27                                |          |

| 67            | VDD3V3               | PA25    | _          | -   | В        | FLEXCOM6_IO0   | I/O      | 4,5    | PIO, I, PD, ST                             |          |

|               |                      |         |            |     | D        | TIOA0          | I/O      | 1      |                                            |          |

| 68            | VDD3V3               | PA26    | _          | _   | Α        | COM5           | 0        | 1      | PIO, I, PD, ST                             |          |

|               |                      |         |            |     | В        | FLEXCOM6_IO1   | I/O      | 4,5    |                                            |          |

| cor           | ntinued              |             |                   |     |        |                |      |        |                                            |                                                |

|---------------|----------------------|-------------|-------------------|-----|--------|----------------|------|--------|--------------------------------------------|------------------------------------------------|

| TOFP128       | Power Rail/          | Primary     | Alternate         |     |        | PIO Peripheral |      |        | Reset State                                |                                                |

| Pin<br>Number | Voltage<br>Reference | Signal      | Signal            | Dir | Func   | Signal         | Dir  | IO Set | Signal, Dir, PU,<br>PD, HiZ, ST,<br>FILTER | Comments                                       |

|               |                      |             |                   |     | Α      | COM6           | 0    | 1      |                                            |                                                |

| 69            | VDD3V3               | PA27        | _                 | -   | В      | FLEXCOM6_IO2   | I/O  | 4      | PIO, I, PD, ST                             |                                                |

|               |                      |             |                   |     | С      | FLEXCOM6_IO4   | 0    | 5      |                                            |                                                |

| 70            | VDD3V3               | PA28        | _                 | _   | Α      | COM7           | 0    | 1      | PIO, I, PD, ST                             |                                                |

|               | 122010               |             |                   |     | В      | FLEXCOM6_IO3   | I/O  | 4,5    | , ,                                        |                                                |

|               |                      |             | AD0/              |     | Α      | SEG0           | 0    | 1      | -                                          | Clock input when oscillator is in Bypass mode  |

| 71            | VDD3V3               | PA29        | ACC_INP0/         | 1   | В      | FLEXCOM0_IO4   | 0    | 1      | PIO, I, PD, ST                             |                                                |

|               |                      |             | XIN               |     | С      | FLEXCOM1_IO4   | 0    | 1      | -                                          |                                                |

|               |                      |             |                   |     | D      | FLEXCOM2_IO4   | 0    | 1      |                                            | -                                              |

| 72            | VDD3V3               | PA30        | AD1/ACC_INP1      | ı   | Α      | SEG1           | 0    | 1      | PIO, I, PD, ST                             | -                                              |

|               |                      |             |                   |     | A      | SEG4           | 0    | 1      |                                            |                                                |

| 74            | VDD3V3               | PB1         | AD4/ACC_INN1      | 1   | В      | FLEXCOM7_IO3   | I/O  | 1,2    | PIO, I, PD, ST                             | ADCx/ACCx Signals: Pull-down must be disabled  |

|               |                      |             |                   |     | С      | PCK1           | 0    | 2      | _                                          | in PIO Controller when using these PIO pins as |

|               |                      |             |                   |     | D      | TCLK1          |      | 1      |                                            | ADC/ACC inputs.                                |

| 7.5           | 1,000,00             | <b>DD</b> 0 | AD3/              |     | A      | SEG3           | 0    | 1      | DIO I DD OT                                | XIN/OUT Signals: Pull-down must be disabled    |

| 75            | VDD3V3               | PB0         | ACC_INN0/<br>XOUT | I/O |        | FLEXCOM3_IO4   | 0    | 1      | PIO, I, PD, ST                             | in PIO Controller when using these PIO pins as |

|               |                      |             | 7,001             |     | D      | TIOB1          | 1/0  | 1      |                                            | Crystal Oscillator XIN/XOUT signals.           |

|               |                      |             |                   |     | A      | SEG5           | 0    | 1      | -                                          |                                                |

| 76            | VDD3V3               | PB2         | ERASE             | 1   | В      | FLEXCOM7_IO2   | 1/0  | 1      | ERASE, I, PD, ST                           |                                                |

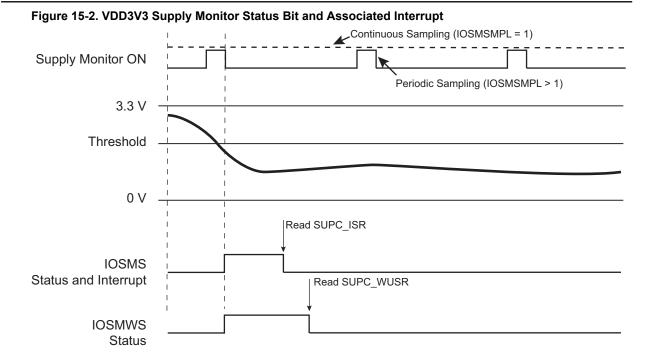

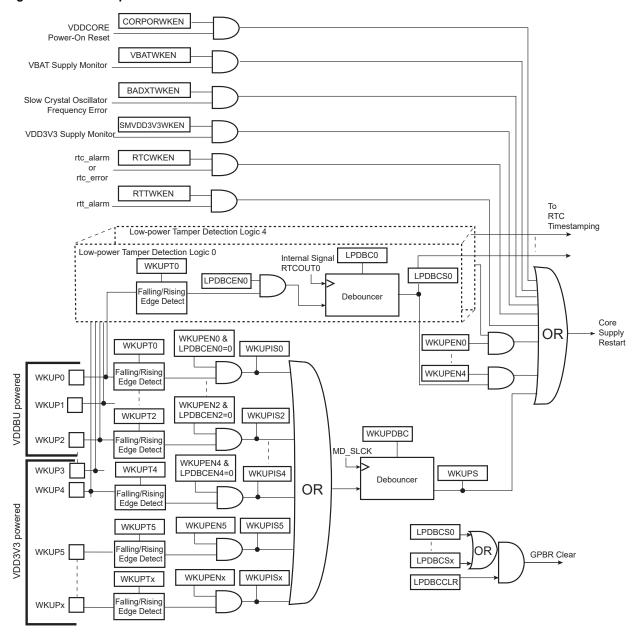

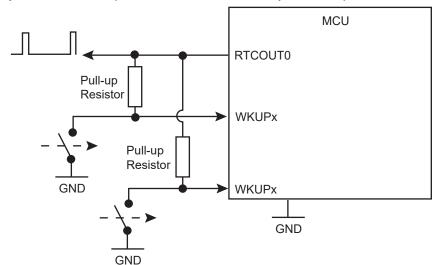

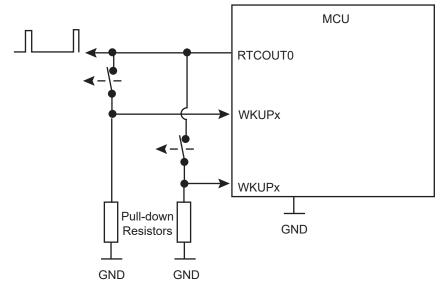

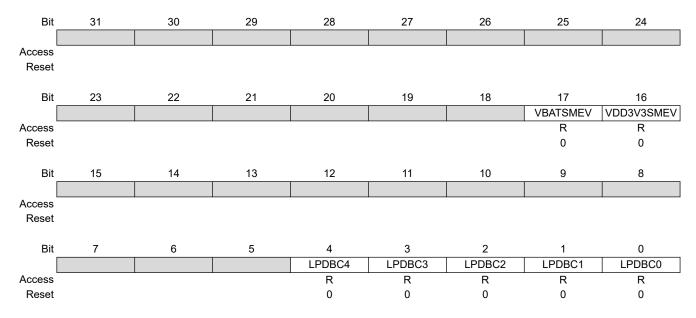

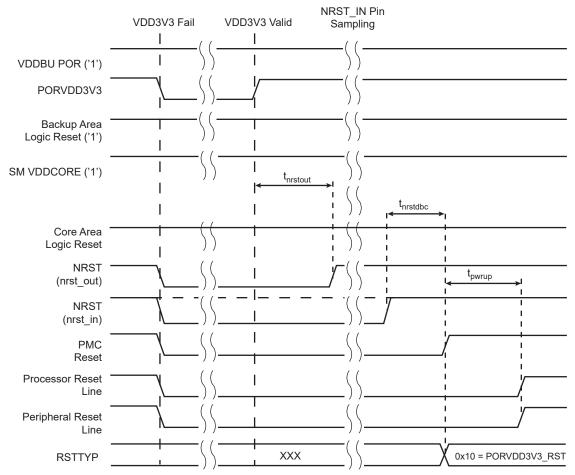

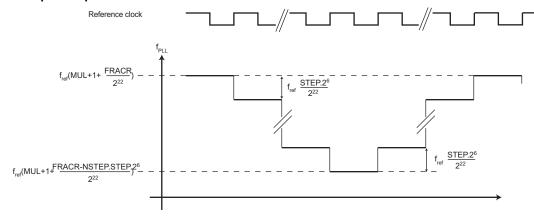

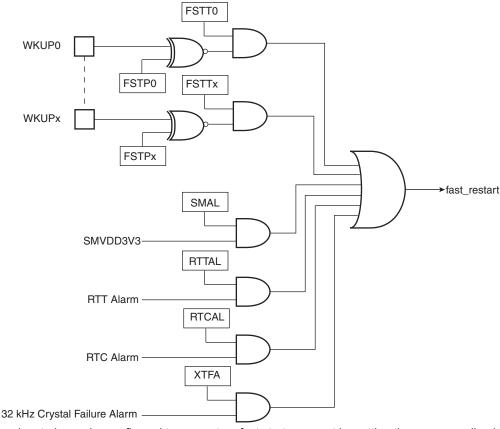

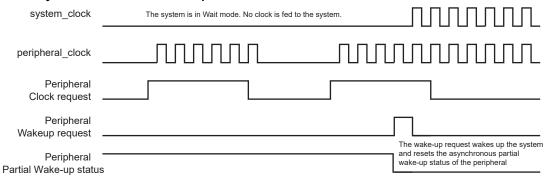

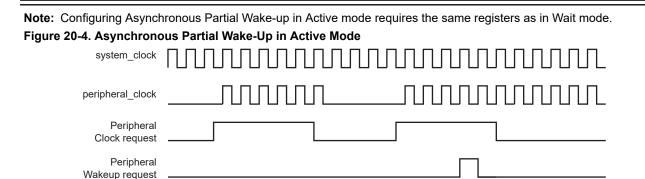

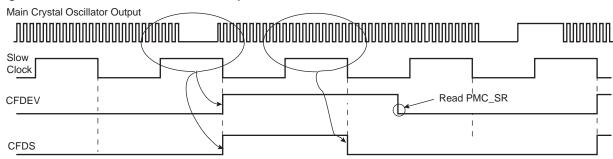

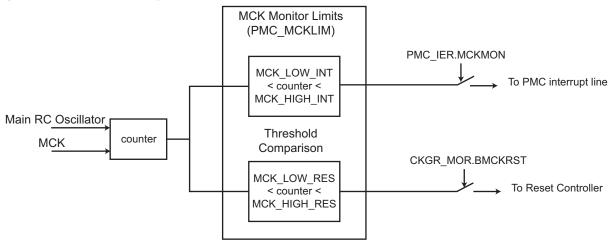

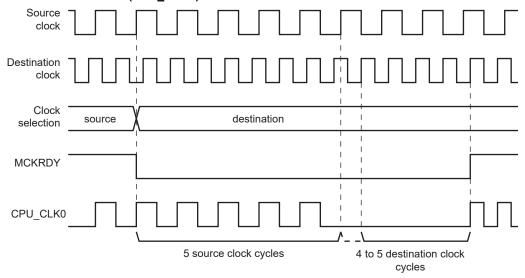

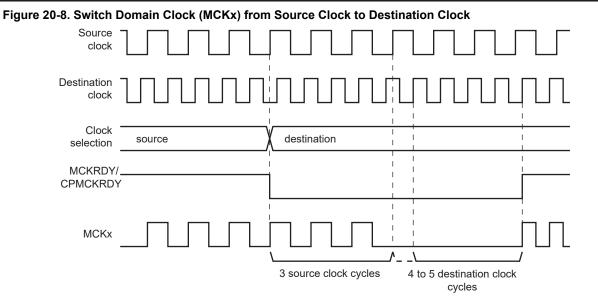

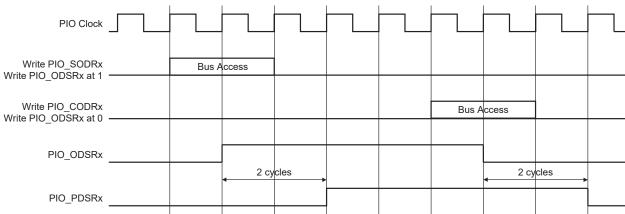

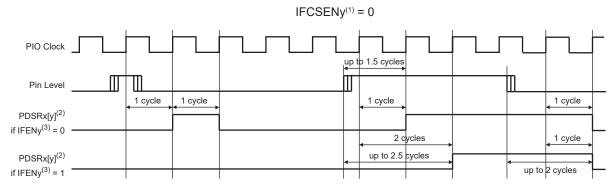

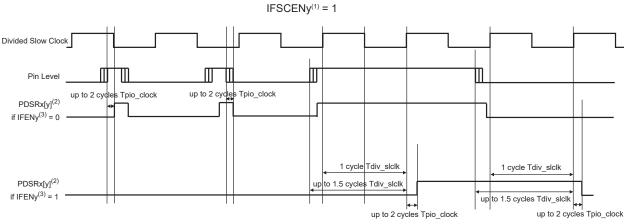

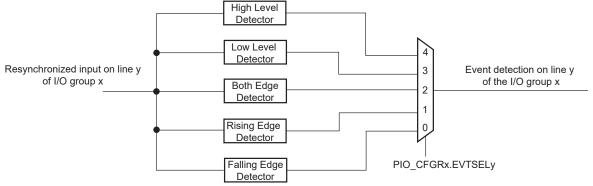

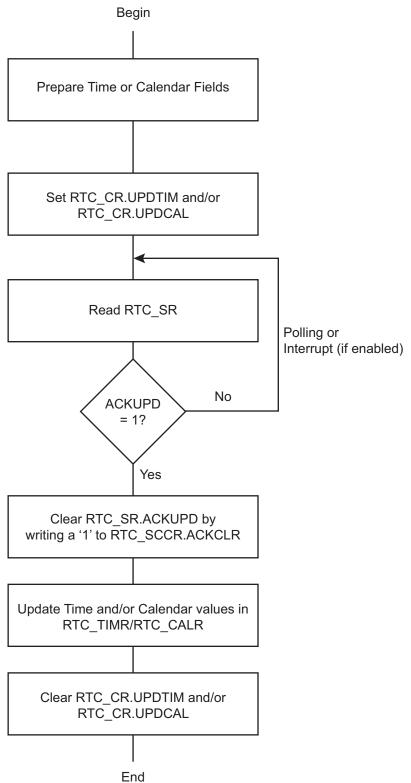

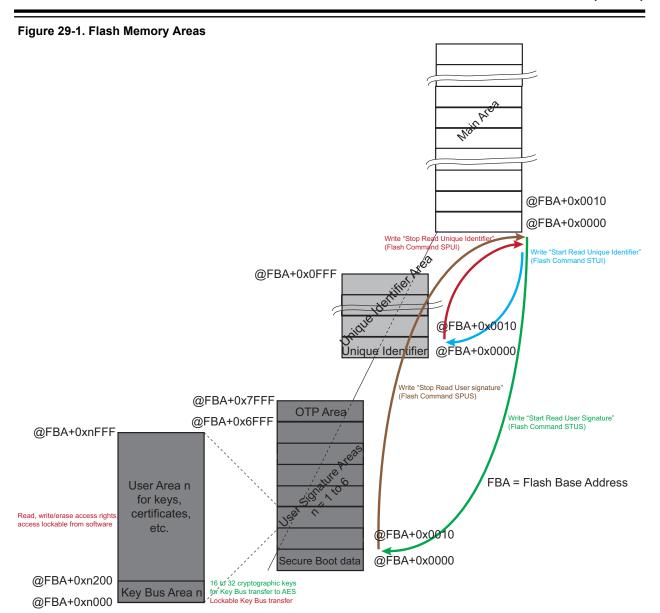

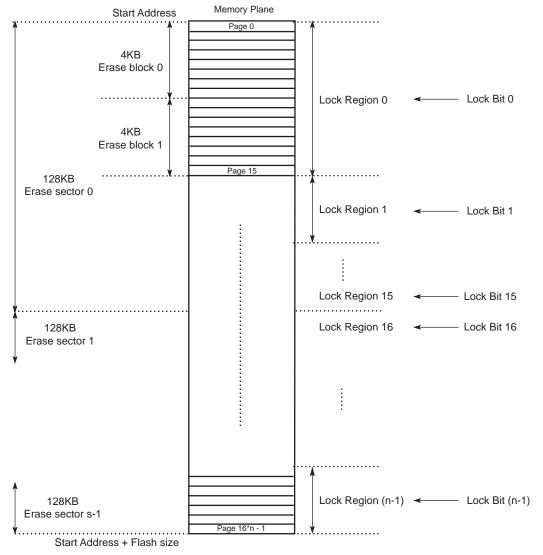

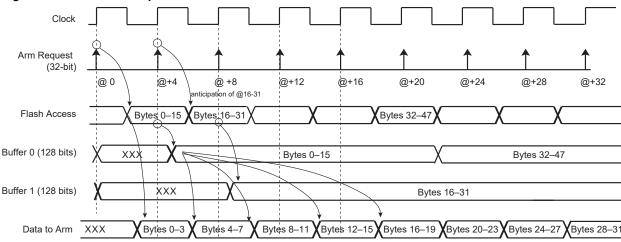

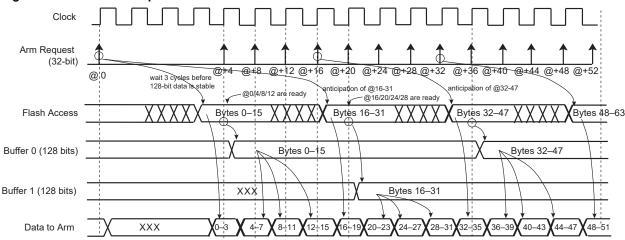

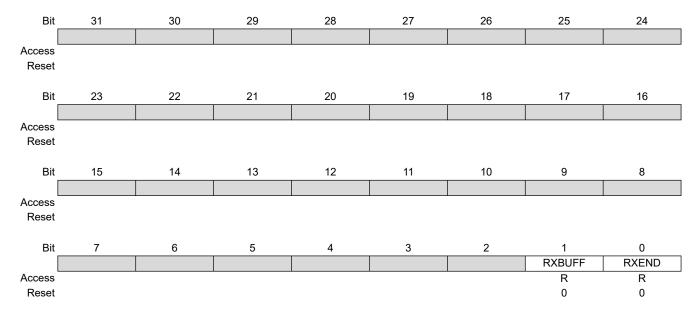

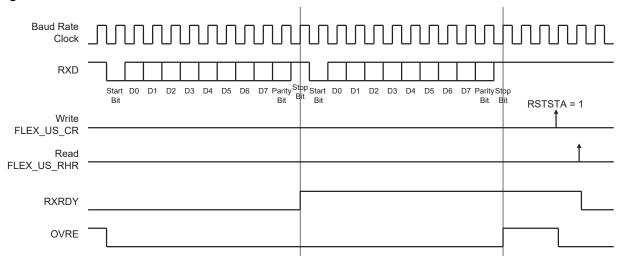

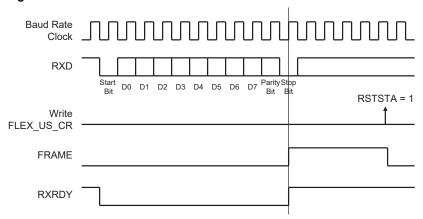

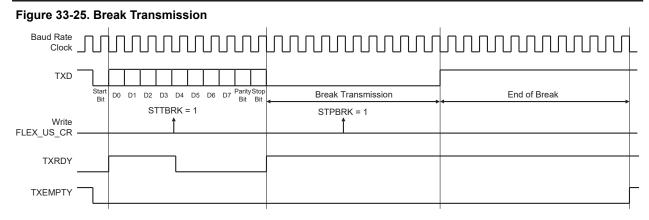

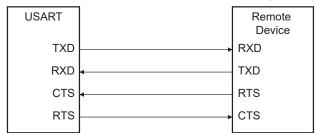

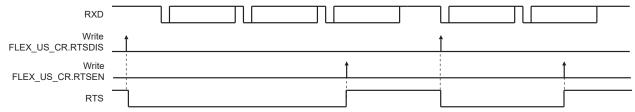

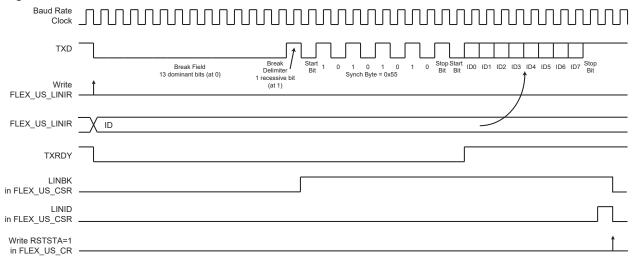

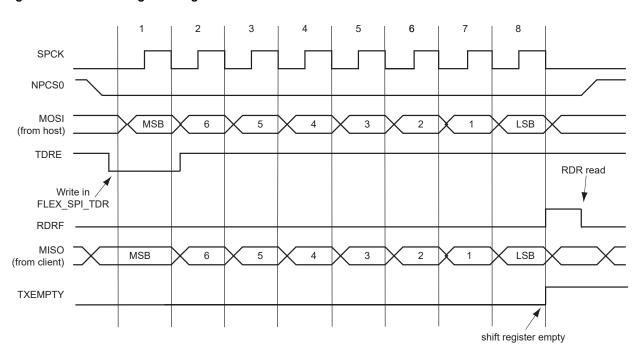

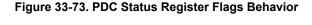

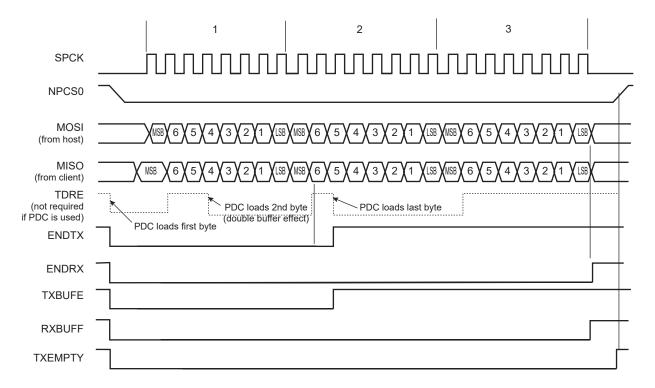

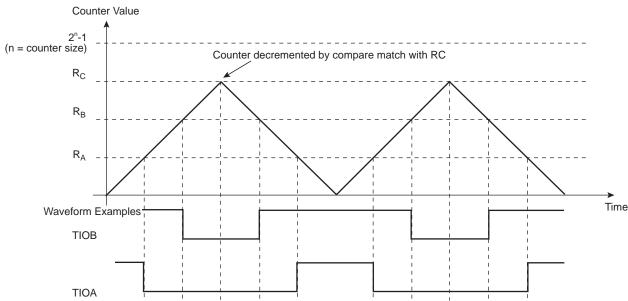

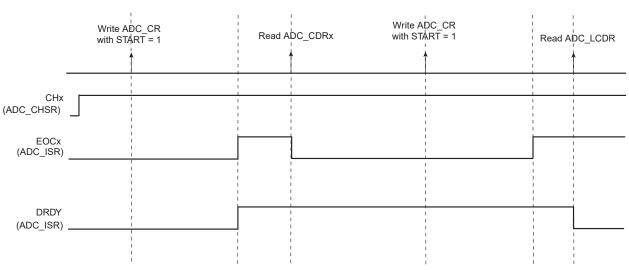

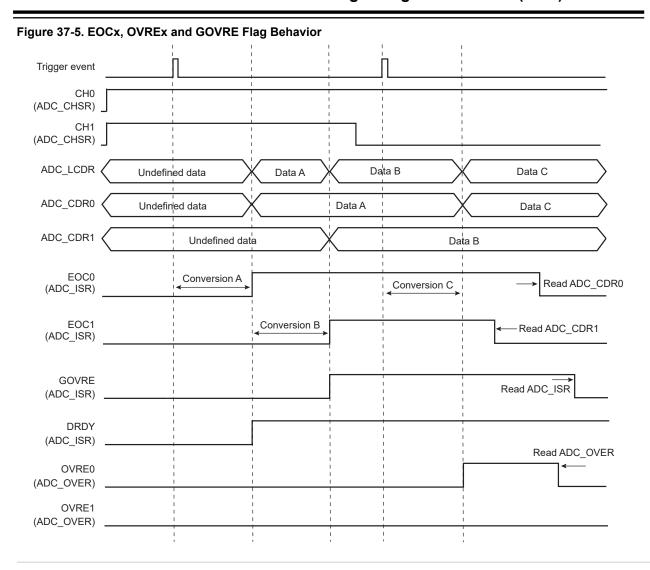

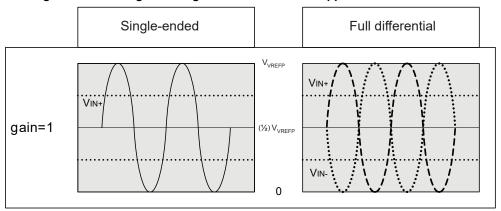

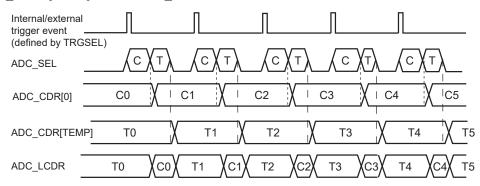

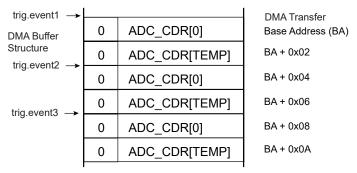

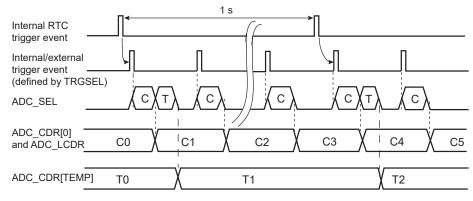

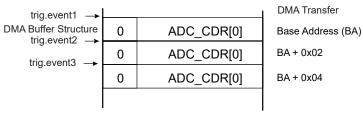

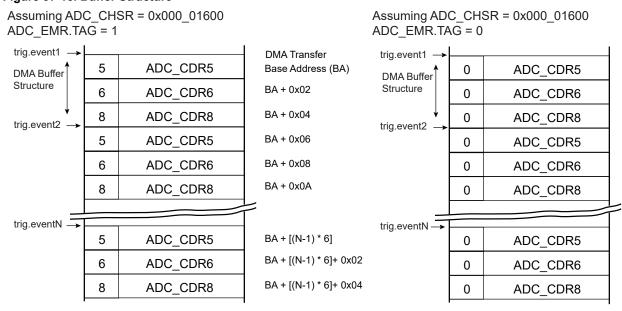

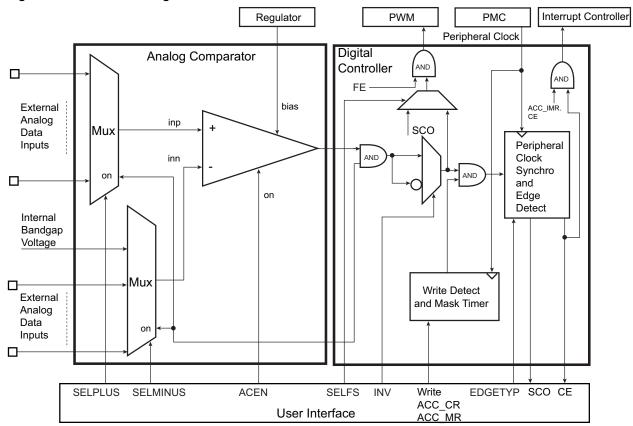

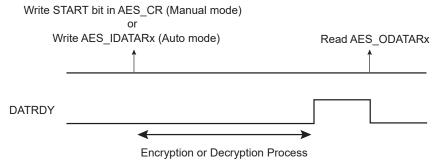

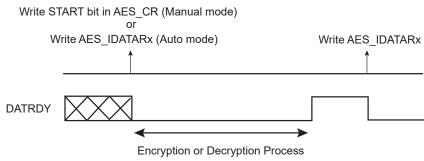

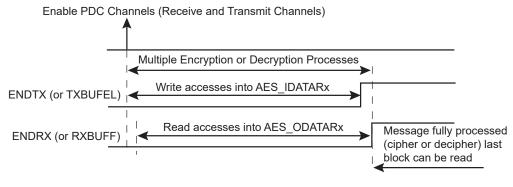

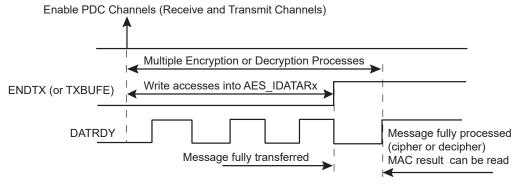

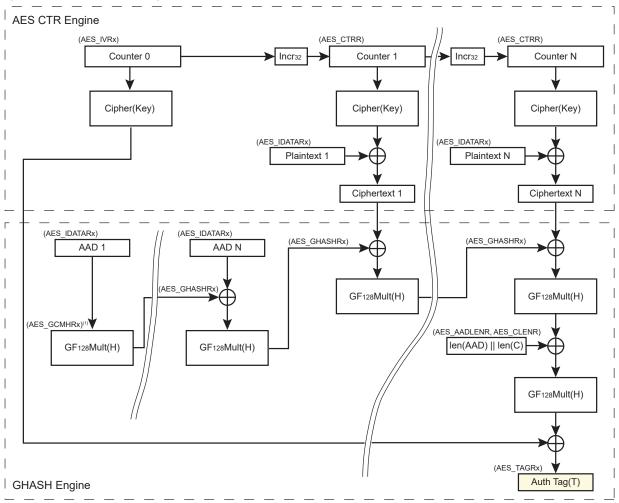

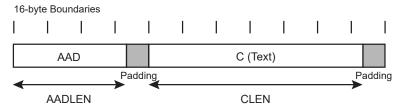

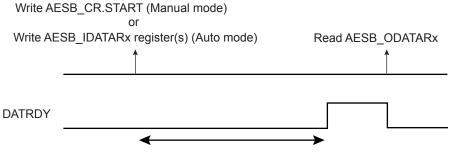

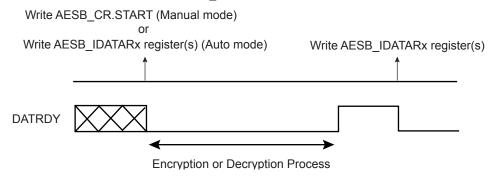

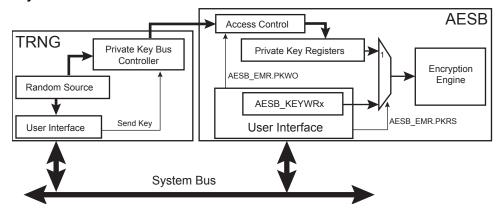

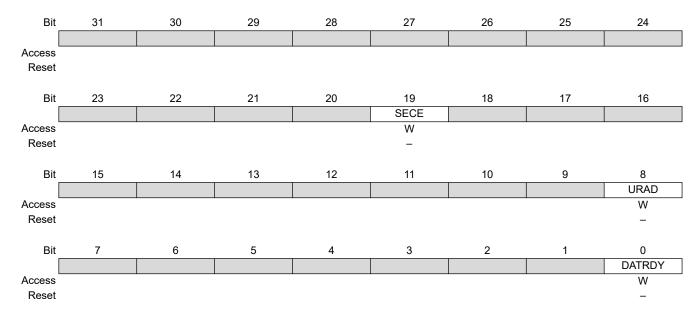

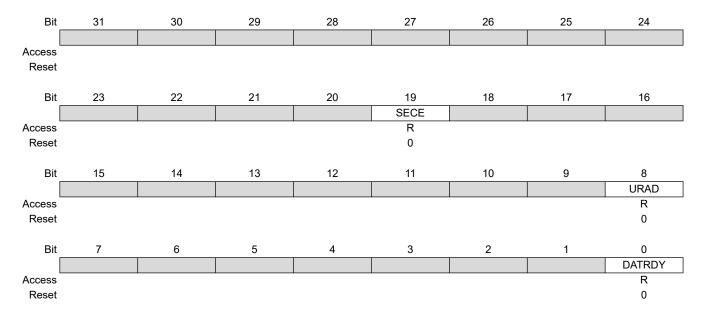

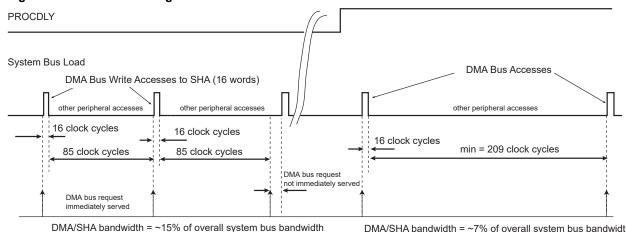

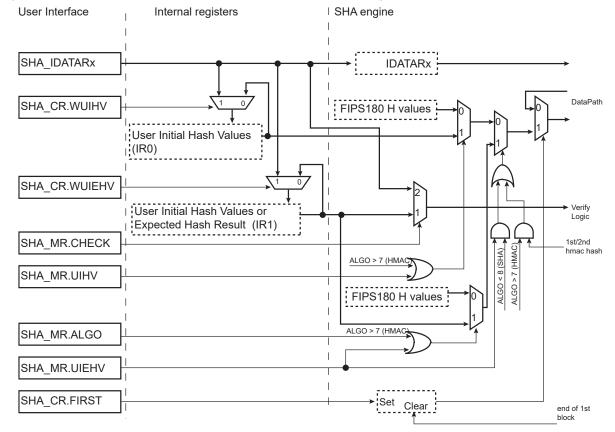

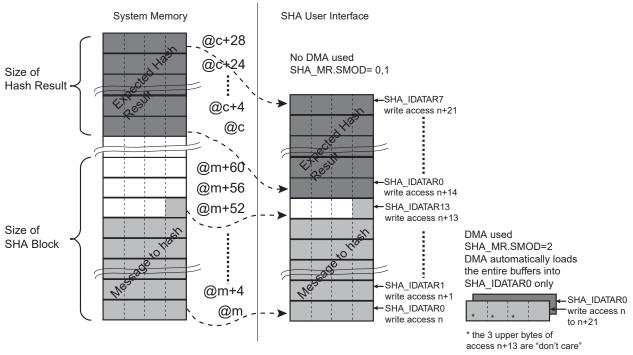

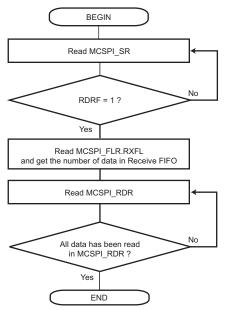

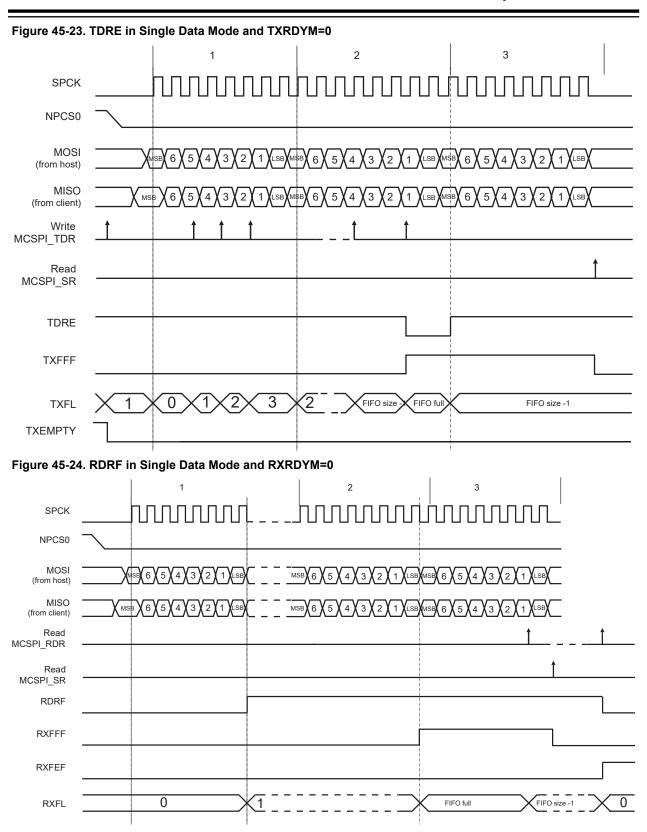

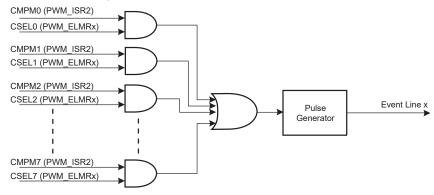

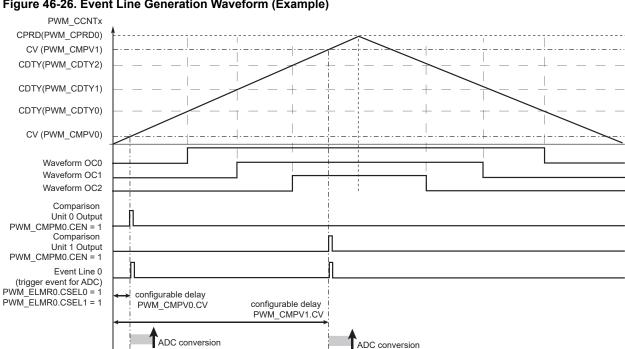

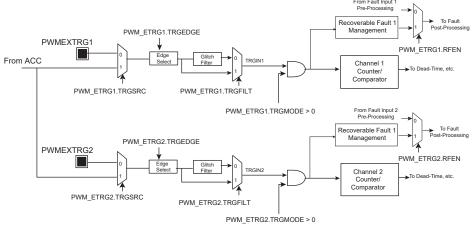

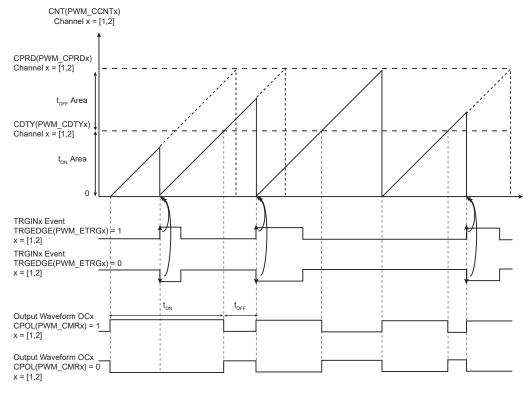

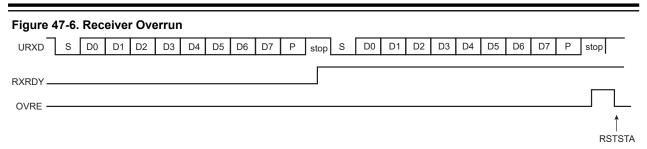

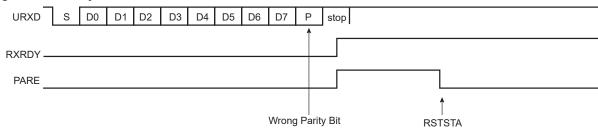

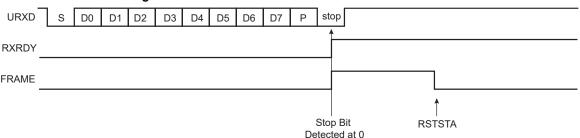

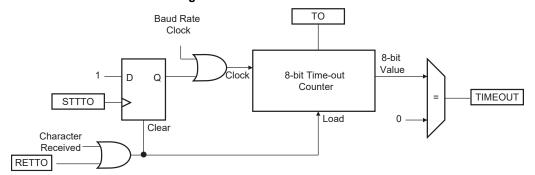

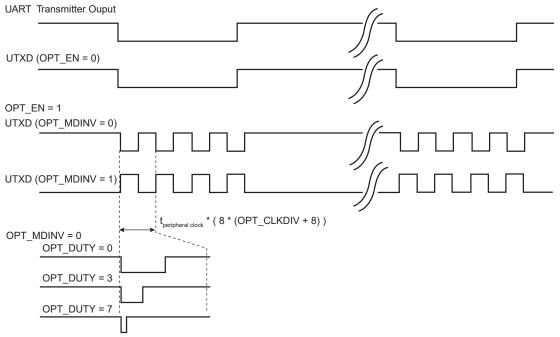

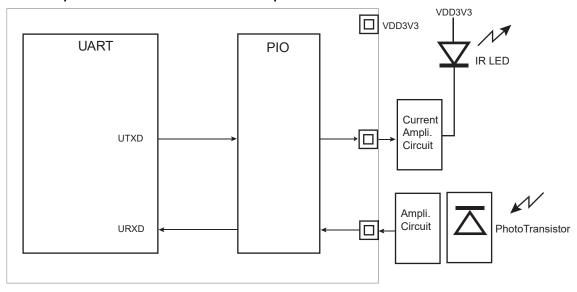

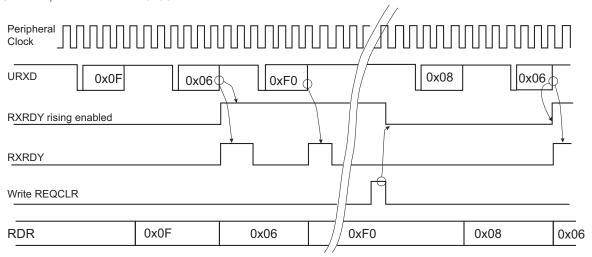

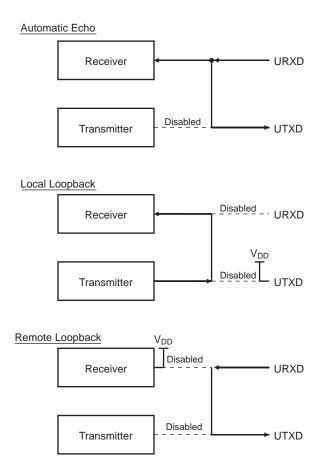

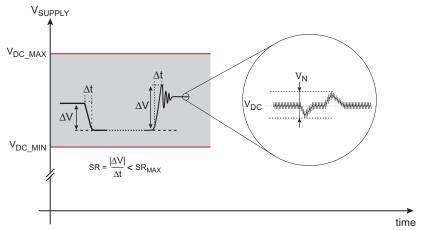

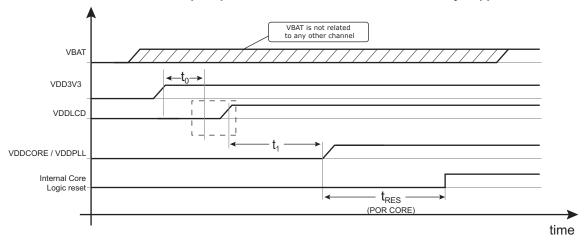

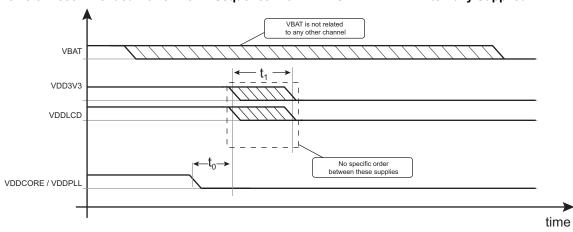

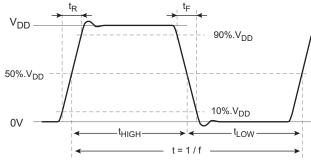

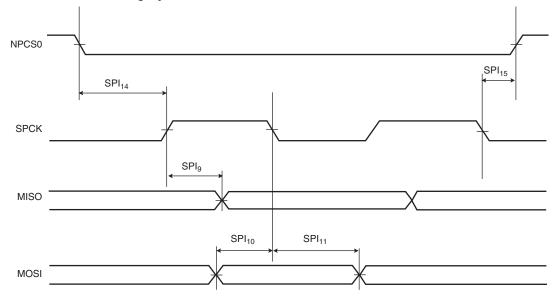

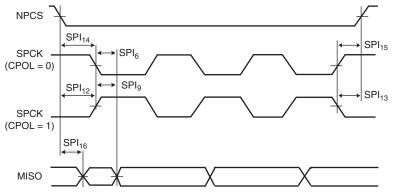

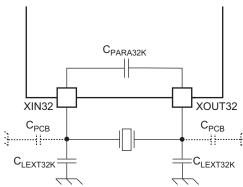

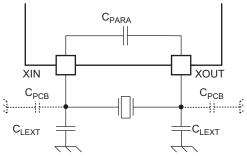

|               |                      |             |                   |     | С      | FLEXCOM7_IO4   | 0    | 2      | -                                          |                                                |