#### WS74285

# **Dual-Channel High-Precision High-Voltage Current-Sense Amplifier**

## **Descriptions**

The WS74285 dual-channel high-side current-sense amplifier has precision accuracy specifications of  $V_{\rm OS}$  less than  $70\mu V$  (max) and gain error less than 0.1%(max).

The WS74285 features an input common-mode voltage range from 2.7V to 76V with 400kHz of small-signal bandwidth, which makes it ideal for interfacing with a SARADC for multichannel multiplexed data acquisition systems.

The WS74285 operates over the -40°C to +125°C temperature range. The WS74285 is offered in 8-pin MSOP and CSP package.

## **Applications**

- Base Stations and Communication Equipment

- Power Management Systems

- Server Backplanes

- Industrial Control and Automation

#### **Features**

- 2.7V to 76V Input Common Mode

- Low 70µV (max) Input Offset Voltage

- Low 0.1% (max) Gain Error

- Gain Options

- G = 12.5V/V (WS74285x1)

- G = 20V/V (WS74285)

- G = 50V/V (WS74285x3)

- G = 100V/V (WS74285x4)

- 8-Pin MSOP Package

- 8-Pin CSP Package

#### Http://www.omnivision-group.com

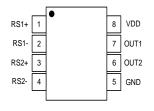

MSOP-8L

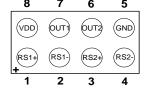

CSP-8L

MSOP-8L (Top view)

CSP-8L (Bottom view)

Pin configuration

CSP-8L

#### Marking

4285 = Device code

GM, SA = Special code

Y = Year code

W = Week code

#### **Order Information**

| Device        | Package | Shipping        |

|---------------|---------|-----------------|

| WS74285M-8/TR | MSOP-8L | 4000/Reel &Tape |

| WS74285C-8/TR | CSP-8L  | 3000/Reel &Tape |

**Pin Descriptions**

| Pin Number | Symbol | Descriptions                                      |

|------------|--------|---------------------------------------------------|

| 1          | RS1+   | Channel 1 External Resistor Power-Side Connection |

| 2          | RS1-   | Channel 1 External Resistor Load-Side Connection  |

| 3          | RS2+   | Channel 2 External Resistor Power-Side Connection |

| 4          | RS2-   | Channel 2 External Resistor Load-Side Connection  |

| 5          | GND    | Ground                                            |

| 6          | OUT2   | Output Channel2                                   |

| 7          | OUT1   | Output Channel1                                   |

| 8          | VDD    | Supply Voltage                                    |

# **Absolute Maximum Ratings**(1)

| Parameter                           | Symbol            | Value      | Unit |

|-------------------------------------|-------------------|------------|------|

| Supply Voltage, ([V+] - [V-])       | Vs <sup>(2)</sup> | 6          | V    |

| RS+, RS- to GND                     |                   | 80         | V    |

| RS+ to RS-                          |                   | ±10        | V    |

| Continuous Input Current (Any Pin)  |                   | ±10        | mA   |

| Output Short-Circuit Duration       | tso               | Unlimited  | /    |

| Operating Fee-Air Temperature Range | T <sub>A</sub>    | -40 to 125 | °C   |

| Storage Temperature Range           | $T_{STG}$         | -65 to 150 | °C   |

| Junction Temperature Range          | TJ                | 206        | °C   |

| Lead Temperature Range              | TL                | 300        | °C   |

| Soldering Temperature               |                   | 260        | °C   |

#### Note:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the

device. These are only stress ratings, and functional operation of the device at these or any other

conditions beyond those indicated under recommended operating conditions are not implied. Exposure

to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All voltage values, except differential voltage are with respect to network terminal.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | MIL-STD-883H Method 3015.8 | +2000         | V    |

| TIDIVI |                          | JEDEC-EIA/JESD22-A114A     | =====         | -    |

| MM     | Machine Model ESD        | JEDEC-EIA/JESD22-A115      | ±400          | V    |

| CDM    | Charged Device Model ESD | JEDEC-EIA/JESD22-C101E     | ±2000         | V    |

Will Semiconductor Ltd. 2 2023/08/16 – Rev. 1.1

# **Electronics Characteristics**

$V_{RS+} = V_{RS-} = +76V$ ,  $V_{DD} = +3.3V$ ,  $V_{SENSE} = V_{RS+} - V_{RS-} = 1 \text{mV}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+125 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}\text{C}$ .

| Symbol                              | Parameter                                                            | Conditions                                   | Min. | Тур. | Max. | Unit  |  |

|-------------------------------------|----------------------------------------------------------------------|----------------------------------------------|------|------|------|-------|--|

| DC Characteristics                  |                                                                      |                                              |      |      |      |       |  |

| V <sub>DD</sub>                     | Supply Voltage                                                       | Guaranteed by PSRR                           | 2.7  |      | 5.5  | V     |  |

|                                     | Complex Commant                                                      | T <sub>A</sub> = +25°C                       |      | 200  | 680  | μA    |  |

| $I_{DD}$                            | Supply Current                                                       | -40°C < T <sub>A</sub> < +125°C              |      |      |      | μA    |  |

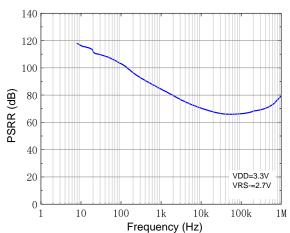

| PSRR                                | Power-Supply Rejection<br>Ratio                                      | 2.7V ≤ V <sub>DD</sub> ≤ 5.5V                | 100  | 130  |      | dB    |  |

| V <sub>CM</sub>                     | Input Common-Mode Voltage Range                                      | Guaranteed by CMRR                           | 2.7  |      | 76   | V     |  |

| I <sub>RS+</sub> , I <sub>RS-</sub> | Input Bias Current at V <sub>RS+</sub> and V <sub>RS-</sub> (Note 3) |                                              |      | 45   | 70   | μA    |  |

| I <sub>RS+</sub> , I <sub>RS-</sub> | Input Offset Current (Note 3)                                        |                                              |      | 100  |      | nA    |  |

| I <sub>RS+</sub> , I <sub>RS-</sub> | Input Leakage Current (Note 3)                                       | V <sub>DD</sub> = 0V, V <sub>RS+</sub> = 76V |      | 50   |      | nA    |  |

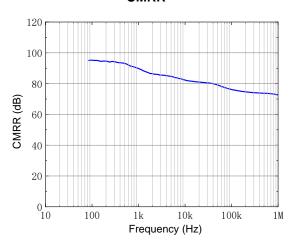

| CMRR                                | Common-Mode Rejection Ratio                                          | 2.7V < V <sub>RS+</sub> < 76V                | 120  | 150  |      | dB    |  |

| V                                   | Input Offset Voltage (Note                                           | T <sub>A</sub> = +25°C                       |      | ±10  | ±70  | μV    |  |

| Vos                                 | 3)                                                                   | -40°C ≤ T <sub>A</sub> ≤ +125°C              |      | ±20  |      | μV    |  |

| TCVos                               | Input Offset Voltage Drift (Note 3)                                  |                                              |      | 100  |      | nV/°C |  |

|                                     |                                                                      | G = 12.5 V/V                                 |      | 200  |      |       |  |

| V <sub>SENSE</sub>                  | Input Conco Voltago                                                  | G = 20 V/V                                   |      | 125  |      | mV    |  |

| V SENSE                             | Input Sense Voltage                                                  | G = 50 V/V                                   |      | 50   |      |       |  |

|                                     |                                                                      | G = 100 V/V                                  |      | 25   |      |       |  |

| G                                   | Gain                                                                 | Full-scale V <sub>SENSE</sub> = 125mV        |      | 20   |      | V/V   |  |

|                                     |                                                                      | T <sub>A</sub> = +25°C                       |      | 0.01 |      |       |  |

| GE                                  | Gain Error (Note 3)                                                  | -40°C ≤ T <sub>A</sub> ≤ +85°C               |      |      |      | %     |  |

|                                     |                                                                      | -40°C ≤ T <sub>A</sub> ≤ +125°C              |      |      |      |       |  |

| $V_{OL}$                            | Output Low Voltage                                                   | Sink 500µA                                   |      | 8    |      | mV    |  |

| VOL                                 | Output Low Voltage                                                   | No load                                      |      | 3    |      | mV    |  |

| Vон                                 | Output High Voltage to rail                                          | Source 500µA                                 |      | 7    |      | mV    |  |

| AC Chara                            | ncteristics                                                          |                                              |      |      |      |       |  |

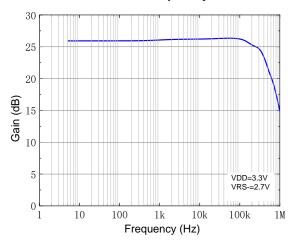

| BW -3dB                             | Signal Bandwidth                                                     | All gain configurations VSENSE > 5mV         |      | 400  |      | kHz   |  |

| AC PSRR                             | AC Power-Supply Rejection Ratio                                      | f = 200kHz                                   |      | 68   |      | dB    |  |

|                                     | •                                                                    |                                              | •    | •    | •    | •     |  |

Will Semiconductor Ltd. 3 2023/08/16 – Rev. 1.1

#### **Electronics Characteristics (continued)**

$V_{RS+} = V_{RS-} = +76V$ ,  $V_{DD} = +3.3V$ ,  $V_{SENSE} = V_{RS+} - V_{RS-} = 1 \text{mV}$ ,  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| AC CMRR           | AC CMRR                                         | £ 200kH=                                       | 1mV sine wave  | 87  | ٩D       |

|-------------------|-------------------------------------------------|------------------------------------------------|----------------|-----|----------|

|                   |                                                 | f = 200kHz                                     | 20mV sine wave | 80  | - dB     |

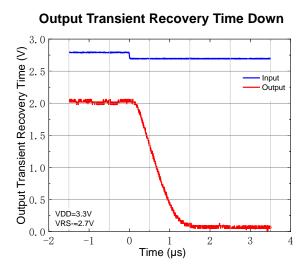

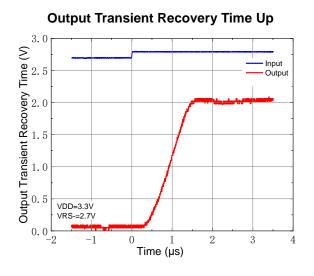

|                   | Output Transient Recovery Time                  | ΔVOUT = 2VP-P                                  |                | 1.5 | μs       |

|                   | Capacitive Load Stability                       | With 250Ω isolation resistor                   |                | 20  | nF       |

| C <sub>LOAD</sub> | Capacitive Load Stability                       | Without any isolation resistor                 |                | 200 | pF       |

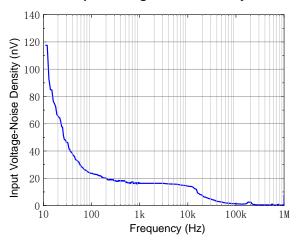

| e <sub>n</sub>    | Input Voltage-Noise Density                     | f = 1kHz                                       |                | 20  | nV/ √ Hz |

| THD               | Total Harmonic Distortion (Up to 7th Harmonics) | f = 1kHz, V <sub>OUT</sub> = 1V <sub>P-P</sub> |                | 60  | dB       |

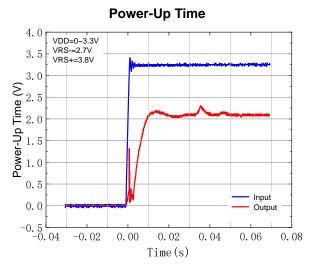

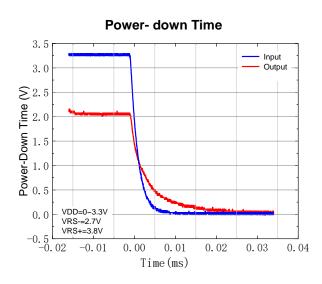

|                   | Power-Up Time (Note 5)                          |                                                |                | 50  | μs       |

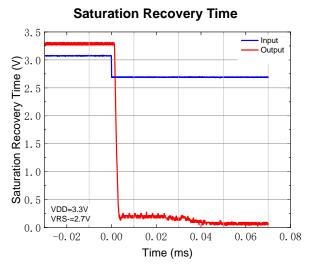

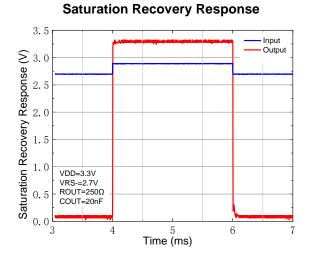

|                   | Saturation Recovery Time                        |                                                |                | 20  | μs       |

#### Note:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

- 2. All devices are 100% production tested at  $T_A = +25$ °C. All temperature limits are guaranteed by design.

- 3. Specifications are guaranteed by design, not production tested.

- 4. Gain and offset voltage are calculated based on two point measurements: V<sub>SENSE1</sub> and V<sub>SENSE2</sub>. V<sub>SENSE1</sub> = 20% x Full Scale V<sub>SENSE2</sub> = 80% x Full Scale V<sub>SENSE</sub>.

- 5. Output is high-Z during power-up.

Will Semiconductor Ltd. 4 2023/08/16 – Rev. 1.1

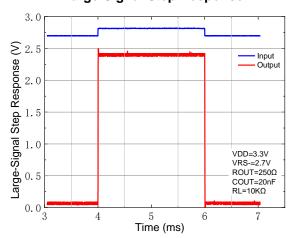

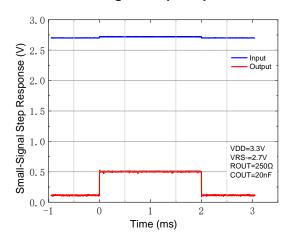

#### **Typical Characteristics**

$V_{RS+} = V_{RS-} = 76V$ ,  $V_{DD} = 3.3V$ ,  $V_{SENSE} = V_{RS+} - V_{RS-} = 1mV$ ,  $T_A = +25$ °C, unless otherwise noted.

# **Typical Characteristics (continued)**

$V_{RS+} = V_{RS-} = 76V$ ,  $V_{DD} = 3.3V$ ,  $V_{SENSE} = V_{RS+} - V_{RS-} = 1mV$ ,  $T_A = +25$ °C, unless otherwise noted.

## Large-Signal Step Response

#### **Small-Signal Step Response**

#### Gain vs. Frequency

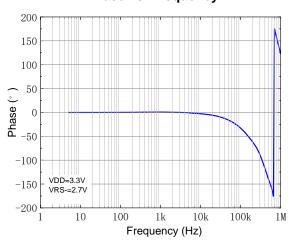

#### Phase vs. Frequency

#### **CMRR**

## **Power-Supply Rejection Ratio**

# **Typical Characteristics (continued)**

$V_{RS+} = V_{RS-} = 76V$ ,  $V_{DD} = 3.3V$ ,  $V_{SENSE} = V_{RS+} - V_{RS-} = 1mV$ ,  $T_A = +25$ °C, unless otherwise noted.

#### Input Voltage-Noise Density

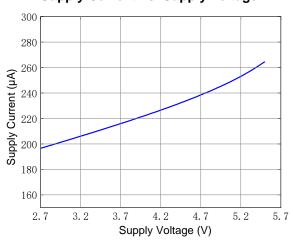

## Supply Current vs. Supply Voltage

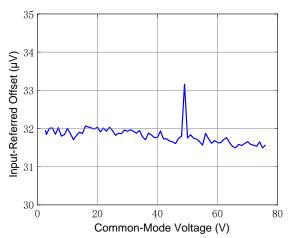

#### Input-Referred Offset vs. Common-Mode Voltage

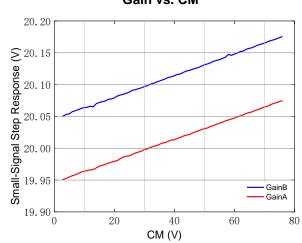

Gain vs. CM

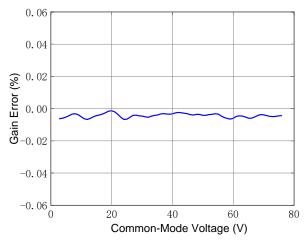

## Gain Error vs. Common-Mode Voltage

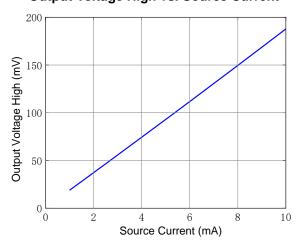

## **Output Voltage High vs. Source Current**

# **Typical Characteristics (continued)**

$V_{\text{RS+}} = V_{\text{RS-}} = 76 \text{V}, \ V_{\text{DD}} = 3.3 \text{V}, \ V_{\text{SENSE}} = V_{\text{RS+}} - V_{\text{RS-}} = 1 \text{mV}, \ T_{\text{A}} = +25 ^{\circ}\text{C}, \ unless \ otherwise \ noted.$

# Output Voltage Low vs. Sink Current

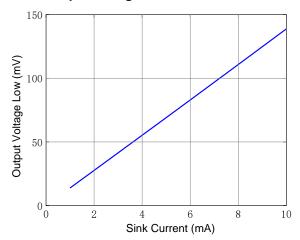

#### **Functional Diagram**

# **Detailed Description**

The WS74285 high-side, current-sense amplifier features a 2.7V to 76V input common-mode range that is independent of supply voltage. This feature allows the monitoring of supply voltage. This feature allows the monitoring of current out of a battery as low as 2.7V and enables high-side current sensing at voltages greater than the supply voltage ( $V_{DD}$ ). The WS74285 monitors current through a current-sense resistor and amplifies the voltage across the resistor.

High-side current monitoring does not interfere with the ground path of the load being measured, making the WS74285 particularly useful in a wide range of high-voltage systems. The WS74285 operates as follows: current from the source flows through  $R_{SENSE}$  to the load (see Functional Diagram), creating a sense voltage,  $V_{SENSE}$ . The internal op amp A1 is used to force the current through an internal gain resistor  $R_{G11}$  at RS1+ pin, such that its voltage drop equals the voltage drop ( $V_{SENSE}$ ) across the external sense resistor ( $R_{SENSE}$ ). The internal resistor at RS1- pin ( $R_{G12}$ ) has the same value as  $R_{G11}$  to minimize error. The 2) has the same value as  $R_{G11}$  to minimize error p-channel FET. Its source current is the same as the drain current which flows through a second gain resistor,  $R_{O1}$  producing a voltage  $V_{RO1} = V_{SENSE} \times R_{O1}/R_{G11}$ .

The output voltage  $V_{OUT1}$  is produced from a second op amp A2 with the gain (1+ RF1/R01). Hence, the  $V_{OUT1}$ =  $I_{LOAD1}$  x  $R_{SENSE1}$  ( $R_{01}/R_{G11}$ ) x (1+  $R_{F1}/R_{01}$ ) for channel 1 and  $V_{OUT2}$ = $I_{LOAD2}$  x  $R_{SENSE2}$  ( $R_{02}/R_{G21}$ ) x (1+ $R_{F2}/R_{02}$ ) for channel 2. Internal resistor  $R_{01}$  =  $R_{02}$ ,  $R_{G11}$ = $R_{G12}$ = $R_{G21}$ = $R_{G22}$ ,  $R_{F1}$ = $R_{F2}$ . The gain-setting resistors  $R_{01}$ ,  $R_{02}$ ,  $R_{G11}$ ,  $R_{G21}$ ,  $R_{G21}$ ,  $R_{G22}$ ,  $R_{F1}$  and  $R_{F2}$  are available in Table 1).

Total gain = 12.5V/V for WS74285x1, 20V/V for the WS74285T, 50V/V for the WS74285x3, and 100V/V for the WS74285x4.

Will Semiconductor Ltd. 9 2023/08/16 – Rev. 1.1

#### **Applications Information**

#### **Recommended Component Values**

Ideally, the maximum load current develops the full-scale sense voltage across the current-sense resistor. Choose the gain needed to yield the maximum output voltage required for the application:

$$V_{OUT} = V_{SENSE} \times A_V$$

Where  $V_{SENSE}$  is the full-scale sense voltage, 200mV for gain of 12.5V/V, 125mV for gain of 20V/V, 50mV for gain of 50V/V, 25mV for gain of 100V/V, and  $A_V$  is the gain of the device.

In applications monitoring a high current, ensure that  $R_{\text{SENSE}}$  is able to dissipate its own  $I^2R$  loss. If the resistor's power dissipation exceeds the nominal value, its value may drift or it may fail altogether. The WS74285 senses a wide variety of currents with different sense-resistor values.

#### **Choosing the Sense Resistor**

Choose Rsense based on the following criteria:

**Voltage Loss:** A high  $R_{SENSE}$  value causes the power- source voltage to degrade through IR loss. For minimal voltage loss, use the lowest  $R_{SENSE}$ .

**Accuracy:** A high R<sub>SENSE</sub> value allows lower currents measured more accurately. This is due to offsets becoming less significant when the sense voltage is larger. For best performance select R<sub>SENSE</sub> to provide approximately 200mV (gain of 12.5V/V), 125mV (gain of 20V/V), or 50mV (gain of 50V/V), 25mV (gain of 100V/V) of sense voltage for the full-scale current in each application.

**Efficiency and Power Dissipation:** At high current levels the I<sup>2</sup>R losses in R<sub>SENSE</sub> can be significant. Consider this when choosing the resistor value and its power dissipation (wattage) rating. In addition, the sense resistor's value might drift if it heats up excessively.

**Inductance:** Keep inductance low if  $I_{SENSE}$  has a large high-frequency component. Wire-wound resistors have the highest inductance, while metal film is somewhat better. Low-inductance, metal-film resistors are also available. Instead of being spiral wrapped around a core, as in metal-film or wire wound resistors, they are a straight band of metal and are available in values under  $1\Omega$ .

Take care to eliminate parasitic trace resistance from causing errors in the sense voltage because of the high currents that flow through R<sub>SENSE</sub>. Either use a four terminal current-sense resistor or use Kelvin (force and sense) PCB layout techniques.

#### **Base Station Application Circuit**

An example of a typical application (Figure 1) of this high-voltage, high-precision current-sense amplifier is in base-station systems where there is a need to monitor the current flowing in the power amplifier. Such amplifiers, depending on the technology, can be biased up to 50V or 60V thus requiring a current-sense amplifier like the WS74285 with high-voltage common mode. The very low input offset voltage of the WS74285 minimizes the value of the external sense resistor thus resulting in system power-saving.

Will Semiconductor Ltd. 10 2023/08/16 – Rev. 1.1

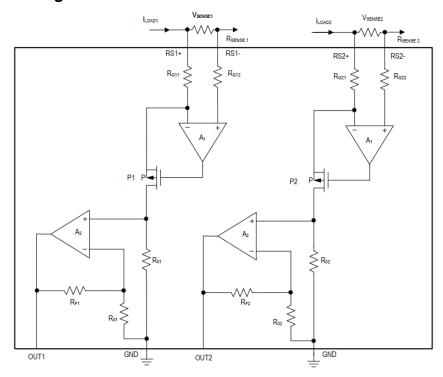

# PACKAGE OUTLINE DIMENSIONS

# MSOP-8L

SIDE VIEW

| Symbol | Dimen | Dimensions In Millimeters (mm) |      |  |  |  |

|--------|-------|--------------------------------|------|--|--|--|

|        | Min.  | Тур.                           | Max. |  |  |  |

| А      | -     | -                              | 1.10 |  |  |  |

| A1     | 0.02  | -                              | 0.15 |  |  |  |

| A2     | 0.75  | 0.80                           | 0.95 |  |  |  |

| b      | 0.25  | -                              | 0.38 |  |  |  |

| С      | 0.09  | -                              | 0.23 |  |  |  |

| D      | 2.90  | 3.00                           | 3.10 |  |  |  |

| Е      | 4.75  | 4.90                           | 5.05 |  |  |  |

| E1     | 2.90  | 3.00                           | 3.10 |  |  |  |

| е      |       | 0.65 BSC                       |      |  |  |  |

| L      | 0.40  | -                              | 0.80 |  |  |  |

| θ      | 0°    | -                              | 6°   |  |  |  |

Will Semiconductor Ltd. 11 2023/08/16 – Rev. 1.1

#### TAPE AND REEL INFORMATION

#### MSOP-8L

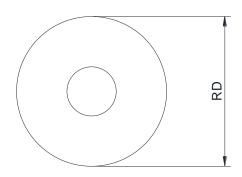

# **Reel Dimensions**

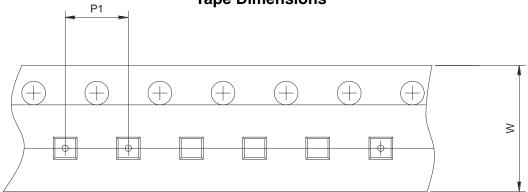

# **Tape Dimensions**

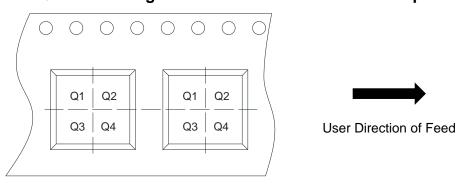

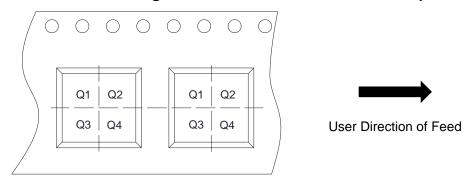

# **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | ☐ 7inch     | <b>✓</b> 13inch |              |      |

|------|-----------------------------------------|-------------|-----------------|--------------|------|

| W    | Overall width of the carrier tape       | ☐ 8mm       | <b>▼</b> 12mm   |              |      |

| P1   | Pitch between successive cavity centers | ☐ 2mm       | ☐ 4mm           | <b>☑</b> 8mm |      |

| Pin1 | Pin1 Quadrant                           | <b>▼</b> Q1 | □ Q2            | ☐ Q3         | □ Q4 |

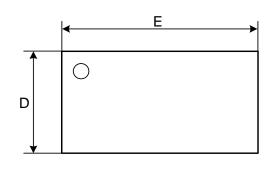

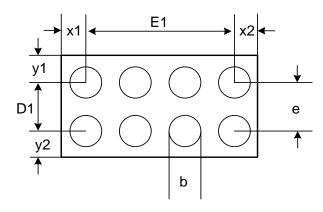

# **PACKAGE OUTLINE DIMENSIONS**

# CSP-8L

TOP VIEW (MARK SIDE)

BOTTOM VIEW (BALL SIDE)

SIDE VIEW

| Symbol | Dimensions In Millimeters (mm) |                 |       |  |  |

|--------|--------------------------------|-----------------|-------|--|--|

|        | Min.                           | Тур.            | Max.  |  |  |

| А      | 0.595                          | 0.640           | 0.685 |  |  |

| A1     | 0.220                          | 0.240           | 0.260 |  |  |

| A2     | 0.375                          | 0.400           | 0.425 |  |  |

| D      | 1.020                          | 1.020 1.050 1.0 |       |  |  |

| D1     |                                | 0.500BSC        |       |  |  |

| Е      | 1.940                          | 1.970 2.000     |       |  |  |

| E1     |                                | 1.500 BSC       |       |  |  |

| b      | 0.300                          | 0.320           | 0.340 |  |  |

| е      |                                | 0.500 BSC       |       |  |  |

| x1     |                                | 0.235 REF       |       |  |  |

| x2     | 0.235 REF                      |                 |       |  |  |

| y1     | 0.275 REF                      |                 |       |  |  |

| y2     |                                | 0.275 REF       |       |  |  |

Will Semiconductor Ltd. 13 2023/08/16 – Rev. 1.1

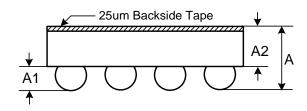

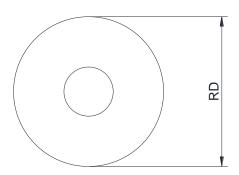

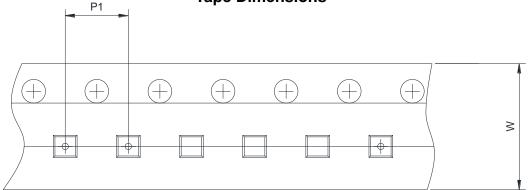

#### TAPE AND REEL INFORMATION

CSP-8L Reel Dimensions

# **Tape Dimensions**

# **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | <b>☑</b> 7inch | ☐ 13inch     |       |      |

|------|-----------------------------------------|----------------|--------------|-------|------|

| W    | Overall width of the carrier tape       | ▼ 8mm          | ☐ 12mm       |       |      |

| P1   | Pitch between successive cavity centers | ☐ 2mm          | <b>✓</b> 4mm | ☐ 8mm |      |

| Pin1 | Pin1 Quadrant                           | □ Q1           | <b>▼</b> Q2  | ☐ Q3  | □ Q4 |