#### WS74242

## 4-Channel Rail-to-Rail High Current VCOM Buffer

#### **Descriptions**

The WS74242 is a 4-channel high performance, high voltage rail-to-rail buffer. It operates up to 20V. The device provides rail-to-rail output and common mode input capability beyond the rails, offering maximum dynamic range at any supply voltage.

The WS74242 provides fast slew rate and settling times, and a high output drive capability of up to 1400mA peak output current. The WS74242 features Over Temperature Protection (OTP), Over Current Protection (OCP) and Output Short Circuit Protection functions, which provide maximum system protection for TFT-LCD panel applications.

The WS74242 is available in the thermally enhanced 14-pin TSSOP package. Standard products are Pb-Free and halogen-Free.

#### **Applications**

- TV TFT-LCD Panels

- TFT-LCD Monitors

- Notebooks and Netbooks

- Personal Communication Devices

- Digital Signage

- Touch-Screen Displays

- ADC/DAC Buffers and Active Filters

#### **Features**

- Beyond the rails input capability

- 1400mA peak output current

- 35MHz 3dB Bandwidth

- Rail-to-rail output swing

- Power supply range from 4V to 20V

- Low supply current per amplifier: 2mA

- High Slew Rate: 50V/µs

- Unity-gain stable

- Protection Function

Over Temperature Protection (OTP)

Over Current Protection (OCP)

**Output Short Protection**

#### Http://www.omnivision-group.com

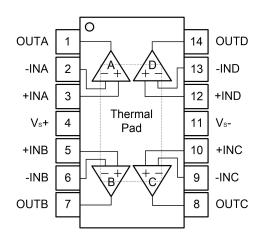

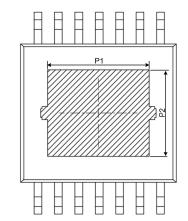

TSSOP-14L

TSSOP-14L

Pin configuration (Top view)

TSSOP-14L

#### Marking

242 = Device code

Y = Year code

W = Week code

#### Order information

|  | Device         | Package   | Shipping  |  |

|--|----------------|-----------|-----------|--|

|  | WS74242H-14/TR | TSSOP-14L | 4000/Reel |  |

|  |                | 1330P-14L | &Tape     |  |

**Pin Descriptions**

| Pin Number Symbol            |                 | Descriptions                                                                                                                 |  |  |  |

|------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 OUTA Output of Amplifier-A |                 | Output of Amplifier-A                                                                                                        |  |  |  |

| 2 -INA                       |                 | Inverting Input of Amplifier-A                                                                                               |  |  |  |

| 3                            | +INA            | Non-inverting Input of Amplifier-A                                                                                           |  |  |  |

| 4                            | V <sub>S+</sub> | Positive Power Supply                                                                                                        |  |  |  |

| 5                            | +INB            | Non-inverting Input of Amplifier-B                                                                                           |  |  |  |

| 6                            | -INB            | Inverting Input of Amplifier-B                                                                                               |  |  |  |

| 7                            | OUTB            | Output of Amplifier-B                                                                                                        |  |  |  |

| 8                            | OUTC            | Output of Amplifier-C                                                                                                        |  |  |  |

| 9                            | -INC            | Inverting Input of Amplifier-C                                                                                               |  |  |  |

| 10 +INC                      |                 | Non-inverting Input of Amplifier-C                                                                                           |  |  |  |

| 11 Vs-                       |                 | Negative Power Supply.                                                                                                       |  |  |  |

| 12                           | +IND            | Non-inverting Input of Amplifier-D                                                                                           |  |  |  |

| 13                           | -IND            | Inverting Input of Amplifier-D                                                                                               |  |  |  |

| 14                           | OUTD            | Output of Amplifier-D                                                                                                        |  |  |  |

| EP                           | Thermal<br>Pad  | Exposed Pad. The exposed pad must be soldered to a large PCB and connected to system ground for maximum thermal dissipation. |  |  |  |

**Absolute Maximum Ratings**(1)

| Parameter                                                 | Symbol                         | Value                              | Unit |

|-----------------------------------------------------------|--------------------------------|------------------------------------|------|

| Supply Voltage, ([V <sub>S+</sub> ] - [V <sub>S-</sub> ]) | Vs                             | 22                                 | V    |

| Input Common Mode Voltage Range                           | V <sub>ICR</sub>               | $(V_{S-})$ -0.3 to $(V_{S+})$ +0.3 | V    |

| Operating Free-Air Temperature Range                      | TA                             | -40 to 85                          | Ĵ    |

| Operating Junction Temperature Range                      | TJ                             | -40 to 150                         | °C   |

| Storage Temperature Range                                 | T <sub>STG</sub>               | -65 to 150                         | °C   |

| Junction to Ambient Thermal Resistance                    | θ <sub>JA</sub> <sup>(3)</sup> | 45.5                               |      |

| Junction to Board Thermal Resistance                      | θ <sub>JB</sub> <sup>(3)</sup> | 18.5                               | °C/W |

| Junction to Case (Top) Thermal Resistance                 | θ <sub>JCtop</sub> (3)         | 17.2                               | C/W  |

| Junction to Case (Bottom) Thermal Resistance              | θ <sub>JCbot</sub> (3)         | 4.6                                |      |

#### Note:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the

device. These are only stress ratings, and functional operation of the device at these or any other

conditions beyond those indicated under recommended operating conditions are not implied.

- 2. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 3. Single component mounted on 2oz, 1.5\*1.5 inch² FR4 PCB with 1.0\*1.0 inch² Cu area.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | MIL-STD-883H Method 3015.8 | ±5000         | V    |

| ПОІ    |                          | JEDEC-EIA/JESD22-A114A     | ±3000         |      |

| CDM    | Charged Device Model ESD | JEDEC-EIA/JESD22-C101E     | ±2000         | V    |

| MM     | Machine Model ESD        | JEDEC-EIA/JESD22-A115      | ±400          | V    |

Will Semiconductor Ltd. 3 2023/3/23 – Rev. 1.1

#### **Electronics Characteristics**

$V_{S^+}$  = 19V,  $V_{S^-}$  = 0V,  $V_{INx}$ + = 9.5V, 4CH unity gain ( $V_{INx^-}$  =  $V_{OUTx}$ ), with  $R_L$  = 10k $\Omega$  and  $C_L$  = 10pF unless otherwise specified. Typical values are tested at +25°C ambient temperature

| Symbol            | Parameter                     | Conditions                                       | Min. | Тур.  | Max. | Unit |

|-------------------|-------------------------------|--------------------------------------------------|------|-------|------|------|

| (Vs+)-(Vs-)       | Supply Voltage Range          |                                                  | 4    | -     | 19   | V    |

| Is                | Supply Current                |                                                  | -    | 8     | 12.8 | mA   |

| Vos               | Input Offset Voltage          |                                                  | -15  | +3    | +15  | mV   |

| I <sub>B</sub>    | Input Bias Current            |                                                  | -0.1 | -     | +0.1 | nA   |

| V <sub>OL</sub>   | Output Swing Low              | V <sub>INx</sub> + = 0V, I <sub>L</sub> =-5mA    | -    | 14    | 25   | mV   |

| V <sub>OH</sub>   | Output Swing High             | V <sub>INx</sub> + = 18V, IL=+5mA                | -    | 22    | 30   | mV   |

| lo                | Continue Output Current       | Before OTP                                       | -    | ±400  | -    | mA   |

| I <sub>Peak</sub> | Peak Output Current           |                                                  | -    | ±1400 | -    | mA   |

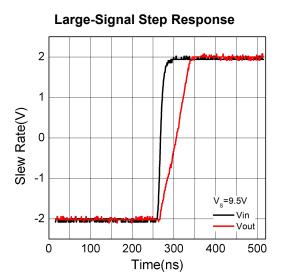

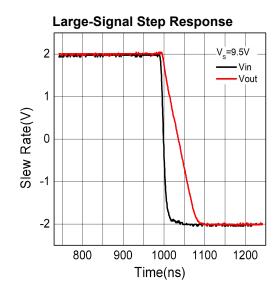

| SR                | Slew Rate                     | 0.5V to 17.5V, 20% to 80%                        | -    | 50    | -    | V/μs |

| BW                | Bandwidth                     | -3dB                                             | -    | 35    | -    | MHz  |

| Avol              | Open-Loop Gain                | R <sub>L</sub> = 10kΩ                            | -    | 100   | -    | dB   |

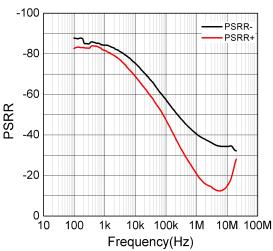

| PSRR              | Power Supply Rejection Ration | 6V < (V <sub>S</sub> +)-(V <sub>S</sub> -) < 18V | 84   | 107   | -    | dB   |

| CMIR              | Common-Mode Input Range       |                                                  | -0.1 | -     | 19.1 | V    |

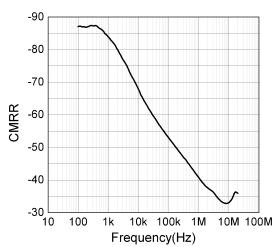

| CMRR              | Common-Mode Rejection Ration  | R <sub>L</sub> = 10kΩ                            | -    | 78    | -    | dB   |

| T <sub>SD</sub>   | Thermal Shutdown              |                                                  | -    | 150   | -    | °C   |

Will Semiconductor Ltd. 4 2023/3/23 – Rev. 1.1

# Applications Information Unused Amplifiers

It is strongly recommended to configure any unused amplifiers as unity gain buffer and directly tie the non-inverting input to the ground plane.

#### **Protection Functions**

The WS74242 features over temperature protection (OTP), over current protection (OCP), and output short circuit protection functions. These features provide maximum system protection for demanding TFT LCD panel applications.

The WS74242 limits the peak output current to  $\pm 1400$ mA and the continue output current to  $\pm 400$ mA for normal operation. If the output of the WS74242 is shorted to  $V_{S-}$  or  $V_{S+}$ , the over current protection (OCP) mechanism will be activate to regulate the power dissipation to prevent overstressing of the power bus. The over temperature protection (OTP) function of the WS74242 monitors the silicon junction temperature. When the junction temperature exceeds 150°C, the OTP protection circuit disables normal operation to lower the chip operating temperature.

The synergistic operation of the OTP, OCP, peak output current limit and continue output current limit functions provides maximum output short protection for the WS74242.

#### **Power Dissipation**

The WS74242 design is optimized to deliver maximum output current driving capability for TFT LCD panel applications. Due to its robust protection features, the WS74242 can endure a momentary output short to ground (or VS-).

Due to its high current driving capability, it is possible for the junction temperature to exceed 150°C under certain output current load conditions. Therefore, it is very important to calculate the WS74242's maximum junction temperature and maximum power dissipation for the application to make sure that the junction temperature does not exceed 150°C or maximum package power rating to ensure the device stays in the safe operating region.

#### **Driving Capacitive Loads**

The strong output current driving capability of the WS74242 allows for a high slew rate even with large capacitive loads. Sometimes there is output peaking for certain application loads and application configurations. If less output peaking is desired for these applications, a small damping resistor (usually between  $2\Omega$  and  $15\Omega$ ) can be connected in series between the output of WS74242 and the load. However, this topology will reduce the gain slightly.

Another method of reducing output peaking is to add a snubber circuit at the output. A snubber circuit consists of a resistor (such as  $100\Omega$  -  $200\Omega$ ) in series with a capacitor (such as 10nF), which improves output settling time and reduces peaking. The advantage of this topology is that it draws no DC current nor does it reduce the gain.

#### **Bypass Capacitors**

For stability while driving load transients, and to minimize the noise to the system, use a 10µF capacitor for the V<sub>S+</sub> supply. Connect this bypass capacitor as close as possible to the input V<sub>S+</sub>.

#### Layout

Connect the exposed pad of the device to the  $V_{S-}$  or GND plane for best thermal dissipation performance, or low thermal resistance. In typical application,  $V_{S-}$  is connected to ground.

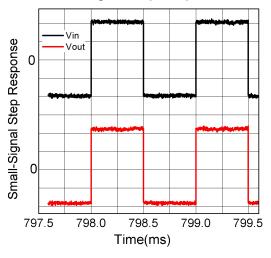

#### **Typical Characteristics**

#### T<sub>A</sub>=25°C, V<sub>S</sub>=5V, V<sub>CM</sub>=V<sub>S</sub>/2, unless otherwise noted

CMRR vs. Frequency

#### **PSRR vs. Frequency**

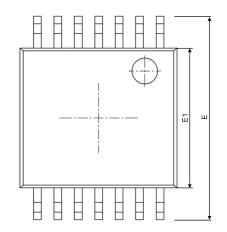

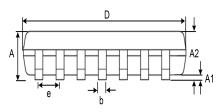

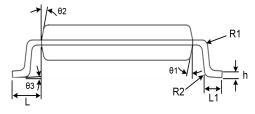

### PACKAGE OUTLINE DIMENSIONS

| Symbol | Dimensions In Millimeters (mm) |          |      |  |

|--------|--------------------------------|----------|------|--|

|        | Min.                           | Тур.     | Max. |  |

| А      | -                              | -        | 1.20 |  |

| A1     | 0.05                           | -        | 0.15 |  |

| A2     | 0.80                           | -        | 1.05 |  |

| D      | 4.90                           | -        | 5.10 |  |

| е      |                                | 0.65 BSC |      |  |

| b      | 0.19                           | -        | 0.30 |  |

| E      | 6.25                           | -        | 6.55 |  |

| E1     | 4.30                           | -        | 4.50 |  |

| P1     | 3.30                           | -        | 3.70 |  |

| P2     | 2.90                           | -        | 3.20 |  |

| L      | -                              | -        | 1.00 |  |

| L1     | 0.45                           | -        | 0.75 |  |

| R1     | -                              | 0.15     | -    |  |

| R2     | -                              | 0.15     | -    |  |

| θ1     | -                              | 12°      | -    |  |

| θ2     | -                              | 12°      | -    |  |

| θ3     | 0°                             | -        | 8°   |  |

| h      | 0.09                           | -        | 0.20 |  |

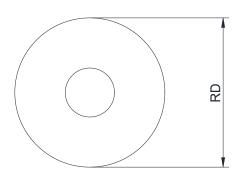

#### TAPE AND REEL INFORMATION

#### **Reel Dimensions**

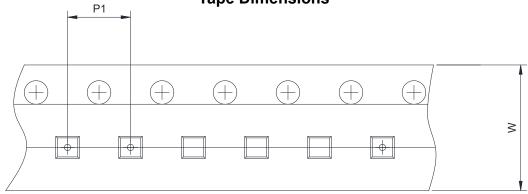

## **Tape Dimensions**

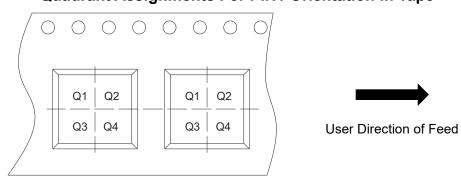

## **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | 7inch       | <b>✓</b> 13inch |              |      |

|------|-----------------------------------------|-------------|-----------------|--------------|------|

| W    | Overall width of the carrier tape       | ☐ 8mm       | <b>▼</b> 12mm   |              |      |

| P1   | Pitch between successive cavity centers | 2mm         | 4mm             | <b>▼</b> 8mm |      |

| Pin1 | Pin1 Quadrant                           | <b>☑</b> Q1 | □ Q2            | □ Q3         | □ Q4 |

Will Semiconductor Ltd. 8 2023/3/23 – Rev. 1.1