# This document has been made public and no NDA is needed.

The "Confidential" statement in the attached material is no longer valid and may be disregarded.

This document falls into one of these categories:

# 1. Document has MaxLinear branding

The "MaxLinear Confidential" statement will be removed from the document upon its next revision

# 2. Document has non-MaxLinear branding

In 2020, MaxLinear acquired the Connected Home Division business of Intel Corporation, including the former Intel<sup>®</sup> product/s referenced in the title of the attached material. The MaxLinear logo will be added to the attached material upon its next revision. MaxLinear is now the manufacturer of this product.

Direct any questions and product support requests to your MaxLinear sales contact, MaxLinear Sales Representative or Distributor, or login to your myMxL account and create a new support ticket.

Corporate Headquarters: 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, and any MaxLinear trademarks, MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, AnyWAN and the MaxLinear logo are all on the products sold, are all trademarks of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

# **Ethernet Network Connection**

GPY111 (PEF7071VV16)

# Hardware Description

MaxLinear Confidential

Revision 1.5, 2021-05-05 Reference ID 618152

# Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

MaxLinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

\*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2021 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008 Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

#### **Revision History**

| Current: Revision 1.5, 2021-05-05<br>Previous: Revision 1.4, 2018-08-29 |                                                                                                                                                                                |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Page Major changes since previous revision                              |                                                                                                                                                                                |  |

| All                                                                     | This document was rebranded from Intel to MaxLinear, including the logo and Legal Notice page. All product names were rebranded by removing Intel <sup>®</sup> from the names. |  |

| 181                                                                     | Chapter 7.2 Chip Identification and Ordering Information updated, including MMID added to Table 74.                                                                            |  |

#### **Table of Contents**

|                                                                                                                                                                                           | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 4                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                           | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 8                                                                                                            |

|                                                                                                                                                                                           | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                             |

| 1                                                                                                                                                                                         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                                                                                                             |

| 1.1                                                                                                                                                                                       | About Ethernet Network Connection GPY111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                                                                             |

| 1.2                                                                                                                                                                                       | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

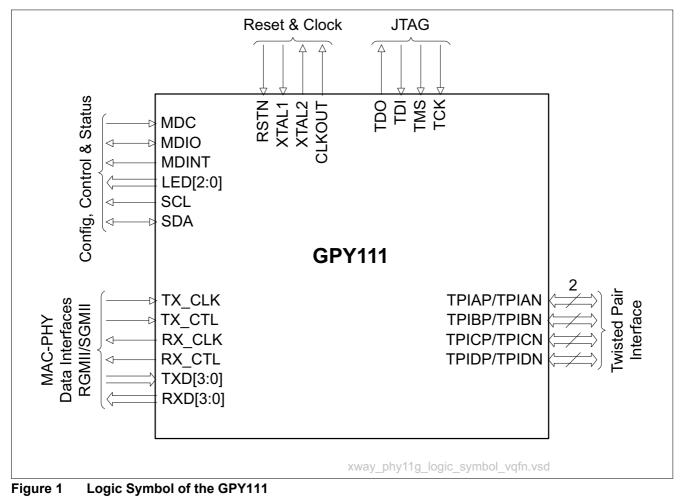

| 1.2.1                                                                                                                                                                                     | Logic Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

| 1.2.2                                                                                                                                                                                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

| 1.2.3                                                                                                                                                                                     | Typical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

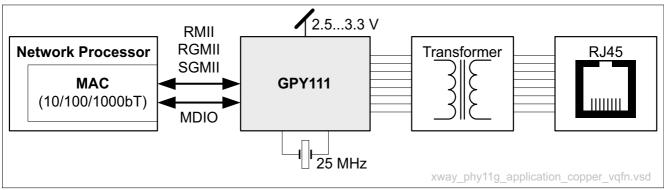

| 1.2.3.1                                                                                                                                                                                   | Copper Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

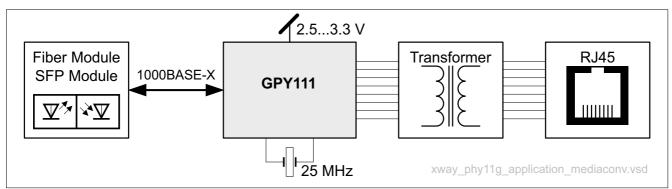

| 1.2.3.2                                                                                                                                                                                   | Media Converter Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

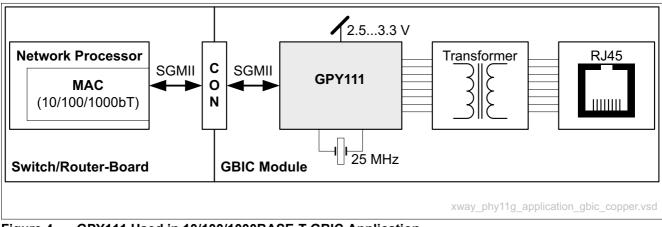

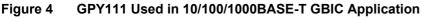

| 1.2.3.3                                                                                                                                                                                   | Gigabit Interface Converter (GBIC) Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

| 1.2.4                                                                                                                                                                                     | Terminology and Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                                             |

| 2                                                                                                                                                                                         | External Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                                             |

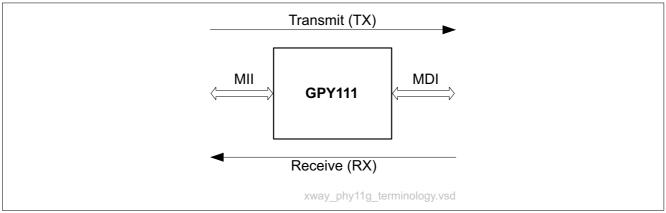

| 2.1                                                                                                                                                                                       | Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| 2.2                                                                                                                                                                                       | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| 2.2.1                                                                                                                                                                                     | Pin Identifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

| 2.2.2                                                                                                                                                                                     | General Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

| 2.2.3                                                                                                                                                                                     | Media-Dependent Interface (MDI) Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| 2.2.4                                                                                                                                                                                     | Media-Independent Interface (MII) Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 2.2.5                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| 2.2.6<br>2.2.7                                                                                                                                                                            | JTAG Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

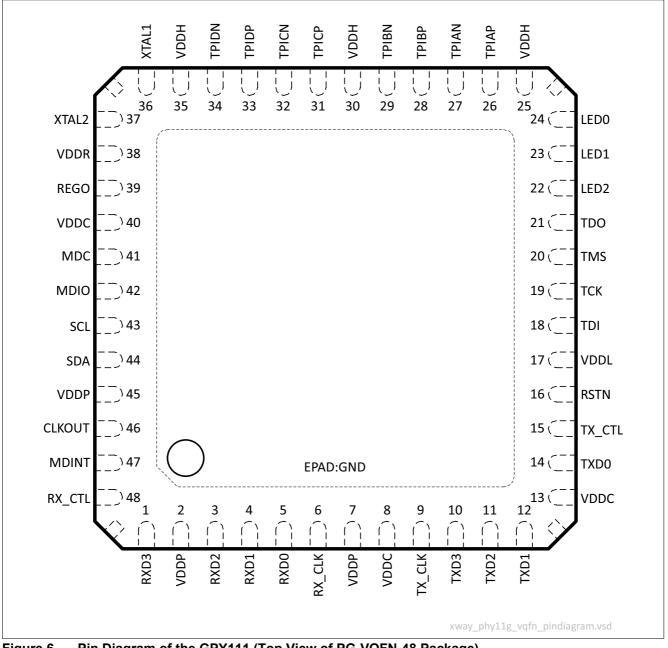

| 3                                                                                                                                                                                         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 3.1                                                                                                                                                                                       | Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                             |

| 3.1.1                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| -                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| 3.1.2                                                                                                                                                                                     | Media Converter Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                             |

| 3.1.2<br>3.2                                                                                                                                                                              | Media Converter Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30<br>30                                                                                                       |

| 3.1.2<br>3.2<br>3.2.1                                                                                                                                                                     | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30<br>30<br>30                                                                                                 |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1                                                                                                                                                          | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30<br>30<br>30<br>30                                                                                           |

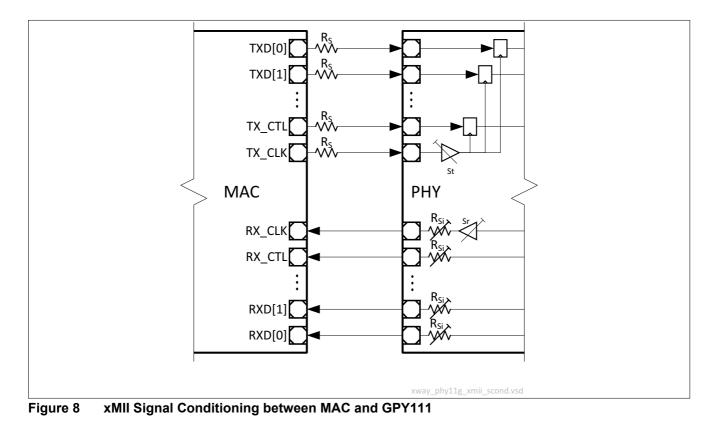

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2                                                                                                                                               | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30<br>30<br>30<br>30<br>31                                                                                     |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2                                                                                                                                      | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>30<br>30<br>30<br>31<br>32                                                                               |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.2<br>3.2.3                                                                                                                    | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)                                                                                                                                                                                                                                                                                                                                                                                                                         | 30<br>30<br>30<br>31<br>32<br>32                                                                               |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4                                                                                                                    | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)                                                                                                                                                                                                                                                                                                                                                              | 30<br>30<br>30<br>31<br>32<br>32<br>35                                                                         |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3                                                                                                             | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions                                                                                                                                                                                                                                                                                                                                      | 30<br>30<br>30<br>31<br>32<br>32<br>35<br>36                                                                   |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4                                                                                                                    | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)                                                                                                                                                                                                                                                                                                                                                              | 30<br>30<br>30<br>31<br>32<br>32<br>35<br>36<br>36                                                             |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1                                                                                                    | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)                                                                                                                                                                                                                                                                                             | 30<br>30<br>30<br>31<br>32<br>32<br>35<br>36<br>36<br>36                                                       |

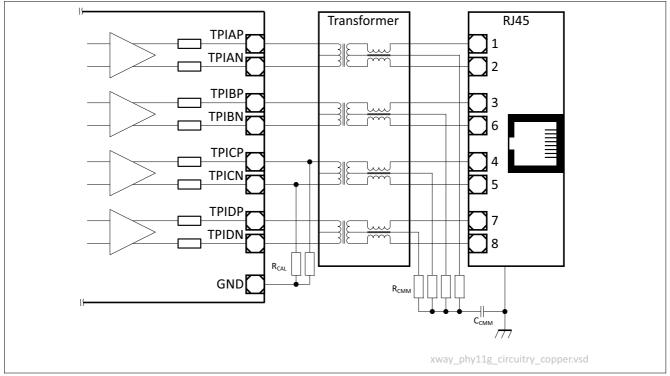

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1                                                                                         | Media Converter Flow<br>Media-Independent Interfaces (MII)<br>X-speed Media-Independent Interface (xMII)<br>xMII Signal Multiplexing<br>xMII Signal Conditioning<br>Reduced Media-Independent Interface (RMII)<br>Reduced Gigabit Media-Independent Interface (RGMII)<br>Serial Gigabit Media-Independent Interface (SGMII)<br>Media Functions<br>Media-Dependent Interfaces (MDI)<br>Copper Interface                                                                                                                                                                                                                                                                                                                      | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37                                                 |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2                                                                              | Media Converter Flow<br>Media-Independent Interfaces (MII)<br>X-speed Media-Independent Interface (xMII)<br>xMII Signal Multiplexing<br>xMII Signal Conditioning<br>Reduced Media-Independent Interface (RMII)<br>Reduced Gigabit Media-Independent Interface (RGMII)<br>Serial Gigabit Media-Independent Interface (SGMII)<br>Media Functions<br>Media-Dependent Interfaces (MDI)<br>Copper Interface<br>Fiber Interface                                                                                                                                                                                                                                                                                                   | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>37                                           |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2                                                                     | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction                                                                                                                                                           | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>37<br>38                                     |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.3                                                            | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction         Configuration, Control and Status Functions                                                                                                       | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39                         |

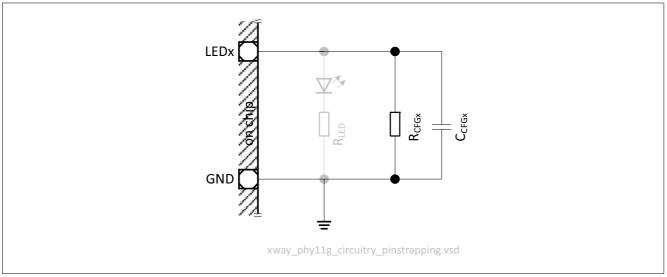

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4<br>3.4.1                            | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction         Configuration, Control and Status Functions         Configuration of GPY111 via Pin-Strapping                                                     | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>38<br>38<br>39<br>41                         |

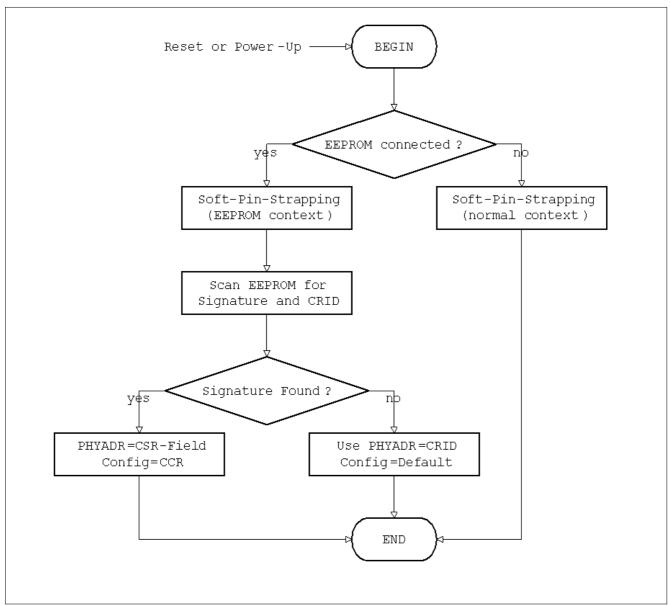

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4<br>3.4.1<br>3.4.2                   | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction         Configuration, Control and Status Functions         Configuration of GPY111 via Pin-Strapping         Configuration of GPY111 via External EEPROM | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>41<br>46                         |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1 | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (RGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction         Configuration, Control and Status Functions         Configuration of GPY111 via External EEPROM         EEPROM Applications                       | 30<br>30<br>30<br>31<br>32<br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>41<br>46<br>46                   |

| 3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4<br>3.4.1<br>3.4.2                   | Media Converter Flow         Media-Independent Interfaces (MII)         X-speed Media-Independent Interface (xMII)         xMII Signal Multiplexing         xMII Signal Conditioning         Reduced Media-Independent Interface (RMII)         Reduced Gigabit Media-Independent Interface (RGMII)         Serial Gigabit Media-Independent Interface (SGMII)         Media Functions         Media-Dependent Interfaces (MDI)         Copper Interface         Fiber Interface         Auto-Negotiation         Auto-Crossover and Polarity-Reversal Correction         Configuration, Control and Status Functions         Configuration of GPY111 via Pin-Strapping         Configuration of GPY111 via External EEPROM | $\begin{array}{c} 30\\ 30\\ 30\\ 30\\ 31\\ 32\\ 35\\ 36\\ 36\\ 37\\ 38\\ 39\\ 41\\ 46\\ 46\\ 46\\ \end{array}$ |

| 3.4.2.4              | EEPROM Frame Formats                                      | 48  |

|----------------------|-----------------------------------------------------------|-----|

| 3.4.2.4.1            | Frame Formats in 11-Bit Addressing Mode                   |     |

| 3.4.2.4.2            | Frame Formats in 16-Bit Addressing Mode                   |     |

| 3.4.2.4.3            | EEPROM Access via MDIO                                    |     |

| 3.4.3                | Configuration and Control Via MDIO                        |     |

| 3.4.3.1              | MDIO Interface                                            |     |

| 3.4.3.2              | MDIO Address Space                                        |     |

| 3.4.3.3              | MDIO Interrupt                                            |     |

| 3.4.4                | LED Interface                                             |     |

| 3.4.4.1              | Single Color LED Mode                                     |     |

| 3.4.4.2              | Bi-Color LED Mode                                         |     |

| 3.4.4.3              | LED Operations                                            |     |

| 3.4.4.3.1            | LED Externally Controlled Mode (ECM)                      |     |

| 3.4.4.3.2            | LED Functions in Internally Controlled Mode (ICM)         |     |

| 3.4.4.3.3            | LED Configuration in ICM                                  |     |

| 3.5                  | Power Management                                          |     |

| 3.5.1                | Power Supply                                              |     |

| 3.5.1.1              | Power Supply Using Integrated Switching Regulator         |     |

| 3.5.1.2              | Power Supply Without Using Integrated Switching Regulator |     |

| 3.5.2                | Power Over Ethernet (PoE)                                 |     |

| 3.5.2.1              | Powered Device (PD)                                       |     |

| 3.5.2.1              | Power Sourcing Equipment (PSE)                            |     |

| 3.5.3                | Energy-Efficient Ethernet                                 |     |

| 3.5.3.1              | EEE for 10BASE-Te                                         |     |

| 3.5.3.1              | EEE for 100BASE-TX                                        |     |

| 3.5.3.2              | EEE for 1000BASE-T                                        |     |

| 3.5.3.4              | Auto-Negotiation for EEE Modes                            |     |

| 3.5.3.4<br>3.5.4     | Wake-on-LAN (WoL)                                         |     |

| 3.5.5                | Power Down Modes                                          |     |

| 3.5.5.1              | PD FORCE Mode                                             |     |

| 3.5.5.1              | ANEG Mode                                                 |     |

|                      |                                                           |     |

| 3.5.5.3              |                                                           |     |

| 3.5.5.4              | DATA Mode                                                 |     |

| 3.5.5.5              | EEE Mode                                                  |     |

| 3.6                  | 0                                                         |     |

| 3.6.1<br>3.6.2       | JTAG Interface                                            |     |

| 3.6.2.1              |                                                           |     |

| 3.6.2.1              | Test Packet Generator (TPG)                               |     |

| 3.6.2.2              | Error Counters                                            |     |

|                      |                                                           |     |

| 3.6.3.1<br>3.6.3.1.1 | Near-End Test Loops       MAC Interface Test Loop         |     |

| 3.6.3.1.2            | •                                                         |     |

| 3.6.3.1.2            | MDI Test Loop                                             |     |

| 3.6.3.1.3            | Echo Test Loop                                            |     |

|                      | Far-End Test Loop                                         |     |

| 4                    | MDIO Registers                                            |     |

| 4.1                  | STD: Standard Management Registers                        |     |

| 4.2                  | PHY: PHY-Specific Management Registers                    | 104 |

| 5                    | MMD Registers                                             | 131 |

| 5.1                  | EEE: Standard EEE Registers for MMD=0x03                  |     |

|                      |                                                           |     |

| 5.2<br>5.3<br>5.4 | ANEG: Standard Auto-Negotiation Registers for MMD=0x07         EEPROM: EEPROM Address Space (MMD=0x1E)         INTERNAL: Internal Address Space (MMD=0x1F) | 140 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6                 | Electrical Characteristics                                                                                                                                 | 153 |

| 6.1               | Absolute Maximum Ratings                                                                                                                                   |     |

| 6.2               | Operating Range                                                                                                                                            |     |

| 6.3               | Recommended Operating Conditions                                                                                                                           |     |

| 6.4               | Power-Up Sequence                                                                                                                                          |     |

| 6.5               | DC Characteristics                                                                                                                                         |     |

| 6.5.1             | Digital Interfaces                                                                                                                                         | 155 |

| 6.5.1.1           | GPIO Interfaces                                                                                                                                            | 155 |

| 6.5.1.2           | MII Receive Interface                                                                                                                                      | 156 |

| 6.5.1.3           | MII Transmit Interface                                                                                                                                     | 156 |

| 6.5.1.4           | LED Interface                                                                                                                                              | 156 |

| 6.5.1.5           | JTAG Interface                                                                                                                                             | 157 |

| 6.5.2             | Twisted-Pair Interface                                                                                                                                     | 157 |

| 6.5.3             | SGMII Interface                                                                                                                                            | 157 |

| 6.5.4             | 1000BASE-X Interface                                                                                                                                       | 157 |

| 6.6               | AC Characteristics                                                                                                                                         | 158 |

| 6.6.1             | Reset                                                                                                                                                      | 158 |

| 6.6.2             | Power Supply                                                                                                                                               | 159 |

| 6.6.3             | Input Clock                                                                                                                                                | 159 |

| 6.6.4             | Output Clock                                                                                                                                               | 160 |

| 6.6.5             | MDIO Interface                                                                                                                                             | 160 |

| 6.6.6             | RMII Interface                                                                                                                                             |     |

| 6.6.7             | RGMII Interface                                                                                                                                            |     |

| 6.6.7.1           | Transmit Timing Characteristics                                                                                                                            |     |

| 6.6.7.2           | Receive Timing Characteristics                                                                                                                             |     |

| 6.6.8             | SGMII Interface                                                                                                                                            |     |

| 6.6.8.1           | Transmit Timing Characteristics                                                                                                                            |     |

| 6.6.8.2           | Receive Timing Characteristics                                                                                                                             |     |

| 6.6.9             | 1000BASE-X Interface                                                                                                                                       |     |

| 6.6.9.1           | Transmit Timing Characteristics                                                                                                                            |     |

| 6.6.9.2           | Receive Timing Characteristics                                                                                                                             |     |

| 6.6.10            | Twisted-Pair Interface                                                                                                                                     |     |

| 6.7               | Power Consumption                                                                                                                                          |     |

| 6.8               | Isolation Requirements                                                                                                                                     |     |

| 6.9               | External Circuitry                                                                                                                                         |     |

| 6.9.1             | Crystal                                                                                                                                                    |     |

| 6.9.2             |                                                                                                                                                            |     |

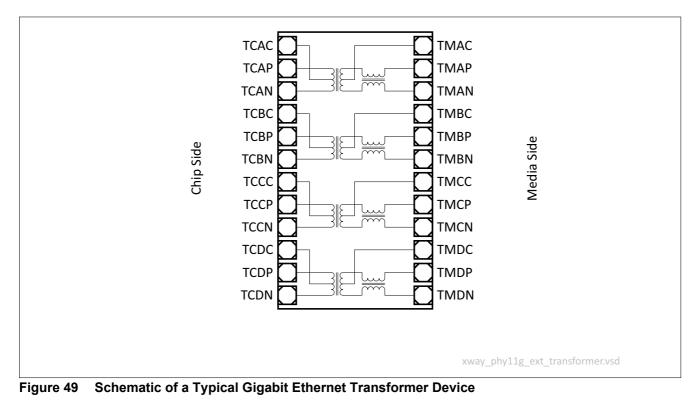

| 6.9.3             | Transformer (Magnetics)                                                                                                                                    |     |

| 6.9.4             | RJ45 Plug                                                                                                                                                  |     |

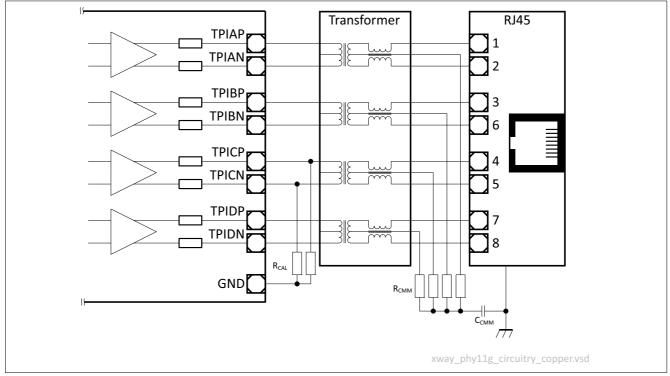

| 6.9.5             | Twisted-Pair Common-Mode Rejection and Termination Circuitry                                                                                               |     |

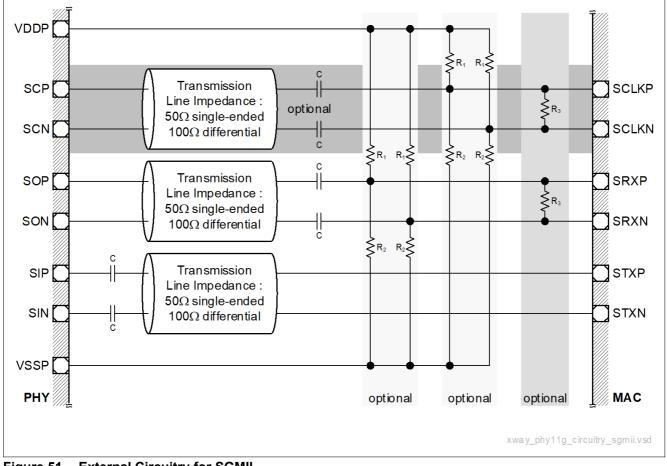

| 6.9.6             |                                                                                                                                                            |     |

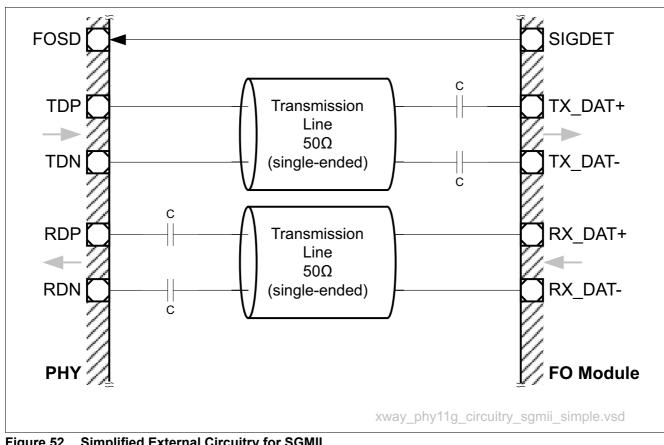

| 6.9.7<br>6 10     | 1000BASE-X Interface                                                                                                                                       |     |

| 6.10              | JTAG Interface Timing                                                                                                                                      |     |

| 7                 | Package                                                                                                                                                    |     |

| 7.1               | Package Outline                                                                                                                                            |     |

| 7.2               | Chip Identification and Ordering Information                                                                                                               |     |

| 7.3               | Thermal Resistance                                                                                                                                         | 182 |

### Ethernet Network Connection GPY111

| References  | . 183 |

|-------------|-------|

| Terminology | . 184 |

**List of Figures**

# List of Figures

| Figure 1  | Logic Symbol of the GPY111                                                   | 13  |

|-----------|------------------------------------------------------------------------------|-----|

| Figure 2  | GPY111 Used in Copper Applications                                           | 15  |

| Figure 3  | GPY111 Used in Media Converter Applications.                                 | 15  |

| Figure 4  | GPY111 Used in 10/100/1000BASE-T GBIC Application.                           | 16  |

| Figure 5  | Transmit and Receive Terminology                                             |     |

| Figure 6  | Pin Diagram of the GPY111 (Top View of PG-VQFN-48 Package)                   | 17  |

| Figure 7  | Functional High-Level Block Diagram of GPY111                                | 29  |

| Figure 8  | xMII Signal Conditioning between MAC and GPY111                              | 32  |

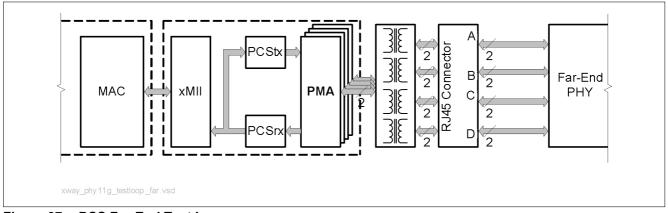

| Figure 9  | Twisted-Pair Interface of GPY111 Including Transformer and RJ45 Plug         | 36  |

| Figure 10 | Overview of the Configuration Flow                                           | 40  |

| Figure 11 | Soft Pin-Strapping External Circuitry                                        | 41  |

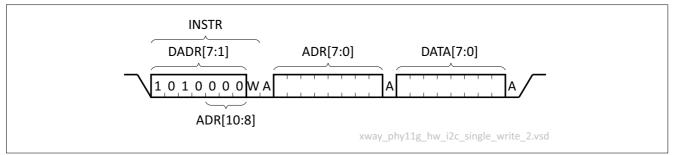

| Figure 12 | Timing Diagram for a Random Address Single Byte Write                        | 49  |

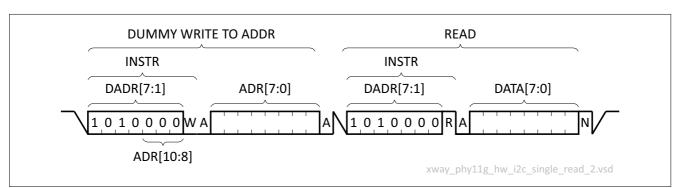

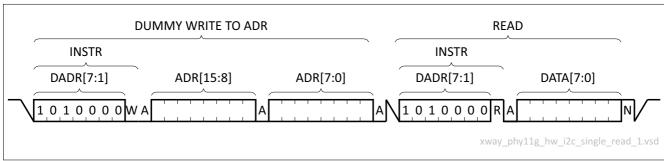

| Figure 13 | Timing Diagram for a Random Address Single Byte Read                         | 50  |

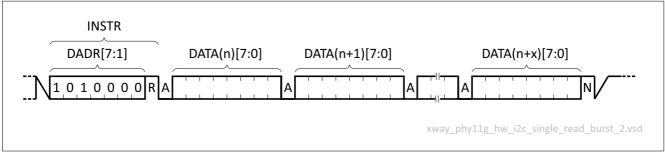

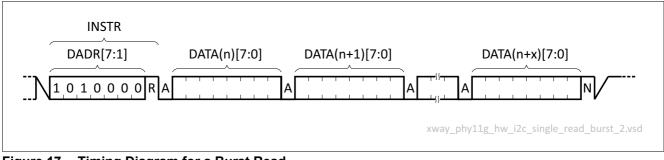

| Figure 14 | Timing Diagram for a Burst Read                                              | 50  |

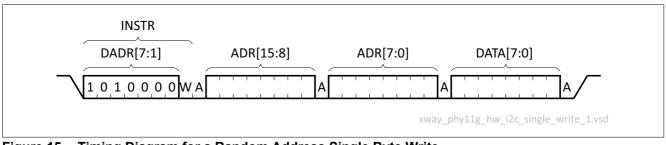

| Figure 15 | Timing Diagram for a Random Address Single Byte Write                        | 51  |

| Figure 16 | Timing Diagram for a Random Address Single Byte Read.                        | 52  |

| Figure 17 | Timing Diagram for a Burst Read                                              | 52  |

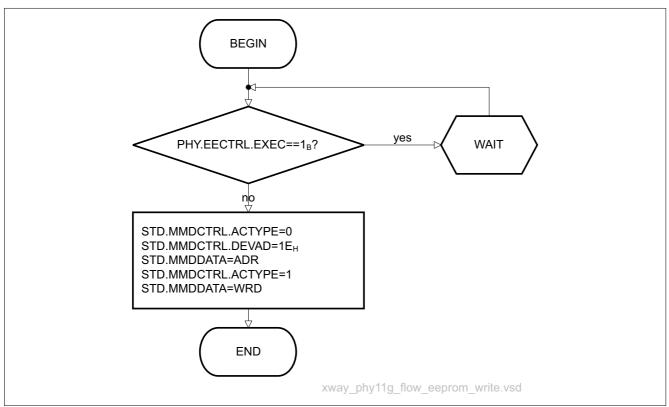

| Figure 18 | Flow-Chart for an Indirect EEPROM Write Cycle Via MDIO-MMD Access            | 53  |

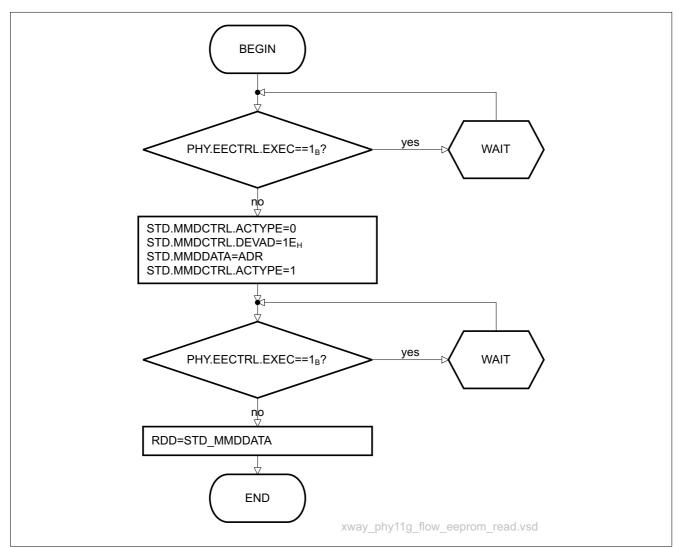

| Figure 19 | Flow-Chart for an Indirect EEPROM Read Cycle Via MDIO-MMD Access             | 54  |

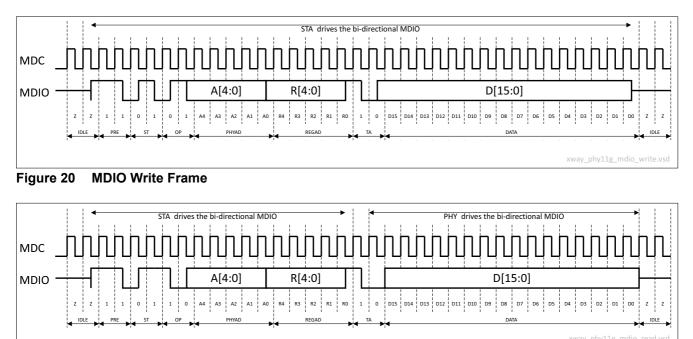

| Figure 20 | MDIO Write Frame                                                             | 55  |

| Figure 21 | MDIO Read Frame                                                              | 55  |

| Figure 22 | Layout of the MDIO Address Space                                             | 57  |

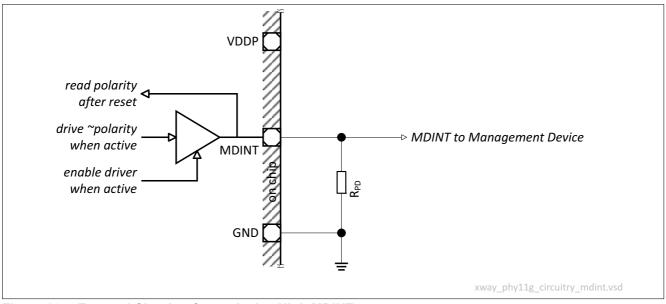

| Figure 23 | External Circuitry for an Active-High MDINT                                  | 58  |

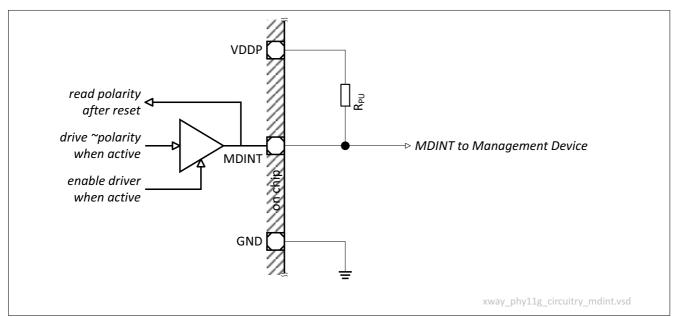

| Figure 24 | External Circuitry for an Active-Low MDINT                                   | 59  |

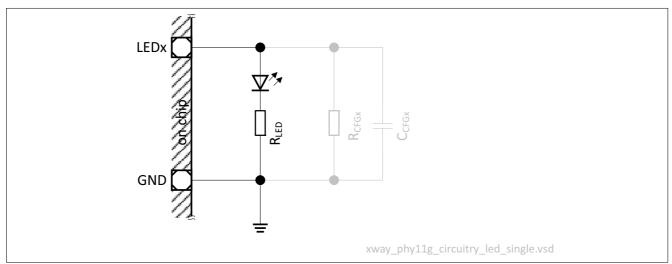

| Figure 25 | Single Color LED External Circuitry                                          | 60  |

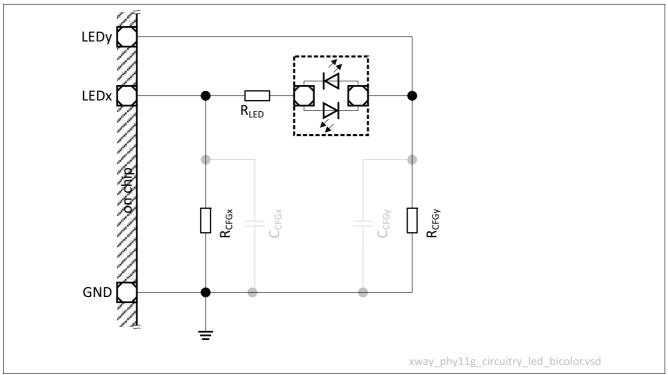

| Figure 26 | Bi-Color LED External Circuitry                                              | 61  |

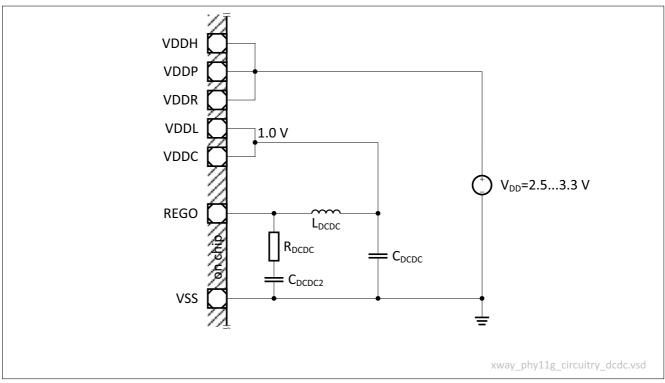

| Figure 27 | External Circuitry using the Integrated Switching Regulator.                 | 64  |

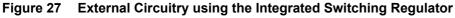

| Figure 28 | External Circuitry without using the Integrated Switching Regulator          | 65  |

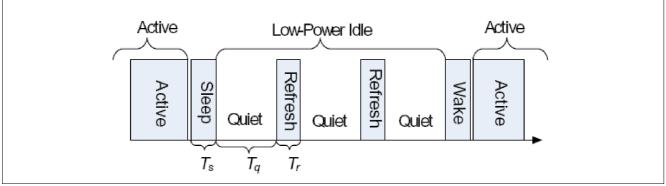

| Figure 29 | EEE Low-Power Idle Sequence                                                  | 67  |

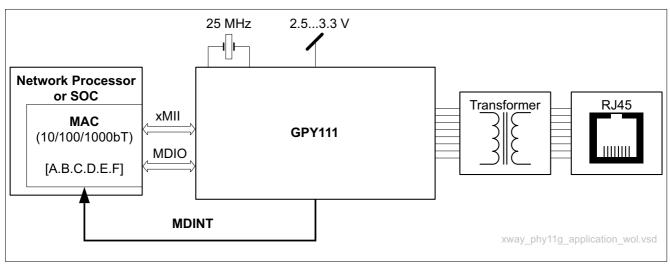

| Figure 30 | Block Diagram of a WoL Application                                           | 69  |

| Figure 31 | The Magic Packet Format.                                                     | 70  |

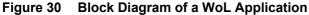

| Figure 32 | State Diagram for Power-Down Mode Management                                 | 72  |

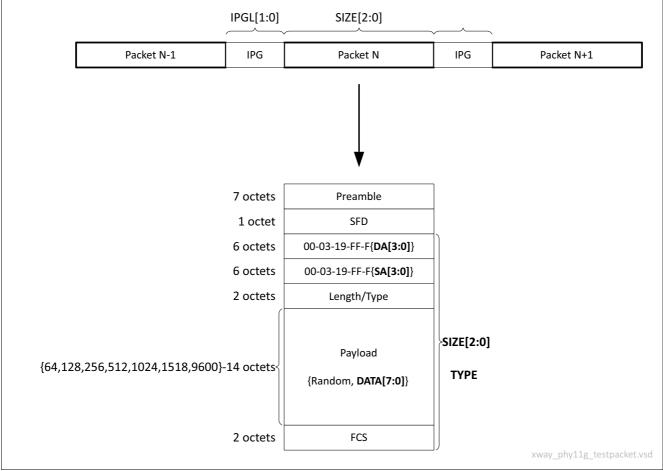

| Figure 33 | Test Packet Format                                                           | 75  |

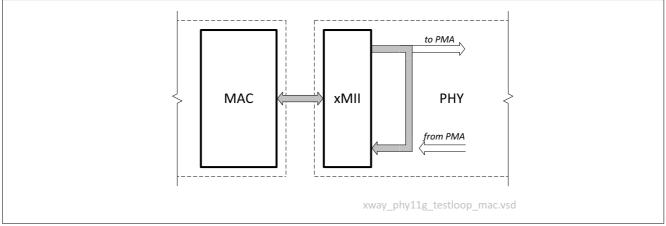

| Figure 34 | MAC Interface Near-End Test Loop                                             | 76  |

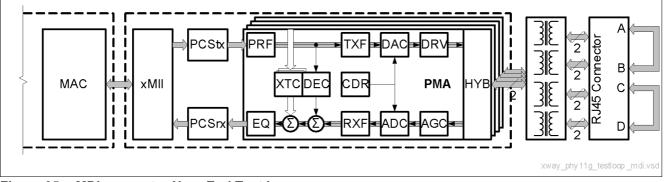

| Figure 35 | MDI connector Near-End Test Loop                                             | 77  |

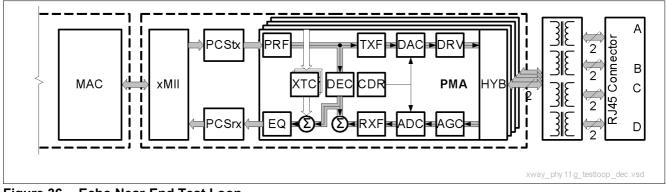

| Figure 36 | Echo Near-End Test Loop                                                      | 77  |

| Figure 37 | PCS Far-End Test Loop                                                        |     |

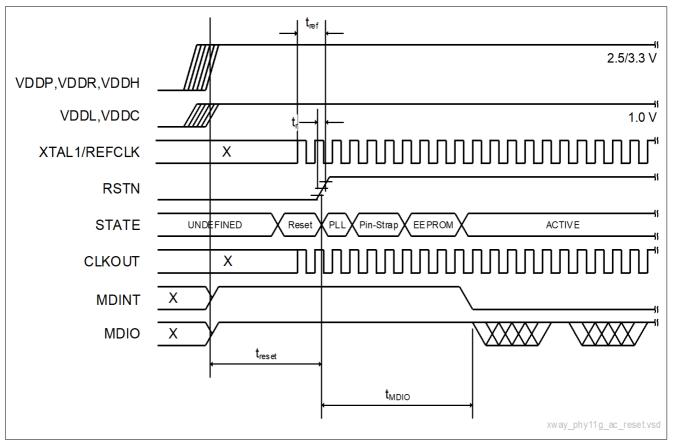

| Figure 38 | Timing Diagram for the GPY111 Reset Sequence                                 |     |

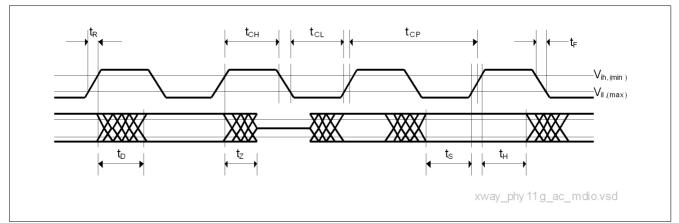

| Figure 39 | Timing Diagram for the MDIO Interface                                        | 160 |

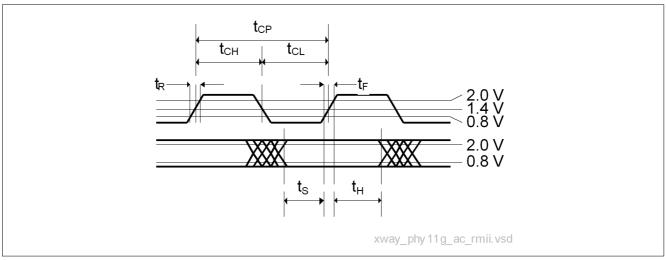

| Figure 40 | Transmit/Receive Timing Diagram of the RMII                                  | 161 |

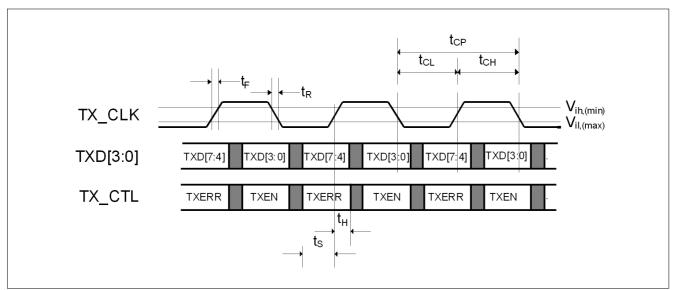

| Figure 41 | Transmit Timing Diagram of the RGMII                                         | 163 |

| Figure 42 | Receive Timing Diagram of the RGMII                                          | 164 |

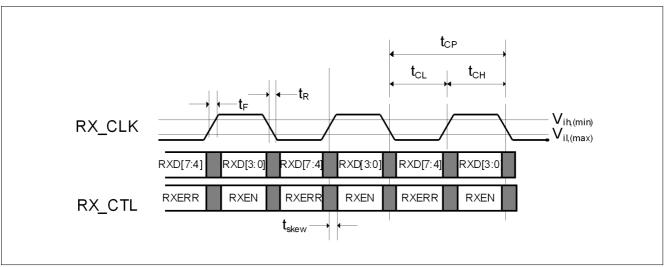

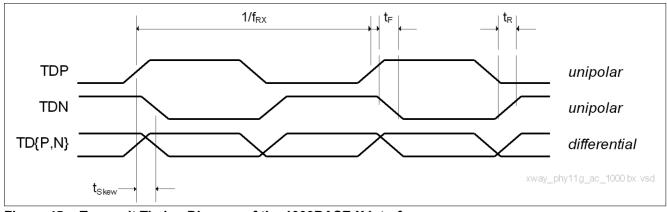

| Figure 43 | Transmit Timing Diagram of the SGMII                                         |     |

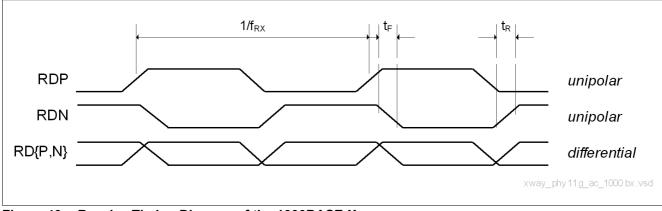

| Figure 44 | Receive Timing Diagram of the SGMII                                          |     |

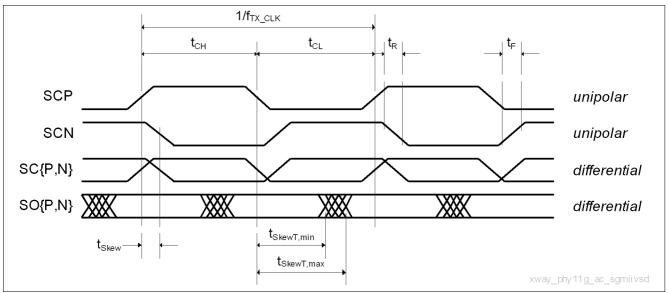

| Figure 45 | Transmit Timing Diagram of the 1000BASE-X Interface                          |     |

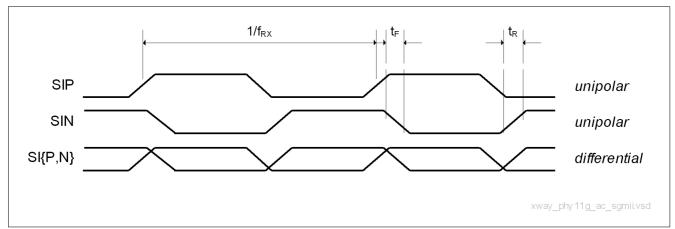

| Figure 46 | Receive Timing Diagram of the 1000BASE-X                                     |     |

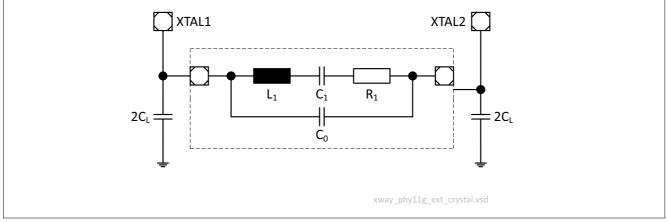

| Figure 47 | Equivalent Circuit for Crystal Specification                                 |     |

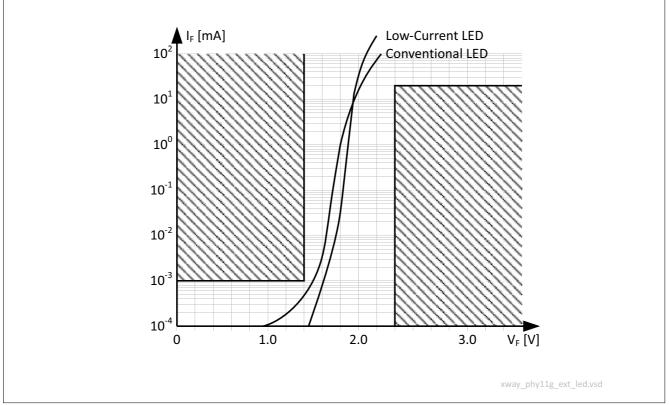

| Figure 48 | Tolerance Graph for the Forward Current Versus Voltage of the Supported LEDs |     |

| Figure 49 | Schematic of a Typical Gigabit Ethernet Transformer Device                   | 173 |

#### List of Figures

| Figure 50 | Twisted-Pair Common-Mode Rejection and Termination Circuitry | 175 |

|-----------|--------------------------------------------------------------|-----|

| Figure 51 | External Circuitry for SGMII                                 | 176 |

| Figure 52 | Simplified External Circuitry for SGMII                      | 177 |

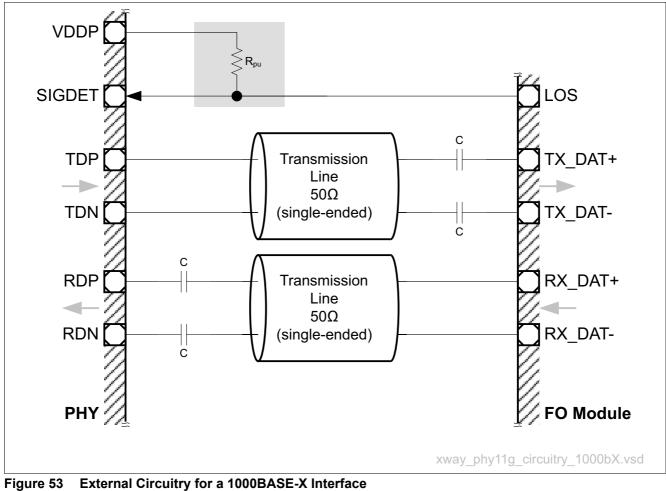

| Figure 53 | External Circuitry for a 1000BASE-X Interface                | 178 |

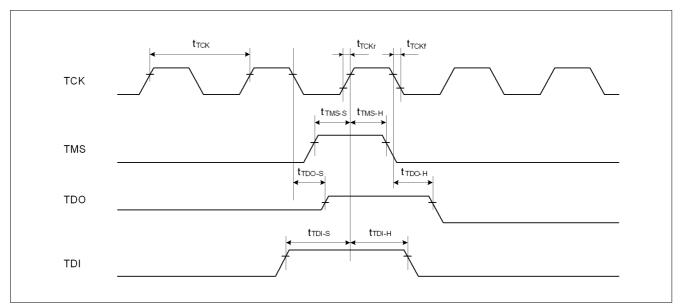

| Figure 54 | JTAG Timing Definition                                       | 179 |

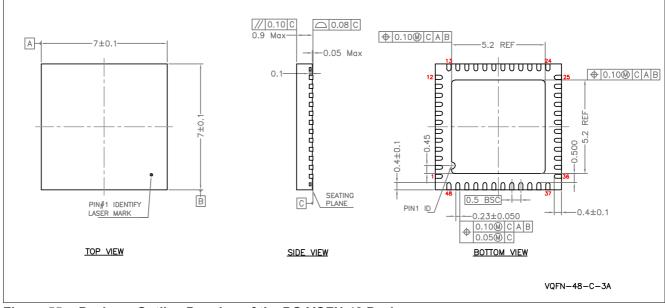

| Figure 55 | Package Outline Drawing of the PG-VQFN-48 Package            | 180 |

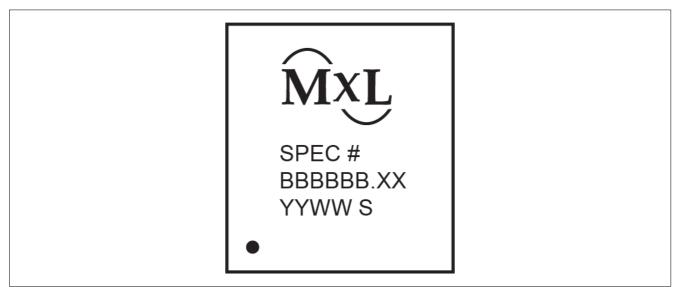

| Figure 56 | Chip Marking of GPY111                                       | 181 |

List of Tables

# List of Tables

| Table 1  | Abbreviations for Pin Types                                                                  | . 18 |

|----------|----------------------------------------------------------------------------------------------|------|

| Table 2  | Abbreviations for Buffer Types                                                               | . 18 |

| Table 3  | General Pins                                                                                 | . 19 |

| Table 4  | Twisted-Pair Interface Pins                                                                  | . 20 |

| Table 5  | Media-Independent Interface Pins                                                             | . 21 |

| Table 6  | Control Interface Pins                                                                       | . 26 |

| Table 7  | JTAG Interface Pins                                                                          | . 27 |

| Table 8  | Power Supply Pins                                                                            | . 28 |

| Table 9  | MII and MDI Combinations Supported by GPY111                                                 | . 29 |

| Table 10 | xMII Signal Multiplexing                                                                     | . 30 |

| Table 11 | Operation of Various Interfaces for Different FLOW and MODE Settings                         | . 31 |

| Table 12 | Transmit Control Encoding                                                                    | . 33 |

| Table 13 | Receive Control Encoding                                                                     | . 33 |

| Table 14 | Supported Twisted-Pair Mappings                                                              | . 38 |

| Table 15 | Soft Pin-Strapping: Mapping of Pull-Down Capacitance/Resistor Values to Configuration Bits . | . 42 |

| Table 16 | Mapping of Configuration Pins/Bits to Device Parameters (No EEPROM Connected)                | . 42 |

| Table 17 | Functions of Device Parameters Controlled by Soft Pin-Strapping (No EEPROM Connected) .      | . 43 |

| Table 18 | Mapping of Configuration Pins/Bits to Device Parameters (EEPROM is Connected)                |      |

| Table 19 | Functions of Device Parameters controlled by Soft Pin-Strapping (EEPROM is Connected)        | . 44 |

| Table 20 | Supported EEPROM Devices                                                                     | . 46 |

| Table 21 | Configuration Signature Record (CSR)                                                         | . 47 |

| Table 22 | Configuration Content Record                                                                 |      |

| Table 23 | Address Bit Mapping in 11-Bit Addressing Mode                                                | . 49 |

| Table 24 | Address Bit Mapping in 16-Bit Addressing Mode                                                |      |

| Table 25 | Definition of MDIO Frame Components                                                          |      |

| Table 26 | MDIO Indirect MMD Device Address Overview                                                    |      |

| Table 27 | Direct LED Functions                                                                         | . 62 |

| Table 28 | Complex LED Functions                                                                        |      |

| Table 29 | Switching Regulator External Component Values                                                | . 65 |

| Table 30 | Programming Sequence for the Wake-On-LAN Functionality                                       |      |

| Table 31 | JTAG TAP Controller Op-Codes                                                                 | . 74 |

| Table 32 | JTAG Boundary Scan ID                                                                        | . 74 |

| Table 33 | Registers Address Space                                                                      | . 79 |

| Table 34 | Registers Overview                                                                           | . 79 |

| Table 35 | Register Access Types                                                                        | . 81 |

| Table 36 | Registers Address Space                                                                      |      |

| Table 37 | Registers Overview                                                                           | 131  |

| Table 38 | Register Access Types                                                                        | 132  |