Features

# High Performance, Single Synchronous Step-Down Controller for Notebook Power Supply

## **General Description**

The uP1537 is a high-efficiency, single synchronous buck controller suitable for low output voltage point-of-load applications in notebook computers and similar digital consumer applications. The proprietary RCOT™ technology provides fast transient response and high noise immunity. It supports ceramic output capacitors. An advantage of this control scheme is that it does not require an external phase compensation network, helping the designer with ease-of-use and realizing low external component count configuration. This combination is ideal for building modern low duty ratio, ultra-fast load step response DC-DC converters. The output voltage ranges from 0.7 V to 2.6V, and the conversion input voltage range is from 3 V to 26V. The switching frequency is selectable from four preset values using a resistor connected from the RF pin to ground. RCOT™ control tracks the preset switching frequency over a wide range of input and output voltages, while it increases the switching frequency at stepup of load.

The RF pin also serves in selecting between auto-skip mode and forced continuous conduction mode for light load conditions. The strong gate drivers of the uP1537 allow low  $R_{\tiny DS(ON)}$  FETs for high current applications.

## **Applications**

- Notebook Computers

- I/O Supplies

- System Power Supplies

## ■ Wide Input Voltage Range 3V ~ 26V

- ☐ Output Voltage Range 0.7V ~ 2.6V

- Build-in 1% 0.7V Reference

- RCOT™ (Robust Constant On-Time) Control Architecture

- 4 Selectable Frequency Setting

- 4700ppm/°C R<sub>DS(ON)</sub> Currrent Sensing

- Internal 1ms Soft-start

- Pre-charged Start-up Capability

- Built-in Output Discharge

- Power OK Indication

- Over Voltage, Under Voltage, and Over Temperature Protection

- WDFN3x3-10L and WQFN2x2-12L package

- RoHS Compliant and Halogen Free

## **Ordering Information**

| Order Number | Package Type | Top Marking |  |  |  |

|--------------|--------------|-------------|--|--|--|

| uP1537PDDA   | WDFN3x3-10L  | uP1537P     |  |  |  |

| uP1537RQKB   | WQFN2x2-12L  | uP1537R     |  |  |  |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

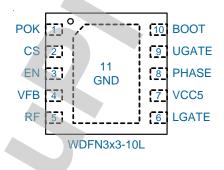

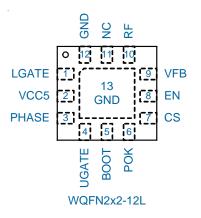

# **Pin Configuration**

# Functional Pin Description

| Pin No.     |         | 5: N     | Die Ferranden                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| uP1537P     | uP1537R | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 1           | 6       | POK      | Power OK Indicator. This pin is an open-drain output.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2           | 7       | CS       | Over Current Protection Setting. Connect a resistor from this pin to GND to set the over current protection level.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 3           | 8       | EN       | Chip Enable. Short to GND to disable the device.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4           | 9       | VFB      | <b>eedback Input.</b> This pin is the inverting input to the error amplifier. A resistorider from output to GND is used to set regulator voltage.                                                                                                                                                                                                                                                                                        |  |  |  |

| 5           | 10      | RF       | itching Frequency Programming. This pin also controls Auto-skip mode or ced CCM selection. Connect a resistor from this pin to GND: Auto-Skip Mode. nnect a resistor from this pin to POK: Forced CCM after POK becomes high.                                                                                                                                                                                                            |  |  |  |

|             | 12      | GND      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 6           | 1       | LGATE    | <b>ower MOSFET Gate Driver Output.</b> Connect this pin to the gate of lower MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry of determine when the lower MOSFET has turned off.                                                                                                                                                                                                                         |  |  |  |

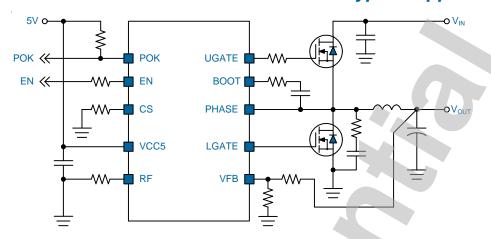

| 7           | 2       | VCC5     | <b>Supply Voltage for the IC</b> . This pin provides bias voltage for the IC. Connect this pin to 5V voltage source and bypass it with a R/C filter.                                                                                                                                                                                                                                                                                     |  |  |  |

| 8           | 3       | PHASE    | <b>Switch Node.</b> Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin is used as the sink for the UGATE driver. This pin is also monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off. A Schottky diode between this pin and ground is recommended to reduce negative transient voltage which is common in a power supply system. |  |  |  |

| 9           | 4       | UGATE    | <b>Upper MOSFET Gate Driver Output.</b> Connect this pin to the gate of upper MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                                                                                                                                        |  |  |  |

| 10          | 5       | воот     | Bootstrap Supply for the Floating Upper MOSFET Gate Driver. Connect the bootstrap capacitor $C_{\text{BOOT}}$ between BOOT pin and the PHASE pin to form a bootstrap circuit. The bootstrap capacitor provides the charge to turn on the upper MOSFET. Ensure that $C_{\text{BOOT}}$ is placed near the IC.                                                                                                                              |  |  |  |

|             | 11      | NC       | Not Internally Connected.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Exposed Pad |         | ad       | <b>Ground.</b> The exposed pad dominates heat conduction path and should be well soldered to PCB for optimal thermal performance.                                                                                                                                                                                                                                                                                                        |  |  |  |

# Typical Application Circuit

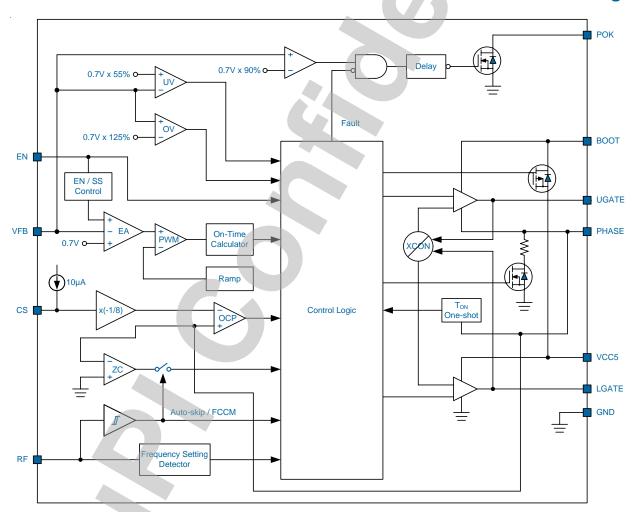

# Functional Block Diagram

## Functional Description

The uP1537 implements an unique RCOT<sup>™</sup> control topology for the synchronous Buck. The uP1537 does not require the external compensator. The RCOT<sup>™</sup> supports extremely low ESR output capacitors and makes the design easier and robust.

#### **Enable and Soft Start**

When the EN pin voltage rises above the enable threshold, the controller enters its start up sequence. The first  $250\mu s$  calibrates the switching frequency setting resistance attached at RF to GND and stores the switching frequency code in internal registers. A voltage of 0.1V is applied to RF for measurement. Switching is inhibited during this period. In the second period, internal soft-start reference voltage starts ramping up from 0V to 0.7V. This ramping time is  $750\mu s$ . Smooth and constant ramp up of the output voltage is maintained during start up regardless of load current. Connect a  $1k\Omega$  resistor in series with the EN pin to provide protection.

### **On-Time Control and Frequency Setting**

The uP1537 does not have a dedicated oscillator that determines switching frequency. However, the device runs with pseudo-constant frequency by feed-forwarding the input and output voltages into its on-time one-shot timer. The RCOT™ control adjusts the on-time to be inversely proportional to the input voltage and proportional to the output voltage. This makes the switching frequency fairly constant in steady state conditions over wide input voltage range. The switching frequency is selectable from four preset values by a resistor connected to RF as shown in Table 1. Leaving the RF pin open sets the switching frequency to the lowest value, 290kHz, with Auto-skip mode. However, it is recommended to apply one of the resistances on the table in any application designs.

Table 1. Resistor and Switching Frequency

| Resistance ( $R_{RF}$ ) ( $k\Omega$ ) | Switching Frequency (f <sub>sw</sub> ) (kHz) |

|---------------------------------------|----------------------------------------------|

| 470                                   | 290                                          |

| 200                                   | 340                                          |

| 100                                   | 380                                          |

| 39                                    | 430                                          |

The off-time is modulated by a PWM comparator. The VFB node voltage (the mid point of resistor divider) is compared to the internal 0.7V reference voltage added with a ramp signal. When both signals match, the PWM comparator asserts the set signal to terminate the off-

time (turn off the low side MOSFET and turn on high side MOSFET). The set signal becomes valid if the inductor current level is below OCP threshold, otherwise the off-time is extended until the current level becomes below the threshold.

### **Light Load Condition in Auto-Skip Operation**

When RF pin is pulled down to low via R<sub>RF</sub>, the uP1537 automatically reduces switching frequency at light load to maintain high efficiency. This reduction of the frequency is achieved smoothly and without increasing VOUT ripples or load regulation. As the output current decreases from heavy load condition, the inductor current will also be reduced, and eventually comes to the point that its valley touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. By emulating the behavior of diodes, the low side MOSFET allows only partial of negative current when the inductor freewheeling current reaches negative. As the load current is further decreased, it takes longer time to discharge the output capacitor to the level than requires the next ON cycle.

The transition point from discontinuous to continuous conduction mode can be calculated as:

$$I_{OUT} = \frac{1}{2 \times f_{OSC} \times L_{OUT}} \times V_{OUT} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

### **Forced Continuous Conduction Mode**

When the RF pin is tied high, the controller keeps continuous conduction mode (CCM) in light load condition. In this mode, switching frequency is kept almost constant over the entire load range which is suitable for applications need tight control of the switching frequency at a cost of lower efficiency. To set the switching frequency to be the same as Auto-skip mode, it is recommended to connect  $R_{\rm RF}$  to POK. In this way, RF is tied low prior to soft-start operation to set frequency and tied high after POK indicates high.

#### **Output Voltage Setting**

Connect a resistor voltage-divider at the FB between VOUT and GND to adjust the respective output voltage between 0.7V and 2.6V. Choose  $R_{\rm FB2}$  and solve for  $R_{\rm FB1}$  using the equation as follows:

$$V_{OUT} = V_{REF} \times (1 + \frac{R_{FB1}}{R_{FB2}})$$

where  $V_{REF}$  is 0.7V (typ.).

## Functional Description

#### POK

The uP1537 has POK output that indicates high when switcher output is within the target. The POK function is activated after soft-start has finished. If the output voltage becomes within 90% of the target value, internal comparators detect POK state and the POK signal becomes high after a 1ms internal delay. If the output voltage goes outside of 55% of the target value, the POK signal becomes low. The POK output is an open-drain output and should be pulled up externally if used.

#### **Output Discharge Control**

When EN is low, the uP1537 discharges the output capacitor using internal MOSFET connected between PHASE and GND while high side and low side MOSFETs are kept off. The current capability of this MOSFET is limited to discharge slowly.

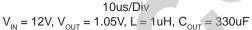

#### **Over Current Limit**

The uP1537 monitors the inductor valley current by low side MOSFET  $R_{DS(ON)}$  when it turns on. The over current limit is triggered once the sensing current level is higher than  $V_{OCSET}$ . When triggered, the over current limit will keep high side MOSFET off even the voltage loop commands it to turn on.

The output voltage will decrease if the load continuously demands more current than current limit level. The current limit level is set at  $I_{LIM}/2$  if the output voltage is lower than 90% of its target level, letting  $V_{OUT}$  decrease faster until UVP occurs and shuts down the uP1537.

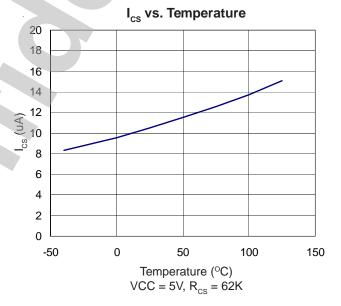

The current limit threshold is set by connecting a resistor from CS to GND. The CS pin will sink a  $10\mu\text{A}$  current source and create a voltage drop across  $R_{cs}$  as the  $V_{ocset}$  . Vocset =  $10\mu\text{A}$  x  $R_{cs}$ . When the voltage drop across the low side MOSFET equals the voltage across the setting resistor, the current limit will be activated.

The voltage across PHASE and GND pins is compared with  $\rm V_{\rm ocset}$  for current limit. The current limit level is calculated as:

$$I_{LIM} = \frac{V_{OCSET}}{8 \times R_{DS(ON)}} + \frac{I_{RIPPLE}}{2}$$

where  $\mathbf{I}_{\text{RIPPLE}}$  is the peak-to-peak inductor ripple current at steady state.

### Over Voltage/Under Voltage Protection

The uP1537 monitors feedback voltage to detect overvoltage and undervoltage. When the feedback voltage becomes higher than 125% of the target voltage, the OVP is triggered, high side MOSFET is off and low side MOSFET is on. When the feedback voltage is lower than

55% of the target voltage, the UVP is triggered, then high side MOSFET and low side MOSFET are latched. This function is enabled after 1ms following EN has becomes high.

### **VCC5 UVLO**

The uP1537 has VCC5 under voltage lockout protection (UVLO) that inhibits switching and resets the protection faults

When the VCC5 voltage is lower than UVLO threshold voltage, all functions are turned off. This is the non-latch protection.

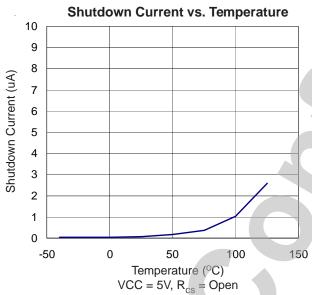

#### **Over Temperature Protection**

The uP1537 monitors the temperature of itself. If the temperature exceeds typical 150°C, the uP1537 will be turned off. This is the non-latch protection. It will be recovered once temperature is lower than 130°C.

|                                              | — Absolute Maximum Rating   |

|----------------------------------------------|-----------------------------|

| (Note 1)                                     |                             |

| VCC5 to GND                                  |                             |

| BOOT to GND                                  |                             |

| DC                                           |                             |

| < 200ns                                      | 5V to +42V                  |

| BOOT to PHASE                                |                             |

| DC                                           |                             |

| < 200ns                                      | 5V to +7.5V                 |

| PHASE to GND                                 |                             |

| DC                                           |                             |

| < 200ns                                      | 5V to +38V                  |

| UGATE to GND DC                              |                             |

|                                              |                             |

| <200ns                                       |                             |

| UGATE to PHASE                               | 0.31/45.461/                |

| DC<                                          | 5\/ to +7\/                 |

| LGATE to GND                                 | -57 (0 +77                  |

| DC                                           |                             |

| <200ns                                       |                             |

| Other Pins to GND                            |                             |

| Storage Temperature Range                    |                             |

| Lead Temperature (Soldering, 10 sec)         |                             |

|                                              | 260°C                       |

| ESD Rating (Note 2) HBM (Human Body Mode)    | 214                         |

| MM (Machine Mode)                            |                             |

| wiw (wacrime wode)                           |                             |

|                                              | Thermal Information         |

| Package Thermal Resistance (Note 3)          |                             |

| WDFN3x3-10L $\theta_{JA}$                    | 68°C/W                      |

| WDFN3x3-10L $\theta_{IC}$                    |                             |

| WDFN2x2-12L θ <sub>JC</sub>                  |                             |

| WDFN2x2-12L θ <sub>.IC</sub>                 |                             |

| Power Dissipation, $P_D @ T_A = 25^{\circ}C$ | <b>-</b> 5 <b>-</b> 7       |

| WDFN3x3-10L                                  | 1 47\\                      |

| WDFN2x2-12L                                  |                             |

| WDI 14272-12L                                | 0.03W                       |

| Recomm                                       | nended Operation Conditions |

| (Note 4)                                     | <del>-</del>                |

| Input Voltage, V <sub>IN</sub>               | 3V to 26V                   |

| Operating Junction Temperature Range         |                             |

| Operating Ambient Temperature Range          | 40°C to +85°C               |

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- Note 3.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for

Note 4. The device is not guaranteed to function outside its operating conditions.

extended periods may remain possibility to affect device reliability.

## Electrical Characteristics

( $V_{IN}$  = 12V,  $V_{VCCS}$  = 5.0V,  $V_{OUT}$  = 1.05V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                               | Symbol                  | Test Conditions                                                        | Min  | Тур   | Max  | Unit |

|-----------------------------------------|-------------------------|------------------------------------------------------------------------|------|-------|------|------|

| Supply Current                          | 2,                      |                                                                        |      | .76   |      | 1    |

| VCC5 Supply Current                     | ı                       | V <sub>EN</sub> = 5V, No Load                                          |      | 320   | 500  | μΑ   |

| VCC5 Shutdown Current                   | VCC5                    |                                                                        |      | 320   |      |      |

|                                         | VCC5_SD                 | $V_{EN} = 0V$ , No Load                                                |      |       | 1    | μΑ   |

| Internal Reference Voltage              | I                       |                                                                        |      |       |      |      |

| VFB Regulation Voltage                  | V <sub>FB</sub>         | CCM condition                                                          |      | 0.704 |      | V    |

|                                         | ГВ                      | Tolerance                                                              | -1.0 |       | +1.0 | %    |

| VFB Input Current                       | I <sub>FB</sub>         | $V_{FB} = 0.735V$ , skip mode                                          |      | 0.01  | 0.2  | μΑ   |

| Output Discharge                        |                         |                                                                        |      |       |      |      |

| Output Discharge Current from PHASE Pin | <b>I</b> <sub>DIS</sub> | $V_{EN} = 0V, V_{PHASE} = 0.5V$                                        | 5    | 13    |      | mA   |

| Output Drivers                          | •                       |                                                                        |      |       |      | •    |

| UGATE Resistance                        | R <sub>UGATE</sub>      | Source, I <sub>UGATE</sub> = - 150mA                                   |      | 2     |      | Ω    |

|                                         |                         | Sink, I <sub>UGATE</sub> = 150mA                                       |      | 1     |      |      |

| LOATE Desistance                        | R <sub>LGATE</sub>      | Source, I <sub>LGATE</sub> = -150mA                                    |      | 1     |      | Ω    |

| LGATE Resistance                        |                         | Sink, I <sub>LGATE</sub> = 150mA                                       |      | 0.7   |      |      |

|                                         | T <sub>D</sub>          | UGATE-off to LGATE-on                                                  |      | 17    |      | ns   |

| Dead Time                               |                         | LGATE-off to UGATE-on                                                  |      | 22    |      |      |

| Internal Bootstrap Switch               |                         |                                                                        | ı    |       |      | 1    |

| Internal Resistance                     | R <sub>BST_F</sub>      | $I_F = 10mA$                                                           |      | 80    |      | Ω    |

| Reverse Leakage Current                 | I <sub>BST_LK</sub>     | V <sub>BOOT</sub> = 26V                                                |      | 0.01  | 1.5  | μΑ   |

| Duty and Frequency Control              |                         |                                                                        |      |       |      |      |

| Minimum Off-Time                        | T <sub>OFF_MIN</sub>    |                                                                        |      | 400   |      |      |

| Minimum On-Time                         | T <sub>ON_MIN</sub>     | $V_{IN} = 26V, V_{OUT} = 0.7V, R_{RF} = 39k\Omega$                     |      | 80    |      | ns   |

| Soft Start                              |                         |                                                                        |      |       |      |      |

| Internal SS Time                        | T <sub>ss</sub>         | From V <sub>EN</sub> = high to V <sub>OUT</sub> = 90%                  |      | 1     |      | ms   |

| POK Comparator                          |                         |                                                                        | 1    |       |      |      |

| POK Threshold                           | V <sub>TPOK</sub>       | POK in from lower, V <sub>FB</sub> with respect to reference, No load. | 87   | 90    | 93   | %    |

| POK Sink Current                        | I <sub>POK_MAX</sub>    | V <sub>POK</sub> = 0.5V                                                |      | 50    |      | mA   |

| POK Delay Time                          | T <sub>POK_DEL</sub>    | Delay from 90% of V <sub>FB</sub> to POK go high                       | 0.8  | 1     | 1.2  | ms   |

## Electrical Characteristics

| Parameter                               | Symbol                | Test Conditions                             | Min  | Тур         | Max | Unit |  |

|-----------------------------------------|-----------------------|---------------------------------------------|------|-------------|-----|------|--|

| Logic Threshold and Setting Co          | nditions              |                                             |      |             |     |      |  |

| EN Voltage Threshold                    | V <sub>EN</sub>       | Enable                                      | 1.8  |             |     | V    |  |

|                                         |                       | Disable                                     | 5-7  | ) +         | 0.5 |      |  |

| EN Input Current                        | I <sub>EN</sub>       | V <sub>EN</sub> = 5V                        |      | <b>/-</b> - | 1   | μΑ   |  |

|                                         | T <sub>on</sub>       | $R_{RF} = 470k\Omega$ for $F_{SW} = 290kHz$ |      | 302         |     | ns   |  |

| On Time                                 |                       | $R_{RF} = 200k\Omega$ for $F_{SW} = 340kHz$ | -    | 257         |     |      |  |

| On-Time                                 |                       | $R_{RF} = 100k\Omega$ for $F_{SW} = 380kHz$ |      | 230         |     |      |  |

|                                         |                       | $R_{RF} = 39k\Omega$ for $F_{SW} = 430kHz$  |      | 203         |     |      |  |

| CCM Setting Voltage                     | V <sub>RF</sub>       | ССМ                                         | 1.8  |             |     | V    |  |

|                                         |                       | Auto-Skip                                   |      |             | 0.5 |      |  |

| Protection: Current Sense               |                       |                                             |      |             |     |      |  |

| CS Source Current                       | I <sub>cs</sub>       |                                             | 9    | 10          | 11  | μΑ   |  |

| OCP Comparator Offset                   | V <sub>OC_OFS</sub>   | A (C)                                       | - 10 | 0           | 10  | mV   |  |

| Zero Crossing Comparator Offset         | V <sub>ZC_OF</sub>    |                                             | - 4  | - 2         | 0   | mV   |  |

| Protection: UVP and OVP                 |                       |                                             |      | 1           |     |      |  |

| Over Voltage Trip Threshold Voltage     | V <sub>OVP</sub>      | Percentage of V <sub>REF</sub>              | 120  | 125         | 130 | %    |  |

| OVP Propagation Delay Time              | T <sub>OVPDEL</sub>   |                                             |      | 5           |     | μs   |  |

| Under Voltage Trip Threshold<br>Voltage | V <sub>UVP</sub>      | Percentage of V <sub>REF</sub>              | 50   | 55          | 60  | %    |  |

| Output UVP Enable Delay Time            | T <sub>UVPEN</sub>    | From Enable to UVP workable                 | 1    |             |     | ms   |  |

| UVLO                                    |                       |                                             | I    | !           |     |      |  |

| WOOF DOD That I I I                     | V <sub>UVLOVCC5</sub> | Rising                                      | 3.8  | 4           | 4.2 | V    |  |

| VCC5 POR Threshold                      |                       | Hysteresis                                  |      | 0.3         |     | V    |  |

| Thermal Shutdown                        |                       |                                             |      |             |     |      |  |

| The second Objection of Theoretical     | T <sub>SDN</sub>      | Shutdown temperature                        |      | 150         |     | °C   |  |

| Thermal Shutdown Threshold              |                       | Hysteresis                                  |      | 20          |     | οС   |  |

# **Typical Operation Characteristics**

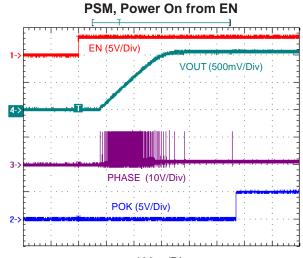

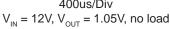

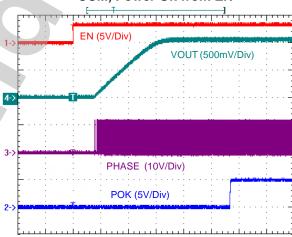

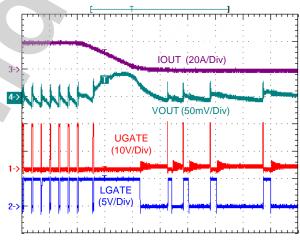

### **PSM**, Power On from EN

$$V_{\text{IN}} = 12 \text{V}, V_{\text{OUT}} = 1.05 \text{V}, \text{Load} = 0.05 \Omega$$

$$V_{IN} = 12V, V_{OUT} = 1.05V, \text{ no load}$$

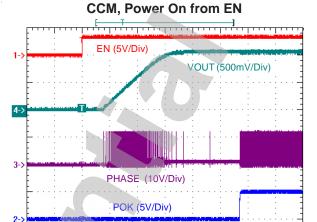

### CCM, Power On from EN

$$V_{IN} = 12V, V_{OUT} = 1.05V, Load = 0.05\Omega$$

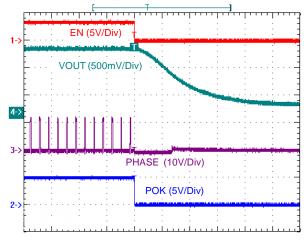

### **CCM**, Power Off from EN

$$V_{IN} = 12V, V_{OUT} = 1.05V, Load = 0.05\Omega$$

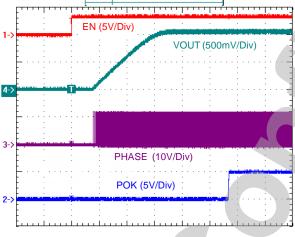

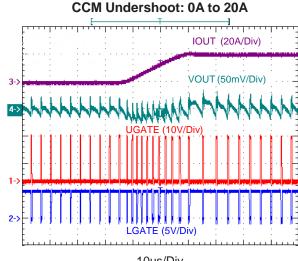

# **Typical Operation Characteristics**

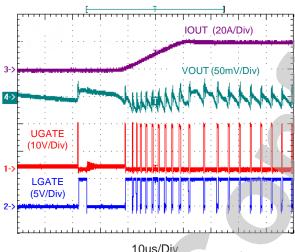

$10 us/Div \\ V_{_{IN}} = 12 V, \ V_{_{OUT}} = 1.05 V, \ L = 1 uH, \ C_{_{OUT}} = 330 uF$

### PSM Undershoot: 0.1A to 20A

10us/Div

$$V_{IN} = 12V$$

,  $V_{OUT} = 1.05V$ ,  $L = 1uH$ ,  $C_{OUT} = 330uF$

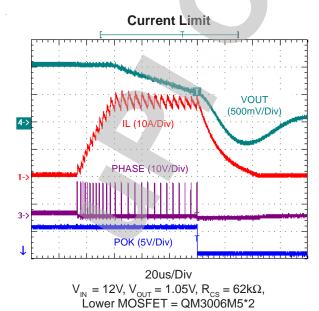

### PSM Overshoot: 20A to 0.1A

10us/Div

$$V_{IN} = 12V, V_{OUT} = 1.05V, L = 1uH, C_{OUT} = 330uF$$

# **Typical Operation Characteristics**

## Application Information

### **Output Inductor Selection**

The inductor plays an important role in step-down converters because it stores the energy from the input power rail and then releases the energy to the load. From the viewpoint of efficiency, the dc resistance (DCR) of the inductor should be as small as possible to minimize the conduction loss. In addition, the inductor covers a significant proportion of the board space, so its size is also important. Low profile inductors can save board space especially when the height has a limitation. However, low DCR and low profile inductors usually cost ineffective.

Additionally, larger inductance results in lower ripple current which translates into the lower power loss. However, the inductor current rising time increases with inductance value. This means the transient response will be slower. Therefore, the inductor design is a trade-off between performance, size and cost.

In general, the switching frequency (on-time) and operating point (% ripple or LIR) determine the inductor value as shown in the following equation:

$$L = \frac{t_{ON} \times (V_{IN} - V_{OUT})}{LIR \times I_{LOAD(MAX)}}$$

where LIR is the ratio of the peak to peak ripple current to the average inductor current.

Find a low loss inductor having the lowest possible DC resistance that fits in the allotted dimensions. Ferrite cores are often the best choices because powdered iron is inexpensive and can work well at 200kHz. The core must be large enough not to saturate at the peak inductor current ( $I_{DEAK}$ ):

$$I_{PEAK} = I_{LOAD(MAX)} + \frac{LIR}{2} \times I_{LOAD(MAX)}$$

The calculation above shall serve as a general reference. To further improve the transient response, the output inductance can be reduced even further. This needs to be considered along with the selection of the output capacitor.

### **Output Capacitor Selection**

The capacitor value and ESR determine the amount of output voltage ripple and load transient response. Thus, the capacitor value must be greater than the largest value calculated from below equations:

$$V_{SOAR} = \frac{\Delta I_{LOAD}^2 \times L}{2 \times C_{OUT} \times V_{OUT}}$$

$$V_{P-P} = LIR \times I_{LOAD(MAX)} \times (ESR + \frac{1}{8 \times C_{OUT} \times f_{SW}})$$

where  $V_{\text{SOAR}}$  are the allowable amount of undershoot voltage and overshoot voltage in the load transient,  $V_{\text{P-P}}$  is the output ripple voltage.

#### **MOSFET Selection**

The majority of power loss in the step-down power converter is the loss in the power MOSFETs. For low voltage high current applications, the duty cycle of the upper MOSFET is small. Therefore, the switching loss of the upper MOSFET is of concern. Power MOSFETs with lower total gate charge are preferred in such kind of application. However, the small duty cycle means the lower MOSFET is on for most of the switching cycle. Therefore, the conduction loss tends to dominate the total power loss of the converter.

To improve the overall efficiency, MOSFETs with low R<sub>DS(ON)</sub> are preferred in the circuit design. In some cases, more than one MOSFET are connected in parallel to further decrease the on-state resistance. However, this depends on the MOSFET driver capability and the budget.

#### **Layout Considerations**

Layout is very important in high frequency switching converter designs, the PCB could radiate excessive noise and contribute to the converter instability with improper layout. Certain points must be considered before starting a layout.

- 1 Place the filter capacitor close to the IC.

- 2 Keep current limit setting network as close as possible to the IC. Routing of the network should avoid coupling to high voltage switching node.

- 3 Connections from the drivers to the respective gate of the both MOSFETs should be as short as possible to reduce stray inductance.

- 4 All sensitive analog traces and components such as VFB, GND, EN, POK, and RF should be placed away from high voltage switching nodes such as PHASE, LGATE, UGATE, or BOOT nodes to avoid coupling. Use internal layer(s) as ground plane(s) and shield the feedback trace from power traces and components.

- 5 Place the ground terminals of VIN capacitor(s), VOUT capacitor(s), and source of lower MOSFETs as close as possible. The PCB trace defined as PHASE node, which connects to source of upper MOSFET, drain of lower MOSFET and high voltage side of the inductor, should be as short and wide as possible.

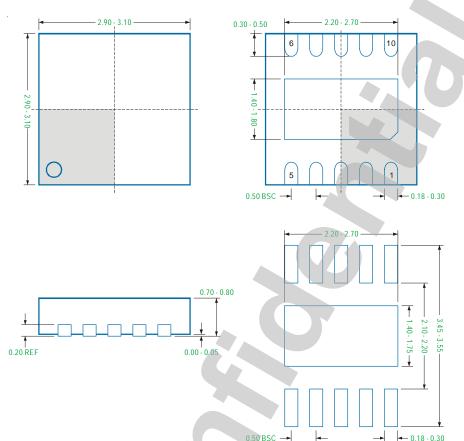

## Package Information

### **WDFN3X3 - 10L**

Recommended Solder Pitch and Dimensions

### Note

- 1. Package Outline Unit Description:

- BSC: Basic. Represents theoretical exact dimension or dimension target

- MIN: Minimum dimension specified.

- MAX: Maximum dimension specified.

- REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

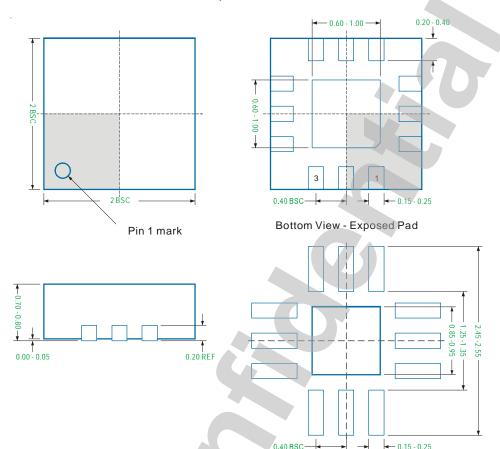

## Package Information

### **WQFN2x2 - 12L**

Recommended Solder Pad Pitch and Dimensions

### Note

- 1. Package Outline Unit Description:

- BSC: Basic. Represents theoretical exact dimension or dimension target

- MIN: Minimum dimension specified.

- MAX: Maximum dimension specified.

- REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

### **Important Notice**

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment. However, no responsibility is assumed by uPI or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (c) 2011, UPI SEMICONDUCTOR CORP.

Headquarter 9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu Taiwan, R.O.C.

TEL: 886.3.560.1666 FAX: 886.3.560.1888

Sales Branch Office 12F-5, No. 408, Ruiguang Rd. Neihu District, Taipei Taiwan, R.O.C.

TEL: 886.2.8751.2062 FAX: 886.2.8751.5064