Features

# Smart 5V Dual Controller

### **General Description**

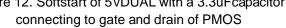

The uP7501 is a switch controller specifically designed to provide 5VDUAL voltage for modern motherboards. It controls the switches to power 5VDUAL plane according to the Sleeping State complaint with ACPI specification: switching in the ATX/BTX 5VCC output through an NMOS transistor in active states, or switching in the ATX/BTX 5VSB through a PMOS transistor in S3 sleep state. A MODE pin programs whether 5VDUAL is shut down or stays on during S4/S5 state.

Soft start function is implemented to limit inrush current from 5VSB supply voltage.

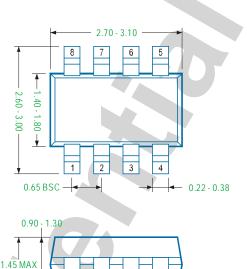

This part comes to a tiny SOT23-8L package.

Applications

□ ACPI-Compliant Power Regulation for Motherboards

### Provide ACPI-Complaint 5VDUAL Voltage

- □ 5VDUAL USB/Keyboard/Mouse

- Small Size; Low External Component Count

- □ Internal Soft Start

- RoHS Compliant and Halogen-Free

### Ordering Information

| Order Number | Package Type | Top Marking |

|--------------|--------------|-------------|

| uP7501M8     | SOT23-8L     | SO          |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

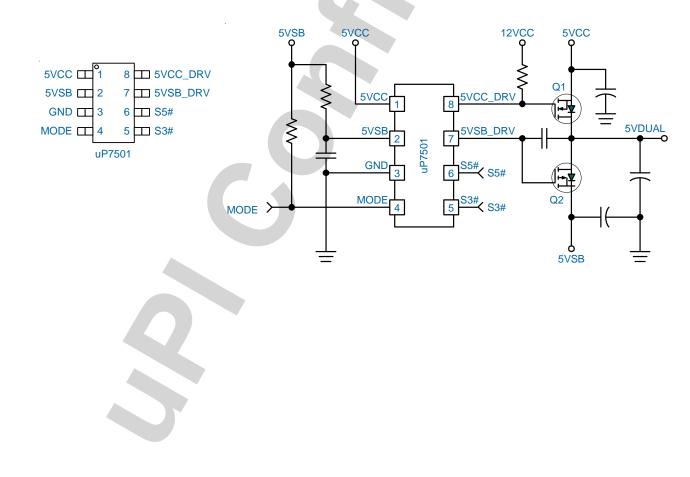

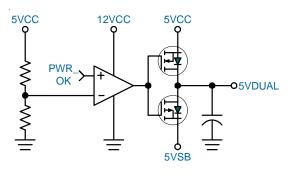

### **Pin Configuration & Typical Application Circuit**

# - Functional Pin Description

| No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 5VCC     | <b>5VCC Input.</b> This pin is continuously monitored for power on reset (POR). The POR threshold level is 4.2V with 0.2V hysteresis. Connect this pin to ATX 5VCC.                                                                                                                                                                                                                                                                                            |

| 2   | 5VSB     | <b>5VSB Input.</b> This pin is power input of the uP7501. This pin is continuously monitored for POR. The POR threshold level is 4.2V with 0.2V hysteresis. Connected this pin to ATX 5VSB with a ceramic decoupling capacitor directly to GND pin.                                                                                                                                                                                                            |

| 3   | GND      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4   | MODE     | <b>Mode Selection.</b> This pin programs whether 5VDUAL is shut down or stays on during S4/S5 state. Logic low shuts down 5VDUAL during S4/S5 state. Logic high powers the 5VDUAL plane from ATX 5VSB during S4/S5 state.                                                                                                                                                                                                                                      |

| 5   | S3#      | <b>S3# Input.</b> This pin companied with S5# switches the IC's operating state from active (S0, S1/S2) to S3 and S4/S5 sleep states. This pin is internally pulled down by a 7uA current source. State 0 of S3# is regarded as S3 when S5# is high. Connect this pin to the computer system's SLP_S3 signals.                                                                                                                                                 |

| 6   | S5#      | <b>S5# Input.</b> This pin companied with S3# switches the IC's operating state from active (S0, S1/S2) to S3 and S4/S5 sleep states. This pin is internally pulled down by a 7uA current source. State 0 of S5# is regarded as S4/S5 regardless of the S3# state. Connect this pin to the computer system's SLP_S5 signals.                                                                                                                                   |

| 7   | 5VSB_DRV | <b>Driver Output for 5VSB.</b> Connect this pin to the gate of a suitable PMOS. The transistor is switched on/off according S5#, S3# and MODE pins status.                                                                                                                                                                                                                                                                                                     |

| 8   | 5VCC_DRV | <b>Driver Output for 5VCC.</b> Connect this pin to the gate of a suitable NMOS. The transistor is switched on/off according S5# and S3# pins status. This pin is an open-drain output. An 1k $\Omega$ resistor must be connected from this pin to the ATX 12VCC output to pull the gates of suitable NMOS to 12V that switches ATX 5VCC output into 5VDUAL output. This pin is also monitored for 12VCC POR. The POR threshold level is 9V with 1V hysteresis. |

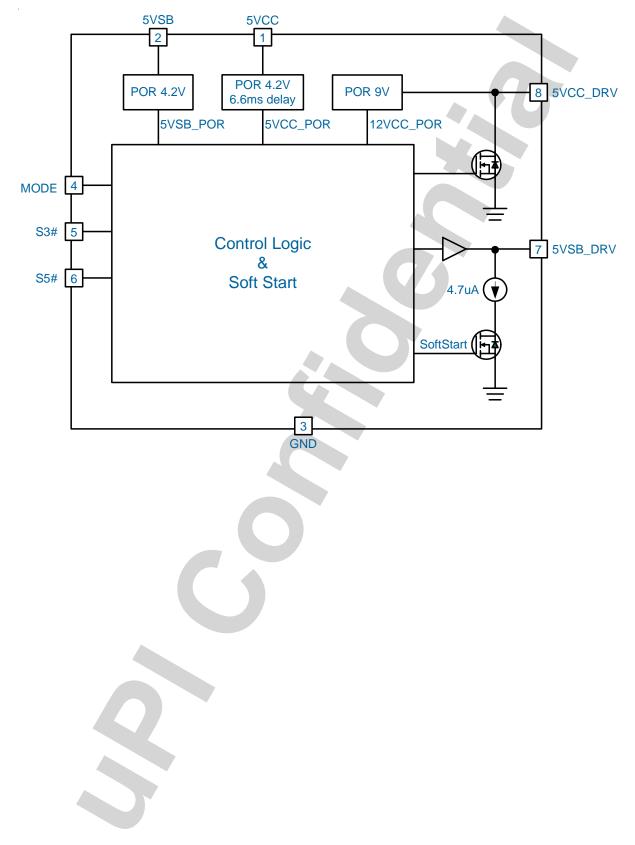

- Functional Block Diagram

### Operation

The uP7501 is a switch controller specifically designed to provide 5VDUAL voltage for modern motherboards. It controls the switches to power 5VDUAL plane according to the Sleeping States complaint with ACPI specification: switching in the ATX/BTX 5VCC output through an NMOS transistor in active states, or switching in the ATX/BTX 5VSB through a PMOS transistor in S3 sleep state. A MODE pin programs whether 5VDUAL is shut down or stays on during S4/S5 state.

### Initialization

The uP7501 automatically initializes upon receipt of input power at 5VSB pin. The Power On Reset (POR) function continually monitors the 5VSB input supply voltage. The rising 5VSB POR threshold is 4.2V typically. The uP7501 also monitors the 12VCC and 5VCC rail to insure that the ATX/BTX rails are up before entering into the S0 state even if S3# and S5# are both high.

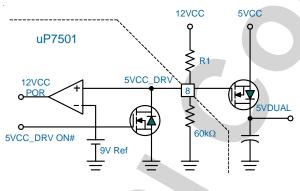

An internal  $60k\Omega$  resistor along with the external pull-high resistor forms a voltage divider when 5VCC\_DRV is set to high as shown in Figure 1. 12VCC is asserted POR when 5VCC DRV pin voltage is higher than 9V that is enough to turn on the NMOS. Choose an appropriate R1 that makes 5VCC DRV above its POR level under normal operation.

### **5VDUAL Output Truth Table**

Table 1 describes the truth combinations pertaining to the 5VDUAL outputs. The 5VDUAL plane is switched into the ATX/BTX 5VCC output through an NMOS transistor in active states when S3# and S5# are both high. It is switched into the ATX/BTX 5VSB through a PMOS transistor in S3 sleep state when S3# is low and S5# is high. The uP7501 asserts S4/S5 state when S5# is low regardless of the S3# status. A MODE pin programs whether 5VDUAL is shut down or stays on during S4/S5 state.

## Functional Description

| li  | Table 1. SVDUAL Output Truth Table |        |         |  |  |  |

|-----|------------------------------------|--------|---------|--|--|--|

| S3# | MODE                               | 5VDUAL | Remarks |  |  |  |

| S5# | S3# | MODE | 5VDUAL   | Remarks           |

|-----|-----|------|----------|-------------------|

| 1   | 1   | Х    | 5VCC     | S0/S1/S2 (Active) |

| 1   | 0   | Х    | 5VSB     | S3                |

| 0   | Х   | 1    | 5VSB     | S4/S5             |

| 0   | Х   | 0    | Shutdown | S4/S5             |

Note that when MODE = L, the 5VDUAL output can only be enabled by 5VCC and 12VCC POR (refer to the related sections for detail).

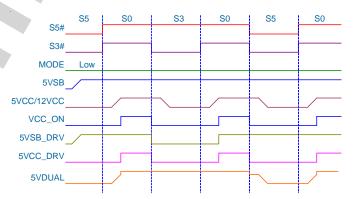

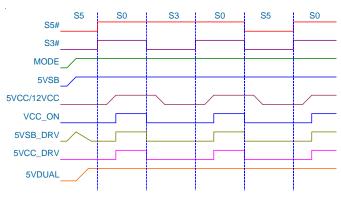

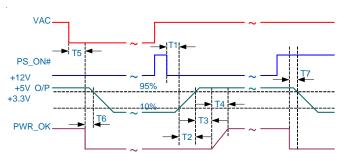

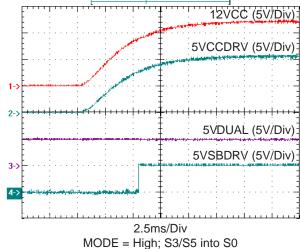

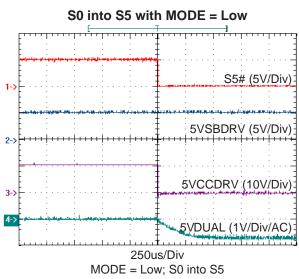

### **Functional Timing Diagrams**

Figures 2 and 3 are simplified timing diagrams with MODE = L and MODE = H respectively, detailing the power up/ down sequences of all the outputs in response to the status of the sleep-state pins (S3#, S5#), as well as the status of the input ATX/BTX supply. Not shown in these diagrams is the deglitching feature used to protect against false sleep state tripping. Additionally, the uP7501 features a 120us delay in transitioning from S0 to S3 states. The transition from the S0 state to S4/S5 state is immediate. The switching between 5VSB and 5VCC is immediately to ensure a seamless 5VDUAL output.

Figure 2. Timing Diagram with MODE = L

Functional Description

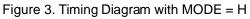

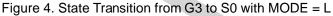

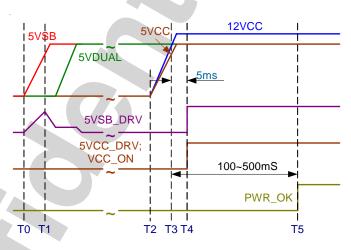

### G3 to S0 State Transition with MODE = L

Figures 4 shows the start up sequence for the typical application power up from G3 state (mechanical off) to S0 state (active) with MODE = L. At time T0, 5VSB (bias) is applied to the circuit. At time T1, the 5VSB surpasses POR level. The uP7501 keeps 5VDUAL voltage off by turning off both PMOS and NMOS. At time T2, the system has transitioned into S0 state and the ATX/BTX supplies have begun to ramp up. The ramping-up 5VCC charges 5VDUAL through the body diode of the NMOS. There is a 0.7V voltage drop between VCC5 and 5VDUAL caused by the body diode. At time T3, 5VCC and 12VCC reach their POR threshold level respectively. At time T4, uP7501 sets high the internal VCC\_ON signal and forces 5VCC\_DRV pin to high impedance state allowing the gate of NMOS be pulled high to 12VCC through external resistor to turn on the NMOS. A 5ms delay is inserted between T3 and T4 to ensure that there is sufficient mains energy stored by the converter to guarantee continuous power operation within specification. There is a voltage jump about 0.7V when uP7501 turns on the NMOS.

It is noted that 5VDUAL is ready before ATX/BTX power supplies set high its PWR\_OK signal.

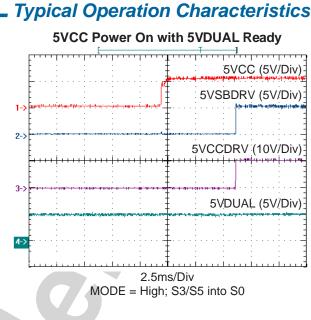

### G3 to S0 State Transition with MODE = H

Figures 5 shows the start up sequence for the typical application power up from G3 state (mechanical off) to S0 state (active) with MODE =H. At time T0, 5VSB (bias) is applied to the circuit. At time T1, the 5VSB surpasses POR level. The uP7501 will draw 4uA into the 5VSB\_DRV for a duration of one soft start period. This current will enhance the PMOS in a controlled manner allowing 5VDUAL ramps up smoothly. At time T2, the system has transitioned into S0 state and the ATX/BTX supplies have begun to ramp up. At time T3, 5VCC and 12VCC reach their POR threshold level respectively. At time T4, uP7501 set high

the internal VCC\_ON signal and force 5VCC\_DRV pin to high impedance state allowing the gate of NMOS be pulled high to 12VCC through external resistor to turn on the NMOS. At time T4, 5VSB\_DRV is pulled high to turn off the PMOS ensuring a seamless transition for 5VSB to 5VCC. A 5ms delay from is inserted between T3 and T4 to ensure that there is sufficient mains energy stored by the converter to guarantee continuous power operation within specification.

Figure 5. State Transition from G3 to S0 with MODE = H

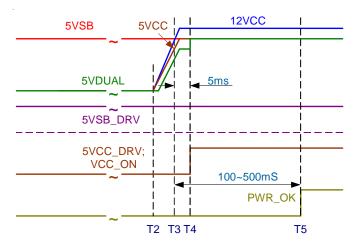

### S5 to S0 State Transition MODE = L

Figures 6 shows the state transition from S5 to S0 with MODE = L. It is exactly the same as the G3 to S0 transition with MODE = L after T2.

Figure 6. State Transition from S5 to S0 with MODE = L

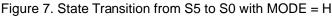

#### S5 to S0 State Transition with MODE = H

Figures 7 shows the state transition from S5 to S0 with MODE = H. It is exactly the same as the G3 to S0 transition with MODE = H after T2.

## Functional Description

### S3 to S0 State Transition with MODE = H/L

This transition is identical to S5 to S0 transition with MODE = H where 5VDUAL is kept on.

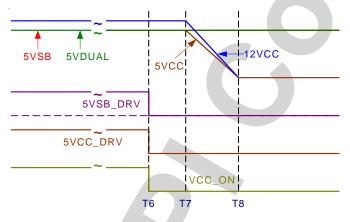

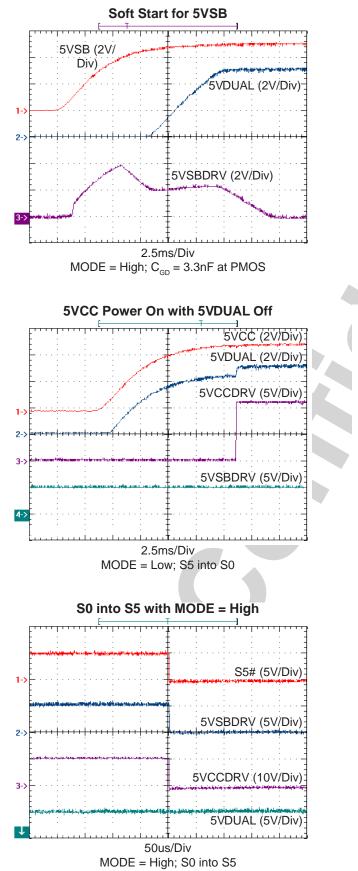

### S0 to S5 State Transition with MODE = H

Figures 8 shows the state transition from S0 to S5 with MODE = H. At time T6, the system has transitioned into S5 state. The uP7501 switches 5VDUAL in 5VSB by pulling low 5VSB\_DRV to turn on the PMOS and pulling low 5VCC\_DRV to turn off the NMOS, ensuring a seamless transition. At time T7, the ATX/BTX power supply turns off and 5VCC and 12VCC start to ramp down and touch 0V at time T8.

### S0 to S5 State Transition with MODE = L

Figures 9 shows the state transition from S5 to S0 with MODE = L. At time T6, the system is transitioned into S0 state. The uP7501 sets internal VCC\_ON low and pull low 5VCC\_DRV to turn off the NMOS. 5VCC/12VCC start ramping down at time T7 where ATX/BTX power supply turns off and touch ground at time T8. 5VDUAL will follow 5VCC waveforms with a diode bias voltage.

### S0 to S3 State Transition with Mode = H/L

This transition is identical to S0 to S5 transition with MODE = H where 5VDUAL is kept on.

Figure 9. State Transition from S0 to S5 with MODE = L

Figure 10 illustrates the timing diagram of ATX/BTX power supplies. The detailed time specifications are illustrated in Table 2. PWR\_OK is a power good signal and should be asserted high by the power supply to indicate that the 3.3VCC/5VCC/12VCC outputs are above the undervoltage thresholds of the power supply. A delay time T3 between 95% rising of 3.3VCC/5VCC/12VCC and PWR\_OK is specified 100ms ~ 2000ms to ensure that there is sufficient mains energy stored by the converter to guarantee continuous power operation within specification. Traditional implementation of 5VDUAL voltage uses PWR\_OK signal to control the switches as shown in Figure 11. 5VDUAL is switched in 5VCC only when PWR\_OK is set high regardless the sleep state signals S3# and S5#.

Some applications require large current from 5VDUAL during T3. Traditional implementation powers 5VDUAL from 5VSB during T3 that cannot provide the demand and may crash.

Figure 10. Timing Diagram of ATX/BTX Power Supplies

Table 2. Typical Timing Specification of ATX/BTX Power Supplies

# Functional Description

| Signal type                       | +5V TTL comptible                               |

|-----------------------------------|-------------------------------------------------|

| Logic level low                   | <0.4V while sinking 4mA                         |

| Logic level high                  | Between 2.4V and 5V output while sourcing 200uA |

| High-state output<br>impedance    | 1kW from output to common                       |

| Turn on delay time                | T1 < 1s                                         |

| Voltage ramp up time              | 2ms < T2 < 200ms                                |

| PWR_OK delay time                 | 100ms < T3 < 2000ms                             |

| PWR_OK rise time                  | T4 < 10ms                                       |

| AC loss to PWR_OK<br>hold-up time | T5 > 16ms                                       |

| Power-down warning                | T6 > 1ms; T7 > 1ms                              |

|                                   |                                                 |

Figure 11. Traditional Implementation of 5VDUAL Voltage

## Absolute Maximum Rating

| Supply Input Voltage, 5VSB (Note 1)  | 0.3V to +6V    |

|--------------------------------------|----------------|

| 5VCC_DRV Voltage                     | ).3V to +13.2V |

| Other Pins                           | 0.3V to +6V    |

| Storage Temperature Range65          | 5°C to +150°C  |

| Junction Temperature                 | 150°C          |

| Lead Temperature (Soldering, 10 sec) | 260°C          |

| ESD Rating (Note 2)                  |                |

| HBM (Human Body Mode)                | 2kV            |

| MM (Machine Mode)                    | 200V           |

## **Thermal Information**

| Package Thermal Resistance (Note 3)    |             |

|----------------------------------------|-------------|

| SOT23-8L 0 <sub>.14</sub>              | <br>250°C/W |

| Power Dissipation, $P_{D}$ @ TA = 25°C |             |

| SOT23-8L                               | <br>0.4W    |

# Recommended Operation Conditions

| Operating Junction Temperature Range (Note 4) | <br>40°C to +125°C |

|-----------------------------------------------|--------------------|

| Operating Ambient Temperature Range           | <br>40°C to +85°C  |

| Supply Input Voltage, V <sub>5VSB</sub>       | +4.5V to +5.5V     |

| Supply input voltage, v <sub>5VSB</sub>       | 14.00 10.00        |

# Electrical Characteristics

$(V_{_{5VSB}} = 5V, T_{_A} = 25^{\circ}C, unless otherwise specified)$

| Parameter                              | Symbol                   | Test Conditions                                                       | Min | Тур | Max  | Unit |

|----------------------------------------|--------------------------|-----------------------------------------------------------------------|-----|-----|------|------|

| Supply Input                           |                          |                                                                       | 1   |     | I    |      |

| Nominal Supply Current                 | I <sub>5VSB</sub>        |                                                                       |     | 0.3 |      | mA   |

| Power On Reset                         |                          |                                                                       | •   |     |      |      |

| Rising 5VSB POR Threshold              | V <sub>5VSB_POR</sub>    |                                                                       | 3.8 | 4.2 | 4.5  | V    |

| 5VSB POR Hysteresis                    | V <sub>5VSB_HYS</sub>    |                                                                       |     | 0.2 |      | V    |

| Rising 5VCC_DRV POR<br>Threshold       | V <sub>5VCCDRV_POR</sub> | 1k $\Omega$ resistor between 5VCC_DRV and 12VCC Rail; 5VCC_DRV rising |     | 9.0 | 10.5 | V    |

| 5VCC_DRV POR Hysteresis                | V <sub>5VCCDRV_HYS</sub> | $1k\Omega$ resistor between 5VCC_DRV and 12VCC Rail; 5VCC_DRV falling |     | 1.0 |      | V    |

| Rising 5VCC POR Threshold              | V <sub>5VCC_POR</sub>    |                                                                       | 3.8 | 4.2 | 4.5  | V    |

| Falling 5VCC POR Threshold             | V <sub>5VCC_HYS</sub>    |                                                                       |     | 0.2 |      | V    |

| 5VCC POR Rising Delay Time             |                          | From 5VCC rising POR to 5VCC_DRV rising                               | 1   | 5   | 10   | ms   |

| Switch Controller                      |                          |                                                                       |     |     |      |      |

| 5VSB_DRV Source Current                | I_<br>5VSB_DRV           | 5VSB_DRV = 0V, 5VSB = 5V                                              | 20  |     | 35   | mA   |

| 5VSB_DRV Sink Current                  | I_<br>5VSB_DRV           | 5VSB_DRV = 5V, 5VSB = 5V                                              | 20  |     | 35   | mA   |

| 5VSB_DRV Soft Start Sinking<br>Current | <b> </b><br>5VSB_DRV     |                                                                       |     | 4.0 |      | uA   |

| 5VCC_DRV Sink Current                  | 5VCC_DRV                 | 5VCC_DRV = 5V, 5VSB = 5V                                              | 20  |     |      | mA   |

## Electrical Characteristics

| Parameter                                     | Symbol | Test Conditions | Min | Тур | Max | Units |

|-----------------------------------------------|--------|-----------------|-----|-----|-----|-------|

| Control I/O (S3#, S5#, and M                  | IODE)  |                 |     |     |     |       |

| High Level Input Threshold                    |        |                 |     | -   | 2.0 | V     |

| Low Level Input Threshold                     |        |                 | 0.8 |     | -   | V     |

| S3#, S5# Internal Pull Down<br>Current to GND |        |                 |     | 7   | -   | uA    |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. The device is not guaranteed to function outside its operating conditions.

#### uPI Semiconductor Corp., http://www.upi-semi.com Rev. F00, File Name: uP7501-DS-F0000

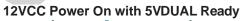

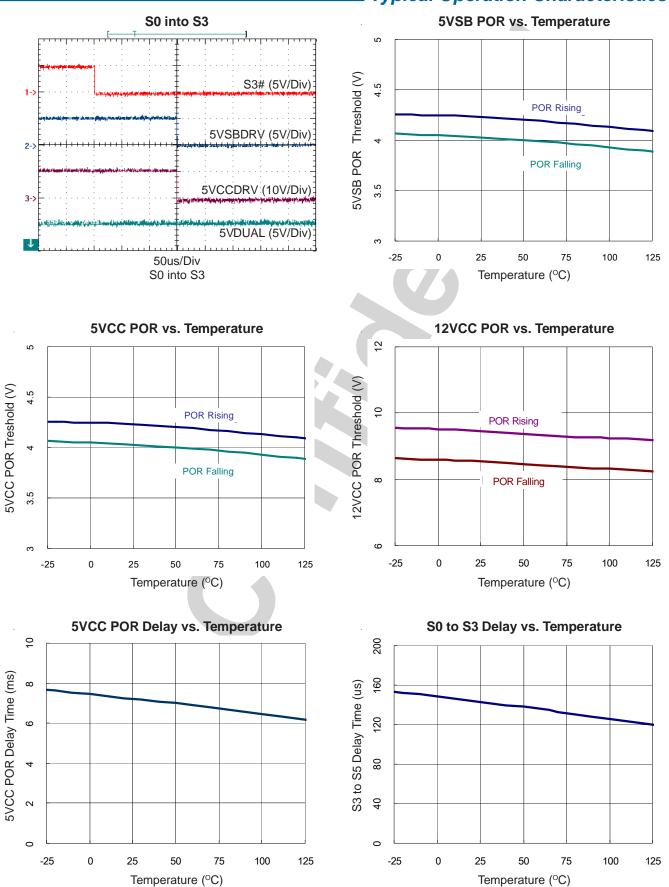

### **Typical Operation Characteristics**

uPI Semiconductor Corp., http://www.upi-semi.com Rev. F00, File Name: uP7501-DS-F0000

### **Component Selection Guidelines**

#### **Output Capacitors Selection**

The output capacitors should be selected to allow the output voltage to meet the dynamic regulation requirements of active state operation (S0/S1). The load transient for the various microprocessor system's components may require high quality capacitors to supply the high slew rate (di/dt) current demands. Thus, it is recommended that the output capacitors be selected for transient load regulation, paying attention to their parasitic components (ESR, ESL).

Switching on/off of the NMOS and PMOS are simultaneouly. Since it takes a finite time to turn off a MOSFET, there is a small overlapping time where both NMOS and PMOS are both on, ensuring seamless transition between 5VSB and 5VCC. No special concern is required for the voltage drop during the transition that should be taken care in traditional implementation.

#### Input Capacitors Selection

The input capacitors for an uP7501 application must have a sufficiently low ESR so that the input voltage will not dip excessively when energy is transferred to the output capacitors. If the ATX/BTX supply does not meet the specifications, certain imbalances between the ATX/BTX outputs and the uP7501 regulation levels could have as a result a brisk transfer of energy from the input capacitors to the supplied outputs. At the transition between active and sleep states, such phenomena could be responsible for the 5VSB voltage drooping excessively and affecting the output regulation. The solution to such a potential problem is using larger input capacitors with a lower total combined ESR.

### Transistor Selection/Considerations

The uP7501 usually requires one P-Channel and one N-Channel MOSFETs as shown in the Typical Application Circuit. Both of these MOSFETs are utilized as ON/OFF switching elements. One important criteria for selection of transistors for all the switching elements is package selection for efficient removal of heat. The power dissipated in a switch element while on is:

$$P_D = I_{OUT}^2 \times R_{DS(ON)}$$

Select a package and heatsink that maintains the junction temperature below the rating with the maximum expected ambient temperature.

### Q1

This is a P-Channel MOSFET used to switch the 5VSB output of the ATX/BTX supply into the 5VDUAL output

### Application Information

during sleep states. The selection criteria of this device, as with the N-Channel MOSFETs, is proper voltage budgeting. The maximum  $R_{DS(ON)}$ , however, has to be achieved with only 4.5V of gate-to-source voltage, so a true logic level MOSFET needs to be selected.

### Q2

This N-Channel MOSFET is used to switch the 5VCC voltage provided by the ATX/BTX supply into the 5VDUAL output while in active (S0, S1) state. The main criteria for the selection of these transistors is output voltage budgeting. The maximum  $R_{DS(ON)}$  allowed at highest junction temperature can be expressed with the following equation:

$$R_{DS(ON)\_MAX} = (T_{J\_MAX} - T_A)/\theta_{JA}/I_{OUT}^2$$

, where T<sub>J\_MAX</sub> = maximum allowable junction temperature,  $\theta_{JA}$  = junction to ambient thermal resistance of the NMOS. Consider the R<sub>DS(ON)</sub> with gate voltage V<sub>GS</sub> = 5V.

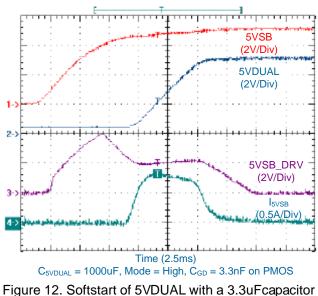

#### Softstart Time Control

During G3 to S5 transition with MODE = High, the current sinking capability of 5VSB\_DRV is limited to 4uA for softstart. A capacitor connecting gate and drain of the PMOSFET is useful to control the ramp up speed of the 5VDUAL, thus limiting the inrush current from 5VSB. Figure 12 illustrates the related waveforms. Initially, the 4uA current discharges input capacitor  $C_{ISS}$  of the PMOSFET and attached capacitor making the gate voltage ramp down linearly. The PMOSFET starts to conducts current and 5VDUAL starts to ramp up after the V<sub>GS</sub> reaches the threshold. During the ramp up of 5VDUAL, the V<sub>GS</sub> keeps flat due to the Miller Effect even though dura current keeps discharging the attached capacitor

The ramp up time of 5VDUAL can be estimated as:

$$T_{RAMP\_UP} = \frac{5V \times (C_{EXT} + C_{GD})}{4uA}$$

### **Layout Considerations**

The typical application employing an uP7501 is a fairly straight forward implementation as shown in Figure 13. Attention should be paid to sensitive logic inputs (S3# and S5#) and those supplying critical bypass current.

### Figure 13. Typical Implementation of 5VDUAL

The input bias supply (5VSB) carries a similar level of current for best results, ensure it is connected to its respective source through an adequately sized trace and is properly decoupled. The pass transistors should be placed on pads capable of heatsinking matching the device's power dissipation. Where applicable, multiple via connections to a large internal plane can significantly lower localized device temperature rise.

Placement of the decoupling and bulk capacitors should reflect their purpose. As such, the high-frequency decoupling capacitors should be placed as close as possible to the load they are decoupling; the ones decoupling the controller close to the controller pins, the ones decoupling the load close to the load connector or the load itself (if embedded). Even though bulk capacitance (aluminum electrolytics or tantalum capacitors) placement is not as critical as the high-frequency capacitor placement, having these capacitors close to the load they serve is preferable.

Locate all small signal components close to the respective pins of the control IC, and connect them to ground, if applicable, through a via placed close to the ground pad. A multilayer printed circuit board is recommended.

### **Application Information**

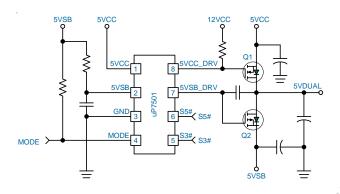

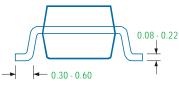

## **Package Information**

0.00 - 0.15

◀ 1.95 BSC −

### Note

- 1. Package Outline Unit Description:

- BSC: Basic. Represents theoretical exact dimension or dimension target

- MIN: Minimum dimension specified.

- MAX: Maximum dimension specified.

- REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shell not exceed 0.15mm.