NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

Rev. 3.4 — 24 June 2016

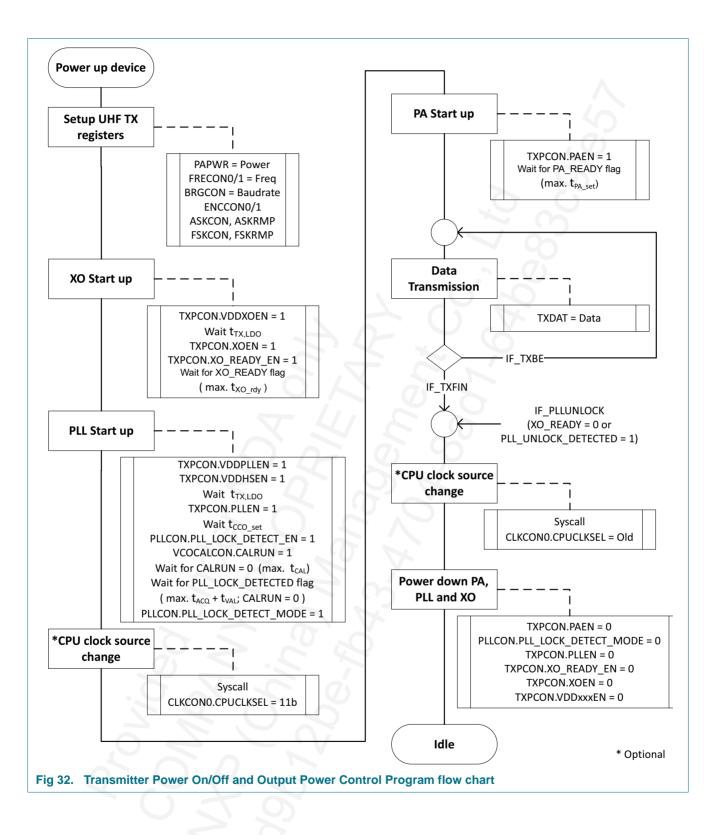

NC

Product data sheet CONFIDENTIAL

#### **Document information**

| Info     | Content                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | Car key, Vehicle Immobilization (IMMO), Passive Keyless Entry (PKE),<br>Remote Keyless Entry (RKE), RF transceiver, ISM band, FSK, ASK,<br>MRK III            |

| Abstract | The NCF29A1 / NCF29A2 is a fully integrated single-chip solution<br>combining RKE, PKE and IMMO functionality designed for use in<br>automotive environments. |

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

## **1. General information**

### 1.1 General description

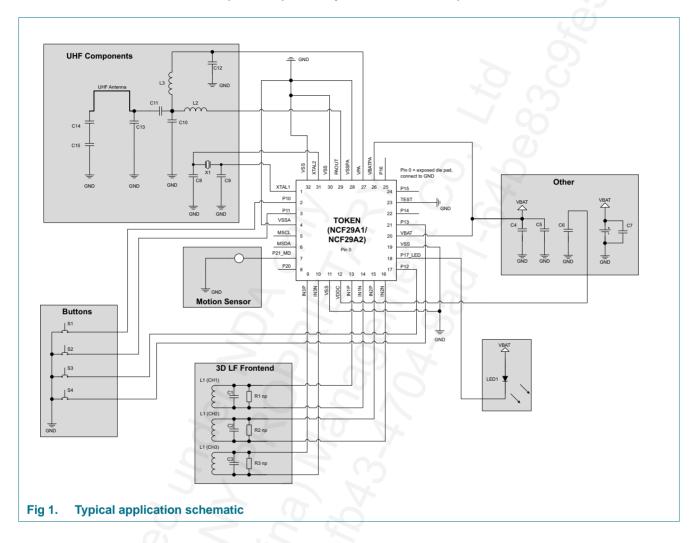

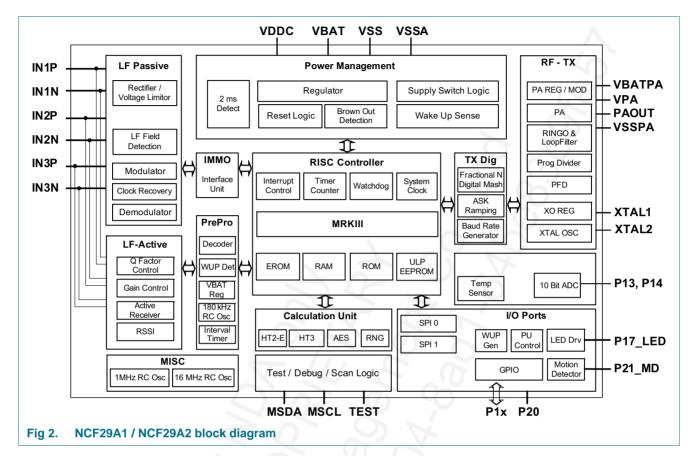

The NCF29A1 / NCF29A2 is an extremely compact single chip solution, ideally suited for automotive applications with combined vehicle immobilization and keyless entry / start functions. The device incorporates a Security Transponder, UHF Transmitter and RISC Controller on the same chip and requires only a few external components.

The RISC Controller is powered by NXP's low power hardware extended (MUL/DIV) 16-Bit MICRO RISC KERNEL (MRK IIIe) employing a 2- stage pipeline architecture in order to improve performance. The device features 10 I/O ports allowing for up to 10 command button inputs. For transponder, keyless entry and go operations, the on-chip hardware Calculation Unit or any user-defined software based algorithm can be employed for data communication.

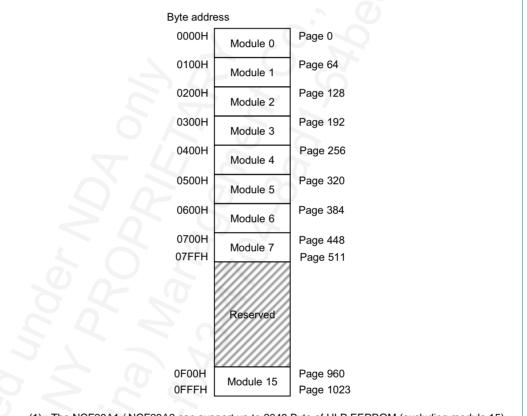

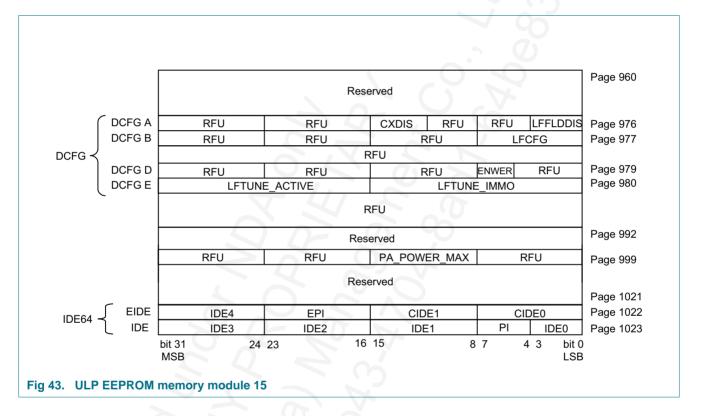

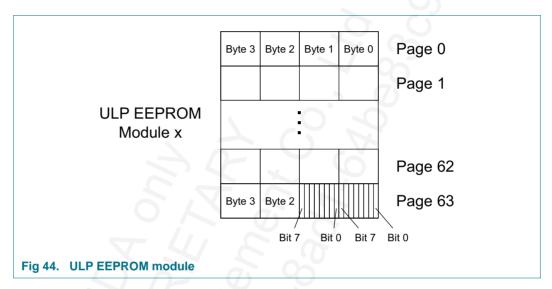

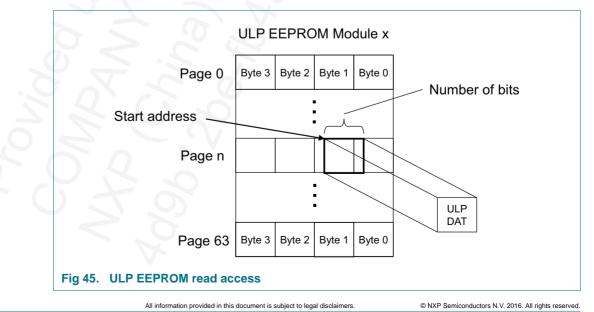

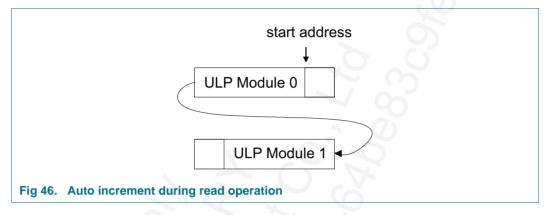

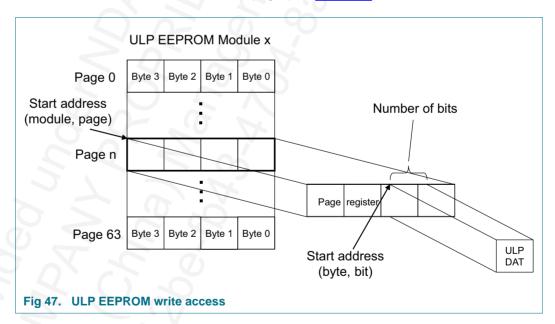

The device provides up to 2048 Byte of EEPROM for data storage with access control as defined by the application. In addition, the device supports a sophisticated EEPROM access scheme when operating as Security Transponder during immobilizer operation.

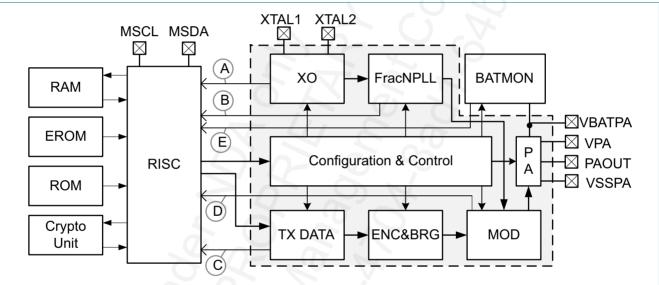

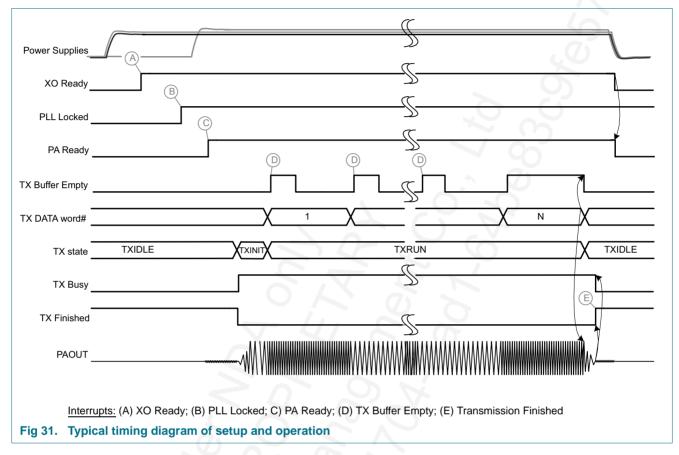

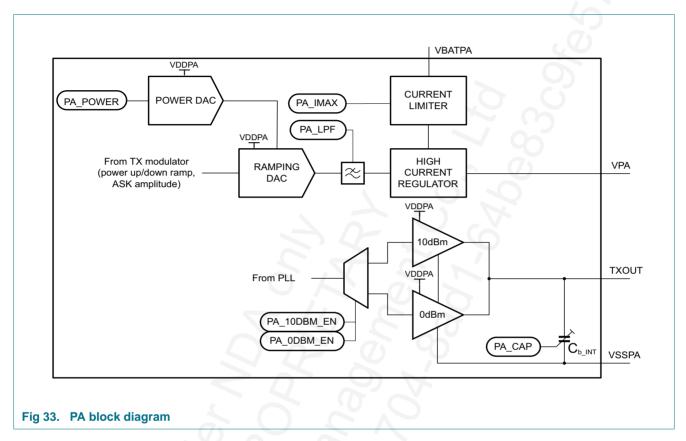

The on-chip multi-channel UHF Transmitter requires no external components to operate except for the reference crystal and the loop antenna matching circuitry. The device is specified to operate in the frequency bands 310-447MHz. The frequency bands 868 MHz and 915 MHz can be supported on request. The device features a uniform reference frequency (27.6 MHz) for all bands. The UHF Transmitter is directly controlled by the RISC Controller and supports FSK, ASK, OOK modulation of the carrier with data rates up to 25 kbit/s (Manchester). The programmable power amplifier regulates the antenna pin voltage in order to minimize carrier variations over temperature and battery voltage variations.

The device provides a motion detection function that detects state changes on the motion sensor pin and may wake-up the CPU core if needed. The device can be configured to automatically disable the LF Active receiver block for saving power when key-fob still (no motion) is detected, and also, to automatically enable the LF Active receiver when key-fob in motion is detected.

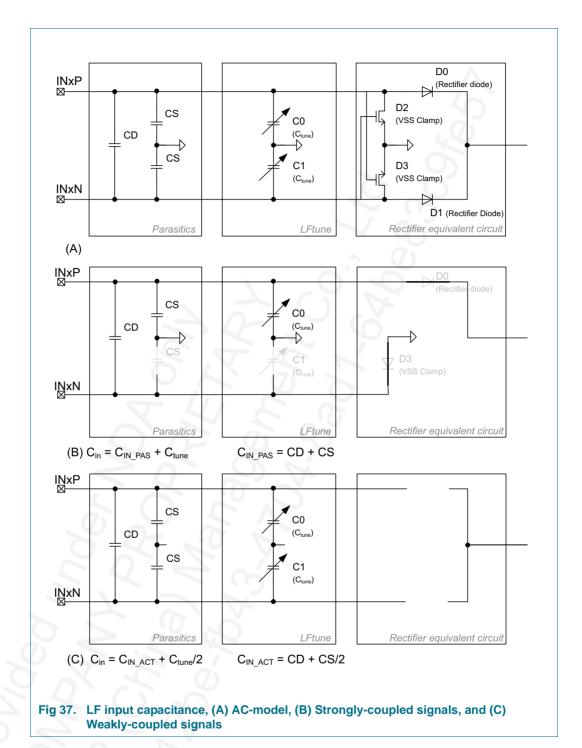

The device provides means for capacitive tuning for maintaining an optimal resonance frequency and optimize reception of an incoming LF signal in order to save cost in the bill of material.

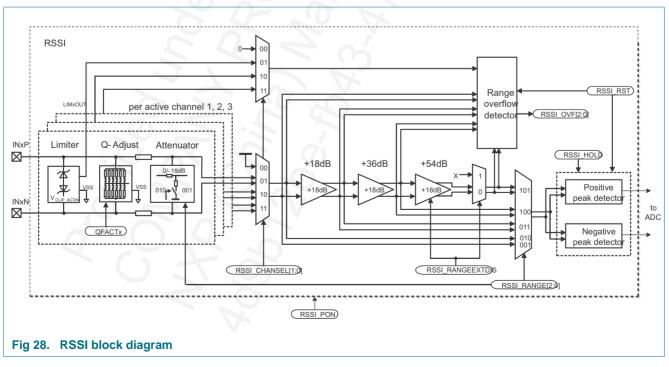

Unused RSSI channels can be attenuated in order to acquire precise single channel RSSI measurements.

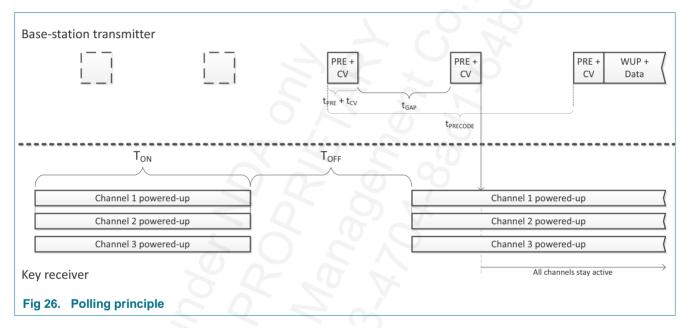

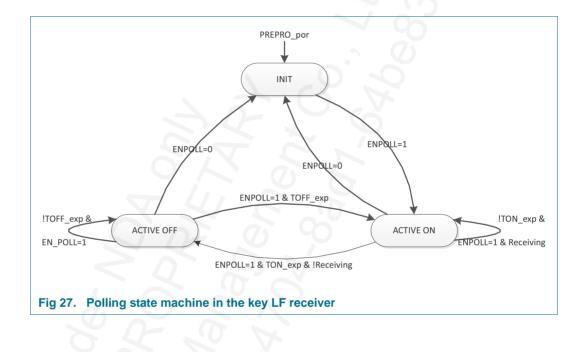

LF Active channel polling enables battery supply current reductions depending on the protocol length and this extend the battery lifetime significantly.

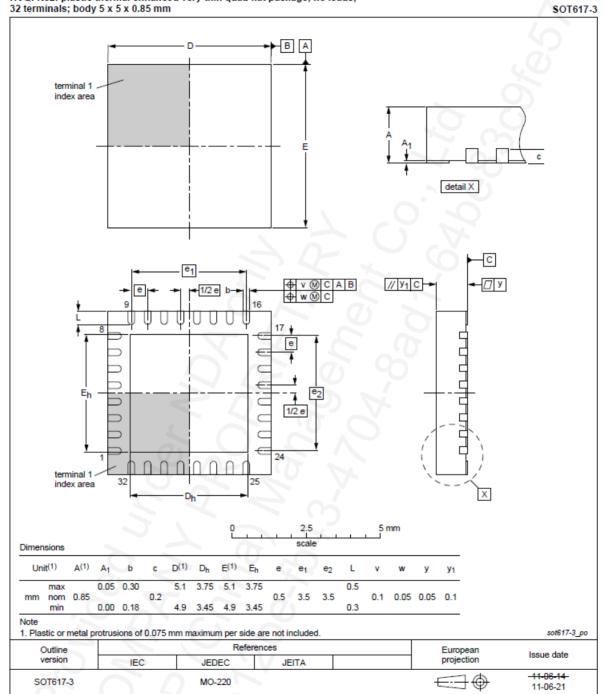

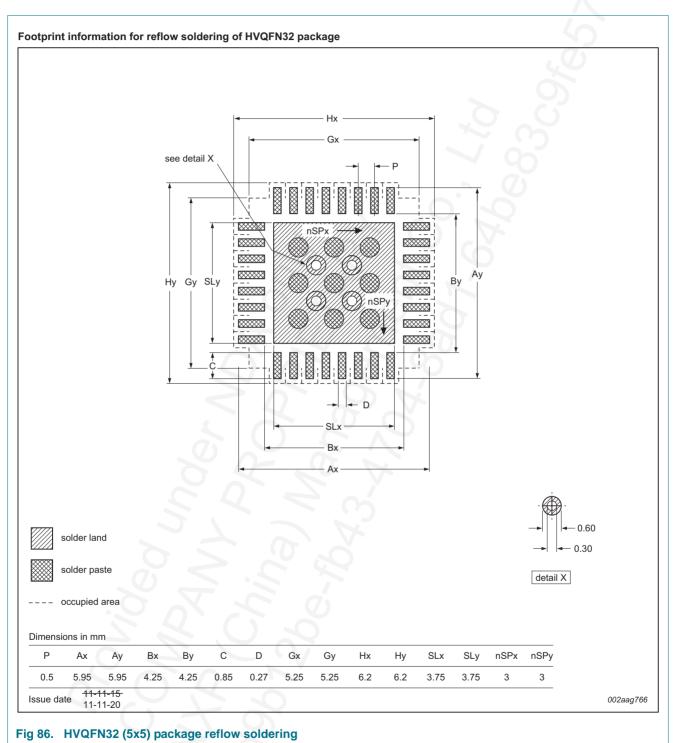

The device comes in a tiny 32 pin HVQFN Package demanding minimal board space (5 mm x 5 mm).

NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

### 1.2 Features and benefits

#### 1.2.1 General

- Single chip security transponder and keyless entry solution

- On-chip UHF transmitter (310 MHz to 447 MHz)

- 868 MHz and 915 MHz on-chip UHF transmitter available on request

- Up to 10 command buttons with wake-up function

- Current source option for direct LED drive

- RISC programmable device operation

- 32 bit quasi unique device and product type identification

- Single Lithium cell operation, 2.0 V to 3.6 V

- C-Compiler supported software development

- 32-pin compact HVQFN package (5 mm x 5 mm)

- On-chip temperature sensor

- Motion sensor interface

#### 1.2.2 Security Transponder

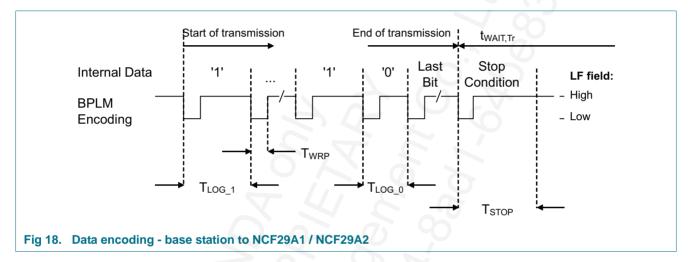

- Operating frequency 125 kHz

- 3D LF transponder operation (NCF29A1 only)

- LF capacitive antenna tuning

- Customer programmable transponder operation

- Fast mutual authentication

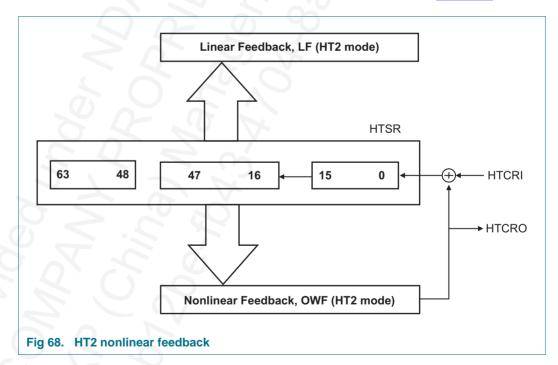

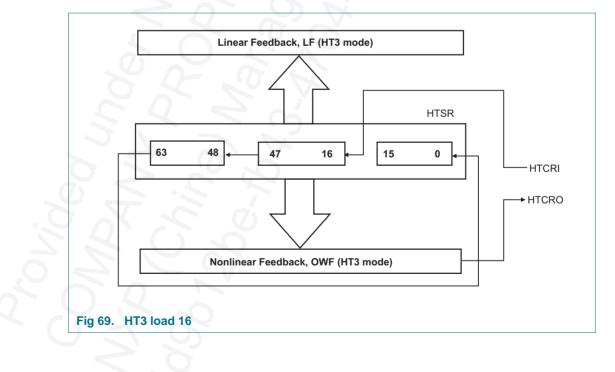

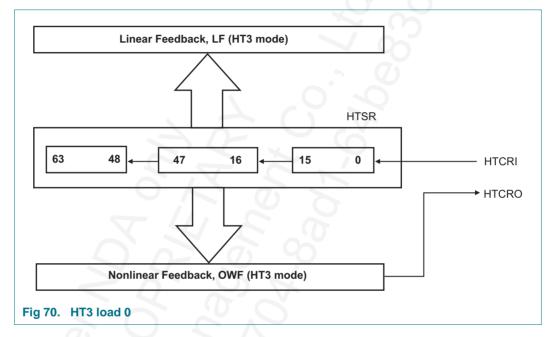

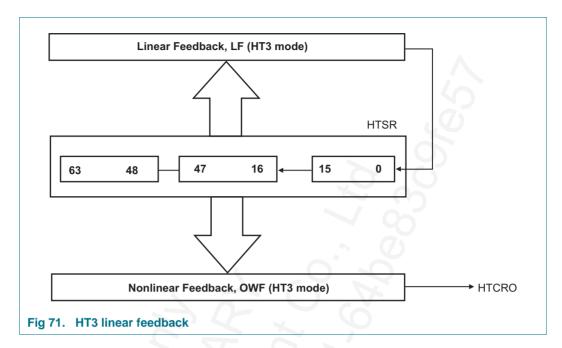

- Built-in HT2-E, HT3, HT-AES or HT-Pro2 based transponder emulations

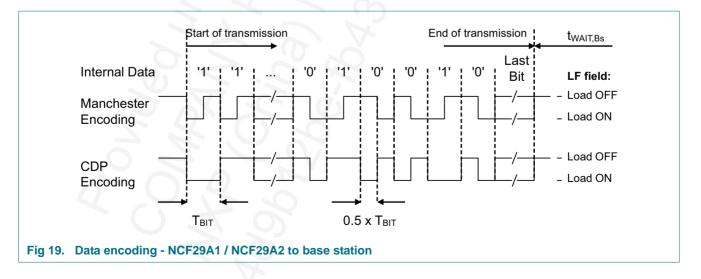

- Data rate (tag to base station) 4 kbit/s

- 2 ms detection unit

- EEPROM read/write protection capability

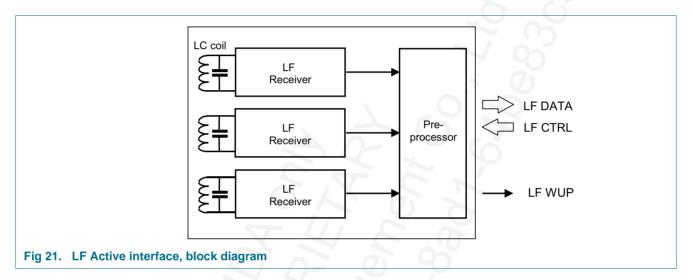

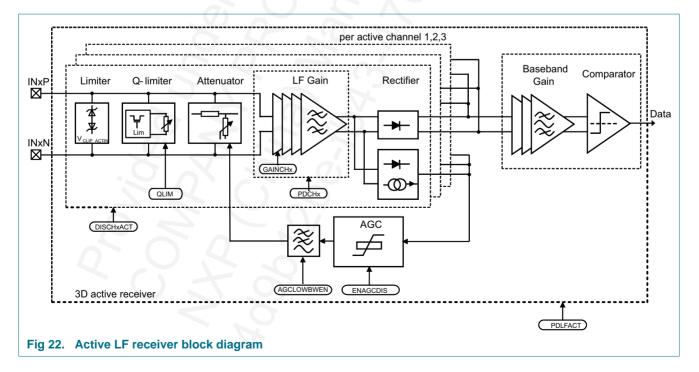

#### 1.2.3 3D LF active interface

- Operating frequency 125 kHz

- Boost mode for long range receive applications

- LF active capacitive antenna tuning

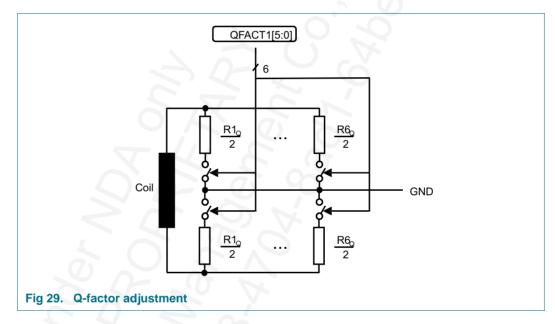

- Adjustable Q-factor with resistive LF active channel tuning

- Low power LF wake-up and data processing

- Single-bit fault tolerant wake-up option

- Polling option

- Options for LF Active receiver control (ON and OFF) coupled to key-fob motion (STILL or MOVING)

- Three axis (3D) LF signal strength measurement and indication (RSSI)

- High receiver sensitivity

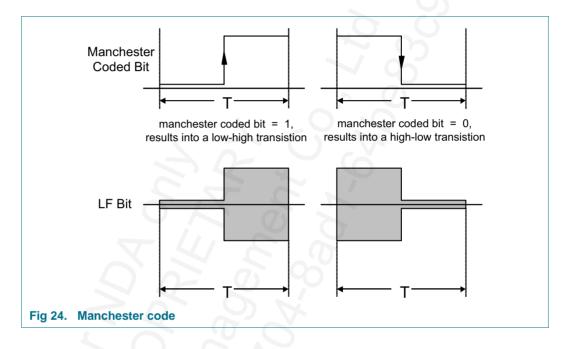

- 2 kbit/s PKE data rate (high-Q mode), 4 and 8 kbit/s Manchester

- Fast A/D conversion for RSSI measurement

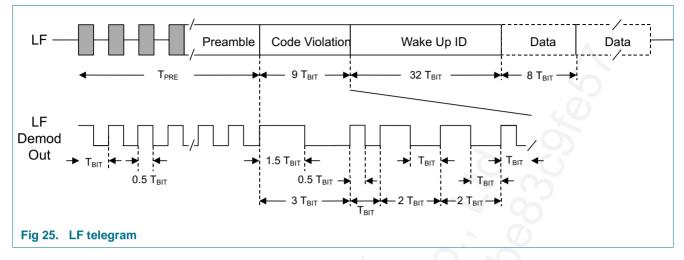

- LF active telegram organization like PCF795x, NCF295x and NCF297x

### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

### 1.2.4 UHF Transmitter

- Multi Channel Fractional-N PLL

- One reference frequency (XTAL) for all bands

- Programmable RF-output power, stabilized over temperature and voltage level

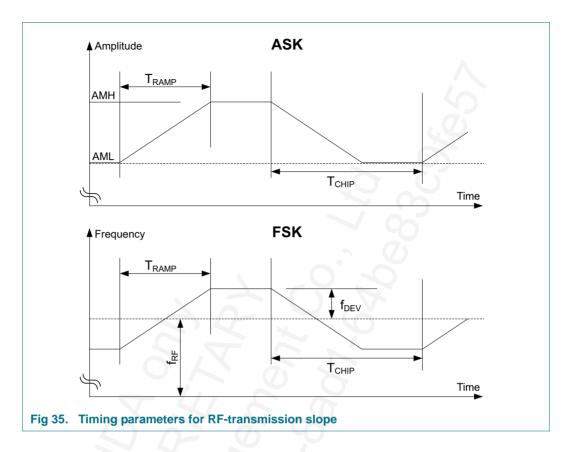

- Programmable ASK/FSK modulation characteristics

- OOK ASK option with higher than 30dB dynamic range

- Low power consumption:

- 12.5 mA @10 dBm (434 MHz)

- ◆ 7 mA @ 0 dBm (434 MHz)

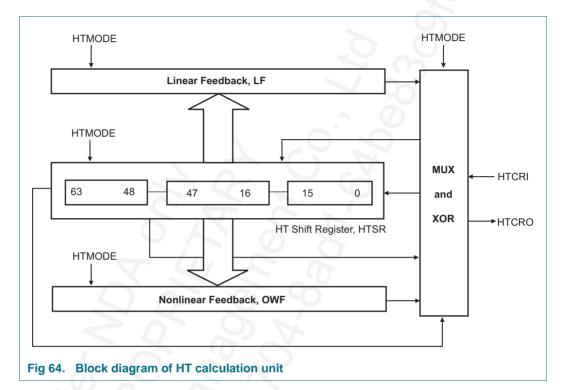

### 1.2.5 Calculation Unit

- Multimode hardware security algorithm

- HT2-E with 48 bit Secret Key

- HT3 with 96 bit Secret Key

- AES128 with 128 bit Secret Key

- CRC hardware co-processor unit

- True hardware and Pseudo Random Number Generator (16 bit)

### 1.2.6 **RISC Controller**

- 16 Bit Harvard Architecture (RISC)

- Hardware supported MUL/DIV instructions

- Two CPU clock cycles per instruction (2-stage instruction pipeline)

- System ROM for NXP firmware

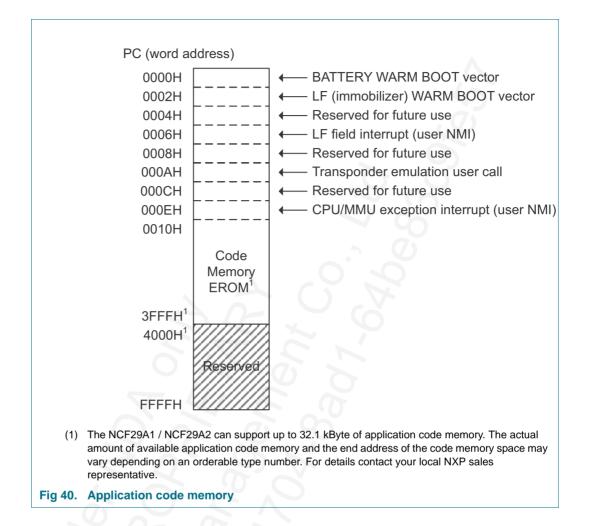

- Up to 32 kByte user EROM for application (code and data space)

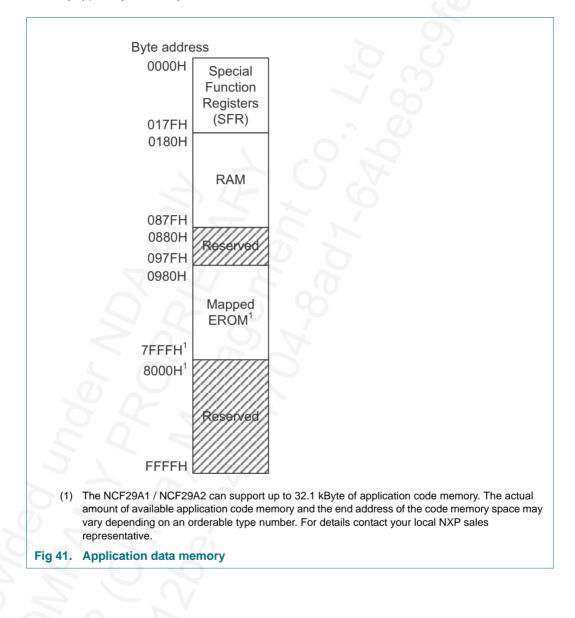

- Up to 2048 Byte Ultra Low Power (ULP) Serial EEPROM for extended user data

- 2 kByte RAM (1792 bytes USER RAM and 256 bytes used for SYSTEM RAM)

- Single level interrupt architecture

- On-chip low tolerance RC Oscillator (< +/- 10%)</p>

- Short instruction execution time (0.125 µs @ 16 MHz CPU clock)

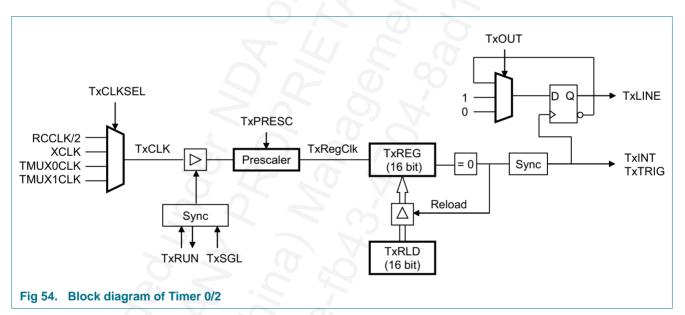

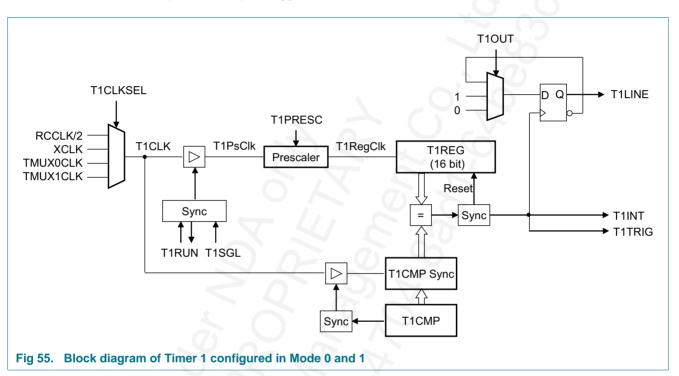

- Three 16-Bit Timer/Counter

- Watchdog

- Low operational power consumption

#### 1.2.7 Peripherals

- Up to 10 general purpose I/Os

- Up to 10 wake-up / button inputs

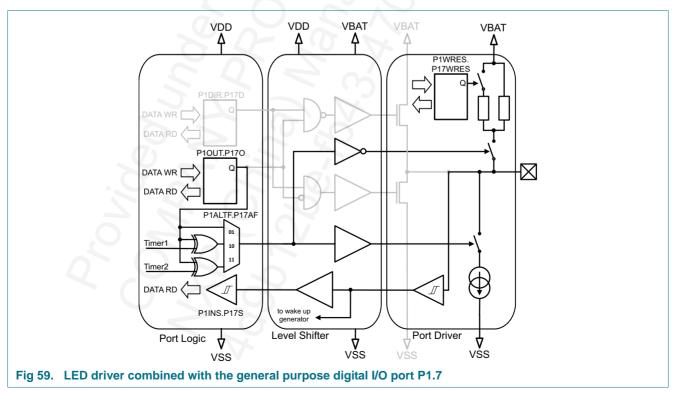

- One I/O with LED drive capability

- Software configurable pull-up or pull-down resistor

- Software configurable pull-up strength: strong (27 k $\Omega$ ) or weak pull up (115 k $\Omega$ )

- Software configurable wake-up either on high to low or low to high transition

- Optional clock/event input for Timer/Counter

- General purpose ADC supporting various analogue sources (incl. external source)

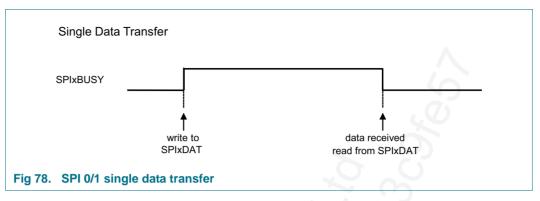

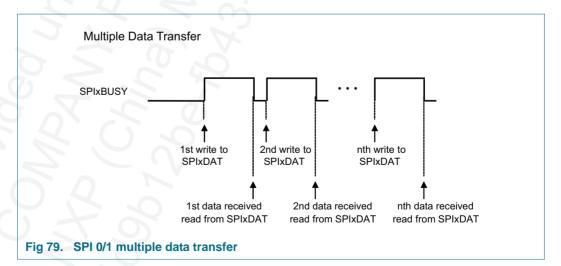

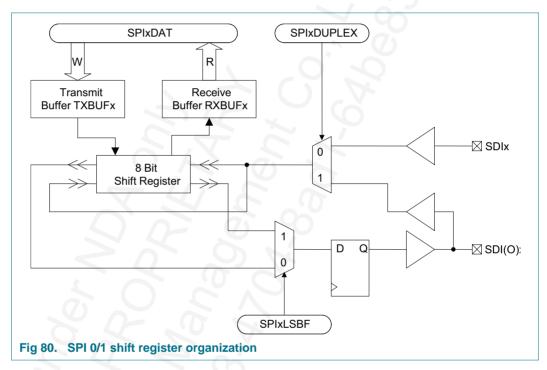

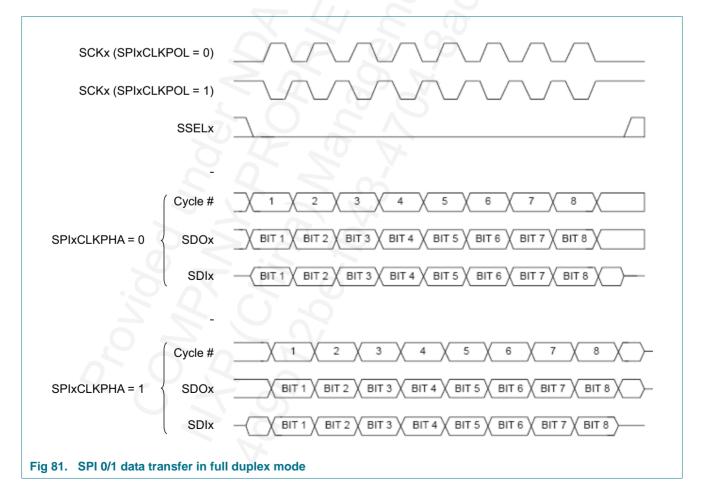

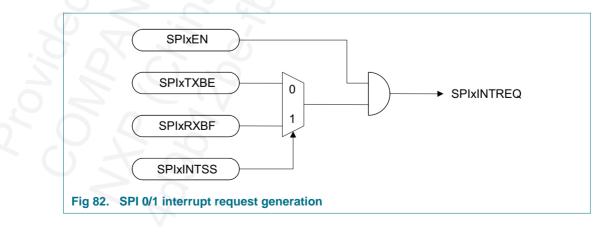

- Two synchronous serial peripheral interfaces SPI 0 and SPI 1 with a baud rate selectable between 125 kHz and 4 MHz

- Battery Voltage Sensor with programmable battery low threshold

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

### **1.3 Applications**

The NCF29A1 / NCF29A2 is a compact single chip solution, ideally suited for automotive applications with combined vehicle immobilization and keyless entry / start functions. The device incorporates a Security Transponder, a UHF Transmitter and a RISC Controller on the same chip and requires only a few external components.

### 1.3.1 Application areas

- Remote Keyless Entry (RKE)

- Passive Keyless Entry (PKE) and/or Passive Keyless Go (PKG)

- Immobilization

### 1.4 Quick reference data

#### Table 1. Quick reference data

| Symbol                     | Parameter                     | Conditions                 | Min       | Тур | Max | Unit   |

|----------------------------|-------------------------------|----------------------------|-----------|-----|-----|--------|

| V <sub>BAT</sub>           | Battery supply voltage        |                            | 1.8       | 3.0 | 3.6 | V      |

| T <sub>amb</sub>           | Operating temperature         |                            | -40       |     | +85 | °C     |

| ULP-serial                 | EEPROM                        |                            |           |     |     |        |

| t <sub>ULPRET</sub>        | Data retention time           | $T_{amb} = 50 \ ^{\circ}C$ | 20        |     |     | years  |

| N <sub>ULPWR-CY</sub><br>L | Write endurance ULP<br>EEPROM | T <sub>amb</sub> = 25 °C   | [1] 100 k |     |     | cycles |

[1] The activation energy equals 0.15 eV. According to Arhennius' Law, the number of useful cycles at room temperature is about 2.5 times higher than at 85 °C.

### 1.5 NCF29A1 / NCF29A2 type naming conventions

The following table explains the naming conventions for the commercial product name of the NCF29A1 / NCF29A2 products. Every NCF29A1 / NCF29A2 product gets assigned a commercial type name, which includes also customer and application specific data.

The NCF29A1 / NCF29A2 commercial type names have the following format.

#### NCF29xxtHN/vrffmn

'NCF29' and 'HN' are constants, all other letters are variables, which are explained in the following Table 2.

| Variable | Meaning                                      | Values     | Description                                                                                                                                |

|----------|----------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| хх       | Product Basic Type<br>Name                   | A2         | NCF29A2                                                                                                                                    |

|          |                                              | A1         | NCF29A1                                                                                                                                    |

| t C      | supported transponder                        | E          | HT2-E based transponder emulation                                                                                                          |

|          | emulation                                    | Х          | HT3 based transponder emulation                                                                                                            |

|          |                                              | М          | HT-AES based transponder emulation                                                                                                         |

|          |                                              | V          | HT-Pro2 based transponder emulation                                                                                                        |

| v        | Product Version Code                         |            |                                                                                                                                            |

| r        | ROM Code ID                                  |            |                                                                                                                                            |

| ff       | FabKey ID                                    |            |                                                                                                                                            |

| m        | code for available amount of EROM and EEPROM | <u>[1]</u> | The available amount of EROM and<br>EEPROM is adoptable on request. Up to<br>32 kByte user EROM and up to 2048 Byt<br>EEPROM is supported. |

| n        | code for available feature set               | <u>[1]</u> | Some product features are optional and<br>only available on request:<br>Support for frequency bands 868 MHz an<br>915 MHz                  |

[1] For details regarding the coding of the available amount of EROM and EEPROM and the available features please contact the local NXP sales representative.

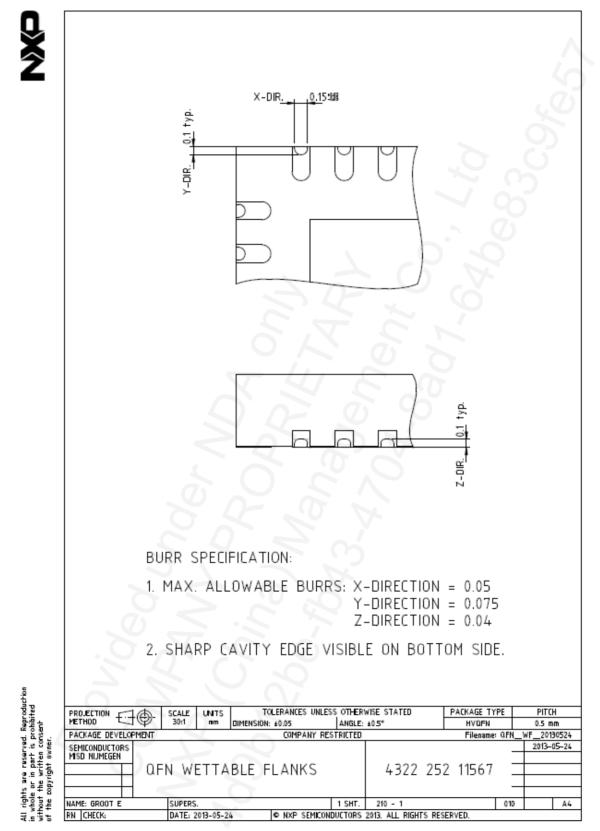

## **1.6 Ordering information**

| Type number               | Package | Package                                                             |          |  |  |  |  |  |

|---------------------------|---------|---------------------------------------------------------------------|----------|--|--|--|--|--|

|                           | Name    | Description                                                         | Version  |  |  |  |  |  |

| NCF29A1EHN <sup>[1]</sup> | HVQFN32 | Plastic thermal enhanced very thin quad flat package; 32 terminals; | SOT617-3 |  |  |  |  |  |

| NCF29A1XHN <sup>[2]</sup> |         | body 5 x 5 x 0.85 mm; terminal pitch 0.5 mm; wettable flanks        |          |  |  |  |  |  |

| NCF29A1MHN[3]             |         |                                                                     |          |  |  |  |  |  |

| NCF29A1VHN <sup>[4]</sup> |         |                                                                     |          |  |  |  |  |  |

| NCF29A2EHN <sup>[1]</sup> | HVQFN32 | Plastic thermal enhanced very thin quad flat package; 32 terminals; | SOT617-3 |  |  |  |  |  |

| NCF29A2XHN <sup>[2]</sup> |         | body 5 x 5 x 0.85 mm; terminal pitch 0.5 mm; wettable flanks        |          |  |  |  |  |  |

| NCF29A2MHN[3]             |         |                                                                     |          |  |  |  |  |  |

| NCF29A2VHN <sup>[4]</sup> |         |                                                                     |          |  |  |  |  |  |

|                           |         | version contains a HT2-Extended based transponder emulation         |          |  |  |  |  |  |

|                           | [2] XHN | version contains a HT3 based transponder emulation                  |          |  |  |  |  |  |

|                           | [3] MHN | I version contains a HT-AES based transponder emulation             |          |  |  |  |  |  |

[4] VHN version contains a HT-Pro2 based transponder emulation

### 1.7 Marking

#### Table 4. NCF29A1 / NCF29A2 marking codes

| Type number               | Marking code                                                                                      |

|---------------------------|---------------------------------------------------------------------------------------------------|

| NCF29A1xHN <sup>[1]</sup> | Line A: A1xnn <sup>[1][2]</sup><br>Line B: db_as <sup>[3]</sup><br>Line C: ZSywwrs <sup>[4]</sup> |

| NCF29A2xHN <sup>[1]</sup> | Line A: A2xnn <sup>[1][2]</sup><br>Line B: db_as <sup>[3]</sup><br>Line C: ZSywwrs <sup>[4]</sup> |

[1] "x" is a code in the product type name indicating the supported transponder emulation:

M: HT-AES based transponder emulation

V: HT-Pro2 based transponder emulation

- [2] "nn" is a two digit code referring to a specific rom code version, to a specific fabkey data image and the supported feature set. For details contact your local NXP sales representative.

- [3] 'db\_as' is a five digit batch code: first two digits for DBSN followed by '\_' and last two digits for ASID The Assembly Sequence ID (ASID) is a 2-digit indicator that counts the number of assembly batches (transport lots) within one diffusion batch id and one weekly date code. The week start and end dates are defined by the assembly center algorithm. The ASID is assigned sequentially starting with 01 and ranging through 99, then each digit ranges upper case alphabet letters in combination with numeric, then numeric in combination with upper case alphabet letters, then upper case alphabet letters in combination with upper case alphabet letters providing 1175 possible values within a week-code. The numeric zero '0' is only allowed within the sequence of 01 to 99. The alphabet letter 'O' is not allowed to avoid confusion with numeric '0'.

The Diffusion Batch Sequence Number (DBSN) is a 2-digit indicator that counts the number of diffusion batches (DBID) within one Package Type (i.e. HVQFN32) and one weekly date code. The DBSN is assigned sequentially starting with 01 and ranging through 99, then each digit ranges upper case alphabet letters in combination with numeric, then numeric in combination with upper case alphabet letters, then upper case alphabet letters in combination with upper case alphabet letters providing 1175 possible values within a week-code. The numeric zero '0' is only allowed within the sequence of 01 to 99. The alphabet letter '0' is not allowed to avoid confusion with numeric '0'.

[4] yww is a three digit Date code: "YWW", \*\* refers to a two digit arbitrary character

"Y" is a code indicating the year in which the IC is assembled. Examples: for year 1999 is Y = 9, for year 2000 is Y = 0, for year 2001 is Y = 1. "WW" is a code indicating the week in which the IC is assembled. It is determined from the date the assembly transport lot is created or alternately the date die is issued from die stores to assembly start or the date die attach (Diebond) occurs or the date encapsulation occurs. Examples: for week 01 is WW = 01, for week 52 is WW = 52, for week 53 is WW = 53.

"r" is the product version code referring to the fab indicator, mask versions and package versions.

"s" is the memory size code referring to the available amount of EROM and EEPROM. For details contact your local NXP sales representative.

E: HT2-E based transponder emulation, legacy support, not recommended for future design in X: HT3 based transponder emulation

NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

### 1.8 Block diagram

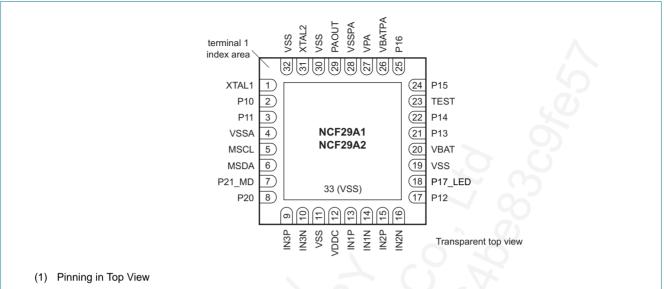

### **1.9 Pinning information**

#### 1.9.1 Pinning

The pin configuration of the NCF29A1 / NCF29A2 in HVQFN32 package is shown in Figure 3.

### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### Fig 3. Pin configuration HVQFN32 (SOT617-3)

### 1.9.2 Pin description

| Table 5. | Pin description |                                                                                                       |

|----------|-----------------|-------------------------------------------------------------------------------------------------------|

| Symbol   | Pin             | Description                                                                                           |

| XTAL1    | 1               | crystal oscillator interface                                                                          |

| P10      | 2               | general purpose digital IO                                                                            |

| P11      | 3               | general purpose digital IO                                                                            |

| VSSA     | 4               | common ground                                                                                         |

| MSCL     | 5               | debug interface. MSCL is an output and shall be unconnected in the application.                       |

| MSDA     | 6               | debug interface. MSDA features an on-chip pull-up to VBAT and may be left open or terminated to VBAT. |

| P21_MD   | 7               | general purpose digital IO, Motion Sensor Interface                                                   |

| P20      | 8               | general purpose digital IO                                                                            |

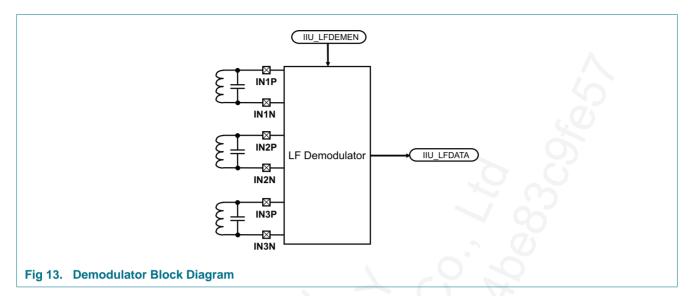

| IN3P     | 9               | LF input, transponder and active interface (LF antenna)[2]                                            |

| IN3N     | 10              | LF input, transponder and active interface (LF antenna)[2]                                            |

| VSS      | 11              | common ground                                                                                         |

| VDDC     | 12              | device LF field supply voltage                                                                        |

| IN1P     | 13              | LF input, transponder and active interface (LF antenna)[2]                                            |

| IN1N     | 14              | LF input, transponder and active interface (LF antenna)[2]                                            |

| IN2P     | 15              | LF input, transponder and active interface (LF antenna)[2]                                            |

| IN2N     | 16              | LF input, transponder and active interface (LF antenna)[2]                                            |

| P12      | 17              | general purpose digital IO                                                                            |

| P17_LED  | 18              | general purpose digital IO, LED driver pin                                                            |

| VSS      | 19              | common ground                                                                                         |

| VBAT     | 20              | battery supply                                                                                        |

| P13      | 21              | general purpose digital IO                                                                            |

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

## NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

| Table 5.            | Pin description |                                         |

|---------------------|-----------------|-----------------------------------------|

| Symbol              | Pin             | Description                             |

| P14                 | 22              | general purpose digital IO              |

| TEST <sup>[1]</sup> | 23              | test terminal - not used in application |

| P15                 | 24              | general purpose digital IO              |

| P16                 | 25              | general purpose digital IO              |

| VBATPA              | 26              | battery supply                          |

| VPA                 | 27              | choke supply                            |

| VSSPA               | 28              | ground power amplifier                  |

| PAOUT               | 29              | power amplifier output                  |

| VSS                 | 30              | common ground                           |

| XTAL2               | 31              | crystal oscillator interface            |

| VSS                 | 32              | common ground                           |

| EP <mark>[1]</mark> | 33              | exposed die pad                         |

| -                   |                 |                                         |

[1] Terminal must be connected to VSS

[2] NCF29A2 (1D) supports only one LF antenna input for the transponder on IN1P and IN1N

### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

## 2. Design information

### 2.1 Special function register set

<u>Table 6</u> summarizes the device Special Function Register (SFR) set. It comprises registers containing configuration bits, status bits, control bits and data bits that serve to operate the device. The detailed bit descriptions are given in the corresponding sections.

| Table 6.         Device register   |                                 |         |                                                       | $\mathbf{O}$     |  |

|------------------------------------|---------------------------------|---------|-------------------------------------------------------|------------------|--|

| Peripheral                         | Register<br>name <sup>[1]</sup> | Address | Description                                           | Supply<br>domain |  |

| CPU/MMU Exceptions 6               | CXPC                            | 0014h   | CPU Exception PC value                                | VDD              |  |

|                                    | CXSW                            | 0016h   | CPU Exception code                                    |                  |  |

| Port 1/2 [4]                       | P1INS                           | 0019h   | Port 1 input sense register                           | VDD              |  |

|                                    | P1OUT                           | 001Ah   | Port 1 output control register                        |                  |  |

|                                    | P1DIR                           | 001Bh   | Port 1 direction control register                     |                  |  |

|                                    | P2INS <sup>[5]</sup>            | 001Ch   | Port 2 input sense register                           |                  |  |

|                                    | P2OUT <sup>[5]</sup>            | 001Dh   | Port 2 output control register                        |                  |  |

|                                    | P2DIR <sup>[5]</sup>            | 001Eh   | Port 2 direction control register                     |                  |  |

|                                    | P1INTDIS                        | 001Fh   | Port 1 Interrupt Disable                              |                  |  |

|                                    | P2INTDIS <sup>[5]</sup>         | 0020h   | Port 2 Interrupt Disable                              |                  |  |

|                                    | P1ALTF <sup>[5]</sup>           | 00ECh   | Port 1 alternative digital functions register         |                  |  |

|                                    | P2ALTF <sup>5</sup>             | 00EEh   | Port 2 alternative digital functions register         |                  |  |

|                                    | P1WRES <sup>[2]</sup>           | 00C8h   | Port 1 Pull-up Resistor Configuration                 | VBAT             |  |

|                                    | P2WRES <sup>[3]</sup>           | 00C9h   | Port 2 Pull-up Resistor Configuration                 |                  |  |

|                                    | PRESWUP0                        | 00C2h   | Port 1 Wake-up Configuration P12-P15                  |                  |  |

|                                    | PRESWUP1                        | 00C4h   | Port 1 Wake-up Configuration P16-P21                  |                  |  |

|                                    | PRESWUP2 <sup>[5]</sup>         | 00C6h   | Port 2 Wake-up Configuration, reserved for future use |                  |  |

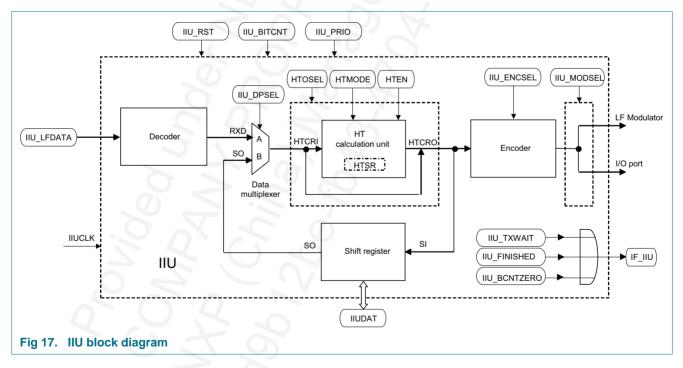

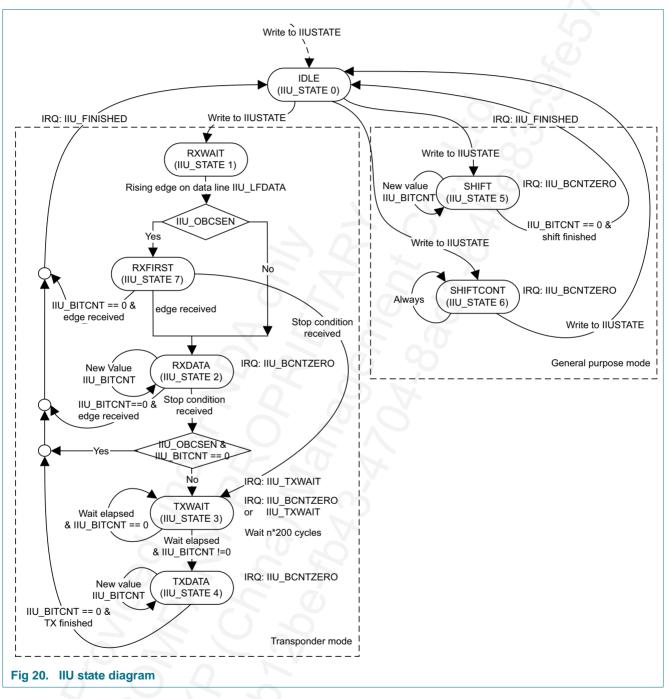

| IU [2]                             | IIUDAT                          | 0025h   | IIU data register                                     | VDD              |  |

|                                    | IIUCON0                         | 0022h   | IIU control register 0                                |                  |  |

|                                    | IIUCON1                         | 0024h   | IIU control register 1                                |                  |  |

|                                    | IIUCON2 [6]                     | 0021h   | IIU control register 2                                |                  |  |

|                                    | IIUSTAT                         | 0023h   | IIU status register                                   |                  |  |

|                                    | IIUSTATE                        | 0026h   | IIU state register                                    |                  |  |

| HT calculation unit <sup>[2]</sup> | HTCON                           | 0027h   | HT control register                                   | VDD              |  |

| AES [2]                            | AESDAT                          | 0028h   | AES data register                                     | VDD              |  |

|                                    | AESCON                          | 002Ah   | AES control register                                  |                  |  |

| Watchdog timer <sup>[2]</sup>      | WDCON                           | 0037h   | Watchdog timer control register                       | VDD              |  |

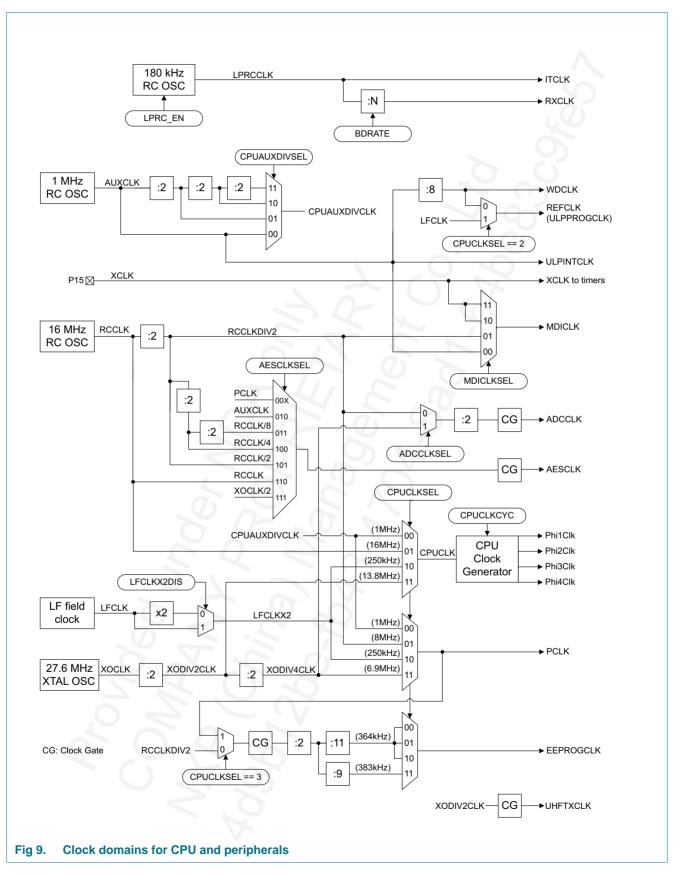

| Clock Control <sup>[2]</sup>       | CLKCON0 <sup>[3]</sup>          | 0038h   | Clock Control register 0                              | VDD              |  |

|                                    | CLKCON1                         | 0039h   | Clock Control register 1                              |                  |  |

|                                    | CLKCON2                         | 003Ah   | Clock Control register 2                              |                  |  |

|                                    | CLKCON4 <sup>[6]</sup>          | 003Fh   | Clock Control register 4                              |                  |  |

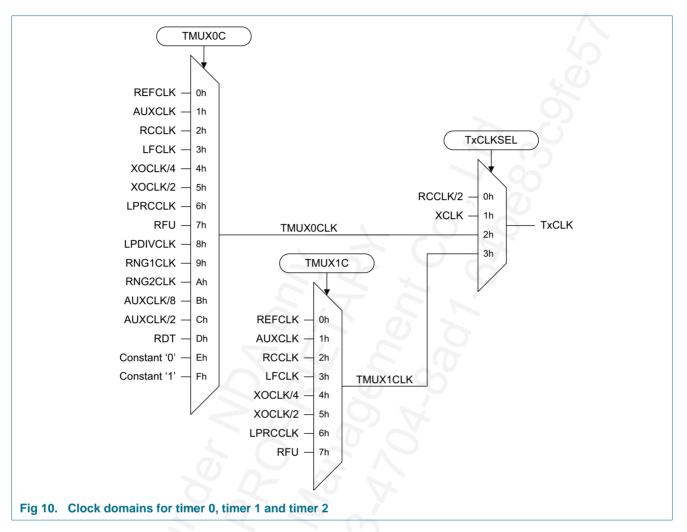

| Timer Clocks <sup>[4]</sup>        | CLKCON3                         | 003Dh   | Timer multiplexors control register                   | VDD              |  |

NCF29A1 / NCF29A2

All information provided in this document is subject to legal disclaimers.

## NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### Table 6.Device register set

| Peripheral                                        | Register<br>name <sup>[1]</sup> | Address | Description                                                | Supply<br>domain |

|---------------------------------------------------|---------------------------------|---------|------------------------------------------------------------|------------------|

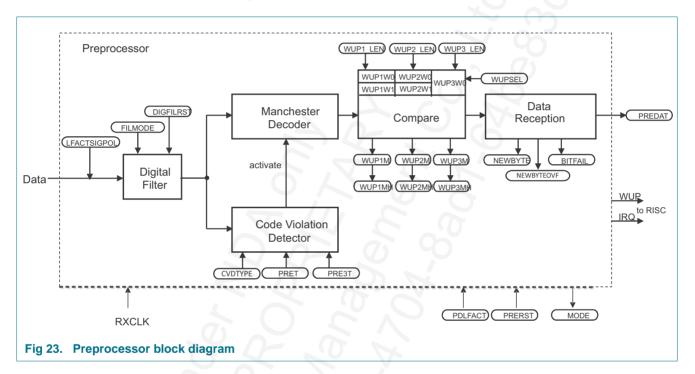

| LF Active Preprocessor,                           | PREDAT                          | 0040h   | Pre-processor data register                                | VBATREG          |

| Interval Timer, Real-time<br>Clock <sup>[4]</sup> | RTCCON                          | 0041h   | Real-time clock control register 1                         |                  |

|                                                   | PRECON2 <sup>[5]</sup>          | 0042h   | Pre-processor control register 2                           |                  |

|                                                   | PRECON3                         | 0043h   | Pre-processor control register 3                           |                  |

|                                                   | PRECON4                         | 0044h   | Pre-processor control register 4                           |                  |

|                                                   | PRECON5                         | 0045h   | Pre-processor control register 5                           |                  |

|                                                   | PRECON6 <sup>[5]</sup>          | 0046h   | Pre-processor control register 6                           |                  |

|                                                   | PRECON7                         | 0047h   | Pre-processor control register 7                           |                  |

|                                                   | PRECON8 <sup>[5]</sup>          | 0048h   | Pre-processor control register 8                           |                  |

|                                                   | PRECON9 <sup>[5]</sup>          | 0049h   | Pre-processor control register 9                           |                  |

|                                                   | PRECON10 <sup>[5]</sup>         | 006Eh   | Pre-processor control register 10                          |                  |

|                                                   | PRECON116                       | 006Fh   | Pre-processor control register 11                          |                  |

|                                                   | PRECON12 <sup>[6]</sup>         | 00F9h   | Pre-processor control register 12, reserved for future use |                  |

|                                                   | PREPD <sup>[5]</sup>            | 004Ah   | Pre-processor control power down                           |                  |

|                                                   | PRESTAT <sup>[5]</sup>          | 005Ch   | Pre-processor status register                              |                  |

|                                                   | WUP1W0                          | 005Eh   | Pre-processor wake-up pattern register 1                   |                  |

|                                                   | WUP1W1                          | 0060h   | Pre-processor wake-up pattern register 1                   |                  |

|                                                   | WUP2W0                          | 0062h   | Pre-processor wake-up pattern register 2                   |                  |

|                                                   | WUP2W1                          | 0064h   | Pre-processor wake-up pattern register 2                   |                  |

|                                                   | WUP3W0                          | 0066h   | Pre-processor wake-up pattern register 3                   |                  |

|                                                   | PRET                            | 0068h   | Pre-processor T timing calibration register                |                  |

|                                                   | PRE3T                           | 006Ah   | Pre-processor 3T timing calibration register               |                  |

|                                                   | RTCDAT                          | 006Ch   | Pre-processor Real Time Clock register                     |                  |

| Polling Configuration <sup>[6]</sup>              | PREPOLL0                        | 00F7h   | Pre-processor polling control register 0                   | VBATREG          |

|                                                   | PREPOLL1                        | 00F8h   | Pre-processor polling control register 1                   |                  |

| Notion Sensor Interface[6]                        | MSICON0                         | 00FAh   | Motion sensor control register 0                           | VBATREG          |

|                                                   | MSICON1                         | 00FBh   | Motion sensor control register 1                           |                  |

|                                                   | MSISTAT0                        | 00FCh   | Motion sensor status register 0                            |                  |

|                                                   | MSISTAT1                        | 00FDh   | Motion sensor status register 1                            |                  |

| ADC <sup>[2]</sup>                                | ADCDAT                          | 0072h   | ADC data register                                          | VDD              |

|                                                   | ADCCON <sup>[3]</sup>           | 0074h   | ADC control register                                       |                  |

| RSSI <sup>[4]</sup>                               | RSSICON <sup>[5]</sup>          | 007Ch   | RSSI control register                                      | VDD              |

| JLP EEPROM 2                                      | ULPDAT                          | 0085h   | ULP EEPROM data register                                   | VDD              |

|                                                   | ULPCON0                         | 0084h   | ULP EEPROM control register 0                              |                  |

|                                                   | ULPCON1                         | 008Ah   | ULP EEPROM control register 1                              |                  |

|                                                   | ULPSEL                          | 0082h   | ULP EEPROM selection register                              |                  |

|                                                   | ULPADDR                         | 0080h   | ULP EEPROM address register                                |                  |

NCF29A1 / NCF29A2

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

## NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

## Table 6. Device register set

| Peripheral                      | Register<br>name <sup>[1]</sup> | Address | Description                              | Supply<br>domain |

|---------------------------------|---------------------------------|---------|------------------------------------------|------------------|

| Timer 0 [2]                     | TOREG                           | 0096h   | Timer 0 register                         | VDD              |

|                                 | T0CON0                          | 0094h   | Timer 0 control register 0               |                  |

|                                 | T0CON1                          | 0095h   | Timer 0 control register 1               |                  |

|                                 | TORLD                           | 0098h   | Timer 0 reload register                  |                  |

| Timer 1 [2]                     | T1REG                           | 009Eh   | Timer 1 register                         | VDD              |

|                                 | T1CON0                          | 009Ah   | Timer 1 control register 0               |                  |

|                                 | T1CON1                          | 009Bh   | Timer 1 control register 1               |                  |

|                                 | T1CON2                          | 009Ch   | Timer 1 control register 2               |                  |

|                                 | T1CMP                           | 00A2h   | Timer 1 compare register                 |                  |

|                                 | T1CAP                           | 00A0h   | Timer 1 capture register                 |                  |

| Fimer 2 [2]                     | T2REG                           | 00A6h   | Timer 2 register                         | VDD              |

|                                 | T2CON0                          | 00A4h   | Timer 2 control register 0               |                  |

|                                 | T2CON1                          | 00A5h   | Timer 2 control register 1               |                  |

|                                 | T2RLD                           | 00A8h   | Timer 2 reload register                  |                  |

| RNG <sup>[2]</sup>              | RNGDAT                          | 00AAh   | Random number generator data register    | VDD              |

|                                 | RNGCON                          | 00ACh   | Random number generator control register |                  |

| Interrupt system <sup>[2]</sup> | INTEN0                          | 00B3h   | User interrupt enable register 0         | VDD              |

|                                 | INTEN1                          | 00B4h   | User interrupt enable register 1         |                  |

|                                 | INTEN2                          | 00B5h   | User interrupt enable register 2         |                  |

|                                 | INTEN3 <sup>[6]</sup>           | 0101h   | User interrupt enable register 3         |                  |

|                                 | INTCON                          | 00AFh   | Interrupt control register               |                  |

|                                 | SYSINTEN0                       | 00B6h   | System interrupt enable register 0       |                  |

|                                 | SYSINTEN1                       | 00B7h   | System interrupt enable register 1       |                  |

|                                 | INTFLAG0                        | 00B0h   | Interrupt request flag register 0        |                  |

|                                 | INTFLAG1                        | 00B1h   | Interrupt request flag register 1        |                  |

|                                 | INTFLAG2                        | 00B2h   | Interrupt request flag register 2        |                  |

|                                 | INTFLAG3[6]                     | 0100h   | Interrupt request flag register 3        |                  |

|                                 | INTSET0                         | 00B8h   | Interrupt set register 0                 |                  |

|                                 | INTSET1                         | 00B9h   | Interrupt set register 1                 |                  |

|                                 | INTSET2                         | 00BAh   | Interrupt set register 2                 |                  |

|                                 | INTSET3[6]                      | 0102h   | Interrupt set register 3                 |                  |

|                                 | INTCLR0                         | 00BBh   | Interrupt clear register 0               |                  |

|                                 | INTCLR1                         | 00BCh   | Interrupt clear register 1               |                  |

|                                 | INTCLR2                         | 00BDh   | Interrupt clear register 2               |                  |

|                                 | INTCLR3 <sup>[6]</sup>          | 0103h   | Interrupt clear register 3               |                  |

|                                 | INTVEC                          | 00BEh   | User interrupt vector address            |                  |

| Battery Control <sup>[4]</sup>  | BATSYS0 <sup>[5]</sup>          | 00C0h   | Battery domain system control register 0 | VBAT             |

|                                 | BATSYS1                         | 00C1h   | Battery domain system control register 1 |                  |

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

## NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### Table 6. Device register set

| Peripheral                      | Register<br>name <sup>[1]</sup> | Address | Description                         | Supply<br>domain |

|---------------------------------|---------------------------------|---------|-------------------------------------|------------------|

| Regulated Battery Domain        | USRBATRGL0                      | 004Ch   | Pre-processor user register 0       | VBATREG          |

| user registers [4]              | USRBATRGL1                      | 004Dh   | Pre-processor user register 1       |                  |

|                                 | USRBATRGL2                      | 004Eh   | Pre-processor user register 2       |                  |

|                                 | USRBATRGL3                      | 004Fh   | Pre-processor user register 3       |                  |

|                                 | USRBATRGL4                      | 0050h   | Pre-processor user register 4       | 5                |

|                                 | USRBATRGL5                      | 0051h   | Pre-processor user register 5       |                  |

|                                 | USRBATRGL6                      | 0052h   | Pre-processor user register 6       |                  |

|                                 | USRBATRGL7                      | 0053h   | Pre-processor user register 7       |                  |

| Battery Domain user             | USRBAT0                         | 00CAh   | Battery domain user register 0      | VBAT             |

| registers <sup>[4]</sup>        | USRBAT1                         | 00CBh   | Battery domain user register 1      |                  |

|                                 | USRBAT2                         | 00CCh   | Battery domain user register 2      |                  |

|                                 | USRBAT3                         | 00CDh   | Battery domain user register 3      |                  |

|                                 | USRBAT4                         | 00CEh   | Battery domain user register 4      |                  |

|                                 | USRBAT5                         | 00CFh   | Battery domain user register 5      |                  |

|                                 | USRBAT6                         | 00D0h   | Battery domain user register 6      |                  |

|                                 | USRBAT7                         | 00D1h   | Battery domain user register 7      |                  |

| LF Tune 6                       | LFTUNEVBAT                      | 00D2h   | Battery domain LF tuning register   | VBAT             |

| LF Tune 6                       | LFTUNEVDD                       | 00D4h   | Vdd domain LF tuning register       | VDD              |

| LF Short 6                      | LFSHCON                         | 00D6h   | LF Channels short control register  | VDD              |

| Power management [4]            | PCON0 <sup>[5]</sup>            | 00D8h   | Power control register 0            | VDD              |

|                                 | PCON15                          | 00D9h   | Power control register 1            |                  |

|                                 | PCON2 <sup>[5]</sup>            | 00DAh   | Power control register 2            |                  |

| SPI0[4]                         | SPI0CON0                        | 00E0h   | SPI0 control register 0             | VDD              |

|                                 | SPI0CON1                        | 00E1h   | SPI0 control register 1             |                  |

|                                 | SPIODAT                         | 00E2h   | SPI0 data register                  |                  |

|                                 | SPIOSTAT                        | 00E3h   | SPI0 status register                |                  |

| SPI1 <sup>[4]</sup>             | SPI1CON0                        | 00E4h   | SPI1 control register 0             | VDD              |

|                                 | SPI1CON1                        | 00E5h   | SPI1 control register 1             |                  |

|                                 | SPI1DAT                         | 00E6h   | SPI1 data register                  |                  |

|                                 | SPI1STAT                        | 00E7h   | SPI1 status register                |                  |

| Mathematical/ logical           | BITSWAP                         | 00F2h   | Bit swap register                   | VDD              |

| registers [4]                   | BITCNT                          | 00F0h   | Bit count register                  |                  |

|                                 | CRCDAT                          | 002Ch   | CRC data register                   |                  |

|                                 | CRC8DIN                         | 002Eh   | CRC data input register             |                  |

| TX Power Control <sup>[2]</sup> | TXPCON                          | 0104h   | TX Power Control register           | VDD              |

| TX Clock Reset Control [2]      | CLKRSTCON                       | 0105h   | TX Clock and Reset Control register | VDD              |

| VCO Calibration Control [2]     | VCOCALCON                       | 0106h   | VCO Calibration Control register    | VDD              |

| TX PLL Control [2]              | PLLCON                          | 0107h   | PLL Control register                | VDD              |

NCF29A1 / NCF29A2

All information provided in this document is subject to legal disclaimers.

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### Table 6.Device register set

| Peripheral                | Register<br>name <sup>[1]</sup> | Address | Description                         | Supply<br>domain |

|---------------------------|---------------------------------|---------|-------------------------------------|------------------|

| TX Data Encoder [2]       | TXDAT                           | 0108h   | TX Data register                    | VDD              |

|                           | TXSPC                           | 010Ah   | Transmission space masking register |                  |

|                           | ENCCON0                         | 010Ch   | TX Encoder control register 0       |                  |

|                           | ENCCON1                         | 010Eh   | TX Encoder control register 1       |                  |

| TX Frequency Control [2]  | FREQCON0                        | 0110h   | Frequency control register 0        | VDD              |

|                           | FREQCON1                        | 0112h   | Frequency control register 1        |                  |

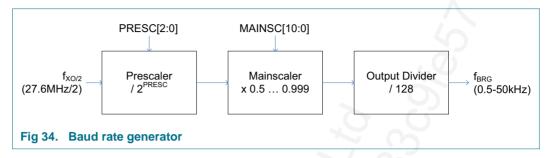

| TX Baud Rate Control [2]  | BRGCON                          | 0114h   | Baud Rate control register          | VDD              |

| TX Modulation Control [2] | FSKCON                          | 0116h   | FSK control register                | VDD              |

|                           | FSKRMP                          | 0117h   | FSK ramp control register           |                  |

|                           | ASKCON                          | 0118h   | ASK control register                |                  |

|                           | ASKRMP                          | 011Ah   | ASK ramp control register           |                  |

| TX PA control [2]         | PACON 3                         | 011Bh   | PA control register                 | VDD              |

|                           | PAPWR 3                         | 011Ch   | PA power control register           |                  |

|                           | PATRIM 6                        | 011Dh   | PA reference trimming register      |                  |

|                           | PALIMIT <sup>[6]</sup>          | 011Eh   | PA current limiter control register |                  |

[1] In the detailed register descriptions, bits marked 'RFU' are reserved for future use. Note that read operation to 'RFU' bits may return an undefined result. For future compatibility, a write operation shall assign a '0'.

[2] Register group as in predecessor device, NCF2960

[3] Register differs from the predecessor device, NCF2960

[4] Register group as in predecessor devices, NCF2971, NCF2950, NCF2951, NCF2952

- [5] Register differs from the predecessor devices, NCF2971, NCF2950, NCF2951, NCF2952

- [6] New register in NCF29A1 / NCF29A2

- [7] Under normal operating conditions all registers belonging to VBAT domain keep their content as long as VBAT power supply is maintained and BATPOR is not asserted. Its recommended that the application software refreshes these registers to improve the system robustness in case of ESD stress conditions.

- [8] Under normal operating conditions all registers belonging to VBATREG domain keep their content as long as VBATREG power supply is maintained. Its recommended that the application software refreshes these registers to improve the system robustness in case of ESD stress conditions.

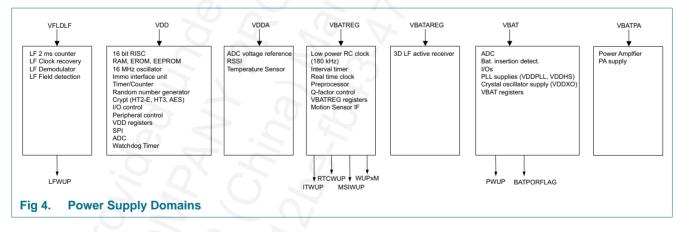

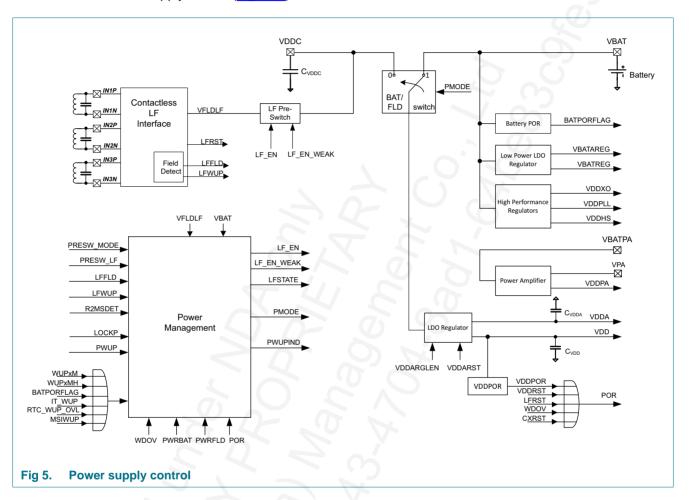

### 2.2 Power management

#### 2.2.1 Power supply domains

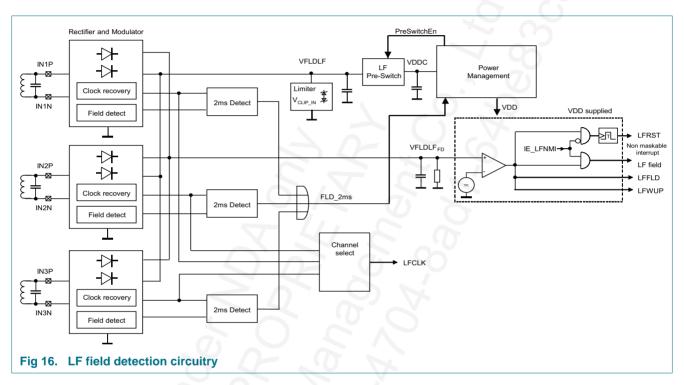

The NCF29A1 / NCF29A2 features several power supply domains (see <u>Figure 4</u>). A versatile power management (see <u>Figure 5</u>) enables the device to derive its power supply from two different energy sources

- External battery (VBAT, VBATPA)

- Low frequency field (VFLDLF)

The two corresponding power supply domains VBAT (VBATPA) and VFLDLF are unregulated. The device is able to operate when any of the energy sources is available regardless the presence or absence of the other.

Derived from either of the two unregulated domains are the regulated power supply domains:

- Digital core supply (VDD)

- Analogue core supply (VDDA)

Derived from the unregulated battery domain are the regulated power supply domains:

- Digital battery supply (VBATREG)

- Analogue battery supply (VBATAREG)

- Crystal oscillator supply (VDDXO)

- Analogue PLL supply (VDDPLL)

- Digital PLL supply (VDDHS)

- Power amplifier internal supplies (VDDPA)

The Digital core supply (VDD) can be derived from the two unregulated domains VBAT and VFLDLF. The regulated analogue core supply (VDDA) supplies the RSSI and ADC bandgap for supply voltage measurements.

The crystal oscillator, PLL, PA, LF active supplies (VDDXO, VDDPLL, VDDHS, VDDPA, VBATREG, VBATAREG) can only be derived from battery pin (VBAT, VBATPA).

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

Except VDD, the voltage regulators for the digital and analogue supplies are turned off after device start-up. In order to employ the blocks supplied with these voltages, the respective dedicated voltage regulators have to be activated first.

Determining the appropriate supply configuration is accomplished by means of the power supply control (Figure 5).

#### 2.2.2 Power supply control

#### 2.2.2.1 Power supply switch

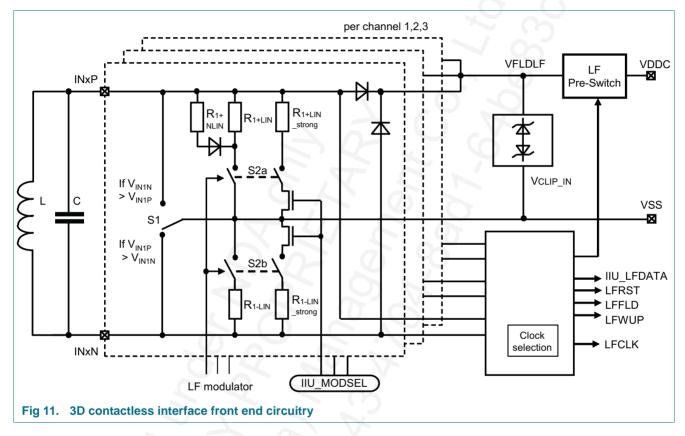

The NCF29A1 / NCF29A2 provides several switches for power supply selection of the core. The main supply switch selects between battery and field supply (set by PWRBAT and PWRFLD).

The field supply is based on one pre-switch for the LF. The pre-switch consist of a weak and a strong part. It can be activated either in one or two stages. The weak pre-switch features a current limitation in order to limit the energy transferred from the field into the blocking capacitor at VDDC. This avoids deep dips in the field supply, which might be erroneously interpreted as a load modulation by the base station.

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

When the power supply state is changed the device supply switch opens the existing connection before connecting the new supply. The device is powered for a short period of time from the internal blocking capacitor. Therefore, the application shall minimize the current consumption when changing the supply state to prevent an accidental power-on reset.

#### 2.2.2.2 Device wake up

The following wake up events terminate the POWER OFF state:

- Presence of LF field

- Port wake-up (button press)

- Motion sensor wake-up

- Detection of valid LF active wake-up pattern

- Interval counter or real time clock wake-up

- Battery insertion

If a wake-up event emerges, the power management selects the corresponding power supply. If more than one wake-up event is pending at the same time, the power management automatically selects the strongest available supply source related to the wake-up event.

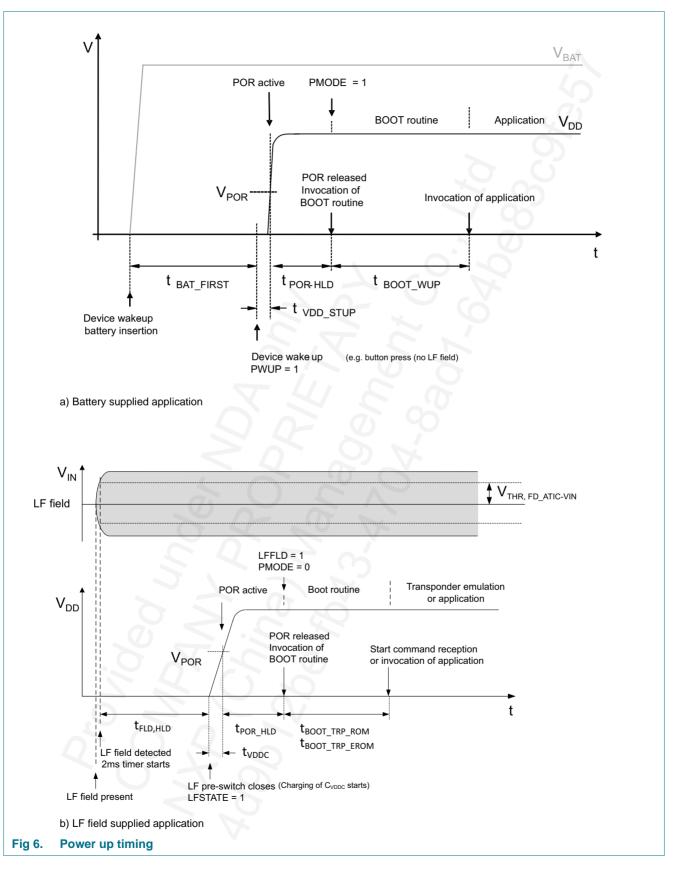

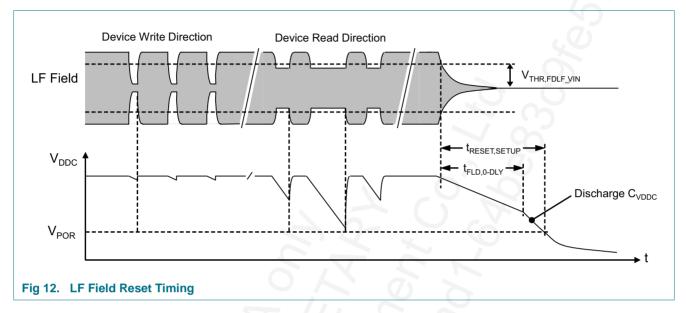

Once the supply voltage (VDD) exceeds the power on reset threshold voltage ( $V_{POR}$ ), the power management state is locked and the power on reset comparator output signal (VDDPOR) becomes low. After a short delay ( $t_{POR\_HLD}$ ), the RISC becomes operational and the device enters RUN mode (Figure 6). All further supply state changes are under control of the application.

Starting with the BOOT sequence, the power supply state of the VDD supplied part can be monitored and influenced via the power control registers. A change of the supply configuration may apply e.g. in case an LF Field and button press is detected at the same time or in case an LF Field is being detected while battery supply has been utilized. If an LF field and button press event are detected at the same time, then the LF field wake up has precedence and will commence.

#### 2.2.2.3 Device reset

The device supply voltage (VDD) is monitored by a power on reset circuitry. A reset (POR) is generated under the following conditions:

- The device leaves the POWER-OFF state

- VDD brown out is detected and code is executed from EROM or a VDD brown out is detected and the CPU clock source is set to a frequency greater than 8MHz.

- Voltage level at VDD falls below power-on reset threshold (VDDPOR)

- LF field emerges and LFNMIEN bit is '0' (LFRST)

- Watchdog overflow (WDOV)

- VDDRST is set by the application (Software reset)

- CPU/MMU exception occurs and CXNMIEN bit is '0' (CXRST)

Upon a device reset the power management logic is released and starts with a new evaluation of the supply condition.

### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

NCF29A1 / NCF29A2

All information provided in this document is subject to legal disclaimers

© NXP Semiconductors N.V. 2016. All rights reserved.

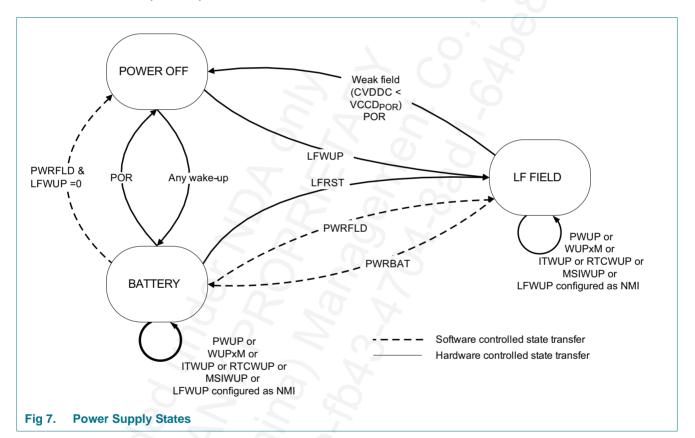

#### 2.2.2.4 Power supply states

Dependent on whether the device power is derived from an external battery or from either the LF field, the device supports two different core supply states:

- Battery supply (BATTERY)

- LF field supply (LF FIELD)

These two supply states are CPU active states. In POWER OFF state, the device remains in a third very low power state (see Figure 7).

Determining the appropriate supply configuration is accomplished by means of the ROM implemented device BOOT sequence called by the RISC controller during device power-up.

#### 2.2.2.5 POWER OFF state

In POWER OFF state, most blocks of the device are internally disconnected from the battery supply, resulting in a very low current consumption. The internal device supply voltage (VDD) stays below the Power On Reset threshold voltage and device operation is halted. Only a minimum of circuitry remains operational, like the power management and I/O ports (configured as input).

The device resides in POWER OFF state any time a Power On Reset comparator output (VDDPOR) condition is applicable because of a weak supply condition. The POWER OFF state is terminated by a Wake Up event, like the presence of an LF Field (LFWUP) or a Port Wake Up (PWUP).

Once the supply condition is evaluated during device power-up and the BOOT sequence is completed, the device will start execution of the application program in either BATTERY state or LF FIELD state.

#### 2.2.2.6 BATTERY state

In BATTERY state, the device is powered from the external battery. After execution of the BOOT sequence, device operation is controlled by the RISC and the program code starts at the BATTERY WARM BOOT vector. The application code can terminate the BATTERY state.

In case an LF field is detected, the device behavior depends on the configuration. If according to the configuration an NMI is caused after field detection, the state is kept and control is still with the RISC. If according to the configuration a reset is caused by field detection, the boot routine is invoked again and the state is changed to LF FIELD, dependent on whether the LF Field has been detected. Activating the LF Field switches also provokes a state change to LF FIELD.

Button events do not cause a state change and have to be handled via the RISC. In case no LF Field is present, and the device supply drops below the Power On Reset threshold voltage, the device enters POWER OFF state.

#### 2.2.2.7 LF FIELD state

In LF FIELD state the device supply is derived from the LF Interface.

After execution of the BOOT sequence, device operation is controlled by the RISC and the program code starts at the LF FIELD WARM BOOT vector (unless a built-in LF transponder emulation is selected in the boot routine).

The LF FIELD state is left either in case of a weak LF Field supply condition, branching to POWER OFF state, or forced by the application program when activating the Battery Supply switch. The state changes to BATTERY state.

#### 2.2.3 Battery supply states

The battery supply domains VBATREG and VBATAREG supports the two supply states ON and OFF. A state change can be initiated via the control bits BATRGLEN and BATRGLRST.

The battery supply states are independent of the power supply states which are related to the core.

#### 2.2.4 Registers

#### 2.2.4.1 Battery system register BATSYS0

The battery system register BATSYS0 controls the VBAT regulator. The VBAT regulator shall be turned on in order to get access to the blocks supplied by the regulated battery supplies VBATREG and VBATAREG, like the interval timer and LF active preprocessor.

BATSYS0 is fully accessible in SYSTEM mode only. An application executed in USER mode shall use a system call to change the register.

| Bit    | Symbol     | Access | Value | Description                           |

|--------|------------|--------|-------|---------------------------------------|

| 7 to 3 | RFU        | R      |       | Reserved for future use               |

| 2      | BATRGLRST  | R      |       | Static reset of VBATREG supplied part |

|        |            |        | 0     | Release reset                         |

|        |            |        | 1     | Reset                                 |

| 1      | BATRGLEN   | R      |       | VBAT regulator enable                 |

|        |            |        | 0     | Disable                               |

|        |            |        | 1     | Enable                                |

| 0      | BATPORFLAG | R      |       | VBAT power-on reset flag              |

|        |            |        | 0     | Clear                                 |

|        |            |        | 1     | Set                                   |

#### Table 7. Battery system register BATSYS0 (reset value xxxx\_x101b)

#### BATRGLRST, static reset of VBATREG supplied part

Setting BATRGLRST resets the battery powered registers in the VBATREG domain.

#### **BATRGLEN, VBAT regulator enable**

BATRGLEN turns on and off the VBAT regulator.

#### **BATPORFLAG, VBAT power-on reset flag**

Sets or clears the Battery Power On Reset (BATPOR) flag. If BATPOR is low and BATPORFLAG is high a battery insertion device wake-up occurs.

#### 2.2.4.2 Battery system register BATSYS1

The battery system register BATSYS1 controls the battery reset.

BATSYS1 is fully accessible in SYSTEM mode only. An application executed in USER mode shall use a system call to change the register.

| Table 0. | Battory by biom | regiotor Brito | 101 (10001 ) |                             |

|----------|-----------------|----------------|--------------|-----------------------------|

| Bit      | Symbol          | Access         | Value        | Description                 |

| 7 to 1   | RDT             | R              |              | Reserved for device test    |

| 0        | BATRST          | R              |              | Reset of VBAT supplied part |

|          |                 |                | 0            | No effect                   |

|          |                 |                | 1            | Reset                       |

#### Table 8. Battery system register BATSYS1 (reset value xxxx\_xx0b)

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### **BATRST**, reset of VBAT supplied part

Setting this bit has the same effect as a battery reset caused by a battery insertion. All registers supplied with VBAT are initialized to their default states. The VBAT regulator is turned off and BATRGLRST is set.

#### 2.2.4.3 Power control register PCON0

The power control register PCON0 provides means to select the supply state of the device and the behavior of the LF passive mode.

| Bit | Symbol                | Access                | Value | Description                                                                                            |

|-----|-----------------------|-----------------------|-------|--------------------------------------------------------------------------------------------------------|

| 7   | VDDRST                | R0 <mark>11</mark> /W |       | Reset of VDD supplied part                                                                             |

|     |                       |                       | 0     | No effect                                                                                              |

|     |                       |                       | 1     | Reset                                                                                                  |

| 6   | VDDARST               | R/W                   |       | Static reset of VDDA supplied part                                                                     |

|     |                       |                       | 0     | Release reset                                                                                          |

|     |                       |                       | 1     | Reset                                                                                                  |

| 5   | VDDARGLEN             | R/W                   |       | Enable VDD regulator for battery and die temperature measurement                                       |

|     |                       |                       | 0     | Disable                                                                                                |

|     |                       |                       | 1     | Enable                                                                                                 |

| 4   | PRESW_MODE            | R/W                   |       | Pre-switch mode                                                                                        |

|     |                       |                       | 0     | see Table 10                                                                                           |

|     |                       |                       | 1     | see <u>Table 10</u>                                                                                    |

| 3   | VBATBRNIND            | R                     |       | 2.4 V VBAT brown-out indicator flag                                                                    |

|     |                       |                       | 0     | The voltage level at VBAT is above the brown-out indicator threshold $V_{\text{VBATIND}}$ (typ. 2.4 V) |

|     |                       |                       | 1     | The voltage level at VBAT is below the brown-out indicator threshold                                   |

| 2   | PRESW_LF              | R/W                   |       | Pre-switch for LF supply                                                                               |

|     |                       |                       | 0     | see <u>Table 10</u>                                                                                    |

|     |                       |                       | 1 0   | see Table 10                                                                                           |

| 1   | PWRBAT <sup>[2]</sup> | R0/W                  |       | Activate power supply from battery                                                                     |

|     |                       |                       | 0     | No effect                                                                                              |

|     |                       |                       | 1     | Activate                                                                                               |

| 0   | PWRFLD <sup>[2]</sup> | R0/W                  |       | Activate power supply from field                                                                       |

|     |                       |                       | 0     | No effect                                                                                              |

|     | 20                    |                       | 1     | Activate                                                                                               |

|     |                       |                       |       |                                                                                                        |

#### Table 9. Power control register PCON0 (reset value 0100\_x000b)

[1] R0 means the return value is always 0

[2] If PWRBAT and PWRFLD are set to '1' at the same time, PWRFLD has priority.

#### VDDRST, Reset of VDD supplied part

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

Setting VDDRST triggers a reset (POR) and sets the device in POWER OFF state, a reset of the entire VDD supplied part is executed, the VDDA regulator will be turned off and the bit VDDARST is set. VDDRST reads always '0'. A pending wake-up triggers an immediate re-boot of the device.

#### VDDARST, static reset of VDDA supplied part

VDDARST is a static reset signal for the VDDA supplied part. If the VDDA regulator is turned off (VDDARGLEN = '0'), VDDARST is always active.

Setting VDDARST to '0' releases the reset of the VDDA supplied part and is only possible when the VDDA regulator is turned on (VDDARGLEN = '1'). Before VDDARST can be released, the VDDA regulator start-up time  $t_{VDDA,PON}$  must be considered.

#### **VDDARGLEN, VDDA regulator enable**

The VDDA regulator is turned on and off by setting and resetting VDDARGLEN, respectively. For VDDARGLEN = '0', VDDARST will become '1' automatically.

Example: In order to turn on the VDDA regulator, execute the following steps:

- Set VDDARGLEN to '1': This activates the VDDA regulator.

- Wait the time t<sub>VDDA,PON</sub> until the voltage at VDDA has stabilized (do not use the VDDA brown-out detector flag VDDABRNFLAG to determine this time).

- Reset VDDARST to release the static reset and to activate the VDDA domain.

The application shall only enable the VDDA regulator, if the voltage at VDD is sufficiently large, i.e. the VDD brown-out flag VDDBRNFLAG is '0'. Otherwise the activation of the VDDA regulator can generate a VDD reset.

NCF29A1 / NCF29A2

© NXP Semiconductors N.V. 2016. All rights reserved.

Product data sheet COMPANY CONFIDENTIAL

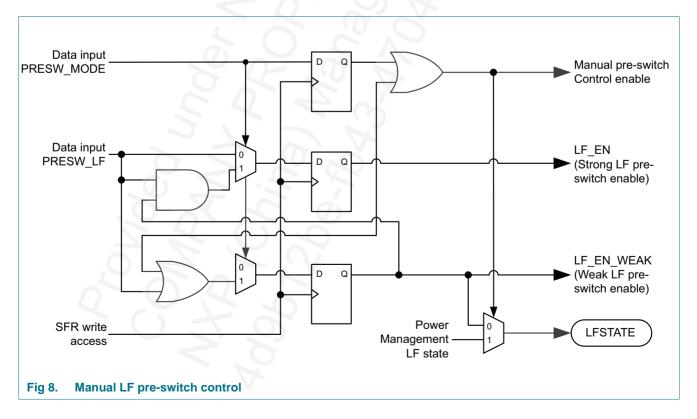

#### PRESW\_MODE, PRESW\_LF, Activate LF field pre-switch

These two control bits are used to activate the pre-switch for LF field supply (Figure 8). If at least one of these bits is set, the LF pre-switch is controlled manually by the application and the state of the power management field selection after device start-up is ignored.

The control of PRESW\_MODE and PRESW\_LF is organized in a state machine, which valid state transitions are given in Table 10.

| Previous s     | state    |         | New data       |          | Next state     |          |         |

|----------------|----------|---------|----------------|----------|----------------|----------|---------|

| PRESW<br>_MODE | PRESW_LF | LFSTATE | PRESW_<br>MODE | PRESW_LF | PRESW<br>_MODE | PRESW_LF | LFSTATE |

| Х              | Х        | Х       | 0              | 0        | 0              | 0        | 0       |

| Х              | Х        | Х       | 0              | 1        | 0              | 1        | 1       |

| Х              | 0        | 0       | 1              | 0        |                | 0        | 0       |

| Х              | 0        | 0       | 1              | 1        | 1              | 0        | 1       |

| 1              | 0        | 1       | 1              | 0        | 1              | 0        | 0       |

| 1              | 0        | 1       | 1              | 1        | 1              | 1        | 1       |

| Х              | 1        | 1       | 1              | 0        | 1              | 0        | 1       |

| Х              | 1        | 1       | 1              | 1        | 1              | 1        | 1       |

#### Table 10. Valid state transitions for PRESW\_MODE, PRESW\_LF and LFSTATE

If PRESW\_MODE is equal to '0' the bit PRESW\_LF controls the weak and the strong pre-switches directly. It is possible to activate and deactivate the pre-switches with one write access.

If the bit PRESW\_MODE is equal to '1' the weak and the strong pre-switch can be activated and deactivated in a sequence. If a '1' is written to PRESW\_LF the weak pre-switch is activated, while the register bit PRESW\_LF is not yet set. Instead a shadow flag is set, which activates the weak pre-switch. The state of the weak pre-switch can be observed via the control bit LFSTATE in this case. The strong pre-switch is finally activated, if the application writes another '1' to register PRESW\_LF. The de-activation follows the same procedure: The first '0' deactivates the strong pre-switch and the second '0' the weak one.

The value, which is written to PRESW\_MODE at the same time when PRESW\_LF is written, determines the mode rather than the stored value in the register. The register content of PRESW\_MODE is required to ensure the manual pre-switch control in case no strong pre-switch is activated.

Example: In order to switch power supply from battery to LF field, execute the following steps:

- Close the pre-switch of the LF supply by writing a '1' to PRESW\_LF. The blocking capacitor at pin VDDC gets charged (if the activation of the strong pre-switch causes a too deep dip in the field supply it is also possible to close only the weak pre-switch prior to the strong one).

- Wait until the voltage at VDDC has settled. The waiting time shall be properly determined for specific capacitance values and field strengths by the user.

- Set the bit PWRFLD to '1' to commutate from battery supply to field supply.

#### NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

#### **VBATBRNIND**, Weak battery indicator

Battery monitoring used to identify battery end of life (approximately 2.4V), VBATBRNINDEN bit must be set to '1'. The battery indicator connects a resistor load (100 to 300 k $\Omega$ ) across the VBAT supply.

#### **PWRBAT, Activate power supply from battery**

If the device is supplied by field and a '1' is written to register bit PWRBAT the main supply switch commutates to battery supply. If the device is already supplied by battery writing a '1' has no effect. The bit reads always '0'.

The application shall reduce the power consumption as much as possible when changing the supply condition. Moreover, the CPU shall not run at a clock speed of more than 250 kHz when PWRBAT is set to '1'. These measures avoid an unintentional reset caused by the "break-before-make" mechanism of the supply switches.

If PWRFLD and PWRBAT are set to '1' at the same time, PWRFLD has priority.

In order to enter POWER-OFF state when the device is running with battery supply, set VDDRST to one.

#### PWRFLD, Activate power supply from field

If the device is supplied by the battery and a '1' is written to register bit PWRFLD the main supply switch commutates to field supply. If the device is already supplied by field, writing a '1' has no effect. The bit reads always '0'.

PWRFLD does not influence the LF field pre-switch.

The application shall reduce the power consumption as much as possible when changing the supply condition. Moreover, the CPU shall not run at a CPU clock speed of more than 250 kHz when PWRFLD is set to '1'. These measures avoid an unintentional reset caused by the "break-before-make" mechanism of the supply switches.

If PWRFLD and PWRBAT are set to '1' at the same time, PWRFLD has priority.

#### 2.2.4.4 Power control register PCON1

The power control register PCON1 provides flags to monitor the current state of the power management, battery voltage and the field supply.

| Bit | Symbol      | Access | Value | Description                                     |

|-----|-------------|--------|-------|-------------------------------------------------|

| 7   | VDDBRNFLAG  | R      |       | VDD brown-out detector flag                     |

|     |             |        | 0     | VDD voltage level is above brown-out threshold  |

|     |             |        | 1     | VDD voltage level is below brown-out threshold  |

| 6   | VDDABRNFLAG | R      |       | VDDA brown-out detector flag                    |

|     |             |        | 0     | VDDA voltage level is above brown-out threshold |

|     |             |        | 1     | VDDA voltage level is below brown-out threshold |

| 5   | VBATMONEN   | R/W    |       | Battery monitoring control                      |

|     |             |        | 0     | Battery brownout disabled                       |

|     |             |        | 1     | Battery brownout enable                         |

#### Table 11. Power control register PCON1 (reset value xx0xxxxb)

NCF29A1 / NCF29A2

NCF29A1 (TOKEN 3D) / NCF29A2 (TOKEN 1D)

| Bit | Symbol        | Access | Value | Description                                                            |

|-----|---------------|--------|-------|------------------------------------------------------------------------|

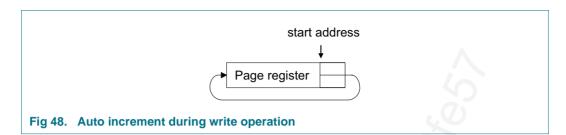

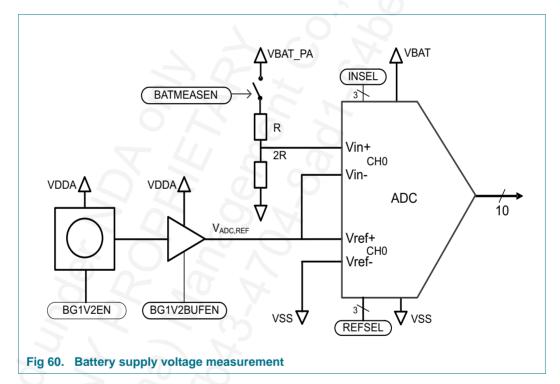

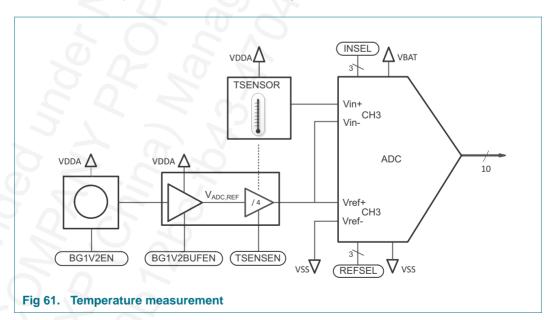

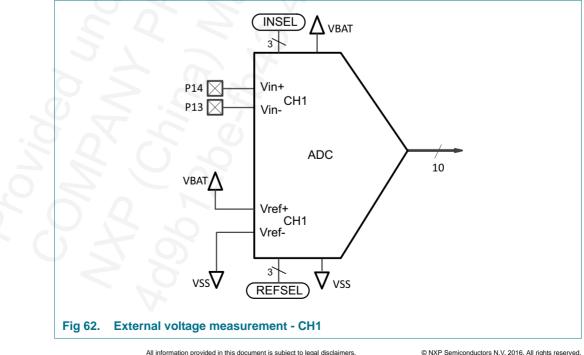

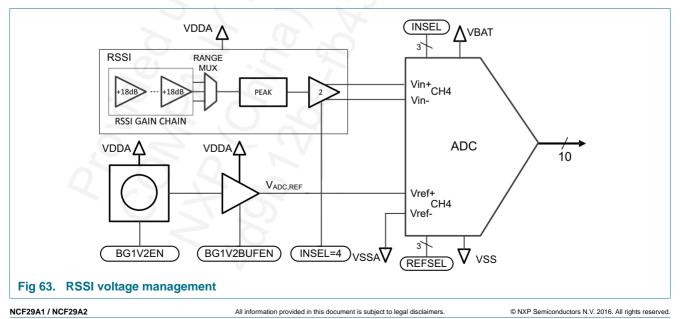

| 4   | PWRMANLFSTATE | R      |       | LF field supply state                                                  |