# 1MHz High Output current High Efficiency Synchronous Step-Up Converter

#### DESCRIPTION

ETA1090 is an ETA Solutions' high efficiency, high frequency synchronous Step-Up converter, capable of delivering output current up to 3A at a 5V output from a 3.6V input. With a low Rdson Power MOS and a built-in synchronous rectifier, its efficiency can be as high as 91% at a 5V/2.1A load. This greatly minimizes power dissipation and reduces heat on the IC, making it ideal for applications that require small board space and have stringent temperature constraints, such as power banks and mobile devices. ETA1090 also incorporates ETA Solutions' True-Shutoff technology that protects against overload and short-circuit conditions. All of these features are integrated in a tiny DFN3x3-12 package. With 1MHz switching frequency, small external input and output capacitors and inductor can be used.

## **FEATURES**

- Up to 97% Energy Converting Efficiency

- Up to 3A output current at 5V output,

3.6V input

- Externally adjustable output voltage

- True Shut off during shutdown and output short-circuit protection

- Thermal Shutdown

- DFN3x3-12 Package

#### **APPLICATIONS**

- 3G/4G PCI-e module

- Power Bank

- Mobile 3G/4G Mi-Fi

- Mobile Bluetooth music player and speaker

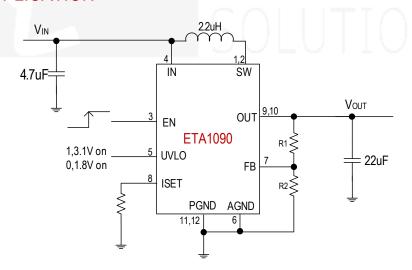

#### TYPICAL APPLICATION

ORDERING INFORMATION

PART No. ETA1090D3M PACKAGE DFN3x3-12 TOP MARK ETA1090

YWW2L

Pcs/Reel 5000

www.etasolution.com

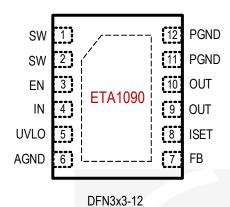

## PIN CONFIGURATION

# ABSOLUTE MAXIMUM RATINGS

(Note: Exceeding these limits may damage the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

| All Pins Voltage        |                   | 0.3          | 3V to 5.5V |

|-------------------------|-------------------|--------------|------------|

| Operating Temperature R | ange              | 40°          | C to 85°C  |

| Storage Temperature Rar | nge               | 55°C         | to 150°C   |

| Thermal Resistance      | $\theta_{\sf JC}$ | $	heta_{JA}$ |            |

| DFN3X3-12               | 3                 | 48           | °C/W       |

| Lead Temperature (Solde | ;)                | 260°C        |            |

| ESD HBM (Human Body     | Mode)             |              | 3KV        |

# **ELECTRICAL CHARACTERISTICS**

$(V_{\text{IN}}$  =3.3V,  $V_{\text{OUT}}$ =3.8V, AGND=PGND, unless otherwise specified. Typical values are at TA = 25°C.)

| PARAMETER                                  | CONDITIONS                                         | MIN   | TYP                  | MAX   | UNITS |

|--------------------------------------------|----------------------------------------------------|-------|----------------------|-------|-------|

| Input Voltage Range                        | UVLO=GND                                           | 1.9   |                      | 5.5   | V     |

| Quiescent Current                          | EN=IN, No load,<br>Not switching                   |       | 50                   | 80    | μA    |

| Shutdown Supply Current at V <sub>IN</sub> | V <sub>EN</sub> =GND                               |       | 0.5                  | 5     | μA    |

| V <sub>UVLO</sub>                          | UVLO=GND, IN rising                                | 1.7   | 1.8                  | 1.9   | V     |

| VUVLO                                      | UVLO=IN, IN rising                                 |       | 3.1                  | /IN.  | V     |

| VIN UVLO hysteresis                        |                                                    |       | 0.3                  |       | V     |

| Feedback Voltage                           | V <sub>OUT</sub> =2.1 to 5V                        | 0.588 | 0.6                  | 0.612 | V     |

| FB Leakage Current                         |                                                    |       | 0                    |       | nA    |

| Output Over Voltage Protection             | Hysteresis=500mV                                   |       | 6                    |       | V     |

| NMOS Switch On Resistance                  |                                                    |       | 55                   |       | mΩ    |

| PMOS Switch On Resistance                  |                                                    |       | 65                   |       | mΩ    |

| SW Leakage Current                         | $V_{OUT}$ =5V, $V_{SW}$ =0 or 5V,<br>$V_{EN}$ =GND |       |                      | 10    | μA    |

| Down Mode Current limit                    |                                                    |       | 2.5                  |       | Α     |

| Down Made Voltage at Ver-                  | V <sub>OUT</sub> Rising                            |       | V <sub>IN</sub> -0.2 |       | V     |

| Down Mode Voltage at Vout                  | V <sub>OUT</sub> falling                           |       | $V_{\text{IN}}$ -0.5 |       | V     |

| Switching Frequency                        |                                                    | 0.75  | 1                    | 1.25  | MHz   |

| Short Circuit Hiccup time                  | ON                                                 |       | 3.75                 |       | ms    |

| Short Circuit Fliccup time                 | OFF                                                |       | 75                   |       | ms    |

| NMOS Switch Current Limit                  | $R_{ISET}$ =51k $\Omega$                           | 2.6   | 3.6                  | 4.6   | Α     |

| TAINTOO OWILLIT OUTTON LITTIE              | $R_{ISET}$ =30k $\Omega$                           |       | 6                    |       | Α     |

| EN Input Current                           | V <sub>EN</sub> =3V                                |       | 1.5                  | 2     | μA    |

| EN logic high voltage                      |                                                    | 1.6   |                      |       | V     |

| EN logic low voltage    |                            |     |     | 0.6 | V  |

|-------------------------|----------------------------|-----|-----|-----|----|

| UVLO Input Current      | V <sub>UVLO</sub> =3V      |     | 1.5 |     | μA |

| UVLO logic high voltage |                            | 1.5 |     |     | V  |

| UVLO logic low voltage  |                            |     |     | 0.6 | V  |

| Thermal Shutdown        | Rising,<br>Hysteresis=20°C |     | 150 |     | °C |

# PIN DESCRIPTION

| between IN and SW pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |      |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PIN#                                                                      | NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |  |  |  |

| disable.  Input pin. Bypass IN to GND with a 10uF or greater ceramic capacitor.  UVLO Select IN UVLO.  AGND AGND Analog ground pin. AGND is internally connected to the analog ground of the control circuitry.  Feedback Input. Connect an external resistor divider from the output to FB and GND to set $V_{OUT}$ Programmable peak-current-limit control. Connect an external resistor (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000 \text{ (A)}$ If $I_{peak} > 6A$ by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  OUT Output pin. Bypass with a 22µF or larger ceramic capacitor closely between this pin and ground. | 1,2                                                                       | SW   | Switching node of the Switching Regulator. Connect a 1uH to 2.2µH inductor between IN and SW pin.                                                                                                                                                                                                                                 |  |  |  |

| 5 UVLO Select IN UVLO. 6, AGND Analog ground pin. AGND is internally connected to the analog ground of the control circuitry.  7 FB Feedback Input. Connect an external resistor divider from the output to FB and GND to set Vout  Programmable peak-current-limit control. Connect an external resistor (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000 \text{ (A)}$ If $I_{peak} > 6\text{A}$ by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  9,10 OUT Output pin. Bypass with a 22μF or larger ceramic capacitor closely between this pin and ground.                                                                      | 3                                                                         | EN   | Enable pin for the IC. Drive this pin high to enable the IC, low or floating to disable.                                                                                                                                                                                                                                          |  |  |  |

| AGND Analog ground pin. AGND is internally connected to the analog ground of the control circuitry.  FB Feedback Input. Connect an external resistor divider from the output to FB and GND to set $V_{OUT}$ Programmable peak-current-limit control. Connect an external resistor (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000 \text{ (A)}$ If $I_{peak} > 6\text{A}$ by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  Output pin. Bypass with a $22\mu\text{F}$ or larger ceramic capacitor closely between this pin and ground.                                                                                            | 4 IN Input pin. Bypass IN to GND with a 10uF or greater ceramic capacitor |      |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Thermal pad AGND control circuitry.  FB Feedback Input. Connect an external resistor divider from the output to FB and GND to set $V_{OUT}$ Programmable peak-current-limit control. Connect an external resistor (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000 \text{ (A)}$ If $I_{peak} > 6A$ by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  9,10 OUT Output pin. Bypass with a $22\mu\text{F}$ or larger ceramic capacitor closely between this pin and ground.                                                                                                                                                          | 5                                                                         | UVLO | Select IN UVLO.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| and GND to set $V_{\text{OUT}}$ Programmable peak-current-limit control. Connect an external resistor (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000  (A)$ If $I_{peak} > 6$ A by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  9,10  OUT  Output pin. Bypass with a 22µF or larger ceramic capacitor closely between this pin and ground.                                                                                                                                                                                                                                                                                     | ,                                                                         | AGND |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{R_{iset}} \times 1000  (A)$ If $I_{peak} > 6$ A by setting Riset, then the setting is invalid, $I_{peak}$ remains 6A.  9,10 OUT Output pin. Bypass with a 22 $\mu$ F or larger ceramic capacitor closely between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                       | 7 FB                                                                      |      |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                                         | ISET | (Riset) between ISET and AGND to set the peak NMOS current-limit threshold. The current-limit threshold may be adjusted from 0.6A to 6.0A, And if follows following equation: $I_{peak} = \frac{180}{\mathrm{R}_{iset}} \times 1000 \ \ (A)$ If $I_{peak}$ > 6A by setting Riset, then the setting is invalid, $I_{peak}$ remains |  |  |  |

| 11,12 PGND Power ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9,10                                                                      | OUT  |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11,12                                                                     | PGND | Power ground pin.                                                                                                                                                                                                                                                                                                                 |  |  |  |

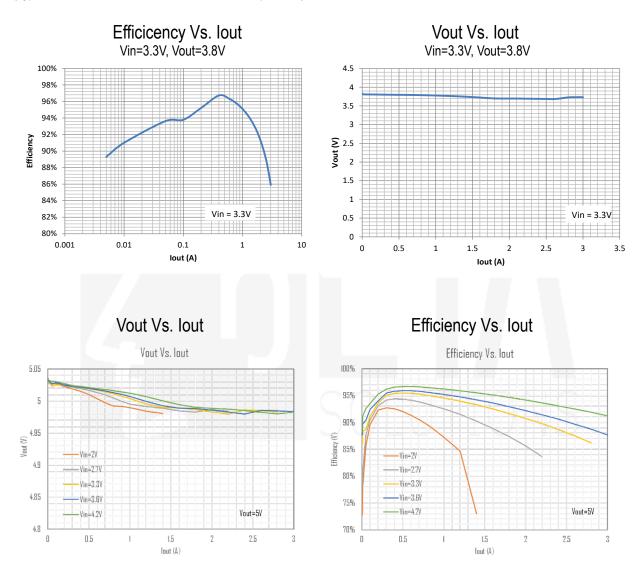

#### TYPICAL CHARACTERISTICS

(Typical values are at T<sub>A</sub> = 25°C unless otherwise specified.)

### APPLICATION INFORMATION

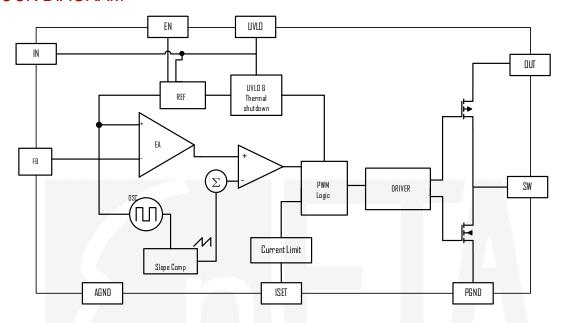

#### **Loop Operation**

The ETA1090 is a wide input range, high-efficiency, DC/DC step up switching regulator, integrated with a  $65m\Omega$  Low Side Main MOSFET and  $55m\Omega$  synchronous MOSFET. It uses a PWM current-mode control scheme. An error amplifier integrates error between the FB signal and the internal reference voltage. The output of the integrator is then compared to the sum of a current-sense signal and the slope compensation ramp. This operation generates a PWM signal that modulates the duty cycle of the power MOSFETs to achieve regulation for output voltage.

# ETA1090

The output voltage is adjustable by external resistor. The peak current of the NMOS switch is also sensed to limit the maximum current flowing through the switch and the inductor. The maximum peak current limit is set to 6A and can be tuned by external resistor. An internal temperature sensor prevents the device from getting overheated in case of excessive power dissipation.

### **Light Load Operation**

Traditionally, a fixed constant frequency PWM DC/DC regulator always switches even when the output load is small. When energy is shuffling back and forth through the power MOSFETs, power is lost due to the finite RDSONs of the MOSFETs and parasitic capacitances. At light load, this loss is prominent and efficiency is therefore very low. ETA1090 employs a proprietary control scheme that improves efficiency in this situation by enabling the device into a power saving mode during light load, thereby extending the range of high efficiency operation.

#### Short-Circuit Protection

Unlike most step-up converters, the ETA1090 allows for short circuits on the output. In the event of a short circuit, the device first turns off the NMOS when the sensed current reaches the current limit. After  $V_{\text{OUT}}$  drops below  $V_{\text{IN}}$  the device then enters a linear charge period with the current limited same as with the start-up period. In addition, the thermal shutdown circuits disable switching if the die temperature rises above 150°C.

#### Down Mode (V<sub>IN</sub>>V<sub>OUT</sub>) Operation

The ETA1090 will continue to supply the output voltage even when the input voltage exceeds the output voltage. Since the PMOS no longer acts as a low-impedance switch in this mode, power dissipation increases within the IC to cause a sharp drop in efficiency. Limit the maximum output current to maintain an acceptable junction temperature.

#### **Output Voltage Setting**

The ETA1090 has an internal reference voltage set at 0.6V as a feedback voltage for setting external output voltage. By connecting a resistor (R1) between Vout and FB, and a resistor (R2) between FB and GND, one can set the output voltage by following equation, and please make sure the output voltage is set higher than the maximum input voltage

Vout =  $0.6 \times (R1+R2)/R2$

### Switching Peak Current Setting

The ETA1090 allows one to set the switching peak current by external resistor (Riset). The switching peak current limit is more like an input current limit given a fixed inductor value. If one need an output current limit, input voltage, output voltage, and efficiency have to be all taken into account to calculate the input current at first. The switching peak current setting follows the equation: Ipeak=(180/Riset)\*1000 (A)

## **PCB GUIDELINES**

A typical ETA1090 demo board is shown below, where you may find only a few peripheral devices are needed. The BAT printed on the PCB is actually the Vin terminal. Cb1 and Cb2 are the 2 input capacitors. Co1 and Co2 are the 2 output capacitors. Rfb1 and Rfb2 are used to setting the output voltage while the Cf (feed-forward capacitor) may help the loop stability. But Cf is not required, one may add it when needed.

Please place the 2 output capacitors (Co1, and Co2) as close to the chip (U1) as possible. The input capacitor Cb1 is also recommended to be placed close to chip.

#### THERMAL CONSIDERATIONS

As the ETA1090 has a power MOSFET with internal current limit up to 6A, heat dissipation is always needed to be considered when designing the PCB for such high-power step-up converter. ETA1090 employs a package of DFN3x3-12 with only 3 °C/W thermal resistance from chip to its thermal pad. So it is crucial for one to lay a large area of copper (in most case, it is the large ground plane), directly contacting the thermal pad of the chip through more than 2 large vias from bottom, to spread the heat away to the ambient environment as fast as possible.

A thicker copper foil is always recommended to help the heat dissipation, so a PCB with 2oz copper thickness is a much better choice than that of 1oz copper.

# **BLOCK DIAGRAM**

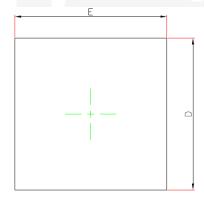

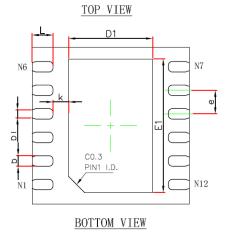

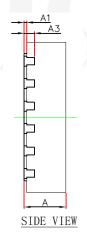

# PACKAGE OUTLINE

Package: DFN3x3-12

| SYMBOL | MILLIMETER |      |  |  |  |  |

|--------|------------|------|--|--|--|--|

| SYMBOL | MIN        | MAX  |  |  |  |  |

| Α      | 0.70       | 0.80 |  |  |  |  |

| A1     | 0.00       | 0.05 |  |  |  |  |

| A3     | 0.203REF   |      |  |  |  |  |

| D      | 2.90       | 3.10 |  |  |  |  |

| Е      | 2.90       | 3.10 |  |  |  |  |

| D1     | 1.45       | 1.70 |  |  |  |  |

| E1     | 2.40       | 2.65 |  |  |  |  |

| b      | 0.15       | 0.28 |  |  |  |  |

| b1     | 0.150REF   |      |  |  |  |  |

| е      | 0.450BSC   |      |  |  |  |  |

| k      | 0.300REF   |      |  |  |  |  |

| L      | 0.30       | 0.50 |  |  |  |  |

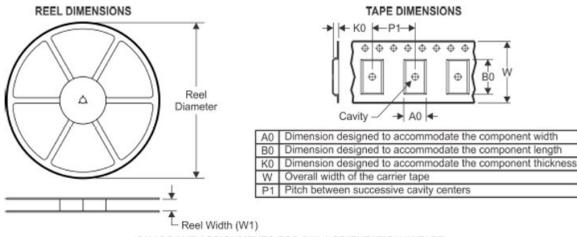

# TAPE AND REEL INFORMATION

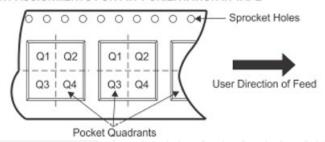

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device     | Package Type | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|--------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ETA1090D3M | DFN3x3-12    | 12   | 5000 | 330                      | 12.4                     | 3.35       | 3.35       | 1.13       | 8          | 12        | Q1               |