# 60V, 3A Non-Synchronous Step-Down DCDC Converter With High Efficiency Sleep Mode

### 1 FEATURES

- Wide Input Range: 4.5V-60V

- Up to 3A Continuous Output Current

- 0.75V ± 1% Feedback Reference Voltage

- Integrated 150mΩ High-Side Power MOSFET

- Adjustable Frequency 200KHz to 2.0MHz

- Pulse Skipping Mode (PSM) at Light Load

- 100uA Quiescent Current in Sleep Mode

- Programmable Soft-start Time

- Available in an eSOP-8L Package

### 2 APPLICATIONS

- 12-V, 24-V, 48-V Industry Power System

- Industrial Automation and Motor Control

- Vehicle Accessories

### 3 ORDERING INFORMATION

| TYPE        | MARKING | PACKAGE |

|-------------|---------|---------|

| GBI1633SMAR | 1633    | eSOP-8  |

### 4 DESCRIPTION

The GBI1633 is 60V, 3A buck converter with an integrated 150 m $\Omega$  high-side MOSFET. The GBI1633 has wide input range from 4.5V to 60V, the GBI1633 is suitable for variable applications which is from unregulated sources, like industrial or automotive applications. The device adopts peak current mode and supports a wide adjustable switching frequency range, setting by external resistor. The quiescent current of this device is 100uA in sleep mode and the shutdown current is 1uA, making it suitable for battery-powered system. The device integrates protections, like cycle-by-cycle current limit, thermal shutdown protection, output over-voltage protection and input voltage under-voltage protection. It's available in an 8-pin eSOP-8L package.

### 5 TYPICAL APPLICATION

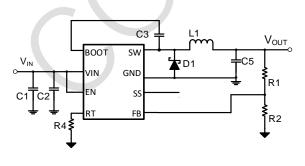

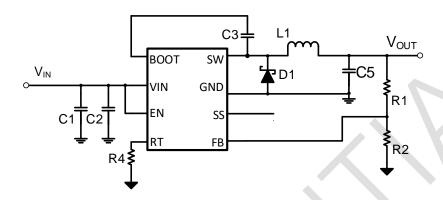

Simplified Schematic

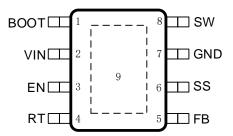

# 6 PIN CONFIGURATION AND FUNCTIONS

Top View: GBI1633 eSOP-8L

| PIN C          | UT  | .,, | DIN FUNCTION                                                                                                                                                                                                                                                                    |  |

|----------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME           | NO. | 1/0 | PIN FUNCTION                                                                                                                                                                                                                                                                    |  |

| ВООТ           | 1   | I   | Power supply for the high-side power MOSFET gate driver. Must connect a 0.1uF or greater ceramic capacitor between BOOT pin and SW pin.                                                                                                                                         |  |

| VIN            | 2   | I   | Power supply input. Must be locally bypassed.                                                                                                                                                                                                                                   |  |

| EN             | 3   | I   | Enable logic input. Floating the pin enables the device. This pin supports high voltage up to VIN supply. The device has precision enable thresholds 1.21V rising / 1.05V falling for programmable UVLO threshold. The hysteresis is programmable by external resistor network. |  |

| RT             | 4   | I   | Resistor Timing.                                                                                                                                                                                                                                                                |  |

| FB             | 5   | I   | Buck converter output feedback sensing voltage. Connect a resistor divider from VOUT node to FB pin and from FB pin to GND to set up output voltage. The device regulates FB to the internal reference of 0.75V typically.                                                      |  |

| SS             | 6   | 1   | Connect to a capacitor to set soft-start time                                                                                                                                                                                                                                   |  |

| GND            | 7   | G   | Ground.                                                                                                                                                                                                                                                                         |  |

| SW             | 8   | 0   | Switching node of the buck converter.                                                                                                                                                                                                                                           |  |

| Thermal<br>Pad | 9   | G   | Must be grounded in PCB layout.                                                                                                                                                                                                                                                 |  |

### 7 SPECIFICATIONS

### 7.1 ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature unless otherwise noted

| DESCRIPTION PARAMETER |                  |      | MAX | UNIT |

|-----------------------|------------------|------|-----|------|

|                       | VIN, EN to GND   | -0.3 | 65  | V    |

| Input Voltage         | FB to GND        | -0.3 | 6.5 | V    |

| Input Voltage         | SS to GND        | -0.3 | 6.5 | V    |

|                       | RT to GND        | -0.3 | 6.5 | V    |

| Output Voltage        | SW to GND        | -3   | 65  | V    |

| Output Voltage        | BOOT to SW       |      | 6.5 | V    |

| Junction temperature  | T <sub>J</sub>   | -40  | 150 | °C   |

| Storage temperature   | T <sub>STG</sub> | -65  | 150 | °C   |

### 7.2 ESD RATINGS

| PARAMETER        | DEFINITION                                     | MIN | MAX   | UNIT |

|------------------|------------------------------------------------|-----|-------|------|

|                  | Human Body Model (HBM), per ANSI-JEDEC-JS-001- |     | ±2000 | V    |

| N/               | 2014 specification, all pins (1)               |     | 12000 | V    |

| V <sub>ESD</sub> | Charged Device Model (CDM), per ANSI-JEDEC-JS- |     | ±500  | V    |

|                  | 002-2014 specification, all pins (1)           |     | ±300  | V    |

<sup>(1)</sup> HBM and CDM stressing are done in accordance with the ANSI/ESDA/JEDEC JS-001-2014 specification

# 7.3 RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER       | DEFINITION                           | MIN | MAX  | UNIT |

|-----------------|--------------------------------------|-----|------|------|

| V <sub>IN</sub> | Supply voltage range                 | 4.5 | 60   | V    |

| BOOT to SW      |                                      | 0   | 6    | V    |

| FB, EN, PG      |                                      | 0   | 6    | V    |

| EN              |                                      | 0   | 60   | V    |

| $f_{SW}$        | Switching frequency range at RT mode | 200 | 2000 | kHz  |

| TJ              | Operating junction temperature       | -40 | 125  | °C   |

## 7.4 THERMAL INFORMATION

| PARAMETER        | THERMAL METRIC                               | eSOP-8L | UNIT |

|------------------|----------------------------------------------|---------|------|

| R <sub>0JA</sub> | Junction to ambient thermal resistance       | 42.5    | °C/W |

| $R_{\theta JC}$  | Junction to case thermal resistance          | 56.1    | °C/W |

| Ψյв              | Junction to board characterization parameter | 25.4    | °C/W |

# 7.5 ELECTRICAL CHARACTERISTICS

$V_{IN}$ =EN=4.5V~60V,  $T_J$ =-40°C~125°C, typical values are tested under 25°C.

| SYMBOL                | PARAMETER                       | TEST CONDITION                                                          | MIN | TYP  | MAX | UNIT |

|-----------------------|---------------------------------|-------------------------------------------------------------------------|-----|------|-----|------|

| Power Su              | pply                            |                                                                         |     |      |     |      |

| V <sub>IN</sub>       | Operating input voltage         |                                                                         | 4.5 |      | 60  | ٧    |

| W                     | Input UVLO                      | V <sub>IN</sub> rising                                                  |     | 4.2  | 4.4 | ٧    |

| $V_{\text{IN\_UVLO}}$ | Hysteresis                      |                                                                         |     | 350  |     | mV   |

| I <sub>SHDN</sub>     | Shutdown current                | EN=0, No load, 4.5V≤V <sub>IN</sub> ≤60V                                |     | 1    |     | uA   |

| ΙQ                    | Quiescent current               | EN=floating, No load, No switch, $4.5V \le V_{IN} \le 60V$ , BOOT-SW=5V |     | 100  |     | uA   |

| Enable ar             | nd Feedback                     |                                                                         |     |      |     |      |

| V <sub>EN_H</sub>     | Enable high threshold           |                                                                         |     | 1.21 |     | ٧    |

| V <sub>EN_L</sub>     | Enable low threshold            |                                                                         |     | 1.05 |     | ٧    |

| V <sub>FB</sub>       | Feedback Voltage                |                                                                         |     | 0.75 |     | ٧    |

| Power M               | OSFET                           |                                                                         |     |      |     |      |

| R <sub>DSON_H</sub>   | High side FET on-<br>resistance |                                                                         |     | 150  |     | mΩ   |

| Switching             | Characteristics                 |                                                                         |     |      |     |      |

|                       | Switching frequency             | R <sub>T</sub> =50k                                                     |     | 470  |     | KHz  |

| f <sub>SW</sub>       | Maximum switching frequency     |                                                                         |     | 2.0  |     | MHz  |

| ton_min               | Minimum on-time                 |                                                                         |     | 100  |     | ns   |

| D <sub>MAX</sub>      | Maximum duty cycle              | f <sub>sw</sub> =500kHz                                                 |     | 95   |     | %    |

| Soft Start            | Time and Protection             |                                                                         | •   |      |     | •    |

| t <sub>SS</sub>       | Internal soft-start time        | GBI1633 5                                                               |     |      | ms  |      |

| I <sub>SS</sub>       | Soft start current              | GBI1634                                                                 |     | 4    |     | uA   |

| I <sub>LIM_HSD</sub>  | HSD peak current limit          | V <sub>IN</sub> =24V                                                    |     | 4.75 |     | Α    |

| SYMBOL             | PARAMETER            | TEST CONDITION | MIN | TYP | MAX | UNIT |

|--------------------|----------------------|----------------|-----|-----|-----|------|

|                    | Thermal shutdown     |                |     | 170 |     |      |

| T <sub>SD</sub>    | threshold            |                |     | 170 |     | °C   |

|                    | Hysteresis           |                |     | 30  |     |      |

| Output Vo          | oltage Protection    |                |     |     |     |      |

| V                  | Output over voltage  |                |     | 108 |     | %    |

| $V_{OVP\_H}$       | protection rising    |                |     | 100 | 100 | 70   |

| V <sub>OVP_L</sub> | Output over voltage  |                |     | 102 | 103 | %    |

|                    | protection falling   |                |     | 103 |     | 70   |

| V                  | Output under voltage |                |     | 92  |     | %    |

| V <sub>UVP_L</sub> | protection falling   |                |     | 92  |     | 70   |

| V <sub>UVP_H</sub> | Output under voltage |                |     | 0.7 |     | %    |

|                    | protection rising    |                |     | 97  |     | 70   |

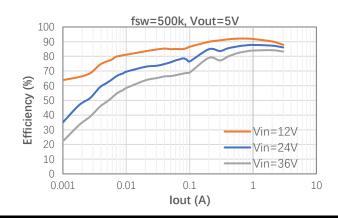

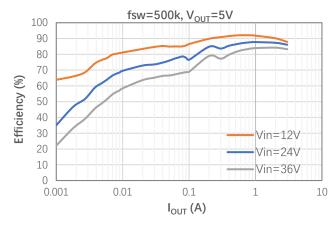

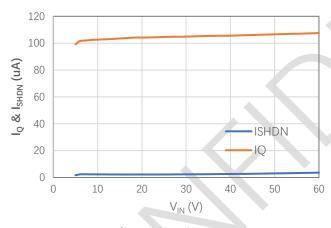

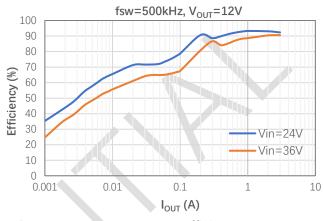

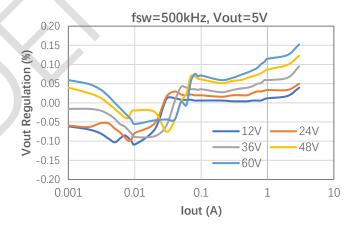

### 7.6 TYPICAL CHARACTERISTICS

$V_{IN}$ =24V,  $f_{SW}$ =500kHz, L=10uH,  $C_{OUT}$ =47uF,  $T_A$ = 25°C.

Figure 1 Power Efficiency

Figure 3 IQ & Ishdn

Figure 2 Power Efficiency

Figure 4 V<sub>OUT</sub> Vs. Load Regulation

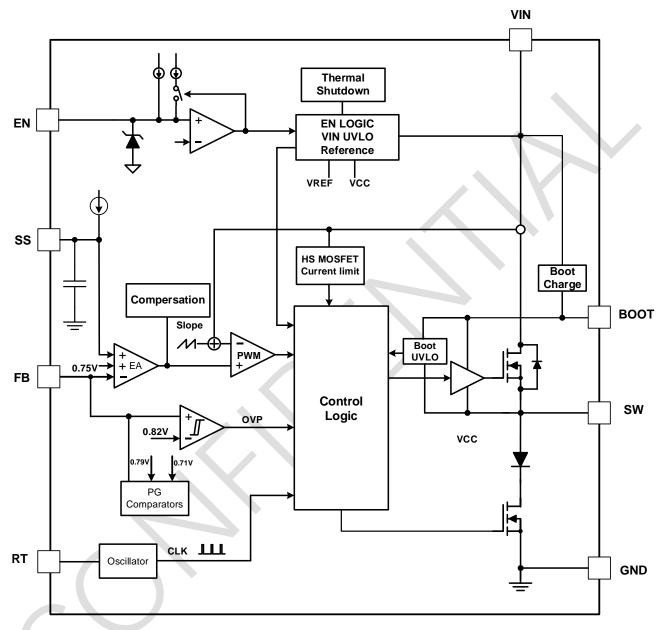

# 8 FUNCTION BLOCK DIAGRAM

Figure 5 Block Diagram of GBI1633

### 9 DISCRIPTION

### 9.1 Overview

The GBI1633 is a 60V, 3A buck converter with an integrated 150 m $\Omega$  high-side MOSFET. With a wide input range from 4.5V to 60V, the device adopts peak current mode and supports a wide adjustable switching frequency range from 200kHz to 2.0MHz setting by external resistor.

The quiescent current of this device is 100uA in sleep mode and the shutdown current is 1uA. The GBI1633 adopts adjustable soft-start time by connecting a capacitor.

The device has a default input start-up voltage of 4.2V with 350mV hysteresis. The EN pin is a high-voltage pin with a precision threshold that can be used to adjust the input voltage lockout thresholds with two external resistors to meet accurate higher UVLO system requirements. Floating EN pin enables the device. Connecting EN pin to VIN directly starts up the device automatically.

The device integrates protections, like cycle-by-cycle current limit, thermal shutdown protection, output over-voltage protection and input voltage under-voltage protection. The device also supports monolithic startup with pre-biased output condition.

It's available in an 8-pin eSOP-8L package.

### 9.2 Peak Current Mode Control

The GBI1633 employs fixed frequency peak current mode control. An internal clock initiates turning on the integrated high-side power MOSFET in each cycle, then inductor current rises linearly. When the current through high-side MOSFET reaches the threshold level set by the internal compensation voltage of the internal error amplifier, the high-side MOSFET turns off. When the high-side MOSFET turns off, the inductor current discharges through the external diode till the next clock cycle begins.

The integrated error amplifier and the internal compensation builds up the feedback loop to regulates the output voltage to the reference. The error amplifier comparing the voltage of the FB pin with an internal reference voltage of 0.75V. The load current increasement reduces the feedback voltage which is relative to a voltage raise of the error amplifier output till the average inductor current matches the increased load current.

The device also integrates an internal slope compensation circuitry to prevent sub-harmonic oscillation when duty cycle is greater than 50% for a fixed frequency peak current mode control.

# 9.3 Pulse Skipping Mode (PSM)

The GBI1633 operates in Pulse Skipping Mode (PSM) with light load current to improve efficiency. A

decrease of the load current leads an increasement in the feedback voltage which yields down the compensation voltage. When the compensation voltage drops to a low clamp threshold, the PSM is triggered. During the skipping period, the discharge of output capacitor leads the output voltage drop which makes the FB voltage decay. Once the FB voltage drops lower than the reference voltage and the compensation voltage rises above the low clamp threshold, the integrated high-side MOSFET turns on in next clock pulse. After several switching cycles with typical 0.2A peak inductor current, the internal compensation voltage drops and is clamped again and pulse skipping mode repeats if the output continues light loaded.

This PSM helps achieving higher efficiency by skipping cycles to reduce switching power loss and gate drive charging loss. Regarding to improve efficiency further, the quiescent current is 100uA during skipping period with no switching.

### 9.4 VIN Power

The GBI1633 is designed to operate from an input voltage supply range between 4.5V to 60V, at least 0.1uF and 10uF decoupling ceramic cap are recommended to bypass the supply noise. If the input supply locates more than a few inches from the converter, an additional 47uF electrolytic bulk capacitor may be required in addition to the local ceramic bypass capacitors.

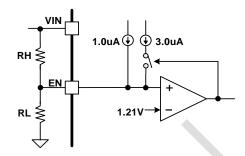

# 9.5 Under Voltage Lockout Threshold and Enable

The EN pin of GBI1633 is a high voltage pin which can be connected to VIN directly to start-up the device. The GBI1633 is enabled when the EN pin voltage higher than the enable threshold of 1.21V and disabled when the EN pin voltage lower than 1.05V. Grace to the internal 1.0uA pull-up current, the device is default enabled when the EN pin floats.

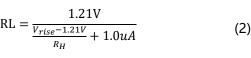

The Under Voltage Lock Out (UVLO) default startup threshold is typical 4.1V with VIN rising and shutdown threshold is 3.8V with VIN falling. The more accurate UVLO threshold can be programmed through the precision enable threshold of EN pin. Connect an external resistor divider (RL and RH) shown in Figure 7 from VIN to EN. The UVLO rising and falling threshold can be calculated by Equation 1 and Equation 2 respectively.

$$RH = \frac{V_{rise} - V_{fall}}{3.0uA} \tag{1}$$

$$RL = \frac{1.21V}{\frac{V_{rise} - 1.21V}{R_H} + 1.0uA}$$

(2)

Figure 6 System UVLO by EN divider

#### where

- V<sub>rise</sub> is rising threshold of Vin UVLO

- V<sub>fall</sub> is falling threshold of Vin UVLO

# 9.6 Bootstrap Voltage Regulator

An external bootstrap capacitor between BOFOT pin and SW pin powers floating high-side power MOSFET gate driver. The bootstrap capacitor voltage is charged from an integrated voltage regulator when highside power MOSFET is off.

The floating supply (BOOT to SW) UVLO threshold is 2.7V rising and hysteresis of 350mV. When the converter operates with high duty cycle or prolongs in sleep mode for certain long time, the required time interval to recharging bootstrap capacitor is too long to keep the voltage at bootstrap capacitor sufficient. When the voltage across bootstrap capacitor drops below 2.35V, BOOT UVLO occurs.

# 9.7 Output Voltage

The GBI1633 regulates the internal reference voltage at 0.75V with ±1% tolerance over the operating temperature and voltage range.

The output voltage is set by a resistor divider from the output node to the FB pin. It is recommended to use 1% tolerance or better resistors. Use Equation 3 to calculate resistance of resistor dividers. To improve efficiency at light loads, larger value resistors are recommended. However, if the value is higher, the regulator will be more noise sensitive. RFB BOT in the range of  $10k\Omega$  to  $100k\Omega$  is recommended for most application.

$$R_{FB\_TOP} = \left(\frac{V_{OUT}}{0.75V} - 1\right) * R_{FB\_BOT}$$

(3)

where

- R<sub>FB TOP</sub> is the resistor connecting the output to the FB pin.

- R<sub>FB BOT</sub> is the resistor connecting the FB pin to the ground.

# 9.8 Switching Frequency

The switching frequency of the GBI1633 is set by placing a resistor between RT pin and the GND. The RT pin is not allowed to be left floating or shorted to the GND.

In resistor setting frequency mode, use Equation 4. to determine the resistance for a switching frequency needed.

$$RT(K\Omega) = \frac{25000}{fsw(KHz)} \tag{4}$$

where, fsw is switching clock frequency.

# 9.9 Programmable Soft-Start

GBI1633 features programmable soft-start time to avoid inrush current during start-up stage by placing a soft-start capacitor from SS pin to ground. The soft-start time is easily calculated following equation 5.

$$C_{soft-start} = t_{ss} * \frac{4uA}{0.75V} \tag{5}$$

Where:

- C<sub>soft-start</sub> is the soft-start capacitor connected from SS pin to the ground

- t<sub>ss</sub> is the soft-start time

# 9.10 Overcurrent and Short Circuit Protection

The GBI1633 adopts the peak current mode control. In the overcurrent momentum, the output voltage is yield down by heavy load and the error amplifier drives the compensation voltage high to increase the switching current. As the error amplifier output increases, it will be clamped internally, and the high-side current is clamped by a maximum peak current threshold. The peak current threshold is constant over the full duty cycle range.

When the output overcurrent or short circuit occurs, the device will trigger a frequency foldback by dividing the oscillator frequency with a pre-set frequency foldback factor to protect itself by increasing the switching frequency and the off time of high-side MOSFET. This will lead more time for the inductor current to ramp down. Otherwise, a lower switching frequency contributes on lower switching loss and avoiding overheating and other potential damages.

The frequency foldback factor is relative with the FB pin voltage.

Table 1 Frequency Foldback Factor vs VFB

|--|

| 75% V <sub>REF</sub> | 2 |

|----------------------|---|

| 50% V <sub>REF</sub> | 4 |

| 25% V <sub>REF</sub> | 8 |

# 9.11 Overvoltage Protection

The GBI1633 implements the overvoltage protection (OVP) circuitry to minimize output voltage overshoot during load transient, recovering from output fault condition or light load transient. When the FB pin voltage reaches the rising OVP threshold which is typically 109% of  $V_{REF}$ , the high-side MOSFET will be turned off immediately which make the device under OVP. When the FB pin voltage drops below the falling OVP threshold, the high-side MOSFET is turned on and resumed normal operation. The falling OVP threshold is typically 105% of  $V_{REF}$ .

## 9.12 Thermal Shutdown

The GBI1633 features an internal thermal shutdown circuit to protect the device from the damage during excessive heat and power dissipation conditions. The thermal shutdown circuit will be asserted when the junction temperature exceeds typically 170°C. When the junction temperature falls below 150C, the device restarts with internal soft start phase.

### 10 APPLICATION INFORMATION

### **Typical Application**

Figure 7 24V INPUT, 5V 3A OUTPUT

**Table 2. Design Parameters**

| Design Parameters                       | Example Value      |

|-----------------------------------------|--------------------|

| Input Voltage                           | 24V typical, 7~60V |

| Output Voltage                          | 5V                 |

| Output Current                          | 3A                 |

| Output voltage ripple (peak to peak)    | <50mV              |

| Overshoot/Undershoot range (0.75~2.25A) | 5%                 |

| Input Voltage ripple (peak to peak)     | <400mV             |

| Switching Frequency                     | 500kHz             |

# 10.1 Set Output Voltage

The GBI1633 output voltage can be easily set up using a resistor divider network R1 and R2 as shown in the typical application circuit Figure 9. Use Equation (6) to calculate the resistor divider values.

$$R1 = \frac{(V_{OUT} - 0.75) \times R2}{0.75} \tag{6}$$

In this design example the Vout is 5V. Set the resistor R2 value to be approximately 10k.

$$R1 = \frac{(V_{OUT} - 0.75) \times R2}{0.75} = \frac{(5 - 0.75) \times 10k\Omega}{0.75} = 56.6 \ k\Omega$$

Slightly increasing or decreasing R1 to a closest available resistance, the 56  $k\Omega$  is selected.

# 10.2 Set Switching Frequency

The GBI1633 switching frequency is able to be set-up by placing a local resistor from RT/SYNC pin to GND. Use following equation to calculate the resistor value.

$$R4(K\Omega) = \frac{25000}{fsw(KHz)} = \frac{25000}{500} = 50 \,k\Omega \tag{7}$$

For 500kHz switching frequency, the R4 is 50 k $\Omega$ .

# 10.3 Input Capacitor Selection

For good input voltage filtering, choose low-ESR ceramic capacitors. A X7R ceramic capacitor 4.7uF to  $10\mu$ F is recommended for the decoupling capacitor and a  $0.1\mu$ F ceramic bypass capacitor is recommended to be placed as close as possible to the VIN pin. These capacitors must be rated for 100V.

For this design, two 2.2uF X7R capacitors and one 0.1uF capacitor rated 100V is recommended.

The input voltage ripple can be calculated by using Equation (8) to calculate the input voltage ripple:

$$\Delta V_{IN} = \frac{I_{OUT}}{C_{IN} \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) = \frac{3A}{4.4uF \times 500k} \times \frac{5V}{24V} \times \left(1 - \frac{5V}{24V}\right) = 224 \ mV \tag{8}$$

Where:

- C<sub>IN</sub> is the input capacitor value

- f<sub>sw</sub> is the converter switching frequency

- I<sub>OUT</sub> is the maximum load current

# 10.4 Inductor Selection

The performance of inductor affects the power supply's steady state operation, transient behavior, loop stability, and buck converter efficiency. The critical parameters of inductor is the inductance, the DC resistance (DCR), the saturation current and the RMS current.

Use following equation to the minimum inductance:

$$L_{MIN} = \frac{V_{OUT} \times (V_{INMAX} - V_{OUT})}{V_{INMAX} \times K_{IND} \times I_{OUT} \times f_{SW}}$$

(9)

Where

- V<sub>OUT</sub> is output voltage

- K<sub>IND</sub> is the Ripple Ration of the inductor ripple current (∆iL/I<sub>OUT</sub>), 0.4 is recommended here

- V<sub>INMAX</sub> is the maximum input voltage

- f<sub>SW</sub> is the converter switching frequency

- I<sub>OUT</sub> is the output current

In this design example:

$$L > L_{MIN} = \frac{V_{OUT} \times (V_{INMAX} - V_{OUT})}{V_{INMAX} \times K_{IND} \times I_{OUT} \times f_{SW}} = \frac{5V \times (60V - 5V)}{60V \times 0.4 \times 3A \times 500KHz} = 7.64 \ uH$$

Generally, the Inductor values can have  $\pm 20\%$  or even  $\pm 30\%$  tolerance with no current bias. When the inductor current approaches saturation level, its inductance can decrease 20% to 35% from the value at 0-A current depending on how the inductor vendor defines saturation. When selecting an inductor, choose its rated current especially the saturation current larger than its peak current during the operation. The peak switching current of inductor is calculated in equation 11:

$$I_{LPEAK} = I_{OUT} + K_{IND} \times \frac{I_{OUT}}{2} = 3A + 0.4 \times \frac{3A}{2} = 3.6 A$$

With a minimum inductance of 7.64uH and the peak current of 3.6A, the inductor of WE-7447714100 is selected with 10uH inductance,  $23m\Omega$  DRC, 5A saturation current.

# 10.5 Output Capacitor

The output capacitor must be chosen carefully with the reason that this capacitor value determines the regulator pole, the output voltage ripple, and how the regulator responds to a large change in load current. Generally, choose a low-ESR output capacitor like a ceramic capacitor from X5R or X7R family to get small output voltage ripple.

From the required output voltage ripple (<50mV), use the Equation 10 to calculate the minimum required effective capacitance, C<sub>OUT</sub>.

$$C_{OUT} > \frac{\Delta I_{LPP}}{8 \times V_{OUT\_Ripple} \times f_{SW}} = \frac{K_{IND} \times I_{OUT}}{8 \times V_{OUT\_Ripple} \times f_{SW}}$$

(10)

The allowed maximum ESR of the output capacitor is calculated by the equation 11.

$$R_{ESR} < \frac{V_{OUT\_Ripple}}{k_{IND} \times I_{OUT}} \tag{11}$$

Where

- V<sub>OUT Ripple</sub> is output voltage ripple caused by charging and discharging of the output capacitor.

- k<sub>IND</sub> is the Ripple Ration of the inductor ripple current (∆iL/I<sub>OUT</sub>), 0.4 is recommended here

- I<sub>OUT</sub> is the maximum output current

- $f_{SW}$  is the converter switching frequency.

In this design, V<sub>OUT\_Ripple</sub> is smaller than 50mV, f<sub>SW</sub> is 500kHz, I<sub>OUT</sub> is 3A and K<sub>IND</sub> is 0.4:

$$C_{OUT} > \frac{0.4 \times 3A}{8 \times 50 mV \times 500 k} = 6 uF$$

$$R_{ESR} < \frac{50mV}{0.4 \times 3A} = 41.7 \ m\Omega$$

In buck converter, higher capacitor values can be used to improve the load transient response. Normally the converter control loop needs to take some switching clock cycles to respond to the output voltage changes. The output capacitors must be relatively large enough to charge or discharge current to maintain the output voltage within the specified range in 3 clock cycles. The following two Equations are used to calculate the minimum capacitance to keep the undershoot and overshoot voltages within a specified range.

$$C_{OUT} > \frac{3 \times (I_{TOH} - I_{TOL})}{f_{SW} \times V_{OUS}} \tag{12}$$

$$C_{OUT} > \frac{I_{TOH}^2 - I_{TOL}^2}{(V_{OUT} + V_{OOS})^2 - V_{OUT}^2} \times L \tag{13}$$

Where

- I<sub>TOH</sub> is the high level of output current during load transient

- I<sub>TOL</sub> is the low level of output current during load transient

- V<sub>OUS</sub> is the undershoot voltage

- V<sub>OOS</sub> is the overshoot voltage

- L is the inductance of inductor in design

- *f*<sub>SW</sub> is the converter switching frequency.

For this design example:

$$C_{OUT} > \frac{3 \times (I_{TOH} - I_{TOL})}{f_{SW} \times V_{OUS}} = \frac{3 \times (2.25A - 0.75A)}{500kHz \times 250mV} = 36 uF$$

$$C_{OUT} > \frac{2.25A^2 - 0.75A^2}{(5V + 250mV)^2 - 5^2} \times 8.2uH = 14.4 uF$$

Therefore, a X7R capacitor of 47uF with 16V DC rating and 15mΩ ESR is selected

### 10.6 Catch Diode

The GBI1633 requires an external catch diode between the SW pin and GND. The critical parameters of this catch diode are the reverse voltage, the peak current, the forward voltage and the junction capacitance. Generally, the reverse voltage rating equal to or greater than the maximum input voltage. The peak current must be greater than the maximum inductor current. Lower forward voltage and smaller junction

capacitance yields higher efficiency and lower power dissipation. The Schottky diodes are typically good choose as the catch diode.

In this design example, the B560C-13-F is selected with 60V reverse voltage, 5A maximum current, 0.7V forwards voltage and 300pF junction capacitance.

The power dissipation is calculated as in following equation

$$P_{DMAX} = \frac{(V_{INMAX} - V_{OUT}) \times I_{OUT} \times V_{fd}}{V_{INMAX}} + \frac{C_j \times f_{SW} \times (V_{INMAX} + V_{fd})^2}{2}$$

(14)

Where

- V<sub>INMAX</sub> is the maximum input voltage

- I<sub>OUT</sub> is the output current

- V<sub>OUT</sub> is the output voltage

- f<sub>SW</sub> is the switching frequency

- V<sub>fd</sub> is the forward voltage

In this design example:

$$P_{DMAX} = \frac{(60V - 5V) \times 3A \times 0.7V}{60V} + \frac{300pF \times 500kHz \times (60V + 0.7V)^2}{2} = 2.2 W$$

# 10.7 Bootstrap Capacitor

For proper operation of the device, a 0.1uF ceramic capacitor of X5R or X7R must be placed between the SW pin to the BOOT pin. The DC rating of this capacitor is must be 10V or higher voltage level.

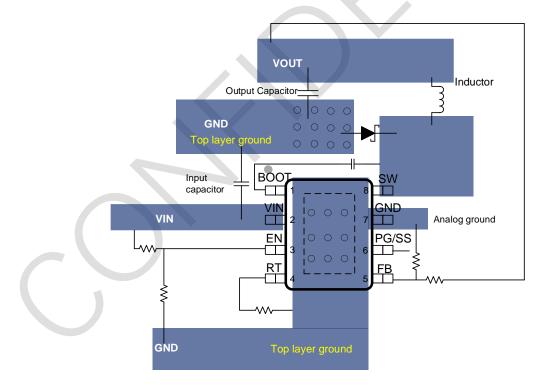

# 11 Layout Guideline

Layout is critical for proper operation. Please follow the layout guidelines.

- The power ground is very critical. The power trace should take lowest impedance as possible and the ground area should be sufficient and event to optimize thermal.

- 2. The GND Pin should be connected directly to the thermal pad under the IC, 8mil Max thermal via recommended.

- 3. Place the bypass input capacitor with low ESR as close as possible to the VIN pin and GND. The bypassing loop from VIN terminal to the GND should be as short as possible.

- 4. The RT is sensitive to noise. The RT resistor should be placed as close as possible to the RT pin with minimum trace length to the GND.

- 5. The inductor should be located as close as possible to the SW pin for reducing magnetic and electrostatic noise

- 6. The feedback resistor divider should be placed close to the FB pin.

- 7. The ground connected to the diode, input capacitors and output capacitors should be tied to the system ground plane in only one spot to minimize conducted noise to the system ground plane

- 8. Four-layer layout is strongly recommended for better thermal performance.

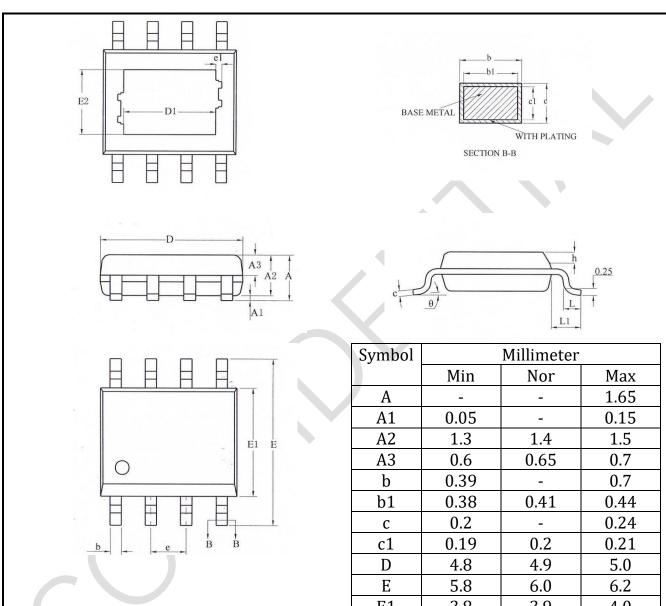

# PACKAGE INFORMATION (eSOP-8L Package)

| LF Size | D1  | E2   | e1   |

|---------|-----|------|------|

| 95*130  | 3.1 | 2.21 | 0.16 |

| Symbol | Millimeter |      |      |

|--------|------------|------|------|

|        | Min        | Nor  | Max  |

| Α      | -          | -    | 1.65 |

| A1     | 0.05       | -    | 0.15 |

| A2     | 1.3        | 1.4  | 1.5  |

| A3     | 0.6        | 0.65 | 0.7  |

| b      | 0.39       | -    | 0.7  |

| b1     | 0.38       | 0.41 | 0.44 |

| С      | 0.2        | -    | 0.24 |

| c1     | 0.19       | 0.2  | 0.21 |

| D      | 4.8        | 4.9  | 5.0  |

| Е      | 5.8        | 6.0  | 6.2  |

| E1     | 3.8        | 3.9  | 4.0  |

| e      | 1.27BSC    |      |      |

| h      | 0.25       | -    | 0.5  |

| L      | 0.5        | 0.6  | 8.0  |

| L1     | 1.05REF    |      |      |

| θ      | 0          | -    | 8°   |

|        |            |      |      |