# S26KL512S, S26KS512S, S26KL256S, S26KS256S, S26KL128S, S26KS128S

# 512 Mb (64 MB)/256 Mb (32 MB)/ 128 Mb (16 MB) HYPERFLASH™ Family

### HYPERBUS™, 3.0 V/1.8 V

### Features

- 3.0 V I/O, 11 bus signals

Single ended clock

- 1.8 V I/O, 12 bus signals

Differential clock (CK, CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Read-write data strobe (RWDS)

HYPERFLASH<sup>™</sup> memories use RWDS only as a Read Data Strobe

- Up to 333 MBps sustained read throughput

- DDR two data transfers per clock

- + 166-MHz clock rate (333 MBps) at 1.8 V  $\rm V_{CC}$

- + 100-MHz clock rate (200 MBps) at 3.0 V  $\rm V_{CC}$

- 96-ns initial random read access time

- Initial random access read latency: 5 to 16 clock cycles

- Sequential burst transactions

- Configurable burst characteristics

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- Linear burst

- Hybrid option: one wrapped burst followed by linear burst

- Wrapped or linear burst type selected in each transaction

- Configurable output drive strength

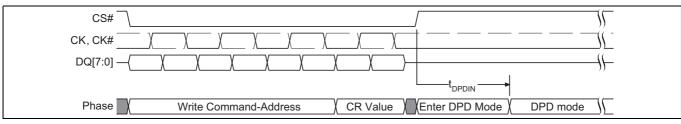

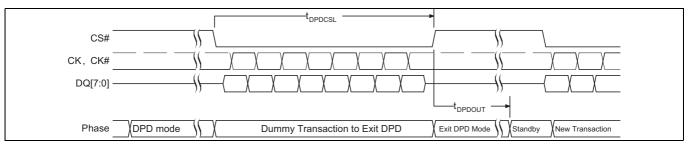

- Low power modes

- Active clock stop during read: 12 mA, no wake-up required

- Standby: 25 µA (typical), no wake-up required

- Deep Power-Down: 8 µA (typical)

- 300 μs wake-up required

- INT# output to generate external interrupt

- Busy to Ready transition

- ECC detection

- RSTO# output to generate system level power-on reset

- User configurable RSTO# LOW period

- 512-byte program buffer

Features

- Sector erase

- Uniform 256-KB sectors

- Optional eight 4-KB parameter sectors (32 KB total)

- Advanced sector protection

- Volatile and non-volatile protection methods for each sector

- Separate 1024-byte one-time program array

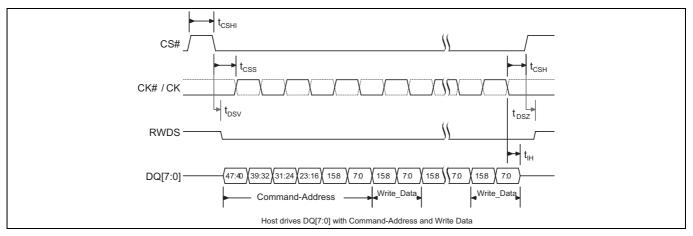

- Operating temperature

- Industrial (-40°C to +85°C)

- Industrial Plus (-40°C to +105°C)

- Extended (-40°C to +125°C)

- Automotive, AEC-Q100 grade 3 (-40°C to +85°C)

- Automotive, AEC-Q100 grade 2 (-40°C to +105°C)

- Automotive, AEC-Q100 grade 1 (-40°C to +125°C)

- ISO/TS16949 and AEC Q100 Certified

- Endurance

- 100,000 program/erase cycles

- Retention

- 20 year data retention

- Erase and program current

- Max peak <<u></u> 100 mA

- Packaging options

- 24-ball FBGA

- Additional features

- ECC 1-bit correction, 2-bit detection

- CRC

Performance summary

### Performance summary

#### **Read access timings**

| Maximum clock rate at 1.8 V V <sub>CC</sub> /V <sub>CC</sub> Q | 166 MHz |

|----------------------------------------------------------------|---------|

| Maximum clock rate at 3.0 V V <sub>CC</sub> /V <sub>CC</sub> Q | 100 MHz |

| Maximum access time, (t <sub>ACC</sub> )                       | 96 ns   |

| Maximum CS# access time to first word @ 166 MHz                | 118 ns  |

#### Typical program / erase times

| Single word programming (2B = 16b)      | 500 μs (~4 KBps)   |

|-----------------------------------------|--------------------|

| Write buffer programming (512B = 4096b) | 475 μs (~1 MBps)   |

| Sector erase time (256 KB = 2 Mb)       | 930 ms (~282 KBps) |

#### **Typical current consumption**

| Burst read (Continuous read at 166 MHz) | 80 mA                      |  |  |  |  |  |

|-----------------------------------------|----------------------------|--|--|--|--|--|

| Power-on reset                          | 80 mA                      |  |  |  |  |  |

| Sector erase current                    | 60 mA                      |  |  |  |  |  |

| Write buffer programming current        | 60 mA                      |  |  |  |  |  |

| Standby (CS# = HIGH)                    | 25 μΑ                      |  |  |  |  |  |

| Deep power down (CS# = LUCU_95°C)       | 30 μA (512 Mb)             |  |  |  |  |  |

| Deep power-down (CS# = HIGH, 85°C)      | 4 μA (all other densities) |  |  |  |  |  |

Table of contents

### Table of contents

| Features                                                                                |    |

|-----------------------------------------------------------------------------------------|----|

| Performance summary                                                                     |    |

| Table of contents                                                                       |    |

| 1 General description                                                                   |    |

| 1.1 DDR center aligned read strobe (DCARS) functionality                                | 7  |

| 1.2 Error detection and correction functionality                                        | 7  |

| 2 Connection diagram                                                                    |    |

| 2.1 FBGA 24-ball 5 × 5 array footprint                                                  | 10 |

| 3 Signal description                                                                    | 11 |

| 4 HYPERBUS™ protocol                                                                    |    |

| 4.1 Command / address bit assignments                                                   |    |

| 4.2 Read operations                                                                     |    |

| 4.3 HYPERFLASH™ Read with DCARS timing                                                  |    |

| 4.4 Write operations                                                                    |    |

| 5 Address space maps                                                                    |    |

| 5.1 Flash memory array                                                                  |    |

| 5.2 Device ID and CFI (ID-CFI) ASO                                                      |    |

| 6 Embedded operations                                                                   |    |

| 6.1 Embedded algorithm controller (EAC)                                                 |    |

| 6.2 Program and erase summary                                                           |    |

| 6.3 Data protection                                                                     |    |

| 7 Device ID and Common Flash Interface (ID-CFI) ASO map                                 |    |

| 7.1 Device ID and Common Flash Interface (ID-CFI) ASO map — standard                    |    |

| 7.2 Device ID and Common Flash Interface (ID-CFI) ASO Map — automotive grade / AEC-Q100 |    |

| 8 Software interface reference                                                          |    |

| 8.1 Command summary                                                                     |    |

| 9 Data integrity                                                                        |    |

| 9.1 Endurance                                                                           |    |

| 9.2 Data retention                                                                      |    |

| 10 Hardware interface                                                                   |    |

| 11 Electrical specifications                                                            |    |

| 11.1 Absolute maximum ratings                                                           |    |

| 11.2 Thermal resistance                                                                 |    |

| 11.3 Latchup characteristics                                                            |    |

| 11.4 Operating ranges                                                                   |    |

| 11.5 DC characteristics (CMOS compatible)                                               |    |

| 11.6 Power-up and power-down                                                            |    |

| 11.7 Power-off with Hardware Data Protection                                            |    |

| 11.8 Power Conservation modes                                                           |    |

| 12 Timing specifications                                                                |    |

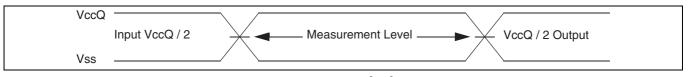

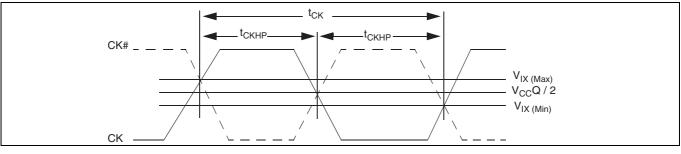

| 12.1 AC test conditions                                                                 |    |

| 12.2 AC characteristics                                                                 |    |

| 13 Embedded algorithm performance                                                       |    |

| 14 Ordering information                                                                 |    |

| 14.1 Ordering part numbers                                                              |    |

| 14.2 Valid combinations — standard                                                      |    |

| 14.3 Valid combinations — automotive grade / AEC-Q100                                   |    |

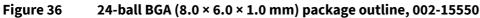

| 15 Package diagram                                                                      |    |

| 15.1 Fortified ball grid array 24-ball 6 × 8 × 1.0 mm (VAA024)                          |    |

| Revision history                                                                        |    |

General description

### 1 General description

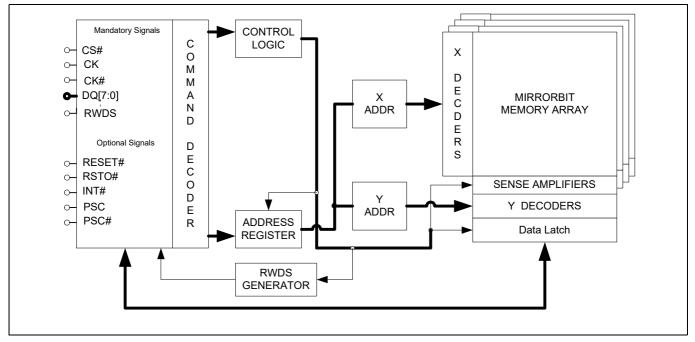

The HYPERFLASH<sup>™</sup> family of products are high-speed CMOS, MIRRORBIT<sup>™</sup> NOR flash devices with the HYPERBUS<sup>™</sup> low signal count DDR interface, that achieves high speed read throughput. The DDR protocol transfers two data bytes per clock cycle on the data (DQ) signals. A read or write access for the HYPERFLASH<sup>™</sup> consists of a series of 16-bit wide, one clock cycle data transfers at the internal HYPERFLASH<sup>™</sup> core and two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals.

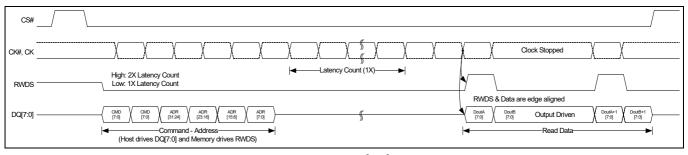

Both data and command/address information are transferred in DDR fashion over the 8-bit data bus. The clock input signals are used for signal capture by the HYPERFLASH<sup>™</sup> device when receiving command/address/data information on the DQ signals. The read data strobe (RWDS) is an output from the HYPERFLASH<sup>™</sup> device that indicates when data is being transferred from the memory to the host. RWDS is referenced to the rising and falling edges of CK during the data transfer portion of read operations.

Command/address/write-data values are center aligned with the clock edges and read-data values are edge aligned with the transitions of RWDS.

Read and write operations to the HYPERFLASH<sup>™</sup> device are burst oriented. Read transactions can be specified to use either a wrapped or linear burst. During wrapped operation, accesses start at a selected location and continue for a configured number of locations in a group wrap sequence. During linear operation accesses start at a selected location and continue in a sequential manner until the read operation is terminated, when CS# returns HIGH. Write transactions transfer one or more 16-bit values.

#### Figure 1 Logic block diagram

The HYPERFLASH<sup>™</sup> family consists of multiple densities, 1.8 V/3.0 V core and I/O, non-volatile, synchronous flash memory devices. These devices have an 8-bit (1-byte) wide DDR data bus and use only word-wide (16-bit data) address boundaries. Read operations provide 16 bits of data during each clock cycle (8 bits on each clock edge). Write operations take 16 bits of data from each clock cycle (8 bits on each clock edge).

General description

Each random read accesses a 32-byte length and aligned set of data called a page. Each page consists of a pair of 16-byte aligned groups of array data called half-pages. Half-pages are aligned on 16-byte address boundaries. A read access requires two clock cycles to define the target half-page address and the burst type, then an additional initial latency. During the initial latency period the third clock cycle will specify the starting address within the target half-page. After the initial data value has been output, additional data can be read from the page on subsequent clock cycles in either a wrapped or linear manner. When configured in linear burst mode, while a page is being burst out, the device will automatically fetch the next sequential page from the MIRRORBIT<sup>™</sup> flash memory array. This simultaneous burst output while fetching from the array allows for a linear sequential burst operation that can provide a sustained output of 333 MBps data rate [1-byte (8-bit data bus) \* 2 (Data on both clock edges) \* 166 MHz = 333 MBps].

#### Table 1S26KS and S26KL address map

| Туре                                                        | Count                                       | Addresses | Notes     |

|-------------------------------------------------------------|---------------------------------------------|-----------|-----------|

| Word address within a half-page (16 byte)                   | 8 (word addresses)                          | A2-A0     | 16 bytes  |

| Word address within write buffer line (512 byte)            | 256 (word addresses)                        | A7-A0     | 512 bytes |

| Half-pages (16 bytes) within erase sector (256 KB)          | 8192 (half-pages)                           | A16-A3    | -         |

| Write buffer lines (512 bytes) within erase sector (256 KB) | 512 (lines)                                 | A16-A8    | -         |

| Total number of erase sectors (256 KB)                      | 256 (512 Mb)<br>128 (256 Mb)<br>64 (128 Mb) | Amax–A17  | -         |

The device control logic is subdivided into two parallel operating sections: the host interface controller (HIC) and the embedded algorithm controller (EAC). The HIC monitors signal levels on the device inputs and drives outputs as needed to complete read and write data transfers with the host system (HYPERFLASH<sup>™</sup> master). The HIC delivers data from the currently entered address map on read transfers; places write transfer address and data information into the EAC command memory; notifies the EAC of power transition, and write transfers. The EAC looks in the command memory, after a write transfer, for legal command sequences and performs the related Embedded Algorithms (EA).

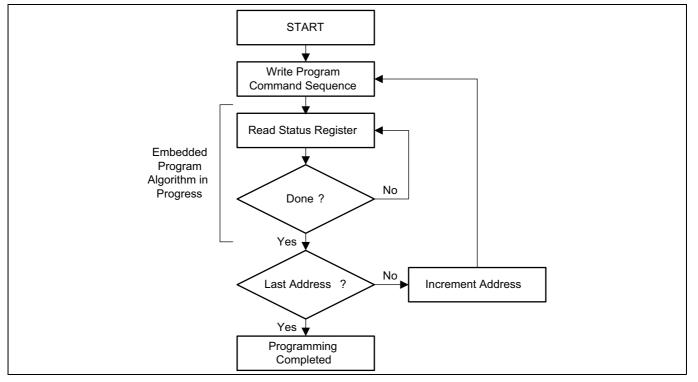

Changing the non-volatile data in the memory array requires a complex sequence of operations that are called EA's. The algorithms are managed entirely by the internal EAC. The main algorithms perform programming and erase of the main flash array data. The host system writes command codes to the flash device address space. The EAC receives the command, performs all the necessary steps to complete the command, and provides status information during the progress of an EA.

The erased state of each memory bit is a logic '1'. Programming changes a logic '1' (HIGH) to a logic '0' (LOW). Only an erase operation is able to change a '0' to a '1'. An erase operation must be performed on an entire 256-KB (or 4-KB for parameter sectors) aligned group of data called a sector. When shipped from Infineon, all sectors are erased.

Programming is done via a 512-byte write buffer. It is possible to write from one to 256 words, anywhere within the write buffer before starting a programming operation. Within the flash memory array, each 512-byte aligned group of data is called a line. A programming operation transfers data from the volatile write buffer to a non-volatile memory array line. The operation is called write buffer programming.

The write buffer is filled with 1s after reset or the completion of any operation using the write buffer. Any locations not written to a '0' by a Write to Buffer command are by default still filled with 1s. Any 1s in the write buffer do not affect data in the memory array during a programming operation.

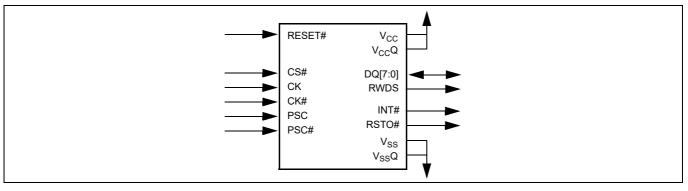

In addition to the mandatory signals (CS#, CK, CK#, DQ [7:0], RWDS) dedicated to the HYPERBUS<sup>™</sup>, the device also includes optional signals (RESET#, INT#, RSTO#, and phase shifted clocks PSC/PSC#).

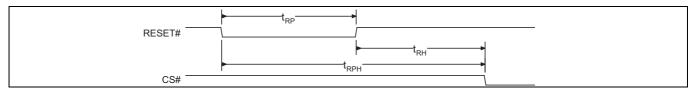

When RESET# transitions from LOW to HIGH the device returns to the default state that occurs after an internal power-on reset (POR).

The INT# output can provide an interrupt to the HYPERFLASH<sup>™</sup> master to indicate when the HYPERFLASH<sup>™</sup> transitions from busy to ready at the end of a program or erase operation.

General description

The RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR, the RSTO# signal will transition from LOW to HIGH impedance after a user defined timeout period has expired. Upon transition to the HIGH impedance state, the external pull-up resistance will pull RSTO# HIGH and the device immediately is placed into the Standby state.

PSC/PSC# are differential phase shifted clock inputs used as a reference for RWDS edges instead of CK/CK#. Refer to **"DDR center aligned read strobe (DCARS) functionality"** on page 7 for more details.

### **1.1** DDR center aligned read strobe (DCARS) functionality

The HYPERFLASH<sup>™</sup> memories offer a configurable feature that enables independent skewing (phase shifting) of the RWDS signal with respect to the read data outputs.

When the DCARS feature is enabled, a second differential phase shifted clock input PSC/PSC# is used as the reference for RWDS edges instead of CK/CK#. The second clock is generally a copy of CK/CK# that is phase shifted 90° to place the RWDS edges centered within the DQ signals valid data window. However, other degrees of phase shift between CK/CK# and PSC/PSC# may be used to optimize the position of RWDS edges within the DQ signals valid data setup and hold time in relation to RWDS edges.

PSC/PSC# is not used during a write transaction. PSC and PSC# may be driven LOW and HIGH respectively or, both may be driven LOW during write transactions.

### **1.2** Error detection and correction functionality

### **1.2.1** Error correction code (ECC)

HYPERFLASH<sup>™</sup> memories provide embedded hamming ECC generation during flash memory array programming, with error detection and correction during read.

As each 16-byte aligned half-page of data, loaded into the write buffer, is transferred to the 512-byte flash memory array line, an ECC for each half-page ECC unit is also programmed in to a portion of the memory array not visible to the host system software.

The ECC information is checked during each half-page flash array read operation. Any one bit error within the half-page will be corrected by the ECC logic during the access of each half-page.

The ECC information for each half-page can be written once after each erase of the sector containing each half-page. Programming within the same half-page more than once will disable error detection and correction within that half-page.

Word programming and write buffer programming, more than once within a half-page, is supported for legacy software compatibility. However, for the best data integrity, it is recommended to not use word programming or write buffer programming to program within a half-page, more than once. Multiple writes to the same half page without an erase will disable the ECC functionality since the ECC syndrome becomes invalid. For applications requiring multiple programming operations within the same half-page, it is recommended to add system software error detection and correction, to enhance the data integrity of half-pages that are programmed more than once.

There is a mode that may be enabled for two bit error detection. When this mode is enabled, any one bit error in a half-page is corrected and any two bit error is detected and reported. In this mode, the ability to write to the same half-page more than once, after an erase, is disabled. In this mode, attempting to program more than once in the same half-page will result in programming operation failure status.

ECC errors may be detected by reading an ECC status register, enabling an interrupt, or enabling the RWDS to stop when an uncorrectable error is encountered - to create a bus error before data is transferred to the HYPERBUS<sup>™</sup> master.

A register is provided to capture the address location of the ECC error.

A counter is provided to count ECC corrections or uncorrectable errors.

General description

### 1.2.2 Cyclic redundancy check

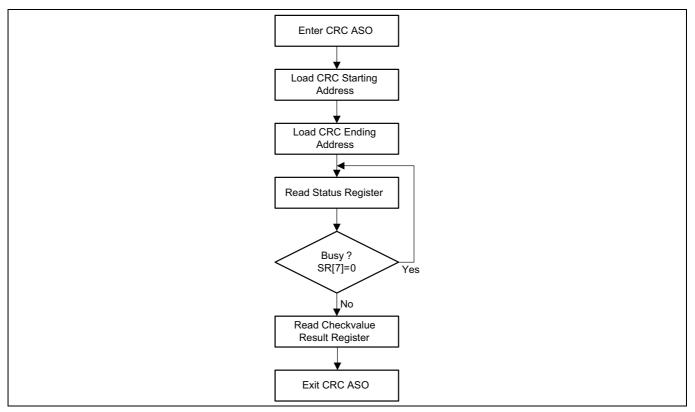

A group of commands are provided to perform a hardware accelerated CRC calculation over a user defined address range. The calculation is another type of embedded operation similar to programming or erase, in which the device is busy while the calculation is in progress. The CRC operation uses a 32-bit polynomial able to detect up to a 32-bit long group of error bits.

A command is used to enter the CRC address space overlay (ASO) where the desired address range is loaded to start the CRC calculation. While entered in the CRC ASO the status of the CRC operation may be checked, suspended to read from the memory array, resumed, and the resulting check-value read. Refer to **"Address space maps"** on page 22 for more details.

### 1.2.2.1 CRC check-value calculation

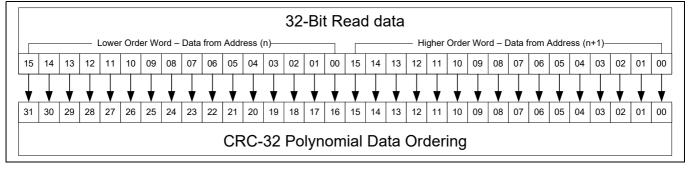

The check-value calculation command sequence causes the device to perform a CRC calculation over a user defined address range. The CRC calculation is achieved with the polynomial described in **Figure 2**.

The check-value generation sequence is started by entering the CRC ASO. The next step is to load the beginning address into the CRC Start Address Register identifying the beginning of the address range that will be covered by the CRC calculation. Next, the ending address is loaded into the CRC End Address Register, this step starts the CRC calculation. The CRC process calculates the check-value on the data contained at the starting address through the ending address.

During the calculation period, the device goes into the Busy state (SR[7] = 0). Once the check-value calculation has completed, the device returns to the Ready state (SR[7] = 1) and the calculated check-value is available in the check-value Low Result Register and the check-value High Result Register. The check-value Low Result Register contains check-value bits 0–15 and can be read from address 0 while the device is in the CRC ASO. The check-value High Result Register contains bits 16–31 and can be read from address 1 while the device is in the CRC ASO. The check-value Low Result Register and the check-value High Result Register are loaded with 0s once the CRC calculation process is initiated.

The check-value calculation can only be initiated when the device is in Standby state and once started can be suspended with the CRC Suspend sequence to read data from the array. During the suspended state, the CRC Suspend Status Bit (CRCSSB) in the Status Register will be set (SR[8] = 1). Once suspended, the host can read the Status Register, read data from the array and can resume the CRC calculation by using the CRC Resume command sequence. Once initiated, the CRC ASO can be terminated with the ASO Exit Command or a Hardware Reset to return the device to read array mode. The check-value calculation cannot be performed while another ASO is active. A hardware reset will clear the value in the CRC Start Address Register, CRC End Address Register, check-value High Result Register, and the check-value Low Result Register.

The Ending Address (EA) should be at least two addresses higher than the Starting Address (SA). If EA < SA + 2, the check-value calculation will abort and the device will return to the ready state (SR[7] = 1). SR[3] will be set (1) to indicate the aborted condition. If EA < SA + 2, the check-value High Result Register and the check-value Low Result Register will hold indeterminate data.

CRC-32C Polynomial =  $X^{32} + X^{28} + X^{27} + X^{26} + X^{25} + X^{23} + X^{22} + X^{20} + X^{19} + X^{18} + X^{14} + X^{13} + X^{11} + X^{10} + X^{9} + X^{8} + X^{6} + 1$

#### Figure 2 CRC-32 polynomial

General description

#### Figure 3 Check-value calculation sequence

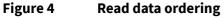

The read data ordering used in calculating the check-value from the CRC-32 polynomial is shown in Figure 4.

Connection diagram

### 2 Connection diagram

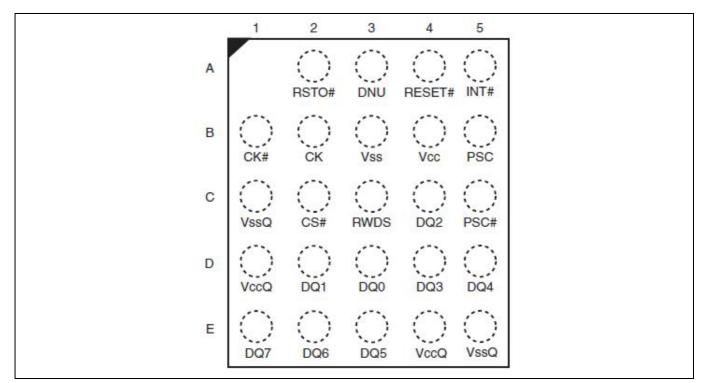

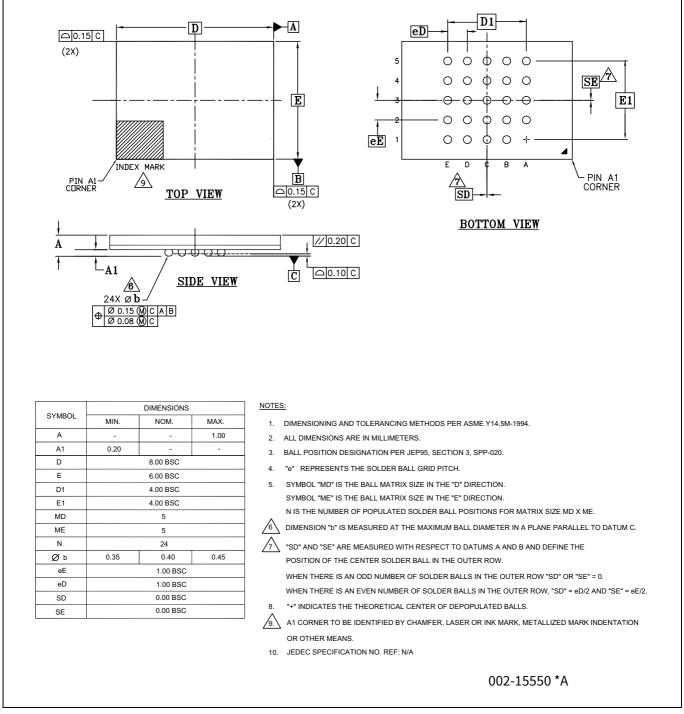

### 2.1 FBGA 24-ball 5 × 5 array footprint

HYPERFLASH<sup>™</sup> devices are provided in fortified ball grid array (FBGA), 1 mm pitch, 24-ball, 5 × 5 ball array footprint, with 6 mm × 8 mm body. The package height is device dependent and may be either 1 mm or 1.2 mm. Refer to **"Ordering information"** on page 115 for more details. Refer to the device datasheet ordering part number valid combinations section for the package in use.

Figure 5 24-ball FBGA,  $6 \times 8 \text{ mm}$ ,  $5 \times 5 \text{ ball footprint, top view}^{[1, 2, 3]}$

#### Notes

- 1. B1 (CK#) is RFU on the 3.0 V device (model 02).

- 2. B5 (PSC) and C5 (PSC#) are RFU on standard 3.0 V and 1.8 V devices (model 02). C5 (PSC#) is RFU on 3 V DCARS device (model 03).

10

3. DNU — Do not Use. This pin/ball is connected internally and must be left unconnected.

Signal description

## 3 Signal description

(infineon

Signal description

| Table 2           | Signal o                  | -   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|---------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Туре                      | М/О | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CS#               | Input                     | М   | <b>Chip Select.</b> HYPERFLASH <sup>™</sup> bus transactions are initiated with a HIGH to LOW transition. HYPERFLASH <sup>™</sup> bus transactions are terminated with a LOW to HIGH transition.                                                                                                                                                                                                                                                                             |

| CK, CK#           | Input                     | М   | <b>Differential Clock.</b> Command / address / data information is input or output with respect to the crossing of the CK and CK# signals. CK# is only used on the 1.8 V devices and may be left open or connected to CK on 3 V devices.                                                                                                                                                                                                                                     |

| RWDS              | Output                    | М   | <b>Read Write Data Strobe.</b> Output data during read transactions are edge aligned with RWDS.                                                                                                                                                                                                                                                                                                                                                                              |

| DQ[70]            | Input /<br>Output         | М   | <b>Data Input / Output.</b> Command / address / data information is transferred on these DQs during read and write transactions.                                                                                                                                                                                                                                                                                                                                             |

| PSC, PSC#         | Input                     | 0   | <b>Phase Shifted Clock.</b> PSC/PSC# allows independent skewing of the RWDS signal with respect to the CK/CK# inputs. PSC# is only used on the 1.8 V device. PSC and PSC# may be driven HIGH and LOW respectively or both may be driven LOW during write transactions.                                                                                                                                                                                                       |

| INT#              | Output<br>(open<br>drain) | 0   | <b>INT Output.</b> When LOW, the device is indicating that an internal event has occurred. This signal is intended to be used as a system level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                                                                                                       |

| RESET#            | Input                     | 0   | <b>Hardware Reset.</b> When LOW, the device will self initialize and return to the array read state. RWDS and DQ[7:0] are placed into the High-Z state when RESET# is LOW. RESET# includes a weak pull-up, if RESET# is left unconnected it will be pulled up to the HIGH state.                                                                                                                                                                                             |

| RSTO#             | Output<br>(open<br>drain) | 0   | <b>RSTO# Output.</b> RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR the RSTO# signal will transition from LOW to HIGH impedance after a user defined timeout period has elapsed. Upon transition to the HIGH impedance state the external pull-up resistance will pull RSTO# HIGH and the device immediately is placed into the Standby state. |

| V <sub>CC</sub>   | Power<br>Supply           | P/G | Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>CC</sub> Q | Power<br>Supply           | P/G | Input / Output Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>   | Power<br>Supply           | P/G | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> Q | Power<br>Supply           | P/G | Input / Output Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

HYPERBUS<sup>™</sup> protocol

### 4 HYPERBUS<sup>™</sup> protocol

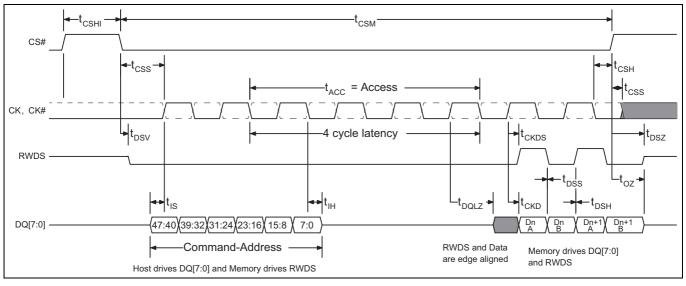

All bus transactions can be classified as either read or write. A bus transaction is started with CS# going LOW with CK = LOW and CK# = HIGH. The transaction to be performed is presented to the HYPERFLASH<sup>™</sup> device during the first three clock cycles in a DDR manner using all six clock edges. These first three clocks transfer three words of command / address (CA0, CA1, CA2) information to define the transaction characteristics:

- Read or write transaction.

- Whether the transaction will be to the memory array or to register space.

- Although the HYPERBUS<sup>™</sup> protocol provides for slave devices that have both memory and register address spaces, HYPERFLASH<sup>™</sup> memories described in this specification do not differentiate between memory and registers as separate address spaces. There is a single address space selected by any transaction, independent of whether the transaction indicates the target location is in memory space or register space. Write transactions always place the transaction address and data into a a command register set (buffer). Read transactions return data from the memory array or from a register address space window that has been temporarily overlaid within the single address space by the execution of commands. The single address space with register space overlays methodology is backward compatible with legacy parallel NOR flash memory program and erase software drivers.

- Whether a transaction will use a linear or wrapped burst sequence.

- HYPERFLASH<sup>™</sup> write transactions do not support burst sequence and ignore the burst type indication. Write command transactions transfer a single word per write. Only the word program command write data transfer may be done with a linear burst at up to 50 MHz.

- The target half-page address (row and upper order column address).

- The target word (within half-page) address (lower order column address).

Once the transaction has been defined, a number of idle clock cycles are used to satisfy any read latency requirements before data is transferred. Once the target data has been transferred, the HYPERBUS<sup>™</sup> master host completes the transaction by driving CS# HIGH with CK = LOW and CK# = HIGH. Data is transferred as 16-bit values with the first eight bits (15–8) transferred on a HIGH going CK (write data or CA bits) or RWDS edge (read data) and the second eight bits (7–0) being transferred on the LOW going CK or RWDS edge. Data transfers during read or write operations can be ended at any time by bringing CS# HIGH when CK = LOW and CK# = HIGH. Read data is edge aligned with RWDS transitions and Write data is center aligned with clock edges.

HYPERBUS™ protocol

### 4.1 Command / address bit assignments

|                                                  | manu / Auuress bit           | assignments                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA Bit#                                          | Bit name                     | Bit function                                                                                                                                                                                                                                                                                                                                                                         |

| 47                                               | R/W#                         | Identifies the transaction as a read or write.<br>1 = Read operation<br>0 = Write operation<br>Target space is defined in CA46.                                                                                                                                                                                                                                                      |

| 46                                               | Target                       | Indicates whether the read or write operation accesses the memory<br>or register spaces.<br>0 = Memory space<br>1 = Register space<br>The register space is intended to be used by volatile memory and<br>peripheral devices. The HYPERFLASH <sup>™</sup> devices will not take<br>advantage of this feature and this bit should be set to '0' during read<br>or write transactions. |

| 45                                               | Burst type                   | Indicates whether the burst will be linear or wrapped.<br>0 = Wrapped Burst<br>1 = Linear Burst                                                                                                                                                                                                                                                                                      |

| 44–39 (1 Gb)<br>44–38 (512 Mb)<br>44–37 (128 Mb) | Reserved                     | Reserved for future address expansion.<br>Reserved bits should be set to '0' by the host controller.                                                                                                                                                                                                                                                                                 |

| 38–16 (1 Gb)<br>37–16 (512 Mb)<br>36–16 (128 Mb) | Row and upper column address | Half page component of target address.                                                                                                                                                                                                                                                                                                                                               |

| 15-3                                             | Reserved                     | Reserved for future column address expansion.<br>Reserved bits should be set to '0' by the host controller.                                                                                                                                                                                                                                                                          |

| 2–0                                              | Lower column<br>address      | Lower column component of the target address: System word address bits A2–0 selecting the starting word within a half-page.                                                                                                                                                                                                                                                          |

#### Table 3 Command / Address bit assignments

HYPERBUS<sup>™</sup> protocol

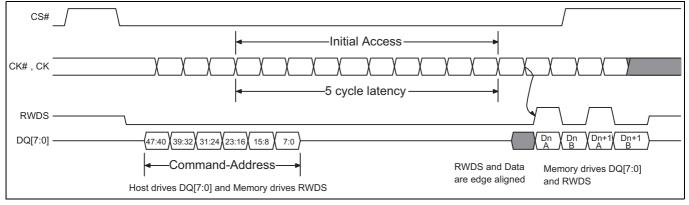

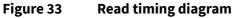

### 4.2 Read operations

CA0 indicates that a read operation is to be performed and also indicates the burst type (wrapped or linear). Read operations begin the internal array access as soon as the half-page address has been presented in CA0 and CA1. CA2 identifies the target word address within the chosen half-page. The host then continues clocking for a number of cycles defined by the latency count setting in the Configuration Register. Once these latency clocks have been completed, the memory starts to simultaneously transition the read write data strobe (RWDS) and begins outputting the target data. New data is output in an edge aligned fashion upon every transition of RWDS. Data will continue to be output as long as the host continues to transition the clock (CK and CK#). Wrapped bursts will continue to wrap within the burst length and linear burst will output data in a sequential manner across page boundaries. A hybrid burst provides one initial wrapped burst followed by linear burst, as described in **"Hybrid Burst**" on page 68. Wrapped reads can be performed from the main array, the CFI tables in **"Device ID and Common Flash Interface (ID-CFI) ASO map**" on page 71 and the secure silicon region (see **"Hybrid Burst**" on page 68). Read transfers can be ended at any time by bringing CS# HIGH when CK = LOW and CK# = HIGH.

When a linear burst reaches the last address in the array, if the burst continues, the address counter will wrap around and roll back to address 000000h, allowing the read sequence to be continued indefinitely. The entire memory can therefore be read out with one single read instruction.

The 16-byte and 32-byte wrapped bursts do not cross page boundaries and do not incur inter-page boundary crossing latencies. For a 64-byte wrapped burst read, a latency may occur during the target address to next page boundary crossing, depending on the starting address (see **Table 22**).

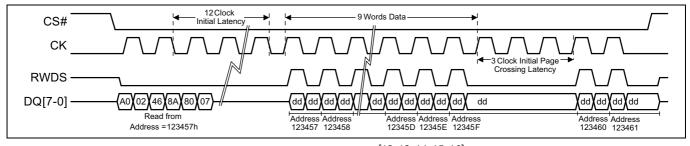

Figure 7 Read operation<sup>[5, 6, 7, 8]</sup>

#### Notes

- 5. Transactions must be initiated with CK = LOW and CK# = HIGH. CS# must return HIGH before a new transaction is initiated.

- 6. Read access from the flash array starts once CA[23:16] is captured.

- 7. The read latency is defined by the read latency value in the Volatile Configuration Register (or the Non-volatile Configuration Register).

- 8. In this example of a read operation, the latency count was set to five clocks.

HYPERBUS<sup>™</sup> protocol

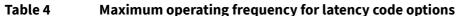

| Table 4         Maximum operating frequency for latency code options |                |                                   |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------|-----------------------------------|--|--|--|--|--|--|--|--|

| Latency code                                                         | Latency clocks | Maximum operating frequency (MHz) |  |  |  |  |  |  |  |  |

| 0000                                                                 | 5              | 52                                |  |  |  |  |  |  |  |  |

| 0001                                                                 | 6              | 62                                |  |  |  |  |  |  |  |  |

| 0010                                                                 | 7              | 72                                |  |  |  |  |  |  |  |  |

| 0011                                                                 | 8              | 83                                |  |  |  |  |  |  |  |  |

| 0100                                                                 | 9              | 93                                |  |  |  |  |  |  |  |  |

| 0101                                                                 | 10             | 104                               |  |  |  |  |  |  |  |  |

| 0110                                                                 | 11             | 114                               |  |  |  |  |  |  |  |  |

| 0111                                                                 | 12             | 125                               |  |  |  |  |  |  |  |  |

| 1000                                                                 | 13             | 135                               |  |  |  |  |  |  |  |  |

| 1001                                                                 | 14             | 145                               |  |  |  |  |  |  |  |  |

| 1010                                                                 | 15             | 156                               |  |  |  |  |  |  |  |  |

| 1011                                                                 | 16             | 166                               |  |  |  |  |  |  |  |  |

| 1100                                                                 | Reserved       | NA                                |  |  |  |  |  |  |  |  |

| 1101                                                                 | Reserved       | NA                                |  |  |  |  |  |  |  |  |

| 1110                                                                 | Reserved       | NA                                |  |  |  |  |  |  |  |  |

| 1111                                                                 | Reserved       | NA                                |  |  |  |  |  |  |  |  |

Figure 8Read transaction crossing a page boundary[12, 13, 14, 15, 16]

#### Notes

- 9. Default NVCR latency setting when the device is shipped from the factory is 16 clocks.

- 10. The latency code is the value loaded into (Non) Volatile Configuration Register bits xVCR[7:4].

- 11.Maximum operating frequency assumed to be using a device with  $t_{ACC} = 96$  ns.

- 12.Read operation starting at device address 123457h.

- 13.Latency code loaded into the Configuration Register is 0111b which results in 12 latency clocks.

- 14.Page boundary crossing requires three clocks in this case. 12 clock initial latency minus 9 clocks (words) of initial data.

- 15.CK# is not shown but is the complement of the CK signal.

- 16.CA45 = 1 for a linear read burst.

HYPERBUS™ protocol

| Target  |     |     | Clock cycle |      |                                     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|---------|-----|-----|-------------|------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| address | 0   | 1   | 2           | 3    |                                     | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  |     |     |     |     |     |     |     |

| 0       |     |     |             |      |                                     |     | D0  | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |     |     |     |     |     |     |     |

| 1       |     |     |             |      |                                     |     | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 |     |     |     |     |     |     |     |

| 2       |     |     |             |      |                                     |     | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 |     |     |     |     |     |     |     |

| 3       |     |     |             |      |                                     |     | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 |     |     |     |     |     |     |     |

| 4       |     |     |             |      |                                     |     | D4  | D6  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 |     |     |     |     |     |     |     |

| 5       |     |     |             |      |                                     |     | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |     |     |

| 6       |     |     |             |      |                                     |     |     |     | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | Х   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |

| 7       |     |     |             |      |                                     |     |     |     |     |     |     |     |     | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | Х   | Х   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |

| 8       | CA0 | CA1 | CA2         |      | Bus turnaround +<br>initial latency |     | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 |     |     |     |     |     |     |     |

| 9       |     |     |             |      |                                     |     |     | -   |     |     | -   | -   | - 7 | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 |

| 10      |     |     |             |      |                                     |     | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 |     |     |     |     |     |     |     |

| 11      |     |     |             |      |                                     |     | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 |     |     |     |     |     |     |     |

| 12      |     |     |             |      |                                     |     | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 |     |     |     |     |     |     |     |

| 13      |     |     |             |      |                                     |     | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |     |     |

| 14      |     |     |             |      |                                     | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | Х   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |     |     |     |

| 15      |     |     |             | 2 11 |                                     |     | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | Х   | х   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |     |     |

| 16      |     |     |             |      |                                     |     | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |     |     |     |     |     |     |     |

|         | -   | _   | 1           |      |                                     |     | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | _   | -   |     |     |     |     |     |     |     |

| Table 6 | First page boundary crossing during linear read (Latency count = 16 clocks) |

|---------|-----------------------------------------------------------------------------|

|---------|-----------------------------------------------------------------------------|

| Target  |     |               |     |   |                     |     |     |     |     | c   | lock cy | /cle aft | er CS# | goes L | .ow |     |     |     |     |     |     |     |     |     |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

|---------|-----|---------------|-----|---|---------------------|-----|-----|-----|-----|-----|---------|----------|--------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|-----|-----|

| address | 0   | 1             | 2   | 3 |                     | 17  | 18  | 19  | 20  | 21  | 22      | 23       | 24     | 25     | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 0       |     |               |     |   |                     |     | D0  | D1  | D2  | D3  | D4      | D5       | D6     | D7     | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 1       |     |               |     |   |                     |     | D1  | D2  | D3  | D4  | D5      | D6       | D7     | D8     | D9  | D10 | D11 | D12 | D13 | D14 | D15 | Х   | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 2       |     |               |     |   |                     |     | D2  | D3  | D4  | D5  | D6      | D7       | D8     | D9     | D10 | D11 | D12 | D13 | D14 | D15 | х   | Х   | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 3       |     |               |     |   |                     |     | D3  | D4  | D5  | D6  | D7      | D8       | D9     | D10    | D11 | D12 | D13 | D14 | D15 | Х   | Х   | Х   | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 4       |     |               |     |   |                     |     | D4  | D6  | D6  | D7  | D8      | D9       | D10    | D11    | D12 | D13 | D14 | D15 | Х   | Х   | х   | Х   | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 5       |     |               |     |   |                     |     | D5  | D6  | D7  | D8  | D9      | D10      | D11    | D12    | D13 | D14 | D15 | Х   | Х   | х   | х   | Х   | D16 | D17 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 6       |     |               |     |   |                     |     |     |     |     |     |         |          |        |        | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | Х | Х | Х | Х   | Х   | Х   | D16 | D17 |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 7       | 7   |               |     |   |                     | D7  | D8  | D9  | D10 | D11 | D12     | D13      | D14    | D15    | Х   | Х   | Х   | Х   | х   | х   | Х   | D16 | D17 |     |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 8       | CA0 | CA1           | CA2 |   | urnaro<br>tial late |     | D8  | D9  | D10 | D11 | D12     | D13      | D14    | D15    | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 9       |     |               |     |   | ,                   |     | D9  | D10 | D11 | D12 | D13     | D14      | D15    | D16    | D17 | D18 | D19 | D20 | D21 | D22 | D23 | Х   | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 10      |     |               |     |   |                     |     | D10 | D11 | D12 | D13 | D14     | D15      | D16    | D17    | D18 | D19 | D20 | D21 | D22 | D23 | х   | Х   | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 11      |     |               |     |   |                     |     | D11 | D12 | D13 | D14 | D15     | D16      | D17    | D18    | D19 | D20 | D21 | D22 | D23 | Х   | Х   | Х   | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 12      |     |               |     |   |                     |     | D12 | D13 | D14 | D15 | D16     | D17      | D18    | D19    | D20 | D21 | D22 | D23 | Х   | Х   | х   | Х   | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 13      |     |               |     |   |                     |     | -   |     |     |     |         |          |        |        |     |     |     |     |     | -   |     |     |     | -   |   |   |   | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | Х | х | х | х | Х | D24 | D25 |

| 14      |     |               |     |   |                     | D14 | D15 | D16 | D17 | D18 | D19     | D20      | D21    | D22    | D23 | Х   | Х   | Х   | Х   | Х   | Х   | D24 | D25 |     |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 15      |     |               |     |   |                     |     | D15 | D16 | D17 | D18 | D19     | D20      | D21    | D22    | D23 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | D24 | D25 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

| 16      |     |               |     |   |                     |     | D16 | D17 | D18 | D19 | D20     | D21      | D22    | D23    | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

|         | _   | Ι             | 1   | 2 |                     | 16  | -   | -   | -   | I   | -       | -        | -      | I      | I   | -   | I   | -   | -   | I   | -   | -   | I   | -   |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

|         |     | Latency count |     |   |                     |     |     |     |     |     |         |          |        |        |     |     |     |     |     |     |     |     |     |     |   |   |   |     |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |     |     |

HYPERBUS<sup>™</sup> protocol

To calculate latency when crossing a page boundary, use the following formula: if ((PS - LTCY) < ADDR & (SP -1)) { ((ADDR & (SP -1)) - PS + LTCY) } else {0}

where: PS = page size = 16 words SP = sub-page size = 8 words LTCY = latency ADDR = target address

HYPERBUS<sup>™</sup> protocol

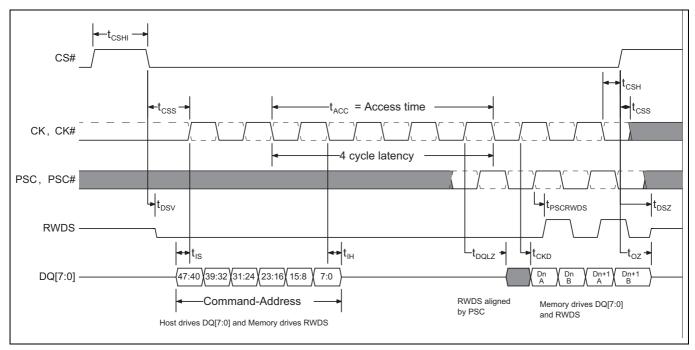

### 4.3 HYPERFLASH<sup>™</sup> Read with DCARS timing

The illustrations and parameters in this section are only those needed to define the DCARS feature and show the relationship between the phase shifted clock, RWDS, and data.

Figure 9 HYPERFLASH<sup>™</sup> Read DCARS timing diagram<sup>[17, 18, 19, 20]</sup>

#### Notes

- 17.Transactions must be initiated with CK = LOW and CK# = HIGH. CS# must return HIGH before a new transaction is initiated.

- 18.CK# and PSC# are optional and shown as dashed line waveforms.

- 19. The memory drives RWDS during read transactions.

- 20. This example demonstrates a latency code setting of four clocks and no additional initial latency required.

HYPERBUS<sup>™</sup> protocol

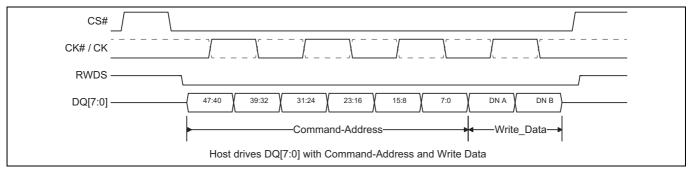

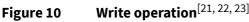

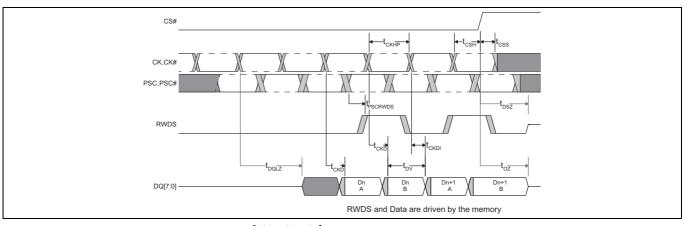

### 4.4 Write operations

A write operation starts with the first three clock cycles providing the CAx (command / address) information indicating the transaction characteristics. The burst type bit CA[45) is 'don't care' because the HYPERFLASH<sup>™</sup> device only supports a single write transaction of 16b or a continuous linear write burst that is only supported when loading data during a Word Program command. Immediately following the CA information the host is able to transfer the write data on the DQ bus. The first byte (A) of data is presented on the rising edge of CK and the second byte (B) is presented on the falling edge of CK. Write data is center aligned with the CK/CK# inputs. Write transfers can be ended at any time by bringing CS# HIGH when CK = LOW and CK# = HIGH.

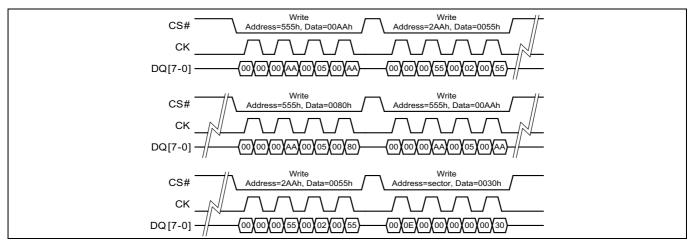

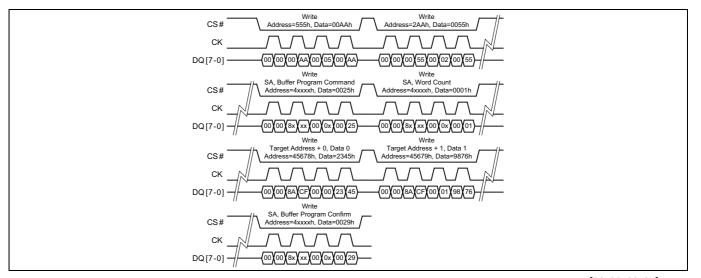

Figure 11 Write transaction usage example: Erase operation command sequence<sup>[24, 25, 26, 27]</sup>

#### Notes

- 21.Transactions must be initiated with CK = LOW and CK# = HIGH. CS# must return HIGH before a new transaction is initiated.

- 22.RWDS will be driven LOW as long as CS# is LOW.

- 23.Write operations are limited to a transaction of a single word (16b) or a linear write burst supported only when loading data during a Word Program command.This example demonstrates a latency code setting of four clocks and no additional initial latency required.

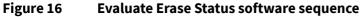

- 24.See **Figure 17** for the Erase Operation command sequence flowchart.

- 25. Erase operation to the sector starting at 0700000h.

- 26.CK# is not shown but is the complement of the CK signal.

- 27.RWDS is not shown and is not used during Write transactions.

### 512 Mb (64 MB)/256 Mb (32 MB)/128 Mb (16 MB) HYPERFLASH™ Family HYPERBUS™, 3.0 V/1.8 V

HYPERBUS™ protocol

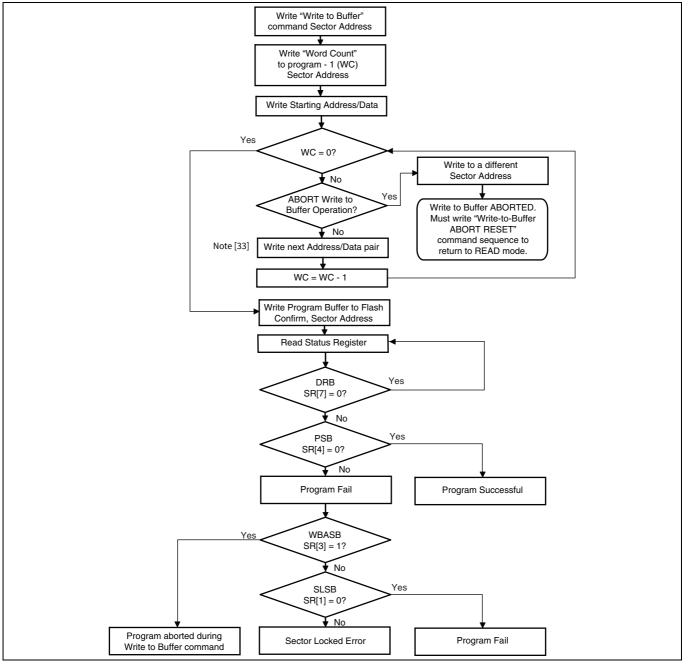

Figure 12Write transaction usage example: Write Buffer Program command sequence

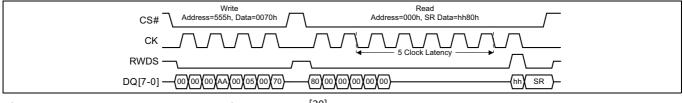

Figure 13 Status Read transaction example<sup>[30]</sup>

#### Notes

28.See Figure 15 for the Write Buffer Program Operation command sequence flowchart.

21

29.Program 2345h into address 45678h, and 9876h into address 45679h.

30.CK# is not shown but is the complement of the CK signal.

31.RWDS is not shown and is not used during Write transactions.

Address space maps

### 5 Address space maps

Although the HYPERBUS<sup>™</sup> protocol provides for slave devices that have both memory and register address spaces, HYPERFLASH<sup>™</sup> memories described in this specification do not differentiate between memory and registers as separate address spaces. There is a single address space selected by any transaction, independent of whether the HYPERBUS<sup>™</sup> transaction indicates the target location is in memory space or register space of the selected device.

Write transactions always place the transaction address and data into a a command register set (buffer).

Read transactions return data from the memory array or from a register address space window that has been temporarily overlaid within the single address space by the execution of commands. The single address range with register space overlays methodology is backward compatible with legacy parallel NOR flash memory program and erase software drivers.

There are several separate address spaces that may appear within the address range of the flash memory device. One address space is visible (entered) at any given time.

- Flash memory array: The main non-volatile memory array used for storage of data that may be randomly accessed by read operations.

- ID/CFI: A flash memory array used for Infineon factory programmed device characteristics information. This area contains the device identification (ID) and common flash interface (CFI) information tables.

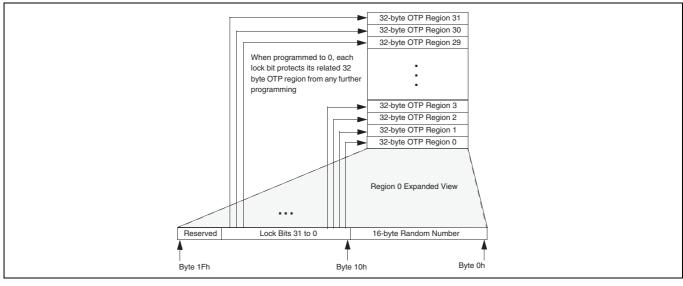

- Secure silicon region (SSR): A 1024-byte one-time programmable non-volatile memory array used for Infineon factory programmed permanent data, and customer programmable permanent data.

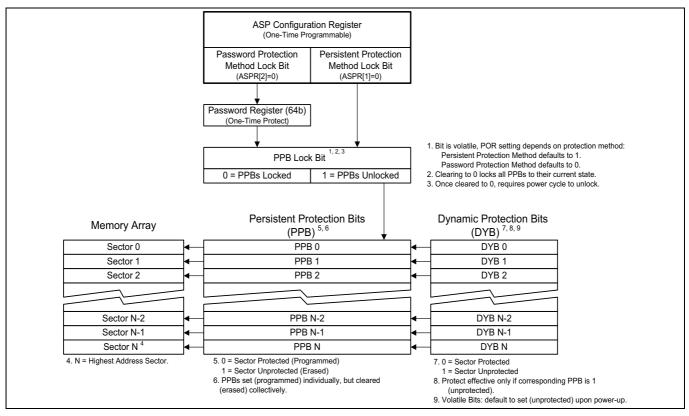

- Persistent protection bits (PPB): A non-volatile memory array with one bit for each sector. When programmed, each bit protects the related sector from erasure and programming.

- PPB lock bit: A volatile register bit used to enable or disable programming and erase of the PPB bits.

- Password: An OTP non-volatile array used to store a 64-bit password used to enable changing the state of the PPB lock bit when using password mode sector protection.

- Dynamic protection bits (DYB): A volatile array with one bit for each Sector. When set, each bit protects the related sector from erasure and programming.

- ECC status: Read the address of ECC corrected data and total ECC error count.

- CRC: Read the CRC check-value.

- Status or Peripheral Registers: Register access used to display EA status and read or write other registers.

The flash memory array is the primary and default address space but, it may be overlaid by one other address space, at any one time. Each alternate address space is called an ASO.

Each ASO replaces (overlays) either the sector selected by the command that enters the ASO or the entire flash device address range, depending on the ASO Entry command. If only one sector is overlaid by an ASO the remaining sectors of the memory array remain readable. Any address range not defined by a particular ASO address map, is reserved for future use. Unless otherwise stated all read accesses outside of an ASO address map returns non-valid (undefined) data. The locations will display actively driven data but their meaning is not defined.

There are multiple address map modes that determine what appears in the flash device address space at any given time:

- Read Mode

- Status Register (SR) Mode

- ASO Mode

- Peripheral Register Mode

### 512 Mb (64 MB)/256 Mb (32 MB)/128 Mb (16 MB) HYPERFLASH™ Family HYPERBUS™, 3.0 V/1.8 V

Address space maps

In Read Mode, the entire flash memory array may be directly read by the host system memory controller. The memory device EAC, puts the device in Read Mode during power-on, after a hardware reset, after a command reset, or after an EA is suspended. Read accesses and commands are accepted in Read Mode. A subset of commands is accepted in Read Mode when an EA is suspended.

While in any mode, the Status Register read command may be issued to cause the Status Register ASO to appear at every word address in the device address space. In this Status Register ASO Mode, the device interface waits for a read access and, any write access is ignored. The next read access to the device accesses the content of the Status Register, exits the Status Register ASO, and returns to the previous (calling) mode in which the Status Register read command was received.

Similarly, commands that read and write other registers use Peripheral Register Mode, in which the register appears in a temporary ASO that is automatically exited after the read or write of the command selected register. The read or write occurs in the last cycle of the Register Access command sequence.

In EA Mode the EAC is performing an EA, such as programming or erasing a non-volatile memory array. While in EA Mode, none of the flash memory array is readable. While in EA Mode, only the Program / Erase Suspend command or the Status Register Read command will be accepted. All other commands are ignored. Thus, no other ASO may be entered from the EA Mode.

In ASO Mode, one of the remaining overlay address spaces is entered (overlaid on the flash memory array address map). Only one ASO may be entered at any one time. Commands to the device affect the currently entered ASO. Only certain commands are valid for each ASO. These are listed in each ASO related section of **Table 41**.

The following ASOs have non-volatile data that may be programmed to change 1s to 0s:

- Secure silicon region

- ASP Configuration Register (ASPR)

- Persistent protection bits (PPB)

- Password

- Only the PPB ASO has nonvolatile data that may be erased to change 0s to 1s.

When a program or erase command is issued while one of the non-volatile ASOs is entered, the EA operates on the ASO. The ASO is not readable while the EA is active. When the EA is completed the ASO remains entered and is again readable. Suspend and Resume commands are ignored during an EA operating on any of these ASOs.

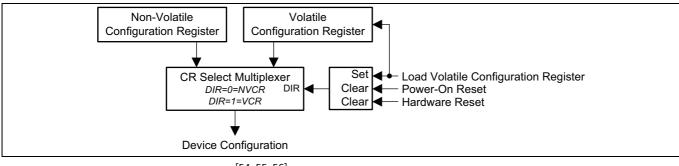

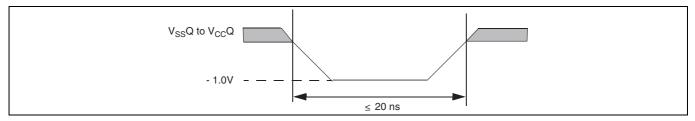

The Peripheral Register Mode is used to manage the POR Timer, Interrupt Configuration Register, Interrupt Status Register, Volatile Configuration Register, and the Non-volatile Configuration Register.

#### 5.1 Flash memory array

The S26KL/S26KS family has a uniform sector architecture with a sector size of 256 KB. The following tables show the sector architecture of the devices.

A user configuration option is available to overlay either the first sector (SA00) or last sector (SAmax) with eight 4-KB parameter-sectors. The parameter-sector address map showing how the lowest or highest sector is partitioned is shown in the following memory address map tables. The parameter-sectors can be erased and programmed in the normal manner using the standard erase and program command sequences targeting the appropriate parameter-sector addresses. Note that the smaller parameter-sectors need to include A[16:11] as part of the address identifying the target parameter-sector during erase and program command sequences. Configuring the first or last uniform sector to include the parameter sectors is accomplished with the Non-volatile Configuration Register.

**Note** The following tables have been condensed to show sector related information for an entire device on a single page. Sectors and their address ranges that are not explicitly listed (such as SA001–SA510) have sector starting and ending addresses that form the same pattern as all other sectors of that size. For example, all 256-KB sectors have the pattern XX00000h–XX1FFFFh.

Address space maps

| Table 7 S26      | KL512S and S2   | 26KS512S sect   | tor and memory address map | )                       |

|------------------|-----------------|-----------------|----------------------------|-------------------------|

| Sector size (KB) | Sector<br>count | Sector<br>range | Address range (16-bit)     | Notes                   |

|                  |                 | SA00            | 0000000h-001FFFFh          | Sector starting address |

| 256              | 256             | :               | :                          | -                       |

|                  |                 | SA255           | 1FE0000h-1FFFFFh           | Sector ending address   |

| Table 8 | S26KL256S and S26KS256S sector and memory address map |

|---------|-------------------------------------------------------|

|---------|-------------------------------------------------------|

| Sector size (KB) | Sector<br>count | Sector<br>range | Address range (16-bit) | Notes                   |

|------------------|-----------------|-----------------|------------------------|-------------------------|

|                  |                 | SA00            | 0000000h-001FFFFh      | Sector starting address |

| 256              | 128             | :               | :                      | _                       |

|                  |                 | SA127           | 0FE0000h-0FFFFFh       | Sector ending address   |

| Table 9 | S26KL128S and S26KS128S sector and memory address map |

|---------|-------------------------------------------------------|

|---------|-------------------------------------------------------|

| Sector size (KB) | Sector<br>count | Sector<br>range | Address range (16-bit) | Notes                   |

|------------------|-----------------|-----------------|------------------------|-------------------------|

|                  |                 | SA00            | 0000000h-001FFFFh      | Sector starting address |

| 256              | 64              | :               | :                      | -                       |

|                  |                 | SA63            | 07E0000h-07FFFFh       | Sector ending address   |

| Table 10 | Main array sector 0 overlaid with eight 4-KB parameter-sectors |

|----------|----------------------------------------------------------------|

|----------|----------------------------------------------------------------|

| Main array<br>sector size | Parameter-sector<br>number             | Address size | Address range (16-bit) | Notes                                               |

|---------------------------|----------------------------------------|--------------|------------------------|-----------------------------------------------------|

|                           | 0                                      | 4 KB         | 0000000h-00007FFh      | Start of parameter-sector 0                         |

|                           | 1                                      | 4 KB         | 0000800h-0000FFFh      | Parameter-sector 1                                  |

|                           | 2                                      | 4 KB         | 0001000h-00017FFh      | Parameter-sector 2                                  |

| 256 KB                    | 3                                      | 4 KB         | 0001800h-0001FFFh      | Parameter-sector 3                                  |

|                           | 4                                      | 4 KB         | 0002000h-00027FFh      | Parameter-sector 4                                  |

|                           | 5                                      | 4 KB         | 0002800h-0002FFFh      | Parameter-sector 5                                  |

|                           | 6                                      | 4 KB         | 0003000h-00037FFh      | Parameter-sector 6                                  |

|                           | 7                                      | 4 KB         | 0003800h-0003FFFh      | End of parameter-sector 7                           |

|                           | Exposed portion of main array sector 0 | 224 KB       | 0004000h-001FFFFh      | Mapped to exposed portion<br>of main array sector 0 |

Address space maps

| Table 11                  | Last sector overlaid with eight 4-KB parameter-sectors |              |                        |                                                       |

|---------------------------|--------------------------------------------------------|--------------|------------------------|-------------------------------------------------------|

| Main array<br>sector size | Parameter-sector<br>number                             | Address size | Address range (16-bit) | Notes                                                 |

|                           | Expose portion of<br>main array last<br>sector         | 224 KB       | xx00000h-xx1BFFFh      | Mapped to exposed portion of main array sector (last) |

|                           | 0                                                      | 4 KB         | xx1C000h-xx1C7FFh      | Start of parameter-sector 0                           |

|                           | 1                                                      | 4 KB         | xx1C800h-xx1CFFFh      | Parameter-sector 1                                    |

| 256 KB                    | 2                                                      | 4 KB         | xx1D000h-xx1D7FFh      | Parameter-sector 2                                    |

|                           | 3                                                      | 4 KB         | xx1D800h-xx1DFFFh      | Parameter-sector 3                                    |

|                           | 4                                                      | 4 KB         | xx1E000h-xx1E7FFh      | Parameter-sector 4                                    |

|                           | 5                                                      | 4 KB         | xx1E800h-xx1EFFFh      | Parameter-sector 5                                    |

|                           | 6                                                      | 4 KB         | xx1F000h-xx1F7FFh      | Parameter-sector 6                                    |

|                           | 7                                                      | 4 KB         | xx1F800h-xx1FFFFh      | End of parameter-sector 7                             |

#### 5.2 **Device ID and CFI (ID-CFI) ASO**

There are two traditional methods for systems to identify the type of flash memory installed in the system. One is device identification (ID). The other method is called common flash interface (CFI).

For ID, a command is used to enable an address space overlay where up to 16 word locations can be read to get JEDEC manufacturer identification (ID), device ID, and some configuration and protection status information from the flash memory. The system can use the manufacturer and device IDs to select the appropriate driver software to use with the flash device.

CFI also uses a command to enable an ASO where an extendable table of standard information about how the flash memory is organized and operates can be read. With this method the driver software does not have to be written with the specifics of each possible memory device in mind. Instead the driver software is written in a more general way to handle many different devices but adjusts the driver behavior based on the information in the CFI table.

Traditionally these two address spaces have used separate commands and were separate overlays. However, the mapping of these two address spaces are non-overlapping and so can be combined in to a single address space and appear together in a single overlay. Either of the traditional commands used to access (enter) the Autoselect (ID) or CFI overlay will cause the now combined ID-CFI address map to appear.

The ID-CFI address map appears within, and overlays the flash memory array data of the sector selected by the address used in the ID-CFI enter command. While the ID-CFI ASO is entered the content of all other sectors is undefined.

The ID-CFI address map starts at location zero of the selected sector. Locations above the maximum defined address of the ID-CFI ASO to the maximum address of the selected sector have undefined data. The ID-CFI enter commands use the same address and data values used on previous generation memories to access the JEDEC manufacturer ID (Autoselect) and CFI information, respectively.

| Word address          | Description                               | Read / Write |

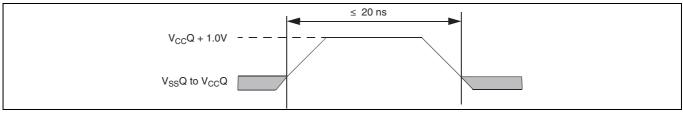

|-----------------------|-------------------------------------------|--------------|