#### **N-Channel Enhancement Mode Field Effect Transistor**

## **General Description**

The 100N68K is N-Channel MOSFET, It has specifically been designed to minimize input capacitance and gate charge. The device is therefore suitable in advanced high-efficiency switching applications.

#### **Features**

- Minimize input capacitance and gate charge

- 100% avalanche tested

- Low On-Resistance

# **Product Summary**

| BVDSS | RDSON | ID   |

|-------|-------|------|

| 68V   | 6.5mΩ | 100A |

## **Applications**

- Motor Control

- DC-DC converters

- Switching applications

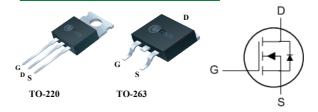

## TO-220/263 Pin Configuration

| Туре       | Package | Marking    |

|------------|---------|------------|

| CMP100N68K | TO-220  | CMP100N68K |

| CMB100N68K | TO-263  | CMB100N68K |

# **Absolute Maximum Ratings**

| Symbol                               | Parameter                                       | Rating | Units      |  |

|--------------------------------------|-------------------------------------------------|--------|------------|--|

| $V_{DS}$                             | Drain-Source Voltage                            | 68     | V          |  |

| $V_{GS}$                             | Gate-Source Voltage                             | ±20    | V          |  |

| I <sub>D</sub> @T <sub>C</sub> =25℃  | Continuous Drain Current                        | 100    | А          |  |

| I <sub>D</sub> @T <sub>C</sub> =100℃ | Continuous Drain Current                        | 80     | А          |  |

| I <sub>DM</sub>                      | Pulsed Drain Current 400                        |        | А          |  |

| EAS                                  | Single Pulse Avalanche Energy                   | 500    | mJ         |  |

| P <sub>D</sub> @T <sub>C</sub> =25°C | Total Power Dissipation                         | 170    | W          |  |

| T <sub>STG</sub>                     | Storage Temperature Range -55 to 150            |        | $^{\circ}$ |  |

| TJ                                   | Operating Junction Temperature Range -55 to 150 |        | $^{\circ}$ |  |

## **Thermal Data**

| Symbol           | Parameter                           | Тур. | Max. | Unit |  |

|------------------|-------------------------------------|------|------|------|--|

| $R_{	heta JA}$   | Thermal Resistance Junction-ambient |      | 62   | °C/W |  |

| R <sub>θJC</sub> | Thermal Resistance Junction-case    |      | 0.88 | °C/W |  |

# CMP100N68K/CMB100N68K

#### **N-Channel Enhancement Mode Field Effect Transistor**

## Electrical Characteristics (T $_J$ =25 $^{\circ}$ C , unless otherwise noted)

| Symbol              | Parameter                         | Conditions                                          | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------|-----------------------------------------------------|------|------|------|------|

| BV <sub>DSS</sub>   | Drain-Source Breakdown Voltage    | V <sub>GS</sub> =0V , I <sub>D</sub> =250uA         | 68   |      |      | V    |

| R <sub>DS(ON)</sub> | Static Drain-Source On-Resistance | V <sub>GS</sub> =10V , I <sub>D</sub> =30A          |      |      | 6.5  | mΩ   |

| $V_{GS(th)}$        | Gate Threshold Voltage            | $V_{GS}=V_{DS}$ , $I_D=250uA$                       | 2    |      | 4    | V    |

| I <sub>DSS</sub>    | Drain-Source Leakage Current      | V <sub>DS</sub> =68V, V <sub>GS</sub> =0V           |      |      | 1    | uA   |

| I <sub>GSS</sub>    | Gate-Source Leakage Current       | $V_{GS} = \pm 20V$ , $V_{DS} = 0V$                  |      |      | ±100 | nA   |

| gfs                 | Forward Transconductance          | V <sub>DS</sub> =5V , I <sub>D</sub> =30A           |      | 42   |      | S    |

| $R_g$               | Gate Resistance                   | V <sub>DS</sub> =0V , V <sub>GS</sub> =0V , f=1MHz  |      | 2.3  |      | Ω    |

| Qg                  | Total Gate Charge                 | I <sub>D</sub> =30A                                 |      | 86   |      |      |

| Q <sub>gs</sub>     | Gate-Source Charge                | V <sub>DD</sub> =30V                                |      | 19   |      | nC   |

| $Q_gd$              | Gate-Drain Charge                 | V <sub>GS</sub> =10 V                               |      | 29   |      |      |

| T <sub>d(on)</sub>  | Turn-On Delay Time                | V <sub>DD</sub> =30V                                |      | 17   |      |      |

| Tr                  | Rise Time                         | I <sub>D</sub> =1A                                  |      | 11   |      | ne   |

| T <sub>d(off)</sub> | Turn-Off Delay Time               | R <sub>G</sub> =2.5Ω                                |      | 56   |      | ns   |

| T <sub>f</sub>      | Fall Time                         | V <sub>GS</sub> =10V                                |      | 14   |      |      |

| C <sub>iss</sub>    | Input Capacitance                 |                                                     |      | 5100 |      |      |

| C <sub>oss</sub>    | Output Capacitance                | V <sub>DS</sub> =30V , V <sub>GS</sub> =0V , f=1MHz |      | 360  |      | pF   |

| C <sub>rss</sub>    | Reverse Transfer Capacitance      |                                                     |      | 320  |      |      |

#### **Diode Characteristics**

| Symbol          | Parameter                 | Conditions                                                      | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------|-----------------------------------------------------------------|------|------|------|------|

| Is              | Continuous Source Current | V <sub>G</sub> =V <sub>D</sub> =0V , Force Current              |      |      | 100  | Α    |

| I <sub>SM</sub> | Pulsed Source Current     |                                                                 |      |      | 400  | Α    |

| V <sub>SD</sub> | Diode Forward Voltage     | V <sub>GS</sub> =0V , I <sub>S</sub> =50A , T <sub>J</sub> =25℃ |      |      | 1.2  | V    |

#### Note:

This product has been designed and qualified for the counsumer market.

Cmos assumes no liability for customers' product design or applications.

Cmos reserver the right to improve product design ,functions and reliability withtout notice.