500V Half-Bridge Module

# For Small Appliance Motor Drive Applications

# LAS1M0750

# Overview

LAS1M0750 is a half-bridge module designed for advanced appliance motor drive applications such as energy efficient fans and pumps. LASemi's technology offers an extremely compact, high performance half-bridge topology in an isolated package. The advanced IPM offers a combination of LASemi's low R<sub>DS(on)</sub> MOSFET technology and the industry benchmark half-bridge high voltage, rugged driver in a small LasSOP-10 package. The dedicated open-source pin from low side MOSFET is provided for current sensing. The input works with

Schmitt-trigger and the logic voltage is compatible with 3.3V/5V/15V signal. The UVLO, deadtime and thermal shutdown are also provided.

### Features

- Built-in high-performance 500V/7A FRMOSFET and >5us short circuit tolerance

- Robust at negative transient voltage

- Gate drive supply range from 10 to 20V

- UVLO for both high side and low side

- Built-in dead time to avoid cross-conduction

- Thermal Shutdown (TSD) protection

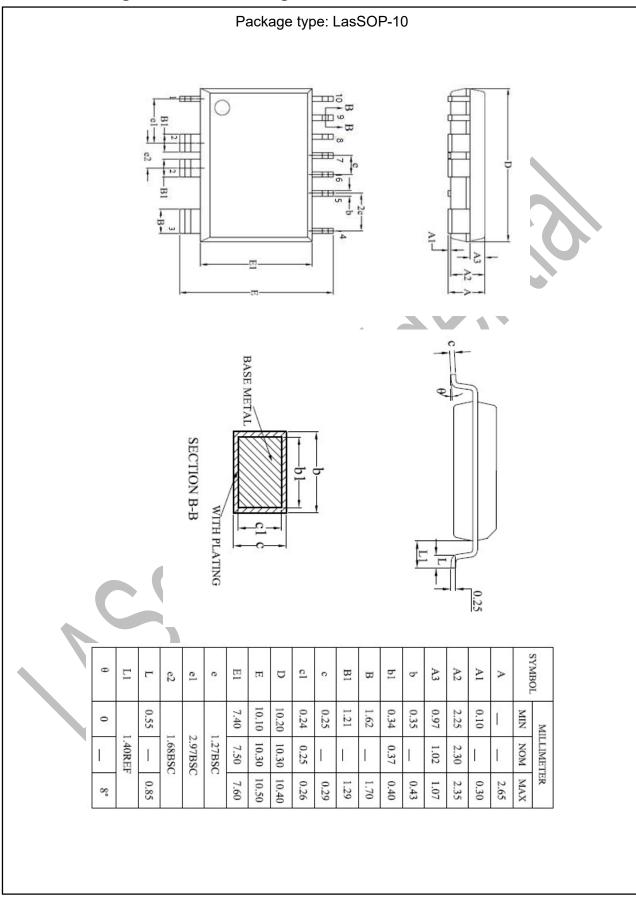

- Available in LasSOP-10 package customized with compact size and low thermal resistance feature

Rev 1.2 2020/12

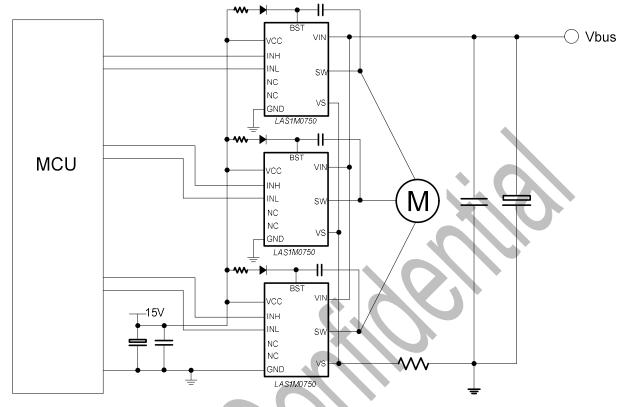

# **Typical Application**

• BLDC fan/pumps

# Package Mark and Order Information

| Device    | Package   | Temperature range | Packaging Type    | Purchase Contact     |

|-----------|-----------|-------------------|-------------------|----------------------|

| LAS1M0750 | LasSOP-10 | -40 to 125ºC      | T/R 1500 pcs/roll | sales@latticeart.com |

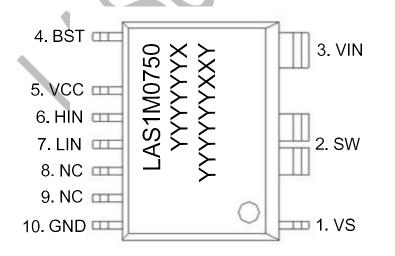

# Pin Diagram

YYYYYY: IC Lot number X: version YYYYYY: MOS Lot Number XX: week number Y: Year code

# **Pin Description**

| Pin No. | Symbol | Pin Description                 |  |  |

|---------|--------|---------------------------------|--|--|

| 1       | VS     | Open source for low side MOSFET |  |  |

| 2       | SW     | SW phase output                 |  |  |

| 3       | VIN    | DC bus                          |  |  |

| 4       | BST    | High side floating supply       |  |  |

| 5       | VCC    | Power supply for low side       |  |  |

| 6       | HIN    | High side gate driver input     |  |  |

| 7       | LIN    | Low side gate driver input      |  |  |

| 8       | NC     | No Connect                      |  |  |

| 9       | NC     | No Connect                      |  |  |

| 10      | GND    | Ground pin                      |  |  |

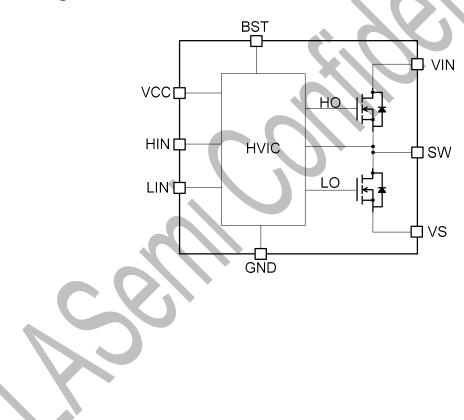

# **Block Diagram**

# Absolute Maximum Ratings (note 1)

| T <sub>A</sub> =25 <sup>0</sup> C, unless otherwise specified. |                                          |           |      |  |  |

|----------------------------------------------------------------|------------------------------------------|-----------|------|--|--|

| Symbol                                                         | Definition Ratings                       |           |      |  |  |

| VCC                                                            | Power supply voltage for low side        | 20        | V    |  |  |

| BST-SW                                                         | Power supply voltage for high side       | 20        | V    |  |  |

| VIN                                                            | DC bus                                   | 500       | V    |  |  |

| ID                                                             | Each MOSFET current, continues, Tj<150°C | 3.5       | А    |  |  |

| Ідм                                                            | Each MOSFET pulse current<100us          | 7         | А    |  |  |

| HIN, LIN                                                       | Input logic voltage                      | 20        | V    |  |  |

| VS                                                             | Open source voltage                      | 10        | V    |  |  |

| Тѕтс                                                           | Storage temperature                      | -55 to150 | °C   |  |  |

| Tj                                                             | Junction temperature                     | -40 to150 | °C   |  |  |

| Rth(j-c)                                                       | Junction to case thermal resistance      | 6         | °C/W |  |  |

| PD                                                             | Total power dissipation                  | 8.3       | W    |  |  |

Note 1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are not tested at manufacturing.

# **Recommended Operating Conditions**

| Symbol  | Definition                        | Ratings        | Unit |

|---------|-----------------------------------|----------------|------|

| VCC     | Power supply pin for low side     | 11 to 17       | V    |

| BST     | High side floating supply voltage | SW+11 to SW+17 | V    |

| VIN     | DC bus voltage                    | <400           | V    |

| HIN/LIN | Logic input voltage               | VCC            | V    |

| Fpwm    | PWM carrier frequency             | <50            | kHz  |

## **Electrical Characteristics**

$T_A=25^{0}C$ , unless otherwise specified.

#### Gate driver part

| Symbol               | Parameter                                             | Condition                               | Min.         | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------|-----------------------------------------|--------------|------|------|------|

| Ιανοο                | Quiescent VCC supply current                          | VCC=15V,<br>HIN=LIN=0V                  | 70           | 95   | 125  | uA   |

| I <sub>BST-SW</sub>  | Quiescent V <sub>BST-SW</sub> supply current          | V <sub>BST-SW</sub> =15V,<br>HIN=LIN=0V | 15           | 30   | 45   | uA   |

| VCC <sub>ON</sub>    | VCC under-voltage rising threshold                    |                                         | 8.3          | 9.1  | 9.9  | V    |

| VBS <sub>ON</sub>    | V <sub>BST-sw</sub> under voltage rising threshold    |                                         | 8            | 8.5  | 9.1  | V    |

| VCC <sub>OFF</sub>   | VCC under-voltage falling<br>threshold                |                                         | 7.5          | 8.1  | 8.8  | V    |

| VBSOFF               | VBS under-voltage falling<br>threshold                | 20                                      | 7.5          | 7.8  | 8.2  | V    |

| VCC <sub>HYS</sub>   | VCC UVLO hysteresis                                   |                                         | $\mathbf{D}$ | 1    |      | V    |

| VBS <sub>HYS</sub>   | BST-SW UVLO hysteresis                                |                                         |              | 0.7  |      | V    |

| I <sub>IN_LKG</sub>  | Logic "1" input bias current                          | HIN,LIN=5V                              |              | 5    |      | uA   |

| I <sub>IN_SINK</sub> | Logic "0" input bias current                          | HIN,LIN=0V                              |              |      | 1    | uA   |

| VIL                  | OFF threshold voltage                                 | Logic low level                         |              |      | 0.8  | V    |

| VIH                  | ON threshold voltage                                  | Logic high level                        | 3            |      |      | V    |

| DT                   | Dead time                                             |                                         |              | 100  |      | ns   |

| T <sub>FLT_IN</sub>  | Input filter                                          |                                         |              | 100  |      | ns   |

| MT                   | High side and low side delay match time               |                                         |              |      | 60   | ns   |

| T <sub>OTP</sub>     | Over temperature protection shutdown rising threshold |                                         |              | 138  |      | °C   |

| T <sub>OTP_HYS</sub> | OTP hysteresis                                        |                                         |              | 28   |      | °C   |

| Power MC                 | DS part                               |                                                                            |      |      |      |      |

|--------------------------|---------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| Symbol                   | Parameter                             | Condition                                                                  | Min. | Тур. | Max. | Unit |

| BV <sub>DSS</sub>        | Drain-Source<br>Breakdown Voltage     | VCC=0V, I <sub>D</sub> =500uA                                              |      |      |      | V    |

| I <sub>DSS</sub>         | Zero Gate voltage<br>Drain Current    | VCC=0V, V <sub>DS</sub> =500V                                              |      |      | 3    | uA   |

| $V_{\text{SD}}$          | Drain-source diode<br>forward voltage | VCC=V <sub>BS</sub> =15V<br>I <sub>D</sub> =2.5A                           |      | 0.95 |      | V    |

| R <sub>DS(ON)</sub>      | Drain-source Turn-On<br>Resistance    | VCC=V <sub>BS</sub> =15V<br>VIN=5V, I <sub>D</sub> =2.5A                   |      | 1.0  | 1.5  | ohm  |

| Trr                      | Reverse recovery time                 |                                                                            |      | 110  |      | ns   |

| E <sub>ON</sub>          | Turn-on switching lost                |                                                                            |      | 150  |      | uJ   |

| EOFF                     | Turn-off switching lost               |                                                                            |      | 15   |      | uJ   |

| T <sub>ON</sub>          | Turn-on propagation delay time        |                                                                            |      | 600  |      | ns   |

| T <sub>OFF</sub>         | Turn-off propagation delay time       | VIN=400V, VCC=V <sub>BST-</sub><br><sub>sw</sub> =15V, I <sub>D</sub> =3A; | 5    | 450  |      | ns   |

| dV/dt <sub>rising</sub>  | SW rising dV/dt slaw<br>rate          | Inductive Load, High-side and Low-side Switching                           |      | 30   |      | V/ns |

| dl/dt <sub>rising</sub>  | SW rising dl/dt slaw<br>rate          |                                                                            |      | 75   |      | A/us |

| dV/dt <sub>falling</sub> | SW falling dV/dt slaw rate            | $C, \mathcal{O}, \mathcal{O}$                                              |      | 10   |      | V/ns |

| dl/dt <sub>falling</sub> | SW falling dI/dt slaw<br>rate         |                                                                            |      | 250  |      | A/us |

# **Function Descriptions**

#### 1. Input and output True Table

| HIN  | LIN  | OUTPUT | Description                                 |

|------|------|--------|---------------------------------------------|

| 0    | 0    | Hi-Z   | High side and low side OFF                  |

| 0    | 1    | 0      | Low side ON, High side OFF                  |

| 1    | 0    | VIN    | High side ON, Low side OFF                  |

| 1    | 1    | Hi-Z   | Forbidden input, High side and low side OFF |

| Open | Open | Hi-Z   | Input internal pull-down resistor 1M ohm    |

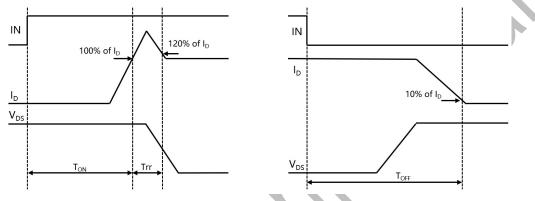

#### 2. Dynamic switching diagram

Figure 1 Dynamic switching diagram

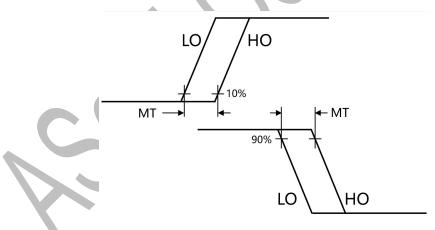

#### 3. Delay Match Time

Figure 2 Delay match time

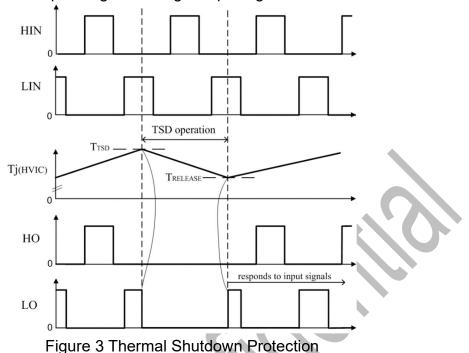

#### 4. Thermal Shutdown (TSD)

LAS1M0750 incorporates a thermal shutdown (TSD) circuit. Figure 3 shows TSD operational waveforms. In case of overheating (e.g., increased power dissipation due to overload, a rise in ambient temperature at the device, etc.), LAS1M0750 shuts down both high-side and low-side output transistors.

The TSD circuit in HVIC can monitor the power MOSFET with a relative accuracy since the compact module package makes the power device and HVIC closely placed. When the temperature of HVIC exceeds the TSD operating temperature (T<sub>TSD</sub>, typ.138°C), the TSD circuit is activated. When the temperature of the HVIC decreases to the TSD

releasing Temperature(typ.110°C) or less, the shutdown condition is released. The output transistors then resume operating according to input signals.

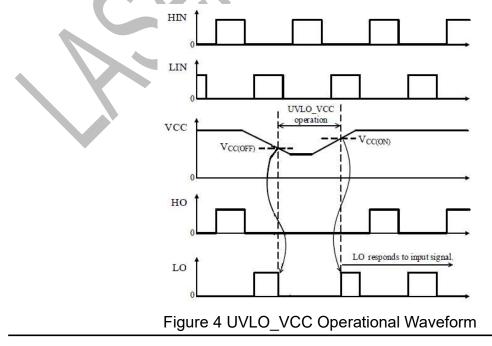

#### 5. Undervoltage Lockout for Low-side Power Supply (UVLO\_VCC)

Figure 4 shows operational waveforms of undervoltage lockout for low-side power supply (i.e., UVLO\_VCC).

When the VCC pin voltage decreases to the logic operation stop voltage(typ.8.1V) or less, the UVLO\_VCC circuit in the corresponding phase gets activated and sets both of HO and LO signals to logic low. When the VCC pin voltage increases to the logic operation start voltage (typ.9.1V) or more, LAS1M0750 releases the UVLO\_VCC operation. Then, LAS1M0750 resumes the following transmissions: a LO signal according to the LIN pin input command; a HO signal according to the rising edge of the first HIN pin input command after the UVLO\_VCC release.

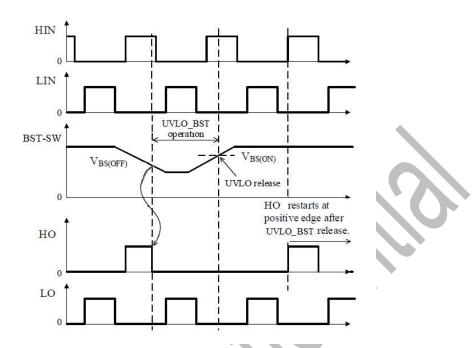

#### 6. Undervoltage Lockout for High-side Power Supply (UVLO\_BST)

Figure 5 shows operational waveforms of undervoltage lockout for high-side power supply (i.e., UVLO\_BST).

Figure 5 UVLO\_BST Operational Waveform

When the voltage between the BST and SW pins decreases to the logic operation stop voltage(typ.7.8V) or less, the UVLO\_BST circuit in corresponding phase gets activated and sets an HO signal to logic low. When the voltage between BST and SW pins increases to the logic operation start voltage(typ.8.5V) or more, LAS1M0750 releases the UVLO\_VB operation. Then, the HO signal becomes logic high at the rising edge of the first input command after the UVLO\_VB release.

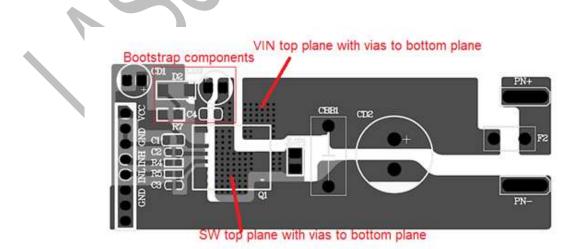

#### 7. PCB Design Guidelines

LAS1M0750's VIN and SW wide-lead pin layout is configured to provided sufficient copper area for heat sinking. Figure 6 gives an example of the PCB layout.

# LAS1M0750

#### **Detail Package Outline Drawing**