### 31V, 3A, Synchronous, Step-Down Converter

# **LA1313**

### **Overview**

The LA1313 is an easy to use synchronous stepdown Buck. Which integrated low on resistance high-side and low-side power MOSFETs. The

LA1313 can deliver 3A of output current efficiently with constant on time (COT) control for fast loop response.

The LA1313 achieves high power conversion efficiency over a wide load range by scaling down the switching frequency under light-load conditions to reduce switching and gate driving losses. The LA1313 has built-in protection features, such as cycle-by-cycle current limit, hiccup mode short-circuit protection, FB open short protection and thermal shutdown in case of excessive power dissipation. The LA1313 is available in a space-saving TSOT23-6L package.

#### **Features**

- 4.5V to 31V Wide Input Range

- 3A Continuous Output Current

- $70m\Omega/45m\Omega$  Internal Power MOSFETs

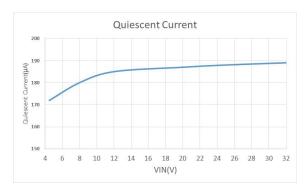

- 185µA Low Quiescent Current

- Constant On Time Control for Fast Loop Response

- 340kHz Switching Frequency

- Support Up to 98% Large Duty Cycle

- Internal Soft Start

- Output Voltage adjustable from 0.6V

- Support Pre-Biased Output Startup

- Full Protection, Over Current Protection and Hiccup, Output Over Voltage Protection, FB Open Short Protection, Over Temperature Protection

- Available in an TSOT23-6L Package

## **Applications**

- Surveillance Camera

- Home Appliance and Whitegoods

- Multi-functional Printer

- Automotive

- Industrial Control

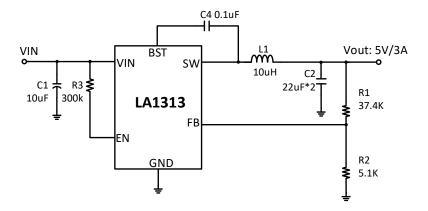

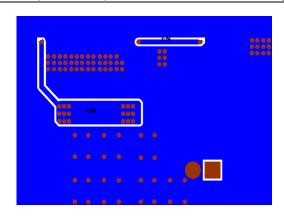

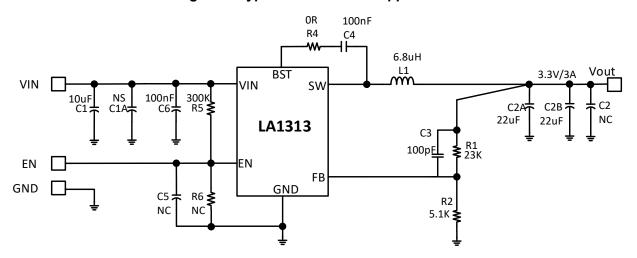

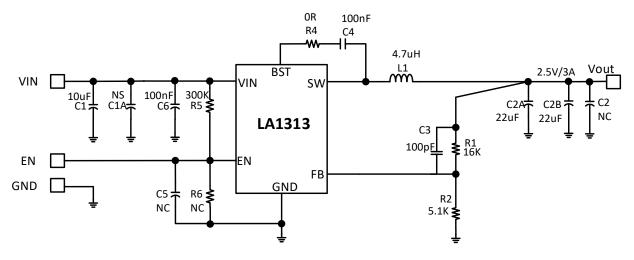

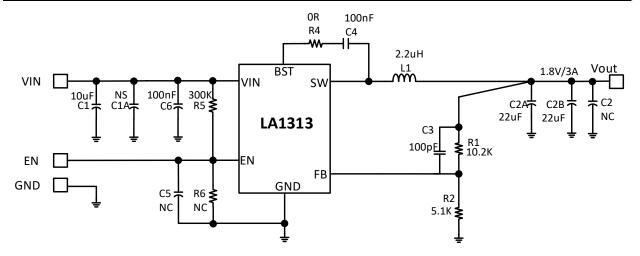

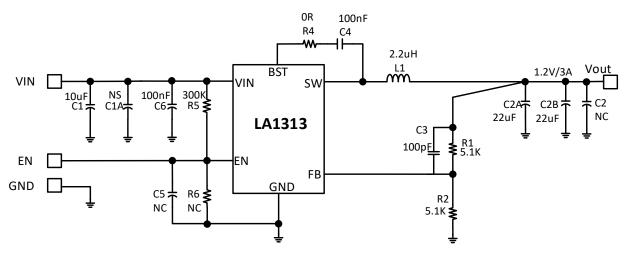

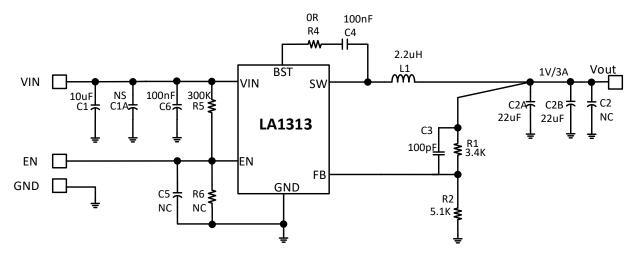

## **Typical Application**

# **Package Mark and Order Information**

| Device | Package   | Temperature range | Packaging Type   | Purchase Contact     |

|--------|-----------|-------------------|------------------|----------------------|

| LA1313 | TSOT23-6L | -40 to 125°C      | T/R 3000pcs/roll | sales@latticeart.com |

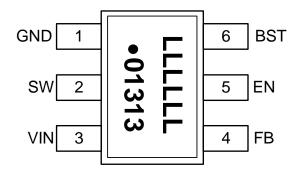

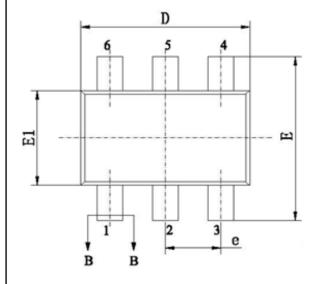

# Pin Diagram (Top view)

LLLLLL: Lot number 01313: Product code

# **Pin Description**

| Pin No. | Symbol | Pin Description                                                        |

|---------|--------|------------------------------------------------------------------------|

|         |        | System ground. GND is the reference ground of the regulated            |

| 1       | GND    | output voltage. Requires extra care during PCB layout. Connect         |

|         |        | to GND with wide copper traces and vias.                               |

|         |        | Switching output of the convertor. Internally connected to             |

| 2       | SW     | source of the high-side FET and drain of the low-side FET.             |

|         |        | Connect to power inductor.                                             |

|         |        | Supply input Pin. VIN supplies power for the internal MOSFET           |

| 3       | VIN    | and regulator. The input capacitors are needed to decouple the         |

|         |        | input rail. Use wide PCB traces to make the connection.                |

| 4       | FB     | Feedback input to the convertor. Connect a resistor divider            |

| 4       | 1 D    | to set the output voltage.                                             |

|         |        | <b>Enable Pin</b> . Drive EN Pin High to enable IC, otherwise float or |

| 5       | EN     | pull down EN to disable IC. EN pin Can be tied to VIN by a             |

| 3       | LIN    | resistor. Precision enable input allows adjustable UVLO by             |

|         |        | external resistor divider.                                             |

|         |        | <b>Bootstrap</b> . Connect a capacitor between SW and BST pins to      |

| 6       | BST    | form a floating supply across the High-side switch driver.             |

| U       | וטם    | Connect a high quality 100nF capacitor from this pin to the SW         |

|         |        | pin.                                                                   |

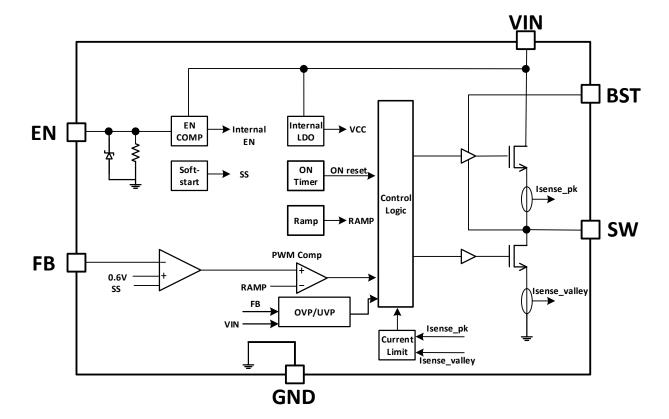

# **Block Diagram**

## **Absolute Maximum Ratings (Note 1/2)**

T<sub>A</sub>=25<sup>o</sup>C, unless otherwise specified.

| Symbol            | Definition                  | Ratings                         | Unit |

|-------------------|-----------------------------|---------------------------------|------|

| V <sub>IN</sub>   | VIN to GND                  | -0.3~33                         | V    |

| SW                | SW to GND                   | -0.7 (-5V in<br>10ns)~VIN + 0.7 | V    |

| EN                | Max Input current to EN pin | 100 <sup>(2)</sup>              | μΑ   |

| BST               | BST to SW                   | -0.3~6                          | V    |

| All Other<br>Pins |                             | -0.3~6                          | V    |

| T <sub>STG</sub>  | Storage temperature         | -65 to150                       | °C   |

| T <sub>j</sub>    | Junction temperature        | -40 to150                       | °C   |

Note 1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are not tested at manufacturing.

## **Recommended Operating Conditions**

| Symbol | Definition                    | Ratings         | Unit |

|--------|-------------------------------|-----------------|------|

| BST    | BST to SW                     | 4~5             | V    |

| Vin    | VIN to GND                    | 4.5~31          | V    |

| Vouт   | Vout to GND                   | 0.6~0.98xVIN or | V    |

|        |                               | VOUT<25         |      |

| Гоит   | Max Continuous Output Current | 3               | Α    |

# **Thermal Resistance (Note 3)**

| Symbol           | Definition                                | Ratings | Unit |

|------------------|-------------------------------------------|---------|------|

| Rејс             | Junction to case (top) thermal resistance | 23      | °C/W |

| R <sub>θJA</sub> | Junction to ambient thermal resistance    | 62      | °C/W |

Note 3: Measured on Latticeart DEMO DEM1313-00A, 2-Layer PCB, 63mm x 48mm board.

### **ESD**

| Symbol | Definition          | Ratings | Unit |

|--------|---------------------|---------|------|

| HBM    | Human Body Mode     | ±2000   | V    |

| CDM    | Charged Device Mode | ±1500   | V    |

Note 2: For details on ENs ABS max rating, please refer to the Enable Control section.

# **Electrical Characteristics**

V<sub>IN</sub>=12V, V<sub>EN</sub>=2V, T<sub>A</sub>=25°C, unless otherwise specified.

| Symbol                                     | Parameter                      | Condition                                               | Min  | Тур  | Max  | Units |

|--------------------------------------------|--------------------------------|---------------------------------------------------------|------|------|------|-------|

| Input UVL                                  | O and Quiescent Curren         | t                                                       |      |      |      |       |

| VIN <sub>UVR</sub>                         | VIN UVLO rising threshold      |                                                         | 4.2  | 4.28 | 4.35 | V     |

| VIN <sub>UVF</sub>                         | VIN UVLO falling threshold     |                                                         | 3.8  | 3.9  | 4    | V     |

| VIN <sub>UV_hys</sub>                      | VIN UVLO hysteresis            |                                                         |      | 0.38 |      | V     |

| I <sub>QS</sub>                            | Shutdown supply current        | $V_{EN} < 0.3V, V_{IN} = 12V$                           |      | 1    |      | μA    |

| IQ                                         | Quiescent supply current       | $V_{IN}$ =12V, No load,<br>VFB = 0.83V, no<br>switching |      | 185  |      | μΑ    |

| High Side                                  | and Low Side MOSFETs           |                                                         |      |      |      |       |

| LKG <sub>HS</sub>                          | High-side leakage              | $V_{EN} = 0V$ , $V_{SW} = 0V$                           |      |      | 1    | μA    |

| LKG <sub>LS</sub>                          | Low-side leakage               | $V_{EN} = 0V, V_{SW} = 31V$                             |      |      | 1    | μA    |

| R <sub>ON_HS</sub>                         | High-Side Switch on resistance | $V_{BST-SW} = 5V$                                       |      | 70   |      | mΩ    |

| R <sub>ON_LS</sub>                         | Low-Side Switch on resistance  | V <sub>IN</sub> = 12V                                   |      | 45   |      | mΩ    |

| Feedback                                   | Voltage and SS                 |                                                         |      |      | l    |       |

| $V_{FB}$                                   | Feedback voltage               | Ta = 25°C                                               | 591  | 600  | 609  | mV    |

| I <sub>LK_FB</sub>                         | Feedback leakage               | $V_{EN} = 1V$ , $V_{FB} = 2V$                           |      |      | 0.1  | μA    |

| Tss                                        | Soft-Start time                | V <sub>FB</sub> from 0% to 100%                         |      | 2.4  |      | ms    |

| Current L                                  | imit                           |                                                         |      |      |      |       |

| I <sub>Valley</sub>                        | Low-Side Current limit         | V <sub>OUT</sub> =0V                                    |      | 4.8  |      | Α     |

| ZCD                                        |                                |                                                         |      | 100  |      | mA    |

| Enable                                     | <del>,</del>                   | <del>,</del>                                            |      |      |      |       |

| $V_{EN\_R}$                                | EN Rising Threshold            | Low to High                                             | 1.1  | 1.2  | 1.3  | V     |

| V <sub>EN_F</sub> Enable falling threshold |                                | High to Low                                             | 0.94 | 0.98 | 1.02 | V     |

| V <sub>EN_Hys</sub>                        | Enable Threshold<br>Hysteresis |                                                         |      | 0.22 |      | V     |

## **Electrical Characteristics**

V<sub>IN</sub>=12V, V<sub>EN</sub>=2V, T<sub>A</sub>=25°C, unless otherwise specified.

| Symbol                              | Parameter              | Condition | Min | Тур  | Max | Units |

|-------------------------------------|------------------------|-----------|-----|------|-----|-------|

| R <sub>EN</sub>                     | Enable input resistor. |           |     | 1500 |     | kΩ    |

| T <sub>ONMIN</sub> <sup>(4)</sup>   | Minimum on time        |           |     | 75   |     | ns    |

| D <sub>MAX</sub> <sup>(4)</sup>     | Max duty cycle         |           |     | 98   |     | %     |

| V <sub>OUT</sub> OVP                | UVP threshold hold     |           |     |      |     |       |

| FB <sub>OVP</sub>                   | Rising                 |           |     | 115  |     | %     |

| FB <sub>UVP</sub>                   |                        |           |     | 35   |     | %     |

| T <sub>OTP_R</sub> <sup>(4)</sup>   | Thermal shutdown       |           |     | 150  |     | °C    |

| T <sub>OTP_Hys</sub> <sup>(4)</sup> | OTP hysteresis         |           |     | 20   |     | °C    |

| T <sub>OFFMIN</sub> <sup>(4)</sup>  | Minimum off time       |           |     | 150  |     | ns    |

Note 4: Guaranteed by design and engineering sample characterization.

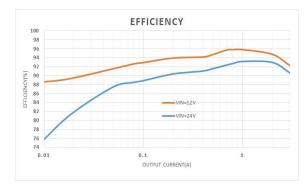

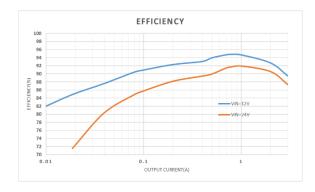

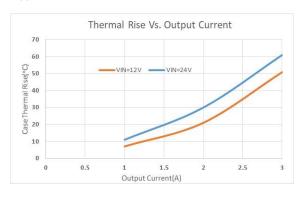

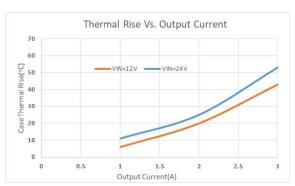

## **Typical Performance Characteristic**

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $C_{IN}$  = 22 $\mu$ F,  $C_{OUT}$  = 44 $\mu$ F, L1 = 10 $\mu$ H, and  $T_A$  = +25°C, unless otherwise noted.

### **Efficiency**

DCR=26mohm, Vout=5V

### **Efficiency**

DCR=26mohm, Vout=3.3V

### **Case Temperature Rise**

V<sub>OUT</sub>=5V

#### **Case Temperature Rise**

V<sub>OUT</sub>=3.3V

#### **Quiescent Current**

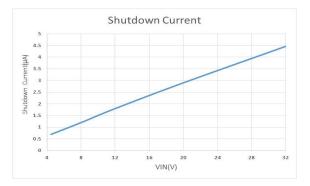

#### **Shutdown Current**

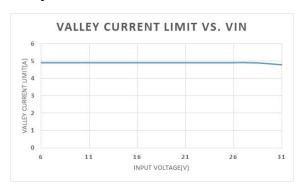

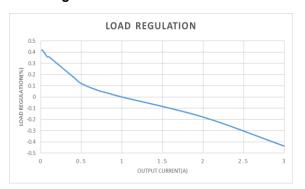

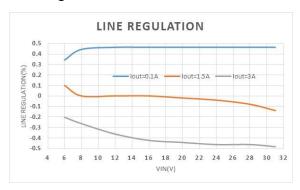

# **Typical Performance Characteristic**

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $C_{IN}$  = 22 $\mu$ F,  $C_{OUT}$  = 44 $\mu$ F, L1 = 10 $\mu$ H, and  $T_A$  = +25°C, unless otherwise noted.

### **Valley Current limit Vs VIN**

### **Load Regulation**

### **Line Regulation**

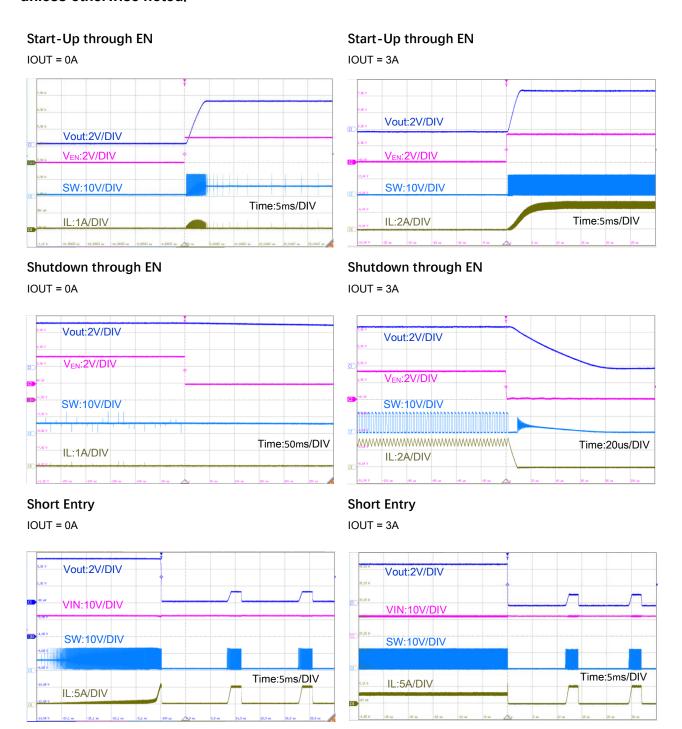

## **Typical Performance Characteristic** *(continued)*

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 44 $\mu$ F, L1 = 10 $\mu$ H, and  $T_A$  = +25°C, Frequency = 340kHz, unless otherwise noted.

## **Typical Performance Characteristic** *(continued)*

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 44 $\mu$ F, L1 = 10 $\mu$ H, and  $T_A$  = +25°C, Frequency = 340kHz, unless otherwise noted.

## **Typical Performance Characteristic** *(continued)*

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $C_{IN}$  = 22 $\mu$ F,  $C_{OUT}$  = 44 $\mu$ F, L1 = 10 $\mu$ H, and  $T_A$  = +25°C, Frequency = 340kHz, unless otherwise noted.

## **Function Descriptions**

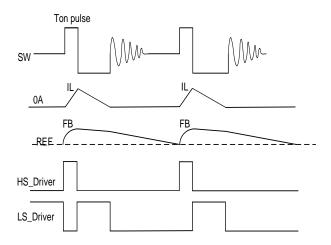

#### Pulse-Width Modulation (PWM) Control

The LA1313 is fully integrated synchronous rectified step-down switch mode converter. Constant-on-time (COT) control is employed to provide fast transient response and easy loop stabilization. At the beginning of each cycle, the high-side MOSFET (HS-FET) is turned ON when the feedback voltage (VFB) is below the reference voltage (VREF), which indicates insufficient output voltage. The ON period is determined by both the output voltage and input voltage to make the switching frequency fairy constant over input voltage range.

After the ON period elapses, the HS-FET is turned off, or becomes OFF state. It is turned ON again when VFB drops below VREF. By repeating operation this way, the converter regulates the output voltage. The integrated low- side MOSFET (LS-FET) is turned on when the HS-FET is in its OFF state to minimize the conduction loss. To avoid shoot-through, a dead-time (DT) is internally generated between HS-FET off and LS-FET on, or LS-FET off and HS-FET on.

Figure 1. PFM Operation

An internal compensation is applied for COT control to make a more stable operation even when ceramic capacitors are used as output capacitors, this internal compensation will then improve the jitter performance without affect the line or load regulation.

With the load decrease, the inductor current decrease too. Once the inductor current touch zero, the operation is transition from continuous-conduction-mode (CCM) to discontinuous- conduction-mode (DCM).

When the LA1313 works in pulse-frequency modulation (PFM) mode during light-load operation, the LA1313 reduces the switching frequency automatically to maintain high efficiency, and the inductor current drops almost to zero. When the inductor current reaches zero, the low-side will be off the LA1313 enters Hi-zi state. The output capacitors discharge slowly to GND through R1 and R2. When VFB drops below the reference voltage, the HS-FET is turned on again. This operation improves device efficiency greatly when the output current is low.

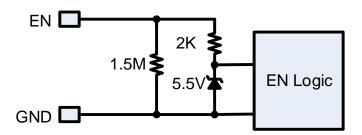

### **Enable (EN) Control**

Enable (EN) is a digital control pin that turns the regulator on and off. Drive EN high to turn on the regulator. Drive EN low to turn off the regulator. An internal  $1.5 \text{M}\Omega$  resistor from EN to GND allows EN to be floated to shut down the chip. EN is clamped internally using a 5.5 V Zener diode. EN can connected to VIN directly by a resistor.

The EN Pin can connect to VIN by a pull-up resistor, but EN input current need below 100uA. For example, if VIN=24V, the IZener=(24-5.5)/RPULL-UP<100uA, So, RPULL-UP>185KO.

Figure 2. Zener Diode between EN and GND

### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The LA1313 UVLO comparator monitors the input voltage. The UVLO rising threshold is 4.28V(typically), while its falling threshold is consistently 3.9V.

### Internal Soft Start (SS)

Soft start (SS) prevents the converter output voltage from overshooting during start-up. When the chip starts, the internal circuitry generates a soft-start voltage (VSS) that ramps up linearly. When SS is below REF, SS overrides REF, so the error amplifier uses SS as the reference. When SS exceeds REF, the error amplifier uses REF as the reference. The SS time is set to 2.4ms(typically) internally.

### Over-Current Protection (OCP) and Short Circuit Protection (SCP)

The LA1313 has a valley current-limit control. During LS-FET on, the inductor current is monitored. If the current is higher than valley current limit, the LS limit compactor active. The device enters over current protection mode. High side will not be turned on until the valley current limit disappear. Meanwhile, the output voltage drops until VFB is below the under voltage (UV) threshold (typically 35% of the reference). Once UV is triggered, the LA1313 enters hiccup mode to restart the part periodically.

During OCP, the device attempts to recover from the over-current fault with hiccup mode. In hiccup mode, the chip disables the output power stage, discharges the soft start, and attempts to soft start again automatically. If the over-current condition still holds after the soft start ends, the device repeats this operation cycle until the over-current condition is removed and the output rises back to regulation levels. OCP is a non-latch protection.

#### **Pre-Bias Start-Up**

The LA1313 is designed for monotonic start-up into pre-biased loads. If the output is pre-biased to a certain voltage during start-up, the BST voltage is refreshed and charged, and

the voltage on the soft start is charged as well. If the BST voltage exceeds its rising threshold voltage and the soft-start voltage exceeds the sensed output voltage at FB, the part works normally.

#### **Output OVP and UVP**

The LA1313 monitors a resistor divided VFB to detect over- and under-voltage. When VFB becomes higher than 115%(typically) of the target voltage, the over-voltage protection (OVP) comparator output goes high, and the circuit will turn on the low side MOSFET to discharge the output. LSFET will turned off until the negative current (-1.1A typically) limit is triggered then LSFET will remain off for 5us to turn on again. IC will repeat this behavior until the output OVP condition is removed. When VFB drops below 35%(typically) of VREF, the UVP comparator output goes high, and the LA1313 enters the hiccup protection.

#### **Large Duty Cycle Operation**

When LA1313 will automatically extend the On time to support the application when VIN is close to VOUT. The frequency extend circuit will be triggered when Toff min time is reached. The LA1313 can support up to 98% maximum duty cycle.

#### **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 150°C, the entire chip shuts down. When the temperature falls below its lower threshold (typically 130°C), the chip is enabled again.

### **Application Information**

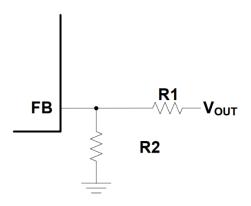

### **Setting the Output Voltage**

The LA1313 output voltage can be set by the external resistor dividers. First, choose a value for R2. R2 should be chosen reasonably, a small R2 will lead to considerable quiescent current loss while too large R2 makes the FB noise sensitive. It I recommended to choose a value within 2k to 100k for R2. The reference voltage is fixed at 0.6V. The feedback network is shown below Figure.

Figure 3. Feedback Network

Choose R1 and R2 using Equation:

$$V_{OUT} = V_{FB}(R_1 + R_2)/R_2$$

### Selecting the Inductor

The inductor is necessary to supply constant current to the output load while being driven by the switched input voltage. A larger-value inductor will result in less ripple current that will result in lower output ripple voltage. However, a larger-value inductor will have a larger physical footprint, higher series resistance, and/or lower saturation current. A good rule for determining the inductance value is to design the peak-to-peak ripple current in the inductor to be in the range of 30% to 60% of the maximum output current, and that the peak inductor current is below the maximum switch current limit. The inductance value can be calculated by:

$$L = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{V_{IN} * \Delta I_L * F_{OSC}}$$

Where  $\Delta IL$  is the inductor ripple current.

The inductor should not saturate under the maximum inductor peak current, where the peak inductor current can be calculated by:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

### **Selecting Input capacitor**

The input current to the step-down converter is discontinuous and therefore requires a capacitor to supply the AC current to the stepdown converter while maintaining the DC input voltage. Ceramic capacitors are recommended for best performance and should be placed as close to the VIN pin as possible. Capacitors with X5R and X7R ceramic dielectrics are recommended because they are fairly stable with temperature fluctuations. The capacitors must also have a ripple current rating greater than the maximum input ripple current of the converter. The input ripple current can be estimated as follows:

$$C_{IN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

The worst case occurs at  $V_{IN} = 2V_{OUT}$ , where:

$$I_{CIN} = \frac{I_{OUT}}{2}$$

For simplification, choose the input capacitor with an RMS current rating greater than half of the maximum load current. The input capacitance value determines the input voltage ripple of the converter. If there is an input voltage ripple requirement in the system, choose the input capacitor that meets the specification. The input voltage ripple can be estimated as follows:

$$\Delta V_{IN} = \frac{I_{OUT}}{F_{OSC} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Under worst-case conditions where V<sub>IN</sub> = 2V<sub>OUT</sub>:

$$\Delta V_{IN} = \frac{1}{4} \times \frac{I_{OUT}}{F_{OSC} \times C_{IN}}$$

#### **Selecting the Output Capacitor**

The output capacitor is required to maintain the DC output voltage. Ceramic or POSCAP capacitors are recommended. The output voltage ripple can be estimated as:

The output capacitor maintains the DC output voltage ripple. Use ceramic, tantalum, or low-ESR electrolytic capacitors. For best results, use low ESR capacitors to keep the output voltage ripple low. The output voltage ripple can be estimated with Equation:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{OSC}*L}*(1 - \frac{V_{OUT}}{V_{IN}})*(R_{ESR} + \frac{1}{8*F_{OSC}*C_{OUT}})$$

Where L is the inductor value, and R<sub>ESR</sub> is the equivalent series resistance (ESR) value of the output capacitor, F<sub>OSC</sub> is the switching frequency. Note that, in real application, should consider that the ceramic capacitor capacitance has derating.

In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. The output voltage ripple caused by ESR is very small. For simplification, the output voltage ripple can be estimated as:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{OSC}*L}*(1-\frac{V_{OUT}}{V_{IN}})*(\frac{1}{8*F_{OSC}*C_{OUT}})$$

In the case of POSCAP capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated as:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{OSC}*L}*(1 - \frac{V_{OUT}}{V_{IN}})*R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The LA1313 can be optimized for a wide range of capacitance and ESR values.

Besides considering the output ripple, chose larger output capacitor also can get better load transient response, but maximum output capacitor limitation should be also considered in design application. If the output capacitor value is too high, the output voltage can't reach the design value during the soft-start time, and then it will fail to regulate. The maximum output capacitor value  $C_{OUT\_max}$  can be limited approximately by:

$$C_{OUT\_MAX} = (I_{limit_{ave}} - I_{OUT}) * T_{ss}/V_{OUT}$$

Where, I<sub>LIM\_AVG</sub> is the average start-up current during soft-start period, Tss is the soft-start time(2.4ms typically).

The recommended parameters for typical output application as table 1 shown.

| V <sub>OUT</sub> (V) | R1 (kΩ) | R2 (kΩ) | L (µH) | С <sub>оит</sub> (uF) |  |  |  |  |

|----------------------|---------|---------|--------|-----------------------|--|--|--|--|

| 5                    | 37.4    | 5.1     | 10     | 44                    |  |  |  |  |

| 3.3                  | 23      | 5.1     | 6.8    | 44                    |  |  |  |  |

| 2.5                  | 16      | 5.1     | 4.7    | 44                    |  |  |  |  |

| 1.8                  | 10.2    | 5.1     | 2.2    | 44                    |  |  |  |  |

| 1.2                  | 5.1     | 5.1     | 2.2    | 44                    |  |  |  |  |

| 1                    | 3.4     | 5.1     | 2.2    | 44                    |  |  |  |  |

Table 1: Resistor Selection for Common Output Voltages

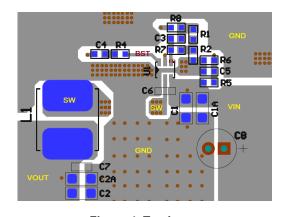

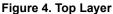

### **PCB** layout Guidelines

Efficient layout of the switching power supplies is critical for stable operation. For the high frequency switching converter, poor layout design may cause poor line or load regulation and stable issues. For best results, refer to below figure and follow the guidelines below and take figures as the reference.

- The high current paths (GND, VIN and SW) should be placed very close to the device with short, direct and wide traces.

- Place the input capacitor as close to VIN and GND as possible.

- Place the external feedback resistors as close to FB as possible.

- Keep the switching node (such as SW, BST) far away from the feedback network.

- Add a grid of thermal vias under the exposed pad to improve thermal conductivity.

Figure 5. Bottom Layer

## **Typical Application Circuits**

Note: C3 is optional for better transient performance.

Figure 6. Typical VOUT=5V/3A application

Note: C3 is optional for better transient performance.

Figure 7. Typical VOUT=3.3V/3A application

Note: C3 is optional for better transient performance.

Figure 8. Typical VOUT=2.5V/3A application

Note: C3 is optional for better transient performance.

Figure 9. Typical VOUT=1.8V/3A application

Note: C3 is optional for better transient performance.

Figure 10. Typical VOUT=1.2V/3A application

Note: C3 is optional for better transient performance.

Figure 11. Typical VOUT=1V/3A application

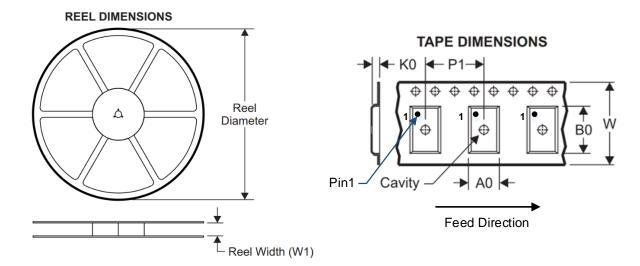

# **Tape and Reel Information**

### Information

| ſ | Device | Package | Pins | SPQ  | Real     | Reel  | A0   | В0   | K0   | P1   | W    |

|---|--------|---------|------|------|----------|-------|------|------|------|------|------|

|   |        | Type    |      |      | Diameter | Width | (mm) | (mm) | (mm) | (mm) | (mm) |

|   |        |         |      |      | (mm)     | W1    |      |      |      |      |      |

|   |        |         |      |      |          | (mm)  |      |      |      |      |      |

|   | LA1313 | TSOT    | 6    | 3000 | 182±1    | 9.5±  | 3.26 | 3.3  | 1.05 | 4    | 8    |

|   |        | 23-6L   |      |      |          | 1.5   | ±0.1 | ±0.1 | ±0.1 | ±0.1 | ±0.1 |

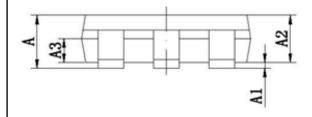

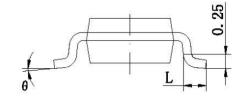

# **Detail Package Outline Drawing**

| SYMBOL     | MI      | LLIMET       | ER   |  |  |

|------------|---------|--------------|------|--|--|

| STAIDOL    | MIN     | NOM          | MAX  |  |  |

| Α          |         | n <u>—</u> 0 | 0.95 |  |  |

| A1         | 0       |              | 0.10 |  |  |

| A2         | 0.75    | 0.80         | 0.85 |  |  |

| A3         | 0.35    | 0.40         | 0.45 |  |  |

| ъ          | 0.38    | -            | 0.46 |  |  |

| <b>b</b> 1 | 0.37    | 0.40         | 0.43 |  |  |

| c          | 0.13    |              | 0.17 |  |  |

| c1         | 0.12    | 0.13         | 0.14 |  |  |

| D          | 2.82    | 2.92         | 3.02 |  |  |

| Е          | 2.60    | 2.80         | 3.00 |  |  |

| <b>E</b> 1 | 1.50    | 1.60         | 1.70 |  |  |

| е          | 0.95BSC |              |      |  |  |

| L          | 0.30    | 0.40         | 0.50 |  |  |

| θ          | 0       | _            | 8°   |  |  |