# Description

The SiT5155 is a  $\pm 0.5$  ppm MEMS Super-TCXO that is engineered for high reliability, GNSS-based precision positioning and timing applications.

Leveraging SiTime's unique DualMEMS™ temperature sensing and TurboCompensation™ technologies, the SiT5155 delivers the best dynamic performance for timing stability in the presence of environmental stressors such as air flow, temperature perturbation, vibration, shock, and electromagnetic interference. This device also integrates multiple on-chip regulators to filter power supply noise, eliminating the need for a dedicated external LDO.

The SiT5155 offers three device configurations that can be ordered using Ordering Codes for:

- 1) TCXO with non-pullable output frequency,

- 2) VCTCXO allowing voltage control of output frequency, and

- DCTCXO, enabling digital control of output frequency using an I<sup>2</sup>C interface, pullable to 5 ppt (parts per trillion) resolution.

The SiT5155 can be factory programmed for specific combinations of frequency, voltage, and pull range. Programmability enables designers to optimize clock configurations while eliminating long lead times and customization costs associated with quartz devices where each frequency is custom built.

Refer to Manufacturing Guideline for proper reflow profile and PCB cleaning recommendations to ensure best performance.

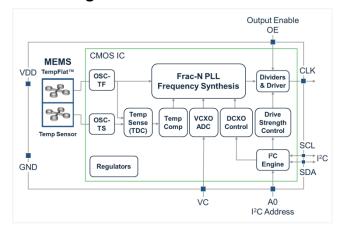

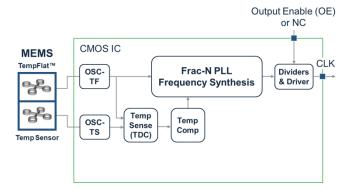

# **Block Diagram**

Figure 1. SiT5155 Block Diagram

#### **Features**

- 12 frequencies from 10 MHz to 40 MHz

- Factory programmable options for short lead time

- Best dynamic stability under airflow, thermal shock

- ±0.5 ppm stability across temperature

- ±15 ppb/°C typical frequency slope (ΔF/ΔT)

- -40°C to +105°C operating temperature

- No activity dips or micro jumps

- Resistant to shock, vibration and board bending

- On-chip regulators eliminate the need for external LDOs

- Digital frequency pulling (DCTCXO) via I<sup>2</sup>C

- Digital control of output frequency and pull range

- Up to ±3200 ppm pull range

- Frequency pull resolution down to 5 ppt

- 2.5 V, 2.8 V, 3.0 V and 3.3 V supply voltage

- LVCMOS or clipped sinewave output

- RoHS and REACH compliant

- Pb-free, Halogen-free, Antimony-free

# **Applications**

- Precision GNSS systems

- Microwave backhaul

- Professional audio and video equipment

- Network routers and switches

- Storage and servers

- Test and measurement

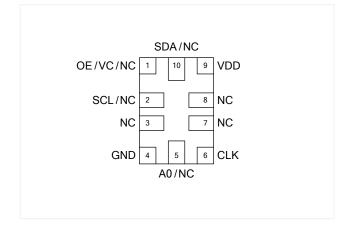

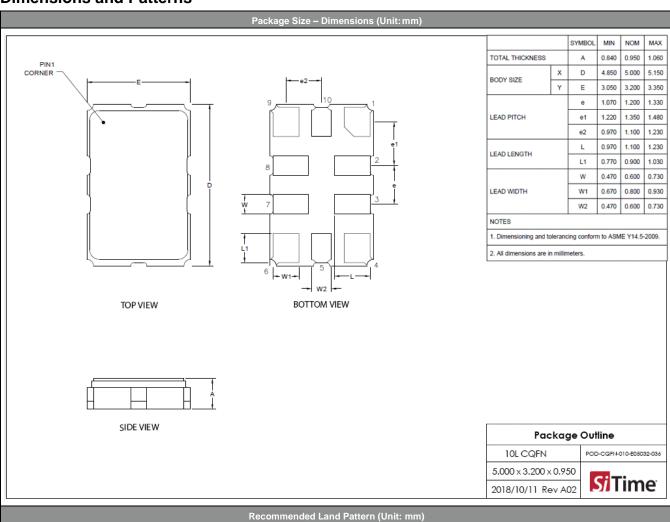

# 5.0 mm x 3.2 mm Package Pinout

Figure 2. Pin Assignments (Top view) (Refer to Table 13 for Pin Descriptions)

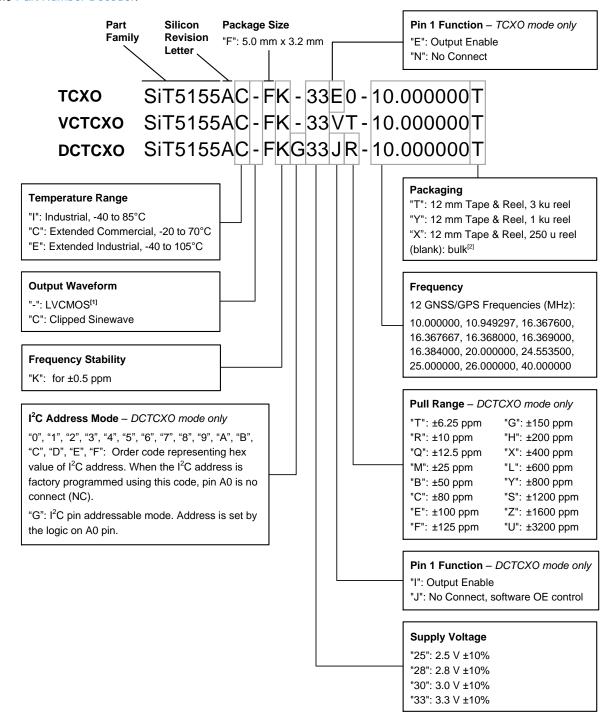

## **Ordering Information**

The part number guide illustrated below is for reference only, in which boxes identify order codes having more than one option. To customize and build an exact part number, use the SiTime Part Number Generator. To validate the part number, use the SiTime Part Number Decoder.

#### Notes:

- 1. "-" corresponds to the default rise/fall time for LVCMOS output as specified in Table 1 (Electrical Characteristics). Contact SiTime for other rise/fall time options for best EMI or driving multiple loads. For differential outputs, contact SiTime.

- 2. Bulk is available for sampling only.

# **TABLE OF CONTENTS**

| Description                                                                               |    |

|-------------------------------------------------------------------------------------------|----|

| Features                                                                                  | 1  |

| Applications                                                                              | 1  |

| Block Diagram                                                                             | 1  |

| 5.0 mm x 3.2 mm Package Pinout                                                            | 1  |

| Ordering Information                                                                      | 2  |

| Electrical Characteristics                                                                | 4  |

| Device Configurations and Pin-outs                                                        | 9  |

| Pin-out Top Views                                                                         |    |

| Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs                             | 10 |

| Waveforms                                                                                 | 12 |

| Timing Diagrams                                                                           | 13 |

| Typical Performance Plots                                                                 | 14 |

| Architecture Overview                                                                     | 16 |

| Frequency Stability                                                                       |    |

| Output Frequency and Format                                                               | 16 |

| Output Frequency Tuning                                                                   |    |

| Pin 1 Configuration (OE, VC, or NC)                                                       | 17 |

| Device Configurations                                                                     | 17 |

| TCXO Configuration                                                                        | 17 |

| VCTCXO Configuration                                                                      | 18 |

| DCTCXO Configuration                                                                      | 19 |

| VCTCXO-Specific Design Considerations                                                     | 20 |

| Linearity                                                                                 |    |

| Control Voltage Bandwidth                                                                 | 20 |

| FV Characteristic Slope K <sub>V</sub>                                                    |    |

| Pull Range, Absolute Pull Range                                                           | 21 |

| DCTCXO-Specific Design Considerations                                                     | 22 |

| Pull Range and Absolute Pull Range                                                        | 22 |

| Output Frequency                                                                          | 23 |

| I <sup>2</sup> C Control Registers                                                        | 25 |

| Register Descriptions                                                                     | 25 |

| Register Address: 0x00. Digital Frequency Control Least Significant Word (LSW)            | 25 |

| Register Address: 0x01. OE Control, Digital Frequency Control Most Significant Word (MSW) |    |

| Register Address: 0x02. DIGITAL PULL RANGE CONTROL <sup>[15]</sup>                        |    |

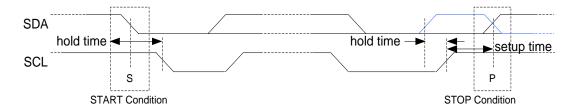

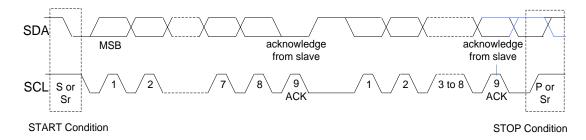

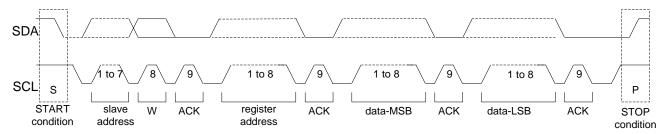

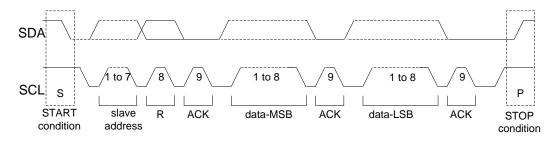

| Serial Interface Configuration Description                                                | 28 |

| Serial Signal Format                                                                      | 28 |

| Parallel Signal Format                                                                    | 29 |

| Parallel Data Format                                                                      | 29 |

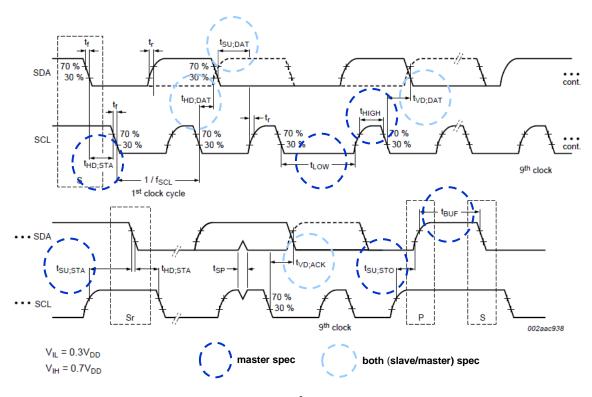

| I <sup>2</sup> C Timing Specification                                                     | 31 |

| I <sup>2</sup> C Device Address Modes                                                     | 32 |

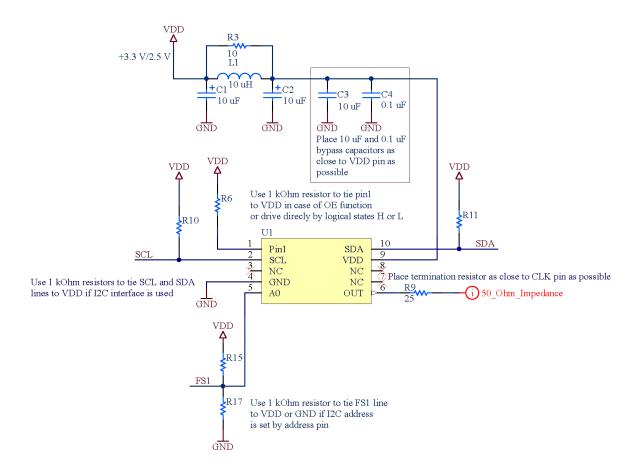

| Schematic Example                                                                         | 33 |

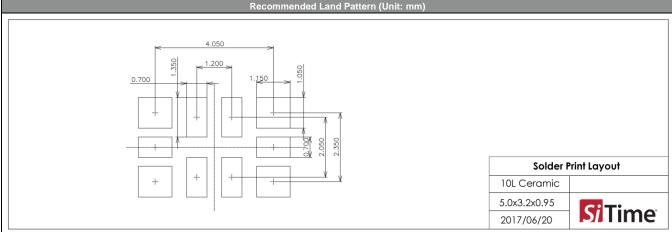

| Dimensions and Patterns                                                                   | 34 |

| Layout Guidelines                                                                         | 35 |

| Manufacturing Guidelines                                                                  |    |

| Additional Information                                                                    | 36 |

| Revision History                                                                          | 37 |

# **Electrical Characteristics**

All Min and Max limits are specified over temperature and rated operating voltage with 15 pF output load unless otherwise stated. Typical values are at 25°C and 3.3 V Vdd.

**Table 1. Output Characteristics**

| Parameters                                          | Symbol      | Min.    | Тур.                       | Max.         | Unit        | Condition                                                                                                                                   |

|-----------------------------------------------------|-------------|---------|----------------------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |             |         | Freque                     | ncy Covera   | ge          |                                                                                                                                             |

| Nominal Output Frequency Range                      | F_nom       | 10.00   | 0000, 10.9                 | 49297        | MHz         |                                                                                                                                             |

|                                                     |             |         | 7600, 16.3                 |              |             |                                                                                                                                             |

|                                                     |             |         | 8000, 16.36<br>4000, 20.06 |              |             |                                                                                                                                             |

|                                                     |             | 24.55   | 3500, 25.00                | 00000        |             |                                                                                                                                             |

|                                                     |             | 26.00   | 0000, 40.00                |              |             |                                                                                                                                             |

|                                                     | 1           |         | Tempe                      | rature Rang  |             | T                                                                                                                                           |

| Operating Temperature Range                         | T_use       | -20     |                            | +70          | °C          | Extended Commercial, ambient temperature                                                                                                    |

|                                                     |             | -40     | _                          | +85          | °C          | Industrial, ambient temperature                                                                                                             |

|                                                     |             | -40     | _                          | +105         | °C          | Extended Industrial, ambient temperature                                                                                                    |

|                                                     | 1           |         | Freque                     | ency Stabili |             |                                                                                                                                             |

| Frequency Stability over<br>Temperature             | F_stab      | -       | 1                          | ±0.5         | ppm         | Referenced to (max frequency + min frequency)/2 over the rated temperature range. Vc=Vdd/2 for VCTCXO                                       |

| Initial Tolerance                                   | F_init      | _       | -                          | ±1           | ppm         | Initial frequency at 25°C at 48 hours after 2 reflows                                                                                       |

| Supply Voltage Sensitivity                          | F_Vdd       |         | ±7.10                      | ±16.25       | ppb         | Vdd ±5%                                                                                                                                     |

| Output Load Sensitivity                             | F_load      | _       | ±0.81                      | ±2.75        | ppb         | LVCMOS output, 15 pF ±10%. Clipped sinewave output, 10 k $\Omega$    10 pF ±10%                                                             |

| Frequency vs. Temperature Slope                     | ΔF/ΔΤ       | -       | ±15                        | ±25          | ppb/°C      | 0.5°C/min temperature ramp rate, -40 to 105°C                                                                                               |

| Dynamic Frequency Change during<br>Temperature Ramp | F_dynamic   | -       | ±0.13                      | ±0.21        | ppb/s       | 0.5°C/min temperature ramp rate, -40 to 105°C                                                                                               |

| One-Year Aging                                      | F_1y        | -       | ±1                         | _            | ppm         | At 25°C, after 2-days of continued operation. Aging is measured with respect to day 3                                                       |

| 20-Year Aging                                       | F_20y       | -       | ±2                         | _            | ppm         | At 25°C, after 2-days of continued operation. Aging is measured with respect to day 3                                                       |

|                                                     |             | LV      | CMOS Out                   | put Charact  | eristics    |                                                                                                                                             |

| Duty Cycle                                          | DC          | 45      | ı                          | 55           | %           |                                                                                                                                             |

| Rise/Fall Time                                      | Tr, Tf      | 0.8     | 1.2                        | 1.9          | ns          | 10% - 90% Vdd                                                                                                                               |

| Output Voltage High                                 | VOH         | 90%     | ı                          | -            | Vdd         | IOH = +3 mA                                                                                                                                 |

| Output Voltage Low                                  | VOL         | -       | ı                          | 10%          | Vdd         | IOL = -3 mA                                                                                                                                 |

| Output Impedance                                    | Z_out_c     | -       | 17                         | -            | Ohms        | Impedance looking into output buffer, Vdd = 3.3 V                                                                                           |

|                                                     |             | -       | 17                         | -            | Ohms        | Impedance looking into output buffer, Vdd = 3.0 V                                                                                           |

|                                                     |             | -       | 18                         | -            | Ohms        | Impedance looking into output buffer, Vdd = 2.8 V                                                                                           |

|                                                     |             | -       | 19                         | _            | Ohms        | Impedance looking into output buffer, Vdd = 2.5 V                                                                                           |

|                                                     |             | Clipped | Sinewave                   | Output Cha   | aracteristi | ics                                                                                                                                         |

| Output Voltage Swing                                | V_out       | 0.8     | -                          | 1.2          | V           | Clipped sinewave output, 10 kΩ    10 pF ±10%                                                                                                |

| Rise/Fall Time                                      | Tr, Tf      | -       | 3.5                        | 4.6          | ns          | 20% - 80% Vdd, F_nom = 20 MHz                                                                                                               |

|                                                     |             |         | Start-up                   | Characteris  | tics        |                                                                                                                                             |

| Start-up Time                                       | T_start     | -       | 2.5                        | 3.5          | ms          | Time to first pulse, measured from the time Vdd reaches 90% of its final value. Vdd ramp time = 100 µs from 0V to Vdd                       |

| Output Enable Time                                  | T_oe        | -       | _                          | 680          | ns          | See Timing Diagrams section below                                                                                                           |

| Time to Rated Frequency Stability                   | T_stability | -       | 5                          | 45           | ms          | Time to first accurate pulse within rated stability, measured from the time Vdd reaches 90% of its final value. Vdd ramp time = 100 $\mu$ s |

**Table 2. DC Characteristics**

| Parameters          | Symbol | Min. | Тур.    | Max.      | Unit | Condition                                             |  |  |

|---------------------|--------|------|---------|-----------|------|-------------------------------------------------------|--|--|

| Supply Voltage      |        |      |         |           |      |                                                       |  |  |

| Supply Voltage      | Vdd    | 2.25 | 2.5     | 2.75      | >    | Contact SiTime for 2.25 V to 3.63 V continuous supply |  |  |

|                     |        | 2.52 | 2.8     | 3.08      | V    | voltage support                                       |  |  |

|                     |        | 2.7  | 3.0     | 3.3       | V    |                                                       |  |  |

|                     |        | 2.97 | 3.3     | 3.63      | V    |                                                       |  |  |

|                     |        |      | Current | Consumpti | on   |                                                       |  |  |

| Current Consumption | ldd    | -    | 44      | 53        | mA   | F_nom = 20 MHz, No Load, TCXO and DCTCXO modes        |  |  |

|                     |        | _    | 48      | 57        | mA   | F_nom = 20 MHz, No Load, VCTCXO mode                  |  |  |

| OE Disable Current  | l_od   | _    | 43      | 51        | mA   | OE = GND, output weakly pulled down. TCXO, DCTCXO     |  |  |

|                     |        | _    | 47      | 55        | mA   | OE = GND, output weakly pulled down. VCTCXO mode      |  |  |

## **Table 3. Input Characteristics**

| Table 3. Input Characteristics     |                        | 3.61                                                                                                                                    | _           |              | 11-1-      | 0. 154                                                                                                              |

|------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|------------|---------------------------------------------------------------------------------------------------------------------|

| Parameters                         | Symbol                 | Min.                                                                                                                                    | Тур.        | Max.         | Unit       | Condition                                                                                                           |

|                                    | 1                      |                                                                                                                                         | nput Chara  | cteristics - |            | 1                                                                                                                   |

| Input Impedance                    | Z_in                   | 75                                                                                                                                      | -           | -            | kΩ         | Internal pull up to Vdd                                                                                             |

| Input High Voltage                 | VIH                    | 70%                                                                                                                                     | -           | _            | Vdd        |                                                                                                                     |

| Input Low Voltage                  | VIL                    | _                                                                                                                                       | _           | 30%          | Vdd        |                                                                                                                     |

|                                    | Fre                    | quency Tu                                                                                                                               | ning Range  | e - Voltage  | Control o  | r I <sup>2</sup> C mode                                                                                             |

|                                    |                        | ±6.25                                                                                                                                   | _           | -            | ppm        | VCTCXO mode; contact SiTime for ±12.5 and ±25 ppm                                                                   |

| Pull Range                         | PR                     | ±6.25<br>±10<br>±12.5<br>±25<br>±50<br>±80<br>±100<br>±125<br>±150<br>±200<br>±400<br>±600<br>±1200<br>±1600<br>±1600<br>±1600<br>±3200 | -           | -            | ppm        | DCTCXO mode                                                                                                         |

| Absolute Pull Range <sup>[3]</sup> | APR                    | ±2.75                                                                                                                                   | -           | _            | ppm        | DCTCXO, VCTCXO for PR = ±6.25 ppm                                                                                   |

| Upper Control Voltage              | VC_U                   | 90%                                                                                                                                     | _           | _            | Vdd        | VCTCXO mode                                                                                                         |

| Lower Control Voltage              | VC_L                   | -                                                                                                                                       | -           | 10%          | Vdd        | VCTCXO mode                                                                                                         |

| Control Voltage Input Impedance    | VC_z                   | 8                                                                                                                                       | _           | _            | МΩ         | VCTCXO mode                                                                                                         |

| Control Voltage Input Bandwidth    | VC_bw                  | -                                                                                                                                       | 10          | -            | kHz        | VCTCXO mode; contact SiTime for other bandwidth options                                                             |

| Frequency Control Polarity         | F_pol                  | Pos                                                                                                                                     | itive       |              |            | VCTCXO mode                                                                                                         |

| Pull Range Linearity               | PR_lin                 | -                                                                                                                                       | 0.5         | 1.0          | %          | VCTCXO mode                                                                                                         |

|                                    | I <sup>2</sup> C Inter | face Chara                                                                                                                              | cteristics, | 200 Ohm, 5   | 550 pF (Ma | x I <sup>2</sup> C Bus Load)                                                                                        |

| Bus Speed                          | F_I2C                  | ≤ ∠                                                                                                                                     | 100         | kl           | Ηz         | -40 to 105°C                                                                                                        |

|                                    |                        | ≤ 1000                                                                                                                                  |             | kl           | Hz         | -40 to 85°C                                                                                                         |

| Input Voltage Low                  | VIL_I2C                | _                                                                                                                                       | _           | 30%          | Vdd        | DCTCXO mode                                                                                                         |

| Input Voltage High                 | VIH_I2C                | 70%                                                                                                                                     | _           | _            | Vdd        | DCTCXO mode                                                                                                         |

| Output Voltage Low                 | VOL_I2C                | _                                                                                                                                       | _           | 0.4          | V          | DCTCXO mode                                                                                                         |

| Input Leakage current              | lι                     | 0.5                                                                                                                                     | -           | 24           | μA         | 0.1 $V_{DD}$ < VOUT < 0.9 $V_{DD}$ . Includes typical leakage current from 200 kΩ pull resister to VDD. DCTCXO mode |

| Input Capacitance                  | C <sub>IN</sub>        | _                                                                                                                                       | _           | 5            | pF         | DCTCXO mode                                                                                                         |

Note:

3. APR = PR – initial tolerance – 20-year aging – frequency stability over temperature. Refer to Table 17 for APR with respect to other pull range options.

Table 4. Jitter & Phase Noise - LVCMOS, -40°C to 85°C

| Parameters                 | Symbol     | Min. | Тур. | Max.      | Unit   | Condition                                                  |  |  |  |  |

|----------------------------|------------|------|------|-----------|--------|------------------------------------------------------------|--|--|--|--|

| Jitter                     |            |      |      |           |        |                                                            |  |  |  |  |

| RMS Phase Jitter (random)  | T_phj      | 1    | 0.31 | 0.48      | ps     | F_nom = 10 MHz, Integration bandwidth = 12 kHz to 5 MHz    |  |  |  |  |

| RMS Period Jitter          | T_jitt_per | 1    | 0.8  | 1.1       | ps     | F_nom = 10 MHz, population 10 k                            |  |  |  |  |

| Peak Cycle-to-Cycle Jitter | T_jitt_cc  | 1    | 6    | 9         | ps     | F_nom = 10 MHz, population 1 k, measured as absolute value |  |  |  |  |

|                            |            |      | Ph   | ase Noise |        |                                                            |  |  |  |  |

| 1 Hz offset                |            | İ    | -80  | -74       | dBc/Hz |                                                            |  |  |  |  |

| 10 Hz offset               |            | I    | -108 | -102      | dBc/Hz |                                                            |  |  |  |  |

| 100 Hz offset              |            | I    | -127 | -123      | dBc/Hz | F_nom = 10 MHz                                             |  |  |  |  |

| 1 kHz offset               |            | I    | -148 | -145      | dBc/Hz | 1 _1011 = 10 10112                                         |  |  |  |  |

| 10 kHz offset              |            | I    | -154 | -151      | dBc/Hz | TCXO and DCTCXO modes, and VCTCXO mode with                |  |  |  |  |

| 100 kHz offset             |            | I    | -154 | -150      | dBc/Hz | ±6.25 ppm pull range                                       |  |  |  |  |

| 1 MHz offset               |            | I    | -167 | -163      | dBc/Hz |                                                            |  |  |  |  |

| 5 MHz offset               |            | -    | -168 | -164      | dBc/Hz |                                                            |  |  |  |  |

| Spurious                   | T_spur     | -    | -112 | -105      | dBc    | F_nom = 10 MHz, 1 kHz to 5 MHz offsets                     |  |  |  |  |

Table 5. Jitter & Phase Noise - Clipped Sinewave, -40°C to 85°C

| Parameters                | Symbol      | Min. | Тур. | Max. | Unit   | Condition                                               |  |  |  |

|---------------------------|-------------|------|------|------|--------|---------------------------------------------------------|--|--|--|

| Jitter                    |             |      |      |      |        |                                                         |  |  |  |

| RMS Phase Jitter (random) | T_phj       | _    | 0.31 | 0.45 | ps     | F_nom = 20 MHz, Integration bandwidth = 12 kHz to 5 MHz |  |  |  |

|                           | Phase Noise |      |      |      |        |                                                         |  |  |  |

| 1 Hz offset               |             | -    | -74  | -68  | dBc/Hz |                                                         |  |  |  |

| 10 Hz offset              |             | -    | -102 | -97  | dBc/Hz |                                                         |  |  |  |

| 100 Hz offset             |             | -    | -121 | -117 | dBc/Hz | F_nom = 20 MHz                                          |  |  |  |

| 1 kHz offset              |             | -    | -142 | -140 | dBc/Hz | 1 _110111 = 20 Wil 12                                   |  |  |  |

| 10 kHz offset             |             | -    | -148 | -146 | dBc/Hz | TCXO and DCTCXO modes, and VCTCXO mode with             |  |  |  |

| 100 kHz offset            |             | -    | -149 | -145 | dBc/Hz | ±6.25 ppm pull range                                    |  |  |  |

| 1 MHz offset              |             | -    | -162 | -159 | dBc/Hz |                                                         |  |  |  |

| 5 MHz offset              |             | -    | -164 | -160 | dBc/Hz |                                                         |  |  |  |

| Spurious                  | T_spur      | -    | -109 | -104 | dBc    | F_nom = 20 MHz, 1 kHz to 5 MHz offsets                  |  |  |  |

Table 6. Jitter & Phase Noise - LVCMOS, -40°C to 105°C

| Parameters                 | Symbol     | Min. | Тур. | Max.      | Unit   | Condition                                                         |  |  |  |

|----------------------------|------------|------|------|-----------|--------|-------------------------------------------------------------------|--|--|--|

| Jitter                     |            |      |      |           |        |                                                                   |  |  |  |

| RMS Phase Jitter (random)  | T_phj      | -    | 0.31 | 0.48      | ps     | F_nom = 10 MHz, Integration bandwidth = 12 kHz to 5 MHz           |  |  |  |

| RMS Period Jitter          | T_jitt_per | -    | 0.8  | 1.1       | ps     | F_nom = 10 MHz, population 10 k                                   |  |  |  |

| Peak Cycle-to-Cycle Jitter | T_jitt_cc  | 1    | 6    | 9         | ps     | F_nom = 10 MHz, population 1 k, measured as absolute value        |  |  |  |

|                            |            |      | Ph   | ase Noise |        |                                                                   |  |  |  |

| 1 Hz offset                |            | -    | -80  | -74       | dBc/Hz |                                                                   |  |  |  |

| 10 Hz offset               |            | -    | -108 | -102      | dBc/Hz |                                                                   |  |  |  |

| 100 Hz offset              |            | -    | -127 | -123      | dBc/Hz |                                                                   |  |  |  |

| 1 kHz offset               |            | -    | -148 | -145      | dBc/Hz | F_nom = 10 MHz                                                    |  |  |  |

| 10 kHz offset              |            | -    | -154 | -151      | dBc/Hz | TCXO and DCTCXO modes, and VCTCXO mode with                       |  |  |  |

| 100 kHz offset             |            | -    | -154 | -150      | dBc/Hz | ±6.25 ppm pull range                                              |  |  |  |

| 1 MHz offset               |            | -    | -167 | -162      | dBc/Hz |                                                                   |  |  |  |

| 5 MHz offset               |            | -    | -168 | -163      | dBc/Hz |                                                                   |  |  |  |

| Spurious                   | T_spur     | 1    | -112 | -101      | dBc    | F_nom = 10 MHz, 1 kHz to 5 MHz offsets, Vdd = 2.5 V               |  |  |  |

|                            |            | ı    | -112 | -106      | dBc    | F_nom = 10 MHz, 1 kHz to 5 MHz offsets, Vdd = 2.8 V, 3.0 V, 3.3 V |  |  |  |

# Table 7. Jitter & Phase Noise - Clipped Sinewave, -40°C to 105°C

| Parameters                | Symbol | Min. | Тур. | Max.      | Unit   | Condition                                               |  |  |  |

|---------------------------|--------|------|------|-----------|--------|---------------------------------------------------------|--|--|--|

| Jitter                    |        |      |      |           |        |                                                         |  |  |  |

| RMS Phase Jitter (random) | T_phj  | _    | 0.31 | 0.46      | ps     | F_nom = 20 MHz, Integration bandwidth = 12 kHz to 5 MHz |  |  |  |

|                           |        |      | Pha  | ase Noise |        |                                                         |  |  |  |

| 1 Hz offset               |        | -    | -74  | -68       | dBc/Hz |                                                         |  |  |  |

| 10 Hz offset              |        | -    | -102 | -97       | dBc/Hz |                                                         |  |  |  |

| 100 Hz offset             |        | -    | -121 | -117      | dBc/Hz | 5 00 MHz                                                |  |  |  |

| 1 kHz offset              |        | _    | -142 | -140      | dBc/Hz | F_nom = 20 MHz                                          |  |  |  |

| 10 kHz offset             |        | _    | -148 | -146      | dBc/Hz | TCXO and DCTCXO modes, and VCTCXO mode with             |  |  |  |

| 100 kHz offset            |        | -    | -149 | -145      | dBc/Hz | ±6.25 ppm pull range                                    |  |  |  |

| 1 MHz offset              |        | _    | -162 | -158      | dBc/Hz |                                                         |  |  |  |

| 5 MHz offset              |        | _    | -164 | -159      | dBc/Hz | ]                                                       |  |  |  |

| Spurious                  | T_spur | _    | -109 | -103      | dBc    | F_nom = 20 MHz, 1 kHz to 5 MHz offsets                  |  |  |  |

#### **Table 8. Absolute Maximum Limits**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Test Conditions | Value      | Unit |

|----------------------------------------------------------------------|-----------------|------------|------|

| Storage Temperature                                                  |                 | -65 to 125 | °C   |

| Continuous Power Supply Voltage Range (Vdd)                          |                 | -0.5 to 4  | V    |

| Human Body Model (HBM) ESD Protection                                | JESD22-A114     | 2000       | V    |

| Soldering Temperature (follow standard Pb-free soldering guidelines) |                 | 260        | °C   |

| Junction Temperature <sup>[4]</sup>                                  |                 | 130        | °C   |

| Input Voltage, Maximum                                               | Any input pin   | Vdd + 0.3  | V    |

| Input Voltage, Minimum                                               | Any input pin   | -0.3       | V    |

#### Table 9. Thermal Considerations<sup>[5]</sup>

| Package                 | θJA <sup>[6]</sup> (°C/W) | θJC, Bottom (°C/W) |

|-------------------------|---------------------------|--------------------|

| Ceramic 5.0 mm x 3.2 mm | 54                        | 15                 |

- Note:

5. Measured in still air. Refer to JESD51 for  $\theta_{JA}$  and  $\theta_{JC}$  definitions.

- 6. Devices soldered on a JESD51 2s2p compliant board.

#### Table 10. Maximum Operating Junction Temperature[7]

| Max Operating Temperature (ambient) | Maximum Operating Junction Temperature |

|-------------------------------------|----------------------------------------|

| 70°C                                | 80°C                                   |

| 85°C                                | 95°C                                   |

| 105°C                               | 115°C                                  |

#### **Table 11. Environmental Compliance**

| Parameter                       | Test Conditions           | Value | Unit |

|---------------------------------|---------------------------|-------|------|

| Mechanical Shock Resistance     | MIL-STD-883F, Method 2002 | 30000 | g    |

| Mechanical Vibration Resistance | MIL-STD-883F, Method 2007 | 70    | g    |

| Temperature Cycle               | JESD22, Method A104       | -     | -    |

| Solderability                   | MIL-STD-883F, Method 2003 | -     | -    |

| Moisture Sensitivity Level      | MSL1 @260°C               | -     | -    |

<sup>4.</sup> Exceeding this temperature for an extended period of time may damage the device.

<sup>7.</sup> Datasheet specifications are not guaranteed if junction temperature exceeds the maximum operating junction temperature.

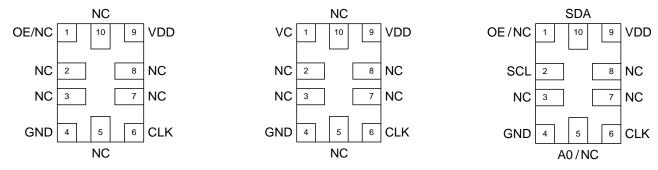

# **Device Configurations and Pin-outs**

## **Table 12. Device Configurations**

| Configuration | Pin 1 | Pin 5 | I <sup>2</sup> C Programmable Parameters                           |

|---------------|-------|-------|--------------------------------------------------------------------|

| TCXO          | OE/NC | NC    | -                                                                  |

| VCTCXO        | VC    | NC    | -                                                                  |

| DCTCXO        | OE/NC | A0/NC | Frequency Pull Range, Frequency Pull Value, Output Enable control. |

#### **Pin-out Top Views**

Figure 3. TCXO

Figure 4. VCTCXO

Figure 5. DCTCXO

## **Table 13. Pin Description**

| Pin | Symbol                    | I/O                | Internal Pull-up/Pull Down<br>Resistor | Function                                                                                                                                                                                                                                   |  |  |  |  |  |

|-----|---------------------------|--------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     |                           | OE – Input         | 100 kΩ Pull-Up                         | H <sup>[8]</sup> : specified frequency output<br>L: output is high impedance. Only output driver is disabled.                                                                                                                              |  |  |  |  |  |

| 1   | OE/NC <sup>[10]</sup> /VC | NC – No Connect    | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |  |  |  |  |  |

|     |                           | VC – Input         | -                                      | Control Voltage in VCTCXO Mode                                                                                                                                                                                                             |  |  |  |  |  |

| 2   | 001 (NO[10]               | SCL – Input        | 200 kΩ Pull-Up                         | I <sup>2</sup> C serial clock input.                                                                                                                                                                                                       |  |  |  |  |  |

| 2   | SCL/NC <sup>1.03</sup>    | No Connect         |                                        | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |  |  |  |  |  |

| 3   | NC <sup>[10]</sup>        | No Connect         | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |  |  |  |  |  |

| 4   | GND                       | Power              | -                                      | Connect to ground                                                                                                                                                                                                                          |  |  |  |  |  |

| 5   | A0/NC <sup>[10]</sup>     | A0 – Input         | 100 kΩ Pull-Up                         | Device I <sup>2</sup> C address when the address selection mode is via the A0 pin. This pin is NC when the I <sup>2</sup> C device address is specified in the ordering code.  A0 Logic Level I <sup>2</sup> C Address 0 1100010 1 1101010 |  |  |  |  |  |

|     |                           | NC[10]/VC          | -                                      | H or L or Open: No effect on output frequency or other device functions.                                                                                                                                                                   |  |  |  |  |  |

| 6   | CLK                       | Output             | -                                      | LVCMOS, or clipped sinewave oscillator output                                                                                                                                                                                              |  |  |  |  |  |

| 7   | NC <sup>[10]</sup>        | No Connect         | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |  |  |  |  |  |

| 8   | NC <sup>[10]</sup>        | No Connect         | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |  |  |  |  |  |

| 9   | VDD                       | Power              | -                                      | Connect to power supply <sup>[9]</sup>                                                                                                                                                                                                     |  |  |  |  |  |

| 10  | SDA /NC[10]               | SDA - Input/Output | 200 kΩ Pull Up                         | I <sup>2</sup> C Serial Data.                                                                                                                                                                                                              |  |  |  |  |  |

| 10  | SDA/NC (10)               | NC – No Connect    | -                                      | H or L or Open: No effect on output frequency or other device functions.                                                                                                                                                                   |  |  |  |  |  |

#### Notes:

- 8. In OE mode for noisy environments, a pull-up resistor of 10  $k\Omega$  or less is recommended if pin 1 is not externally driven. If pin 1 needs to be left floating, use the NC option.

- 9. A 0.1 μF capacitor in parallel with a 10 μF capacitor are required between VDD and GND. The 0.1 μF capacitor is recommended to place close to the device, and place the 10 μF capacitor less than 2 inches away.

- 10. All NC pins can be left floating and do not need to be soldered down.

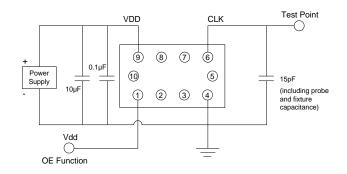

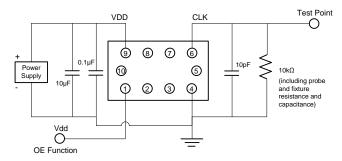

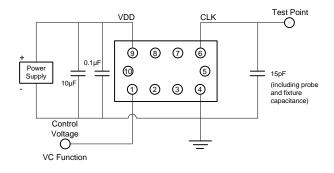

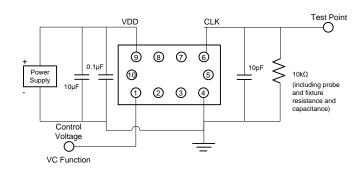

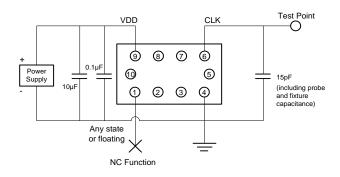

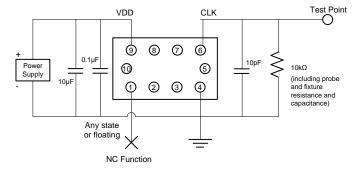

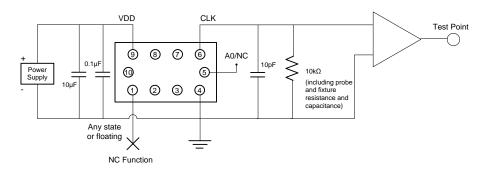

# **Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs**

Figure 6. LVCMOS Test Circuit (OE Function)

Figure 7. Clipped Sinewave Test Circuit (OE Function) for AC and DC Measurements

Figure 8. LVCMOS Test Circuit (VC Function)

Figure 9. Clipped Sinewave Test Circuit (VC Function) for AC and DC Measurements

Figure 10. LVCMOS Test Circuit (NC Function)

Figure 11. Clipped Sinewave Test Circuit (NC Function) for AC and DC Measurements

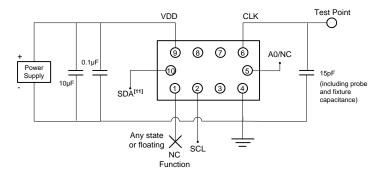

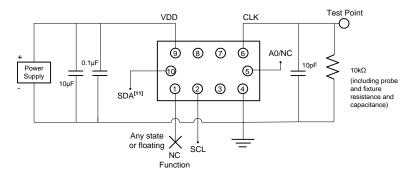

# Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs (continued)

Figure 12. LVCMOS Test Circuit (I<sup>2</sup>C Control), DCTCXO mode for AC and DC Measurements

Figure 13. Clipped Sinewave Test Circuit (I<sup>2</sup>C Control), DCTCXO mode for AC and DC Measurements

Figure 14. Clipped Sinewave Test Circuit for Phase Noise Measurements, Applies to All Configurations (NC Function shown for example only)

#### Note:

11. SDA is open-drain and may require pull-up resistor if not present in I<sup>2</sup>C test setup.

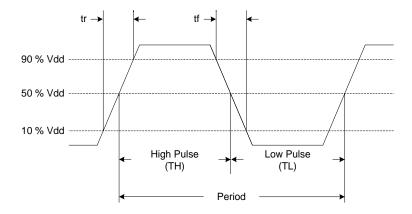

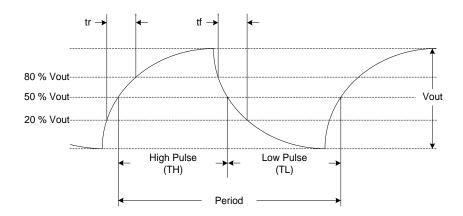

# **Waveforms**

Figure 15. LVCMOS Waveform Diagram<sup>[12]</sup>

Figure 16. Clipped Sinewave Waveform Diagram<sup>[12]</sup>

Note:

12. Duty Cycle is computed as Duty Cycle = TH/Period.

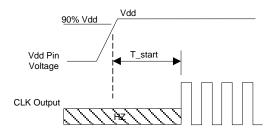

# **Timing Diagrams**

T\_start: Time to start from power-off

Figure 17. Startup Timing

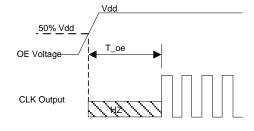

T\_oe: Time to re-enable the clock output

Figure 18. OE Enable Timing (OE Mode Only)

# **Typical Performance Plots**

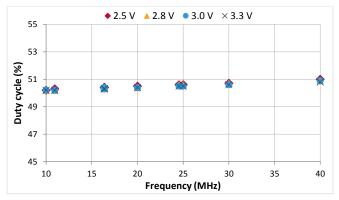

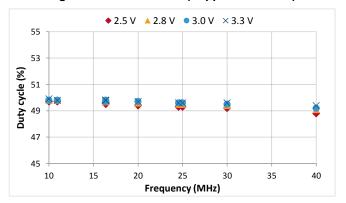

Figure 19. Duty Cycle (LVCMOS)

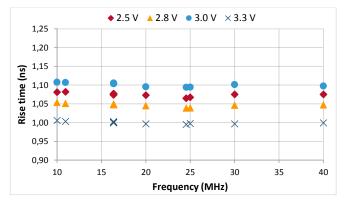

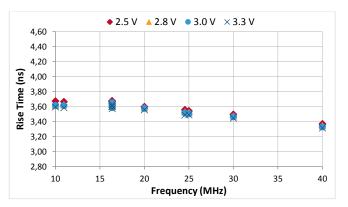

Figure 20. Rise Time (LVCMOS)

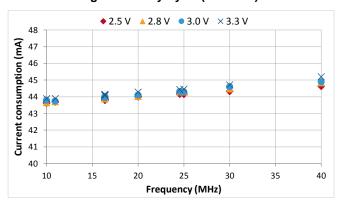

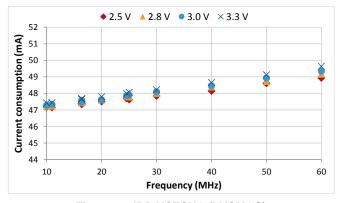

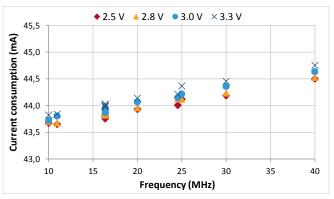

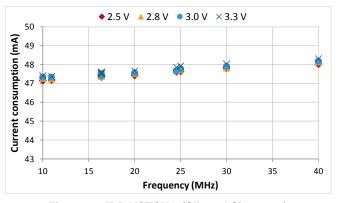

Figure 21. IDD TCXO (LVCMOS)

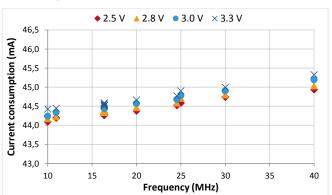

Figure 22. IDD VCTCXO (LVCMOS)

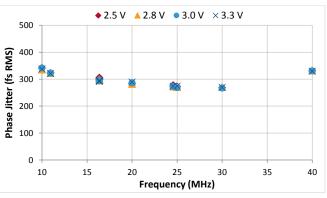

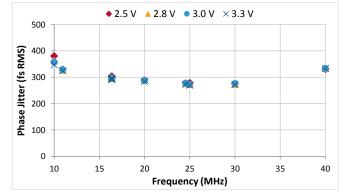

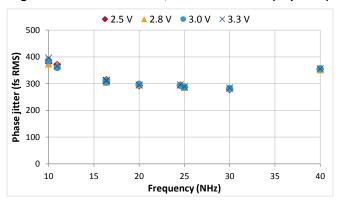

Figure 23. RMS Phase Jitter, TCXO & DCTCXO (LVCMOS)

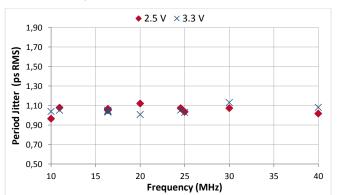

Figure 24. RMS Period Jitter (LVCMOS)

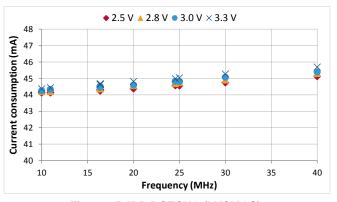

Figure 25. IDD DCTCXO (LVCMOS)

Figure 26. RMS Phase Jitter, VCTCXO (LVCMOS)

# **Typical Performance Plots (continued)**

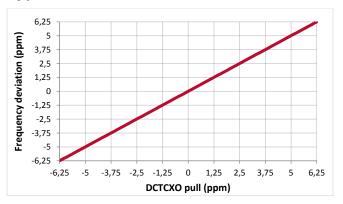

Figure 27. DCTCXO frequency pull characteristic

Figure 29. IDD TCXO (Clipped Sinewave)

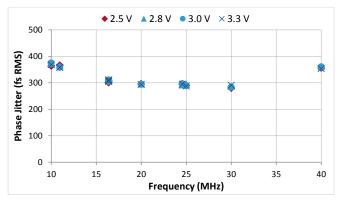

Figure 31. RMS Phase Jitter, TCXO & DCTCXO (Clip Sine)

Figure 33. RMS Phase Jitter, VCTCXO (Clipped Sine)

Figure 28. Rise Time (Clipped Sinewave)

Figure 30. IDD VCTCXO (Clipped Sinewave)

Figure 32. IDD DCTCXO (Clipped Sinewave)

Figure 34. Duty Cycle (Clipped Sinewave)

#### Architecture Overview

Based on SiTime's innovative Elite Platform™, the SiT5155 delivers exceptional dynamic performance, i.e. resilience to environmental stressors such as shock, vibration, and fast temperature transients. Underpinning the Elite platform are SiTime's unique DualMEMS™ temperature sensing architecture and TurboCompensation™ technologies.

DualMEMS is a noiseless temperature compensation scheme. It consists of two MEMS resonators fabricated on the same die substrate. The TempFlat  $^{\text{TM}}$  MEMS resonator is designed with a flat frequency characteristic over temperature whereas the temperature sensing resonator is by design sensitive to temperature changes. The ratio of frequencies between these two resonators provides an accurate reading of the resonator temperature with 20  $\mu\text{K}$  resolution.

By placing the two MEMS resonators on the same die, this temperature sensing scheme eliminates any thermal lag and gradients between resonator and temperature sensor, thereby overcoming an inherent weakness of legacy quartz TCXOs.

The DualMEMS temperature sensor drives a state-of-theart CMOS temperature compensation circuit. The TurboCompensation design, with >100 Hz compensation bandwidth, achieves a dynamic frequency stability that is far superior to any quartz TCXO. The digital temperature compensation enables additional optimization of frequency stability and frequency slope over temperature within any chosen temperature range for a given system design.

The Elite platform also incorporates a high resolution, low noise frequency synthesizer along with the industry standard  $I^2C$  bus. This unique combination enables system designers to digitally control the output frequency in steps as low as 5 ppt and over a wide range up to  $\pm 3200$  ppm.

For more information regarding the Elite platform and its benefits please visit:

- SiTime's breakthroughs section

- TechPaper: DualMEMS Temperature Sensing Technology

- TechPaper: DualMEMS Resonator TDC

#### **Functional Overview**

The SiT5155 is designed for flexibility with a variety of factory programmable options, enabling system designers to configure this precision device for optimal performance in GNSS/GPS applications.

### **Frequency Stability**

The SiT5155 comes in one factory-trimmed stability grade.

Table 14. Stability Grades vs. Ordering Codes

| Frequency Stability Over Temperature | Ordering Code |

|--------------------------------------|---------------|

| ±0.5 ppm                             | К             |

#### **Output Frequency and Format**

The SiT5155 is available in a variety of pre-determined frequencies for both LVCMOS and clipped sinewave output. Ordering codes for the output format are shown below:

Table 15. Output Formats vs. Ordering Codes

| Output Format    | Ordering Code |  |  |  |  |

|------------------|---------------|--|--|--|--|

| LVCMOS           | 66_66         |  |  |  |  |

| Clipped Sinewave | "C"           |  |  |  |  |

#### **Output Frequency Tuning**

In addition to the non-pullable TCXO, the SiT5155 can also support output frequency tuning through either an analog control voltage (VCTCXO), or  $\rm l^2C$  interface (DCTCXO). The  $\rm l^2C$  interface enables 16 factory programmed pull-range options from  $\pm 6.25$  ppm to  $\pm 3200$  ppm. The pull range can also be reprogrammed via  $\rm l^2C$  to any supported pull-range value.

Refer to Device Configuration section for details.

#### Pin 1 Configuration (OE, VC, or NC)

Pin 1 of the SiT5155 can be factory programmed to support three modes: Output Enable (OE), Voltage Control (VC), or No Connect (NC).

**Table 16. Pin Configuration Options**

| Pin 1 Configuration | Operating Mode | Output           |

|---------------------|----------------|------------------|

| OE                  | TCXO/DCTCXO    | Active or High-Z |

| NC                  | TCXO/DCTCXO    | Active           |

| VC                  | VCTCXO         | Active           |

When pin 1 is configured as OE pin, the device output is guaranteed to operate in one of the following two states:

- Clock output with the frequency specified in the part number when Pin 1 is pulled to logic high

- Hi-Z mode with weak pull down when pin 1 is pulled to logic low.

When pin 1 is configured as NC, the device is guaranteed to output the frequency specified in the part number at all times, regardless of the logic level on pin 1.

In the VCTCXO configuration, the user can fine-tune the output frequency from the nominal frequency specified in the part number by varying the pin 1 voltage. The guaranteed allowable variation of the output frequency is specified as pull range. A VCTCXO part number must contain a valid pull-range ordering code.

# **Device Configurations**

The SiT5155 supports 3 device configurations – TCXO, VCTCXO, and DCTCXO. The TCXO and VCTCXO options are directly compatible with the quartz TCXO and VCTCXO. The DCTCXO configuration provides performance enhancement by eliminating VCTCXO's sensitivity to control voltage noise with an I<sup>2</sup>C digital interface for frequency tuning.

Figure 35. Block Diagram - TCXO

#### **TCXO Configuration**

The TCXO generates a fixed frequency output, as shown in Figure 35. The frequency is specified by the user in the frequency field of the device ordering code and then factory programmed. Other factory programmable options include supply voltage, output types (LVCMOS or clipped sinewave), and pin 1 functionality (OE or NC).

Refer to the Ordering Information section at the end of the datasheet for a list of all ordering options.

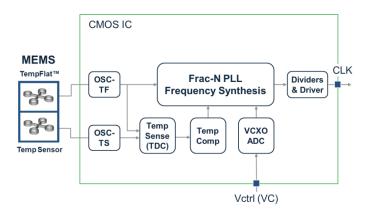

### **VCTCXO** Configuration

A VCTCXO, shown in Figure 36, is a frequency control device whose output frequency is an approximately linear function of control voltage applied to the voltage control pin. VCTCXOs have a number of use cases including the VCO portion of a jitter attenuation/jitter cleaner PLL Loop.

The SiT5155 achieves a 10x better pull range linearity of <0.5% via a high-resolution fractional PLL and low-noise precision analog-to-digital converter. By contrast, quartz-based VCTCXOs change output frequency by varying the capacitive load of a crystal resonator using varactor diodes, which results in linearity of 5% to 105%.

Figure 36. Block Diagram - VCTCXO

Note that the output frequency of the VCTCXO is proportional to the analog control voltage applied to pin 1. Because this control signal is analog and directly controls the output frequency, care must be taken to minimize noise on this pin.

The nominal output frequency is factory programmed per the customer's request to 6 digits of precision and is defined as the output frequency when the control voltage equals Vdd/2. The maximum output frequency variation from this nominal value is set by the pull range, which is also factory programmed to the customer's desired value and specified by the ordering code. The Ordering Information section shows all ordering options and associated ordering codes.

Refer to VCTCXO-Specific Design Considerations for more information on critical VCTCXO parameters including pull range linearity, absolute pull range, control voltage bandwidth, and K<sub>V</sub>.

#### **DCTCXO Configuration**

The SiT5155 offers digital control of the output frequency, as shown in Figure 37. The output frequency is controlled by writing frequency control words over the I<sup>2</sup>C interface.

There are several advantages of DCTCXOs relative to VCTCXOs:

- Frequency control resolution as low as 5 ppt. This high resolution minimizes accumulated time error in synchronization applications.

- 2) Lower system cost A VCTCXO may need a Digital to Analog Converter (DAC) to drive the control voltage input. In a DCTCXO, the frequency control is achieved digitally by register writes to the control registers via I<sup>2</sup>C, thereby eliminating the need for a DAC.

- 3) Better noise immunity The analog signal used to drive the voltage control pin of a VCTCXO can be sensitive to noise, and the trace over which the signal is routed can be susceptible to noise coupling from the system. The DCTCXO does not suffer from analog noise coupling since the frequency control is performed digitally through I<sup>2</sup>C.

- **Output Enable** OF **CMOSIC MEMS** CLK TempFlat™ osc-Frac-N PLL Dividers & Driver Z. **Frequency Synthesis** Drive Temp DCXO osc. Strength Comp TS (TDC) Control Temp Senso SCI 120 L²C Engine SDA A0 I2C Address

Figure 37. Block Diagram

- 4) No frequency-pull non-linearity The frequency pulling is achieved via fractional feedback divider of the PLL, eliminating any pull non-linearity concerns typical of quartz-based VCTCXOs. This improves dynamic performance in closed-loop applications.

- 5) Programmable wide pull range The DCTCXO pulling mechanism is via the fractional feedback divider and is therefore not constrained by resonator pullability as in quartz-based solutions. The SiT5155 offers 16 frequency pull-range options from ±6.25 ppm to ±3200 ppm, providing system designers great flexibility.

Refer to DCTCXO-Specific Design Considerations for more information on critical DCTCXO parameters including pull range, absolute pull range, frequency output, and I<sup>2</sup>C control registers.

# **VCTCXO-Specific Design Considerations**

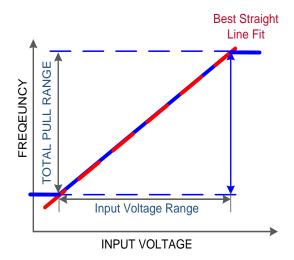

### Linearity

In any VCTCXO, there will be some deviation of the frequency-voltage (FV) characteristic from an ideal straight line. Linearity is the ratio of this maximum deviation to the total pull range, expressed as a percentage. Figure 38 below shows the typical pull linearity of a SiTime VCTCXO. The linearity is excellent (1% maximum) relative to most quartz offerings because the frequency pulling is achieved with a PLL rather than varactor diodes.

Figure 38. Typical SiTime VCTCXO Linearity

#### **Control Voltage Bandwidth**

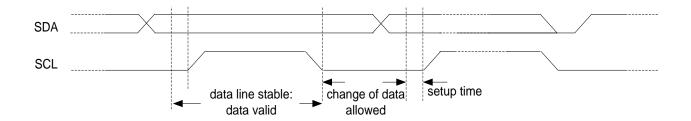

Control voltage bandwidth, sometimes called "modulation rate" or "modulation bandwidth", indicates how fast a VCO can respond to voltage changes at its input. The ratio of the output frequency variation to the input voltage variation, previously denoted by Kv, has a low-pass characteristic in most VCTCXOs. The control voltage bandwidth equals the modulating frequency where the output frequency deviation equals 0.707 (e.g. -3 dB) of its DC value, for DC inputs swept in the same voltage range.

For example, a part with a  $\pm 6.25$  ppm pull range and a 0-3V control voltage can be regarded as having an average KV of 4.17 ppm/V (12.5 ppm/3 V = 4.17 ppm/V). Applying an input of 1.5 V DC  $\pm$  0.5 V (1.0 V to 2.0 V) causes an output frequency change of 4.17 ppm ( $\pm 2.08$  ppm). If the control voltage bandwidth is specified as 10 kHz, the peak-to-peak value of the output frequency change will be reduced to 4.33 ppm/ $\sqrt{2}$  or 2.95 ppm, as the frequency of the control voltage change is increased to 10 kHz.

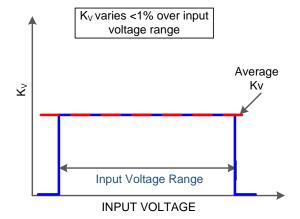

#### FV Characteristic Slope K<sub>V</sub>

The slope of the FV characteristic is a critical design parameter in many low bandwidth PLL applications. The slope is the derivative of the FV characteristic – the deviation of frequency divided by the control voltage change needed to produce that frequency deviation, over a small voltage span, as shown below:

$$K_{v} = \frac{\Delta f_{out}}{\Delta V_{in}}$$

It is typically expressed in kHz/Volt, MHz/Volt, ppm/Volt, or similar units. This slope is usually called "K $_{V}$ " based on terminology used in PLL designs.

The extreme linear characteristic of the SiTime SiT5155 VCTCXO family means that there is very little K<sub>V</sub> variation across the whole input voltage range (typically <1%), significantly reducing the design burden on the PLL designer. Figure 39 below illustrates the typical K<sub>V</sub> variation.

Figure 39. Typical SiTime K<sub>V</sub> Variation

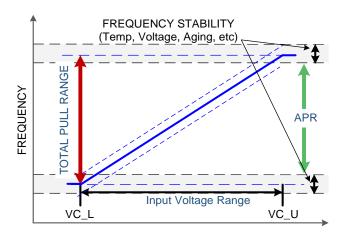

#### Pull Range, Absolute Pull Range

Pull range (PR) is the amount of frequency deviation that will result from changing the control voltage over its maximum range under nominal conditions.

Absolute pull range (APR) is the guaranteed controllable frequency range over all environmental and aging conditions. Effectively, it is the amount of pull range remaining after taking into account frequency stability, tolerances over variables such as temperature, power supply voltage, and aging, i.e.:

$$APR = PR - F_{\text{stability}} - F_{\text{aging}}$$

where  $F_{\rm stability}$  is the device frequency stability due to initial tolerance and variations on temperature, power supply, and load.

Figure 40 shows a typical SiTime VCTCXO FV characteristic. The FV characteristic varies with conditions, so that the frequency output at a given input voltage can vary by as much as the specified frequency stability of the VCTCXO. For such VCTCXOs, the frequency stability and APR are independent of each other. This allows very wide range of pull options without compromising frequency stability.

Figure 40. Typical SiTime VCTCXO FV Characteristic

The upper and lower control voltages are the specified limits of the input voltage range as shown in Figure 40 above. Applying voltages beyond the upper and lower voltages do not result in noticeable changes of output frequency. In other words, the FV characteristic of the VCTCXO saturates beyond these voltages. Figures 1 and 2 show these voltages as Lower Control Voltage (VC\_L) and Upper Control Voltage (VC\_U).

Table 17 below shows the pull range and corresponding APR values for each of the frequency vs. temperature ordering options.

#### Table 17. VCTCXO Pull Range, APR Options[13]

Typical unless specified otherwise. Pull range (PR) is ±6.25 ppm.

| Pull Range<br>Ordering Code | Device Option(s) | APR ppm<br>±0.5 ppm option<br>±2 ppm 20-year aging |

|-----------------------------|------------------|----------------------------------------------------|

| Т                           | VCTCXO           | ±2.75                                              |

#### Notes:

13. APR includes initial tolerance, frequency stability vs. temperature, and the corresponding 20-year aging.

# **DCTCXO-Specific Design Considerations**

# **Pull Range and Absolute Pull Range**

Pull range and absolute pull range are described in the previous section. Table 18 below shows the pull range and corresponding APR values for each of the frequency vs. temperature ordering options.

Table 18. APR Options<sup>[14]</sup>

| Pull Range<br>Ordering Code | Pull Range<br>ppm | APR ppm<br>±0.5 ppm option<br>±2 ppm 20-year aging |

|-----------------------------|-------------------|----------------------------------------------------|

| Т                           | ±6.25             | ±2.75                                              |

| R                           | ±10               | ±6.50                                              |

| Q                           | ±12.5             | ±9.0                                               |

| М                           | ±25               | ±21.5                                              |

| В                           | ±50               | ±46.5                                              |

| С                           | ±80               | ±76.5                                              |

| E                           | ±100              | ±96.5                                              |

| F                           | ±125              | ±121.5                                             |

| G                           | ±150              | ±146.5                                             |

| Н                           | ±200              | ±196.5                                             |

| х                           | ±400              | ±396.5                                             |

| L                           | ±600              | ±596.5                                             |

| Y                           | ±800              | ±796.5                                             |

| s                           | ±1200             | ±1196.5                                            |

| Z                           | ±1600             | ±1596.5                                            |

| U                           | ±3200             | ±3196.5                                            |

#### Notes

<sup>14.</sup> APR includes initial tolerance, frequency stability vs. temperature, and the corresponding 20-year aging.

#### **Output Frequency**

The device powers up at the nominal operating frequency and pull range specified by the ordering code. After power-up both pull range and output frequency can be controlled via I<sup>2</sup>C writes to the respective control registers. The maximum output frequency change is constrained by the pull range limits.

The pull range is specified by the value loaded in the digital pull-range control register. The 16 pull range choices are specified in the control register and range from ±6.25 ppm to ±3200 ppm.

Table 19 below shows the frequency resolution versus pull range programmed value

Table 19. Frequency Resolution versus Pull Range

| Programmed Pull Range | Frequency Resolution  |

|-----------------------|-----------------------|

| ±6.25 ppm             | 5x10 <sup>-12</sup>   |

| ±10 ppm               | 5x10 <sup>-12</sup>   |

| ±12.5 ppm             | 5x10 <sup>-12</sup>   |

| ±25 ppm               | 5x10 <sup>-12</sup>   |

| ±50 ppm               | 5x10 <sup>-12</sup>   |

| ±80 ppm               | 5x10 <sup>-12</sup>   |

| ±100 ppm              | 5x10 <sup>-12</sup>   |

| ±120 ppm              | 5x10 <sup>-12</sup>   |

| ±150 ppm              | 5x10 <sup>-12</sup>   |

| ±200 ppm              | 5x10 <sup>-12</sup>   |

| ±400 ppm              | 1x10 <sup>-11</sup>   |

| ±600 ppm              | 1.4x10 <sup>-11</sup> |

| ±800 ppm              | 2.1x10 <sup>-11</sup> |

| ±1200 ppm             | 3.2x10 <sup>-11</sup> |

| ±1600 ppm             | 4.7x10 <sup>-11</sup> |

| ±3200 ppm             | 9.4x10 <sup>-11</sup> |

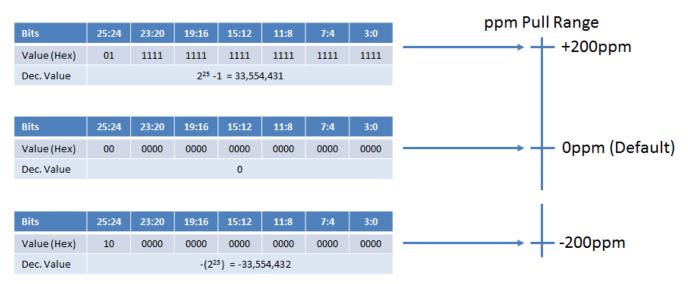

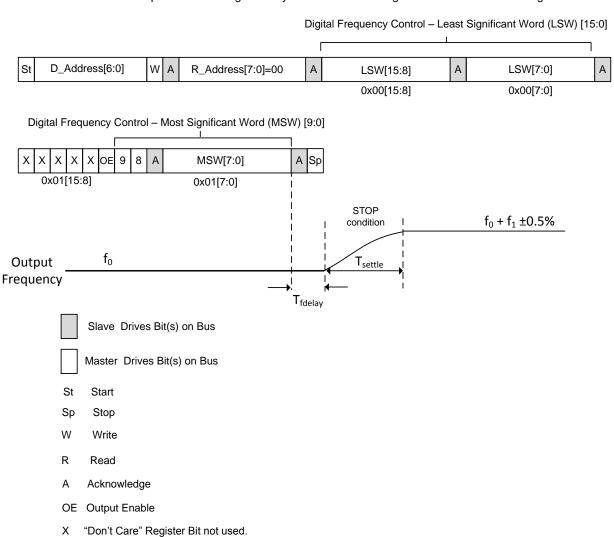

The ppm frequency offset is specified by the 26 bit DCXO frequency control register in two's complement format as described in the I<sup>2</sup>C Register Descriptions. The power up default value is 000000000000000000000000000 which sets the output frequency at its nominal value (0 ppm). To change the output frequency, a frequency control word is written to 0x00[15:0] (Least Significant Word) and 0x01[9:0] (Most Significant Word). The LSW value should be written first followed by the MSW value; the frequency change is initiated after the MSW value is written.

Figure 41. Pull Range and Frequency Control Word

Figure 41 shows how the two's complement signed value of the frequency control word sets the output frequency within the ppm pull range set by 0x02:[3:0]. This example shows use of the ±200 ppm pull range. Therefore, to set the desired output frequency, one just needs to calculate the fraction of full scale value ppm, convert to two's complement binary, and then write these values to the frequency control registers.

The following formula generates the control word value:

Control word value = RND( $(2^{25}-1)$  × ppm shift from nominal/pull range), where RND is the rounding function which rounds the number to the nearest whole number. Two examples follow, assuming a  $\pm 200$  ppm pull range:

#### Example 1:

- Default Output Frequency = 19.2 MHz

- Desired Output Frequency = 19.201728 MHz (+90 ppm)

$2^{25}$ -1 corresponds to +200 ppm, and the fractional value required for +90 ppm can be calculated as follows.

• 90 ppm / 200 ppm ×  $(2^{25}-1) = 15,099,493.95$ .

Rounding to the nearest whole number yields 15,099,494 and converting to two's complement gives a binary value of 111001100110011001100110, or E66666 in hex.

#### Example 2:

- Default Output Frequency = 10 MHz

- Desired Output Frequency = 9.9995 MHz (-50 ppm)

Following the formula shown above,

•  $(-50 \text{ ppm} / 200 \text{ ppm}) \times (2^{25}) = -8,388,608.$

Converting this to two's complement binary results in 11100000000000000000000000, or 3800000 in hex.

To summarize, the procedure for calculating the frequency control word associated with a given ppm offset is as follows:

- Calculate the fraction of the half-pull range needed. For example, if the total pull range is set for ±100 ppm and a +20 ppm shift from the nominal frequency is needed, this fraction is 20 ppm/100 ppm = 0.2

- 2) Multiply this fraction by the full-half scale word value,  $2^{25}$ -1 = 33,554,431, round to the nearest whole number, and convert the result to two's complement binary. Following the +20ppm example, this value is 0.2 × 33,554,431 = 6,710,886.2 and rounded to 6,710,886.

- 3) Write the two's complement binary value starting with the Least Significant Word (LSW) 0x00[16:0], followed by the Most Significant Word (MSW), 0x01[9:0]. If the user desires that the output remains enabled while changing the frequency, a 1 must also be written to the OE control bit 0x01[10] if the device has software OE Control Enabled.

It is important to note that the maximum Digital Control update rate is 38 kHz regardless of I<sup>2</sup>C bus speed.

## I<sup>2</sup>C Control Registers

The SiT5155 enables control of frequency pull range, frequency pull value, and Output Enable via  $I^2C$  writes to the control registers. Table 20 below shows the register map summary, and detailed register descriptions follow.

### Table 20. Register Map Summary

| Address | Bits    | Access                                                                                                                                                                              | Description                                            |  |  |  |  |  |  |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| 0x00    | [15:0]  | RW                                                                                                                                                                                  | DIGITAL FREQUENCY CONTROL LEAST SIGNIFICANT WORD (LSW) |  |  |  |  |  |  |

| 0x01    | [15:11] | R                                                                                                                                                                                   | NOT USED                                               |  |  |  |  |  |  |

|         | [10]    | [10] RW OE Control. This bit is only active if the output enable function is under software conconfigured for hardware control using the OE pin, writing to this bit has no effect. |                                                        |  |  |  |  |  |  |

|         | [9:0]   | RW                                                                                                                                                                                  | DIGITAL FREQUENCY CONTROL MOST SIGNIFICANT WORD (MSW)  |  |  |  |  |  |  |

| 0x02    | [15:4]  | R                                                                                                                                                                                   | NOT USED                                               |  |  |  |  |  |  |

|         | [3:0]   | RW                                                                                                                                                                                  | DIGITAL PULL RANGE CONTROL                             |  |  |  |  |  |  |

# **Register Descriptions**

## Register Address: 0x00. Digital Frequency Control Least Significant Word (LSW)

| Bit     | 15 | 14                                                           | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|--------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Access  | RW | RW                                                           | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW |

| Default | 0  | 0                                                            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Name    |    | DIGITAL FREQUENCY CONTROL LEAST SIGNIFICANT WORD (LSW)[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Bits | Name                                                   | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|--------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|