# 2/3-Port EtherCAT® Slave Controller with Integrated Ethernet PHYs

#### **Highlights**

- 2/3-port EtherCAT slave controller with 8 Fieldbus Memory Management Units (FMMUs) and 8 SyncManagers

- Interfaces to most 8/16-bit embedded controllers and 32-bit embedded controllers with an 8/16-bit bus

- · Integrated Ethernet PHYs with HP Auto-MDIX

- · Wake on LAN (WoL) support

- Low power mode allows systems to enter sleep mode until addressed by the Master

- · Cable diagnostic support

- 1.8V to 3.3V variable voltage I/O

- · Integrated 1.2V regulator for single 3.3V operation

#### **Target Applications**

- · Motor Motion Control

- · Process/Factory Automation

- · Communication Modules, Interface Cards

- Sensors

- · Hydraulic & Pneumatic Valve Systems

- · Operator Interfaces

#### **Key Benefits**

- Integrated high-performance 100Mbps Ethernet transceivers

- Compliant with IEEE 802.3/802.3u (Fast Ethernet)

- Signal Quality Index diagnostics

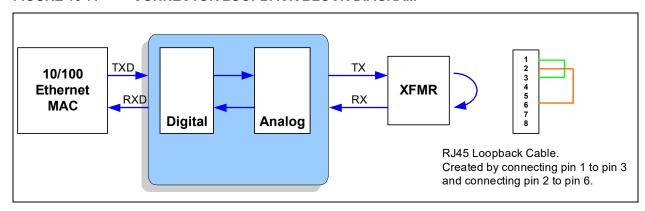

- Loop-back modes

- Automatic polarity detection and correction

- HP Auto-MDIX

- Compatible with EtherCAT P

- · EtherCAT slave controller

- Supports 8 FMMUs

- Supports 8 SyncManagers

- Distributed clock support allows synchronization with other EtherCAT devices

- · 8K bytes of DPRAM

- · 8/16-Bit Host Bus Interface

- Indexed register or multiplexed bus

- Allows local host to enter sleep mode until addressed by EtherCAT Master

- · SPI / SQI (Quad SPI) support

- · Digital I/O Mode for optimized system cost

- 16 available Digital I/Os

- · 3rd port for flexible network configurations

- · Comprehensive power management features

- 3 power-down levels

- Wake on link status change (energy detect)

- Magic packet wakeup, Wake on LAN (WoL), wake on broadcast, wake on perfect DA

- Wakeup indicator event signal

- · Power and I/O

- Integrated power-on reset circuit

- Latch-up performance exceeds 150mA per EIA/JESD78, Class II

- JEDEC Class 3A ESD performance

- Single 3.3V power supply (integrated 1.2V regulator)

- Additional Features

- EEPROM emulation

- Transformer-less link support

- Multifunction GPIOs

- Ability to use low cost 25MHz crystal for reduced BOM

- 25MHz clock output for reference clock daisy chaining

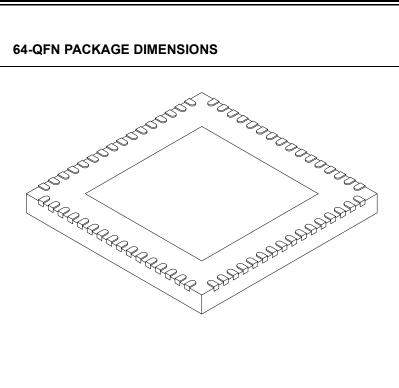

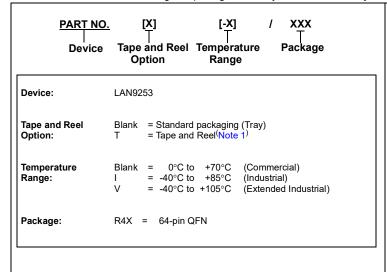

- Packaging

- Pb-free RoHS compliant 64-pin QFN

- Available in commercial, industrial, and extended industrial temp. ranges

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Documentation**

To obtain the most up-to-date version of this documentation, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **Table of Contents**

| 1.0 Preface                                     | 4   |

|-------------------------------------------------|-----|

| 2.0 General Description                         | 8   |

| 3.0 Pin Descriptions and Configuration          |     |

| 4.0 Power Connections                           |     |

| 5.0 Register Map                                | 40  |

| 6.0 Clocks, Resets, and Power Management        | 45  |

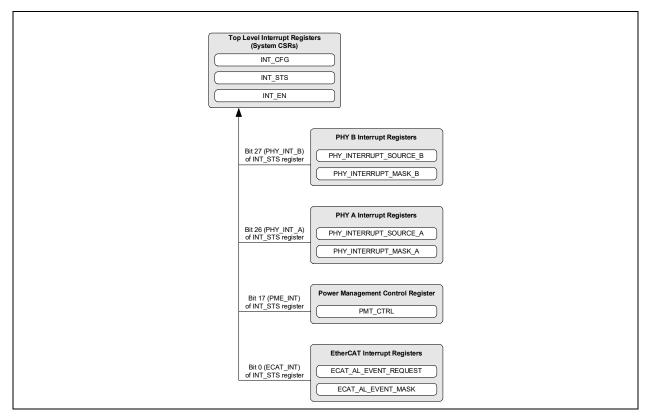

| 7.0 System Interrupts                           |     |

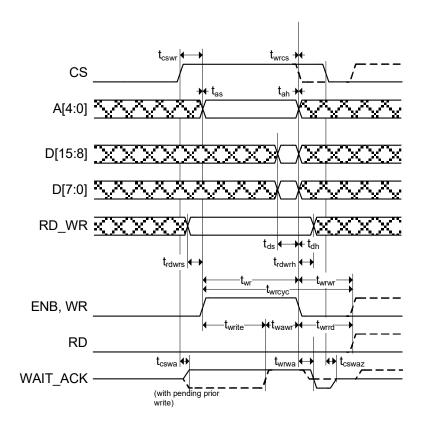

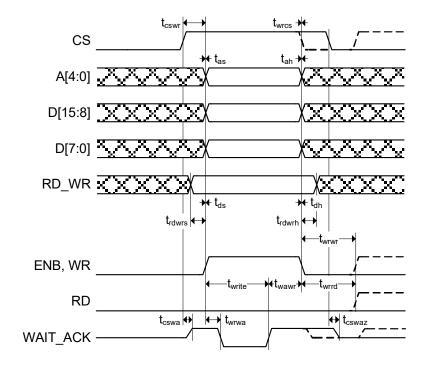

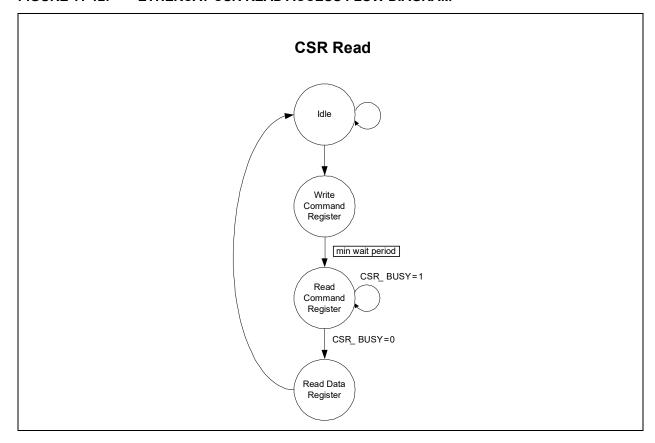

| 8.0 Host Bus Interface                          | 68  |

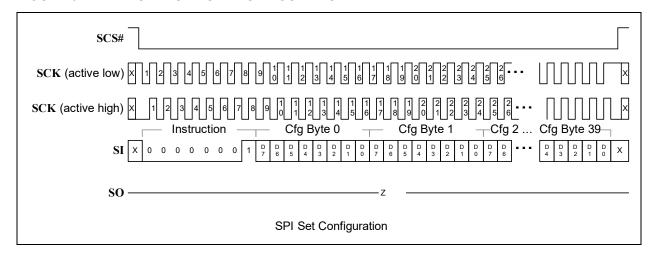

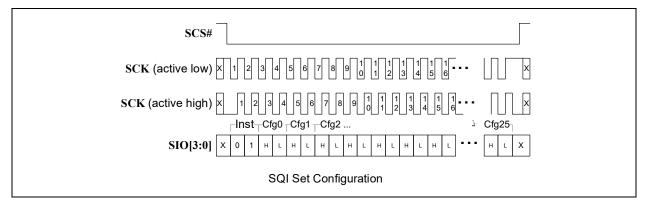

| 9.0 SPI/SQI Slave                               | 142 |

| 10.0 Ethernet PHYs                              | 180 |

| 11.0 EtherCAT                                   | 261 |

| 12.0 EEPROM Interface                           | 366 |

| 13.0 Chip Mode Configuration                    | 368 |

| 14.0 General Purpose Timer & Free-Running Clock | 372 |

| 15.0 Miscellaneous                              | 375 |

| 16.0 JTAG                                       | 379 |

| 17.0 Operational Characteristics                | 381 |

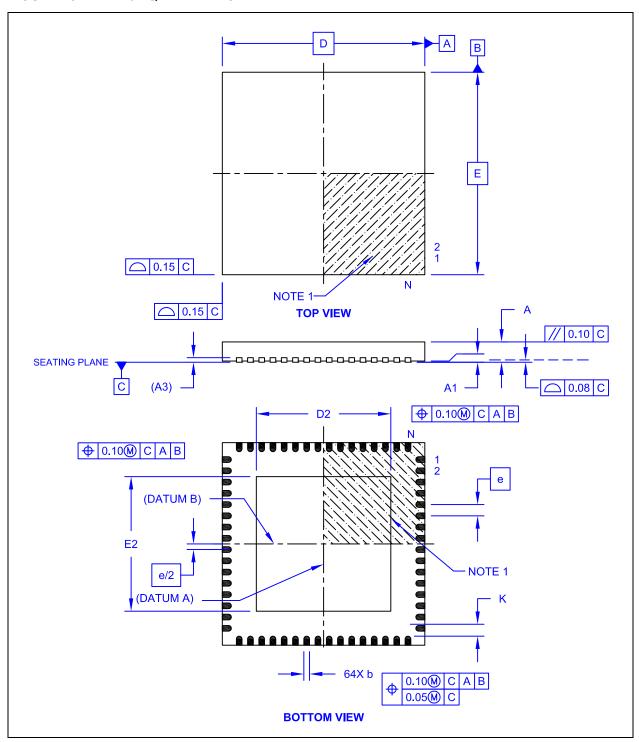

| 18.0 Package Information                        | 396 |

| Appendix A: Revision History                    | 398 |

| The Microchip Web Site                          | 399 |

| Customer Change Notification Service            | 399 |

| Customer Support                                |     |

| Product Identification System                   | 400 |

#### 1.0 PREFACE

#### 1.1 General Terms

TABLE 1-1: GENERAL TERMS

| Term                       | Description                                                                                                                                                                                                       |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 10BASE-T                   | 10 Mbps Ethernet, IEEE 802.3 compliant                                                                                                                                                                            |  |  |  |

| 100BASE-TX                 | 100 Mbps Fast Ethernet, IEEE802.3u compliant                                                                                                                                                                      |  |  |  |

| ADC                        | Analog-to-Digital Converter                                                                                                                                                                                       |  |  |  |

| ALR                        | Address Logic Resolution                                                                                                                                                                                          |  |  |  |

| AN                         | Auto-Negotiation                                                                                                                                                                                                  |  |  |  |

| BLW                        | Baseline Wander                                                                                                                                                                                                   |  |  |  |

| ВМ                         | Buffer Manager - Part of the switch fabric                                                                                                                                                                        |  |  |  |

| BPDU                       | Bridge Protocol Data Unit - Messages which carry the Spanning Tree Protocol information                                                                                                                           |  |  |  |

| Byte                       | 8 bits                                                                                                                                                                                                            |  |  |  |

| CSMA/CD                    | Carrier Sense Multiple Access/Collision Detect                                                                                                                                                                    |  |  |  |

| CSR                        | Control and Status Registers                                                                                                                                                                                      |  |  |  |

| CTR                        | Counter                                                                                                                                                                                                           |  |  |  |

| DA                         | Destination Address                                                                                                                                                                                               |  |  |  |

| DWORD                      | 32 bits                                                                                                                                                                                                           |  |  |  |

| EPC                        | EEPROM Controller                                                                                                                                                                                                 |  |  |  |

| FCS                        | Frame Check Sequence - The extra checksum characters added to the end of an Ethernet frame, used for error detection and correction.                                                                              |  |  |  |

| FIFO                       | First In First Out buffer                                                                                                                                                                                         |  |  |  |

| FSM                        | Finite State Machine                                                                                                                                                                                              |  |  |  |

| GPIO                       | General Purpose I/O                                                                                                                                                                                               |  |  |  |

| Host                       | External system (Includes processor, application software, etc.)                                                                                                                                                  |  |  |  |

| IGMP                       | Internet Group Management Protocol                                                                                                                                                                                |  |  |  |

| Inbound                    | Refers to data input to the device from the host                                                                                                                                                                  |  |  |  |

| Level-Triggered Sticky Bit | This type of status bit is set whenever the condition that it represents is asserted. The bit remains set until the condition is no longer true and the status bit is cleared by writing a zero.                  |  |  |  |

| Isb                        | Least Significant Bit                                                                                                                                                                                             |  |  |  |

| LSB                        | Least Significant Byte                                                                                                                                                                                            |  |  |  |

| LVDS                       | Low Voltage Differential Signaling                                                                                                                                                                                |  |  |  |

| MDI                        | Medium Dependent Interface                                                                                                                                                                                        |  |  |  |

| MDIX                       | Media Independent Interface with Crossover                                                                                                                                                                        |  |  |  |

| MII                        | Media Independent Interface                                                                                                                                                                                       |  |  |  |

| MIIM                       | Media Independent Interface Management                                                                                                                                                                            |  |  |  |

| MIL                        | MAC Interface Layer                                                                                                                                                                                               |  |  |  |

| MLD                        | Multicast Listening Discovery                                                                                                                                                                                     |  |  |  |

| MLT-3                      | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0". |  |  |  |

| msb                        | Most Significant Bit                                                                                                                                                                                              |  |  |  |

| MSB                        | Most Significant Byte                                                                                                                                                                                             |  |  |  |

### TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term     | Description                                                                                                                                                                                                                                                                  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NRZI     | Non Return to Zero Inverted. This encoding method inverts the signal for a "1" and leaves the signal unchanged for a "0"                                                                                                                                                     |  |  |  |

| N/A      | Not Applicable                                                                                                                                                                                                                                                               |  |  |  |

| NC       | No Connect                                                                                                                                                                                                                                                                   |  |  |  |

| OUI      | Organizationally Unique Identifier                                                                                                                                                                                                                                           |  |  |  |

| Outbound | Refers to data output from the device to the host                                                                                                                                                                                                                            |  |  |  |

| PISO     | Parallel In Serial Out                                                                                                                                                                                                                                                       |  |  |  |

| PLL      | Phase Locked Loop                                                                                                                                                                                                                                                            |  |  |  |

| PTP      | Precision Time Protocol                                                                                                                                                                                                                                                      |  |  |  |

| RESERVED | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must always be zero for write operations. Unless otherwise noted, values are not guaranteed when reading reserved bits. Unless otherwise noted, do not read or write to reserved addresses. |  |  |  |

| RTC      | Real-Time Clock                                                                                                                                                                                                                                                              |  |  |  |

| SA       | Source Address                                                                                                                                                                                                                                                               |  |  |  |

| SFD      | Start of Frame Delimiter - The 8-bit value indicating the end of the preamble of an Ethernet frame.                                                                                                                                                                          |  |  |  |

| SIPO     | Serial In Parallel Out                                                                                                                                                                                                                                                       |  |  |  |

| SMI      | Serial Management Interface                                                                                                                                                                                                                                                  |  |  |  |

| SQE      | Signal Quality Error (also known as "heartbeat")                                                                                                                                                                                                                             |  |  |  |

| SSD      | Start of Stream Delimiter                                                                                                                                                                                                                                                    |  |  |  |

| UDP      | User Datagram Protocol - A connectionless protocol run on top of IP networks                                                                                                                                                                                                 |  |  |  |

| UUID     | Universally Unique IDentifier                                                                                                                                                                                                                                                |  |  |  |

| WORD     | 16 bits                                                                                                                                                                                                                                                                      |  |  |  |

### 1.2 Buffer Types

TABLE 1-2: BUFFER TYPES

| BUFFER TYPE | DESCRIPTION                                                                                                                                                                                                                                         |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IS          | Schmitt-triggered input                                                                                                                                                                                                                             |  |  |  |

| O8          | 3.3V output with 8 mA sink and 8 mA source                                                                                                                                                                                                          |  |  |  |

| OD8         | 3.3V open-drain output with 8 mA sink                                                                                                                                                                                                               |  |  |  |

| OD12        | 3.3V open-drain output with 12 mA sink                                                                                                                                                                                                              |  |  |  |

| OS12        | 3.3V open-source output with 12 mA source                                                                                                                                                                                                           |  |  |  |

| VIS         | Variable voltage Schmitt-triggered input                                                                                                                                                                                                            |  |  |  |

| VO8         | Variable voltage output with 8 mA sink and 8 mA source                                                                                                                                                                                              |  |  |  |

| VOD8        | Variable voltage open-drain output with 8 mA sink                                                                                                                                                                                                   |  |  |  |

| VOS8        | Variable voltage open-source output with 8 mA source                                                                                                                                                                                                |  |  |  |

| VO12        | Variable voltage output with 12 mA sink and 12 mA source                                                                                                                                                                                            |  |  |  |

| VOD12       | Variable voltage open-drain output with 12 mA sink                                                                                                                                                                                                  |  |  |  |

| VOS12       | Variable voltage open-source output with 12 mA source                                                                                                                                                                                               |  |  |  |

| PU          | 50 μA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                              |  |  |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added. |  |  |  |

| PD          | 50 μA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                          |  |  |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added.       |  |  |  |

| Al          | Analog input                                                                                                                                                                                                                                        |  |  |  |

| AIO         | Analog bidirectional                                                                                                                                                                                                                                |  |  |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                        |  |  |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                       |  |  |  |

| Р           | Power pin                                                                                                                                                                                                                                           |  |  |  |

### 1.3 Register Nomenclature

TABLE 1-3: REGISTER NOMENCLATURE

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                                                                                    |  |  |

| W                          | Read: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                                                                                 |  |  |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                                                                                |  |  |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                                                                                         |  |  |

| W1S                        | Write One to Set: Writing a one sets the value. Writing a zero has no effect                                                                                                                                                                                                                                                                                                                |  |  |

| W1C                        | Write One to Clear: Writing a one clears the value. Writing a zero has no effect                                                                                                                                                                                                                                                                                                            |  |  |

| WAC                        | Write Anything to Clear: Writing anything clears the value.                                                                                                                                                                                                                                                                                                                                 |  |  |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                                                                                                                                   |  |  |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                                                                                   |  |  |

| RO/LH                      | <b>Read Only, Latch High:</b> Bits with this attribute will stay high until the bit is read. After it is read, the bit will either remain high if the high condition remains, or will go low if the high condition has been removed. If the bit has not been read, the bit will remain high regardless of a change to the high condition. This mode is used in some Ethernet PHY registers. |  |  |

| NASR                       | Not Affected by Software Reset. The state of NASR bits do not change on assertion of a software reset.                                                                                                                                                                                                                                                                                      |  |  |

| RESERVED                   | <b>Reserved Field:</b> Reserved fields must be written with zeros to ensure future compatibility. The value of reserved bits is not guaranteed on a read.                                                                                                                                                                                                                                   |  |  |

#### 2.0 GENERAL DESCRIPTION

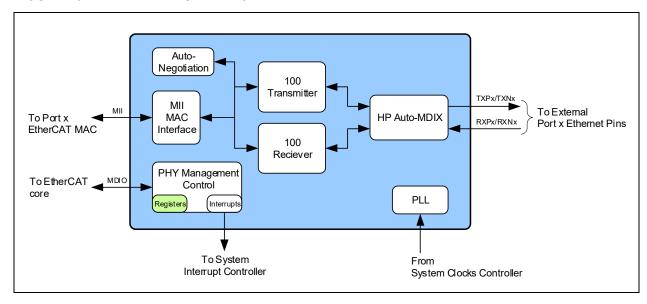

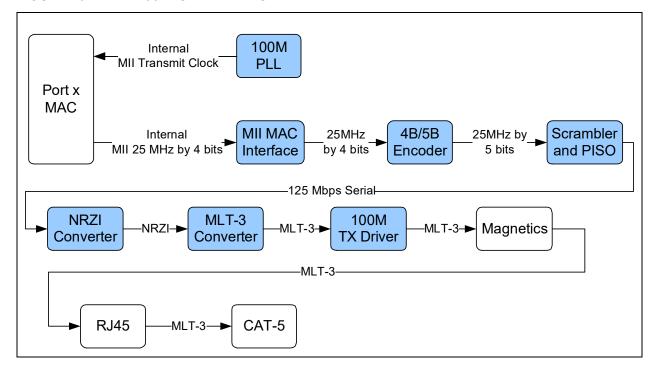

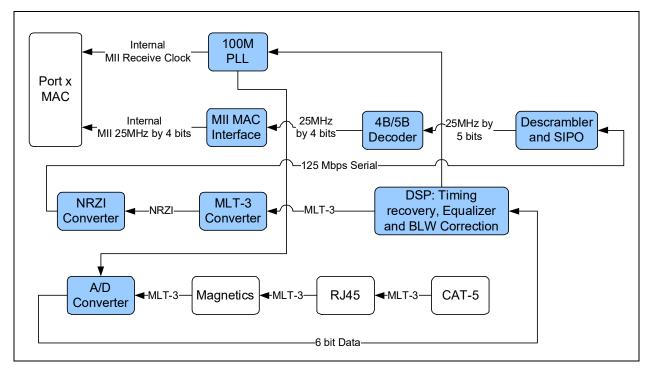

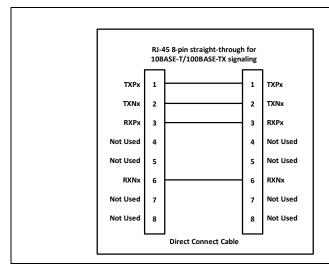

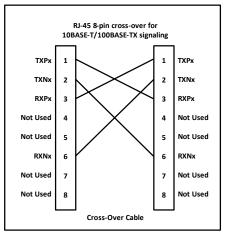

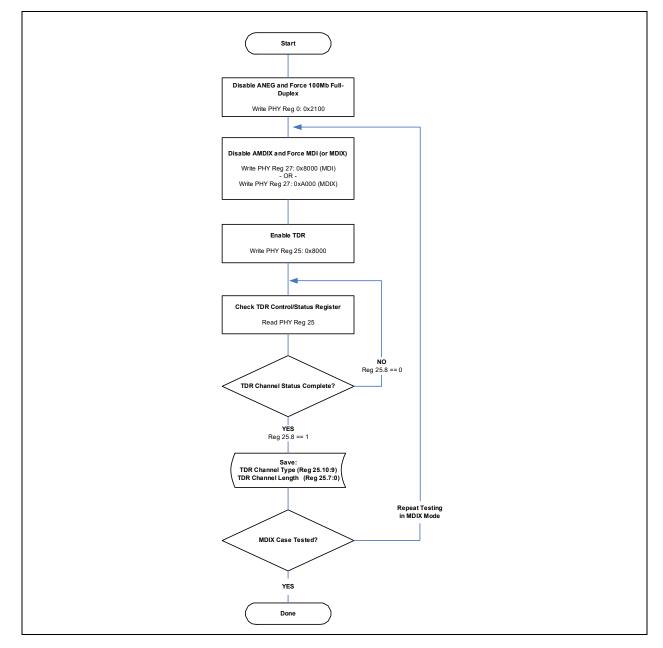

The LAN9253 is a 2/3-port EtherCAT slave controller with dual integrated Ethernet PHYs, each containing a full-duplex 100BASE-TX transceiver that supports 100Mbps (100BASE-TX) operation. The LAN9253 supports HP Auto-MDIX, allowing the use of direct connect or cross-over LAN cables. EtherCAT P and Signal Quality Index PHY diagnostics are supported.

The LAN9253 includes an EtherCAT slave controller with 8K bytes of Dual Port memory (DPRAM) and 8 Fieldbus Memory Management Units (FMMUs). Each FMMU performs the task of mapping logical addresses to physical addresses. The EtherCAT slave controller also includes 8 SyncManagers to allow the exchange of data between the EtherCAT master and the local application. Each SyncManager's direction and mode of operation is configured by the EtherCAT master. Two modes of operation are available: buffered mode or mailbox mode. In the buffered mode, both the local microcontroller and EtherCAT master can write to the device concurrently. The buffer within the LAN9253 will always contain the latest data. If newer data arrives before the old data can be read out, the old data will be dropped. In mailbox mode, access to the buffer by the local microcontroller and the EtherCAT master is performed using handshakes, guaranteeing that no data will be dropped.

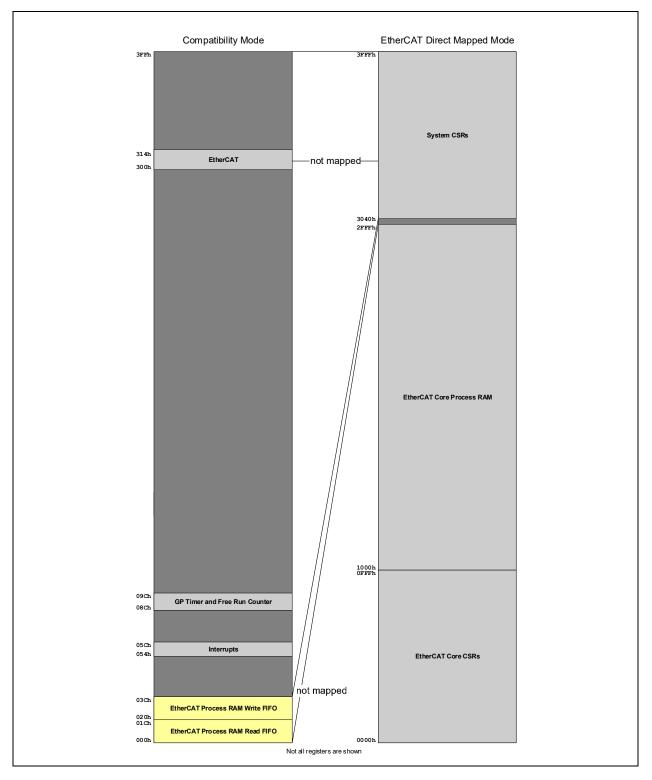

The LAN9253 provides an EtherCAT direct mapping mode, which inserts the EtherCAT registers into the base address space. The EtherCAT direct mapping mode eliminates the need for a command/data access structure, which can increase the speed of smaller data blocks.

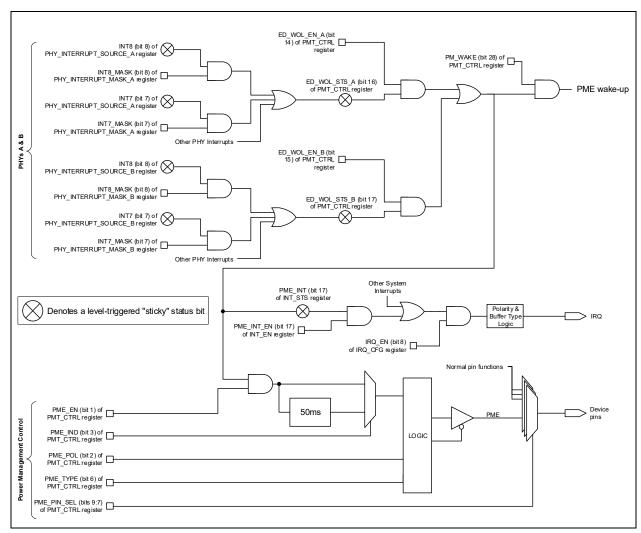

The LAN9253 supports numerous power management and wakeup features. The LAN9253 can be placed in a reduced power mode and can be programmed to issue an external wake signal (IRQ or PME) via several methods, including "Magic Packet", "Wake on LAN", wake on broadcast, wake on perfect DA, and "Link Status Change". This signal is ideal for triggering system power-up using remote Ethernet wakeup events. The device can be removed from the low power state via a host processor command or one of the wake events.

The LAN9253 contains an I<sup>2</sup>C master EEPROM controller for connection to an EEPROM, allowing for the storage and retrieval of static data. The internal EEPROM Loader automatically loads stored configuration settings from the EEPROM into the device at reset. An EEPROM emulation feature, which requires additional software support, is available for EEPROM-less operation.

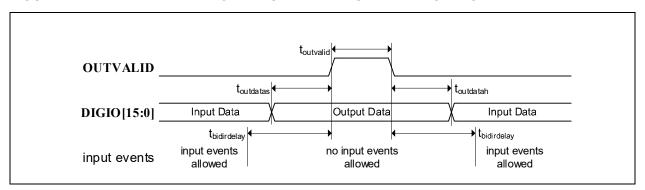

For simple digital modules without microcontrollers, the LAN9253 can also operate in Digital I/O Mode where 16 digital signals can be controlled or monitored by the EtherCAT master.

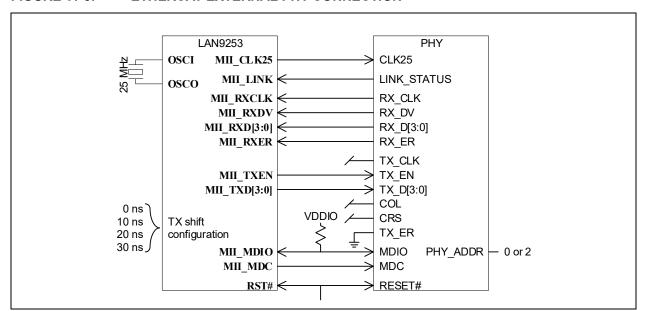

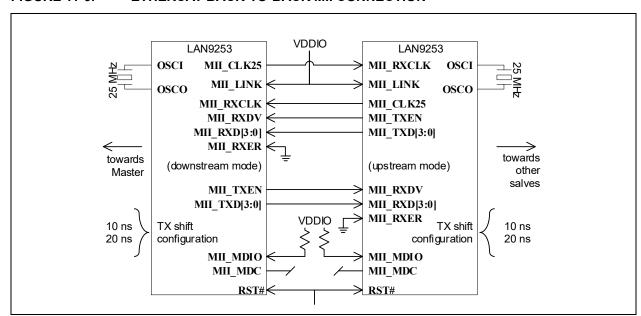

To enable star or tree network topologies, the device can be configured as a 3-port slave, providing an additional MII port. This port can be connected to an external PHY, forming a tap along the current daisy chain, or to another LAN9253 creating a 4-port solution. The MII port can point upstream (as Port 0) or downstream (as Port 2).

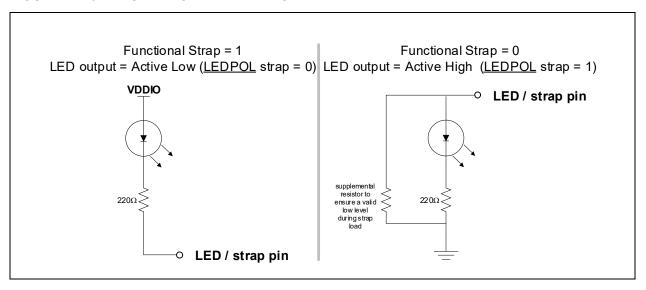

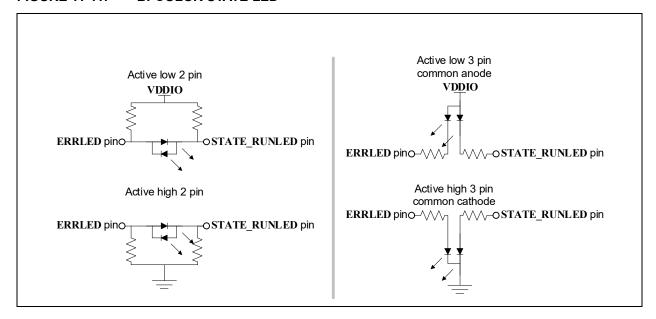

LED support consists of a standard RUN indicator and a LINK / Activity indicator per port. Configuration options enable ERR and STATE RUN indicators.

A 64-bit distributed clock is included to enable high-precision synchronization and to provide accurate information about the local timing of data acquisition.

The LAN9253 can be configured to operate via a single 3.3V supply utilizing an integrated 3.3V to 1.2V linear regulator. The linear regulator may be optionally disabled, allowing usage of a high efficiency external regulator for lower system power dissipation.

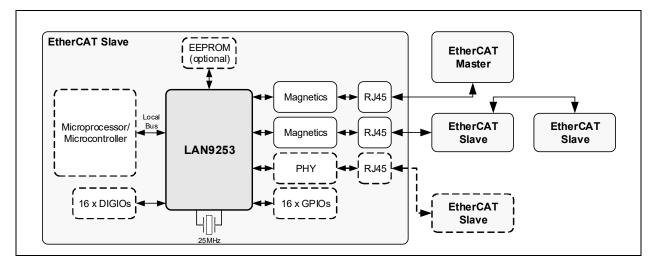

The LAN9253 is available in commercial, industrial, and extended industrial temperature ranges. Figure 2-1 details a typical system application, while Figure 2-2 provides an internal block diagram of the LAN9253.

**Note:** Extended temp. (105°C) is supported only with an external voltage regulator (internal regulator must be disabled) and 2.5V (typ) Ethernet magnetics.

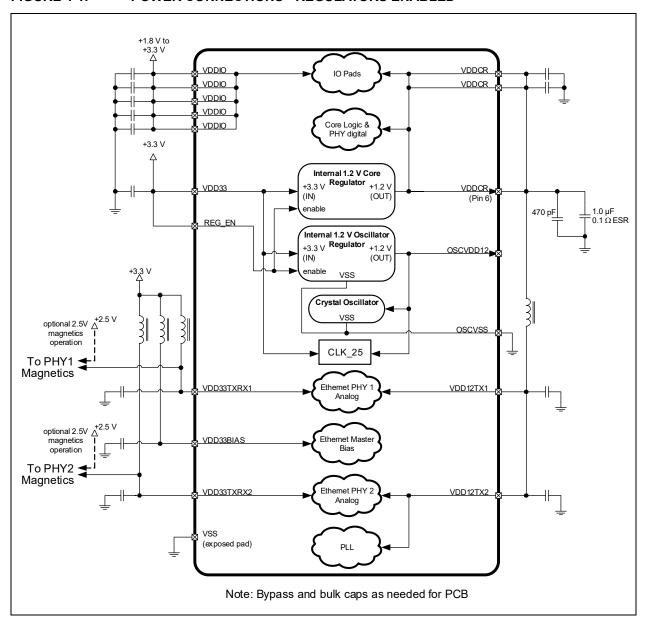

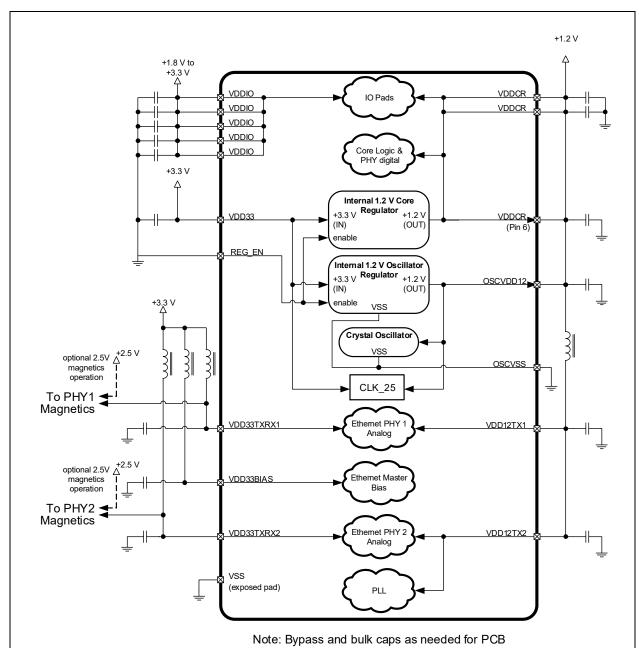

FIGURE 2-1: SYSTEM BLOCK DIAGRAM

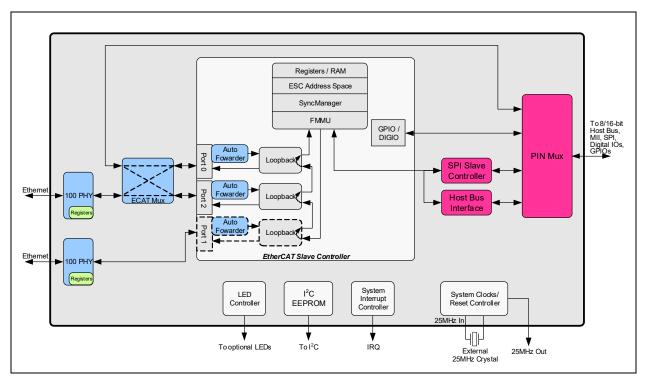

#### FIGURE 2-2: INTERNAL BLOCK DIAGRAM

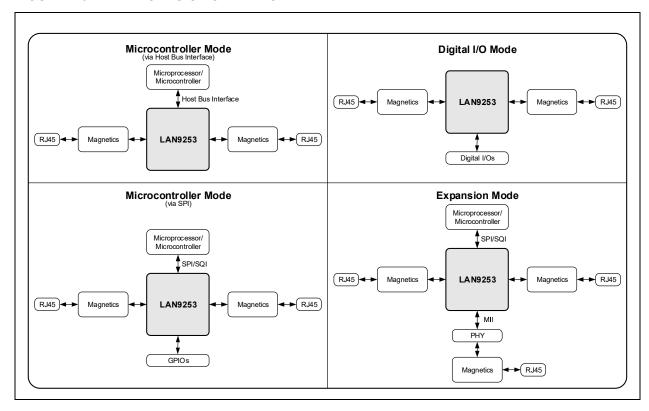

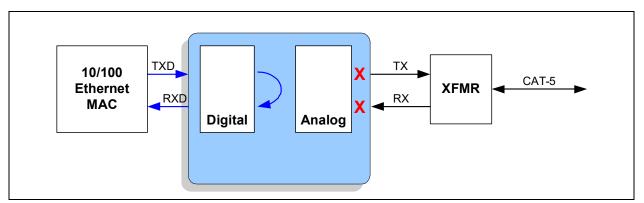

The LAN9253 can operate in Microcontroller, Expansion, or Digital I/O mode:

<u>Microcontroller Mode:</u> The LAN9253 communicates with the microcontroller through an SRAM-like slave interface. The simple, yet highly functional host bus interface provides a glue-less connection to most common 8 or 16-bit microprocessors and microcontrollers as well as 32-bit microprocessors with an 8 or 16-bit external bus.

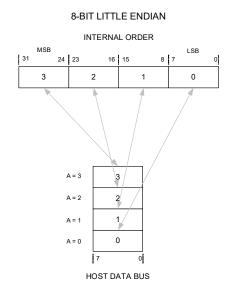

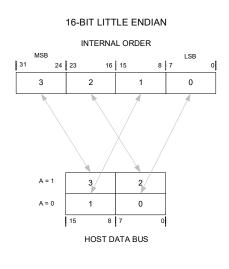

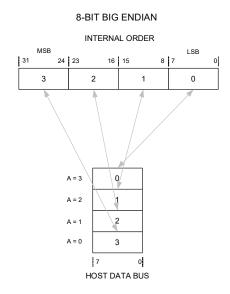

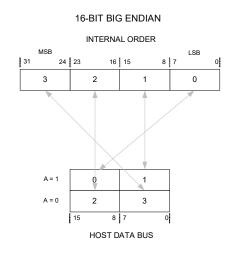

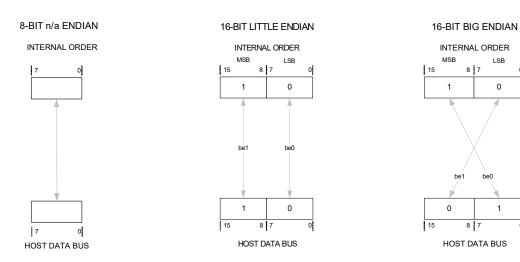

The integrated Host Bus Interface (HBI) supports 8/16-bit operation with big, little, and mixed endian operations. Two process data RAM FIFOs interface the HBI to the EtherCAT slave controller and facilitate the transferring of process data information between the host CPU and the EtherCAT slave. A configurable host interrupt pin allows the device to inform the host CPU of any internal interrupts.

Two user selectable Microcontroller Mode Host Bus Interface (HBI) options are available:

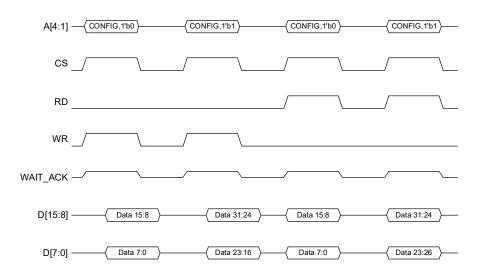

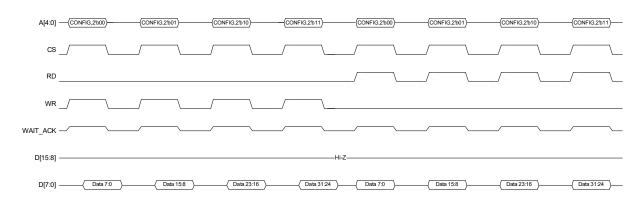

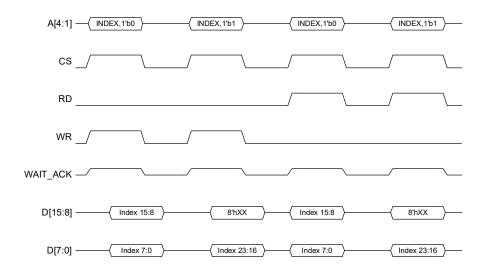

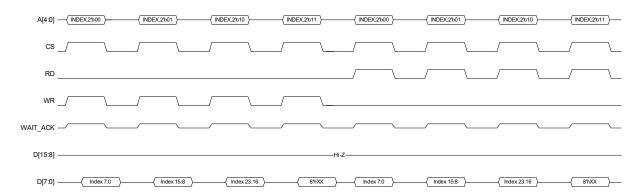

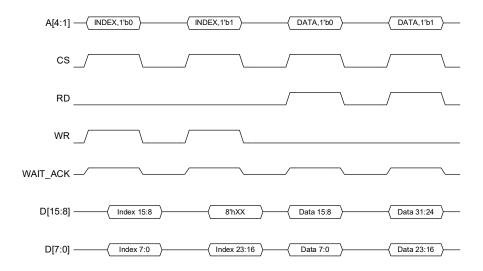

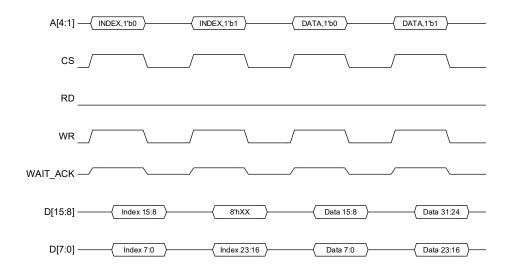

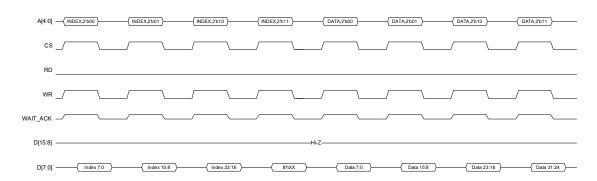

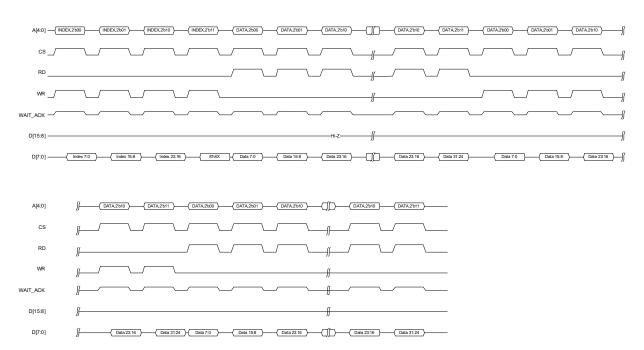

#### Indexed register access

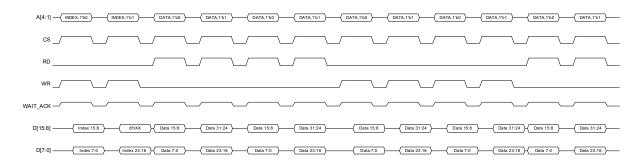

This implementation provides three index/data register banks, each with independent Byte/WORD to DWORD conversion. Internal registers are accessed by first writing one of the three index registers, followed by reading or writing the corresponding data register. Three index/data register banks support up to 3 independent driver threads without access conflicts. Each thread can write its assigned index register without the issue of another thread overwriting it. Two 16-bit cycles or four 8-bit cycles are required within the same 32-bit index/data register however, these access can be interleaved. Non-indexed read and write accesses are supported to the process data FIFOs. The non-indexed FIFO access provides independent Byte/WORD to DWORD conversion, supporting interleaved accesses with the index/data registers.

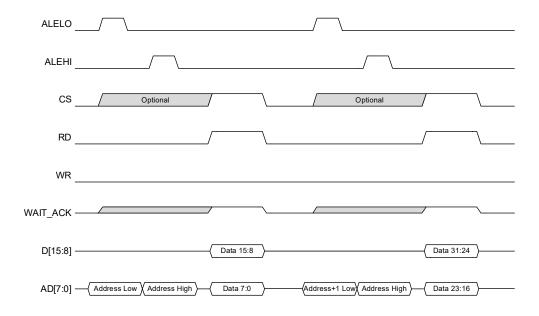

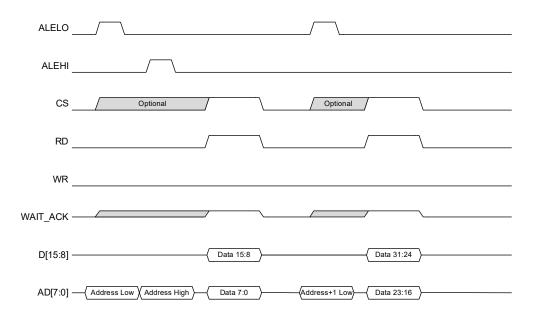

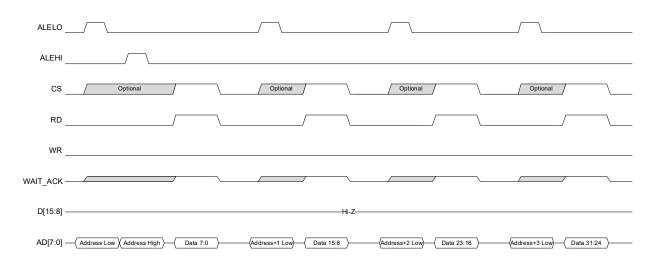

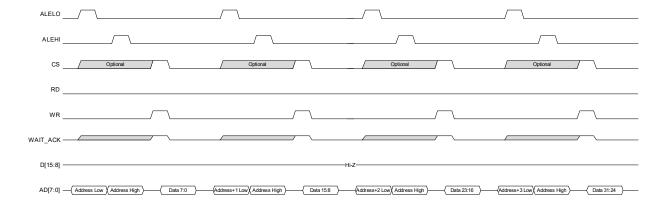

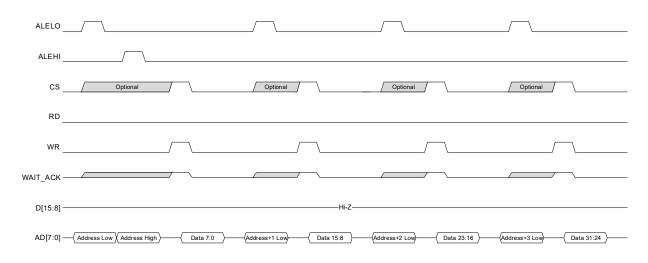

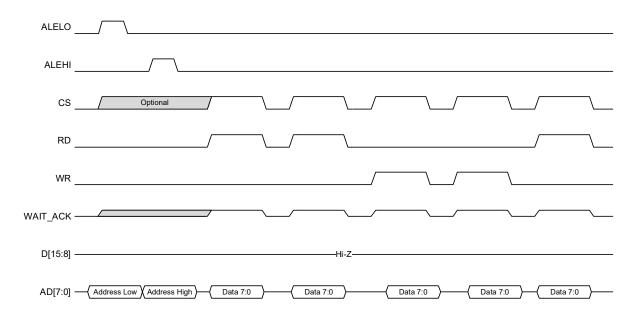

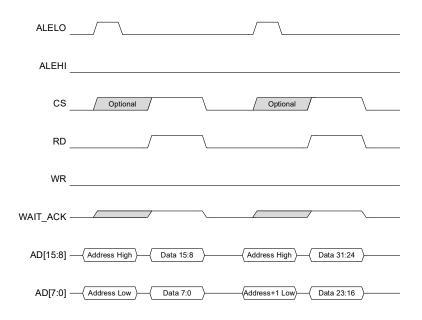

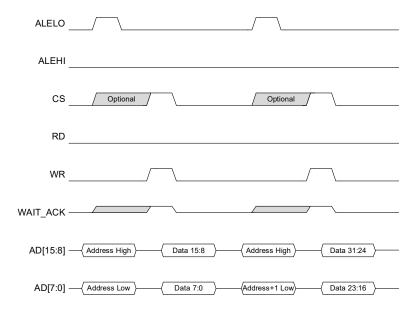

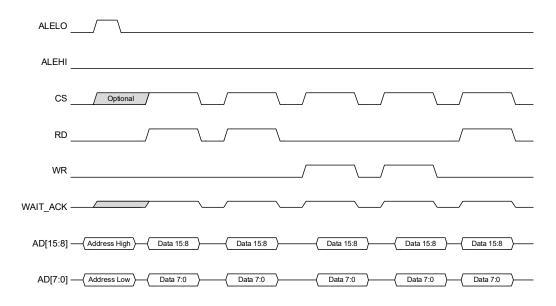

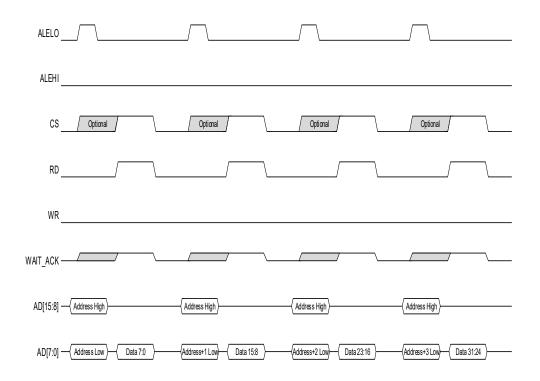

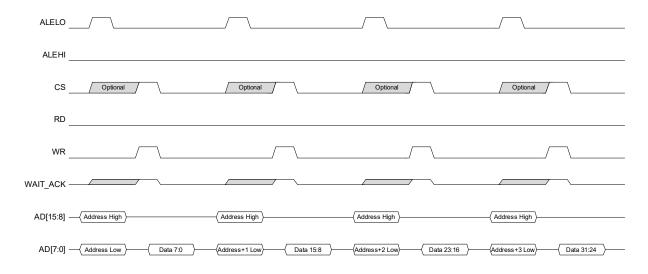

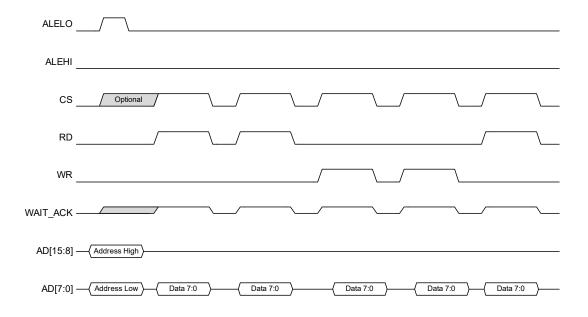

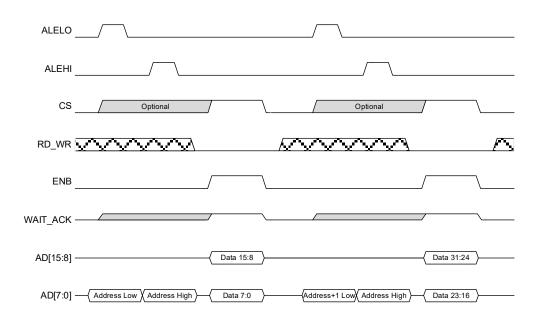

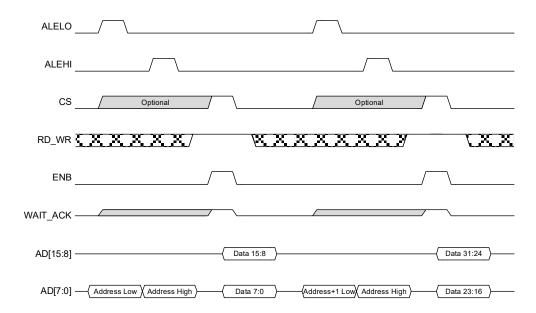

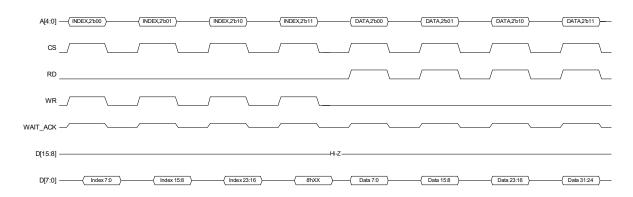

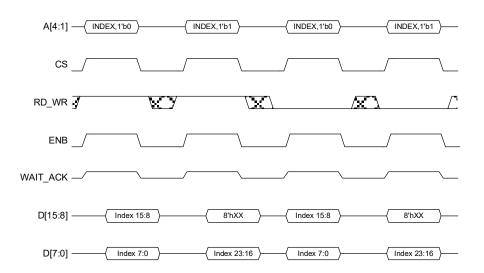

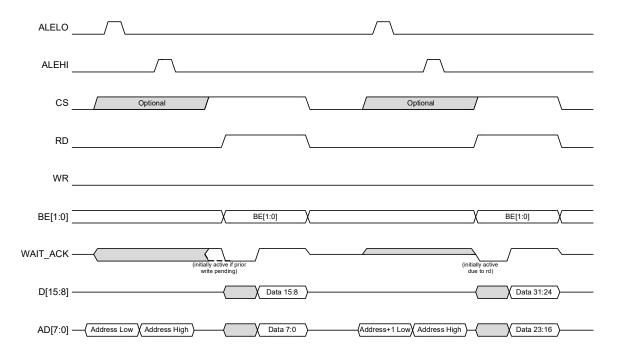

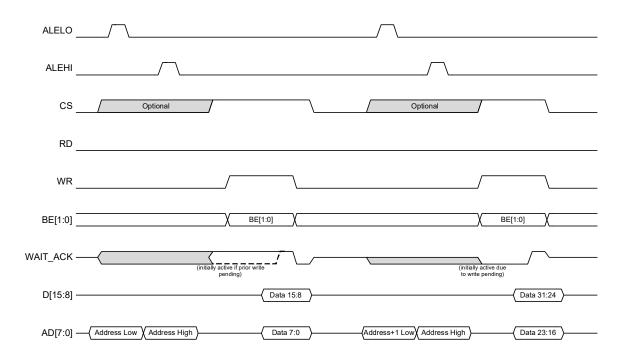

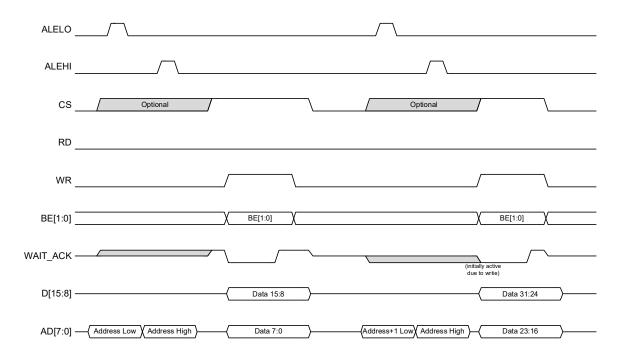

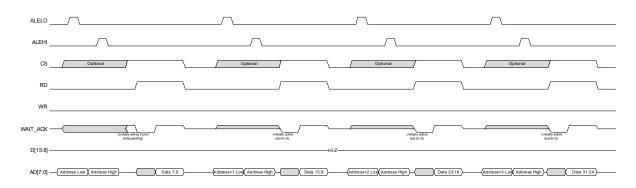

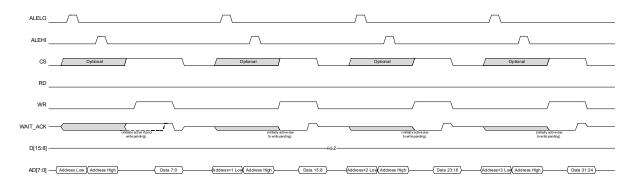

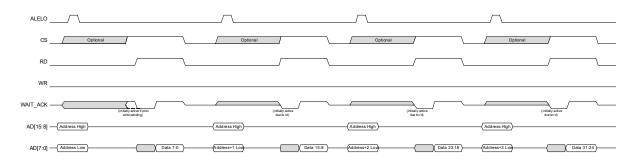

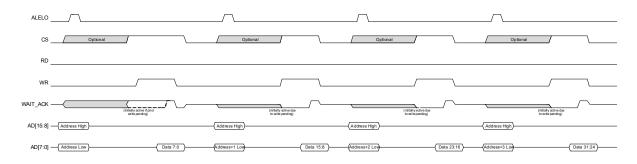

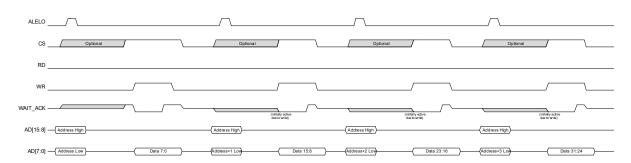

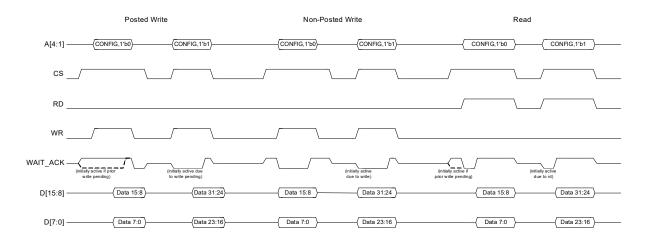

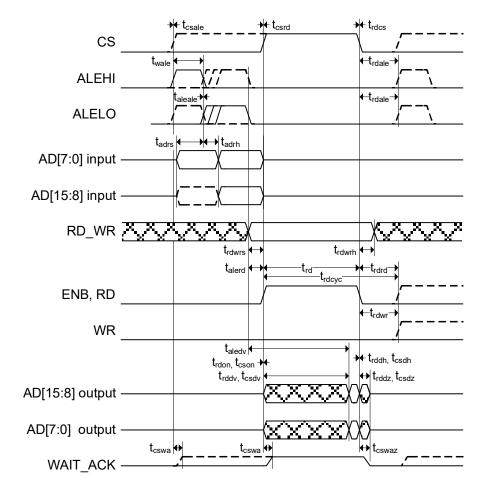

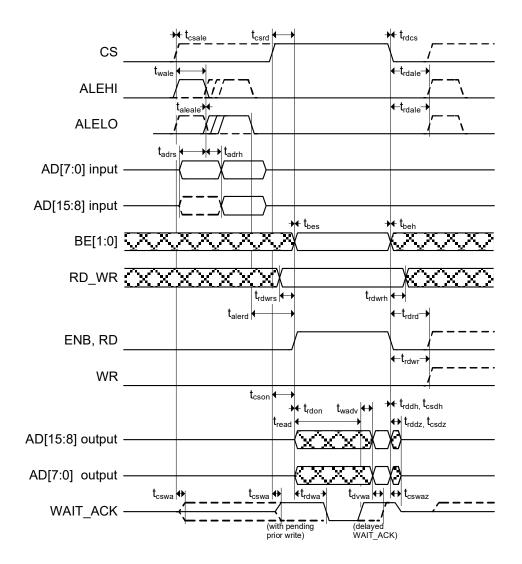

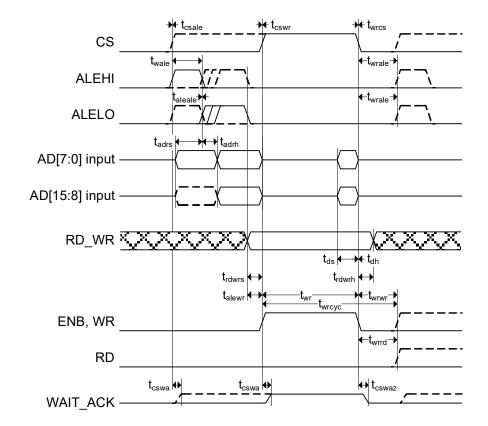

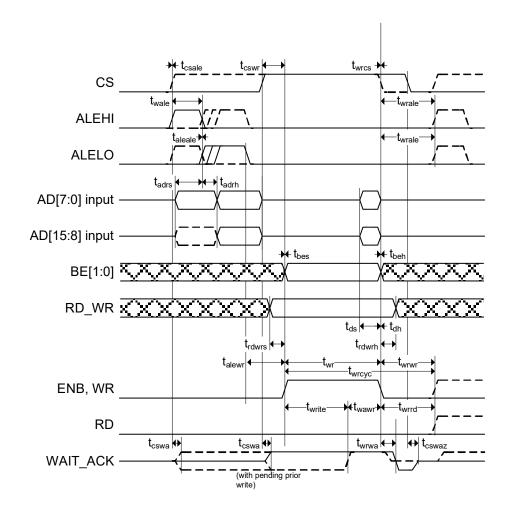

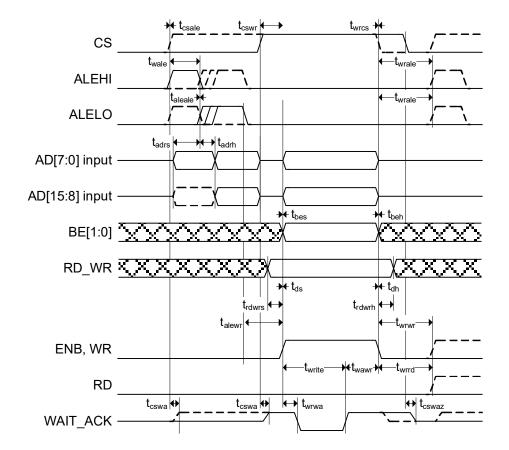

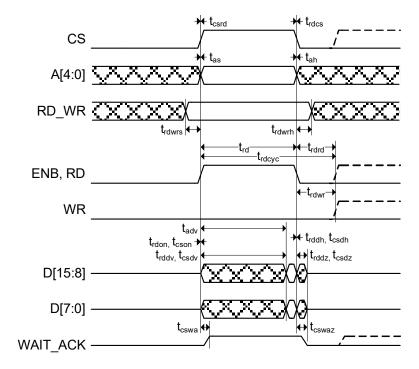

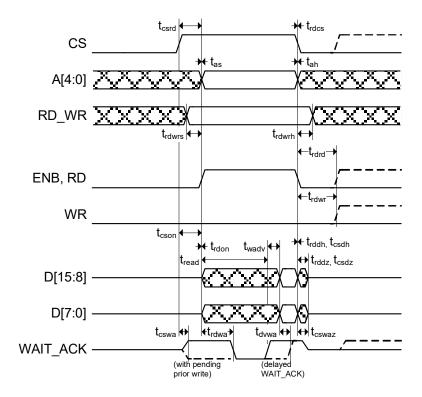

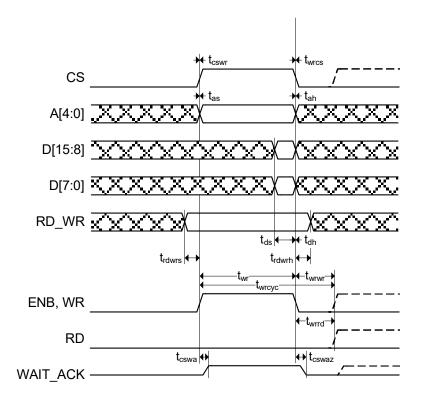

#### Multiplexed address/data bus

This implementation provides a multiplexed address and data bus with both single phase and dual phase address support. The address is loaded with an address strobe followed by data access using a read or write strobe. Two back to back 16-bit data cycles or 4 back to back 8-bit data cycles are required within the same 32-bit DWORD. These accesses must be sequential without any interleaved accesses to other registers.

Alternatively, the device can be accessed via SPI/SQI, while also providing up to 16 inputs or outputs for general purpose usage. An SPI / SQI (Quad SPI) slave controller provides a low pin count synchronous slave interface that facilitates communication between the device and a host system. The SPI / SQI slave allows access to the System CSRs, internal FIFOs and memories. It supports single and multiple register read and write commands with incrementing, decrementing and static addressing. Single, Dual and Quad bit lanes are supported with a clock rate of up to 80 MHz.

<u>Expansion Mode:</u> While the device is in SPI/SQI mode, a third networking port can be enabled to provide an additional MII port. This port can be connected to an external PHY, to enable star or tree network topologies, or to another LAN9253 to create a four port solution. This port can be configured for the upstream or downstream direction.

<u>Digital I/O Mode:</u> For simple digital modules without microcontrollers, the LAN9253 can operate in Digital I/O Mode where 16 digital signals can be controlled or monitored by the EtherCAT master. Up to 7 control signals are also provided.

Figure 2-3 provides a system level overview of each mode of operation.

#### FIGURE 2-3: MODES OF OPERATION

#### 3.0 PIN DESCRIPTIONS AND CONFIGURATION

#### 3.1 Pin Assignments

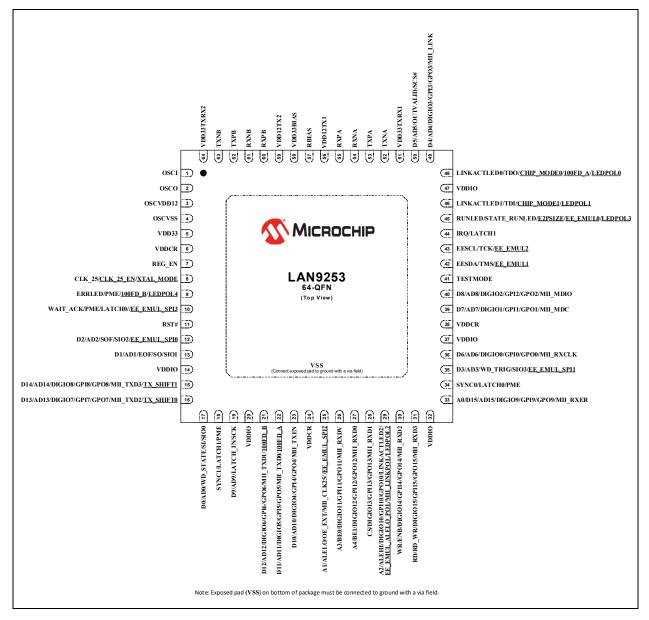

FIGURE 3-1: PIN ASSIGNMENTS (TOP VIEW)

**Note:** When a "#" is used at the end of the signal name, it indicates that the signal is active low. For example, RST# indicates that the reset signal is active low.

Configuration straps are identified by an underlined symbol name. Refer to Section 3.3, "Configuration Straps," on page 36 for additional information.

The buffer type for each signal is indicated in the "Buffer Type" column of the pin description tables in Section 3.2, "Pin Descriptions". A description of the buffer types is provided in Section 1.2, "Buffer Types".

Table 3-1 details the pin assignments in table format. As shown, select pin functions may change based on the device's mode of operation. For modes where a specific pin has no function, the table cell will be marked with "-".

TABLE 3-1: PIN ASSIGNMENTS

| Pin<br>Number | HBI Indexed Mode<br>Pin Name | HBI Multiplexed<br>Mode Pin Name | SPI with GPIO<br>Mode Pin Name    | SPI with MII Mode<br>Pin Name     | Digital I/O<br>Mode Pin Name   |  |  |

|---------------|------------------------------|----------------------------------|-----------------------------------|-----------------------------------|--------------------------------|--|--|

| 1             | OSCI                         |                                  |                                   |                                   |                                |  |  |

| 2             | OSCO                         |                                  |                                   |                                   |                                |  |  |

| 3             |                              |                                  | OSCVDD12                          |                                   |                                |  |  |

| 4             |                              |                                  | OSCVSS                            |                                   |                                |  |  |

| 5             |                              |                                  | VDD33                             |                                   |                                |  |  |

| 6             |                              |                                  | VDDCR                             |                                   |                                |  |  |

| 7             |                              |                                  | REG_EN                            |                                   |                                |  |  |

| 8             |                              | CLK_2                            | 5/ <u>CLK_25_EN/XTAL</u>          | <u>MODE</u>                       |                                |  |  |

| 9             | ERRLE                        | D/PME/ <u>100FD_B/LE</u>         | DPOL4                             | ERRLED/<br>PME/<br><u>LEDPOL4</u> | ERRLED/<br>100FD_B/<br>LEDPOL4 |  |  |

| 10            | WAIT_A                       | CK/PME                           | WAIT_ACK/PMI                      | E/EE_EMUL_SPI3                    | LATCH0                         |  |  |

| 11            |                              |                                  | RST#                              |                                   |                                |  |  |

| 12            | D2                           | AD2                              | SIO2/ <u>EE_H</u>                 | EMUL_SPIO                         | SOF                            |  |  |

| 13            | D1                           | AD1                              | SO/                               | SIO1                              | EOF                            |  |  |

| 14            |                              |                                  | VDDIO                             |                                   |                                |  |  |

| 15            | D14                          | AD14                             | GPI8/GPO8                         | MII_TXD3/<br>TX_SHIFT1            | DIGIO8                         |  |  |

| 16            | D13                          | AD13                             | GPI7/GPO7                         | MII_TXD2/<br>TX_SHIFT0            | DIGIO7                         |  |  |

| 17            | D0                           | AD0                              | SI/S                              | SIO0                              | WD_STATE                       |  |  |

| 18            |                              | SYNC1/LA                         | TCH1/PME                          |                                   | SYNC1/LATCH1                   |  |  |

| 19            | D9                           | AD9                              | Se                                | CK                                | LATCH_IN                       |  |  |

| 20            |                              |                                  | VDDIO                             |                                   |                                |  |  |

| 21            | D12                          | AD12                             | GPI6/GPO6                         | MII_TXD1/<br><u>100FD_B</u>       | DIGIO6                         |  |  |

| 22            | D11                          | AD11                             | GPI5/GPO5 MII_TXD0/<br>100FD_A    |                                   | DIGIO5                         |  |  |

| 23            | D10                          | AD10                             | GPI4/GPO4                         | MII_TXEN                          | DIGIO4                         |  |  |

| 24            | VDDCR                        |                                  |                                   |                                   |                                |  |  |

| 25            | A1                           | ALELO                            | - MII_CLK25<br><u>EE_EMUL_S</u> 1 |                                   | OE_EXT                         |  |  |

| 26            | A3                           | BE0                              | GPI11/GPO11                       | MII_RXDV                          | DIGIO11                        |  |  |

| 27            | A4                           | BE1                              | GPI12/GPO12                       | MII_RXD0                          | DIGIO12                        |  |  |

| 28            | C                            | S                                | GPI13/GPO13                       | MII_RXD1                          | DIGIO13                        |  |  |

|               |                              |                                  |                                   |                                   |                                |  |  |

TABLE 3-1: PIN ASSIGNMENTS (CONTINUED)

| Pin<br>Number | HBI Indexed Mode<br>Pin Name                                                                                             | HBI Multiplexed<br>Mode Pin Name | SPI with GPIO<br>Mode Pin Name                      |            |              |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------|------------|--------------|--|

| 29            | A2                                                                                                                       | ALEHI/ EE EMUL ALEL O_POL        | GPI10/GPO10 LINKACTLED2/<br>MIL_LINKPOL/<br>LEDPOL2 |            | DIGIO10      |  |

| 30            | WR/                                                                                                                      | ENB                              | GPI14/GPO14                                         | MII_RXD2   | DIGIO14      |  |

| 31            | RD/R                                                                                                                     | D_WR                             | GPI15/GPO15                                         | MII_RXD3   | DIGIO15      |  |

| 32            |                                                                                                                          |                                  | VDDIO                                               |            |              |  |

| 33            | A0/D15                                                                                                                   | AD15                             | GPI9/GPO9                                           | MII_RXER   | DIGIO9       |  |

| 34            |                                                                                                                          | SYNC0/LA                         | ТСН0/РМЕ                                            |            | SYNC0/LATCH0 |  |

| 35            | D3                                                                                                                       | AD3                              | SIO3/ <u>EE_I</u>                                   | EMUL_SPI1  | WD_TRIG      |  |

| 36            | D6                                                                                                                       | AD6                              | GPI0/GPO0                                           | MII_RXCLK  | DIGIO0       |  |

| 37            |                                                                                                                          |                                  | VDDIO                                               |            |              |  |

| 38            |                                                                                                                          |                                  | VDDCR                                               |            |              |  |

| 39            | D7                                                                                                                       | AD7                              | GPI1/GPO1                                           | MII_MDC    | DIGIO1       |  |

| 40            | D8                                                                                                                       | AD8                              | GPI2/GPO2                                           | MII_MDIO   | DIGIO2       |  |

| 41            |                                                                                                                          |                                  | TESTMODE                                            |            |              |  |

| 42            |                                                                                                                          | EESDA/TMS                        | S/ <u>EE_EMUL1</u>                                  |            | EESDA/TMS    |  |

| 43            |                                                                                                                          | EESCL/TCK                        | /EE_EMUL2                                           |            | EESCL/TCK    |  |

| 44            |                                                                                                                          | IF                               | RQ                                                  |            | LATCH1       |  |

| 45            | RUNLED/STATE_RUNLED/ <u>E2PSIZE/EE_EMUL0/LEDPOL3</u> RUNLED/ STATE_RUN- LED/ <u>E2PSIZE/</u> LEDPOL3                     |                                  |                                                     |            |              |  |

| 46            |                                                                                                                          | LINKACTLE                        | ED1/TDI/ <u>CHIP_MOD</u>                            | E1/LEDPOL1 |              |  |

| 47            |                                                                                                                          |                                  | VDDIO                                               |            |              |  |

| 48            | LINKACTLED0/TDO/CHIP_MODE0/100FD_A/LEDPOL0  LINKACTLED0/ TDO/ CHIP_MODE0/ LEDPOL0  LINKACTLED0/ TDO/ CHIP_MODE0/ LEDPOL0 |                                  |                                                     |            |              |  |

| 49            | D4                                                                                                                       | AD4                              | GPI3/GPO3                                           | MII_LINK   | DIGIO3       |  |

| 50            | D5                                                                                                                       | AD5                              | SC                                                  | CS#        | OUTVALID     |  |

| 51            | VDD33TXRX1                                                                                                               |                                  |                                                     |            |              |  |

| 52            | TXNA                                                                                                                     |                                  |                                                     |            |              |  |

| 53            | TXPA                                                                                                                     |                                  |                                                     |            |              |  |

| 54            | RXNA                                                                                                                     |                                  |                                                     |            |              |  |

| 55            | RXPA                                                                                                                     |                                  |                                                     |            |              |  |

| 56            | VDD12TX1                                                                                                                 |                                  |                                                     |            |              |  |

| 57            | RBIAS                                                                                                                    |                                  |                                                     |            |              |  |

| 58            | VDD33BIAS                                                                                                                |                                  |                                                     |            |              |  |

TABLE 3-1: PIN ASSIGNMENTS (CONTINUED)

| Pin<br>Number  | HBI Indexed Mode<br>Pin Name |  |          | SPI with MII Mode<br>Pin Name | Digital I/O<br>Mode Pin Name |  |  |

|----------------|------------------------------|--|----------|-------------------------------|------------------------------|--|--|

| 59             |                              |  | VDD12TX2 |                               |                              |  |  |

| 60             |                              |  | RXPB     |                               |                              |  |  |

| 61             | RXNB                         |  |          |                               |                              |  |  |

| 62             | TXPB                         |  |          |                               |                              |  |  |

| 63             | TXNB                         |  |          |                               |                              |  |  |

| 64             | VDD33TXRX2                   |  |          |                               |                              |  |  |

| Exposed<br>Pad | VSS                          |  |          |                               |                              |  |  |

#### 3.2 Pin Descriptions

This section contains descriptions of the various LAN9253 pins. The pin descriptions have been broken into functional groups as follows:

- · LAN Port A Pins

- LAN Port B Pins

- · LAN Port A & B Power and Common Pins

- EtherCAT MII Port & Configuration Strap Pins

- · Host Bus Pins

- SPI/SQI Pins

- EtherCAT Distributed Clock Pins

- EtherCAT Digital I/O and GPIO Pins

- EEPROM Pins

- LED & Configuration Strap Pins

- · Miscellaneous Pins

- JTAG Pins

- · Core and I/O Power and Ground Pins

**Note:** Table 3-1 details how the functions described in this section are mapped on the physical device pins. Not all functions are used for all modes of operation.

**TABLE 3-2: LAN PORT A PINS**

| NUM<br>PINS | NAME                                      | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                            |

|-------------|-------------------------------------------|--------|----------------|------------------------------------------------------------------------|

| 1           | Port A TP TX/<br>RX Positive<br>Channel 1 | ТХРА   | AIO            | Port A Twisted Pair Transmit/Receive Positive Channel 1. See Note 3-1. |

| 1           | Port A TP TX/<br>RX Negative<br>Channel 1 | TXNA   | AIO            | Port A Twisted Pair Transmit/Receive Negative Channel 1. See Note 3-1. |

| 1           | Port A TP TX/<br>RX Positive<br>Channel 2 | RXPA   | AIO            | Port A Twisted Pair Transmit/Receive Positive Channel 2. See Note 3-1. |

| 1           | Port A TP TX/<br>RX Negative<br>Channel 2 | RXNA   | AIO            | Port A Twisted Pair Transmit/Receive Negative Channel 2. See Note 3-1. |

Note 3-1 Either channel 1 or 2 may function as the transmit pair while the other channel functions as the receive pair. The pin name symbols for the twisted pair pins apply to a normal connection. If Auto-MDIX is enabled and a reverse connection is detected or manually selected, the RX and TX pins will be swapped internally.

Note: Port A is connected EtherCAT port 0 or 2.

TABLE 3-3: LAN PORT B PINS

| NUM<br>PINS | NAME                                      | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                            |

|-------------|-------------------------------------------|--------|----------------|------------------------------------------------------------------------|

| 1           | Port B TP TX/<br>RX Positive<br>Channel 1 | ТХРВ   | AIO            | Port B Twisted Pair Transmit/Receive Positive Channel 1. See Note 3-2. |

| 1           | Port B TP TX/<br>RX Negative<br>Channel 1 | TXNB   | AIO            | Port B Twisted Pair Transmit/Receive Negative Channel 1. See Note 3-2. |

| 1           | Port B TP TX/<br>RX Positive<br>Channel 2 | RXPB   | AIO            | Port B Twisted Pair Transmit/Receive Positive Channel 2. See Note 3-2. |

| 1           | Port B TP TX/<br>RX Negative<br>Channel 2 | RXNB   | AIO            | Port B Twisted Pair Transmit/Receive Negative Channel 2. See Note 3-2. |

Note 3-2 Either channel 1 or 2 may function as the transmit pair while the other channel functions as the receive pair. The pin name symbols for the twisted pair pins apply to a normal connection. If Auto-MDIX is enabled and a reverse connection is detected or manually selected, the RX and TX pins will be swapped internally.

Note: Port B is connected EtherCAT port 1.

TABLE 3-4: LAN PORT A & B POWER AND COMMON PINS

| NUM<br>PINS | NAME                                            | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Bias Reference                                  | RBIAS      | AI             | Used for internal bias circuits. Connect to an external 12.1 kΩ, 1% resistor to ground.  Refer to the device reference schematic for connection information.  Note: The nominal voltage is 1.2 V and the resistor will dissipate approximately 1 mW of power. |

| 1           | +3.3 V Port A<br>Analog Power<br>Supply         | VDD33TXRX1 | Р              | See Note 3-3.                                                                                                                                                                                                                                                 |

| 1           | +3.3 V Port B<br>Analog Power<br>Supply         | VDD33TXRX2 | Р              | See Note 3-3.                                                                                                                                                                                                                                                 |

| 1           | +3.3 V Master<br>Bias Power<br>Supply           | VDD33BIAS  | Р              | See Note 3-3.                                                                                                                                                                                                                                                 |

| 1           | Port A<br>Transmitter<br>+1.2 V Power<br>Supply | VDD12TX1   | Р              | This pin is supplied from the VDDCR supply either externally or from the internal voltage regulator. This pin must be tied to the VDD12TX2 pin for proper operation.  See Note 3-3.                                                                           |

| 1           | Port B<br>Transmitter<br>+1.2 V Power<br>Supply | VDD12TX2   | Р              | This pin is supplied from the VDDCR supply either externally or from the internal voltage regulator. This pin must be tied to the VDD12TX1 pin for proper operation.  See Note 3-3.                                                                           |

**Note 3-3** Refer to the Power Connections section of the datasheet, the device reference schematic, and the device LANCheck schematic checklist for additional connection information.

TABLE 3-5: ETHERCAT MII PORT & CONFIGURATION STRAP PINS

| NUM<br>PINS | NAME                                                | SYMBOL                   | BUFFER<br>TYPE   | DESCRIPTION                                                                                                                                                                                                                                              |

|-------------|-----------------------------------------------------|--------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 25MHz Clock                                         | MII_CLK25                | VO12<br>Note 3-4 | This pin is a free running 25MHz clock that can be used as the clock input to the PHY.                                                                                                                                                                   |

| 1           | EEPROM<br>Emulation SPI<br>Configuration<br>Strap 2 | EE EMUL SPI2<br>Note 3-5 | VIS<br>(PD)      | This configuration strap, along with EE EMUL S-PIO, EE EMUL SPI1, and EE EMUL SPI3, configures the operation of the Beckhoff SPI interface during EEPROM Emulation mode. EE EMUL S-PI2 configures SCS# polarity.  0: SCS# active low 1: SCS# active high |

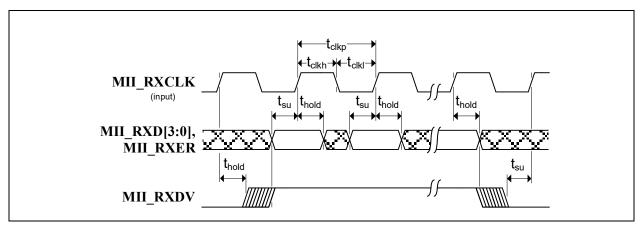

| 4           | Receive Data<br>MII Port                            | MII_RXD[3:0]             | VIS<br>(PD)      | These pins are the receive data from the external PHY.                                                                                                                                                                                                   |

| 1           | Receive Data<br>Valid MII Port                      | MII_RXDV                 | VIS<br>(PD)      | This pin is the receive data valid signal from the external PHY.                                                                                                                                                                                         |

| 1           | Receive Error<br>MII Port                           | MII_RXER                 | VIS<br>(PD)      | This pin is the receive error signal from the external PHY.                                                                                                                                                                                              |

| 1           | Receive Clock<br>MII Port                           | MII_RXCLK                | VIS<br>(PD)      | This pin is the receive clock from the external PHY.                                                                                                                                                                                                     |

TABLE 3-5: ETHERCAT MII PORT & CONFIGURATION STRAP PINS (CONTINUED)

| NUM<br>PINS | NAME                                                    | SYMBOL                    | BUFFER<br>TYPE          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------|---------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Transmit Data<br>MII Port                               | MII_TXD[3:0]              | VO8                     | These pins are the transmit data to the external PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

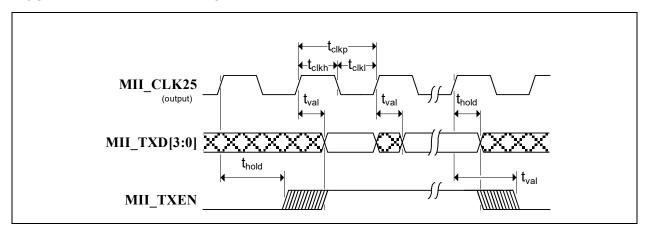

|             | MII Transmit<br>Timing Shift<br>Configuration<br>Straps | TX SHIFT[1:0]<br>Note 3-5 | VIS<br>(PU)<br>Note 3-6 | These straps configure the value of the external MII Bus TX timing.  TX SHIFT1 is on the MII_TXD3 pin and TX SHIFT0 is on the MII_TXD2 pin.  TX SHIFT[1:0]  00: 20ns 01: 30ns 10: 0ns 11: 10ns                                                                                                                                                                                                                                                                                                    |

| 4           | 100Mbps Full<br>Duplex<br>Configuration<br>Strap B      | 100FD_B<br>Note 3-5       | VIS<br>(PD)<br>Note 3-6 | For 3 port mode (as selected by CHIP_MODE1), this strap configures the default of the ANEG Disable PHY B and AMDIX Disable PHY B fields in the Hardware Configuration Register (HW_CFG) and sets the PHY to fixed 100Mbps full-duplex operation by default.  0: Auto-negotiation and AMDIX enabled by default 1: Auto-negotiation and AMDIX disabled (fixed 100Mbps full-duplex) by default  100FD_B is located on the MII_TXD1 pin.  Note: In 2 port mode, this strap is on the ERRLED pin.      |

|             | 100Mbps Full<br>Duplex<br>Configuration<br>Strap A      | 100FD A<br>Note 3-5       | VIS<br>(PD)<br>Note 3-6 | For 3 port mode (as selected by CHIP_MODE1), this strap configures the default of the ANEG Disable PHY A and AMDIX Disable PHY A fields in the Hardware Configuration Register (HW_CFG) and sets the PHY to fixed 100Mbps full-duplex operation by default.  0: Auto-negotiation and AMDIX enabled by default 1: Auto-negotiation and AMDIX disabled (fixed 100Mbps full-duplex) by default  100FD_A is located on the MII_TXD0 pin.  Note: In 2 port mode, this strap is on the LINKACTLED0 pin. |

| 1           | Transmit Data<br>Enable MII Port                        | MII_TXEN                  | VO8                     | This pin is the transmit data enable signal to the external PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1           | Link Status MII<br>Port                                 | MII_LINK                  | VIS                     | This pin is the provided by the PHY to indicate that a 100 Mbit/s Full Duplex link is established. The polarity is configurable via the MII_LINKPOL configuration strap.                                                                                                                                                                                                                                                                                                                          |

TABLE 3-5: ETHERCAT MII PORT & CONFIGURATION STRAP PINS (CONTINUED)

| NUM<br>PINS | NAME      | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                      |

|-------------|-----------|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

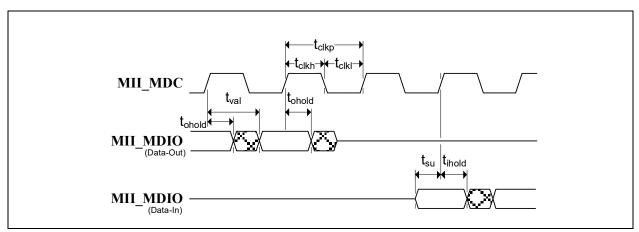

| 1           | SMI Clock | MII_MDC  | VO8            | This pin is the serial management clock to the external PHY.                                                                                                                                     |

| 1           | SMI Data  | MII_MDIO | VIS/<br>VO8    | This pin is the serial management Interface data input/output to the external PHY.  Note: An external pull-up is required to ensure that the non-driven state of the MDIO signal is a logic one. |

- Note 3-4 A series terminating resistor is recommended for the best PCB signal integrity.

- Note 3-5 Configuration strap pins are identified by an underlined symbol name. Configuration strap values are latched on power-on reset, EtherCAT reset, or RST# de-assertion. Refer to Section 3.3, "Configuration Straps," on page 36 for further information.

- Note 3-6 An external supplemental pull-up or pull-down may be needed, depending upon the input current loading of the external MAC/PHY device.

TABLE 3-6: HOST BUS PINS

| NUM<br>PINS | NAME          | SYMBOL      | BUFFER<br>TYPE | DESCRIPTION                                                                                                                       |

|-------------|---------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

|             |               |             |                | This pin is the host bus read strobe.                                                                                             |

|             | Read          | RD          | VIS            | Normally active low, the polarity can be changed via configuration register settings.                                             |

| 1           |               |             | .,,,,          | This pin is the host bus direction control. Used in conjunction with the ENB pin it indicates a read or write operation.          |

|             | Read or Write | RD_WR       | VIS            | The normal polarity is read when 1, write when 0 (R/nW) but can be changed via configuration register settings.                   |

|             |               | e WR        | VIS            | This pin is the host bus write strobe.                                                                                            |

|             | Write         |             |                | Normally active low, the polarity can be changed via configuration register settings.                                             |

| 1           | Enable        | ENB         | VIS            | This pin is the host bus data enable strobe. Used in conjunction with the RD_WR pin it indicates the data phase of the operation. |

|             |               |             |                | Normally active low, the polarity can be changed via configuration register settings.                                             |

| 1           | Chip Select   | o Select CS | VIS            | This pin is the host bus chip select and indicates that the device is selected for the current transfer.                          |

|             | Strip Colcot  |             | VIO            | Normally active low, the polarity can be changed via configuration register settings.                                             |

TABLE 3-6: HOST BUS PINS (CONTINUED)

| NUM<br>PINS | NAME                | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

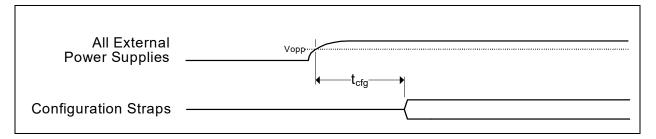

|-------------|---------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|