# Quad Output, Multiphase Step-Down Voltage Mode DC/DC Controller with Accurate Current Sharing

## **FEATURES**

- Operates with Power Blocks, DrMOS or External Gate Drivers and MOSFETs

- Voltage Mode Control with Accurate Current Sharing

- ±0.75% 0.6V Voltage Reference

- Quad Differential Output Voltage Sense Amplifiers

- Multiphase Capability

- Phase-Lockable Fixed Frequency 250kHz to 2.25MHz

- Lossless Current Sensing Using Inductor DCR or Precision Current Sensing with Sense Resistor or DrMOS with Integrated Current Sensing

- V<sub>CC</sub> Range: 3V to 5.5V

- V<sub>OUT</sub> Range: 0.6V to V<sub>CC</sub> 0.5V

- Power Good Output Voltage Monitor

- Output Voltage Tracking Capability with Soft-Start

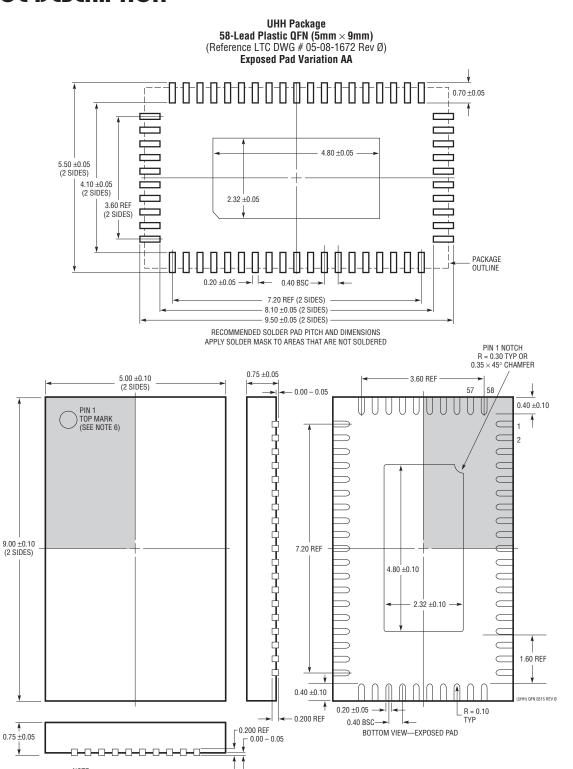

- Available in 58-Lead 5mm × 9mm QFN Package

## **APPLICATIONS**

- High Current Distributed Power Systems

- DSP, FPGA and ASIC Supplies

- Datacom, Telecom and Computing Systems

#### DESCRIPTION

The LTC®7851/LTC7851-1 are quad output multiphase synchronous step-down switching regulator controllers that employ a constant frequency voltage mode architecture. They maintain excellent current balance between channels when paralleled with their internal current sharing loop. Lossless DCR or a low value R<sub>SENSE</sub> is used for output current sensing. Multiple LTC7851/LTC7851-1 devices can be used for high phase count operation.

Avery low offset, high bandwidth error amplifier, combined with remote output voltage sensing, provides excellent transient response and output regulation. The LTC7851/LTC7851-1 operates with a  $V_{CC}$  supply voltage from 3V to 5.5V and is designed for step-down conversion with  $V_{IN}$  from 3V to 27V\* and produces an output voltage from 0.6V to  $V_{CC}$  – 0.5V.

The LTC7851-1 is identical to the LTC7851 except it has a lower current sense amplifier gain, making it ideal for DrMOS devices with internal current sense.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 6144194, 5055767.

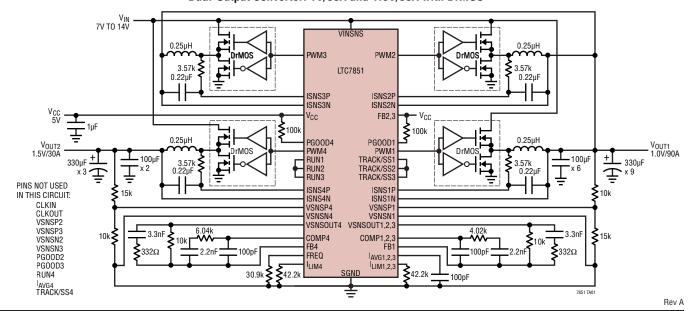

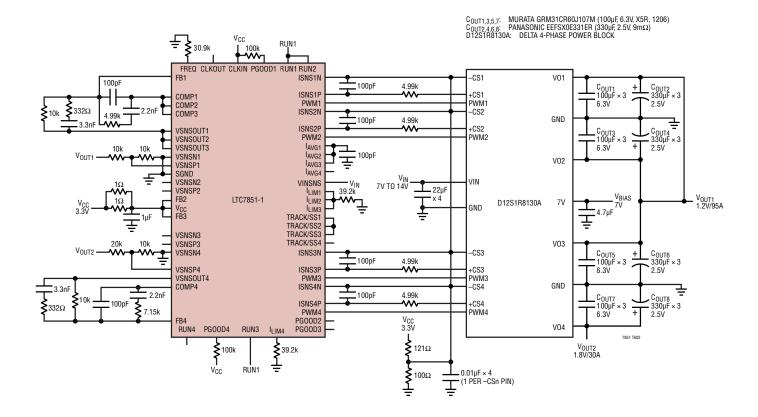

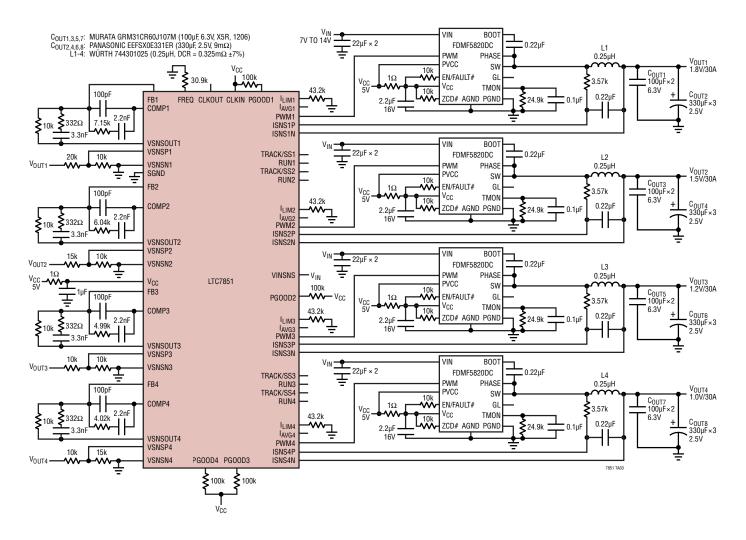

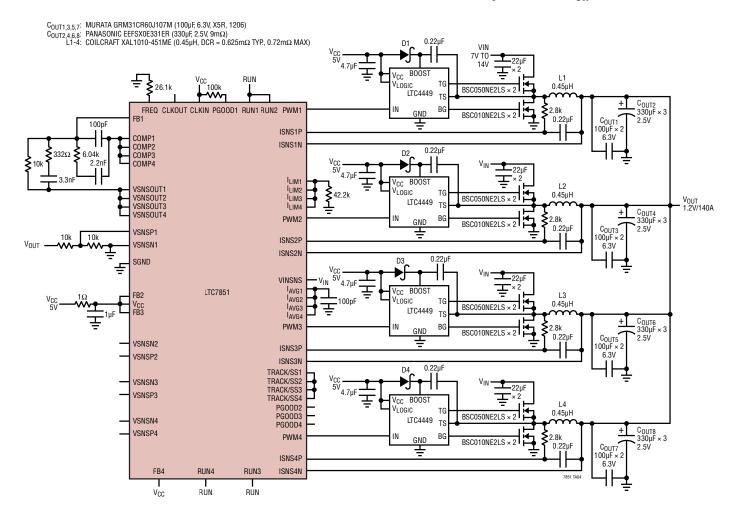

## TYPICAL APPLICATION

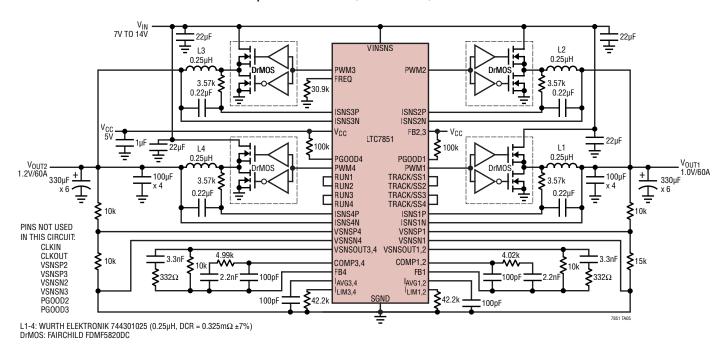

Dual-Output Converter: 1V/90A and 1.5V/30A with DrMOS

1

<sup>\*</sup>See Note 5.

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| 0.3V to 6.5V                 |

|------------------------------|

| 0.3V to 30V                  |

|                              |

| 0.3V to $(V_{CC}+0.3V)$      |

|                              |

| $-0.3V$ to $(V_{CC} + 0.1V)$ |

|                              |

| $-0.3V$ to $(V_{CC} + 0.1V)$ |

| $-0.3V$ to $(V_{CC} + 0.3V)$ |

| Range40° to 125°C            |

| 65°C to 150°C                |

|                              |

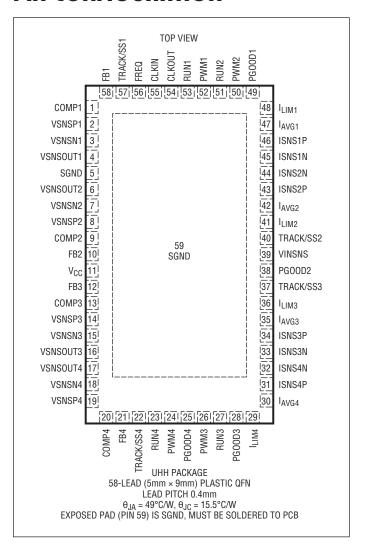

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|-------------------|

| LTC7851EUHH#PBF   | LTC7851EUHH#TRPBF   | 7851         | 58-LEAD (5mm × 9mm) Plastic QFN | -40°C to 125°C    |

| LTC7851IUHH#PBF   | LTC7851IUHH#TRPBF   | 7851         | 58-LEAD (5mm × 9mm) Plastic QFN | -40°C to 125°C    |

| LTC7851EUHH-1#PBF | LTC7851EUHH-1#TRPBF | 78511        | 58-LEAD (5mm × 9mm) Plastic QFN | -40°C to 125°C    |

| LTC7851IUHH-1#PBF | LTC7851IUHH-1#TRPBF | 78511        | 58-LEAD (5mm × 9mm) Plastic QFN | -40°C to 125°C    |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{CC} = 5V$ ,  $V_{RUN1,2,3,4} = 5V$ ,  $V_{FREQ} = V_{CLKIN} = 0V$ ,  $V_{FB} = 0.6V$ ,  $f_{OSC} = 600$ kHz, unless otherwise specified.

| SYMBOL                        | PARAMETER                                                                 | CONDITIONS                                                                                                            |   | MIN          | TYP         | MAX                   | UNITS          |

|-------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|--------------|-------------|-----------------------|----------------|

| V <sub>INSNS</sub>            | V <sub>IN</sub> Sense Range                                               | V <sub>CC</sub> = 5V (Note 5)                                                                                         | • | 3            |             | 27                    | V              |

| $\overline{V_{CC}}$           | V <sub>CC</sub> Voltage Range                                             |                                                                                                                       | • | 3            |             | 5.5                   | V              |

| V <sub>OUT</sub>              | V <sub>OUT</sub> Voltage Range                                            | Limited by ISNSP/N Common Mode<br>Voltage Range (Note 3)                                                              | • | 0.6          |             | V <sub>CC</sub> - 0.5 | V              |

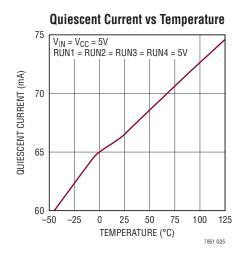

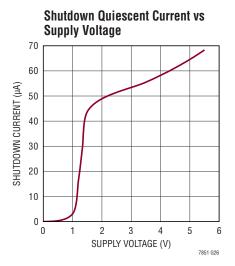

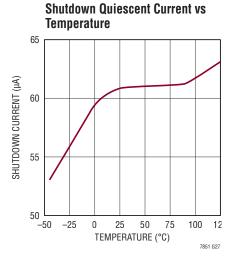

| IQ                            | Input Voltage Supply Current<br>Normal Operation<br>Shutdown Mode<br>UVLO | V <sub>RUN1,2,3,4</sub> = 5V<br>V <sub>RUN1,2,3,4</sub> = 0V<br>V <sub>CC</sub> < V <sub>UVLO</sub>                   |   |              | 60<br>16    | 110<br>100            | mA<br>μA<br>mA |

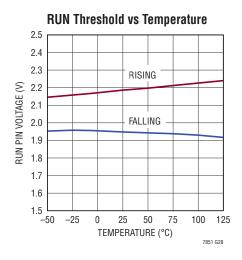

| V <sub>RUN</sub>              | RUN Input Threshold                                                       | V <sub>RUN</sub> Rising<br>V <sub>RUN</sub> Hysteresis                                                                |   | 1.95         | 2.25<br>250 | 2.45                  | V<br>mV        |

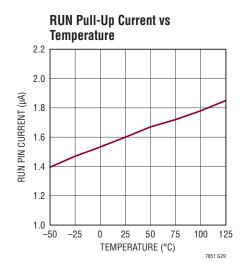

| I <sub>RUN</sub>              | RUN Input Pull-Up Current                                                 | V <sub>RUN</sub> = 2.4V                                                                                               |   |              | 1.5         |                       | μA             |

| V <sub>UVLO</sub>             | Undervoltage Lockout Threshold                                            | V <sub>CC</sub> Rising<br>V <sub>CC</sub> Hysteresis                                                                  | • |              | 100         | 3                     | V<br>mV        |

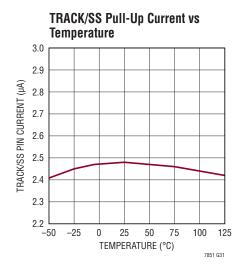

| I <sub>SS</sub>               | Soft-Start Pin Output Current                                             | V <sub>SS</sub> = 0V                                                                                                  |   | 1.5          | 2.5         | 3.5                   | μA             |

| t <sub>SS</sub>               | Internal Soft-Start Time                                                  |                                                                                                                       |   |              | 1.5         |                       | ms             |

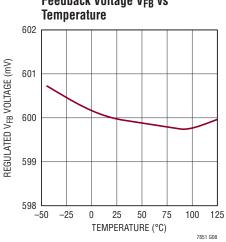

| $V_{FB}$                      | Regulated Feedback Voltage                                                | -20°C to 85°C<br>-40°C to 125°C                                                                                       | • | 595.5<br>594 | 600<br>600  | 604.5<br>606          | mV<br>mV       |

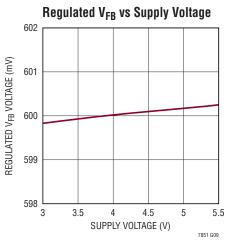

| $\Delta V_{FB}/\Delta V_{CC}$ | Regulated Feedback Voltage Line Dependence                                | 3.0V < V <sub>CC</sub> < 5.5V                                                                                         |   |              | 0.05        | 0.2                   | %/V            |

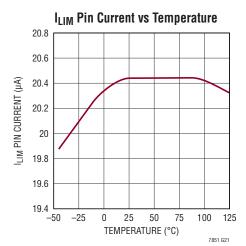

| I <sub>LIMIT</sub>            | I <sub>LIM</sub> Pin Output Current                                       | $V_{ILIM} = 0.8V$                                                                                                     |   | 18.5         | 20          | 21.5                  | μΑ             |

| Power Good                    |                                                                           |                                                                                                                       |   |              |             |                       |                |

| V <sub>FB(OV)</sub>           | PGOOD/V <sub>FB</sub> Overvoltage Threshold                               | V <sub>FB</sub> Falling<br>V <sub>FB</sub> Rising                                                                     |   | 650          | 645<br>660  | 670                   | mV<br>mV       |

| V <sub>FB(UV)</sub>           | PGOOD/V <sub>FB</sub> Undervoltage Threshold                              | V <sub>FB</sub> Falling<br>V <sub>FB</sub> Rising                                                                     |   | 530          | 540<br>555  | 550                   | mV<br>mV       |

| V <sub>PGOOD(ON)</sub>        | PGOOD Pull-Down Resistance                                                |                                                                                                                       |   |              | 15          | 60                    | Ω              |

| I <sub>PGOOD(OFF)</sub>       | PGOOD Leakage Current                                                     | V <sub>PG00D</sub> = 5V                                                                                               |   |              |             | 2                     | μA             |

| t <sub>PGOOD</sub>            | PGOOD Delay                                                               | V <sub>PGOOD</sub> High to Low                                                                                        |   |              | 30          |                       | μs             |

| Error Amplifie                | r                                                                         |                                                                                                                       |   |              |             |                       |                |

| I <sub>FB</sub>               | FB Pin Input Current                                                      | V <sub>FB</sub> = 600mV                                                                                               |   | -100         |             | 100                   | nA             |

| I <sub>OUT</sub>              | COMP Pin Output Current                                                   | Sourcing<br>Sinking                                                                                                   |   |              | 1<br>4      |                       | mA<br>mA       |

| A <sub>V(OL)</sub>            | Open Loop Voltage Gain                                                    |                                                                                                                       |   |              | 75          |                       | dB             |

| SR                            | Slew Rate                                                                 | (Note 4)                                                                                                              |   |              | 45          |                       | V/µs           |

| $f_{\text{0dB}}$              | COMP Unity-Gain Bandwidth                                                 | (Note 4)                                                                                                              |   |              | 40          |                       | MHz            |

| Differential A                | mplifier                                                                  |                                                                                                                       |   |              |             |                       |                |

| $\overline{V_{DA}}$           | V <sub>SNSP</sub> Accuracy                                                | Measured in a Servo Loop with EA in Loop<br>0°C to 85°C<br>Measured in a Servo Loop with EA in Loop<br>-40°C to 125°C | • | 594<br>592   | 600<br>600  | 606<br>608            | mV<br>mV       |

| I <sub>DIFF</sub> +           | Input Bias Current                                                        | V <sub>SNSP</sub> = 600mV                                                                                             |   | -100         |             | 100                   | nA             |

| f <sub>Odb</sub>              | DA Unity-Gain Bandwidth                                                   | (Note 4)                                                                                                              |   |              | 40          |                       | MHz            |

| I <sub>OUT(SINK)</sub>        | Maximum Sinking Current                                                   | VSNSOUT = 600mV                                                                                                       |   |              | 100         |                       | μA             |

| I <sub>OUT(SOURCE)</sub>      | Maximum Sourcing Current                                                  | VSNSOUT = 600mV                                                                                                       |   |              | 500         |                       | <u></u><br>μΑ  |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{CC} = 5V$ ,  $V_{RUN1,2,3,4} = 5V$ ,  $V_{FREQ} = V_{CLKIN} = 0V$ ,  $V_{FB} = 0.6V$ ,  $f_{OSC} = 600$ kHz, unless otherwise specified.

| SYMBOL                   | PARAMETER                                  | CONDITIONS                                                                                                                                                                                                     |   | MIN                   | TYP                                           | MAX                   | UNITS                                         |

|--------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|-----------------------------------------------|-----------------------|-----------------------------------------------|

| Current Sense            | Amplifier                                  |                                                                                                                                                                                                                |   |                       |                                               |                       |                                               |

| V <sub>ISENSE(MAX)</sub> | Maximum Differential Current Sense Voltage | LTC7851                                                                                                                                                                                                        |   | 50                    |                                               |                       | mV                                            |

|                          | (VISNSP - VISNSN)                          | LTC7851-1                                                                                                                                                                                                      |   | 150                   |                                               |                       | mV                                            |

| A <sub>V(ISENSE)</sub>   | Voltage Gain                               | LTC7851                                                                                                                                                                                                        |   |                       | 20                                            |                       | V/V                                           |

|                          |                                            | LTC7851-1                                                                                                                                                                                                      |   |                       | 4                                             |                       | V/V                                           |

| V <sub>CM(ISENSE)</sub>  | Input Common Mode Range                    |                                                                                                                                                                                                                |   | -0.3                  |                                               | V <sub>CC</sub> - 0.5 | V                                             |

| I <sub>ISENSE</sub>      | SENSE Pin Input Current                    | V <sub>CM</sub> = 1.5V                                                                                                                                                                                         |   |                       | 100                                           |                       | nA                                            |

| V <sub>IAVG</sub>        | Zero Current I <sub>AVG</sub> Pin Voltage  | V <sub>ISNSP</sub> = V <sub>ISNSN</sub>                                                                                                                                                                        |   |                       | 500                                           |                       | mV                                            |

| $\overline{V_{0S}}$      | Current Sense Input Referred Offset        | LTC7851                                                                                                                                                                                                        | • | -1                    |                                               | 1                     | mV                                            |

|                          |                                            | LTC7851-1                                                                                                                                                                                                      | • | -3                    |                                               | 3                     | mV                                            |

| Oscillator and           | Phase-Locked Loop                          |                                                                                                                                                                                                                |   |                       |                                               |                       |                                               |

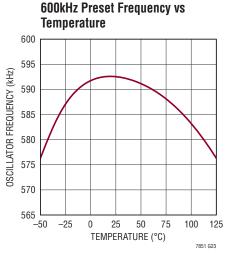

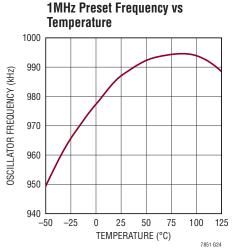

| f <sub>OSC</sub>         | Oscillator Frequency                       | $V_{CLKIN} = 0V$ $V_{FREQ} = 0V$ $V_{FREQ} = 5V$                                                                                                                                                               | • | 520<br>0.85           | 600<br>1                                      | 680<br>1.15           | kHz<br>MHz                                    |

|                          |                                            | V <sub>CLKIN</sub> = 5V  R <sub>FREQ</sub> < 24.9k R <sub>FREQ</sub> = 30.9k R <sub>FREQ</sub> = 36.5k R <sub>FREQ</sub> = 48.7k R <sub>FREQ</sub> = 64.9k R <sub>FREQ</sub> = 82.5k R <sub>FREQ</sub> = 88.7k |   |                       | 180<br>370<br>570<br>970<br>1.4<br>1.9<br>2.1 |                       | kHz<br>kHz<br>kHz<br>kHz<br>MHz<br>MHz<br>MHz |

|                          |                                            | Maximum Frequency                                                                                                                                                                                              |   | 3                     |                                               |                       | MHz                                           |

|                          |                                            | Minimum Frequency                                                                                                                                                                                              |   |                       |                                               | 0.25                  | MHz                                           |

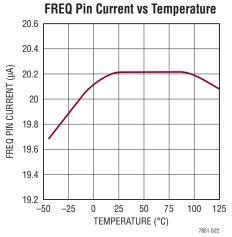

| I <sub>FREQ</sub>        | FREQ Pin Output Current                    | V <sub>FREQ</sub> = 0.8V                                                                                                                                                                                       |   | 18.5                  | 20                                            | 21.5                  | μA                                            |

| t <sub>CLKIN(HI)</sub>   | CLKIN Pulse Width High                     | V <sub>CLKIN</sub> = 0V to 5V                                                                                                                                                                                  |   | 100                   |                                               |                       | ns                                            |

| t <sub>CLKIN(LO)</sub>   | CLKIN Pulse Width Low                      | V <sub>CLKIN</sub> = 0V to 5V                                                                                                                                                                                  |   | 100                   |                                               |                       | ns                                            |

| R <sub>CLKIN</sub>       | CLKIN Pull Up Resistance                   |                                                                                                                                                                                                                |   |                       | 20                                            |                       | kΩ                                            |

| V <sub>CLKIN</sub>       | CLKIN Input Threshold                      | V <sub>CLKIN</sub> Falling<br>V <sub>CLKIN</sub> Rising                                                                                                                                                        |   |                       | 0.8<br>2                                      |                       | V                                             |

| V <sub>FREQ</sub>        | FREQ Input Threshold                       | V <sub>CLKIN</sub> = 0V<br>V <sub>FREQ</sub> Falling<br>V <sub>FREQ</sub> Rising                                                                                                                               |   |                       | 1.5<br>2.5                                    |                       | V                                             |

| V <sub>OL(CLKOUT)</sub>  | CLKOUT Low Output Voltage                  | $I_{LOAD} = -500\mu A$                                                                                                                                                                                         |   |                       | 0.2                                           |                       | V                                             |

| V <sub>OH(CLKOUT)</sub>  | CLKOUT High Output Voltage                 | $I_{LOAD} = 500\mu A$                                                                                                                                                                                          |   |                       | $V_{CC} - 0.2$                                | 2                     | V                                             |

| $\theta_2 - \theta_1$    | Channel 2 to Channel 1 Phase Relationship  |                                                                                                                                                                                                                |   |                       | 180                                           |                       | Deg                                           |

| θ3 – θ1                  | Channel 3 to Channel 1 Phase Relationship  |                                                                                                                                                                                                                |   |                       | 90                                            |                       | Deg                                           |

| θ4 – θ1                  | Channel 4 to Channel 1 Phase Relationship  |                                                                                                                                                                                                                |   |                       | 270                                           |                       | Deg                                           |

| θ <sub>CLKOUT</sub> – θ1 | CLKOUT to Channel 1 Phase Relationship     |                                                                                                                                                                                                                |   |                       | 45                                            |                       | Deg                                           |

| PWM Output               |                                            | <del></del>                                                                                                                                                                                                    |   |                       |                                               |                       |                                               |

| PWM                      | PWM Output High Voltage                    | I <sub>LOAD</sub> = 500μA                                                                                                                                                                                      | • | V <sub>CC</sub> - 0.5 |                                               |                       | V                                             |

|                          | PWM Output Low Voltage                     | $I_{LOAD} = -500\mu A$                                                                                                                                                                                         | • |                       |                                               | 0.5                   | V                                             |

|                          | PWM Output Current in Hi-Z State           |                                                                                                                                                                                                                |   |                       |                                               | ±5                    | μΑ                                            |

|                          | PWM Maximum Duty Cycle                     |                                                                                                                                                                                                                |   |                       | 91.5                                          |                       | %                                             |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC7851/LTC7851-1 are tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC7851E/LTC7851E-1 are guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the  $-40^{\circ}\text{C}$  to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC7851I/LTC7851I-1 are guaranteed over the  $-40^{\circ}\text{C}$  to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package

thermal impedance and other environmental factors.  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation PD according to the following formula:

$$T_J = T_A + (P_D \cdot 49^{\circ}C/W)$$

**Note 3:** The maximum  $V_{OUT}$  range is limited by the current sense pins (ISNSP/ISNSN) common mode voltage range. See the Current Sensing in the Applications Information section.

Note 4: Guaranteed by design.

**Note 5:** The Absolute Maximum Voltage Rating for the VINSNS voltage limits the Maximum  $V_{IN}$  Voltage. For operation with a  $V_{IN}$  range higher than 27V, the VINSNS pin must be connected through a resistor divider from  $V_{IN}$  to limit the maximum VINSNS voltage to less than 27V.

## TYPICAL PERFORMANCE CHARACTERISTICS

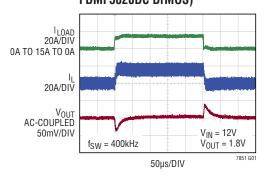

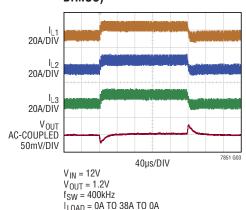

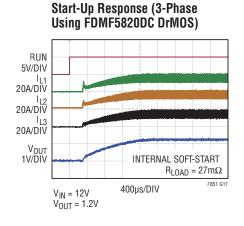

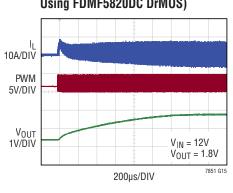

#### Load Step Transient Response (Single Phase Using FDMF5820DC DrMOS)

#### Load Step Transient Response (2-Phase Using FDMF58200C DrMOS)

I<sub>LOAD</sub> = 10A TO 30A TO 10A

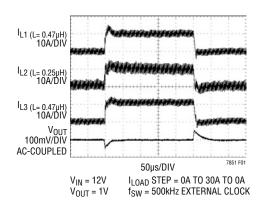

#### Load Step Transient Response (3-Phase Using FDMF5820DC DrMOS)

#### Load Step Transient Response (4-Phase Using FDMF5820DC DrMOS)

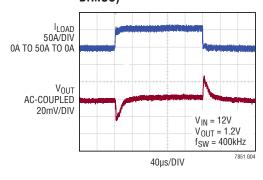

## TYPICAL PERFORMANCE CHARACTERISTICS

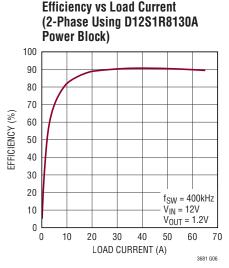

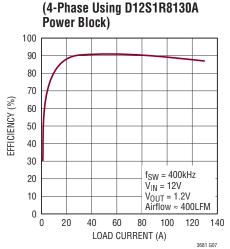

**Efficiency vs Load Current**

(4-Phase Using D12S1R8130A

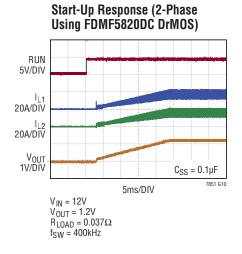

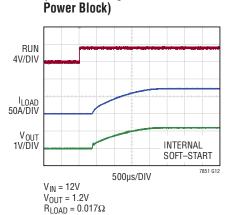

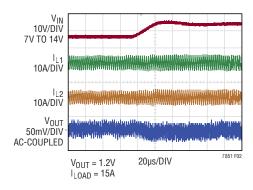

Start-Up Response

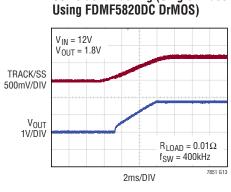

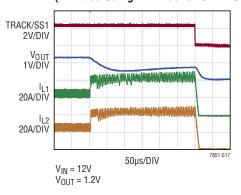

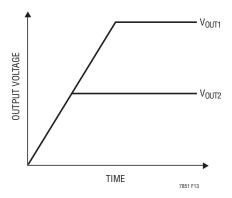

**Coincident Tracking (Single Phase**

Rev A

$f_{SW} = 400kHz$

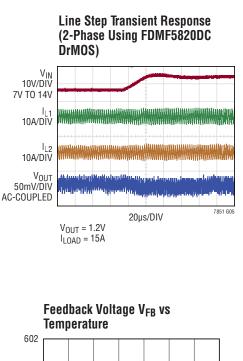

## TYPICAL PERFORMANCE CHARACTERISTICS

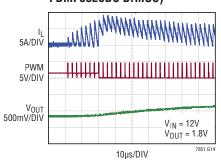

Initial 7-Cycle Nonsynchronous Start-Up (Single Phase Using FDMF5820DC DrMOS)

Start-Up Response Into a 300mV Prebiased Output (Single Phase Using FDMF5820DC DrMOS)

Start-Up Into a Short (2-Phase Using FDMF5820DC DrMOS)

128-Cycle Overcurrent Counter (2-Phase Using FDMF5820DC DrMOS)

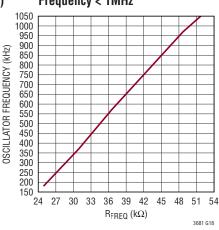

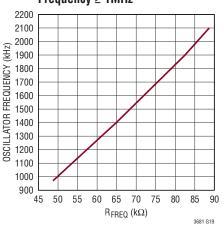

Oscillator Frequency vs R<sub>FREQ</sub> Frequency < 1MHz

Oscillator Frequency vs  $R_{FREQ}$  Frequency  $\geq 1 MHz$

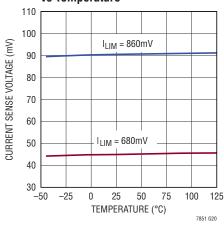

LTC7851-1 Overcurrent Threshold vs Temperature

Rev A

## TYPICAL PERFORMANCE CHARACTERISTICS

Rev A

## PIN FUNCTIONS

**COMP1** (Pin 1), COMP2 (Pin 9), COMP3 (Pin 13), COMP4 (Pin 20): Error Amplifier Outputs. PWM duty cycle increases with this control voltage. The error amplifiers in the LTC7851/LTC7851-1 are true operational amplifiers with low output impedance. As a result, the outputs of two active error amplifiers cannot be directly connected together! For multiphase operation, connecting the FB pin on an error amplifier to  $V_{CC}$  will three-state the output of that amplifier. Multiphase operation can then be achieved by connecting all of the COMP pins together and using one channel as the master and all others as slaves. When the RUN pin is low, the respective COMP pin is actively pulled down to ground.

VSNSP1 (Pin 2), VSNSP2 (Pin 8), VSNSP3 (Pin 14), VSNSP4 (Pin 19): Differential Sense Amplifier Noninverting Input. Connect this pin to the midpoint of the feedback resistive divider between the positive and negative output capacitor terminals.

VSNSN1 (Pin 3), VSNSN2 (Pin 7), VSNSN3 (Pin 15), VSNSN4 (Pin 18): Differential Sense Amplifier Inverting Input. Connect this pin to sense ground at the output load. If the differential sense amplifier is not used, connect this pin to local ground. Float this pin when the channel is a slave channel.

VSNSOUT1 (Pin 4), VSNSOUT2 (Pin 6), VSNSOUT3 (Pin 16), VSNSOUT4 (Pin 17): Differential Amplifier Output. Connect to the corresponding FB pin with a compensation network for remote V<sub>OUT</sub> sensing. PolyPhase control is also implemented in part by connecting all slave VSNSOUT pins to the master VSNSOUT output. Only the master phase's differential amplifier contributes information to this output.

**SGND (Pin 5, Exposed Pad Pin 59):** Signal Ground. All soft-start, small-signal and compensation components should return to SGND. The exposed pad must be soldered to PCB ground for rated thermal performance.

**FB1** (Pin 58), FB2 (Pin 10), FB3 (Pin 12), FB4 (Pin 21): Error Amplifier Inverting Input. Connect to the corresponding VSNSOUT pin with a compensation network for remote  $V_{OUT}$  sensing. Connecting the FB to  $V_{CC}$  disables the differential and error amplifiers of the respective channel, and will three-state the amplifier outputs.

$V_{CC}$  (Pin 11): Chip Supply Voltage. Bypass this pin to GND with a capacitor (0.1 $\mu$ F to 1 $\mu$ F ceramic) in close proximity to the chip.

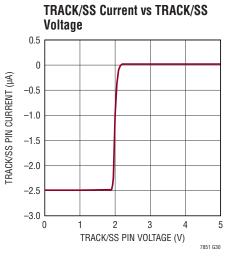

TRACK/SS1 (Pin 57), TRACK/SS2 (Pin 40), TRACK/SS3 (Pin 37), TRACK/SS4 (Pin 22): Combined Soft-Start and Tracking Inputs. For soft-start operation, connecting a capacitor from this pin to ground will control the voltage ramp at the output of the power supply. An internal 2.5µA current source will charge the capacitor and thereby control an extra input on the reference side of the error amplifier. For coincident tracking of both outputs at start-up, a resistor divider with values equal to those connected to the secondary VSNSP pin from the secondary output should be used to connect the secondary track input from the primary output. This pin is internally clamped to 2V, and is used to communicate over current events in a master-slave configuration.

RUN1 (Pin 53), RUN2 (Pin 51), RUN3 (Pin 27), RUN4 (Pin 23): Run Control Inputs. A voltage above 2.25V on either pin turns on the IC. However, forcing a RUN pin below 2V causes the IC to shut down that particular channel. There are  $1.5\mu A$  pull-up currents for these pins.

**PWM1 (Pin 52), PWM2 (Pin 50), PWM3 (Pin 26), PWM4 (Pin 24):** (Top) Gate Signal Output. This signal goes to the PWM or top gate input of the external gate driver or integrated driver MOSFET. This is a three-state compatible output. In three-state, the voltage of this pin will be determined by the external resistor divider.

PG00D1 (Pin 49), PG00D2 (Pin 38), PG00D3 (Pin 28), PG00D4 (Pin 25): Power Good Indicator Output for Each Channel. Open-drain logic out that is pulled to SGND when either channel output exceeds a ±10% regulation window, after the internal 30µs power bad mask timer expires.

$I_{LIM1}$  (Pin 48),  $I_{LIM2}$  (Pin 41),  $I_{LIM3}$  (Pin 36),  $I_{LIM4}$  (Pin 29): Current Comparator Sense Voltage Limit Selection Pin. Connect a resistor from this pin to SGND. This pin sources 20μA when the channel is a master channel. This pin does not source current when the channel is a slave channel. The resultant voltage sets the threshold for overcurrent protection. For multiphase operation, all  $I_{LIM}$  pins are tied together and only master channel's  $I_{LIM}$  pin sources 20μA.

## PIN FUNCTIONS

**lavg1** (**Pin 47**), **lavg2** (**Pin 42**), **lavg3** (**Pin 35**), **lavg4** (**Pin 30**): Average Current Monitor Pin. A capacitor tied to ground from the  $I_{AVG}$  pin stores a voltage proportional to the instantaneous average current of the master channel. When the average current is zero, the  $I_{AVG}$  pin voltage is 500mV. PolyPhase control is also implemented in part by connecting all slave  $I_{AVG}$  pins together to the master  $I_{AVG}$  output. The total capacitance on the  $I_{AVG}$  bus should range from 47pF to 220pF, inclusive, with the typical value being 100pF. Only the master phase contributes information to this average through an internal resistor in current sharing mode.

ISNS1P (Pin 46), ISNS2P (Pin 43), ISNS3P (Pin 34), ISNS4P (Pin 31): Current Sense Amplifier (+) Input. The (+) input to the current sense amplifier is normally connected to the midpoint of the inductor's parallel RC sense circuit or to the node between the inductor and sense resistor if using a discrete sense resistor.

**ISNS1N (Pin 45)**, **ISNS2N (Pin 44)**, **ISNS3N (Pin 33)**, **ISNS4N (Pin 32)**: Current Sense Amplifier (–) Input. The (–) input to the current amplifier is normally connected to the respective  $V_{OUT}$  at the inductor.

**VINSNS (Pin 39):**  $V_{IN}$  Sense Pin. Connects to the  $V_{IN}$  power supply to provide line feedforward compensation. A change in  $V_{IN}$  immediately modulates the input to the PWM comparator and changes the pulse width in an inversely proportional manner, thus bypassing the feedback loop and providing excellent transient line regulation. An external lowpass filter can be added to this pin to prevent noisy signals from affecting the loop gain.

**CLKOUT (Pin 54):** Digital Output used for Daisychaining Multiple LTC7851/LTC7851-1 ICs in Multiphase Systems. When all RUN pins are driven low, the CLKOUT pin is actively pulled up to  $V_{CC}$ . Signal swing is from  $V_{CC}$  to ground.

**CLKIN (Pin 55):** External Clock Synchronization Input. Applying an external clock between 250kHz to 2.25MHz will cause the switching frequency to synchronize to the clock. CLKIN is pulled high to  $V_{CC}$  by a 20k internal resistor. The rising edge of the CLKIN input waveform will align with the rising edge of PWM1 in closed-loop operation. If CLKIN is high or floating, a resistor from the FREQ pin to SGND sets the switching frequency. If CLKIN is low, the FREQ pin logic state selects an internal 600kHz or 1MHz preset frequency.

**FREQ (Pin 56):** Frequency Set/Select Pin. This pin sources  $20\mu\text{A}$  current. If CLKIN is high or floating, then a resistor between this pin and SGND sets the switching frequency. If CLKIN is low, the logic state of this pin selects an internal 600kHz or 1MHz preset frequency.

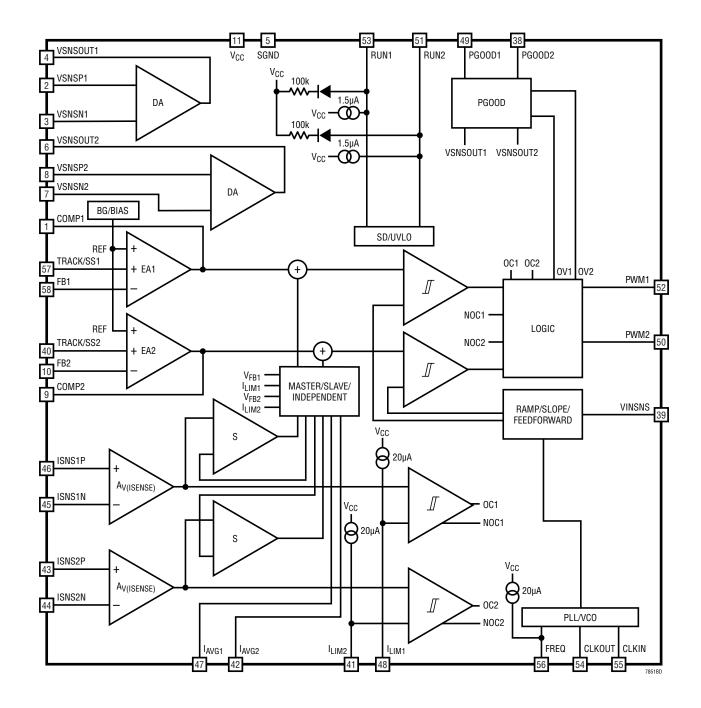

## **BLOCK DIAGRAM** (Only CH1 and CH2 Are Shown)

#### **Main Control Architecture**

The LTC7851/LTC7851-1 are guad-channel/guad-phase. constant frequency, voltage mode controllers for DC/DC step-down applications. They are designed to be used in a synchronous switching architecture with external integrated-driver MOSFETs (DrMOS), power blocks, or external drivers and N-channel MOSFETs using single wire three-state PWM interfaces. The LTC7851-1 is particularly suited for applications using power stages with integrated current sense signals. The controllers allow the use of sense resistors or lossless inductor DCR current sensing to maintain current balance between phases and to provide overcurrent protection. The operating frequency is selectable from 250kHz to 2.25MHz. To multiply the effective switching frequency, multiphase operation can be extended to 2, 3, 4, 8, or higher phases by paralleling additional controllers. In single phase operation, each channel can be used as an independent output, i.e. one single LTC7851/LTC7851-1 can provide four outputs.

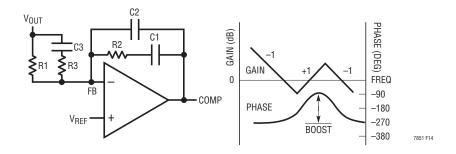

Unlike a conventional differential amplifier, in which the output is connected directly to the diffamp sensing pins, the output voltage is resistively divided externally to create a feedback voltage for the controller (see Figure 3, and Figure 4). Connect VSNSP of the unity-gain internal differential amplifier, DA, to the center tap of the feedback divider across the output load, and VSNSN to the load ground. The output of the differential amplifier VSNSOUT produces a signal equal to the differential voltage sensed across VSNSP and VSNSN. This scheme overcomes any ground offsets between local ground and remote output ground and common mode voltage variations, resulting in a more accurate output voltage.

In the main voltage mode control loop, the error amplifier output (COMP) directly controls the converter duty cycle in order to drive the FB pin to 0.6V in steady state. Dynamic changes in output load current can perturb the output voltage. When the output is below regulation, COMP rises, increasing the duty cycle. If the output rises above regulation, COMP will decrease, decreasing the duty cycle. As the output approaches regulation, COMP will settle to the steady-state value representing the stepdown conversion ratio.

In normal operation, the PWM latch is set high at the beginning of the clock cycle (assuming COMP > 0.5V). When the (line feedforward compensated) PWM ramp exceeds the COMP voltage, the comparator trips and resets the PWM latch. If COMP is less than 0.5V at the beginning of the clock cycle, as in the case of an overvoltage at the outputs, the PWM pin remains low throughout the entire cycle. When the PWM pin goes high, it has a minimum on-time of approximately 20ns and a minimum off-time of approximately one-twelfth the switching period.

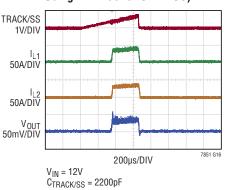

## **Current Sharing**

In multiphase operation, the LTC7851/LTC7851-1 also incorporate an auxiliary current sharing loop. Inductor current is sampled each cycle. The master's current sense amplifier output is averaged at the  $I_{AVG}$  pin. A small capacitor connected from  $I_{AVG}$  to GND (typically 100pF) stores a voltage corresponding to the instantaneous average current of the master. Master phase's and slave phase's  $I_{AVG}$  pins must be connected together. Each slave phase integrates the difference between its current and the master's. Within each phase the integrator output is proportionally summed with the system error amplifier voltage (COMP), adjusting that phase's duty cycle to equalize the currents. When multiple ICs are daisy chained, the  $I_{AVG}$  pins must be connected together. Figure 1 shows a transient load step with current sharing in a 3-phase system.

Figure 1. Mismatched Inductor Load Step Transient Response

Overcurrent Protection

The current sense amplifier outputs also connect to overcurrent (OC) comparators that provide fault protection in the case of an output short. When an OC fault is detected

Rev A

for 128 consecutive clock cycles, the controller three-states the PWM output, resets the soft-start capacitor, and waits for 32768 clock cycles before attempting to start up again. The 128 consecutive clock cycle counter has a 7-cycle hysteresis window, after which it will reset. The LTC7851/LTC7851-1 also provide negative OC (NOC) protection by preventing turn-on of the bottom MOSFET during a negative OC fault condition. In this condition, the bottom MOSFET will be turned on for 40ns every eight cycles to allow the driver IC to recharge its topside gate drive capacitor. The negative OC threshold is equal to -3/4 the positive OC threshold. See the Applications Information section for guidelines on setting these thresholds.

#### **Excellent Transient Response**

The LTC7851/LTC7851-1 error amplifiers are true operational amplifiers, meaning that they have high bandwidth, high DC gain, low offset and low output impedance. Their bandwidth, when combined with high switching frequencies and low-value inductors, allows the compensation network to be optimized for very high control loop crossover frequencies and excellent transient response. The 600mV internal reference allows regulated output voltages as low as 600mV without external level-shifting amplifiers.

#### **Line Feedforward Compensation**

The LTC7851/LTC7851-1 achieve outstanding line transient response using a feedforward correction scheme which instantaneously adjusts the duty cycle to compensate for changes in input voltage, significantly reducing output overshoot and undershoot. It has the added advantage of making the DC loop gain independent of input voltage. Figure 2 shows how large transient steps at the input have little effect on the output voltage.

Figure 2. Line Step Transient Response

#### Remote Sense Differential Amplifier

The LTC7851/LTC7851-1 include four low offset, unity gain, high bandwidth differential amplifiers for differential output sensing. Output voltage accuracy is significantly improved by removing board interconnection losses from the total error budget.

The noninverting input of the differential amplifier is connected to the midpoint of the feedback resistive divider between the positive and negative output capacitor terminals. The VSNSOUT is connected to the FB pin and the amplifier will attempt to regulate this voltage to 0.6V. The amplifier is configured for unity gain, meaning that the differential voltage between  $V_{SNSP}$  and  $V_{SNSN}$  is translated to  $V_{SNSOUT}$ , relative to SGND.

## **Shutdown Control Using the RUN Pins**

Each channel of the LTC7851/LTC7851-1 can be independently enabled using its own RUN pin. When all RUN pins are driven low, all internal circuitry, including the internal reference and oscillator, are completely shut down. When the RUN pin is low, the respective COMP pin is actively pulled down to ground. In a multiphase operation when the COMP pins are tied together, the COMP pin is held low until all the RUN pins are enabled. This ensures a synchronized start-up of all the channels. A 1.5 $\mu$ A pull-up current is provided for each RUN pin internally. The RUN pins remain high impedance up to V<sub>CC</sub>.

#### **Undervoltage Lockout**

To prevent operation of the power supply below safe input voltage levels, all channels are disabled when  $V_{\rm CC}$  is below

the undervoltage lockout (UVLO) threshold (2.9V falling, 3V rising). If a RUN pin is driven high, the LTC7851/LTC7851-1 will start up the reference to detect when  $V_{CC}$  rises above the UVLO threshold, and enable the appropriate channel.

#### **Overvoltage Protection**

If the output voltage rises to more than 10% above the set regulation value, which is reflected as a VSNSOUT voltage of 0.66V or above, the LTC7851/LTC7851-1 will force the PWM output low to turn on the bottom MOSFET and discharge the output. Normal operation resumes once the output is back within the regulation window. However, if the reverse current flowing from V<sub>OUT</sub> back through the bottom power MOSFET to PGND is greater than 3/4 the positive OC threshold, the NOC comparator trips and shuts off the bottom power MOSFET to protect it from being destroyed. This scenario can happen when the LTC7851/LTC7851-1 try to start into a precharged load higher than the OV threshold. As a result, the bottom switch turns on until the amount of reverse current trips the NOC comparator threshold.

## Nonsynchronous Start-Up and Prebiased Output

The LTC7851/LTC7851-1 will start up with seven cycles of nonsynchronous operation before switching over to a forced continuous mode of operation. The PWM output will be in a three-state condition until start-up. The controller will start the seven nonsynchronous cycles if it is not in an overcurrent or prebiased condition, and if the COMP pin voltage is higher than 500mV, or if the TRACK/SS pin voltage is higher than 900mV. During the seven nonsynchronous cycles the PWM latch is set high at the beginning of the clock cycle, if COMP > 0.5V, causing the PWM output to transition from three-state to  $V_{CC}$ . The latch is reset when the PWM ramp exceeds the COMP voltage, causing the PWM output to transition from V<sub>CC</sub> to threestate followed immediately by a 20ns three-state to ground pulse. The 7-cycle nonsynchronous mode of operation is enabled at initial start-up and also during a restart from a fault condition. In multiphase operation, where all the TRACK/SS pins should be connected together, only an overcurrent event on the master channel will discharge the

soft-start capacitor. After 32768 cycles, it will synchronize the restart of all channels in to the nonsynchronous mode of operation.

The LTC7851/LTC7851-1 can safely start-up into a prebiased output without discharging the output capacitors. A prebias is detected when the FB pin voltage is higher than the TRACK/SS or the internal soft-start voltage. A prebiased condition will force the COMP pin to be held low, and will three-state the PWM output. The prebiased condition is cleared when the TRACK/SS or the internal soft-start voltage is higher than the FB pin voltage or 900mV, whichever is lower. If the output prebias is higher than the OV threshold then the PWM output will be low, which will pull the output back in to the regulation window.

#### **Internal Soft-Start**

By default, the start-up of each channel's output voltage is normally controlled by an internal soft-start ramp. The internal soft-start ramp represents a noninverting input to the error amplifier. The FB pin is regulated to the lower of the error amplifier's three noninverting inputs (the internal soft-start ramp for that channel, the TRACK/SS pin or the internal 600mV reference). As the ramp voltage rises from 0V to 0.6V over approximately 2ms, the output voltage rises smoothly from its prebiased value to its final set value.

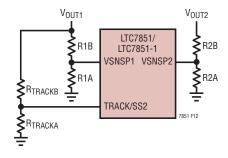

#### Soft-Start and Tracking Using TRACK/SS Pin

The user can connect an external capacitor greater than 10nF to the TRACK/SS pin for the relevant channel to increase the soft-start ramp time beyond the internally set default. The TRACK/SS pin represents a noninverting input to the error amplifier and behaves identically to the internal ramp described in the previous section. An internal 2.5µA current source charges the capacitor, creating a voltage ramp on the TRACK/SS pin. The TRACK/SS pin is internally clamped to 2V. As the TRACK/SS pin voltage rises from 0V to 0.6V, the output voltage rises smoothly from 0V to its final value in:

$$\frac{C_{SS}(\mu F) {\bullet} 0.6 V}{2.5 \mu A} \text{ seconds}$$

Alternatively, the TRACK/SS pin can be used to force the start-up of  $V_{OUT}$  to track the voltage of another supply. Typically this requires connecting the TRACK/SS pin to an external divider from the other supply to ground (see the Applications Information section). It is only possible to track another supply that is slower than the internal soft-start ramp. The TRACK/SS pin also has an internal open-drain NMOS pull-down transistor that turns on to reset the TRACK/SS voltage when the channel is shut down (RUN = 0V or  $V_{CC}$  < UVLO threshold) or during an OC fault condition.

In multiphase operation, one master error amplifier is used to control all of the PWM comparators. The FB pins for the unused error amplifiers are connected to  $V_{CC}$  in order to three-state these amplifier outputs and the COMP pins are connected together. When the FB pin is tied to  $V_{CC}$ , the internal 2.5µA current source on the TRACK/SS pin is disabled for that channel. The TRACK/SS pins should also be connected together so that the slave phases can detect when soft-start is complete and to synchronize the nonsynchronous mode of operation.

#### Frequency Selection and the Phase-Locked Loop (PLL)

The selection of the switching frequency is a trade-off between efficiency, transient response and component size. High frequency operation reduces the size of the inductor and output capacitor as well as increasing the maximum practical control loop bandwidth. However, efficiency is generally lower due to increased transition and switching losses.

The LTC7851/LTC7851-1's switching frequency can be set in three ways: using an external resistor to linearly program the frequency, synchronizing to an external clock, or simply selecting one of two fixed frequencies (600kHz and 1MHz). Table 1 highlights these modes.

**Table 1. Frequency Selection**

| CLKIN PIN     | FREQ PIN                 | FREQUENCY         |

|---------------|--------------------------|-------------------|

| Clocked       | R <sub>FREQ</sub> to GND | 250kHz to 2.25MHz |

| High or Float | R <sub>FREQ</sub> to GND | 250kHz to 2.25MHz |

| Low           | Low                      | 600kHz            |

| Low           | High                     | 1MHz              |

No external PLL filter is required to synchronize the LTC7851/LTC7851-1 to an external clock. Applying an external clock signal to the CLKIN pin will automatically enable the PLL with internal filter.

Constant-frequency operation brings with it a number of benefits: inductor and capacitor values can be chosen for a precise operating frequency and the feedback loop can be similarly tightly specified. Noise generated by the circuit will always be at known frequencies.

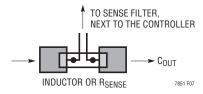

#### Using the CLKOUT Pin in Multiphase Applications

The LTC7851/LTC7851-1 feature a CLKOUT pin, which allows multiple LTC7851/LTC7851-1 ICs to be daisy chained together in multiphase applications. The clock output signal on the CLKOUT pin can be used to synchronize additional ICs in a multiphase power supply solution feeding a single high current output, or even several outputs from the same input supply.

The phase relationship among each channel, as well as the phase relationship between channel 1 and CLKOUT, are summarized in Table 2. The phases are calculated relative to zero degrees, defined as the rising edge of PWM1. Refer to Application Information for more details on how to create multiphase applications.

Table 2. Phase Relationship

| CH-1   | 0°   |

|--------|------|

| CH-2   | 180° |

| CH-3   | 90°  |

| CH-4   | 270° |

| CLKOUT | 45°  |

## Using the LTC7851/LTC7851-1 Error Amplifiers in Multiphase Applications

Due to the low output impedance of the error amplifiers, multiphase applications using the LTC7851/LTC7851-1 use one error amplifier as the master with all of the slaves' error amplifiers disabled. The channel 1 error amplifier (phase =  $0^{\circ}$ ) may be used as the master with phases 2 through n (up to 12) serving as slaves. To disable the slave error amplifiers, connect the FB pins of the slaves

to  $V_{CC}$ . This three-states the output stages of the amplifiers. All COMP pins should then be connected together to create PWM outputs for all phases. As noted in the section on soft-start, all TRACK/SS pins should also be shorted together. Refer to the Multiphase Operation section in Applications Information for schematics of various multiphase configurations.

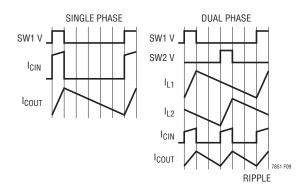

#### Theory and Benefits of Multiphase Operation

Multiphase operation provides several benefits over traditional single phase power supplies:

- Greater output current capability

- Improved transient response

- Reduction in component size

- Increased real world operating efficiency

Because multiphase operation parallels power stages, the amount of output current available is n times what it would be with a single comparable output stage, where n is equal to the number of phases.

The main advantages of PolyPhase operation are ripple current cancellation in the input and output capacitors, a faster load step response due to a smaller clock delay and reduced thermal stress on the inductors and MOSFETs due to current sharing between phases. These advantages allow for the use of a smaller size or a smaller number of components.

#### Power Good Indicator Pins (PGOOD)

Each PGOOD pin is connected to the open drain of an internal pull-down device which pulls the PGOOD pin low when the corresponding VSNSOUT pin voltage is outside the PGOOD regulation window (±7.5% entering regulation, ±10% leaving regulation). The PGOOD pins

are also pulled low when the corresponding RUN pin is low, or during UVLO.

When the VSNSOUT pin voltage is within the  $\pm 10\%$  regulation window, the internal PGOOD MOSFET is turned off and the pin is normally pulled up by an external resistor. When the VSNSOUT pin is exiting a fault condition (such as during normal output voltage start-up, prior to regulation), the PGOOD pin will remain low for an additional  $30\mu s$ . This allows the output voltage to reach steady-state regulation and prevents the enabling of a heavy load from retriggering a UVLO condition.

In multiphase application, only the master phase differential and error amplifiers are used to control all phases. The slave phase differential amplifiers are three-stated. The slave phase VSNSOUT pins are connected to the master phase VSNSOUT pin to obtain output voltage information. Only the PGOOD output for the master control error amplifier should be connected to the fault monitor.

#### **PWM Pins**

The PWM pins are three-state compatible outputs, designed to drive MOSFET drivers, DrMOSs, power blocks, etc., which do not represent a heavy capacitive load. An external resistor divider may be used to set the voltage to mid-rail while in the high impedance state.

#### **Line Feedforward Gain**

In a typical LTC7851/LTC7851-1 circuit, the feedback loop consists of the line feedforward circuit, the modulator, the external inductor, the output capacitor and the feedback amplifier with its compensation network. All these components affect loop behavior and need to be accounted for in the loop compensation. The modulator consists of the PWM generator, the external output MOSFET drivers and the external MOSFETs themselves. The modulator gain varies linearly with the input voltage. The line feedforward circuit compensates for this change in gain, and provides a constant gain from the error amplifier output to the inductor input regardless of input voltage. From a feedback loop point of view, the combination of the line feedforward circuit and the modulator looks like a linear voltage transfer function from COMP to the inductor input and has a gain roughly equal to 12V/V.

Rev A

## Output Voltage Programming and Differential Output Sensing

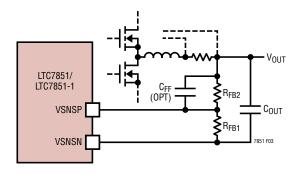

The LTC7851/LTC7851-1 integrate differential output sensing with output voltage programming, allowing for a simple and seamless design. As shown in Figure 3, the output voltage is programmed by an external resistor divider from the regulated output point to its ground reference. The resistive divider is tapped by the VSNSP pin, and the ground reference is sensed by VSNSN. An optional feedforward capacitor, C<sub>FF</sub>, can be used to improve the transient performance. The resulting output voltage is given according to the following equation:

$$V_{OUT} = 0.6V \bullet \left(1 + \frac{R_{FB2}}{R_{FB1}}\right)$$

Figure 3. Setting Output Voltage

More precisely, the  $V_{OUT}$  value programmed in the previous equation is with respect to the output's ground reference, and thus, is a differential quantity. The minimum differential output voltage is limited to the internal reference, 0.6V, and the maximum differential output voltage is  $V_{CC} = 0.5V$ .

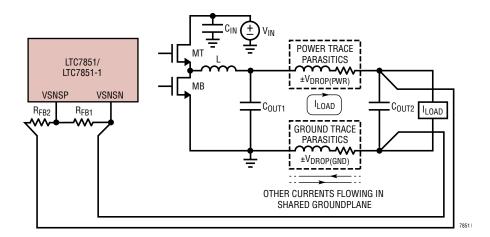

The VSNSP pin is high impedance with no input bias current. The VSNSN pin has about 7.5µA of current flowing out of the pin. Differential output sensing allows for more accurate output regulation in high power distributed systems having large line losses. Figure 4 illustrates the potential variations in the power and ground lines due to parasitic elements. These variations are exacerbated in multi-application systems with shared ground planes. Without differential output sensing, these variations directly reflect as an error in the regulated output voltage.

The LTC7851/LTC7851-1's differential output sensing scheme is distinct from conventional schemes. In conventional schemes, the regulated output and its ground reference are directly sensed with a difference amplifier whose output is then divided down with an external resistive divider and fed into the error amplifier input. This conventional scheme is limited by the common mode input range of the difference amplifier and typically limits differential sensing to the lower range of output voltages.

The LTC7851/LTC7851-1 allow for seamless differential output sensing by sensing the resistively divided feedback voltage differentially. This allows for differential sensing in the full output range from 0.6V to  $V_{CC}$  – 0.5V. The dif-

Figure 4. Differential Output Sensing Used to Correct Line Loss Variations in a High Power Distributed System with a Shared Ground Plane

ference amplifier of the LTC7851/LTC7851-1 has a gain bandwidth of 40MHz, high enough not to affect main loop compensation and transient behavior. To avoid noise coupling into VSNSP, the resistor divider should be placed near the VSNSP and VSNSN pins and physically close to the LTC7851/LTC7851-1. The remote output and ground traces should be routed parallel to each other as a differential pair to the remote output. These traces should be terminated as close as physically possible to the remote output point that is to be accurately regulated through remote differential sensing. In addition, avoid routing these sensitive traces near any high speed switching nodes in the circuit. Ideally, they should be shielded by a low impedance ground plane to maintain signal integrity.

#### **Programming the Operating Frequency**

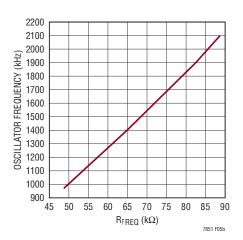

The LTC7851/LTC7851-1 can be hard wired to one of two fixed frequencies, linearly programmed to any frequency between 250kHz and 2.25MHz or synchronized to an external clock.

Table 1 in the Operation section shows how to connect the CLKIN and FREQ pins to choose the mode of frequency programming. The frequency of operation is given by the following equation:

Frequency =  $(R_{FREQ} - 19.8k\Omega) \cdot 33.5Hz/\Omega$ , when Frequency is <1MHz

Frequency =  $(R_{FREQ} - 14.6k\Omega) \cdot 28.1Hz/\Omega$ , when Frequency is  $\geq 1MHz$

Figure 5 shows operating frequency vs R<sub>FREQ</sub>.

Figure 5. Oscillator Frequency vs R<sub>FREO</sub>

#### **Frequency Synchronization**

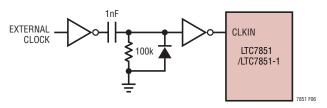

The LTC7851/LTC7851-1 incorporate an internal phase-locked loop (PLL) which enables synchronization of the internal oscillator (rising edge of PWM1) to an external clock from 250kHz to 2.25MHz.

Since the entire PLL is internal to the LTC7851/LTC7851-1, simply applying a CMOS level clock signal to the CLKIN pin will enable frequency synchronization. A resistor from FREQ to GND is still required to set the free running frequency close to the sync input frequency. For cases where the LTC7851/LTC7851-1's CLKOUT and CLKIN signals are daisy chained, make sure the controllers in the daisy chain are enabled at the same time or the slave is enabled after its master.

There is a sequencing requirement for the external clock and the RUN pin. Make sure the external clock is applied before any RUN pin is enabled. If the external clock has to be applied after the RUN pin is enabled, the initial frequency must be set by R<sub>FREQ</sub>. To enable this resistor-set frequency, keep CLKIN high until the external clock starts switching. (The circuit in Figure 6 can be used to achieve this function.)

Figure 6. The Circuit to Keep the CLKIN Pin High Before the External Clock Starts Switching

## **Choosing the Inductor and Setting the Current Limit**

The inductor value is related to the switching frequency, which is chosen based on the trade-offs discussed in the Operation section. The inductor can be sized using the following equation:

$$L = \left(\frac{V_{OUT}}{f \bullet \Delta I_{L}}\right) \bullet \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Choosing a larger value of  $\Delta I_L$  leads to smaller L, but results in greater core loss (and higher output voltage ripple for a given output capacitance and/or ESR). A reasonable starting point for setting the ripple current is 30% of the maximum output current, or:

$$\Delta I_L = 0.3 \bullet I_{OUT}$$

The inductor saturation current rating needs to be higher than the peak inductor current during transient conditions. If  $I_{OUT}$  is the maximum rated load current, then the maximum transient current,  $I_{MAX}$ , would normally be chosen to be some factor (e.g., 60%) greater than  $I_{OUT}$ :

$$I_{MAX} = 1.6 \bullet I_{OUT}$$

The minimum saturation current rating should be set to allow margin due to manufacturing and temperature variation in the sense resistor or inductor DCR. A reasonable value would be:

$$I_{SAT} = 2.2 \bullet I_{OUT}$$

The programmed current limit must be low enough to ensure that the inductor never saturates and high enough to allow increased current during transient conditions, to account for inductor ripple current and to allow margin for DCR variation.

For DCR sensing:

$$I_{LIMIT} = 1.6 \bullet I_{OUT} + \frac{\Delta I_L}{2}$$

For discrete sense resistor:

$$I_{LIMIT} = 1.3 \bullet I_{OUT} + \frac{\Delta I_L}{2}$$

where

$$\Delta I_{L} = \frac{V_{OUT}}{L \bullet f_{SW} \bullet \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

provided that  $I_{LIMIT} < I_{SAT}$ .

If the sensed inductor current exceeds current limit for 128 consecutive clock cycles, the IC will three-state the PWM output, reset the soft-start timer and wait 32768 switching cycles before attempting to return the output to regulation.

The current limit is programmed using a resistor from the  $I_{LIM}$  pin to SGND. The  $I_{LIM}$  pin sources  $20\mu\text{A}$  to generate a voltage corresponding to the current limit. The current sense circuit has a voltage gain of 20 for the LTC7851 (4 for the LTC7851-1) and a zero current level of 500mV. Therefore, the current limit resistor should be set using the following equation for the LTC7851:

$$R_{ILIM} = \frac{20 \bullet I_{LIMIT\_PHASE} \bullet R_{SENSE} + 0.5V}{20 \mu A}$$

The equation for the LTC7851-1 is:

$$R_{ILIM} = \frac{4 \cdot I_{LIMIT\_PHASE} \cdot R_{SENSE} + 0.5V}{20 \mu A}$$

In multiphase applications, all  $I_{LIM}$  pins are tied together and only one current limit resistor should be used. The master channel's  $I_{LIM}$  pin sources 20µA. Slave channels'  $I_{LIM}$  pins do not source any current.

#### Inductor Core Selection

Once the value of L is known, the type of inductor must be selected. High efficiency converters generally cannot afford the core losses found in low cost powdered iron cores, forcing the use of more expensive ferrite or molypermalloy cores. Also, core losses decrease as inductance increases. Unfortunately, increased inductance requires more turns of wire, larger inductance and larger copper losses.

Ferrite designs have very low core loss and are preferred at high switching frequencies. However, these core materials exhibit "hard" saturation, causing an abrupt reduction in the inductance when the peak current capability is exceeded. **Do not allow the core to saturate!**

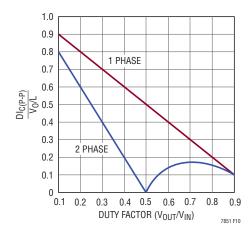

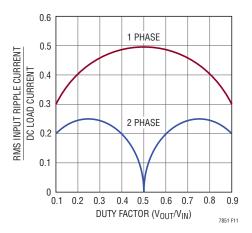

#### **CIN Selection**

The input bypass capacitor in the LTC7851/LTC7851-1 circuit is common to all channels. The input bypass capacitor needs to meet these conditions: its ESR must be low

enough to keep the supply drop low as the top MOSFETs turn on, its RMS current capability must be adequate to withstand the ripple current at the input, and the capacitance must be large enough to maintain the input voltage until the input supply can make up the difference. Generally, a capacitor (particularly a non-ceramic type) that meets the first two parameters will have far more capacitance than is required to keep capacitance-based droop under control.

The input capacitor's voltage rating should be at least 1.4 times the maximum input voltage. Power loss due to ESR occurs not only as I<sup>2</sup>R dissipation in the capacitor itself, but also in overall battery efficiency. For mobile applications, the input capacitors should store adequate charge to keep the peak battery current within the manufacturer's specifications.

The input capacitor RMS current requirement is simplified by the multiphase architecture and its impact on the worst-case RMS current drawn through the input network (battery/fuse/capacitor). It can be shown that the worst-case RMS current occurs when only one controller is operating. The controller with the highest  $(V_{OUT})(I_{OUT})$  product needs to be used to determine the maximum RMS current requirement. Increasing the output current drawn from the other out-of-phase controller will actually decrease the input RMS ripple current from this maximum value. The out-of-phase technique typically reduces the input capacitor's RMS ripple current by a factor of 30% to 70% when compared to a single phase power supply solution.

In continuous mode, the source current of the top N-channel MOSFET is approximately a square wave of duty cycle  $V_{OUT}/V_{IN}$ . The maximum RMS capacitor current is given by:

$$I_{RMS} \approx I_{OUT(MAX)} \frac{\sqrt{V_{OUT} \left(V_{IN} - V_{OUT}\right)}}{V_{IN}}$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. The total RMS current is lower when both controllers are operating due to the interleaving of current pulses through the input capacitors. This is why the input capacitance requirement calculated above for the worst-case controller is adequate for the dual controller design.

Rev A

Note that capacitor manufacturer's ripple current ratings are often based on only 2000 hours of life. This makes it advisable to further derate the capacitor or to choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design. Always consult the manufacturer if there is any question.

Ceramic, tantalum, OS-CON and switcher-rated electrolytic capacitors can be used as input capacitors, but each has drawbacks: ceramics have high voltage coefficients of capacitance and may have audible piezoelectric effects; tantalums need to be surge-rated; OS-CONs suffer from higher inductance, larger case size and limited surface mount applicability; and electrolytics' higher ESR and dryout possibility require several to be used. Sanyo OS-CON SVP, SVPD series; Sanyo POSCAP TQC series or aluminum electrolytic capacitors from Panasonic WA series or Cornell Dubilier SPV series, in parallel with a couple of high performance ceramic capacitors, can be used as an effective means of achieving low ESR and high bulk capacitance.

## **COUT Selection**

The selection of  $C_{OUT}$  is primarily determined by the ESR required to minimize voltage ripple and load step transients. The output ripple  $\Delta V_{OUT}$  is approximately bounded by:

$$\Delta V_{OUT} \le \Delta I_L \left( ESR + \frac{1}{8 \bullet f_{SW} \bullet C_{OUT}} \right)$$

where  $\Delta I_L$  is the inductor ripple current.

$\Delta I_{L}$  may be calculated using the equation:

$$\Delta I_{L} = \frac{V_{OUT}}{L \bullet f_{SW}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Since  $\Delta I_L$  increases with input voltage, the output ripple voltage is highest at maximum input voltage. Typically, once the ESR requirement is satisfied, the capacitance is adequate for filtering and has the necessary RMS current rating.

Manufacturers such as Sanyo, Panasonic and Cornell Dubilier should be considered for high performance throughhole capacitors. The OS-CON semiconductor electrolyte capacitor available from Sanyo has a good (ESR)(size) product. An additional ceramic capacitor in parallel with OS-CON capacitors is recommended to offset the effect of lead inductance.

In surface mount applications, multiple capacitors may have to be paralleled to meet the ESR or transient current handling requirements of the application. Aluminum electrolytic and dry tantalum capacitors are both available in surface mount configurations. New special polymer surface mount capacitors offer very low ESR also but have much lower capacitive density per unit volume. In the case of tantalum, it is critical that the capacitors are surge tested for use in switching power supplies. Several excellent output capacitor choices include the Sanyo POSCAP TPD, TPE, TPE series, the Kemet T520, T530 and A700 series, NEC/Tokin NeoCapacitors and Panasonic SP series. Other capacitor types include Nichicon PL series and Sprague 595D series. Consult the manufacturer for other specific recommendations.

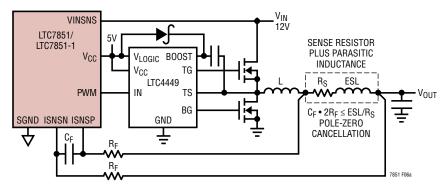

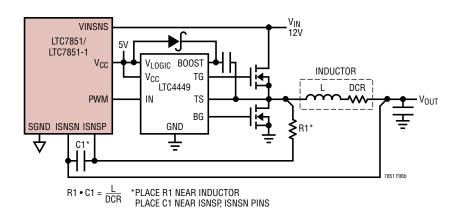

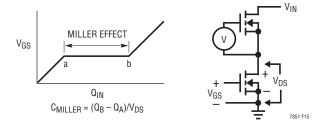

#### **Current Sensing**

To maximize efficiency, the LTC7851/LTC7851-1 are designed to sense current through the inductor's DCR, as shown in Figure 7. The DCR of the inductor represents the small amount of DC winding resistance of the copper, which for most inductors applicable to this application, is between  $0.3 m\Omega$  and  $1 m\Omega$  for the LTC7851, between  $1 m\Omega$  and  $3 m\Omega$  for the LTC7851-1. If the filter RC time constant is chosen to be exactly equal to the L/DCR time constant of the inductor, the voltage drop across the external capacitor is equal to the voltage drop across the inductor DCR. Check the manufacturer's data sheet for specifications regarding the inductor DCR in order to properly dimension the external filter components. The DCR of the inductor can also be measured using a good RLC meter.

FILTER COMPONENTS PLACED NEAR SENSE PINS

#### (a) Using a Resistor to Sense Current

(b) Using the Inductor to Sense Current

Figure 7. Two Different Methods of Sensing Current

Since the temperature coefficient of the inductor's DCR is 3900ppm/°C, first order compensation of the filter time constant is possible by using filter resistors with an equal but opposite (negative) TC, assuming a low TC capacitor is used. That is, as the inductor's DCR rises with increasing temperature, the L/DCR time constant drops. Since we want the filter RC time constant to match the L/DCR time constant, we also want the filter RC time constant to drop with increasing temperature. Typically, the inductance will also have a small negative TC.

The ISNSP and ISNSN pins are the inputs to the current comparators. The common mode range of the current comparators is -0.3V to  $V_{CC}-0.5V$ . Continuous linear operation is provided throughout this range, allowing output voltages between 0.6V (the reference input to the error amplifiers) and  $V_{CC}-0.5V$ . The maximum output voltage is lower than  $V_{CC}$  to account for output ripple and output overshoot. The maximum differential current sense input ( $V_{ISNSP}-V_{ISNSN}$ ) is 50mV for the LTC7851, 150mV for the LTC7851-1.

The high impedance inputs to the current comparators allow accurate DCR sensing. However, care must be taken not to float these pins during normal operation.

Filter components mutual to the sense lines should be placed close to the LTC7851/LTC7851-1, and the sense lines should run close together to a Kelvin connection underneath the current sense element (shown in Figure 8). Sensing current elsewhere can effectively add parasitic

Figure 8. Sense Lines Placement with Inductor or Sense Resistor

inductance and capacitance to the current sense element, degrading the information at the sense terminals and making the programmed current limit unpredictable. If low value ( $<5m\Omega$ ) sense resistors are used, verify that the signal across  $C_F$  resembles the current through the inductor, and reduce  $R_F$  to eliminate any large step associated with the turn-on of the primary switch. If DCR sensing is used (Figure 7b), sense resistor R1 should be placed close to the switching node, to prevent noise from coupling into sensitive small-signal nodes. The capacitor C1 should be placed close to the IC pins.

For the DrMOS with integrated current sensing, the current sense information is provided by the DrMOS itself. The common mode voltage of the ISNSP and ISNSN pins are set by the DrMOS. As a result, the maximum  $V_{OUT}$  is not limited by  $V_{CC}-0.5V$  anymore.

#### **Multiphase Operation**

When the LTC7851/LTC7851-1 are used in a single output, multiphase application, the slave error amplifiers must be disabled by connecting their FB pins to  $V_{CC}$ . All current limits should be set to the same value using only one resistor to SGND. In a multiphase application, all COMP, RUN,  $I_{LIM}$ ,  $I_{AVG}$ , VSNSOUT and TRACK/SS pins must be connected together.

The total capacitance on the I<sub>AVG</sub> bus should range from 47pFto 220pF, inclusive, with the typical value being 100pF.

For output loads that demand high current, multiple LTC7851/LTC7851-1s can be daisy chained to run out of phase to provide more output current without increasing input and output voltage ripple. The CLKIN pin allows the LTC7851/LTC7851-1 to synchronize to the CLKOUT signal of another LTC7851/LTC7851-1. The CLKOUT signal can be connected to the CLKIN pin of the following LTC7851/LTC7851-1 stage to line up both the frequency and the phase of the entire system. Figure 9 shows the pin connections necessary for 3-, 4-, 8- or 12-phase operation. A total of twelve phases can be daisy chained to run simultaneously out of phase with respect to each other.

0 LTC6902 OUT1 0, 180, 90, 270 120, 300, 210, 30 240, 60, 330, 150 CLKOUT COMP1 COMP2 CLKIN CLKOUT CLKIN CLKOUT COMP1 CLKIN FR1 COMP1 VCC . FR1 FR<sub>1</sub> LTC7851 COMP2 LTC7851 COMP2 FB2 LTC7851  $V_{\text{CC}}$ FB3 FB4 COMP3 COMP4 FB3 FB4 COMP3 COMP4 FB3 FB4 COMP3 /LTC7851-1 /LTC7851-1 /LTC7851-1 TRACK/SS1 TRACK/SS1 TRACK/SS1 I<sub>LIM1</sub> I<sub>LIM1</sub> I<sub>LIM1</sub> TRACK/SS2 TRACK/SS2 TRACK/SS2 LIM2 LIM2 LIM2 TRACK/SS3 TRACK/SS3 TRACK/SS3 I<sub>IIM3</sub> I<sub>LIM3</sub> I<sub>LIM3</sub> I<sub>LIM4</sub> VSNSOUT1 TRACK/SS4 TRACK/SS4 TRACK/SS4 I<sub>LIM4</sub> VSNSOUT1 I<sub>LIM4</sub> VSNSOUT1 I<sub>AVG1</sub> I<sub>AVG2</sub> I<sub>AVG1</sub> I<sub>AVG2</sub> I<sub>AVG1</sub> I<sub>AVG2</sub> <u>}</u> VSNSOUT2 VSNSOUT2 VSNSOUT3 VSNSOUT4 VSNSOUT3 I<sub>AVG3</sub> VSNSOUT3 I<sub>AVG3</sub> I<sub>AVG3</sub> VSNSOUT4 I<sub>AVG4</sub> I<sub>AVG4</sub> I<sub>AVG4</sub> (d) 12-Phase

Figure 9. Multiphase Operation Setup