## LTC6226/LTC6227

$1nV/\sqrt{Hz}$  420MHz GBW, 180V/µs, Low Distortion Rail-to-Rail Output Op Amps

### FEATURES

- Ultra Low Voltage Noise: 1nV/√Hz

- Low Distortion: HD2/HD3<–90dB<sub>C</sub> at 4V<sub>P-P</sub>,1MHz into 1kΩ

- High Slew Rate: 180V/µs

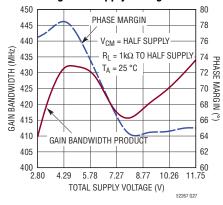

- GBW = 420MHz

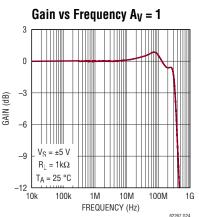

- -3dB Frequency (A<sub>V</sub> = +1): 330MHz

- Input Common Mode Range Includes Negative Rail

- Output Swings Rail-to-Rail

- Supply Current: 5.5mA/Channel Typ

- Operating Supply Range: 2.8V to 11.75V

- Input Offset Voltage: 95µV Max

- Offset Drift :0.4µV/°C

- Low Power Shutdown

- Very High Open Loop Gain: 9V/μV (139dB), R<sub>L</sub> = 1kΩ

- Operating Temp Range: –40°C to 125°C

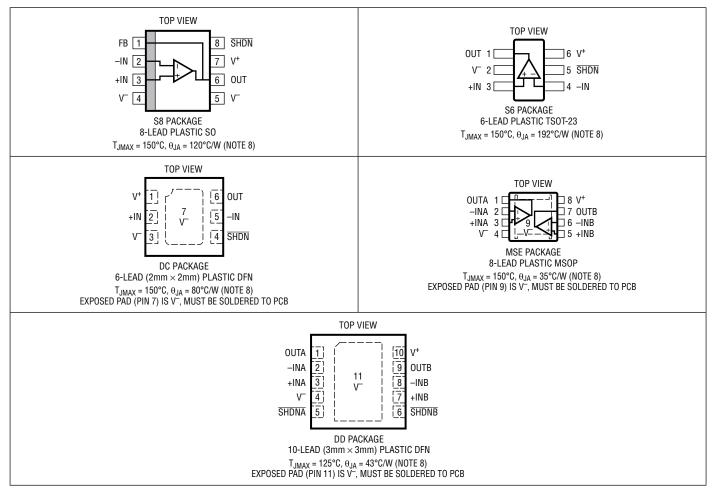

- Single in 8-Lead SOIC, TSOT-23, 2mm × 2mm DFN. Duals in 3mm × 3mm DFN, MS8E

### **APPLICATIONS**

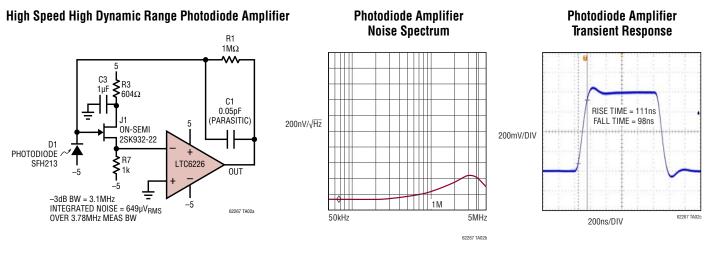

- Optical Electronics: Fast AC-Coupled Transimpedance Amplifiers

- Driving High Dynamic Range A/D Converters

- Active Filters

- Video Amplifiers

- Low Voltage Low Distortion Amplification

### DESCRIPTION

The LTC®6226/LTC6227 are very fast, low noise rail-to-rail output, unity gain stable single/dual op amps, with a gainbandwidth product of 420MHz and a slew rate of 180V/µs. The low input referred voltage noise of only  $1nV/\sqrt{Hz}$  and low distortion of less than  $-90dB_C$  for  $4V_{P-P}$  signals at 1MHz makes them ideal for applications that require high dynamic range and deal with very fast signals, such as driving A/D converters.

The combination of low offset, low offset drift, high gain (139dB) and high CMRR (114dB) make these excellent devices for high dynamic range applications.

The LTC6226 family maintains excellent performance for supply voltages of 2.8V to 11.75V and the devices are fully specified at supplies of 3V, 5V and 10V ( $\pm$ 5V).

With an input range extending to the negative rail and rail-to-rail output stage, the operational amplifier can accommodate wide swinging signals, and true single supply operation.

For space constrained applications, the amplifiers come in  $2mm \times 2mm$  DFN (single) and  $3mm \times 3mm$  DFN (dual) packages. The devices are also available in 8-lead SOIC,TSOT-23 and MS8E.

These amplifiers can be used as replacements for many high speed op amps to improve speed, noise and dynamic range.

All registered trademarks and trademarks are the property of their respective owners.

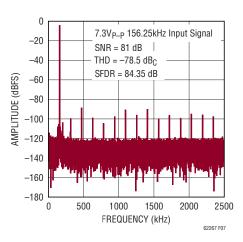

## TYPICAL APPLICATION

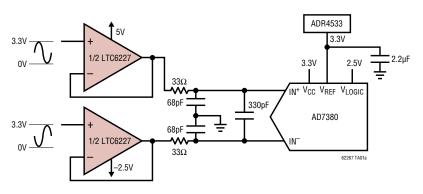

High Performance Transparent LTC6227 Based Driver for the 16-Bit AD7380

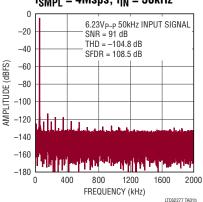

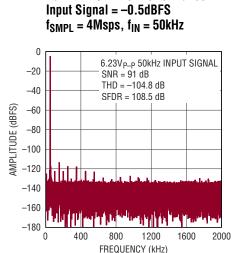

#### 16-Bit ADC Driver Performance Input Signal = -0.5dBFS f<sub>SMPL</sub> = 4Msps, f<sub>IN</sub> = 50kHz

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Total Supply Voltage (V <sup>-</sup> to V <sup>+</sup> )12                                 |    |

|--------------------------------------------------------------------------------------------|----|

| Input Voltage (–IN, +IN, $\overline{SHDN}$ ) V <sup>–</sup> – 0.3V to V <sup>+</sup> + 0.3 | ۶V |

| Input Current (-IN, +IN, SHDN) (Note 2)±10m                                                | ۱A |

| Operating Temperature Range                                                                |    |

| LTC6226I/LTC6227I (Note 4)40°C to 85°                                                      | °C |

| LTC6226H/LTC6227H (Note 4)40°C to 125°                                                     | °C |

| Specified Temperature Range                                                                |    |

| LTC6226I/LTC6227I (Note 4)40°C to 85°                                                      | °C |

| LTC6226H/LTC6227H (Note 4) –40°C to 125°                                                   | °C |

|                                                                                            |    |

| Output Current (Note 3)          | ±100mA            |

|----------------------------------|-------------------|

| Output Short-Circuit Duration    | Thermally Limited |

| Storage Temperature Range        | –65°C to 125°C    |

| Maximum Junction Temperature     | 150°C             |

| MSOP Lead Temperature (Soldering | 10s) 300°C        |

### PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL      | PART MARKING | PACKAGE DESCRIPTION      | TEMPERATURE RANGE |

|-------------------|--------------------|--------------|--------------------------|-------------------|

| LTC6226IS6#TRMPBF | LTC6226IS6#TRPBF   | LTHGY        | 6-Lead TSOT-23           | -40°C to 85°C     |

| LTC6226HS6#TRMPBF | LTC6226HS6#TRPBF   | LTHGY        | 6-Lead TSOT-23           | -40°C to 125°C    |

| LTC6226IDC#TRMPBF | LTC6226IDC#TRPBF   | LHGZ         | 6-Lead 2mm × 2mm DFN     | -40°C to 85°C     |

| LTC6226HDC#TRMPBF | LTC6226HDC#TRPBF   | LHGZ         | 6-Lead 2mm × 2mm DFN     | -40°C to 125°C    |

| LTC6226IS8#PBF    | LTC6226IS8#TRPBF   | 6226         | 8-Lead SOIC-8            | -40°C to 85°C     |

| LTC6226HS8#PBF    | LTC6226HS8#TRPBF   | 6226         | 8-Lead SOIC-8            | -40°C to 125°C    |

| LTC6227IMS8E#PBF  | LTC6227IMS8E#TRPBF | LTHHB        | 8-Lead MSOP, Exposed Pad | -40°C to 85°C     |

| LTC6227HMS8E#PBF  | LTC6227HMS8E#TRPBF | LTHHB        | 8-Lead MSOP, Exposed Pad | -40°C to 125°C    |

| LTC6227IDD#PBF    | LTC6227IDD#TRPBF   | LHHC         | 10-Lead 3mm × 3mm DFN    | -40°C to 85°C     |

| LTC6227HDD#PBF    | LTC6227HDD#TRPBF   | LHHC         | 10-Lead 3mm × 3mm DFN    | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS (V**<sub>S</sub> = ±5V) The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 5V$ , $V_{CM} = 0V$ , $V_{SHDN} =$ floating unless otherwise noted.

| SYMBOL            | PARAMETER                                                          | CONDITIONS                                                   |   | MIN                  | ТҮР      | MAX         | UNITS             |

|-------------------|--------------------------------------------------------------------|--------------------------------------------------------------|---|----------------------|----------|-------------|-------------------|

| V <sub>OS</sub>   | Input Offset Voltage                                               |                                                              | • | -95<br>-225          | 20       | 95<br>225   | μV<br>μV          |

| $\Delta V_{0S}$   | Input Offset Voltage Match (Channel to Channel, LTC6227, Note 5)   |                                                              | • | -140<br>-400         | 18       | 140<br>400  | μV<br>μV          |

| T <sub>CVOS</sub> | Input Offset Voltage Drift                                         |                                                              | ٠ |                      | 0.4      |             | µV/°C             |

| I <sub>B</sub>    | Input Bias Current (Note 6)                                        |                                                              | • | -20<br>-25           | -8.4     |             | μΑ<br>μΑ          |

| $\Delta I_B$      | Input Bias Current Match<br>(Channel to Channel,LTC6227, Note 5)   |                                                              | • | -2<br>-3             | 0.3      | 2<br>3      | μA<br>μA          |

| I <sub>OS</sub>   | Input Offset Current                                               |                                                              | • | -0.35<br>-0.5        | 0.2      | 0.35<br>0.5 | μA<br>μA          |

| ΔI <sub>OS</sub>  | Input OffsetCurrent Match<br>(Channel to Channel, LTC6227, Note 5) |                                                              | • | -0.7<br>-1           | 0.15     | 0.7<br>1    | μA<br>μA          |

| e <sub>n</sub>    | Input Noise Voltage Spectral Density                               | f = 1MHz                                                     |   |                      | 1        |             | nV/√Hz            |

|                   | Integrated 1/f Noise                                               | 0.1Hz to 10Hz                                                |   |                      | 0.77     |             | μV <sub>P-P</sub> |

| i <sub>n</sub>    | Input Noise Current Spectral Density                               | f = 1MHz                                                     |   |                      | 2.4      |             | pA/√Hz            |

| C <sub>IN</sub>   | Input Capacitance                                                  | Differential Mode<br>Common Mode                             |   |                      | 3<br>1   |             | pF<br>pF          |

| R <sub>IN</sub>   | Input Resistance                                                   | Differential Mode<br>Common Mode                             |   |                      | 4.7<br>6 |             | kΩ<br>MΩ          |

| A <sub>VOL</sub>  | Large Signal Voltage Gain                                          | $R_L = 1k\Omega$ to Half Supply $V_{OUT} = \pm 4V$           | • | 114<br>110           | 139      |             | dB<br>dB          |

|                   |                                                                    | $R_L$ = 100 $\Omega$ to Half Supply V <sub>OUT</sub> = ±2.5V | • | 93<br>88             | 110      |             | dB<br>dB          |

| CMRR              | Common Mode Rejection Ratio                                        | $V_{CM} = V^ 0.1V$ to $V^+ - 1.2V$                           | • | 100<br>95            | 114      |             | dB<br>dB          |

| V <sub>CMR</sub>  | Input Common Mode Range (Note 10)                                  |                                                              | • | V <sup>-</sup> - 0.1 |          | V+ – 1.2    | V                 |

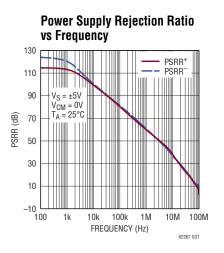

| PSRR+             | Positive Power Supply Rejection Ratio                              | V <sup>-</sup> = -1V, V <sup>+</sup> = 1.8V to 10.75V        | • | 100<br>95            | 115      |             | dB<br>dB          |

# **ELECTRICAL CHARACTERISTICS** ( $V_S = \pm 5V$ ) The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 5V$ , $V_{CM} = 0V$ , $V_{SHDN} =$ floating unless otherwise noted.

| SYMBOL              | PARAMETER                                              | CONDITIONS                                               |   | MIN        | ТҮР  | MAX                   | UNITS      |

|---------------------|--------------------------------------------------------|----------------------------------------------------------|---|------------|------|-----------------------|------------|

| PSRR <sup>-</sup>   | Negative Power Supply Rejection Ratio                  | V <sup>+</sup> = 1.5V, V <sup>-</sup> = -1.3V to -10.25V | • | 103<br>108 | 127  |                       | dB<br>dB   |

|                     | Supply Voltage Range $(V^+ - V^-)$ (Note 7)            |                                                          | • | 2.8        |      | 11.75                 | V          |

| V <sub>OL</sub>     | Output Swing Low (V <sub>OUT</sub> – V <sub>EE</sub> ) | No Load                                                  | • |            | 19   | 21<br>26              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |            | 100  | 45<br>120             | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 25mA                                 | • |            | 330  | 427<br>670            | mV<br>mV   |

| V <sub>OH</sub>     | Output Swing High ( $V_{CC} - V_{OUT}$ )               | No Load                                                  | • |            | 14   | 20<br>26              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |            | 140  | 180<br>200            | mV<br>mV   |

|                     |                                                        | I <sub>SOURCE</sub> = 25mA                               | • |            | 600  | 1000<br>1370          | mV<br>mV   |

| I <sub>SC</sub>     | Output Short-Circuit Current                           | Sourcing                                                 | • |            | -64  | -42<br>-35            | mA<br>mA   |

|                     |                                                        | Sinking                                                  | • | 45<br>32   | 60   |                       | mA<br>mA   |

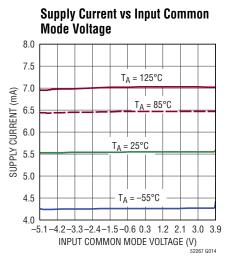

| I <sub>S</sub>      | Supply Current per Channel                             |                                                          | • |            | 5.5  | 5.8<br>7.4            | mA<br>mA   |

| I <sub>SD</sub>     | Disable Supply Current Per Channel, Amplifier<br>Off   | $V_{\overline{SHDN}} = V^+ - 2.75V$                      | • |            | 350  | 450<br>520            | μA<br>μA   |

| VL_SHDN             | SHDN Pin Input Voltage Low, Disable Amplifier          |                                                          | • |            |      | V <sup>+</sup> – 2.75 | V          |

| V <sub>H_SHDN</sub> | SHDN Pin Input Voltage High, Enable Amplifier          |                                                          | • | V+ – 1.6   |      |                       | V          |

| IL_SHDN             | SHDN Pin Input Current, Disable Amplifier              | V <sub>SHDN</sub> = V <sup>+</sup> - 2.75V               | • | -10        | -2.5 | 10                    | μA         |

| I <sub>H_SHDN</sub> | SHDN Pin Input Current, Enable Amplifier               | V <sub>SHDN</sub> = V <sup>+</sup> - 1.6V                | • | -10        | -0.3 | 10                    | μA         |

| I <sub>OSD</sub>    | Output Leakage Current in Shutdown                     |                                                          |   |            | 100  |                       | nA         |

| BW                  | –3dB Closed Loop Bandwidth                             | $A_V = 1$ , $R_L = 1k\Omega$ to Half Supply              |   |            | 330  |                       | MHz        |

| GBW                 | Gain-Bandwidth Product                                 | f = 5MHz, $R_L = 1k\Omega$ to Half Supply                | • | 350<br>300 | 420  |                       | MHz<br>MHz |

| t <sub>ON</sub>     | Turn-On Time                                           | $V_{\overline{SHDN}} = V^+ - 2.75V$ to $V^+ - 1.6V$      |   |            | 2100 |                       | ns         |

| t <sub>OFF</sub>    | Turn-Off Time                                          | $V_{\overline{SHDN}} = V^+ - 1.6V$ to $V^+ - 2.75V$      |   |            | 800  |                       | ns         |

| t <sub>S_0.1</sub>  | Settling Time to 0.1%                                  | $A_V$ = 1, 2V Output Step, $R_L$ = 1k $\Omega$           |   |            | 58   |                       | ns         |

|                     |                                                        | $A_V = 1, 4V$ Output Step, $R_L = 1k\Omega$              |   |            | 61   |                       | ns         |

| t <sub>S_0.01</sub> | Settling Time to 0.01%                                 | $A_V = 1, 6V$ Output Step, $R_L = 1k\Omega$              |   |            | 150  |                       | ns         |

## **ELECTRICAL CHARACTERISTICS** ( $V_S = \pm 5V$ ) full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 5V$ , $V_{CM} = 0V$ , $V_{SHDN} =$ floating unless otherwise noted.

| SYMBOL  | PARAMETER                                                           | CONDITIONS                                                                                                                                                                                                                |   | MIN       | ТҮР                                                    | MAX | UNITS                                  |

|---------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|--------------------------------------------------------|-----|----------------------------------------|

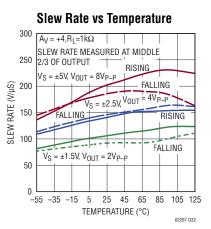

| SR      | Slew Rate                                                           | A <sub>V</sub> = +4, 8V Output Step (Note 9)                                                                                                                                                                              | • | 115<br>90 | 180                                                    |     | V/μS<br>V/μS                           |

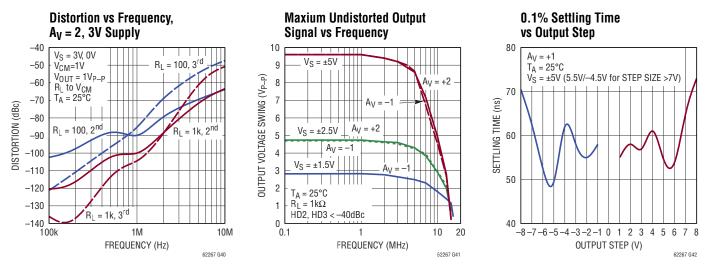

| FPBW    | Full Power Bandwidth                                                | $V_{OUT} = 8V_{P-P}, A_V = +2, THD < -40dBc$                                                                                                                                                                              |   |           | 5.5                                                    |     | MHz                                    |

| HD2/HD3 | Harmonic Distortion, $R_L$ = 1k $\Omega$ to Half Supply, $A_V$ = +1 |                                                                                                                                                                                                                           |   |           | -128/-136<br>-99/-91<br>-104/-95<br>-89/-79<br>-91/-80 |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc<br>dBc |

|         | Harmonic Distortion, $R_L = 100\Omega$ to Half Supply, $A_V = +1$   | $ \begin{array}{l} f_{C} = 100 kHz, \ V_{0} = 4 V_{P-P} \\ f_{C} = 1MHz, \ V_{0} = 4 V_{P-P} \\ f_{C} = 1MHz, \ V_{0} = 2 V_{P-P} \\ f_{C} = 2MHz, \ V_{0} = 4 V_{P-P} \\ f_{C} = 2MHz, \ V_{0} = 2 V_{P-P} \end{array} $ |   |           | -111/-123<br>-93/-77<br>-96/-80<br>-89/-70<br>-90/-70  |     | dBc<br>dBc<br>dBc<br>dBc<br>dBc<br>dBc |

| ΔG      | Differential Gain                                                   | $\begin{array}{l} A_V = 2,  R_L = 150\Omega \\ A_V = +1,  R_L = 1 k\Omega \end{array}$                                                                                                                                    |   |           | 0.4<br>0.08                                            |     | %<br>%                                 |

| Δθ      | Differential Phase                                                  |                                                                                                                                                                                                                           |   |           | 0.025<br>0.13                                          |     | Deg<br>Deg                             |

**ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = 5V, OV)** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_S = 5V$ , 0V,  $V_{CM} = V_{OUT} = 2.5V$ ,  $V_{SHDN} =$  floating unless otherwise noted.

| SYMBOL            | PARAMETER                                                           | CONDITIONS                                                          |   | MIN           | ТҮР      | MAX         | UNITS             |

|-------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---|---------------|----------|-------------|-------------------|

| V <sub>OS</sub>   | Input Offset Voltage                                                |                                                                     | • | -100<br>-235  | 20       | 100<br>235  | μV<br>μV          |

| $\Delta V_{OS}$   | Input Offset Voltage Match<br>(Channel to Channel, LTC6227, Note 5) |                                                                     | • | -140<br>-400  | 18       | 140<br>400  | μV<br>μV          |

| T <sub>CVOS</sub> | Input Offset Voltage Drift                                          |                                                                     | • |               | 0.4      |             | μV/°C             |

| IB                | Input Bias Current (Note 5)                                         |                                                                     | • | -20<br>-25    | -8.4     |             | μA<br>μA          |

| ΔI <sub>B</sub>   | Input Bias Current Match<br>(Channel to Channel, LTC6227, Note 5)   |                                                                     | • | -2<br>-3      | 0.3      | 2<br>3      | μA<br>μA          |

| l <sub>os</sub>   | Input Offset Current                                                |                                                                     |   | -0.35<br>-0.5 | 0.2      | 0.35<br>0.5 | μA<br>μA          |

| ΔI <sub>OS</sub>  | Input Offset Current Match<br>(Channel to Channel, LTC6227, Note 5) |                                                                     | • | -0.7<br>-1    | 0.15     | 0.7<br>1    | μΑ<br>μΑ          |

| e <sub>n</sub>    | Input Noise Voltage Spectral Density                                | f = 1MHz                                                            |   |               | 1        |             | nV/√Hz            |

|                   | Integrated 1/f Noise                                                | 0.1Hz to 10Hz                                                       |   |               | 0.77     |             | μV <sub>P-P</sub> |

| in                | Input Noise Current Spectral Density                                | f = 1MHz                                                            |   |               | 2.4      |             | pA/√Hz            |

| C <sub>IN</sub>   | Input Capacitance                                                   | Differential Mode<br>Common Mode                                    |   |               | 3<br>1   |             | pF<br>pF          |

| R <sub>IN</sub>   | Input Resistance                                                    | Differential Mode<br>Common Mode                                    |   |               | 4.7<br>6 |             | kΩ<br>MΩ          |

| A <sub>VOL</sub>  | Large Signal Voltage Gain                                           | $R_L = 1k\Omega$ to Half Supply<br>V <sub>OUT</sub> = 0.5V to 4.5V  | • | 114<br>110    | 135      |             | dB<br>dB          |

|                   |                                                                     | $R_L = 100\Omega$ to Half Supply<br>V <sub>OUT</sub> = 0.9V to 4.1V | • | 105<br>93     | 120      |             | dB<br>dB          |

| CMRR              | Common Mode Rejection Ratio                                         | $V_{CM} = V^ 0.1V$ to $V^+ - 1.2V$                                  |   | 99<br>95      | 114      |             | dB<br>dB          |

**ELECTRICAL CHARACTERISTICS** ( $V_S = 5V$ , OV) The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_S = 5V$ , 0V,  $V_{CM} = V_{OUT} = 2.5V$ ,  $V_{SHDN} =$  floating unless otherwise noted.

| SYMBOL              | PARAMETER                                              | CONDITIONS                                               |   | MIN                  | ТҮР  | MAX                   | UNITS      |

|---------------------|--------------------------------------------------------|----------------------------------------------------------|---|----------------------|------|-----------------------|------------|

| V <sub>CMR</sub>    | Input Common Mode Range (Note 10)                      |                                                          |   | V <sup>-</sup> -0.1  |      | V <sup>+</sup> – 1.2  | V          |

| PSRR+               | Positive Power Supply Rejection Ratio                  | V <sup>-</sup> = -1V, V <sup>+</sup> = 1.8V to 10.75V    | • | 100<br>95            | 115  |                       | dB<br>dB   |

| PSRR <sup>-</sup>   | Negative Power Supply Rejection Ratio                  | V <sup>+</sup> = 1.5V, V <sup>-</sup> = -1.3V to -10.25V | • | 103<br>100           | 127  |                       | dB<br>dB   |

|                     | Supply Voltage Range ( $V^+ - V^-$ ) (Note 7)          |                                                          |   | 2.8                  |      | 11.75                 | V          |

| V <sub>OL</sub>     | Output Swing Low (V <sub>OUT</sub> – V <sub>EE</sub> ) | No Load                                                  | • |                      | 16   | 21<br>23              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |                      | 90   | 110<br>155            | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 15mA                                 | • |                      | 220  | 270<br>370            | mV<br>mV   |

| V <sub>OH</sub>     | Output Swing High ( $V_{CC} - V_{OUT}$ )               | No Load                                                  | • |                      | 11   | 15<br>20              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |                      | 150  | 180<br>200            | mV<br>mV   |

|                     |                                                        | I <sub>SOURCE</sub> = 15mA                               | • |                      | 331  | 500<br>650            | mV<br>mV   |

| I <sub>SC</sub>     | Output Short-Circuit Current                           | Sourcing                                                 | • |                      | -52  | -34<br>-30            | mA<br>mA   |

|                     |                                                        | Sinking                                                  | • | 42<br>30             | 57   |                       | mA<br>mA   |

| I <sub>S</sub>      | Supply Current per Channel                             |                                                          | • |                      | 5.8  | 6.3<br>7.6            | mA<br>mA   |

| I <sub>SD</sub>     | Disable Supply Current Per Amplifier, Amplifier<br>Off | V <sub>SHDN</sub> = V <sup>+</sup> - 2.65V               | • |                      | 245  | 310<br>330            | μΑ<br>μΑ   |

| $V_{L}SHDN}$        | SHDN Pin Input Voltage Low, Disable Amplifier          |                                                          | • |                      |      | V <sup>+</sup> – 2.65 | V          |

| V <sub>H_SHDN</sub> | SHDN Pin Input Voltage High, Enable Amplifier          |                                                          | • | V <sup>+</sup> – 1.6 |      |                       | V          |

| IL_SHDN             | SHDN Pin Input Current, Disable Amplifier              | $V_{\overline{SHDN}} = V^+ - 2.65V$                      | • | -10                  | -2.9 | 10                    | μA         |

| I <sub>H_SHDN</sub> | SHDN Pin Input Current, Enable Amplifier               | $V_{\overline{SHDN}} = V^+ - 1.6V$                       | • | -10                  | -0.3 | 10                    | μA         |

| I <sub>OSD</sub>    | Output Leakage Current in Shutdown                     |                                                          |   |                      | 100  |                       | nA         |

| BW                  | –3dB Closed Loop Bandwidth                             | $A_V = 1$ , $R_L = 1k\Omega$ to Half Supply              |   |                      | 490  |                       | MHz        |

| GBW                 | Gain-Bandwidth Product                                 | f = 5MHz, $R_L$ = 1k $\Omega$ to Half Supply             | • | 350<br>290           | 430  |                       | MHz<br>MHz |

| t <sub>ON</sub>     | Turn-On Time                                           | $V_{\overline{SHDN}} = V^{+} - 2.65V$ to $V^{+} - 1.6V$  |   |                      | 2100 |                       | ns         |

| t <sub>OFF</sub>    | Turn-Off Time                                          | $V_{SHDN} = V^+ - 1.6V$ to $V^+ - 2.65V$                 |   |                      | 800  |                       | ns         |

| t <sub>S_0.1</sub>  | Settling Time to 0.1%                                  | $A_V = 1$ , 2V Output Step, $R_L = 1k\Omega$             |   |                      | 59   |                       | ns         |

**ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = 5V, OV)** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_S = 5V$ , 0V,  $V_{CM} = V_{OUT} = 2.5V$ ,  $V_{SHDN} =$  floating unless otherwise noted.

| SYMBOL     | PARAMETER                                             | CONDITIONS                                                                                                                                                             | MIN TYP MAX                       | UNITS             |

|------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|

| SR         | Slew Rate                                             | A <sub>V</sub> = +4, 4V Output Step (Note 9)                                                                                                                           | 140                               | V/µS              |

| FPBW       | Full Power Bandwidth                                  | $V_{OUT} = 4V_{P-P}, A_V = +2, THD < -40dBc$                                                                                                                           | 6                                 | MHz               |

| HD2/HD3    | Harmonic Distortion, $R_L = 1k\Omega$ to Half Supply  |                                                                                                                                                                        | -125/-135<br>-104/-106<br>-90/-90 | dBc<br>dBc<br>dBc |

|            | Harmonic Distortion, $R_L = 100\Omega$ to Half Supply | $ \begin{array}{l} f_{C} = 100 \text{kHz}, \ V_{0} = 2 V_{P-P} \\ f_{C} = 1 \text{MHz}, \ V_{0} = 2 V_{P-P} \\ f_{C} = 2 \text{MHz}, \ V_{0} = 2 V_{P-P} \end{array} $ | -112/-128<br>-96/-88<br>-88/-74   | dBc<br>dBc<br>dBc |

| $\Delta G$ | Differential Gain                                     | $\begin{array}{c} A_V = 2,  R_L = 150\Omega \\ A_V = +1,  R_L = 1k\Omega \end{array}$                                                                                  | 0.17<br>0.09                      | %<br>%            |

| Δθ         | Differential Phase                                    | $\begin{array}{l} A_V = 2,  R_L = 150\Omega \\ A_V = +1,  R_L = 1 k\Omega \end{array}$                                                                                 | 0.3<br>0.04                       | Deg<br>Deg        |

# **ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = 3V, OV)** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_S = 3V$ , $OV, V_{CM} = 1.5V$ , $V_{SHDN} =$ floating unless otherwise noted.

| SYMBOL            | PARAMETER                                                           | CONDITIONS                                                                    |   | MIN                 | ТҮР      | MAX         | UNITS             |

|-------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|---|---------------------|----------|-------------|-------------------|

| V <sub>0S</sub>   | Input Offset Voltage                                                |                                                                               | • | -110<br>-250        | 24       | 110<br>250  | μV<br>μV          |

| $\Delta V_{0S}$   | Input Offset Voltage Match<br>(Channel to Channel, LTC6227, Note 5) |                                                                               | • | -140<br>-400        | 18       | 140<br>400  | μV<br>μV          |

| T <sub>CVOS</sub> | Input Offset Voltage Drift                                          |                                                                               | • |                     | 0.4      |             | μV/°C             |

| I <sub>B</sub>    | Input Bias Current (Note 6)                                         | Bias Cancellation Disabled                                                    | • | -20<br>-26          | -8.4     |             | μA<br>μA          |

| $\Delta I_B$      | Input Bias Current Match<br>(Channel to Channel, LTC6227, Note 5)   |                                                                               | • | -2<br>-3            | 0.3      | 2<br>3      | μA<br>μA          |

| I <sub>OS</sub>   | Input Offset Current                                                |                                                                               | • | -0.35<br>-0.5       | 0.2      | 0.35<br>0.5 | μA<br>μA          |

| $\Delta I_{0S}$   | Input Offset Current Match<br>(Channel to Channel,LTC6227, Note 5)  |                                                                               | • | -0.7<br>-1          | 0.15     | 0.7<br>1    | μA<br>μA          |

| e <sub>n</sub>    | Input Noise Voltage Spectral Density                                | f = 1MHz                                                                      |   |                     | 1        |             | nV/√Hz            |

|                   | Integrated 1/f Noise                                                | 0.1Hz to 10Hz                                                                 |   |                     | 0.77     |             | μV <sub>P-P</sub> |

| i <sub>n</sub>    | Input Current Noise Spectral Density                                | f = 1MHz                                                                      |   |                     | 2.4      |             | pA/√Hz            |

| C <sub>IN</sub>   | Input Capacitance                                                   | Differential Mode<br>Common Mode                                              |   |                     | 3<br>1   |             | pF<br>pF          |

| R <sub>IN</sub>   | Input Resistance                                                    | Differential Mode<br>Common Mode                                              |   |                     | 4.7<br>6 |             | kΩ<br>MΩ          |

| A <sub>VOL</sub>  | Large Signal Voltage Gain                                           | $R_L = 1k\Omega$ to Half Supply,<br>(V <sub>OUT</sub> = V <sub>CM</sub> ±1V)  | • | 114<br>100          | 135      |             | dB<br>dB          |

|                   |                                                                     | $R_L = 100\Omega$ to Half Supply,<br>(V <sub>OUT</sub> = V <sub>CM</sub> ±1V) |   |                     | 114      |             | dB                |

| CMRR              | Common Mode Rejection Ratio                                         | $V_{CM} = V^ 0.1V$ to $V^+ - 1.2V$                                            | • | 98<br>90            | 114      |             | dB<br>dB          |

| V <sub>CMR</sub>  | Input Common Mode Range (Note 10)                                   |                                                                               | • | V <sup>-</sup> -0.1 |          | V+ – 1.2    | V                 |

| PSRR+             | Positive Power Supply Rejection Ratio                               | V <sup>−</sup> = −1V, V <sup>+</sup> = 1.8V to 10.75V                         | • | 100<br>95           | 115      |             | dB<br>dB          |

**ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = 3V, OV)** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_S = 3V$ ,  $OV, V_{CM} = 1.5V$ ,  $V_{SHDN} =$  floating unless otherwise noted.

| SYMBOL              | PARAMETER                                              | CONDITIONS                                               |   | MIN                  | ТҮР  | MAX                   | UNITS      |

|---------------------|--------------------------------------------------------|----------------------------------------------------------|---|----------------------|------|-----------------------|------------|

| PSRR <sup>-</sup>   | Negative Power Supply Rejection Ratio                  | V <sup>+</sup> = 1.5V, V <sup>-</sup> = -1.3V to -10.25V | • | 103<br>100           | 127  |                       | dB<br>dB   |

|                     | Supply Voltage Range $(V^+ - V^-)$ (Note 7)            |                                                          | • | 2.8                  |      | 11.75                 | V          |

| V <sub>OL</sub>     | Output Swing Low (V <sub>OUT</sub> – V <sub>EE</sub> ) | No Load                                                  | • |                      | 12   | 14<br>18              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |                      | 91   | 121<br>160            | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 10mA                                 | • |                      | 161  | 205<br>275            | mV<br>mV   |

| V <sub>OH</sub>     | Output Swing High ( $V_{CC} - V_{OUT}$ )               | No Load                                                  | • |                      | 10   | 14<br>18              | mV<br>mV   |

|                     |                                                        | I <sub>SINK</sub> = 5mA                                  | • |                      | 150  | 180<br>230            | mV<br>mV   |

|                     |                                                        | I <sub>SOURCE</sub> = 10mA                               | • |                      | 250  | 330<br>430            | mV<br>mV   |

| I <sub>SC</sub>     | Output Short Circuit Current                           | Sourcing                                                 |   |                      | 47   |                       | mA         |

|                     |                                                        | Sinking                                                  |   |                      | 57   |                       | mA         |

| I <sub>S</sub>      | Supply Current/Channel                                 |                                                          | • |                      | 5.5  | 6<br>7.25             | mA<br>mA   |

| I <sub>SD</sub>     | Disable Supply Current, Amplifier Off                  | V <sub>SHDN</sub> = V <sup>+</sup> - 2.65V               | • |                      | 195  | 247<br>278            | μΑ<br>μΑ   |

| V <sub>L_SHDN</sub> | SHDN Pin Input Voltage Low, Disable Amplifier          |                                                          |   |                      |      | V <sup>+</sup> – 2.65 | V          |

| V <sub>H_SHDN</sub> | SHDN Pin Input Voltage High, Enable Amplifier          |                                                          |   | V <sup>+</sup> – 1.6 |      |                       | V          |

| IL_SHDN             | SHDN Pin Input Current, Disable Amplifier              | $V_{\overline{SHDN}} = V^+ - 2.65V$                      | • | -10                  | -2.9 | 10                    | μA         |

| I <sub>H_SHDN</sub> | SHDN Pin Input Current, Enable Amplifier               | $V_{\overline{SHDN}} = V^+ - 1.6V$                       | • | -10                  | 0.3  | 10                    | μA         |

| I <sub>OSD</sub>    | Output Leakage Current in Shutdown                     |                                                          |   |                      | 100  |                       | nA         |

| BW                  | –3dB Closed Loop Bandwidth                             | $A_V = 1$ , $R_L = 1k\Omega$ to Half Supply              |   |                      | 450  |                       | MHz        |

| GBW                 | Gain-Bandwidth Product                                 | f = 5MHz, $R_L = 1k\Omega$ to Half Supply                | • | 340<br>280           | 415  |                       | MHz<br>MHz |

| t <sub>ON</sub>     | Turn-On Time                                           | $V_{\overline{SHDN}} = V^+ - 2.65V$ to $V^+ - 1.6V$      |   |                      | 2100 |                       | ns         |

| t <sub>OFF</sub>    | Turn-Off Time                                          | $V_{\overline{SHDN}} = V^+ - 1.6V$ to $V^+ - 2.65V$      |   |                      | 800  |                       | ns         |

| t <sub>S_0.1</sub>  | Settling Time to 0.1%                                  |                                                          |   |                      | 84   |                       | ns         |

| SR                  | Slew Rate (Note 9)                                     | A <sub>V</sub> = +4, 2V Output Step                      |   |                      | 100  |                       | V/µS       |

| FPBW                | Full Power Bandwidth                                   | $V_{OUT} = 2V_{P-P}, A_V = -1, THD < -40dBc$             |   |                      | 8    |                       | MHz        |

## **ELECTRICAL CHARACTERISTICS (V<sub>S</sub> = 3V, OV)** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_S = 3V$ , $OV, V_{CM} = 1.5V$ , $V_{SHDN} =$ floating unless

over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = 3V, 0V,V<sub>CM</sub> = 1.5V, V<sub>SHDN</sub> = floating unless otherwise noted.

| SYMBOL  | PARAMETER                                                                                 | CONDITIONS                                                                                              | MIN TYP MAX                       | UNITS             |

|---------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|

| HD2/HD3 | Harmonic Distortion, $R_L = 1k\Omega$ to $V_{CM}$ , $V_{OUT} = 1V_{P-P}$ , $V_{CM} = 1V$  | $f_{C} = 100 \text{kHz}$<br>$f_{C} = 1 \text{MHz}$<br>$f_{C} = 2 \text{MHz}$                            | -122/-137<br>-108/-111<br>-95/-95 | dBc<br>dBc<br>dBc |

| _       | Harmonic Distortion, $R_L = 100\Omega$ to $V_{CM}$ , $V_{OUT} = 1V_{P-P}$ , $V_{CM} = 1V$ | $ \begin{array}{l} f_{C} = 100 \text{kHz} \\ f_{C} = 1 \text{MHz} \\ f_{C} = 2 \text{MHz} \end{array} $ | -113/-130<br>-100/-94<br>-90/-79  | dBc<br>dBc<br>dBc |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The inputs are protected by back-to-back diodes. If any of the input or shutdown pins goes 300mV beyond either supply or the differential input voltage exceeds 0.7V, the input current should be limited to less than 10mA.

**Note 3:** A heat sink may be required to keep the junction temperature below the absolute maximum rating when the output current is high.

**Note 4:** The LTC6226I/LTC6227I are guaranteed functional and specified over the temperature range of  $-40^{\circ}$ C to 85°C. The LTC6226H/LTC6227H are guaranteed and specified functional over the temperature range of  $-40^{\circ}$ C to 125°C.

**Note 5:** Matching parameters are the difference between amplifiers A and B on the LTC6227.

**Note 6:** The input bias current is the average of the average of the currents through the positive and negative input pins.

**Note 7:** Supply Voltage Range is guaranteed by Power Supply Rejection Ratio test.

**Note 8:** Thermal resistance varies with the amount of PC board metal connected to the package. The specified values are with short traces connected to the leads.

**Note 9:** Middle 2/3 of the output waveform is observed for Slew Rate.  $R_L = 1k$  to half supply.

**Note 10:** Input Common Mode Range is guaranteed by Common Mode Rejection Ratio Test.

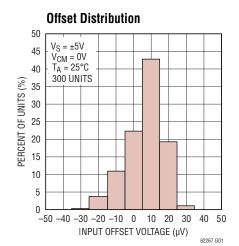

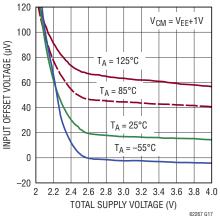

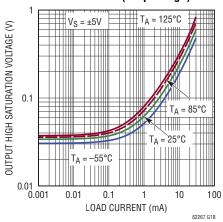

### **TYPICAL PERFORMANCE CHARACTERISTICS** $V_{S} = \pm 5V$ , $V_{CM} = 0V$ , $R_{L} = 1k\Omega$ to Half Supply,

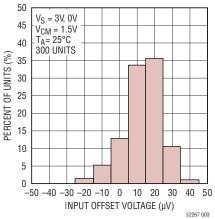

**Offset Distribution**

PERCENT OF UNITS (%)

25

20

15

10

5

0

$T_A = 25^{\circ}C$ , unless otherwise noted.

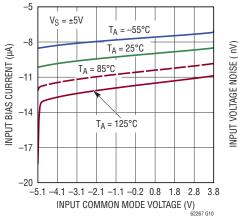

#### 50 45 V<sub>S</sub> = 5V, 0V V<sub>CM</sub> = 2.5V 40 T<sub>A</sub> = 25°C 300 UNITS 30

-50 -40 -30 -20 -10 0 10 20

INPUT OFFSET VOLTAGE (µV)

30 40

50

62267 G02

#### Offset Distribution

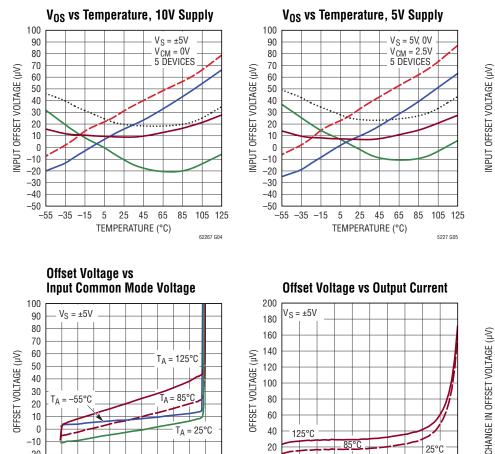

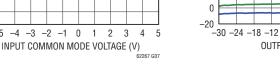

### TYPICAL PERFORMANCE CHARACTERISTICS $V_{S} = \pm 5V$ , $V_{CM} = 0V$ , $R_{L} = 1k\Omega$ to Half Supply,

$T_A = 25^{\circ}C$ , unless otherwise noted.

**Input Bias Current vs** Input Common Mode Voltage

0

-4 -3 -2 -1

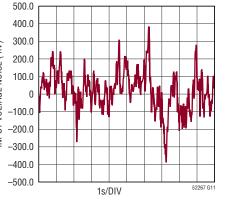

0.1Hz to 10Hz Voltage Noise

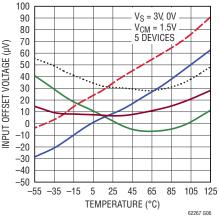

V<sub>OS</sub> vs Temperature, 3V Supply

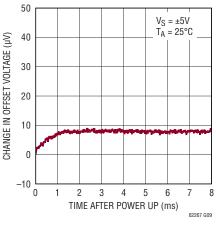

Warm Up Drift vs Time

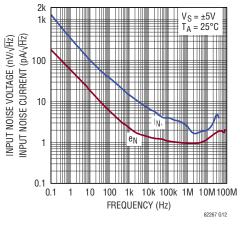

**Input Noise Voltage and Noise Current Spectral Densities** vs Frequency

Rev 0

-20

-30 -40

-6 -5

### TYPICAL PERFORMANCE CHARACTERISTICS $V_{S} = \pm 5V$ , $V_{CM} = 0V$ , $R_{L} = 1k\Omega$ to Half Supply,

$T_A = 25^{\circ}C$ , unless otherwise noted.

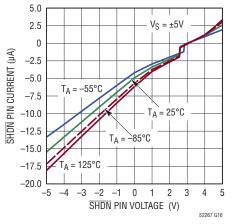

**SHDN** Pin Current vs SHDN Pin Voltage

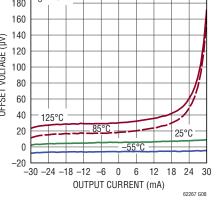

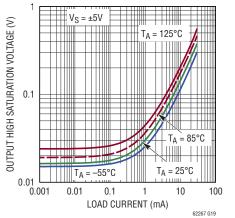

**Output Saturation Voltage** vs Load Current (Output Low)

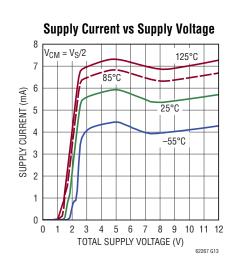

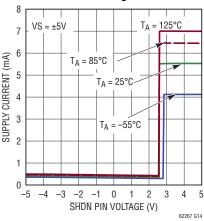

**Supply Current** vs SHDN Pin Voltage

Minimum Supply Voltage

**Output Saturation Voltage** vs Load Current (Output High)

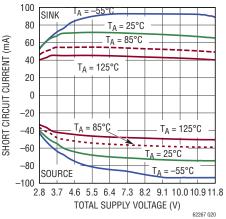

**Output Short Circuit Current** vs Supply Voltage

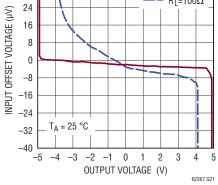

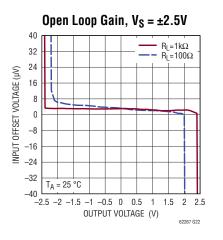

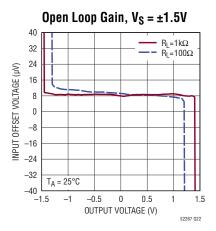

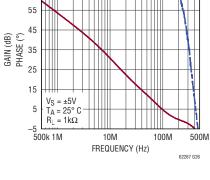

Open Loop Gain,  $V_S = \pm 5V$ 40  $R_L=1k\Omega$ 32  $R_{L} = 100\Omega$

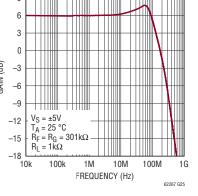

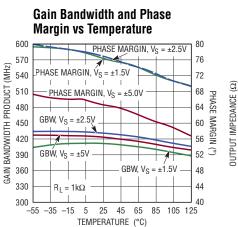

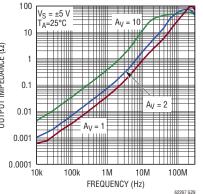

# **TYPICAL PERFORMANCE CHARACTERISTICS** $V_S = \pm 5V$ , $V_{CM} = 0V$ , $R_L = 1k\Omega$ to Half Supply, $T_A = 25^{\circ}C$ , unless otherwise noted.

Gain vs Frequency A<sub>V</sub> = 2 9 6 3 0 GAIN (dB) -3 -6 -9  $V_S = \pm 5V$ -12  $T_A = 25 \degree C$  $R_F = R_G = 3$ 301kΩ -15  $\dot{R_L} = 1 k\Omega$ -18 100k 10k 1M 10M 100M 1G

vs Frequency 75 GAIN 65 PHASE 55 45

**Open Loop Gain and Phase**

Gain Bandwidth and Phase Margin vs Supply Voltage

62267 G28

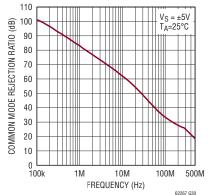

#### **Common Mode Rejection Ratio** vs Frequency

### TYPICAL PERFORMANCE CHARACTERISTICS $V_{S} = \pm 5V$ , $V_{CM} = 0V$ , $R_{L} = 1k\Omega$ to Half Supply,

$T_A = 25^{\circ}C$ , unless otherwise noted.

Overshoot vs Capacitive Load ( $A_V = +2$ ) 75  $R_S = 10\Omega C_F = 0$  $V_S = \pm 5V$  $R_S = 20\Omega C_F = 0$  $\begin{array}{l} \mathsf{R}_{S} = 50 \Omega \ \mathsf{C}_{\mathsf{F}} = 0 \\ \mathsf{R}_{S} = 10 \Omega \ \mathsf{C}_{\mathsf{F}} = 2.7 \text{pF} \end{array}$ 60  $R_S=20\Omega C_F = 2.7 pF$  $R_S = 50\Omega C_F = 2.7 pF$ OVERSHOOT (%) 45 30 15 0 10 100 1000 10000 CAPACITIVE LOAD (pF) 62267 G34

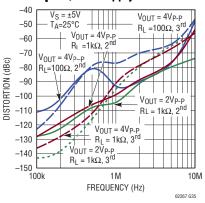

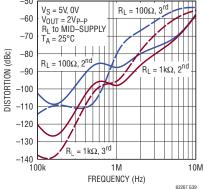

**Distortion vs Frequency**,  $A_V = 1$ , ±5V Supply

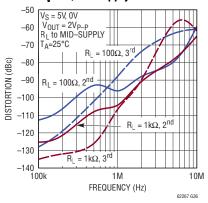

Distortion vs Frequency,  $A_V = 1$ , 5V Supply

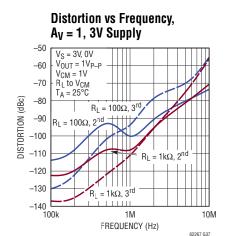

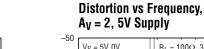

**Distortion vs Frequency**,  $A_V = 2, \pm 5V$  Supply -30  $V_{\rm S} = \pm 5V$ -40  $T_A = 25^{\circ}C$ -50  $V_{OUT} = 4V_{P-P}$  $R_{L} = 100\Omega, 3$ -60  $V_{OUT} = 4V_{P-P}$  $R_{L} = 100\Omega, 2^{nd}$ -70  $V_{OUT} = 4V_{P-P}$ -80  $R_L = 1k\Omega$ ,  $2^{nO}$ -90 V<sub>OUT</sub> = 2V<sub>P-P</sub>  $R_L = 1k\Omega, 2^{nd}$

$V_{OUT} = 2V_{P-P}$ R<sub>L</sub> = 1k $\Omega$ , 3<sup>rd</sup>

1 M

FREQUENCY (Hz)

$V_{OUT} = 4V_{P-P}$ R<sub>L</sub> = 1k $\Omega$ , 3<sup>rd</sup>

10M

82267 638

DISTORTION (dBc)

-100

-110

-120

-130

100k

Rev 0

### **TYPICAL PERFORMANCE CHARACTERISTICS** $V_{S} = \pm 5V$ , $V_{CM} = 0V$ , $R_{L} = 1k\Omega$ to Half Supply,

$T_A = 25^{\circ}C$ , unless otherwise noted.

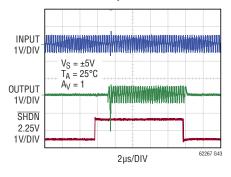

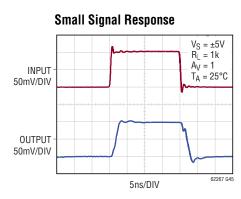

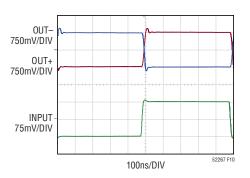

**SHDN** Pin Response Time

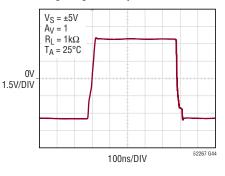

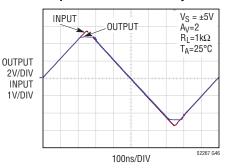

Large Signal Response

#### **Output Overdriven Recovery**

#### PIN FUNCTIONS

**FB (SOIC-8 Only):** Feedback Pin. Internally connected to OUT.

**+IN:** Non-Inverting Input of Amplifier. Valid input range is from  $V^-$  to  $V^+ - 1.2V$

–IN: Inverting Input of Amplifier. Valid input range is from  $V^-$  to  $V^+ - 1.2V$

**OUT:** Output of the Amplifier. Swings rail to rail and can typically source/sink 60mA of current.

**SHDN:** Shutdown Pin (Active Low). Referenced to V<sup>+</sup>. When taken 2.75V below V<sup>+</sup>, the amplifier shuts down and enters low power mode, with the outputs in a high impedance state. When left floating, the amplifier is on.

**V<sup>+</sup>:** Positive Supply to Amplifier. Valid range is from 2.8V to 11.75V when V<sup>-</sup> is 0V.

**V**<sup>-</sup>: Negative Supply to Amplifier. Typically 0V. This can be made a negative voltage as long as  $2.8V \le (V^+ - V^-) \le 11.75V$

### **APPLICATIONS INFORMATION**

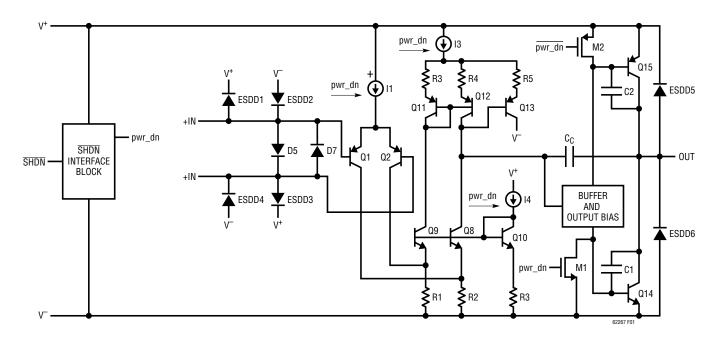

#### **Circuit Description**

The LTC6226/LTC6227 have an input signal range that extends from the negative power supply to 1.2V below the positive power supply. Figure 1 depicts a simplified schematic of the amplifier. The input stage consists of PNP transistors Q1 and Q2. Bootstrap transistor Q13 improves DC accuracy by reducing the offset contribution of the base currents of Q11 and Q12 since it has twice their collector current thus Q11/Q12 current matching becomes

independent of transistor  $\beta$ . The bootstrap arrangement also enhances gain by improving output impedance. A pair of complementary common emitter stages, Q15 and Q14, enables the output to swing to either rail. The SHDN Interface block translates the SHDN signal into pwr\_dn for powering down the device (by deactivating current sources I1 - I4) and putting the output in a high impedance state (by shorting the bases of Q15/Q14 to the supplies via M2 and M1).

### **APPLICATIONS INFORMATION**

#### Output

The LTC6226 family has excellent output drive capability. The amplifiers can typically deliver more than 50mA of output drive current at a total supply of 10V, and can typically swing to within 600mV of the rail for load currents as high as 25mA. As the supply voltage to the amplifier decreases, the output current capability also decreases. Attention must be paid to keep the junction temperature of the IC below 150°C (refer to power dissipation section) when the output is in continuous short-circuit. The output of the amplifier has reverse-biased diodes connected to each supply. If the output is forced beyond either supply, extremely high currents will flow through those diodes which can result in damage to the device. Forcing the output to even 1V beyond either supply could result in several hundred milliamps of current through either diode. Thus forcing the output beyond the supplies should be avoided.

#### **Input Protection**

The LTC6226/LTC6227 has a pair of back to back diodes (D5 and D7) to prevent the emitter base breakdown of the input transistors and limit the differential input to  $\pm 700$  mV. Unlike many other high performance amplifiers, the bases of the input pair transistors Q1 and Q2 are not connected to the pins using internal resistors to limit input current. since that would cause the noise to increase. For instance, a 100 $\Omega$  resistor in series with each input would generate 1.8 nV/ $\sqrt{Hz}$  of noise, and the total amplifier noise voltage would rise from  $1nV/\sqrt{Hz}$  to  $2.06nV/\sqrt{Hz}$ . Once the input differential voltage exceeds ±0.7V, current conducted though the protection diodes should be limited to  $\pm 10$  mA. This implies  $25\Omega$  of protection resistance per guarter volt (250 mV) of overdrive beyond  $\pm 0.7 \text{V}$ . In addition, the input and shutdown pins have reverse biased diodes connected to the supplies. The current in these diodes must be limited to less than 10mA. The amplifiers should not be used as comparators or in other open loop applications.

#### ESD

The LTC6226 family has reverse biased ESD protection diodes on all inputs as shown in Figure 1. There is an additional clamp between the positive and negative supplies that further protects the device during ESD strikes.

Hot plugging of the device into a powered socket must be avoided since this can trigger the clamp resulting in larger currents flowing between the supply pins.

#### **Capacitive Loads**

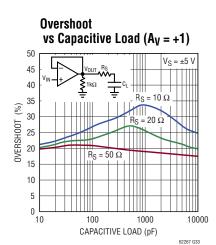

The LTC6226/LTC6227 are optimized for high bandwidth applications, and have not been designed to directly drive capacitive loads. Hence any trace capacitance at the output should be made as small as possible. Increased capacitance at the output creates an additional pole in the open loop frequency response, worsening the phase margin. When driving capacitive loads, a resistor of  $10\Omega$ to  $100\Omega$  should be connected between the amplifier output and the capacitive load to avoid ringing or oscillation. The feedback should be taken directly from the amplifier output. Higher voltage gain configurations tend to have better capacitive drive capability than lower gain configurations due to lower closed loop bandwidth and hence higher phase margin. The graphs titled Overshoot vs Capacitive Load demonstrate the transient response of the amplifier when driving capacitive loads with various series resistors.

### **APPLICATIONS INFORMATION**

#### **Feedback Components**

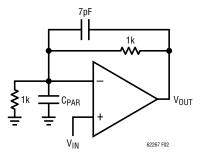

When feedback resistors are used to set up gain, care must be taken to ensure that the pole formed by the feedback resistors and the parasitic capacitance at the inverting input does not degrade stability. For example if the amplifier is set up in a gain of +2 configuration with gain and feedback resistors of 1k, a parasitic capacitance of 7pF (device + PC board) at the amplifier's inverting input will cause the part to oscillate, due to a pole formed at 45MHz. An additional capacitor of 7pF across the feedback resistor as shown in Figure 2 will eliminate any ringing or oscillation. In general, if the resistive feedback network results in a pole whose frequency lies within the closed loop bandwidth of the amplifier, a capacitor can be added in parallel with the feedback resistor to introduce a zero whose frequency is close to the frequency of the pole, improving stability. For high speed designs, minimizing parasitic inductance is important. The use of capacitors where the electrodes are terminated on the long side instead of the short side (for example the use of 0306 instead of 0603 components) can help in this regard.

Figure 2. 7pF Feedback Cancels Parasitic Pole

#### Shutdown

The LTC6226 and LTC6227DD have  $\overline{SHDN}$  pins that can shut down the amplifier to  $350\mu$ A typical supply current. The  $\overline{SHDN}$  pin needs to be taken 2.75V below the positive supply to shut down. When left floating, the  $\overline{SHDN}$ pin is internally pulled up to 1.2V below the positive supply and the amplifier remains on. During shutdown, the output transistors Q15 and Q14 in Figure 1 are in a high impedance state.

#### **Power Dissipation**

Care must be taken to ensure that the junction temperature of the die does not exceed 150°C.

The junction temperature,  $T_J$ , is calculated from the ambient temperature,  $T_A$ , power dissipation,  $P_D$ , and thermal resistance,  $\theta_{JA}$ :

$$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D} \bullet \theta_\mathsf{J}_\mathsf{A}).$$

The power dissipation in the IC is a function of the supply voltage, output voltage and load resistance. For symmetric supply voltages with output load connected to ground, the worst-case power dissipation  $P_{D(MAX)}$  occurs when the supply current is maximum and the output voltage at half of either supply voltage for a given load resistance.  $P_{D(MAX)}$  is approximately (since I<sub>S</sub> actually changes with output load current) given by:

$$P_{D(MAX)} = (2 \bullet V_{S} \bullet I_{S(MAX)}) + (V_{S}/2)^{2}/R_{L}$$

Example: For an LTC6227 in a 8-lead MS package operating on ±5V supplies and driving a 250 $\Omega$  load to ground, the worst-case power dissipation is approximately given by  $P_{D(MAX)}/Amp = (10 \cdot 7.4mA) + (5/2)^2/250 = 99mW$ . If both channels are loaded identically, the total power dissipation is 198mW.

At the Absolute Maximum ambient operating temperature, the junction temperature under these conditions will be:

$$T_J = T_A + (P_D \bullet \theta_{JA}) = 125 + 0.198 \bullet 35 = 132^{\circ}C$$

which is less than the absolute maximum junction temperature for the LTC6227.

Refer to the Pin Configuration section for thermal resistances of various packages

#### **Board Layout and Bypass Capacitors**

High speed and RF board layout techniques should be applied due to the very high speeds of the signals involved. For the LTC6226 SOIC-8 package option, the feedback should be taken from the FB pin rather than from the output pin, to reduce signal trace length.

Stray capacitances at the -IN and +IN pins should be made as low as possible to reduce stability degradation.

## **APPLICATIONS INFORMATION**

For single supply applications, it is recommended that high quality  $0.1\mu$ F||1000pF ceramic bypass capacitors be placed directly between each V<sup>+</sup> pin and its closest V<sup>-</sup> pin with short connections. The V<sup>-</sup> pins (including the Exposed Pad) should be tied directly to a low impedance ground plane with minimal routing. For dual (split) power supplies, it is recommended that additional high quality  $0.1\mu$ F||1000pF ceramic capacitors be used to bypass V<sup>+</sup> pins to ground and V<sup>-</sup> pins to ground, again with minimal routing.

#### **Noise Considerations**

The ultralow input referred voltage noise of of  $1nV/\sqrt{Hz}$  is equivalent to that of an  $60\Omega$  resistor. As with all BJT input amplifiers, lowering input referred noise is achieved by increasing the collector current of the input differential pair, which increases the input referred current noise.

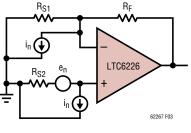

Figure 3 shows the LTC6226 in a typical gain configuration.

Figure 3.

As can be seen, the input referred noise spectral density of the gain stage  $(e_T)$  can be calculated by the following equations:

$$e_T^2 = e_n^2 + i_n^2 R_{EQ}^2 + 4kTR_{EQ}$$

Where

$R_{EQ} = R_{S2} + R_{S1} || R_F$ , k is the Boltzmann constant and T is the temperature (in Kelvin).

Op amp input referred noise dominates the input referred noise of the gain stage when

$R_{EQ} \ll e_n^2/4kT$

Resistor noise dominated the input referred noise of the gain stage when

$R_{EQ} >> e_n^2/4kT$  and  $R_{EQ} << 4kT/i_n^2$

Op amp input referred current noise dominates the input referred noise when

$R_{EQ} >> 4kT/i_n^2$

With an input referred voltage noise spectral density of 1nV/Hz and an input referred current noise of 2.4pA/Hz, it is easy to see that the gain stage's input referred noise is dominated by op amp voltage noise when  $R_{EQ} \ll 60\Omega$  and by resistor noise when

$60\Omega \ll R_{EQ} \ll 2.9 k\Omega$ .

Above an  $\mathsf{R}_{\mathsf{EQ}}$  of 2.9k $\Omega,$  input referred current noise dominates.

#### Distortion/Noise Trade-Off

As evident from the previous section, gain stage noise can be reduced by reducing  $R_{FQ}$ . However, reducing  $R_{FQ}$ has its disadvantages. In addition to increasing power dissipation in the presence of large output signals, the use of smaller resistors for a given gain results in increased distortion, because the internal nonlinearities of the op amp worsen with increasing load current. In addition, smaller resistors decrease op amp gain and hence can affect bandwidth. Hence when designing a system using the LTC6226/LTC6227, it is recommended that the resistor values be limited only by the system noise requirements with the caveat that the effect of the impedances' parasitic capacitances shouldn't affect the gain below the intended bandwidth. For example, for a feedback resistor of  $5k\Omega$ , a parasitic capacitor of 400fF will impact gain at frequencies above 79MHz.

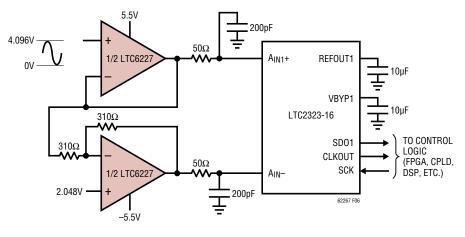

Figure 4. Transparent Driver for 16-Bit ADC

#### **16-Bit High Performance Transparent ADC Driver**

The ultralow noise and distortion performance of the LTC6226/LTC6227 makes it an excellent candidate for driving high sample rate high resolution ADCs. Figure 4 shows the LTC6227 driven by a differential input, driving an AD7380, a 4Msps, 16-bit ADC. Figure 5 shows the FFT obtained with a -0.5 dBFS, 50kHz input signal. Spurious free dynamic range is an excellent 108.5dB with an SNR of 91dB. Increasing the input frequency to 100kHz results in excellent performance as well, with a THD of -100dBc, SNR of 89dB and SFDR of 104.9dB.

16-Bit ADC Driver Performance

Figure 5. Measured Performance of LTC6227 Based Driver Driving the AD7380

62267 F05

## High Performance Single Ended to Differential 16-Bit ADC Driver

In many applications, the signal to be digitized is single ended, whereas the A/D Converter needs differential inputs to maximize performance. The LTC6227 can be used to implement a Single-Ended to differential ADC driver as shown in Figure 6. One channel is configured in unity gain and drives another channel configured in an inverting gain stage of 1, both outputs drive the LTC2323-16 through an RC filter. Figure 7 shows the FFT obtained with a –1dBFS 156.25kHz input signal, with a demanding 5Msps sample rate. The obtained SNR of 81 dB is equivalent to that of the ADC by itself, thus there is no degradation due to the driver. The SFDR obtained is 84dB.

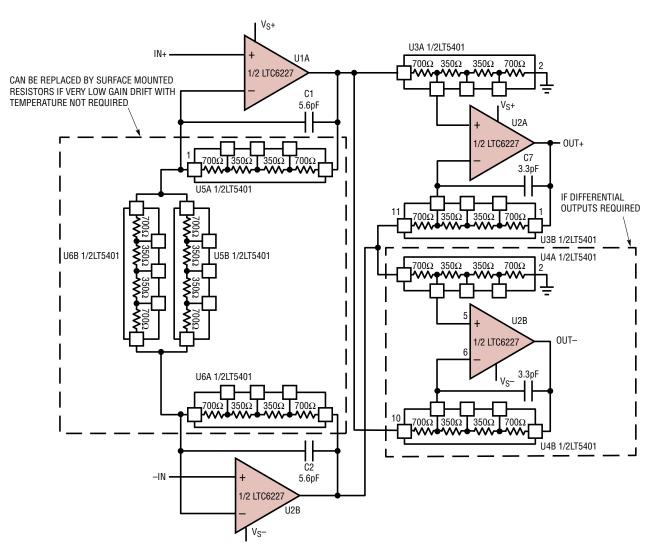

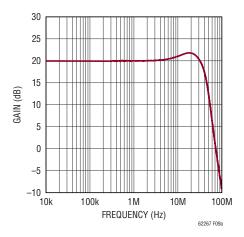

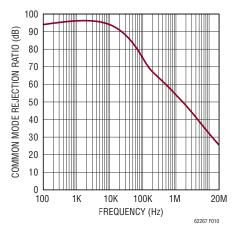

#### High Speed Low Voltage Low Noise Instrumentation Amplifier with High CMRR

Figure 8 shows a three op amp instrumentation amplifier with a gain of 10V/V which can operate on a wide range of supply voltages. The resistors are implemented using instances of the LT5401, a matched resistor array chip. The resistor matching of U3 is crucial in achieving high common mode rejection. The front end gain stage resistors were also implemented using instances of the LT5401, but can be implemented using other means as well, since they are not crucial for common mode rejection. Implementing them using the LT5401 minimizes gain variation across temperature. The amplifiers were implemented using instances of the LTC6227MS8, and supply voltages of  $\pm 1.5V$  were used. Figure 9 shows the measured frequency response, and Figure 10 shows the measured CMRR of the instrumentation amplifier, with the single ended output observed. Figure 11 shows the transient response for a  $150mV_{P-P}$  input square wave.The low offset and 1/f noise allow for wide band operation down to DC. The broadband input referred noise of  $4.6nV/\sqrt{Hz}$  is dominated by the resistors.

Figure 6. Single-Ended to Differential Driver for 16-Bit ADC

Figure 7. Measured Performance of the LTC6227 Based Single-Ended to Differential Converter Driving the LTC2323-16 ADC

Figure 8. High Speed High CMRR Instrumentation Amplifier

Figure 9. LTC6227-LT5401 Based Instrumentation Amplifier Frequency Response

Figure 10. LTC6227-LT5401 Based Instrumentation Amplifier CMRR

Figure 11. LTC6227-LT5401 Based Instrumentation Amplifier Transient Response

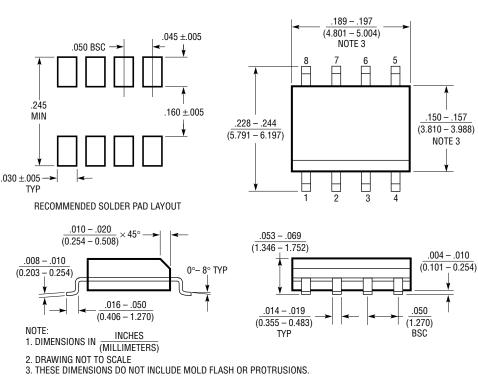

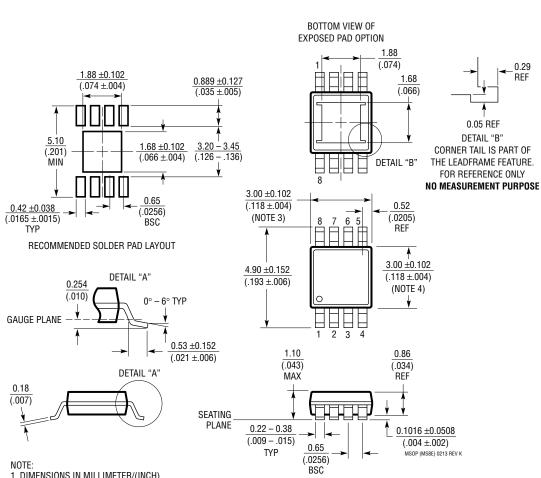

S8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch) (Reference LTC DWG # 05-08-1610 Rev G)

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

4. PIN 1 CAN BE BEVEL EDGE OR A DIMPLE

S08 REV G 0212

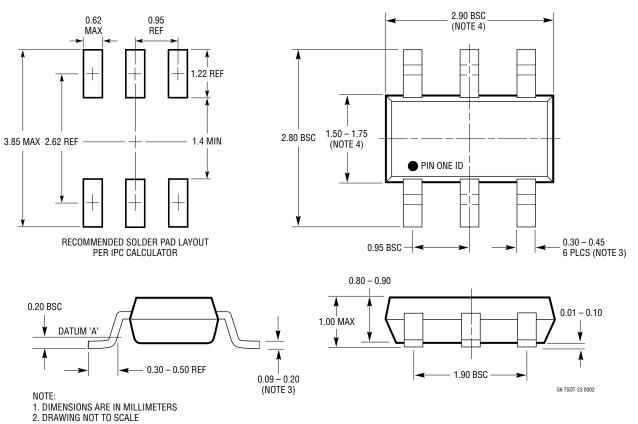

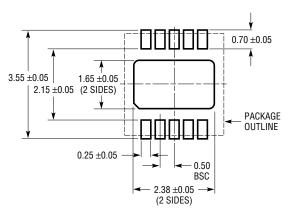

S6 Package 6-Lead Plastic TSOT-23 (Reference LTC DWG # 05-08-1636)

- 3. DIMENSIONS ARE INCLUSIVE OF PLATING

- 4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

- 5. MOLD FLASH SHALL NOT EXCEED 0.254mm

- 6. JEDEC PACKAGE REFERENCE IS MO-193

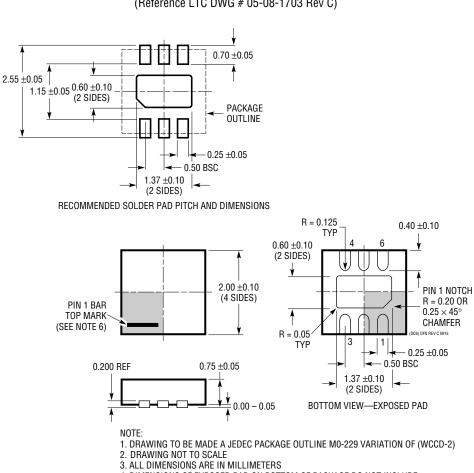

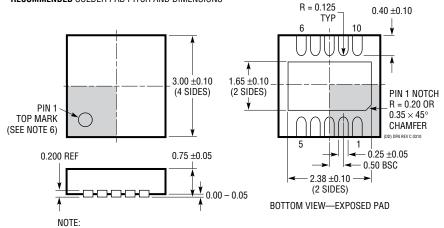

**DC6** Package 6-Lead Plastic DFN ( $2mm \times 2mm$ )

(Reference LTC DWG # 05-08-1703 Rev C)

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

**MS8E** Package 8-Lead Plastic MSOP, Exposed Die Pad (Reference LTC DWG # 05-08-1662 Rev K)

1. DIMENSIONS IN MILLIMETER/(INCH)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

DD Package 10-Lead Plastic DFN (3mm × 3mm) (Reference LTC DWG # 05-08-1699 Rev C)

**RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

TOP AND BOTTOM OF PACKAGE

## **RELATED PARTS**

| PART NUMBER                 | DESCRIPTION                                                                          | COMMENTS                                                                                   |

|-----------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <b>Operational Amplif</b>   | iers                                                                                 |                                                                                            |

| LTC6228/LTC6229             | Single/Dual High Speed Ultra Low Noise Low Distortion<br>Rail-to-Rail Output Op Amps | 0.88 nV/ <del>√Hz,</del> 730MHz, 500V/µs Unity Gain Stable                                 |

| LTC6252/LTC6253/<br>LTC6254 | Single/Dual/Quad High Speed Rail-to-Rail Input and Output<br>Op Amps                 | 720MHz, 3.5mA, 2.75nV/ $\sqrt{\text{Hz}}$ , 280V/ $\mu$ s, 0.35mV, Unity Gain Stable       |

| ADA4899-1                   | High Speed Ultra Low Noise Ultra Low Distortion                                      | 1 nV/√Hz, 600MHz, 310V/µs Unity Gain Stable                                                |

| LTC6268/LTC6269             | Single/Dual High Speed FET Input Op Amp                                              | 400MHz, 4nV/ <del>/Hz</del> , ±3f <sub>A</sub> Input Bias Current                          |

| LT1818/LT1819               | Single/Dual Wide Bandwidth, High Slew Rate Low Noise and Distortion Op Amps          | 400MHz, 9mA, 6nV/√Hz, 2500V/µs, 1.5mV –85dBc at 5MHz                                       |

| ADA4896-1/<br>ADA4896-2     | Low Noise Low Power Rail-to-Rail Output                                              | 3mA 1 nV/ $\sqrt{\text{Hz}}$ 230 MHz 120 V/µs Unity Gain Stable                            |

| LT6230/LT6231/<br>LT6232    | Single/Dual/Quad Low Noise Rail-to-Rail Output Op Amps                               | 215MHz, 3.5mA, 1.1nV/√Hz, 70V/µs, 350µV                                                    |

| LTC6246/LTC6247/<br>LTC6248 | Single/Dual/Quad High Speed Rail-to-Rail Input and Output Op Amps                    | 180MHz, 1mA, 4.2nV/√Hz, 90V/μs, 0.5mV                                                      |

| LT6200/LT6201               | Single/Dual Ultralow Noise Rail-to-Rail Input/Output Op Amps                         | 165MHz, 20mA, 0.95nV/ <del>/Hz</del> , 44V/µs, 1mV                                         |

| LT6202/LT6203/<br>LT6204    | Single/Dual/Quad Ultralow Noise Rail-to-Rail Op Amp                                  | 100MHz, 3mA, 1.9nV/ <del>/Hz</del> , 25V/µs, 0.5mV                                         |

| LT1801/LT1802               | Dual/Quad Low Power High Speed Rail-to-Rail Input and<br>Output Op Amps              | 80MHz, 2mA, 8.5nV√Hz, 25V/µs, 350µV                                                        |

| LT1028                      | Ultralow Noise, Precision High Speed Op Amps                                         | 75MHz, 9.5mA, 0.85nV/ <del>/Hz</del> , 11V/µs, 40µV                                        |

| LTC6350                     | Low Noise Single-Ended to Differential Converter/ADC Driver                          | 33MHz (–3dB), 4.8mA, 1.9nV/ $\sqrt{\text{Hz}}$ , 240ns Settling to 0.01% 8V <sub>P-P</sub> |

| ADCs                        |                                                                                      |                                                                                            |

| LTC2387-18                  | 18-Bit, 15Msps SAR-ADC                                                               | 95.7dB SNR                                                                                 |

| AD7380                      | 4Msps 16-Bit SAR-ADC                                                                 | 92dB DNR SNR, 6.6 V <sub>P-P</sub> Input Range                                             |

| LTC2323-16                  | 5Msps 16-Bit SAR-ADC                                                                 | 81dB SNR,8V <sub>P-P</sub> Input Range                                                     |

| AD4020                      | 1.8 Msps 20-Bit SAR-ADC                                                              | 99 dB SNR                                                                                  |

ANALOG DEVICES

- ...