80V Synchronous 4-Switch Buck-Boost DC/DC Slave Controller for LT8708 Multiphase System

### FEATURES

ANALOG

Slave Chip of LT8708 to Deliver Additional Power

POWER BY

- Good Current Matching to the Average Output Current of LT8708 Through Current Regulation

- Easily Paralleled with LT8708 Through Four Pins

- Synchronized Start-Up with LT8708

- Same Conduction Modes as LT8708

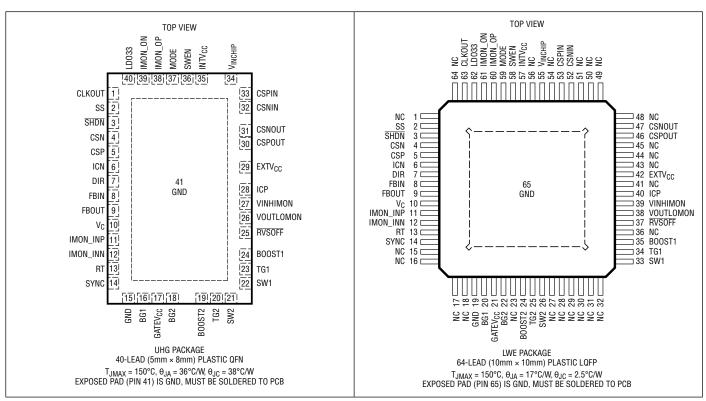

- Synchronous Rectification: Up to 98% Efficiency

- Frequency Range: 100kHz to 400kHz

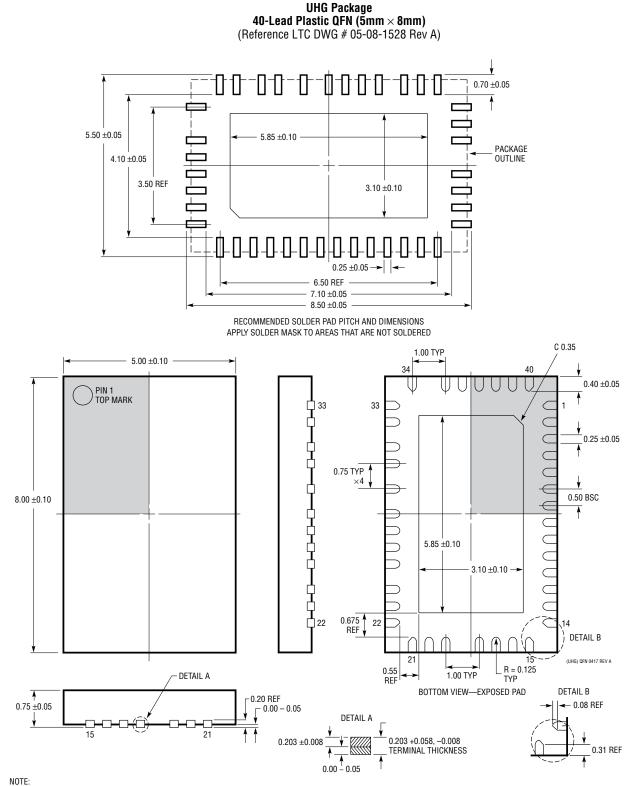

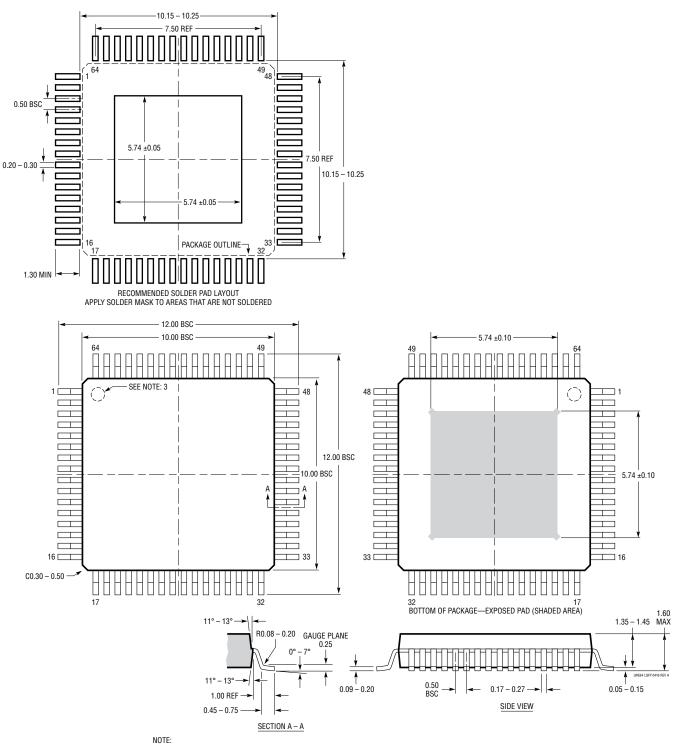

- Available in 40-Lead (5mm × 8mm) QFN with High Voltage Pin Spacing and 64-Lead (10mm × 10mm) eLQFP

- AEC-Q100 in Progress

### **APPLICATIONS**

- High Voltage Buck-Boost Converters

- Bidirectional Charging Systems

- Automotive 48V Systems

All registered trademarks and trademarks are the property of their respective owners.

### DESCRIPTION

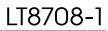

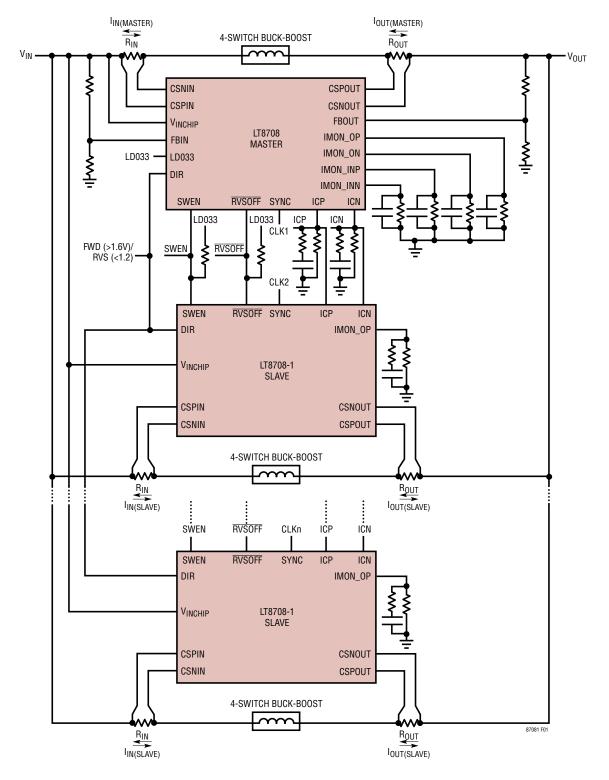

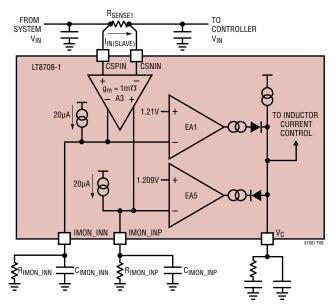

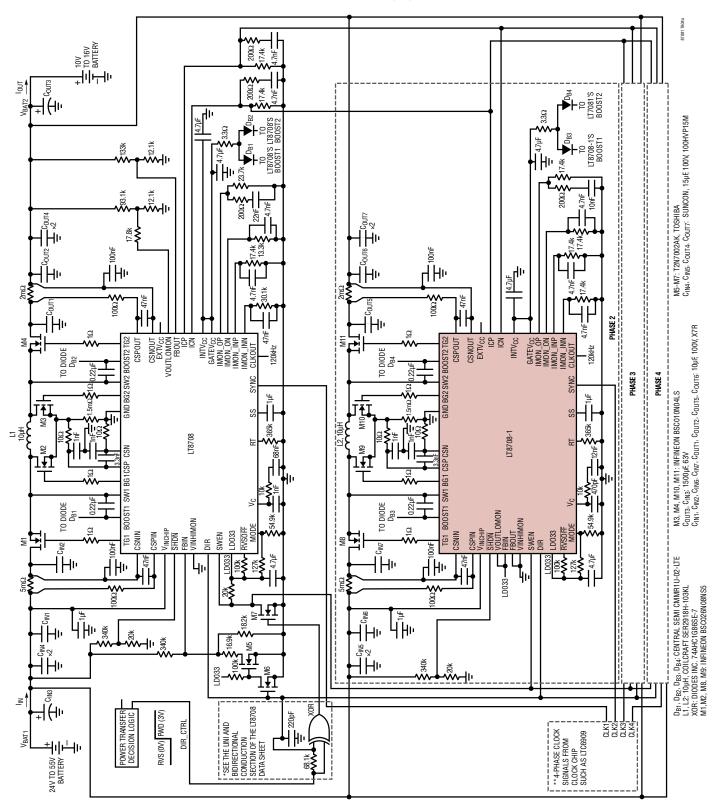

The LT<sup>®</sup>8708-1 is a high performance buck-boost switching regulator controller that is paralleled with the LT8708 to add power and phases to an LT8708 system. The LT8708-1 always operates as a slave to the master LT8708 and has the capability of delivering as much current or power as the master. One or more slaves can be connected to a single master, proportionally increasing power and current capability of the system.

The LT8708-1 has the same conduction modes as LT8708, allowing the LT8708-1 to conduct current and power in the same direction(s) as the master. The master controls the overall current and voltage limits for an LT8708 multiphase system, and the slaves comply with these limits.

LT8708-1s can be easily paralleled with the LT8708 by connecting four signals together. Two additional current limits (forward  $V_{\rm IN}$  current and reverse  $V_{\rm IN}$  current) are available on each slave that can be set independently.

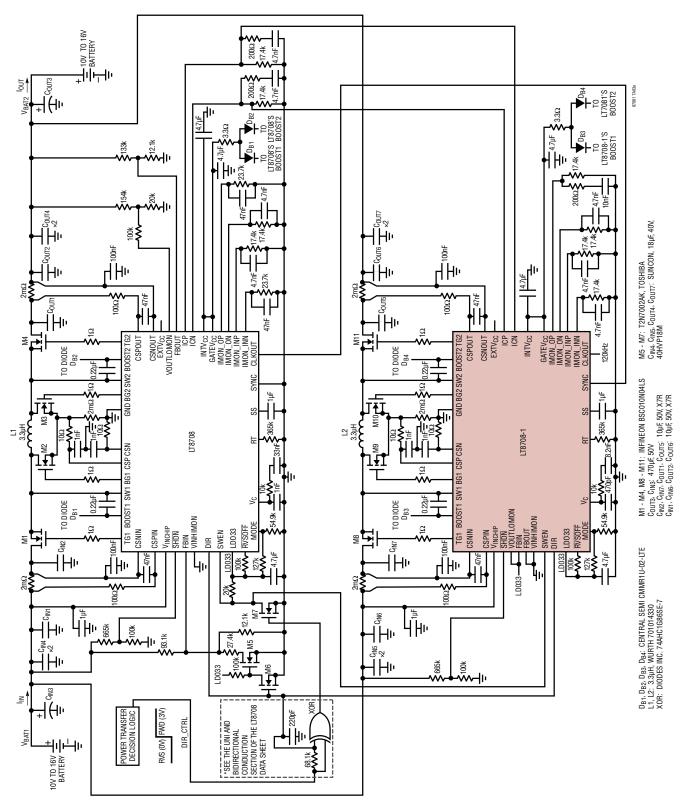

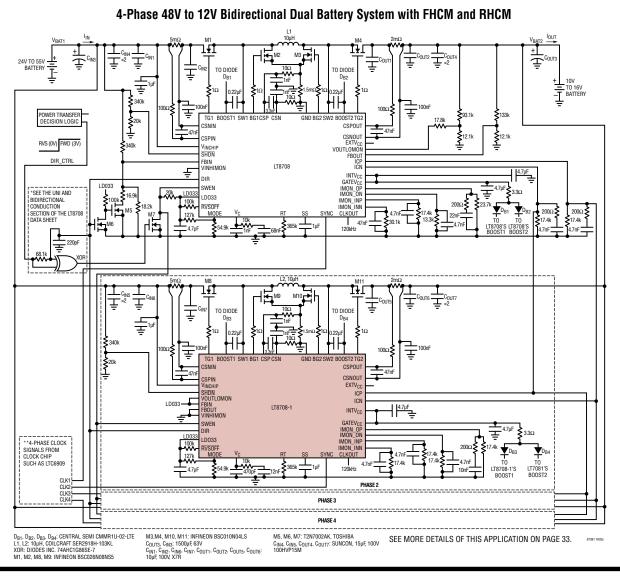

### TYPICAL APPLICATION

# TABLE OF CONTENTS

| Features                                                                                         | 1  |

|--------------------------------------------------------------------------------------------------|----|

| Applications                                                                                     | 1  |

| Typical Application                                                                              | 1  |

| Description                                                                                      |    |

| Absolute Maximum Ratings                                                                         |    |

| Pin Configuration                                                                                |    |

| Order Information                                                                                |    |

| Electrical Characteristics                                                                       |    |

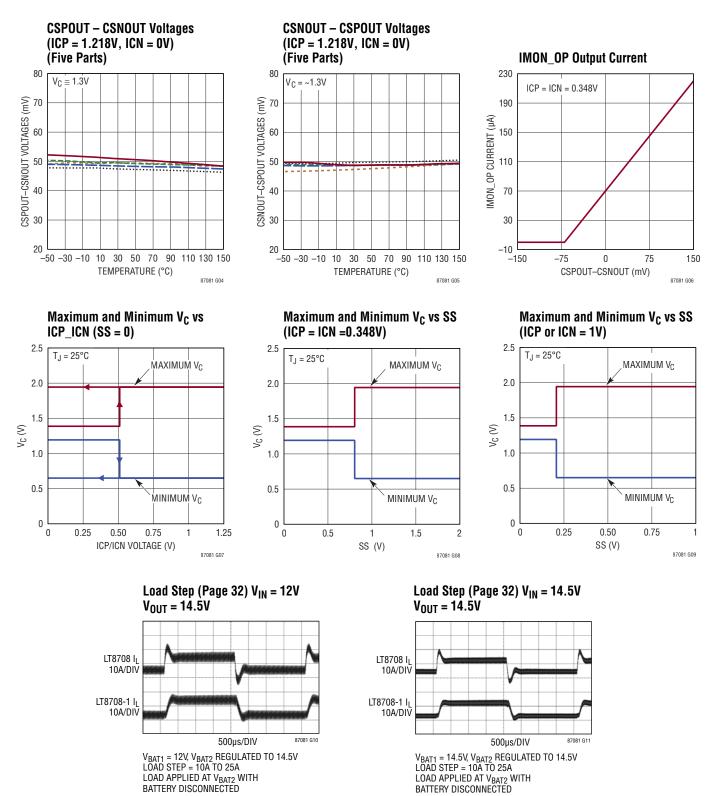

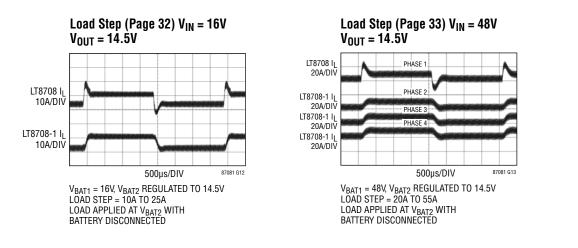

| Typical Performance Characteristics                                                              |    |

| Pin Functions                                                                                    |    |

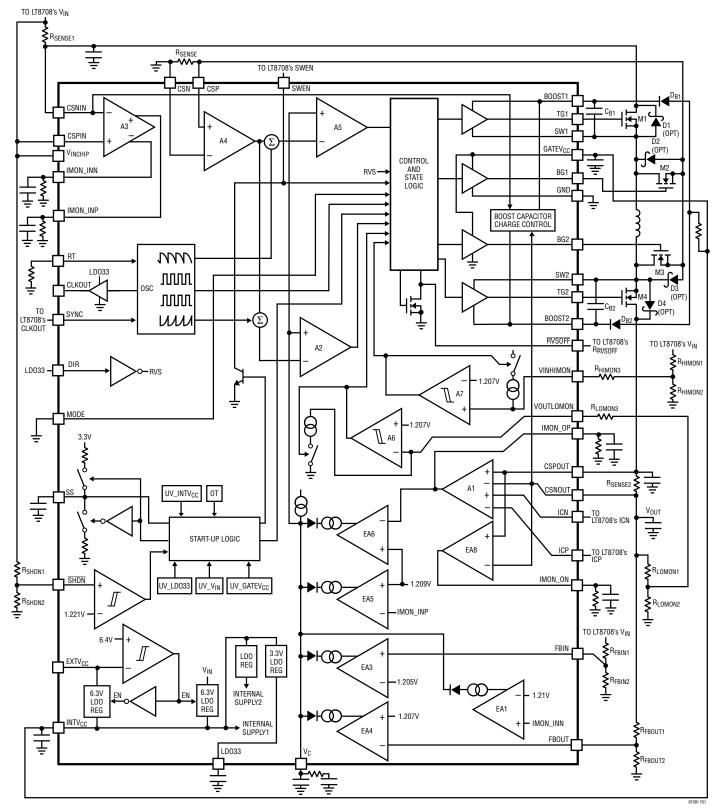

| Block Diagram                                                                                    | 13 |

| Operation                                                                                        | 14 |

| Common LT8708-1 and LT8708 Features                                                              | 14 |

| Adding Phases to an LT8708 Application                                                           | 14 |

| Adding Phases: The Master LT8708                                                                 | 14 |

| Adding Phases: The Slave LT8708-1                                                                | 16 |

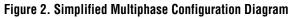

| Start-Up                                                                                         | 17 |

| Start-Up: SWEN Pin                                                                               |    |

| Start-Up: Soft-Start of Switching Regulator                                                      | 18 |

| Control Overview                                                                                 |    |

| Power Switch Control                                                                             |    |

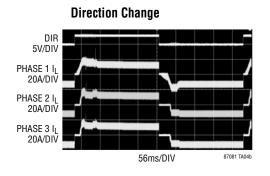

| Unidirectional and Bidirectional Conduction                                                      | 19 |

| Error Amplifiers                                                                                 |    |

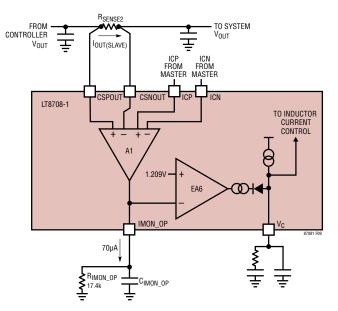

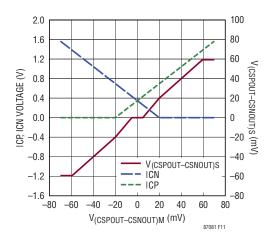

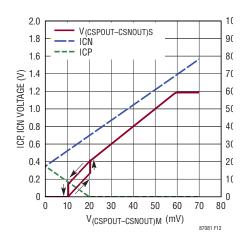

| Transfer Function: I <sub>OUT(SLAVE)</sub> vs I <sub>OUT(MASTER)</sub><br>Transfer Function: CCM | 20 |

| Transfer Function: CCM                                                                           | 21 |

| Transfer Function: DCM, HCM and Burst Mode                                                       |    |

| Operation                                                                                        | 21 |

|                                                                                                  |    |

| Current Monitoring and Limiting                                              | 21 |

|------------------------------------------------------------------------------|----|

| Monitoring: I <sub>OUT(SLAVE)</sub>                                          |    |

| Monitoring and Limiting: I <sub>IN(SLAVE)</sub>                              | 21 |

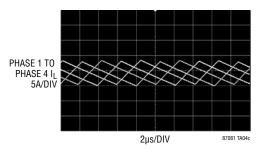

| Multiphase Clocking                                                          | 22 |

| Applications Information                                                     |    |

| Quick-Start Multiphase Setup                                                 |    |

| Quick Setup: Design the Master Phase                                         |    |

| Quick Setup: Design the Slave Phase(s)                                       |    |

| Quick Setup: Evaluation                                                      |    |

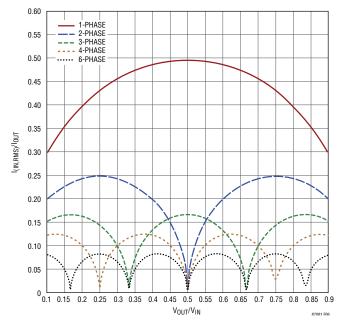

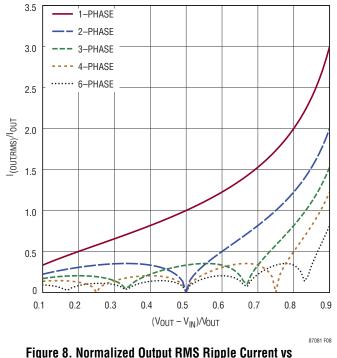

| Choosing the Total Number of Phases                                          |    |

| Operating Frequency Selection                                                |    |

| C <sub>IN</sub> and C <sub>OUT</sub> Selection                               |    |

| C <sub>IN</sub> and C <sub>OUT</sub> Selection: V <sub>IN</sub> Capacitance  |    |

| C <sub>IN</sub> and C <sub>OUT</sub> Selection: V <sub>OUT</sub> Capacitance |    |

| VINHIMON, VOUTLOMON and RVSOFF                                               |    |

| Configuring the I <sub>IN(SLAVE)</sub> Current Limits                        |    |

| Regulating IOUT(SLAVE)                                                       | 26 |

| Regulating I <sub>OUT(SLAVE)</sub>                                           | 26 |

| I <sub>OUT(SLAVE)</sub> : Configuration                                      | 28 |

| Loop Compensation                                                            | 28 |

| Voltage Lockouts                                                             |    |

| Circuit Board Layout Checklist                                               |    |

| Design Example                                                               |    |

| Typical Applications                                                         |    |

| Package Description                                                          |    |

| Revision History                                                             |    |

| Typical Application                                                          |    |

| Related Parts                                                                |    |

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| V <sub>CSP</sub> – V <sub>CSN</sub> , V <sub>CSPIN</sub> – V <sub>CSNIN</sub> , |               |

|---------------------------------------------------------------------------------|---------------|

| V <sub>CSPOUT</sub> – V <sub>CSNOUT</sub>                                       | –0.3V to 0.3V |

| CSP, CSN Voltage                                                                |               |

| V <sub>C</sub> Voltage (Note 2)                                                 | 0.3V to 2.2V  |

| RT, FBOUT, SS Voltage                                                           | 0.3V to 5V    |

| IMON_INP, IMON_INN, IMON_OP,                                                    |               |

| IMON_ON, ICP, ICN Voltage                                                       | 0.3V to 5V    |

| SYNC Voltage                                                                    | –0.3V to 5.5V |

| INTV <sub>CC</sub> , GATEV <sub>CC</sub> Voltage                                | 0.3V to 7V    |

| $V_{BOOST1} - V_{SW1}, V_{BOOST2} - V_{SW2}$                                    | 0.3V to 7V    |

| SWEN, RVSOFF Voltage                                                            |               |

| SWEN Current                                                                    | 0.5mA         |

| RVSOFF Current                                                                  | 1mA           |

| FBIN, SHDN Voltage                                                              | –0.3V to 30V  |

| -                                                                               |               |

| $eq:vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vinite_vini$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT8708-1E (Notes 3, 8)40°C to 125°C<br>LT8708-1I (Notes 3, 8)40°C to 125°C<br>LT8708-1H (Notes 3, 8)40°C to 150°C<br>Storage Temperature Range65°C to 150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

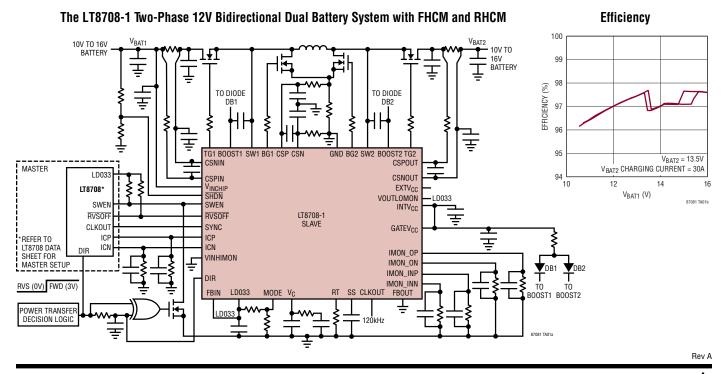

### PIN CONFIGURATION

Rev A

## ORDER INFORMATION

| LEAD FREE FINISH    | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|---------------------|---------------------|---------------|---------------------------------|-------------------|

| LT8708EUHG-1#PBF    | LT8708EUHG-1#TRPBF  | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 125°C    |

| LT8708IUHG-1#PBF    | LT8708IUHG-1#TRPBF  | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 125°C    |

| LT8708HUHG-1#PBF    | LT8708HUHG-1#TRPBF  | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 150°C    |

| AUTOMOTIVE PRODUCTS | **                  |               | · ·                             |                   |

| LT8708EUHG-1#WPBF   | LT8708EUHG-1#WTRPBF | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 125°C    |

| LT8708IUHG-1#WPBF   | LT8708IUHG-1#WTRPBF | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 125°C    |

| LT8708HUHG-1#WPBF   | LT8708HUHG-1#WTRPBF | 87081         | 40-Lead (5mm × 8mm) Plastic QFN | -40°C to 150°C    |

| TRAY                  | PART MARKING* | PACKAGE DESCRIPTION                 | MSL RATING | TEMPERATURE RANGE |

|-----------------------|---------------|-------------------------------------|------------|-------------------|

| LT8708ELWE-1#PBF      | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 125°C    |

| LT8708ILWE-1#PBF      | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 125°C    |

| LT8708HLWE-1#PBF      | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 150°C    |

| AUTOMOTIVE PRODUCTS** | ;             |                                     |            | -                 |

| LT8708ELWE-1#WPBF     | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 125°C    |

| LT8708ILWE-1#WPBF     | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 125°C    |

| LT8708HLWE-1#WPBF     | LT8708LWE-1   | 64-Lead (10mm × 10mm) Plastic eLQFP | 3          | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{INCHIP} = 12V$ , SHDN = 3V, DIR = 3.3V unless otherwise noted. (Note 3).

| PARAMETER                                                     | RAMETER CONDITIONS                                                                                                                                                                                                                      |   | MIN        | ТҮР         | MAX        | UNITS    |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------|------------|----------|

| Voltage Supplies and Regulators                               |                                                                                                                                                                                                                                         |   |            |             |            |          |

| V <sub>INCHIP</sub> Operating Voltage Range                   | $EXTV_{CC} = 0V$ $EXTV_{CC} = 7.5V$                                                                                                                                                                                                     | • | 5.5<br>2.8 |             | 80<br>80   | V<br>V   |

| V <sub>INCHIP</sub> Quiescent Current                         | Not Switching, V <sub>EXTVCC</sub> = 0<br>SWEN = 3.3V<br>SWEN = 0V                                                                                                                                                                      |   |            | 4.7<br>2.45 | 7.5<br>4.5 | mA<br>mA |

| VINCHIP Quiescent Current in Shutdown                         | V <sub>SHDN</sub> = 0V                                                                                                                                                                                                                  |   |            | 0           | 1          | μA       |

| EXTV <sub>CC</sub> Switchover Voltage                         | I <sub>INTVCC</sub> = -20mA, V <sub>EXTVCC</sub> Rising                                                                                                                                                                                 | • | 6.15       | 6.4         | 6.6        | V        |

| EXTV <sub>CC</sub> Switchover Hysteresis                      |                                                                                                                                                                                                                                         |   |            | 0.2         |            | V        |

| INTV <sub>CC</sub> Current Limit                              | $\begin{array}{l} \mbox{Max Current Draw from INTV}_{CC} \mbox{ and LD033 Pins} \\ \mbox{Combined. Regulated from } V_{INCHIP} \mbox{ or EXTV}_{CC} \mbox{ (12V)} \\ \mbox{INTV}_{CC} = 5.25 V \\ \mbox{INTV}_{CC} = 4.4 V \end{array}$ | • | 90<br>28   | 127<br>42   | 165<br>55  | mA<br>mA |

| INTV <sub>CC</sub> Voltage                                    | Regulated from $V_{INCHIP}$ , $I_{INTVCC} = 20mA$<br>Regulated from $EXTV_{CC}$ (12V), $I_{INTVCC} = 20mA$                                                                                                                              | • | 6.1<br>6.1 | 6.3<br>6.3  | 6.5<br>6.5 | V<br>V   |

| INTV <sub>CC</sub> Load Regulation                            | I <sub>INTVCC</sub> = 0mA to 50mA                                                                                                                                                                                                       |   |            | -0.5        | -1.5       | %        |

| INTV <sub>CC</sub> , GATEV <sub>CC</sub> Undervoltage Lockout | INTV <sub>CC</sub> Falling, GATEV <sub>CC</sub> Connected to INTV <sub>CC</sub>                                                                                                                                                         | • | 4.45       | 4.65        | 4.85       | V        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>INCHIP</sub> = 12V, SHDN = 3V, DIR = 3.3V unless otherwise noted. (Note 3).

| PARAMETER                                                                                      | CONDITIONS                                                                      |   | MIN            | TYP            | MAX           | UNITS        |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|----------------|----------------|---------------|--------------|

| INTV <sub>CC</sub> , GATEV <sub>CC</sub> Undervoltage Lockout Hysteresis                       | GATEV <sub>CC</sub> Connected to INTV <sub>CC</sub>                             |   |                | 160            |               | mV           |

| INTV <sub>CC</sub> Regulator Dropout Voltage                                                   | VINCHIP – VINTVCC, IINTVCC = 20mA                                               |   |                | 245            |               | mV           |

| LD033 Pin Voltage                                                                              | 5mA from LDO33 Pin                                                              | • | 3.23           | 3.295          | 3.35          | V            |

| LD033 Pin Load Regulation                                                                      | I <sub>LD033</sub> = 0.1mA to 5mA                                               |   |                | -0.25          | -1            | %            |

| LD033 Pin Current Limit                                                                        | SYNC = 3V                                                                       | • | 12             | 17.25          | 22            | mA           |

| LD033 Pin Undervoltage Lockout                                                                 | LD033 Falling                                                                   |   | 2.96           | 3.04           | 3.12          | V            |

| LD033 Pin Undervoltage Lockout Hysteresis                                                      |                                                                                 |   |                | 35             |               | mV           |

| Switching Regulator Control                                                                    |                                                                                 |   |                |                |               |              |

| Maximum Current Sense Threshold (V <sub>CSP</sub> – V <sub>CSN</sub> )                         | Boost Mode, Minimum M3 Switch Duty Cycle                                        | • | 76             | 93             | 110           | mV           |

| Maximum Current Sense Threshold (V <sub>CSN</sub> – V <sub>CSP</sub> )                         | Buck Mode, Minimum M2 Switch Duty Cycle                                         | • | 68             | 82             | 97            | mV           |

| Maximum Current Sense Threshold (V <sub>CSN</sub> – V <sub>CSP</sub> )                         | Boost Mode, Minimum M3 Switch Duty Cycle                                        | • | 79             | 93             | 108           | mV           |

| Maximum Current Sense Threshold (V <sub>CSP</sub> – V <sub>CSN</sub> )                         | Buck Mode, Minimum M2 Switch Duty Cycle                                         | • | 72             | 84             | 96            | mV           |

| Gain from $V_C$ to Max Current Sense Voltage ( $V_{CSP} - V_{CSN}$ ) (A5 in the Block Diagram) | Boost Mode<br>Buck Mode                                                         |   |                | 135<br>-135    |               | mV/V<br>mV/V |

| SHDN Input Voltage High                                                                        | SHDN Rising to Enable the Device<br>QFN<br>LWE                                  | • | 1.175<br>1.175 | 1.221<br>1.221 | 1.275<br>1.29 | V<br>V       |

| SHDN Input Voltage High Hysteresis                                                             |                                                                                 |   |                | 40             |               | mV           |

| SHDN Input Voltage Low                                                                         | Device Disabled, Low Quiescent Current<br>(LT8708E-1, LT8708I-1)<br>(LT8708H-1) | • |                |                | 0.35<br>0.3   | V<br>V       |

| SHDN Pin Bias Current                                                                          | V <sub>SHDN</sub> = 3V<br>V <sub>SHDN</sub> = 12V                               |   |                | 0<br>14        | 1<br>22       | μA<br>μA     |

| SWEN Rising Threshold Voltage                                                                  |                                                                                 | • | 1.156          | 1.208          | 1.256         | V            |

| SWEN Threshold Voltage Hysteresis                                                              |                                                                                 |   |                | 22             |               | mV           |

| SWEN Output Voltage Low                                                                        | I <sub>SWEN</sub> = 200µA<br>SHDN = 0V or V <sub>INCHIP</sub> = 0V<br>SHDN = 3V | • |                | 0.9<br>0.2     | 1.1<br>0.5    | V<br>V       |

| SWEN Internal Pull-Down Release Voltage                                                        | SHDN = 3V                                                                       | • | 0.75           | 0.8            |               | V            |

| MODE Pin Continuous Conduction Mode (CCM) Threshold                                            |                                                                                 | • | 0.4            |                |               | V            |

| MODE Pin Hybrid DCM/CCM Mode (HCM) Range                                                       |                                                                                 | • | 0.8            |                | 1.2           | V            |

| MODE Pin Discontinuous Conduction Mode (DCM) Range                                             |                                                                                 | • | 1.6            |                | 2.0           | V            |

| MODE Pin Burst Mode Operation Threshold                                                        |                                                                                 | • |                |                | 2.4           | V            |

| DIR Pin Forward Operation Threshold                                                            |                                                                                 | • | 1.6            |                |               | V            |

| DIR Pin Reverse Operation Threshold                                                            |                                                                                 | • |                |                | 1.2           | V            |

| RVSOFF Output Voltage Low                                                                      | I <sub>RVSOFF</sub> = 200μA                                                     | • |                | 0.08           | 0.5           | V            |

| RVSOFF Falling Threshold Voltage                                                               |                                                                                 | • | 1.155          | 1.209          | 1.275         | V            |

| RVSOFF Threshold Voltage Hysteresis                                                            |                                                                                 |   |                | 165            |               | mV           |

| Soft-Start Charging Current                                                                    | $V_{SS} = 0V$<br>$V_{SS} = 0.5V$                                                |   | 13<br>21       | 19<br>31       | 25<br>41      | μA<br>μA     |

| IMON_ON Rising Threshold for FDCM Operation                                                    | MODE = 1V (HCM), DIR = 3.3V                                                     |   | 235            | 255            | 280           | mV           |

| IMON_ON Falling Threshold for CCM Operation                                                    | MODE = 1V (HCM), DIR = 3.3V                                                     | • | 185            | 205            | 235           | mV           |

| IMON_INP Rising Threshold for RDCM Operation                                                   | MODE = 1V (HCM), DIR = 0V                                                       | • | 235            | 255            | 280           | mV           |

| IMON_INP Falling Threshold for CCM Operation                                                   | MODE = 1V (HCM), DIR = 0V                                                       | • | 185            | 205            | 235           | mV           |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating innertion temperature range otherwise specifications are at T<sub>A</sub> = 25°C. VINCHIP = 12V. SHDN = 3V. DIR = 3.3V unless otherwise noted. (Note 3).

| junction temperature range, otherwise specifications are at T                     | $_{A}$ = 25°C. $V_{INCHIP}$ =12V, SHDN = 3V, DIR = 3.3V                                                                                                                                                                                                                                                                                      | unle | ess othe                 | rwise n              | oted. (N                 | lote 3).             |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|----------------------|--------------------------|----------------------|

| PARAMETER                                                                         | CONDITIONS                                                                                                                                                                                                                                                                                                                                   |      | MIN                      | ТҮР                  | MAX                      | UNITS                |

| ICP Rising Threshold for Start Switching                                          |                                                                                                                                                                                                                                                                                                                                              |      | 485                      | 510                  | 536                      | mV                   |

| ICN Rising Threshold for Start Switching                                          |                                                                                                                                                                                                                                                                                                                                              |      | 485                      | 510                  | 536                      | mV                   |

| ICP Rising Threshold for Enabling Non-CCM Offset Current                          |                                                                                                                                                                                                                                                                                                                                              |      | 680                      | 704                  | 730                      | mV                   |

| ICP Falling Threshold for Disabling Non-CCM Offset Current                        |                                                                                                                                                                                                                                                                                                                                              |      | 500                      | 530                  | 560                      | mV                   |

| ICN Rising Threshold for Enabling Non-CCM Offset Current                          |                                                                                                                                                                                                                                                                                                                                              |      | 680                      | 704                  | 730                      | mV                   |

| ICN Falling Threshold for Disabling Non-CCM Offset Current                        |                                                                                                                                                                                                                                                                                                                                              |      | 500                      | 530                  | 560                      | mV                   |

| Voltage Regulation Loops (Refer to Block Diagram to Locate Am                     | plifiers)                                                                                                                                                                                                                                                                                                                                    |      |                          |                      |                          |                      |

| Regulation Voltage for FBOUT                                                      | Regulate V <sub>C</sub> to 1.2V                                                                                                                                                                                                                                                                                                              |      | 1.193                    | 1.207                | 1.222                    | V                    |

| Regulation Voltage for FBIN                                                       | Regulate V <sub>C</sub> to 1.2V                                                                                                                                                                                                                                                                                                              |      | 1.184                    | 1.205                | 1.226                    | V                    |

| Line Regulation for FBOUT and FBIN Error Amp Reference Voltage                    | V <sub>INCHIP</sub> = 12V to 80V, Not Switching                                                                                                                                                                                                                                                                                              |      |                          | 0.002                | 0.005                    | %/V                  |

| FBOUT Pin Bias Current                                                            | Current Out of Pin                                                                                                                                                                                                                                                                                                                           |      |                          | 15                   |                          | nA                   |

| FBOUT Error Amp EA4 g <sub>m</sub>                                                |                                                                                                                                                                                                                                                                                                                                              |      |                          | 345                  |                          | µmho                 |

| FBOUT Error Amp EA4 Voltage Gain                                                  |                                                                                                                                                                                                                                                                                                                                              |      |                          | 245                  |                          | V/V                  |

| VOUTLOMON Voltage Activation Threshold                                            | Falling                                                                                                                                                                                                                                                                                                                                      | •    | 1.185                    | 1.207                | 1.225                    | V                    |

| VOUTLOMON Threshold Voltage Hysteresis                                            |                                                                                                                                                                                                                                                                                                                                              |      |                          | 24                   |                          | mV                   |

| VOUTLOMON Pin Bias Current                                                        | V <sub>VOUTLOMON</sub> = 1.24V, Current Into Pin                                                                                                                                                                                                                                                                                             |      |                          | 0.01                 |                          | μA                   |

|                                                                                   | V <sub>VOUTLOMON</sub> = 1.17V, Current Into Pin                                                                                                                                                                                                                                                                                             | •    | 0.8                      | 1                    | 1.2                      | μA                   |

| FBIN Pin Bias Current                                                             | Current Out of Pin                                                                                                                                                                                                                                                                                                                           |      |                          | 10                   |                          | nA                   |

| FBIN Error Amp EA3 g <sub>m</sub>                                                 |                                                                                                                                                                                                                                                                                                                                              |      |                          | 235                  |                          | µmho                 |

| FBIN Error Amp EA3 Voltage Gain                                                   |                                                                                                                                                                                                                                                                                                                                              |      |                          | 150                  |                          | V/V                  |

| VINHIMON Voltage Activation Threshold                                             | Rising                                                                                                                                                                                                                                                                                                                                       | •    | 1.185                    | 1.207                | 1.23                     | V                    |

| VINHIMON Threshold Voltage Hysteresis                                             |                                                                                                                                                                                                                                                                                                                                              |      |                          | 24                   |                          | mV                   |

| VINHIMON Pin Bias Current                                                         | $V_{VINHIMON} = 1.17V$ , Current Into Pin<br>$V_{VINHIMON} = 1.24V$ , Current Out of Pin                                                                                                                                                                                                                                                     | •    | 0.8                      | 0.01<br>1            | 1.2                      | μΑ<br>μΑ             |

| Current Regulation Loops (Refer to Block Diagram to Locate Am                     | plifiers)                                                                                                                                                                                                                                                                                                                                    |      |                          |                      |                          |                      |

| Regulation Voltages for IMON_INP and IMON_OP                                      | V <sub>C</sub> = 1.2V                                                                                                                                                                                                                                                                                                                        | •    | 1.185                    | 1.209                | 1.231                    | V                    |

| Regulation Voltages for IMON_INN                                                  | V <sub>C</sub> = 1.2V                                                                                                                                                                                                                                                                                                                        | •    | 1.185                    | 1.21                 | 1.24                     | V                    |

| Line Regulation for IMON_INP, IMON_INN and IMON_OP Error<br>Amp Reference Voltage | V <sub>INCHIP</sub> = 12V to 80V                                                                                                                                                                                                                                                                                                             |      |                          | 0.002                | 0.005                    | %/V                  |

| CSPIN Bias Current                                                                | V <sub>CSPIN</sub> = 12V<br>V <sub>CSPIN</sub> = 1.5V                                                                                                                                                                                                                                                                                        |      |                          | 0.01<br>0.01         |                          | μΑ<br>μΑ             |

| CSNIN Bias Current                                                                | $\begin{array}{l} \text{BOOST Capacitor Charge Control Block Not Active} \\ \text{V}_{\text{SWEN}} = 3.3\text{V}, \text{V}_{\text{CSPIN}} = \text{V}_{\text{CSNIN}} = 12\text{V} \\ \text{V}_{\text{SWEN}} = 3.3\text{V}, \text{V}_{\text{CSPIN}} = \text{V}_{\text{CSNIN}} = 1.5\text{V} \\ \text{V}_{\text{SWEN}} = 0\text{V} \end{array}$ |      |                          | 84<br>4.25<br>0.01   |                          | μΑ<br>μΑ<br>μΑ       |

| CSPIN, CSNIN Common Mode Operating Voltage Range                                  |                                                                                                                                                                                                                                                                                                                                              |      | 0                        |                      | 80                       | V                    |

| CSPIN, CSNIN Differential Mode Operating Voltage Range                            |                                                                                                                                                                                                                                                                                                                                              | •    | -100                     |                      | 100                      | mV                   |

| IMON_INP Output Current                                                           | $ \begin{array}{l} V_{CSPIN} - V_{CSNIN} = 50 \text{mV}, \ V_{CSNIN} = 5 \text{V} \\ V_{CSPIN} - V_{CSNIN} = 50 \text{mV}, \ V_{CSNIN} = 5 \text{V} \\ V_{CSPIN} - V_{CSNIN} = 5 \text{mV}, \ V_{CSNIN} = 5 \text{V} \\ V_{CSPIN} - V_{CSNIN} = 5 \text{mV}, \ V_{CSNIN} = 5 \text{V} \end{array} $                                          | •    | 67<br>64.5<br>22.5<br>20 | 70<br>70<br>25<br>25 | 73<br>75.5<br>27.5<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| IMON_INN Output Current                                                           | $\begin{array}{l} V_{CSNIN}-V_{CSPIN}=50mV, V_{CSNIN}=5V\\ V_{CSNIN}-V_{CSPIN}=50mV, V_{CSNIN}=5V\\ V_{CSNIN}-V_{CSPIN}=5mV, V_{CSNIN}=5V\\ V_{CSNIN}-V_{CSPIN}=5mV, V_{CSNIN}=5V \end{array}$                                                                                                                                               | •    | 66<br>65<br>19<br>18     | 70<br>70<br>25<br>25 | 74<br>75<br>30.5<br>32   | μΑ<br>μΑ<br>μΑ<br>μΑ |

Rev A

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>INCHIP</sub> = 12V, SHDN = 3V, DIR = 3.3V unless otherwise noted. (Note 3).

| PARAMETER                                                                                                               | CONDITIONS                                                                                                                                                                                                                                                                                                                                             |                                                                                               |   | MIN                                      | ТҮР                              | MAX                                    | UNITS                      |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---|------------------------------------------|----------------------------------|----------------------------------------|----------------------------|

| IMON_INP and IMON_INN Max Output Current                                                                                |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   | 120                                      |                                  |                                        | μA                         |

| IMON_INP Error Amp EA5 gm                                                                                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   |                                          | 190                              |                                        | µmho                       |

| IMON_INP Error Amp EA5 Voltage Gain                                                                                     |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   |                                          | 130                              |                                        | V/V                        |

| IMON_INN Error Amp EA1 gm                                                                                               | FBIN = 0V, FBOUT = 3.3                                                                                                                                                                                                                                                                                                                                 | /                                                                                             |   |                                          | 190                              |                                        | µmho                       |

| IMON_INN Error Amp EA1 Voltage Gain                                                                                     | FBIN = 0V, FBOUT = 3.3                                                                                                                                                                                                                                                                                                                                 | /                                                                                             |   |                                          | 130                              |                                        | V/V                        |

| CSPOUT Bias Current                                                                                                     | V <sub>CSPOUT</sub> = 12V<br>V <sub>CSPOUT</sub> = 1.5V                                                                                                                                                                                                                                                                                                |                                                                                               |   |                                          | 0.01<br>0.01                     |                                        | μΑ<br>μΑ                   |

| CSNOUT Bias Current                                                                                                     | BOOST Capacitor Charge<br>V <sub>SWEN</sub> = 3.3V, V <sub>CSPOUT</sub><br>V <sub>SWEN</sub> = 3.3V, V <sub>CSPOUT</sub><br>V <sub>SWEN</sub> = 0V                                                                                                                                                                                                     | e Control Block Not Active<br>T = V <sub>CSNOUT</sub> = 12V<br>T = V <sub>CSNOUT</sub> = 1.5V |   |                                          | 83<br>4.25<br>0.01               |                                        | μΑ<br>μΑ<br>μΑ             |

| CSPOUT, CSNOUT Common Mode Operating Voltage Range                                                                      |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               | • | 0                                        |                                  | 80                                     | V                          |

| CSPOUT, CSNOUT Differential Mode Operating Voltage Range                                                                |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   | -100                                     |                                  | 100                                    | mV                         |

| IMON_ON Output Current                                                                                                  | $ \begin{array}{l} V_{CSNOUT} - V_{CSPOUT} = 50mV, \ V_{CSNOUT} = 5V\\ V_{CSNOUT} - V_{CSPOUT} = 50mV, \ V_{CSNOUT} = 5V\\ V_{CSNOUT} - V_{CSPOUT} = 5mV, \ V_{CSNOUT} = 5V\\ V_{CSNOUT} - V_{CSPOUT} = 5mV, \ V_{CSNOUT} = 5V\\ V_{CSNOUT} - V_{CSPOUT} = -5mV, \ V_{CSNOUT} = 5V\\ V_{CSNOUT} - V_{CSPOUT} = -5mV, \ V_{CSNOUT} = 5V\\ \end{array} $ |                                                                                               | • | 67<br>65<br>22.5<br>20.5<br>12.5<br>10.5 | 70<br>70<br>25<br>25<br>15<br>15 | 73<br>75<br>27.5<br>29<br>17.5<br>19.5 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

| IMON_ON Max Output Current                                                                                              |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               | ٠ | 120                                      |                                  |                                        | μA                         |

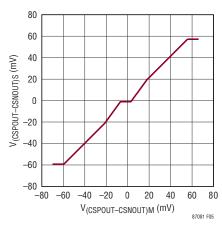

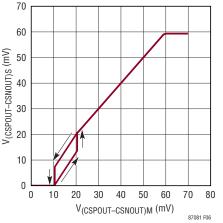

| CSPOUT-CSNOUT Regulation Voltage                                                                                        | Regulate V <sub>C</sub> to 1.2V                                                                                                                                                                                                                                                                                                                        | ICP = 1.218V, ICN = 0V                                                                        |   | 43                                       | 50                               | 55                                     | mV                         |

|                                                                                                                         | $R_{IMON_{OP}} = 17.4 k\Omega$<br>V <sub>CSNOUT</sub> = 12V                                                                                                                                                                                                                                                                                            | ICP = 0V, ICN = 1.218V                                                                        |   | -55                                      | -50                              | -44                                    | mV                         |

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                        | ICP = ICN = 0.348V                                                                            | • | -6                                       | 0                                | 6                                      | mV                         |

| NMOS Gate Drivers                                                                                                       |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   |                                          |                                  |                                        |                            |

| TG1, TG2 Rise Time                                                                                                      | C <sub>LOAD</sub> = 3300pF (Note 4)                                                                                                                                                                                                                                                                                                                    |                                                                                               |   |                                          | 20                               |                                        | ns                         |

| TG1, TG2 Fall Time                                                                                                      | C <sub>LOAD</sub> = 3300pF (Note 4)                                                                                                                                                                                                                                                                                                                    |                                                                                               |   |                                          | 20                               |                                        | ns                         |

| BG1, BG2 Rise Time                                                                                                      | C <sub>LOAD</sub> = 3300pF (Note 4)                                                                                                                                                                                                                                                                                                                    |                                                                                               |   |                                          | 20                               |                                        | ns                         |

| BG1, BG2 Fall Time                                                                                                      | C <sub>LOAD</sub> = 3300pF (Note 4)                                                                                                                                                                                                                                                                                                                    |                                                                                               |   |                                          | 20                               |                                        | ns                         |

| TG1 Off to BG1 On Delay                                                                                                 | C <sub>LOAD</sub> = 3300pF Each Driver                                                                                                                                                                                                                                                                                                                 |                                                                                               |   |                                          | 90                               |                                        | ns                         |

| BG1 Off to TG1 On Delay                                                                                                 | C <sub>LOAD</sub> = 3300pF Each Dr                                                                                                                                                                                                                                                                                                                     | iver                                                                                          |   |                                          | 80                               |                                        | ns                         |

| TG2 Off to BG2 On Delay                                                                                                 | C <sub>LOAD</sub> = 3300pF Each Dr                                                                                                                                                                                                                                                                                                                     | iver                                                                                          |   |                                          | 90                               |                                        | ns                         |

| BG2 Off to TG2 On Delay                                                                                                 | C <sub>LOAD</sub> = 3300pF Each Dr                                                                                                                                                                                                                                                                                                                     | iver                                                                                          |   |                                          | 80                               |                                        | ns                         |

| $\underbrace{\text{Min On-Time for Main Switch in Boost Operation }(t_{\text{ON}(\text{M3},\text{MIN})})}_{\text{CON}}$ | Switch M3, C <sub>LOAD</sub> = 330                                                                                                                                                                                                                                                                                                                     | 0pF                                                                                           |   |                                          | 200                              |                                        | ns                         |

| $\underline{\mbox{Min On-Time for Synchronous Switch in Buck Operation}} (t_{ON(M2,MIN)})$                              | ) Switch M2, C <sub>LOAD</sub> = 330                                                                                                                                                                                                                                                                                                                   | 0pF                                                                                           |   |                                          | 200                              |                                        | ns                         |

| Min Off-Time for Main Switch in Steady-State Boost Operation                                                            | Switch M3, C <sub>LOAD</sub> = 330                                                                                                                                                                                                                                                                                                                     | 0pF                                                                                           |   |                                          | 230                              |                                        | ns                         |

| Min Off-Time for Synchronous Switch in Steady-State Buck Operation                                                      | n Switch M2, C <sub>LOAD</sub> = 330                                                                                                                                                                                                                                                                                                                   | 0pF                                                                                           |   |                                          | 230                              |                                        | ns                         |

| Oscillator                                                                                                              |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   |                                          |                                  |                                        |                            |

| Switch Frequency Range                                                                                                  | SYNCing or Free Running                                                                                                                                                                                                                                                                                                                                | g                                                                                             |   | 100                                      |                                  | 400                                    | kHz                        |

| Switching Frequency, f <sub>OSC</sub>                                                                                   | $R_{T} = 365k$<br>$R_{T} = 215k$<br>$R_{T} = 124k$                                                                                                                                                                                                                                                                                                     |                                                                                               | • | 102<br>170<br>310                        | 120<br>202<br>350                | 142<br>235<br>400                      | kHz<br>kHz<br>kHz          |

| SYNC High Level for Synchronization                                                                                     |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   | 1.3                                      |                                  |                                        | V                          |

| SYNC Low Level for Synchronization                                                                                      |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               | • |                                          |                                  | 0.5                                    | V                          |

| SYNC Clock Pulse Duty Cycle                                                                                             | V <sub>SYNC</sub> = 0V to 2V                                                                                                                                                                                                                                                                                                                           |                                                                                               |   | 20                                       |                                  | 80                                     | %                          |

| Recommended Min SYNC Ratio f <sub>SYNC</sub> /f <sub>OSC</sub>                                                          |                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |   | -                                        | 3/4                              |                                        |                            |

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{INCHIP} = 12V$ , SHDN = 3V, DIR = 3.3V unless otherwise noted. (Note 3).

| PARAMETER                  | CONDITIONS                                                                |   | MIN | ТҮР                | MAX | UNITS       |

|----------------------------|---------------------------------------------------------------------------|---|-----|--------------------|-----|-------------|

| CLKOUT Output Voltage High | $V_{LD033} - V_{CLKOUT},$ 1mA Out of CLKOUT Pin, $I_{LD033} = 0 \mu A$    |   |     | 100                | 250 | mV          |

| CLKOUT Output Voltage Low  | 1mA Into CLKOUT Pin                                                       |   |     | 25                 | 100 | mV          |

| CLKOUT Duty Cycle          | T <sub>J</sub> = −40°C<br>T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C |   |     | 22.7<br>44.1<br>77 |     | %<br>%<br>% |