RN8302B

# RN8302B USER MANUAL

Date: 2019-08-09 Version: 1.1

# CONTENTS

| 1. Introduction                                      |

|------------------------------------------------------|

| 1.1 Features                                         |

| 1.2 Functional Block Diagram                         |

| 1.3 Pin Definition                                   |

| 1.4 Typical Application                              |

| 2 System Function                                    |

| 2.1 Power Supply Monitoring                          |

| 2.2 Operating Mode                                   |

| 2.3 System Reset                                     |

| 2.4 Measurement Mode                                 |

| 2.5 Low Power Mode                                   |

| 2.6 Interrupt                                        |

| 3 Register                                           |

| 3.1 Parameter Register List                          |

| 3.2 Description of Parameter Register                |

| 3.3 Configuration and Status Register List           |

| 3.4 Description of Configuration and Status Register |

| 3.5 Reset and Mode Switching72                       |

| 3.6 Write Protection75                               |

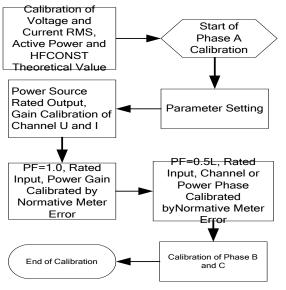

| 4 Calibration Method                                 |

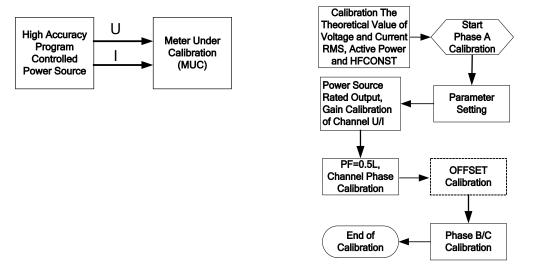

| 4.1 General Description                              |

| 4.2 Power Calibration Method76                       |

| 4.3 Example of Power Calibration Method              |

| 4.4 Pulse Calibration Method                         |

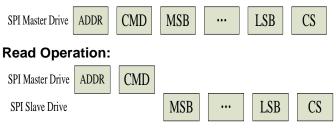

| 5 Communication Interface                            |

| 5.1 SPI Address Space Description                    |

| 5.2 SPI Interface Signal Description                 |

| 5.3 SPI Frame Format                                 |

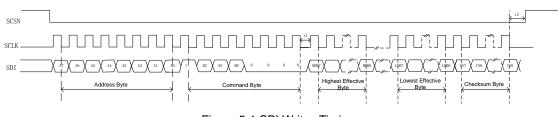

| 5.4 SPI Writes Timing                                |

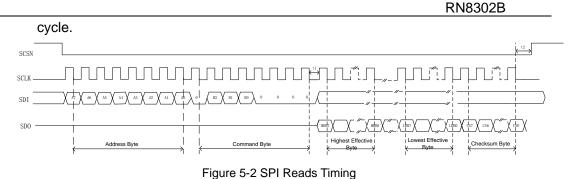

| 5.5 SPI Reads Timing                                 |

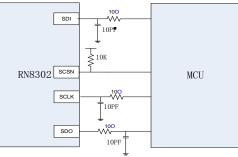

| 5.6 SPI Interface Reliability Design                 |

| 6 Electrical Specifications                          |

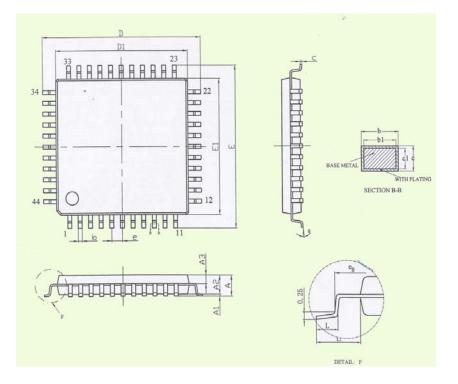

| 7 Package Size                                       |

| 8 Package Information                                |

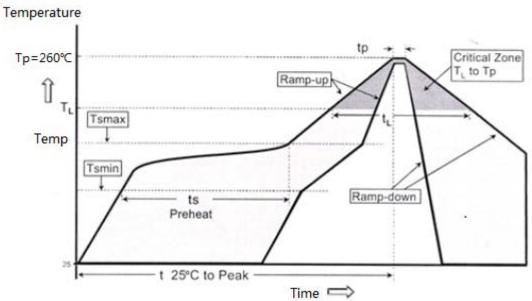

| 9 Temperature Setting Conditions of SMT              |

# 1. Introduction

#### 1.1 Features

- Metering

- Less than 0.1% error in total and fundamental active energy over a dynamic range of 5000: 1, meet the accuracy requirement for the class 0.5S and 0.2S active electrical energy meter of the national grid.

- ✓ Less than 0.1% error in total and fundamental reactive energy over a dynamic range of 5000: 1.

- ✓ Total and fundamental apparent energy.

- ✓ Active and reactive power orientations, four-quadrant reactive judging.

- ✓ No-load and startup function, adjustable startup threshold.

- ✓ Adjustable electrical energy meter constant(EC).

- ✓ Fast pulse count of the active, reactive and apparent powers.

- ✓ Total and fundamental active, reactive and apparent CF frequency outputs.

- Measurement

- ✓ Total and fundamental active, reactive and apparent powers.

- ✓ Three-phase total, fundamental and harmonic Voltage RMS and current RMS.

- ✓ Total and fundamental power factors.

- ✓ Less than 0.02% accuracy of voltage line frequence.

- ✓ Less than 0.02° resolution of fundamental voltage and current phase angle for each phase.

- ✓ Seven channels zero-crossing detection and settable zero-crossing threshold.

- ✓ Voltage phase sequence error detection.

- ✓ Loss of voltage indication and settable loss of voltage threshold.

- ✓ Flexible voltage and current waveform buffer data.

- ✓ Voltage sag detection.

- ✓ Overvoltage and overcurrent detection.

- Anti-tampering

- ✓ Neutral current measurement.

- ✓ A low power dissipated mode NVM2 for the current comparison and pre-judging. Settable two levels of threshold and less than 150µA of power dissipated.

- ✓ A low power mode NVM1 to implement the low power current RMS measurement, and less than 2mA of power dissipated.

- ✓ Transformer open-circuit and short-circuit detection function at the secondary side.

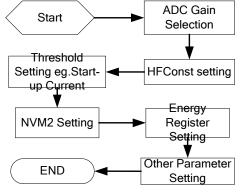

- Software Calibration

- Channel gain calibration of seven ADCs, and compatible with the power calibration method.

- ✓ Channel phase calibration of seven ADCs, current channel A, B and C support

RN8302B

per-phase calibration.

- ✓ Power gain and phase calibration.

- ✓ Active, reactive and RMS offset calibration.

- $\checkmark$  Checksum register to check the calibration data automatically.

- Compatible with three-phase three-wire system and three-phase four-wire system.

- 3.3V signle power supply with power monitoring function.

- On-chip 1.25V ADC reference voltage, typical 20 ppm/°C of temperature coefficient, connectable reference voltage externally.

- High speed SPI interface with transmission rate up to 3.5Mbps and write protection function.

- One interrupt pin.

- Operating voltage range: 3.0V 3.6V

- ◆ Operating temperature range: -40°C 85°C

- LQFP44 package is adopted.

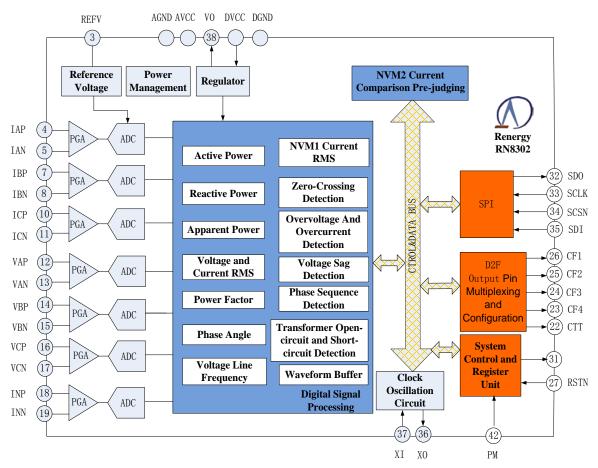

#### **1.2 Functional Block Diagram**

Figure 1-1 System Block Diagram

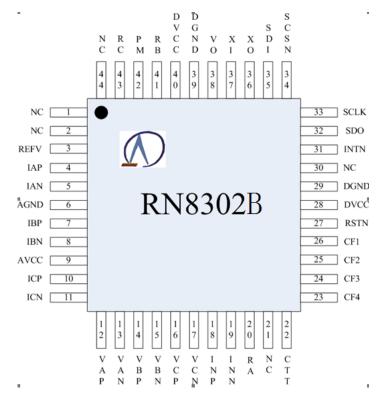

#### **1.3 Pin Definition**

| Pin No.    | Name     | Туре  | Description                                                     |  |  |

|------------|----------|-------|-----------------------------------------------------------------|--|--|

| 1,2,21,30, | NC       |       | Not connected                                                   |  |  |

| 44         |          |       |                                                                 |  |  |

| 3          | REFV     | I/O   | Output of the on-chip reference voltage when the                |  |  |

|            |          |       | register bit REFSEL ( <u>ADCCFG</u> .14) = 0. This pin          |  |  |

|            |          |       | shound be decoupled to AGND with 10 $\mu$ F and 0.1 $\mu$ F     |  |  |

|            |          |       | capacitor.                                                      |  |  |

|            |          |       | This pin is the input of the external high accurate             |  |  |

|            |          |       | reference voltage when the register bit REFSEL                  |  |  |

|            |          |       | $(\underline{ADCCFG}.14) = 1$ , as the reference voltage of the |  |  |

|            |          |       | internal ADC.                                                   |  |  |

| 4,5        | IAP, IAN | I     | Positive and negative analog input pins for Phase A             |  |  |

|            |          |       | Current. These pins are differential inputs, with the           |  |  |

|            |          |       | maximum input Vpp is 800mVpp in normal                          |  |  |

|            |          |       | operation.                                                      |  |  |

| 6          | AGND     | Power | Analog ground.                                                  |  |  |

| 7,8        | IBP, IBN | I     | Positive and negative analog input pins for Phase B             |  |  |

|            |          |       | Current. These pins are differential inputs, with the           |  |  |

|           |           |       | RN8302B                                                    |

|-----------|-----------|-------|------------------------------------------------------------|

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 9         | AVCC      | Power | 3.3V analog power supply. The operating range is           |

|           |           |       | 3.0V-3.6V. This pin shound be decoupled to AGND            |

|           |           |       | with $10\mu$ F capacitor and $0.1\mu$ F capacitor.         |

| 10,11     | ICP, ICN  | I     | Positive and negative analog input pins for Phase C        |

|           |           |       | Current. These pins are differential inputs, with the      |

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 12,13     | VAP, VAN  | I     | Positive and negative analog input pins for Phase A        |

|           |           |       | Voltage. These pins are differential inputs, with the      |

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 14,15     | VBP, VBN  | I     | Positive and negative analog input pins for Phase B        |

|           |           |       | Voltage. These pins are differential inputs, with the      |

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 16,17     | VCP, VCN  | I     | Positive and negative analog input pins for Phase C        |

|           |           |       | Voltage. These pins are differential inputs, with the      |

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 18,19     | INP, INN  | I     | Positive and negative analog input pins for Neutral        |

|           |           |       | Current. These pins are differential inputs, with the      |

|           |           |       | maximum input Vpp is 800mVpp in normal                     |

|           |           |       | operation.                                                 |

| 20        | RA        |       | Reserved pin. Connect with the analog ground.              |

| 22        | CTT       | 0     | Used to perform the transformer open-circuit and           |

|           |           | -     | short-circuit detection function at the secondary side.    |

| 23,24,25, | CF4, CF3, | 0     | Calibration Frequency (CF) Logic Outputs. Can be           |

| 26        | CF2, CF1  |       | configured by register <u>CFCFG</u> into any pulse of the  |

|           |           |       | all-phase sum output of the fundamental/total and          |

|           |           |       | active/reactive/apparent powers or the high                |

|           | DOT       |       | frequency pulse of the all-phase sum output.               |

| 27        | RSTN      | I     | Reset pin, active low. For the details, refer to           |

|           |           |       | Chapter 2.3. It is internal floating and shall be          |

|           |           |       | connected with the power supply or the 1K $\Omega$ pull-up |

| 00.40     |           |       | resistor externally.                                       |

| 28,40     | DVCC      | Power | 3.3 digital power supply. The operating range is 3.0V      |

|           |           |       | - 3.6V. This pin shound be decoupled to AGND with          |

| 00.00     |           |       | 10µF and 0.1µF capacitor.                                  |

| 29,39     | DGND      | Power | Digital ground.                                            |

|    |       |   | RIN8302B                                                   |

|----|-------|---|------------------------------------------------------------|

| 31 | INTN  | 0 | Interrupt output pin, active low. High level, by default.  |

|    |       |   | When the allowed interrupt event of the interrupt          |

|    |       |   | enable register has occurred, the pin level is toggled.    |

|    |       |   | When CPU clears corresponding interrupt flag by the        |

|    |       |   | SPI interface, the pin resets its high level.              |

| 32 | SDO   | 0 | SPI serial data output, data is shifted out on the         |

|    |       |   | SCLK rising edge. When SCS_N is high, it stays in          |

|    |       |   | high impedance.                                            |

| 33 | SCLK  | I | SPI serial clock input. Serial clock to synchronize the    |

|    |       |   | serial interface configuration generated by MCU.           |

|    |       |   | The master writes data at the High level of SCLK,          |

|    |       |   | and the slave reads the data at the SCLK low level.        |

| 34 | SCS_N | I | SPI selection signal, active low.                          |

| 35 | SDI   | I | SPI serial data input. Data is shifted in on the SCLK      |

|    |       |   | falling edge.                                              |

| 36 | XO    | 0 | Output terminal of the clock crystal.                      |

| 37 | XI    | I | Input terminal of the clock critical or the system clock   |

|    |       |   | input of the external clock. The typical frequency of      |

|    |       |   | the clock crystal is 8.192MHz. The typical value of        |

|    |       |   | the load capacitance is 15pF, and it is necessary to       |

|    |       |   | connect with the $10M\Omega$ resistor between this pin and |

|    |       |   | the XO pin.                                                |

| 38 | VO    | 0 | On-chip regulator output. This pin shall shunt $10\mu F$   |

|    |       |   | capacitor and $0.1\mu F$ capacitor to the digital ground   |

|    |       |   | for the decoupling. Note that this pin shall not be        |

|    |       |   | connected with the external load.                          |

| 41 | RB    |   | Reserved. Shall be connected with DVCC.                    |

| 42 | PM    | I | Default operating mode select pin. PM = 1, select          |

|    |       |   | sleep mode (SLM). PM = 0, select measurement               |

|    |       |   | mode (EMM). This pin is internal floating and shall        |

|    |       |   | be pulled up with $1K\Omega$ resistor externally or        |

|    |       |   | connected with grounded.                                   |

| 43 | RC    |   | Reserved. Shall be connected with digital ground.          |

|    | •     |   |                                                            |

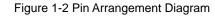

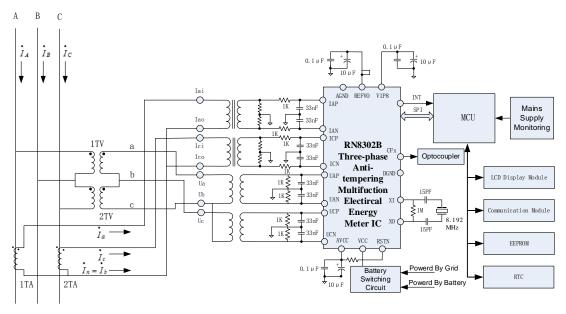

### **1.4 Typical Application**

Figure 1-3 Typical Application Circuit Schematic of Three-phase Four-wire Meter

Figure 1-4 Typical Application Circuit Schematic of Three-phase Three-wire Meter

#### 2.1 Power Supply Monitoring

The RN8302B contains an on-chip 3.3V analog power supply monitor supervises the power supply AVCC. When AVCC is lower than 2.70V under the room temperature, the RN8302B is reset globally. When AVCC is higher than 2.82V under the room temperature, the RN8302B operates normally.

#### 2.2 Operating Mode

The RN8302B is equipped with four operating mode, such as the measurement mode (EMM), **no-voltage** mode 1 (NVM1), no-voltage mode 2 (NVM2) and sleep mode (SLM).

- Measurement Mode (EMM): It is used to measure and meter various electrical parameter when the electrical energy meter operates in the power supply mode.

- No-voltage Mode 1 (NVM1): It is used to measure the low power no-voltage current RMS.

- No-voltage Mode 2 (NVM2): It is used to pre-judge the low power no-voltage current.

- Sleep Mode (SLM): It is used in the sleep status when the electrical energy meter is powered by the backup battery after the grid is powered down.

The power dissipated of each modes for RN8302B is shown as follows:

Table 2-1 Power Dissipated in Each Operating Modes

| Measuring  | Symb             | Minim | Турі | Maxim | Unit | Test Condition |

|------------|------------------|-------|------|-------|------|----------------|

| Items      | ol               | um    | cal  | um    |      |                |

| Power      |                  |       |      |       |      | fosc=8.192MHz  |

| Dissipated | Іемм             |       | 5    |       | mA   |                |

| (EMM)      |                  |       |      |       |      |                |

| Power      |                  |       |      |       |      | fosc=8.192MHz  |

| Dissipated | INVM1            |       | 2    |       | mA   |                |

| (NVM1)     |                  |       |      |       |      |                |

| Power      |                  |       |      |       |      |                |

| Dissipated | NVM2             |       | 150  |       | μA   |                |

| (NVM2)     |                  |       |      |       |      |                |

| Power      |                  |       |      |       |      |                |

| Dissipated | I <sub>SLM</sub> |       | 2    |       | μA   |                |

| (SLM)      |                  |       |      |       |      |                |

(Room Temperature, AVCC= DVCC=3.3V)

The RN8302B operating mode is switched by the SPI command. For the mode switching command registers and the command words, refer to <u>Chapter 3.4.32</u>.

For the effect of the RN8302B mode switching on the register and the change, refer to <u>Chapter 3.5.4</u>. The bits of the system status register SYSSR (0x8A) WMS [1:0] indicate current operating mode of RN8302B.

The system default mode can be configured as SLM or EMM by the PM pin after RN8302B is power-on reset. Refer to <u>Chapter 1.4</u>. The bit of the system status register SYSSR (0x8A) PM indicates current operating mode of RN8302B.

For the details on the SYSSR (0x8A) register, refer to Chapter 3.4.36.

#### 2.3 System Reset

RN8302B supports the following reset mode:

- Power-up and power-down reset

- External pin reset

- Software reset

- Wake-up reset

The power-up and power-down reset is the global reset, and other reset modes are the local reset. Upon completion of the reset, the reset flag bit of the system status register SYSR (B1 0x8A) changes. For the concrete description of the reset flag bit, refer to Chapter 3.4.36 Register.

#### 1. Power-up and Power-down Reset

After the power-up and power-down reset has occurred, the system is reset to the default mode SLM or EMM that is configured by the PM pin. The register is reset to the initial value in the default operating mode. The external pin level is reset to the initial state. For the details on the power-up and power-down reset register, refer to <u>Chapter 3.5.1</u>.

#### 2. External Pin Reset

When the system is in the SLM mode, the external pin reset is invalid. When the system is in the EMM, NVM1 and NVM2 mode, the external pin reset is valid. After the external pin reset has occurred, the current operating mode of the system is constant, and only part of registers are reset to the initial value in this operating mode. For the details on the external pin reset register, refer to <u>Chapter 3.5.2</u>.

#### 3. Software Reset

For the details on the software reset command registers, refer to <u>Chapter 3.4.33</u>. When the system is in the SLM mode, the software reset is invalid. When the system is in the EMM, NVM1 and NVM2 mode, the software reset is valid. After the software reset has occurred, the current operating mode of the system is constant, and only part of registers are reset to the initial value in this operating mode. For the details on the external pin reset to register, refer to <u>Chapter 3.5.3</u>.

#### 4. Wake-up Reset

When SLM or NVM2 is switched to EMM or NVM1, the wake-up reset takes place. After the reset has occurred for 1.5ms, the register is reset to the initial value of the wake-up reset. For the details on the wake-up reset register, refer to <u>Chapter 3.5.4</u>.

#### 2.4 Measurement Mode

The measurement mode (EMM) is used to measure and meter various electrical parameters when the electrical energy meter operates in the power supply mode.

#### 2.4.1 Sampling Channel

The RN8302B sampling channel includes seven ADCs and the sampling data processing circuit.

Three of seven ADCs are used for phase current sampling, one of them is used for the neutral current sampling, and three of them are used for the voltage sampling. ADC takes the fully differential mode input, with the maximum input amplitude vpp is 800mVpp.

Configure PGA to amplify seven ADCs for 1/2/4/8 times respectively, and select whether the ADC reference voltage comes from the on-chip reference voltage or the external reference voltage. For the instruction for use of the ADCCFG register, refer to Chapter 3.4.34.

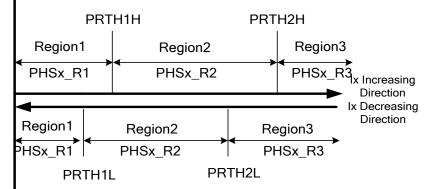

Carry out the channel phase calibration of seven ADCs by configuring the PHS register (B1 0x0C-0x12). For the instruction for use of the PHS register, refer to <u>Chapter 3.4.7</u> and <u>Chapter 4 Calibration</u>. Of which, the register PRTHx (B10x06-0x09) is set to implement the per-phase calibration of three current channels. For the details on the PRTHx register, refer to <u>Chapter 3.4.5</u>.

Carry out the channel gain calibration of seven ADCs by configuring the GS register (B1 0x13-0x19). For the instruction for use of the GS register, refer to <u>Chapter 3.4.8</u> and <u>Chapter 4 Calibration</u>.

Configure the high-pass filter enable and disable of seven sampling channels by configuring the HPFOFF [6:0] register in the EMUCFG register (B1 0x61).For the details on HPFOFF [6:0], refer to <u>Chapter 3.4.17 Register</u>.

Carry out the DC OFFSET calibration of seven ADCs by configuring DC\_OS register (B1 0x1A - 0x20). For the details on the DC\_OS register, refer to <u>Chapter 3.4.9</u>.

The real-time sampling data of seven ADCs for RN8302B is output to the waveform sampling register (B0 0x00-0x06). For the details on the waveform sampling register, refer to <u>Chapter 3.2.1</u>.

#### 2.4.2 Sampled Waveform Buffer

In addition to In, six 24bits ADC sample data can be stored to the on-chip waveform storage cell, to carry out the FFT analysis.

#### 1. Buffer Area Capacity

There are 768 address units in the buffer area, which can store the data of 128 points for six ADCs in one cycle, such as UA, UB, UC, IA, IB and IC.

#### 2. Address Mapping

1) Byte Length: There are three bytes for one address unit, which is used to store one sampling data of ADC.

2) Address Mapping: 768 address units with the address 200H-4FFH.

#### 3. Sampling Rate and Buffer Control

The waveform sampling rate can be configured by writing buffer control register WSAVECON (B1 0x63) under the condition of fosc = 8.192 Mhz. For 50Hz application, the waveform sampling rate is 6.4 KHz. For 60Hz application, the waveform sampling rate 7.699 KHz.

Whether the ADC data of each channels is written into the buffer and the arrangement mode in the buffer, the buffer size of each channels, enable/disable buffer and buffer status after the buffer is enabled are controlled by writing buffer control register WSAVECON (B1 0x63). For the details, refer to <u>Chapter 3.4.19</u>.

#### 4. SPI BURST Read Operation of Buffer

Users can read the buffer data by SPI. For the details on the read operation of the buffer SPI, refer to <u>Chapter 5 Communication Interface</u>.

When SPI reads the waveform buffer successfully for one time, the data buffer addresses read for the last time are stored in the waveform buffer address register LRBufAddr (B1 0x8E). For the details on the LRBufAddr register, refer to <u>Chapter 3.4.40</u>.

#### 5. Operating Mode and Waveform Buffer:

The waveform buffer in SLM, NVM2 and NVM1 is invalid. The waveform buffer RAM value is uncertain in the EMM mode after the power-up reset or the wake-up reset, write the value after write buffer or clear command. For the software reset and the hardware pin reset, the waveform buffer RAM value is constant.

#### 2.4.3 Active Power

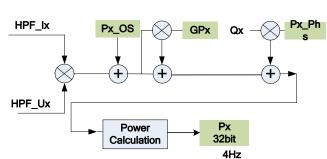

#### Figure 2-1 Per-Phase Active Power

#### 1. Per-phase Active Power

For the details on the per-phase active power Px (x = A, B, C, the same below) register, refer to Chapter 3.2.3.

As shown in the figure below, carry out the active power gain calibration by the register in the per-phase active power channel. For

the details on the GPx register, refer to Chapter 3.4.11.

Carry out the active power phase calibration by the Px\_PHS register in the per-phase active power channel. For the details on the Px\_PHS register, refer to <u>Chapter 3.4.12</u>.

Carry out the active power Offset calibration by the Px\_OS register in the per-phase active power channel. For the details on the Px\_OS register, refer to <u>Chapter 3.4.13</u>.

#### RN8302B

#### 2. All-phase sum Active Power

The average value of the all-phase sum active power register  $P_T$  (B0 0x17) is the algebraic sum of the average active power for each per-phase. For the details on the  $P_T$  register, refer to <u>Chapter 3.2.3</u>.

$P_T$  can be configured into the three-phase four-wire algorithm and the three-phase three-wire algorithm by selecting the register MODSEL (B1 0x86) in the three-phase four-wire and three-phase three-wire mode.

For the details on the MODSEL register, refer to Chapter 3.4.35.

If it is configured into the three-phase four-wire system,  $P_T = P_A + P_B + P_C$ .

If it is configured into the three-phase three-wire system, the power of phase B is not

calculated, so  $P_T = P_A + P_C$ .

#### 3. Fundamental Active Power

There is a set of the active power parameters and calibration registers which correspond to the total active power, and the fundamental power shares the MODSEL register with the total. For the details on the fundamental active power and calibration register, refer to Chapter <u>3.2.3, 3.4.11</u> - <u>3.4.13</u>. The fundamental filter can attenuate the harmonic power with the frequency 120Hz or higher.

#### 4. Active Power Direction

The total and fundamental active power orientation of the per-phase and all-phase sum is provided by the power orientationregister PQSign (0x66). For the details on the PQSign register, refer to <u>Chapter 3.4.21</u>. The PSIGNCfg [2:0] register in the <u>EMUCFG register</u> (B1 0x61) performs the sign reverse selection function of the PC/PB/PA/FPC/FPB/FPA active power.

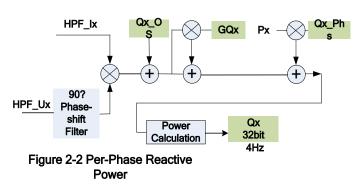

#### 2.4.3 Reactive Power

The RN8302B provides the total and fundamental per-phase reactive power and all-phase sum reactive power and provides the sign bit of the per-phase and the all-phase sum reactive power for the four quadrants judging. Furthermore, it provides the reactive power gain calibration,

phase calibration and Offset calibration register.

For the details on the reactive power and the calibration register, refer to <u>Chapter 3.2.2</u>, <u>3.4.11 - 3.4.13</u>. For the details on the power orientation register PQSign, refer to <u>Chapter</u> <u>3.4.21</u>. The QSIGNCfg [2:0] register in the <u>EMUCFG register</u> (B1 0x61) performs the sign

reverse selection function of the QC/QB/QA/FQC/FQB/FQA reactive power.

The all-phase sum reactive power can be configured into the three-phase four-wire mode and the three-phase three-wire mode by the MODSEL register.

The RN8302B reactive 90° phase shift Hilbert algorithm ensures it can provide excellent phase shift characteristic and amplitude-frequency response characteristic within the 0-51 harmonic range.

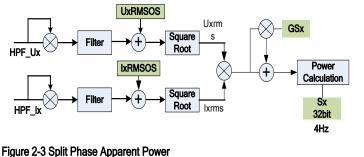

#### 2.4.5 Apparent Power

The RN8302B provides the total and fundamental apparent power of the per-phase and all-phase sum. Furthermore, it also provides

the gain calibration register of the apparent power.

For the details on the apparent power register, refer to <u>Chapter 3.2.3</u>. For the details on the power gain calibration register, refer to <u>Chapter 3.4.11</u>.

The per-phase apparent power takes the RMS method, namely,  $Sx = Uxrms^*Ixrms$ .

Where, Uxrms and Ixrms indicate the RMS value of phase x respectively. The all-phase sum apparent power can be configured into the three-phase four-wire mode and the three-phase three-wire mode by the MODSEL register.

#### 2.4.6 Energy Output

The RN8302B provides three energy output modes, such as the energy register, CF frequency output and fast pulse count Fcnt.

#### 1. Energy Register:

The RN8302B provides several types of the energy registers, including the total/fundamental active/reactive/apparent, per-phase/all-phase sum and forward/reverse energy register. For the details, refer to <u>Chapter 3.2.6 Energy Register</u>.

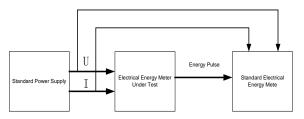

#### 2. Energy Pulse Output:

The all-phase sum pulse output, namely the Calibration Frequency output, can be connected with the standard electrical energy meter for the error comparison directly. The RN8302B provides four CF pins. For the definition of the CF pin, refer to <u>Chapter 1.4</u>.

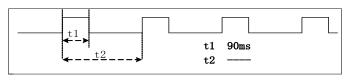

Each CF output meets the following timing.

Note: When the pulse output period is less than 180ms, the

pulse is output in the equal duty cycle way.

CF1 is the all-phase sum CF frequency output of the total active power, CF2 is the all-phase sum CF frequency output of the total reactive power, CF3 is the all-phase sum CF frequency output of the total apparent power, and CF4 is the all-phase sum CF frequency output of the fundamental active power. Each CF pin can be configured into the any all-phase sum pulse output of the total active all-phase sum, total reactive, total apparent, total active, fundamental reactive and fundamental apparent power flexibly by the CFCFG register (0x60) by default.

Each CF pin outputs the pulse by taking HFCONST1 as the high-frequency pulse constant, to synchronize the update of corresponding all-phase sum energy register by default. Each CF pin can take HFCONST2 as the high-frequency pulse constant to output the pulse by configuring the CFCFG register (0x60). At this time, if <u>HFCONST1</u> is not equal to <u>HFCONST2</u>, the CF pulse output doesn't synchronize with corresponding all-phase sum energy register update. This function can be used for measuring the maximum demand pulse.

For the CFCFG register, refer to <u>Chapter 3.4.16</u>. The <u>MODSEL register</u> is the three-phase four-wire mode by default.

Accordingly, the all-phase sum pulse output of each CF pin is also the three-phase four-wire mode. The <u>MODSEL register</u> is the three-phase four-wire mode by default. Accordingly, the all-phase sum pulse output of each CF pin is also the three-phase four-wire mode.

When the <u>MODSEL register</u> is the three-phase four-wire mode, configure the active all-phase sum energy cumulative mode in algebraic sum or absolute value sum mode by configuring the EPADDMOD register bit (EMUCFG.20). Accordingly, the all-phase sum pulse output cumulative mode of the active CF pin is also configured by the bit of the EPADDMOD register.

When the <u>MODSEL register</u> is the three-phase four-wire mode, configure the reactive all-phase sum energy cumulative in algebraic sum or absolute value sum mode by configuring the EPADDMOD register bit (EMUCFG.21). Accordingly, the all-phase sum pulse output cumulative mode of the reactive CF pin is also configured by the bit of the EPADDMOD register.

For the details on the EMUCFG register (B1 0x61), refer to Chapter 3.4.17.

If users require the per-phase pulse output during the calibration, configure which phases implement the all-phase sum operation by configuring the measurement control register EMUCON (B1 0x60). If users require CF1 outputs the active CF frequency of phase A only, configure PRUN0=1, PRUN1=0 and PRUN2=0 in EMUCON, phase B and C don't implement the all-phase sum operation, and the CF1 output pulse represents the active CF frequency of phase A.

For the details on the EMUCON register (B1 0x60), refer to Chapter 3.4.18.

#### 3. Fast Pulse Count Register:

The fast pulse count register includes the total/fundamental active/reactive/apparent and per-phase/all-phase sum fast pulse count register. For the details, refer to Chapter

#### <u>3.2.5</u>.

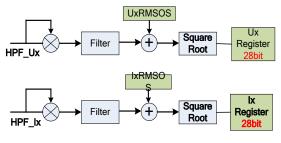

#### 2.4.7 Voltage RMS and Current RMS

#### 1. Total Voltage RMS and Current RMS

The total Voltage RMS includes the three-phase Voltage RMS UA, UB and UC. The total current RMS includes the three-phase current RMS IA, IB, IC and the neutral current RMS IN.

Figure 2-4 Voltage and Current RMS

Calibration of Voltage RMS and current RMS: ① Calibrate the gain by the channel gain register.② RMS OFFSET calibration. For the details, refer to Chapter 3.4.8 and 3.4.10 Register and Chapter 4 Calibration.

2. Fundamental Voltage RMS and Current RMS

The fundamental Voltage RMS includes the three-phase fundamental Voltage RMS FUA, FUB and FUC, and the fundamental current RMS includes the three-phase current RMS FIA, FIB and FIC.

In addition to output as the parameters, FUA, FUB and FUC are also taken as the criterion for the voltage <u>zero-crossing detection</u>, <u>voltage line frequency measurement</u> and <u>phase angle</u> threshold detection. In addition to output as the parameters, the current RMS FIA, FIB and FIC are also taken as the criterion for the <u>startup of each fundamental phases</u>, current <u>zero-crossing detection</u> and current <u>phase angle</u> threshold detection.

Calibration of Fundamental Voltage RMS and current RMS: ① Calibrate the gain by the channel gain register.② Fundamental RMS OFFSET calibration. For the details, refer to <u>Chapter 3.4.8</u> and <u>3.4.10 Register</u> and <u>Chapter 4 Calibration</u>.

#### 3. Harmonic Voltage RMS and Current RMS

The harmonic Voltage RMS includes the three-phase fundamental Voltage RMS HUA, HUB and HUC, and the harmonic current RMS includes the three-phase current RMS HIA, HIB and HIC.

The harmonic RMS can be used to calculate the harmonic content of voltage and current channel. The relationship among the harmonic Voltage RMS, total Voltage RMS and current RMS and fundamental Voltage RMS and current RMS is shown as follows:

$$HU_{X} = \sqrt{U_{X}^{2} - FU_{X}^{2}}; HI_{X} = \sqrt{I_{X}^{2} - FI_{X}^{2}}$$

4. Voltage Vector sum Voltage RMS

It is defined as follows:

$$U_{T} = \frac{1}{4} * \sqrt{\frac{1}{T} \int_{0}^{t} (u_{A}(t) + u_{B}(t) + u_{C}(t))^{2} dt}$$

Where,  $u_A(t)$ ,  $u_B(t)$  and  $u_C(t)$  are the sampling value of each voltage channel ADCs.

#### ADCs.

#### 5. Current Vector sum Current RMS

There are two algorithms for the current vector sum current RMS, taking the three-phase four-wire system with the neutral current transformer and without the neutral current transformer into account.

Algorithm 1:

$$I_T = \frac{1}{4} * \sqrt{\frac{1}{T} \int_0^t (i_A(t) + i_B(t) + i_C(t))^2 dt}$$

Algorithm 2:

$$I_T = \frac{1}{4} * \sqrt{\frac{1}{T} \int_0^t (i_A(t) + i_B(t) + i_C(t) - i_N(t))^2 dt}$$

Where,  $i_A(t)$ ,  $i_B(t)$ ,  $i_C(t)$  and  $i_N(t)$  are the sampling value of various current

channel ADCs.

Which algorithm is taken is depended by the ISUMMOD bit in the measurement unit configuration register EMUCFG (B1 0x61).If ISUMMOD=0, take the algorithm 1. If ISUMMOD=1, take the algorithm 2.For the details on the ISUMMOD bit, refer to <u>Chapter</u> <u>3.4.17</u>.

The update cycle for above RMS data is 250ms.For the details on the RMS register, refer to Chapter 3.2.2.

#### 2.4.8 Startup and No-load Setting

The RN8302B takes current RMS as the criterion of the total active, reactive and apparent no-load and startup, and fundamental active, reactive and apparent no-load and startup.

For the total active, reactive and apparent no-load and startup function, the RN8302B provides the total current RMS- and fundamental current RMS-based criterion. Which criterion is taken is depended by the NoloadCFG bit in the measurement unit configuration register EMUCFG (B1 0x61).For the details on NoloadCFG, refer to <u>Chapter 3.4.17</u> Register.

For the fundamental active, reactive and apparent no-load and startup function, the RN8302B provides the fundamental current RMS-based criterion.

The RN8302B provides two startup current threshold registers. The total and fundamental active and apparent share one startup current threshold register IStart\_PS (B1 0x02), and the total and fundamental reactive share one startup current threshold register IStart\_Q (B1 0x03).For the details, refer to <u>Chapter 3.4.2 Startup Current Threshold</u> <u>Register</u>.

The RN8302B provides the no-load and startup judge result register Noload (B1 0x67),

to indicate the total active and apparent/total reactive/fundamental active and apparent/ fundamental reactive/fundamental apparent no-load status of each per-phase. For the details, refer to <u>Chapter 3.4.22 No-load Status Register</u>.

If the active, reactive or apparent energy of some phase are in the no-load staus, this phase stops measuring, the FCnt of this phase stops increasing, and the energy register of this phase stops increasing. Furthermore, this phase doesn't carry out the all-phase sum operation.

#### 2.4.9 Power Factor

The power factor register of RN8302B includes the total power factor PfA/PfB/PfC/PfT of the per-phase and all-phase sum, and the fundamental power factor FPfA/FPfB/FPfC/FPfT of the per-phase and all-phase sum.

$$PFx = \frac{P_x}{S}$$

Total Per-phase Power Factor:  $S_x$ . Where, x = a, b, c. Sx indicates the apparent power of each per-phase, and Px indicates the active power of each per-phase, which is the signed value.

Total All-phase sum Power Factor:  $PF_T = \frac{P_T}{S_T}$ . Where, x=a, b, c. ST indicates the

apparent power of each all-phase sum, and PT indicates the active power of each all-phase sum, which is the signed value.

The fundamental power factor is calculated by the fundamental active and fundamental apparent power parameters, and the calculation method is the same as that of the total.

For the details on the power factor register, refer to Chapter 3.2.4.

#### 2.4.10 Phase Angle

The RN8302B performs the function of phase angle measurement among seven fundamental energys. For the description and usage of seven phase angle registers YUA, YUB, YUC, YIA, YIB, YIC and YIN, refer to <u>Chapter 3.2.7</u>.

For the rated input (Un=220mV, Ib=50mV), the phase angle resolution of RN8302B is less than 0.02°.

#### 2.4.11 Voltage Line Frequency

The RN8302B performs the function of the voltage line frequency measurement. For the details on the voltage line frequency register UFeq (B0 0x57), refer to <u>Chapter 3.2.8</u> Register. The resolution of the voltage line frequency is up to 0.0001Hz, and the measuring accuracy is up to 0.02%.

#### 2.4.12 Zero-crossing Detection

The RN8302B performs the forward zero-crossing function of the voltage and current waveform for seven fundamental energyss.

The RN8302B provides the voltage and current zero-crossing threshold register ZXOT (B1 0x05). If this fundamental Voltage RMS and current RMS is less than the ZXOT threshold, this zero-crossing current is not output. For the details on the ZXOT register, refer to <u>Chapter 3.4.4</u>.

The RN8302B provides seven zero-crossing interrupt outputs to the INT pin. For the details on the zero-crossing interrupt enable and flag register, refer to <u>Chapter 3.4.20</u> and <u>2.6 Interrupt</u>.

#### 2.4.13 Loss of Voltage Detection

The RN8302B provides the loss of voltage threshold register LostVoltage (0x04) and the loss of voltage state flag bit LostVoltSA, LostVoltSB and LostVoltSC (B1 0x69.0-2) of each phase for the loss of voltage detection.

The loss of voltage threshold register LostVoltage (B1 0x04) is used to set the loss of voltage threshold of RN8302B.For the details, refer to <u>Chapter 3.4.3</u> Register.

The loss of voltage state flag bit LostVoltSA, LostVoltSB and LostVoltSC indicate the loss of voltage judgment result of each phase. For the details on the criterion and flag bit, refer to <u>Chapter 3.4.24</u>.

#### 2.4.14 Voltage Phase Sequence Detection

The RN8302B performs the function of the voltage phase sequence error detection, and the voltage phase sequence error flag bit UPhSqErr (B1 0x69.3) indicates the detection result. For the details on the voltage phase sequence error criterion and the flag bit UPhSqErr, refer to <u>Chapter 3.4.24</u>.

#### 2.4.15 Voltage Sag Detection

The RN8302B performs the function of the three-phase input voltage UA, UB and UC voltage sag detection.

Criterion of Voltage Sag Detection for Some Phase: If the high 16-bit of the peak absolute value for the voltage fundamental sample value of this phase is less than SAGLVL [15:0] and the duration is SAGCYC [7:0] half cycles, it is judged as this phase voltage is sag. Of which, SAGLVL [15:0] is the low 16-bit of the voltage sag threshold register SAGCFG (B1 0x58), and SAGCYC [7:0] is the high 8-bit of SAGCFG (B1 0x58).For the details on the SAGCFG register, refer to Chapter 3.4.14.

The voltage sag of some phase will cause the bit of the SAGUx (x=A, B, C) register for this phase in the PHASES register (B1 0x69) is set to 1, and the bit of the SAGIF register in the EMMIF register (B1 0x64) is set to 1. If SAGIE=1 in the EMMIE (B1 0x65) register, setting SAGIF to 1 will interrupt INT. It will clear this interrupt when clear SAGIF. At the same time, it will clear the SAGUx flag in the PHASES register.

For the details on the PHASES register, refer to <u>Chapter 3.4.24</u>.For the details on the bit of the SAGIE register and the bit of the SAGIF register, refer to <u>Chapter 3.4.20</u> and <u>2.6</u> <u>Interrupt</u>.

#### 2.4.16 Overvoltage and Overcurrent Detection

The RN8302B performs the overvoltage and overcurrent judging function of the three-phase input voltage and current.

Criterion of OverVoltage for Some Phase: When the high 16-bit of the absolute value for the voltage sample value of some phase is greater than the overvoltage threshold register OVLVL (0x59), it judges the voltage of this phase is overvoltage. For the details on the OVLVL register, refer to <u>Chapter 3.4.15</u>.

The overvoltage of some phase will cause the bit of the OVUx (x=A, B, C) register for this phase in the PHASES register (B1 0x69) is set to 1, and the bit of the OVIIF register in the EMMIF register is set to 1. If OVIIE=1 in the EMMIE register, setting OVIIF to 1 will cause the interrupt. It will clear this interrupt when clear OVIIF. At the same time, it will clear the OVUx flag in the PHASES register.

Criterion of OverCurrent for Some Phase: When the high 16-bit of the absolute value for the current sample value of some phase is greater than the overcurrent threshold register OILVL (0x60), it judges the current of this phase is overcurrent. For the details on the OVLIL register, refer to <u>Chapter 3.4.15</u>.

The overcurrent of some phase will cause the bit of the OVIx (x=A, B, C) register for this phase in the PHASES register (B1 0x69) is set to 1, and the bit of the OVIIF register in the EMMIF register is set to 1. If OVIIE=1 in the EMMIE register, setting OVIIF to 1 will cause the interrupt. It will clear this interrupt when clear OVIIF. At the same time, it will clear the OVIx flag in the PHASES register.

For the details on the PHASES register, refer to <u>Chapter 3.4.24</u>.For the details on the bit of the OVIIE register and the bit of the OVIIF register, refer to <u>Chapter 3.4.20</u> and <u>2.6</u> <u>Interrupt</u>.

#### 2.4.17 Transformer Open-circuit and Short-circuit Detection at Secondary Side

The RN8302B supports the proprietary Renergy transformer open-circuit and short-circuit detection function at the secondary side. For the details, refer to the application note **RN8302B Transformer Open-circuit and Short-circuit Detection Function at Secondary Side**.

#### 2.5 Low Power Mode

The RN8302B provides the no-voltage mode 1 (NVM1) to measure the low power current RMS and the no-voltage mode 2 (NVM2) to pre-judge the low power no-voltage current, and judges the no-voltage accurately by current RMS. Furthermore, it will Supplies sleep mode (SLM), which is used in the sleep status when the electrical energy meter is powered by the backup battery after the grid is powered down.

Users can combine with NVM1, NVM2 and SLM, to complete each phase currents judgment and the current RMS measurement of the **no-voltage**. For the details, refer to the application note RN8302B No-voltage Measurement Function.

#### 2.5.1 No-voltage Mode 1

The no-voltage mode 1 (NVM1) is used to measure the low power current RMS and judge the no-voltage accurately by current RMS.

The RN8302B includes the three-phase current RMS measurement unit under the NVM1 mode, and the result is output to the three-phase current RMS register IA\_NVM1, IB\_NVM1 and IC\_NVM1 under the NVM1 mode. For the details on the register, refer to Chapter 3.2.2.

The error over the 400:1 range of the current RMS in the NVM1 mode is less than 0.5%.

This chip writes the GONVM1 command into the operating mode switching register (0x81) in the Write Enable condition in other operating modes, and the RN8302B is switched to NVM1 automatically and starts to calculate current RMS. The update cycle of the current RMS register in the NVM1 mode is 125ms. The current RMS register value is stable within 1.6s after the switching, and then users can read the current RMS register to judge the no-voltage.

The NVM1CFG register (0x70) configures the Interrupt Enable closure in the NVM1 mode. The NVM1IF register (0x71) NVM1Done is set after the switching. If NVM1IE=1, it will cause the interrupt. For the details on the NVM1CFG register, refer to <u>Chapter</u> <u>3.4.26</u>.For the details on the NVM1IF register, refer to <u>Chapter 3.4.27</u>.

#### 2.5.2 No-voltage Mode 2

The no-voltage mode 2 (NVM2) is used to pre-judge the low power no-voltage current.

The RN8302B includes the three-phase current comparison unit in the NVM2 mode, to compare the three-phase input current and the comparison unit threshold. Two levels of the comparison unit threshold are optional and can be configured by the bit of the NVM2TH [1:0] register in the NVM2CFG register (0x72).

The RN8302B can configure the current comparison cycle in the NVM2 mode by the bit

of the NVM2TNUM[4:0] register in the NVM2CFG register (0x72).

RN8302B can configure the interrupt enable closure in the NVM2 mode by the bit of the NVM2IE register in the NVM2CFG register (0x72). For the details on the NVM2CFG register, refer to <u>Chapter 3.4.28</u>.

Three registers NVM2CMP A/B/C (0x73-75) are used to output and process three comparators in the NVM2 mode. It shall be initialized as 0x0000 during the normal use. For the details on the register, refer to <u>Chapter 3.4.29</u>.

After RN8302B configures above register in other operating modes (such as SLM, EMM and NVM1), write the GONVM2 command into the operating mode switching register (0x81) in the Write Enable condition. The RN8302B is switched to NVM2 automatically and enables the comparison of the three-phase input current for one time by the <u>NVM2CFG</u> <u>register</u> configuration. The comparison result is stored in the NVM2IF register (0x76) after NVM2TNUM [4:0] + 1 cycles. If <u>NVM2IE</u>=1, the bit of the NVM2Done (NVM2IF.0) register is set upon completion of the comparison of the three-phase input current and causes the interrupt. For the details on the NVM2IF register, refer to <u>Chapter 3.4.30</u> and <u>2.6</u>.

#### 2.5.3 Sleep Mode

The SPI and AVCC power supply monitoring operate only in the sleep mode, and users can read and write NVM1, NVM2 and System Configuration and Status Register by SPI.

When the external pin  $\underline{PM}$  is configured to 1 and power-up reset, the system is in the SLM mode.

After the GOEMM, GONVM1 and GONVM2 command are written into the <u>Operating</u> <u>Mode Switching Register</u> (0x81) in the SLM mode in the Write Enable condition, The RN8302B is switched to EMM, NVM1 and NVM2 automatically.

After the GOSLM command are written into the <u>Operating Mode Switching Register</u> (0x81) in other operating modes in the Write Enable condition, switch to SLM automatically.

#### 2.6 Interrupt

| Ν          | Interrupt   | Description                                | Interrupt | Interrupt |

|------------|-------------|--------------------------------------------|-----------|-----------|

| <b>o</b> : |             |                                            | Enable    | Flag      |

| 15         | Overvoltage | When any phase of the three-phase          | OVIIE     | OVIIF     |

|            | and         | voltage is overvoltage or any phase of the |           |           |

|            | Overcurrent | three-phase current is overcurrent, OVIIF  |           |           |

|            | Interrupt   | is set to 1.If OVIE = 1, it will cause the |           |           |

|            |             | INTN pin is toggled from high to low.      |           |           |

|            |             | OVIIF writes 1 and clears 0, and clears    |           |           |

|            |             | the interrupt and the OVUA, OVUB,          |           |           |

Table 2-6-1: Interrupt in EMM Mode of RN8302B

The RN8302B interrupt is summarized as shown in the table below.

|    | RN8302B                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |            |  |  |  |

|----|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|--|--|--|

|    |                                                       | OVUC, OIIA, OIIB and OIIC status flag                                                                                                                                                                                                                                                                                                                                                                                                       |                |            |  |  |  |

|    |                                                       | bits in the PHASES status register.                                                                                                                                                                                                                                                                                                                                                                                                         |                |            |  |  |  |

| 14 | Voltage Sag<br>Interrupt                              | When any phase of the three-phase<br>voltage sags, SAGIF is set to 1.If SAGIE<br>= 1, it will cause the INTN pin is toggled<br>from high to low.<br>SAGIF writes 1 and clears 0, and clears<br>the interrupt and the SAGUA, SAGUB<br>and SAGUC status flag bits in the<br>PHASES status register.                                                                                                                                           | SAGIE          | SAGIF      |  |  |  |

| 13 | Status Change<br>Interrupt of<br>Current<br>Segment 3 | When any phase of current RMS for three<br>phases A/B/C changes compared to the<br>piecewise status set by<br>IRegion3H/IRegion3L, IRegion3IF is set<br>to 1.<br>Query the Regions register further, to<br>confirm which piecewise status of the<br>current RMS changes.<br>If IRegion3IE = 1, it will cause the INTN<br>pin is toggled from high to low.IRegion3IF<br>writes 1 and clears 0, and clears the<br>interrupt at the same time. | IRegion3I<br>E | IRegion3IF |  |  |  |

| 11 | CF4 Pulse<br>Output<br>Interrupt                      | CF4 outputs the pulse, and the output<br>changes into the high level from the low<br>level. CF4IF is set to 1.If CF4IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.<br>CF4IF writes 1 and clears 0.It clears 0<br>and clears interrupt simultaneously.                                                                                                                                                    | CF4IE          | CF4IF      |  |  |  |

| 10 | CF3 Pulse<br>Output<br>Interrupt                      | CF3 outputs the pulse, and the output<br>changes into the high level from the low<br>level. CF3IF is set to 1.If CF3IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.<br>CF3IF writes 1 and clears 0.It clears 0<br>and clears interrupt simultaneously.                                                                                                                                                    | CF3IE          | CF3IF      |  |  |  |

| 9  | CF2 Pulse<br>Output<br>Interrupt                      | CF2 outputs the pulse, and the output<br>changes into the high level from the low<br>level. CF2IF is set to 1.If C2IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.                                                                                                                                                                                                                                        | CF2IE          | CF2IF      |  |  |  |

| 8       CF1       Pulse<br>Output       CF1 outputs the pulse, and the output<br>changes into the high level from the low<br>level. CF1IF is set to 1.If C1IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.       CF1IE       CF1IE         7       IN       Forward       When IN > ZXOT and IN is forward<br>Zero-crossing       ZXINIF       ZXINIF         8       IC       Forward       When IN > ZXOT and IN is forward<br>Zero-crossing       ZXINIF       ZXINIF         7       IN       Forward       When IN > ZXOT and IN is forward<br>Zero-crossing       ZXINIF       ZXINIF         8       Interrupt       ZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.       ZXICIE       ZXICIF         6       IC       Forward       When IC > ZXOT and IC is forward<br>Zero-crossing       ZXICIF       ZXICIF         5       IB       Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF       ZXIBIF         5       IB       Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF       ZXIBIF         6       IA       Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF       ZXIBIF         7       IB       Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF       ZXIBI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | RN8302B       |                                               |        |        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|-----------------------------------------------|--------|--------|--|--|--|

| 8       CF1       Pulse       CF1 outputs the pulse, and the output changes into the high level from the low level. CF1IF is set to 1.If C1IE = 1, it will cause the INTN pin is toggled from high level to low level. CF1IF writes 1 and clears 0.It clears 0 and clears interrupt simultaneously.       CF1IE       ZXINIE         7       IN       Forward Zero-crossing Interrupt       When IN > ZXOT and IN is forward Zero-crossing ZXINIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXINI       ZXINIE       ZXINIE         6       IC       Forward When IC > ZXOT and IC is forward Zero-crossing ZXICIF is set to 1.If Lears 0 and clears interrupt simultaneously.       ZXICIE       ZXICIE         5       IB       Forward Zero-crossing ZXICIF writes 1, clears 0 and clears interrupt simultaneously.       ZXICIF writes 1, clears 0 and clears interrupt is toggled from high level to low level. ZXICIE       ZXICIE         5       IB       Forward Zero-crossing, ZXIEIF is set to 1.If ZXIBIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXICIF writes 1, clears 0 and clears interrupt simultaneously.       ZXIEIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXICIF         5       IB       Forward Zero-crossing ZXIBIF is set to 1.If ZXIBIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXIBIF       ZXIBIF         4       IA       Forward Zero-crossing ZXIAIF is set to 1.If ZXIAIE = 1, it will cause the INTN pin is toggled from high level to I.If ZXIAIE = 1, it will cause the INTN pin is toggled from high level to lo                                                                                                                                                                                                                                                                                                                                                                                                                      |   |               | CF2IF writes 1 and clears 0.It clears 0       |        |        |  |  |  |

| Output<br>Interruptchanges into the high level from the low<br>level. CF1IF is set to 1.If C1IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.<br>CF1IF writes 1 and clears 0.It clears 0<br>and clears interrupt simultaneously.ZXINIEZXINIE7IN<br>ForwardWhen IN > ZXOT and IN is forward<br>Zero-crossing<br>toggled from high level to low level.<br>ZEro-crossing<br>zero-crossing, ZXINIF is set to 1.If<br>InterruptZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXICIEZXINIE6IC<br>ForwardWhen IC > ZXOT and IC is forward<br>Zero-crossing, ZXICIF is set to 1.If<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF is set to 1.If<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXICIEZXICIE5IB<br>Zero-crossing<br>Zero-crossing<br>InterruptWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.If ZXIBIE<br>interrupt simultaneously.ZXIBIEZXIBIE5IB<br>ForwardWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.If ZXIBIE<br>interruptZXIBIFZXIBIF4IA<br>ForwardWhen IA > ZXOT and IA is forward<br>zero-crossing, ZXIAIF is set to 1.If ZXIAIE<br>imultaneously.ZXIAIEZXIAIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |               | and clears interrupt simultaneously.          |        |        |  |  |  |

| Interruptlevel. CF1IF is set to 1.If C1IE = 1, it will<br>cause the INTN pin is toggled from high<br>level to low level.<br>CF1IF writes 1 and clears 0.It clears 0<br>and clears interrupt simultaneously.ZXINIE7IN Forward<br>Zero-crossing<br>InterruptWhen IN > ZXOT and IN is forward<br>ZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXINIEZXINIE6IC Forward<br>Zero-crossing<br>InterruptWhen IC > ZXOT and IC is forward<br>Zero-crossing, ZXICIF is set to 1.If<br>ZEro-crossing<br>InterruptZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF is set to 1.If<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXICIEZXICIF5IB Forward<br>Zero-crossing<br>InterruptWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.If ZXIBIE<br>interrupt simultaneously.ZXIBIFZXIBIF4IA Forward<br>Zero-crossing<br>InterruptWhen IA > ZXOT and IA is forward<br>zero-crossing, ZXIAIF is set to 1.If ZXIAIE<br>imultaneously.ZXIAIEZXIAIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 | CF1 Pulse     | CF1 outputs the pulse, and the output         | CF1IE  | CF1IF  |  |  |  |

| Image: Section of the section of th |   | Output        | changes into the high level from the low      |        |        |  |  |  |

| Ievel to low level.       CF1IF writes 1 and clears 0.1t clears 0 and clears interrupt simultaneously.       ZXINIE         7       IN Forward       When IN > ZXOT and IN is forward Zero-crossing zero-crossing, ZXINIF is set to 1.1f Interrupt       ZXINIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXINI writes 1, clears 0 and clears interrupt simultaneously.       ZXICIE       ZXICIE         6       IC Forward       When IC > ZXOT and IC is forward Zero-crossing zero-crossing, ZXICIF is set to 1.1f Interrupt       ZXICIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXINI       ZXICIE         6       IC Forward       When IC > ZXOT and IC is forward Zero-crossing zero-crossing, ZXICIF is set to 1.1f Interrupt       ZXICIE = 1, it will cause the INTN pin is toggled from high level to low level. ZXICIF writes 1, clears 0 and clears interrupt simultaneously.       ZXIBIE       ZXIBIF         5       IB Forward When IB > ZXOT and IB is forward Zero-crossing zero-crossing, ZXIBIF is set to 1.1f ZXIBIE Interrupt       ZXIBIF is set to 1.1f ZXIBIE Interrupt       ZXIBIF         7       IN clears 0 and clears interrupt simultaneously.       ZXIBIF       ZXIBIF       ZXIBIF         5       IB Forward       When IB > ZXOT and IB is forward Interrupt simultaneously.       ZXIBIF       ZXIBIF       ZXIBIF         4       IA Forward When IA > ZXOT and IA is forward Zero-crossing ZIAIF       ZXIAIF is set to 1.1f ZXIAIE Interrupt Interrupt Interrupt Interrupt Interrupt Interrupt Interrupt Interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | Interrupt     | level. CF1IF is set to 1.If C1IE = 1, it will |        |        |  |  |  |

| Ievel to low level.<br>CF1IF writes 1 and clears 0.It clears 0<br>and clears interrupt simultaneously.ZXINIE7IN Forward<br>Zero-crossing<br>InterruptWhen IN > ZXOT and IN is forward<br>Zero-crossing, ZXINIF is set to 1.If<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXINIEZXINIF6IC Forward<br>Zero-crossing, ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>primet is inultaneously.ZXICIEZXICIE6IC Forward<br>Zero-crossing, ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXIBIEZXIBIE5IB Forward<br>Zero-crossing<br>Interrupt = 1, it will cause the INTN pin is toggled<br>from high level to low level.<br>ZXIBIF writes<br>1, clears 0 and clears interrupt<br>simultaneously.ZXIBIEZXIBIE4IA Forward<br>Zero-crossing<br>Interrupt = 1, it will cause the INTN pin is toggled<br>from high level to low level.<br>ZXIBIF is set to 1.If ZXIBIE<br>is multaneously.ZXIAIEZXIAIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |               | cause the INTN pin is toggled from high       |        |        |  |  |  |

| Image: section of the section of th |   |               | level to low level.                           |        |        |  |  |  |

| 7       IN Forward<br>Zero-crossing       When IN > ZXOT and IN is forward<br>zero-crossing, ZXINIF is set to 1.lf       ZXINIE       ZXINIE         1       Interrupt       ZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.       ZXICIE       ZXICIE         6       IC Forward<br>Zero-crossing       When IC > ZXOT and IC is forward<br>zero-crossing, ZXICIF is set to 1.lf       ZXICIE       ZXICIF         1       Interrupt       ZXICIF writes 1, clears 0 and clears<br>interrupt       Interrupt       ZXICIF       ZXICIF         5       IB Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF is set to 1.lf       ZXIBIE       ZXIBIF         5       IB Forward       When IB > ZXOT and IB is forward<br>Zero-crossing       ZXIBIF is set to 1.lf       ZXIBIE       ZXIBIF         4       IA Forward<br>IA Forward       When IA > ZXOT and IA is forward<br>Zero-crossing       ZXIAIF       ZXIAIF         4       IA Forward<br>Interrupt       = 1, it will cause the INTN pin is toggled       ZXIAIF       ZXIAIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |               | CF1IF writes 1 and clears 0.It clears 0       |        |        |  |  |  |

| Zero-crossing<br>Interruptzero-crossing, ZXINIF is set to 1.lf<br>ZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXICIEZXICIE6IC Forward<br>Zero-crossingWhen IC > ZXOT and IC is forward<br>zero-crossing, ZXICIF is set to 1.lf<br>InterruptZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXICIEZXICIF5IB Forward<br>Zero-crossingWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.lf ZXIBIE<br>interrupt simultaneously.ZXIBIF5IB Forward<br>InterruptWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.lf ZXIBIE<br>interruptZXIBIF4IA Forward<br>Zero-crossingWhen IA > ZXOT and IA is forward<br>zero-crossing, ZXIAIF is set to 1.lf ZXIAIE<br>imultaneously.ZXIAIEZXIAIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |               | and clears interrupt simultaneously.          |        |        |  |  |  |

| InterruptZXINIE = 1, it will cause the INTN pin is<br>toggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXICIE6IC Forward<br>Zero-crossing<br>InterruptWhen IC > ZXOT and IC is forward<br>ZXICIF is set to 1.If<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXICIEZXICIE5IB Forward<br>Zero-crossing<br>InterruptWhen IB > ZXOT and IB is forward<br>ZEro-crossing<br>Interrupt simultaneously.ZXIBIEZXIBIF5IB Forward<br>InterruptWhen IB > ZXOT and IB is forward<br>InterruptZXIBIF<br>ZERO-crossing<br>InterruptZXIBIF is set to 1.If ZXIBIE<br>InterruptZXIBIF<br>ZIBIF is set to 1.If ZXIBIE<br>InterruptZXIBIF<br>ZIBIF<br>ZIBIF is set to 1.If ZXIBIE<br>InterruptZXIAIE<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>InterruptZXIAIE<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>InterruptZXIAIE<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBIF<br>ZIBI                                                                                                                                                                                                                                                                                                                                                        | 7 | IN Forward    | When IN > ZXOT and IN is forward              | ZXINIE | ZXINIF |  |  |  |

| Image: Second systemtoggled from high level to low level. ZXINI<br>writes 1, clears 0 and clears interrupt<br>simultaneously.ZXICIEZXICIEInterruptIC Forward<br>Zero-crossing<br>InterruptWhen IC > ZXOT and IC is forward<br>ZXICIF is set to 1.If<br>ZXICIE = 1, it will cause the INTN pin is<br>toggled from high level to low level.<br>ZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXICIEZXICIFInterruptZXICIF writes 1, clears 0 and clears<br>interrupt simultaneously.ZXIBIEZXIBIEIB Forward<br>Zero-crossing<br>InterruptWhen IB > ZXOT and IB is forward<br>zero-crossing, ZXIBIF is set to 1.If ZXIBIE<br>from high level to low level. ZXIBIF<br>is imultaneously.ZXIBIEZXIBIFInterrupt= 1, it will cause the INTN pin is toggled<br>from high level to low level. ZXIBIF writes<br>1, clears 0 and clears interrupt<br>simultaneously.ZXIAIEZXIAIEIA Forward<br>Zero-crossing<br>Zero-crossing<br>InterruptWhen IA > ZXOT and IA is forward<br>zero-crossing<br>ZXIAIF is set to 1.If ZXIAIE<br>imultaneously.ZXIAIEZXIAIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | Zero-crossing | zero-crossing, ZXINIF is set to 1.If          |        |        |  |  |  |