# **User's Guide**

DX81C01 DX81C02 DX81C04 DX81C08 DX81C16 DX81C32 DX81C64 DX81C128 DX81C256

I2C/SPI Serial Security EEPROM With SHA1 Anti-Clone Authentication

Revision 2.3

**Chip For Security**

# Features

- A family of 9 devices with Security User EEPROM Memory from 1Kbits to 256Kbits

- --- DX81C01: 1Kbits DX81C02: 2Kbits

- --- DX81C04: 4Kbits DX81C08: 8Kbits

- --- DX81C16: 16Kbits DX81C32: 32Kbits

- --- DX81C64: 64Kbits DX81C128: 128Kbits

- ---- DX81C256: 256Kbits

- Secure authentication and validation device

- I2C Interface

- --- 1.0 MHz Compatibility for Fast Operation

- ---- Same Pinout as 2-wire (24 Series) Serial EEPROM's

- SPI Interface

- --- Compatibility for SPI Standard Protocol (Mode0 and 3)

- --- Max Speed up to 10MHz

- ---- Same Pinout as 4-wire (25 Series) EEPROM's

- Configuration Memory

- --- Guaranteed Unique 64bits Serial Number in wafer manufacture

- ---- 7-bytes OTP Area for User definable ID

- --- 64 bits User PIN authentication for memory configured

- EEPROM User Memory

- ---- Divided into 4 -- 16 User Zones

- --- Read only mode can be individually set for each zone

- --- PGO (program only) mode can be individually set for each zone

- --- Programmable Access Mode for each zone read/write

- Normal mode

- Authentication mode

- **Encryption mode**

- ---- 4 --- 16 individual 128 bits length Keys for each zone

- --- Individual bi-directional authentication for accessing each zone

- --- Single-Byte, Multiple-Byte or Page-Write Modes

- --- Self-timed Write Cycles

- Host Anti-Clone Authentication

- --- Superior SHA1 Hash Algorithm with MAC and HMAC options

- --- 128 bits Key length for authentication

- --- Each time random response even for the same challenge

- High security features in hardware

- --- Stream Encryption and CRC checking for Data transmission on Data Line Avoid capturing the real data on Data Line

- --- EEPROM Physical address Scramble with SN involved

- --- EEPROM Physical Data Encryption with SN involved Storing the same data in each device has different physical address and data.

- Prevent EEPROM Data from physically copying between devices.

- --- Internal and High-quality True Random Number Generator

- ---- Internal POR and High-accuracy Oscillator

- --- Voltage Monitor

- High reliability

- --- Endurance: >1M Cycles

- --- Data Retention: >10 years

- ---- ESD Protection: >4KV

- Operating Voltage: 2.0V—5.5V

- Temperature: -40°C --- +85°C

- < 2uA Sleep current

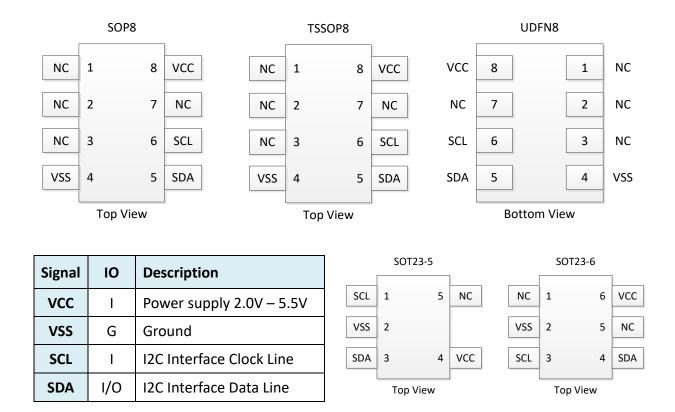

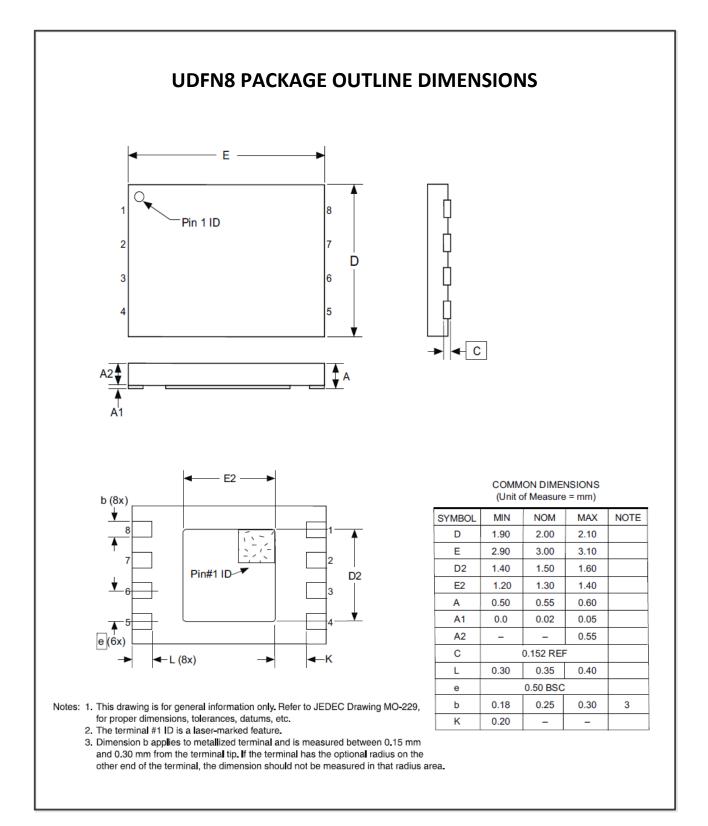

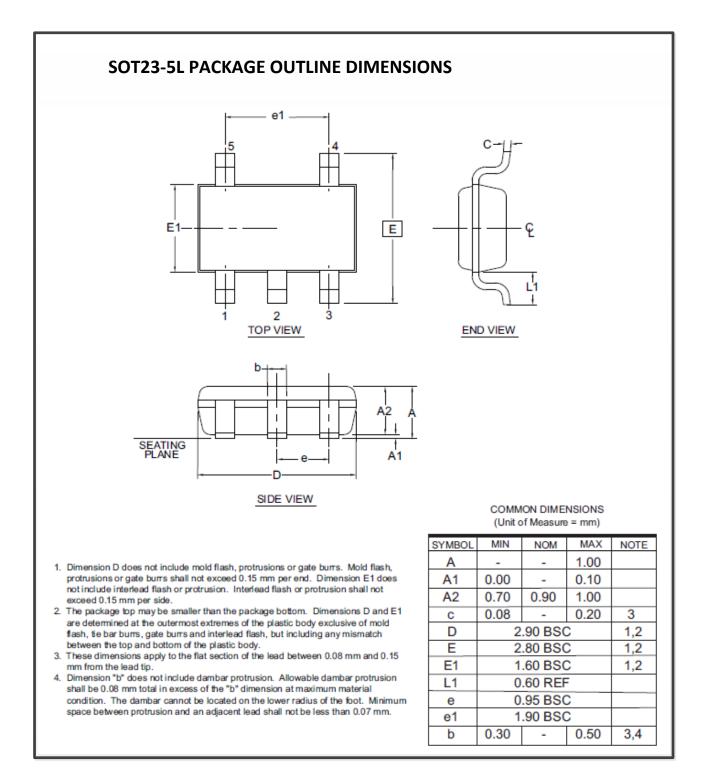

- Package: SOP8, TSSOP8, UDFN8, SOT23-5, SOT23-6

- Development Kits

- --- Evaluation Board Kits

- --- Customized Library and SDK for Android and iOS

- --- Secure Personalization device and software

- Applications

- --- Anti-Clone protection for accessories, peripherals and consumables

- --- Electronic device management of OEM/Post-sale Service/Authorization

- ---- Secure parameter/data storing

- ---- User Password Checking

- --- Software anti-piracy

- ---- PCB ID and Authentication

- --- Print-Cartridge ID

- --- Medical Consumable ID

- ---- STB, GPS, web camera system

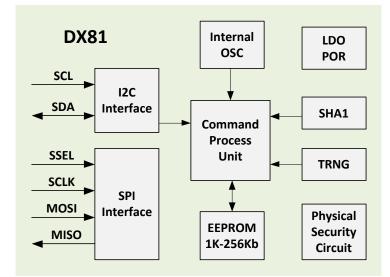

# Diagram

# **Package and PINs**

# I2C Interface

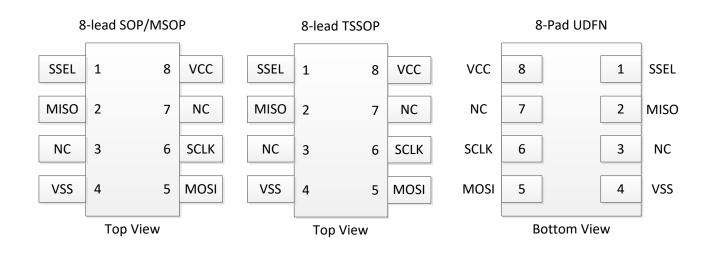

# **SPI Interface**

| Signal | ю | Description              |

|--------|---|--------------------------|

| VCC    | I | Power supply 2.0V – 5.5V |

| VSS    | G | Ground                   |

| SSEL   | I | Chip Select, Active Low  |

| SCLK   | I | SPI Clock Line           |

| MOSI   | I | Input data Line          |

| MISO   | 0 | Output data Line         |

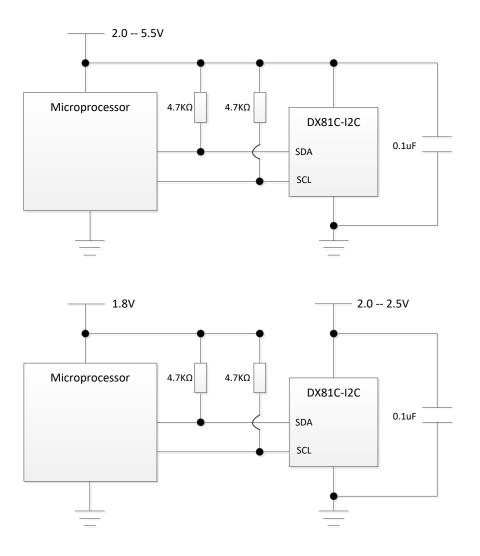

# **Typical Operation Circuit**

# **I2C Interface**

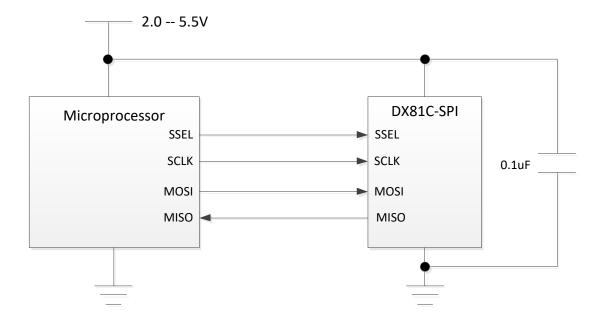

# **SPI Interface**

# **Order Information**

| Part       | EEPROM    | User<br>Zones | Zone<br>Size | Interface | Package Type                      |

|------------|-----------|---------------|--------------|-----------|-----------------------------------|

| DX81C01-C  | 1K bits   | 4             | 22 Dutos     | I2C       | SOP8/TSSOP8/UDFN8/SOT23-5/SOT23-6 |

| DX81C01-S  | IN DILS   | 4             | 32 Bytes     | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C02-C  | 2K bits   | 4             | 64 Putor     | I2C       | SOP8/TSSOP8/UDFN8/SOT23-5/SOT23-6 |

| DX81C02-S  |           | 4             | 64 Bytes     | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C04-C  | 4K bits   | 4             | 100 Dutoc    | I2C       | SOP8/TSSOP8/UDFN8/SOT23-5/SOT23-6 |

| DX81C04-S  | 4K DILS   | 4             | 128 Bytes    | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C08-C  | 8K bits   | 8             | 100 Dutos    | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C08-S  | OK DILS   | õ             | 128 Bytes    | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C16-C  | 16K bits  | 16            | 100 Dutos    | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C16-S  | TOK DILS  | 10            | 128 Bytes    | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C32-C  | 32K bits  | 16            | JEG Dutos    | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C32-S  | 32K DILS  | 10            | 256 Bytes    | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C64-C  | 64K bits  | 16            | E12 Dutoc    | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C64-S  |           | 10            | 512 Bytes    | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C128-C | 128K bits | 16            | 1K Dutos     | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C128-S | 128K DILS | 10            | 1K Bytes     | SPI       | SOP8/TSSOP8/UDFN8                 |

| DX81C256-C | 256K bits | 16            | 2K Putor     | I2C       | SOP8/TSSOP8/UDFN8                 |

| DX81C256-S | 230N DILS | 10            | 2K Bytes     | SPI       | SOP8/TSSOP8/UDFN8                 |

# Introduction

DX81 family is a secure EEPROM memory with high-security hardware authentication devices. It has a simple and flexible command set that allows use for many applications. DX81 family devices mainly have the following functions:

- Host anti-clone authentication

Validate that a removable, replaceable, or consumable Client is authentic. Example Clients could be printer ink tanks, electronic daughter cards, or other spare parts. It can also be used to validate a software/firmware module or memory storage element.

Password checking and varify authentication

- Password checking and verify authentication

Validate user entered passwords without letting the expected value become known, authenticate the access privilege for security memory.

#### • Secure User EEPROM memory

Device can store small quantities of data necessary for configuration, calibration, sensitive value, consumption data, or other secrets. It has programmable protection through encrypted/authenticated mode to read and write. Also you can permanently lock data prevented from modification.

All DX81 family devices include an EEPROM array that can be used for storage keys, miscellaneous read/write, read-only or secret data, consumption logging and security configuration. Access to the various zones of memory can be restricted in a programmable security accessing mode and the configuration then locked or prevented changes. Access to the device is through a standard I2C interface at speeds up to 1Mbps or SPI interface speeds up to 10Mbps, compatible with I2C/SPI interface specifications.

Each DX81 device ships with a guaranteed unique 8-bytes serial number, additional 7-bytes User ID can be set for the third party. Using the cryptographic protocols supported by the device, a Host system or remote server can prove that the SN and UID are both authentic and is not a copy. The unique ROM SN and User defined UID are used as a fundamental input parameter for cryptographic operations. Also each DX81 device ships with an initial PIN code, which can be used for DX81 configuration. Only the PIN authenticated, then you can personalize the DX81 device.

DX81 family devices can generate high-quality random numbers and employ them for any purpose, including as part of the crypto protocols of this device. And there are 128 bits key length KEYA for host anti-clone authentication and 4-16 Zone Keys for user memory accessing authentication or user password checking.

DX81 combines crypto-strong bidirectional secure challenge-and-responses authentication functional with an implementation using the industry-standard SHA-1 secure hash algorithm. A bidirectional security model enables tow-way authentication between a host system and slave-embedded DX81. Slave-to-host authentication is used by a host system to securely validate that attached or embedded DX81 is authentic. Host-to-slave authentication is used to protect DX81

user memory from being modified by a non-authentic host.

# **Device Interface Protocol**

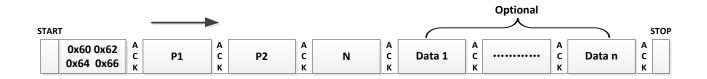

# **I2C Command Format**

#### **I2C RESET**

#### I2C\_READ

### **I2C\_WRITE**

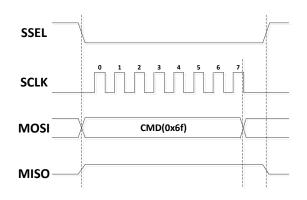

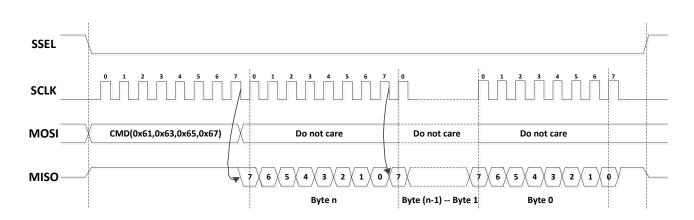

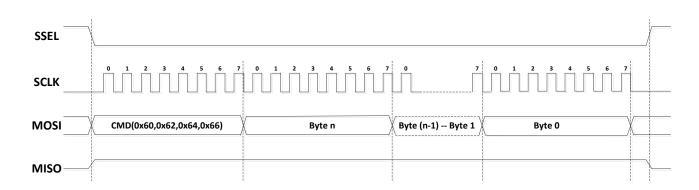

# **SPI Command Format**

#### SPI\_RESET

#### SPI\_READ

#### SPI\_WRITE

# **Device Memory**

# User Memory (DX81C01/02/04)

| Address     | DX81C01       | DX81C02        | DX81C04         |  |

|-------------|---------------|----------------|-----------------|--|

|             | (1K bits)     | (2K bits)      | (4K bits)       |  |

| 0x000—0x01f | Zone 0 (32 B) | Zone 0 (64 B)  |                 |  |

| 0x020—0x03f | Zone 1 (32 B) | 2011e 0 (04 B) | Zene () (129 B) |  |

| 0x0400x05f  | Zone 2 (32 B) | Zere 1 (C4 D)  | Zone 0 (128 B)  |  |

| 0x0600x07f  | Zone 3 (32 B) | Zone 1 (64 B)  |                 |  |

| 0x080—0x09f |               | 7000 2 (64 B)  |                 |  |

| 0x0a0—0x0bf |               | Zone 2 (64 B)  | 7000 1 (120 B)  |  |

| 0x0c0—0x0df |               | 7000 2 (64 P)  | Zone 1 (128 B)  |  |

| 0x0e0—0x0ff |               | Zone 3 (64 B)  |                 |  |

| 0x100—0x11f |               |                |                 |  |

| 0x120—0x13f | RSV           |                | 7000 2 (129 B)  |  |

| 0x1400x15f  | ĸsv           |                | Zone 2 (128 B)  |  |

| 0x1600x17f  |               | RSV            |                 |  |

| 0x1800x19f  |               | NOV            |                 |  |

| 0x1a00x1bf  |               |                | Zone 3 (128 B)  |  |

| 0x1c00x1df  |               |                | ZUIIE 2 (120 D) |  |

| 0x1e00x1ff  |               |                |                 |  |

Page Size: 16 bytes

# User Memory (DX81C08/16/32/64)

| Address       | DX81C08           | DX81C16         | DX81C32          | DX81C64        |  |

|---------------|-------------------|-----------------|------------------|----------------|--|

| Address       | (8K bits)         | (16K bits)      | (32K bits)       | (64K bits)     |  |

| 0x000-0x07f   | Zone 0 (128 B)    | Zone 0 (128 B)  | Zone 0 (256 B)   |                |  |

| 0x080-0x0ff   | Zone 1 (128 B)    | Zone 1 (128 B)  | 2011e 0 (250 B)  | Zone 0(512B)   |  |

| 0x100-0x17f   | Zone 2 (128 B)    | Zone 2 (128 B)  | Zone 1 (256 B)   | 20110 0(5128)  |  |

| 0x180-0x1ff   | Zone 3 (128 B)    | Zone 3 (128 B)  | 2011e I (250 B)  |                |  |

| 0x200-0x27f   | Zone 4 (128 B)    | Zone 4 (128 B)  | Zone 2 (256 B)   |                |  |

| 0x280-0x2ff   | Zone 5 (128 B)    | Zone 5 (128 B)  | 2011e 2 (250 B)  | Zone 1(512B)   |  |

| 0x300-0x37f   | Zone 6 (128 B)    | Zone 6 (128 B)  | Zone 3 (256 B)   | 2016 1(2120)   |  |

| 0x380-0x3ff   | Zone 7 (128 B)    | Zone 7 (128 B)  | 2011e 5 (250 B)  |                |  |

| 0x400-0x47f   |                   | Zone 8 (128 B)  | Zone 4 (256 B)   |                |  |

| 0x480-0x4ff   |                   | Zone 9 (128 B)  | ZONE 4 (250 B)   | 7000 2(E12P)   |  |

| 0x500-0x57f   | f Zone 10 (128 B) |                 | Zone 5 (256 B)   | Zone 2(512B)   |  |

| 0x580-0x5ff   |                   | Zone 11 (128 B) |                  |                |  |

| 0x600-0x67f   |                   | Zone 12 (128 B) | Zone 6 (256 B)   | – Zone 3(512B) |  |

| 0x680-0x6ff   |                   | Zone 13 (128 B) | ZONE 6 (250 B)   |                |  |

| 0x700-0x77f   |                   | Zone 14 (128 B) | Zone 7 (256 B)   | 20110 5(512B)  |  |

| 0x780-0x7ff   |                   | Zone 15 (128 B) | 2011e 7 (250 B)  |                |  |

|               |                   |                 |                  |                |  |

|               |                   |                 |                  |                |  |

|               |                   |                 |                  |                |  |

|               | RSV               |                 |                  |                |  |

| 0xe00-0xe7f   | N3V               |                 | Zone 14 (256 B)  |                |  |

| 0xe80-0xeff   |                   |                 | 2011e 14 (250 B) | Zone 7(512B)   |  |

| 0xf00-0xf7f   |                   |                 | Zone 15 (256 B)  | 20110 7(5128)  |  |

| 0xf80-0xfff   |                   | RSV             | Zone 13 (230 B)  |                |  |

|               |                   | NOV             |                  |                |  |

|               |                   |                 |                  |                |  |

|               |                   |                 |                  |                |  |

|               |                   |                 | DC//             |                |  |

| 0x1e00-0x1e7f |                   |                 | RSV              |                |  |

| 0x1e80-0x1eff |                   |                 |                  | 7              |  |

| 0x1f00-0x1f7f | D-0x1f7f          |                 |                  | Zone 15(512B)  |  |

| 0x1f80-0x1fff |                   |                 |                  |                |  |

Page Size: 32 bytes

# User Memory (DX81C128/256)

| مادانيم       | DX81C128       | DX81C256       |  |

|---------------|----------------|----------------|--|

| Address       | (128K bits)    | (256K bits)    |  |

| 0x0000-0x03ff | Zone 0 (1K B)  | 7000 0 (2)( 2) |  |

| 0x0400-0x07ff | Zone 1 (1K B)  | Zone 0 (2K B)  |  |

| 0x0800-0x0bff | Zone 2 (1K B)  | 7000 1 (2/ 0)  |  |

| 0x0c00-0x0fff | Zone 3 (1K B)  | Zone 1 (2K B)  |  |

| 0x1000-0x13ff | Zone 4 (1K B)  | 7ana 2 (2K B)  |  |

| 0x1400-0x17ff | Zone 5 (1K B)  | Zone 2 (2K B)  |  |

| 0x1800-0x1bff | Zone 6 (1K B)  | 7000 2 (2K P)  |  |

| 0x1c00-0x1fff | Zone 7 (1K B)  | Zone 3 (2K B)  |  |

| 0x2000-0x23ff | Zone 8 (1K B)  | 7000 4 (2K P)  |  |

| 0x2400-0x27ff | Zone 9 (1K B)  | Zone 4 (2K B)  |  |

| 0x2800-0x2bff | Zone 10 (1K B) | 7000 E (2K P)  |  |

| 0x2c00-0x2fff | Zone 11 (1K B) | Zone 5 (2K B)  |  |

| 0x3000-0x33ff | Zone 12 (1K B) | Zone 6 (2K B)  |  |

| 0x3400-0x37ff | Zone 13 (1K B) |                |  |

| 0x3800-0x3bff | Zone 14 (1K B) | Zone 7 (2K B)  |  |

| 0x3c00-0x3fff | Zone 15 (1K B) |                |  |

| 0x4000-0x43ff |                | Zone 8 (2K B)  |  |

| 0x4400-0x47ff |                |                |  |

| 0x4800-0x4bff |                | Zone 9 (2K B)  |  |

| 0x4c00-0x4fff |                |                |  |

| 0x5000-0x53ff |                | Zono 10 (2K B) |  |

| 0x5400-0x57ff |                | Zone 10 (2K B) |  |

| 0x5800-0x5bff |                | Zone 11 (2K B) |  |

| 0x5c00-0x5fff | RSV            |                |  |

| 0x6000-0x63ff | лэv            | Zono 12 (2K P) |  |

| 0x6400-0x67ff |                | Zone 12 (2K B) |  |

| 0x6800-0x6bff |                | Zono 12 (2K P) |  |

| 0x6c00-0x6fff |                | Zone 13 (2K B) |  |

| 0x7000-0x73ff |                | Zono 14 (2K D) |  |

| 0x7400-0x77ff |                | Zone 14 (2K B) |  |

| 0x7800-0x7bff |                | 7000 15 (0K D) |  |

| 0x7c00-0x7fff |                | Zone 15 (2K B) |  |

Page Size: 64 bytes

# **Configuration Memory**

| Address | <b>\$0</b> | \$1           | \$2                                       | \$3       | \$4 | \$5 | \$6   | \$7              | Description       |  |

|---------|------------|---------------|-------------------------------------------|-----------|-----|-----|-------|------------------|-------------------|--|

| \$00    |            | Serial Number |                                           |           |     |     |       |                  | ROM SN, Read Only |  |

| \$08    | FUSE       |               |                                           |           | UID |     |       |                  | FUSE and User ID  |  |

| \$10    |            |               | Manufact                                  | ture Code |     |     | ZKE   | YST              | Read Only         |  |

| \$18    | ZAMFE      | ZAMDC         | ZAMDC ZAMBA ZAM98 ZAM76 ZAM54 ZAM32 ZAM10 |           |     |     | ZAM10 | Zone Access Mode |                   |  |

| \$20    |            | iiiiii        |                                           |           |     |     |       |                  | Host Anti-Clone   |  |

| \$28    |            | ΚΕΥΑ          |                                           |           |     |     |       |                  | Authorization Key |  |

| \$30    |            | RSV           |                                           |           |     |     |       |                  | Reserved          |  |

| \$38    |            | PIN           |                                           |           |     |     |       |                  | User PIN          |  |

#### ROM SN (0x00--0x07)

The device's 64-bits Serial Number of ROM SN in wafer manufacture guarantees unique identification and can be used to electronically identify the equipment in which it is used. In addition to its important use as a unique data value participates in cryptographic computations.

#### FUSE (0x08)

FUSE byte is PGO (Program Only) lock byte, only can be programed from "1" to "0". If one FUSE bit changed to 0, it cannot be changed to 1 forever. Configuration bytes of UID, ZAM, KEYA and PIN, after blowing corresponding FUSE bit to zero, will be locked permanently and cannot be modified forever.

- Bit 7-5: Reserved

- Bit 4: UID: Modify UID(0x09—0x0f) enable, Active High

- Bit 3: ZAM: Modify ZAM(0x18—0x1f) enable, Active High

- Bit 2: KEYA: Modify KEYA(0x20—0x2f) enable, Active High

- Bit 1: Reserved

- Bit 0: PIN: Modify PIN(0x38—0x3f) enable, Active High

### ZKEYST (0x16--0x17)

ZKEYST bits always read only, indicates the setting status of each zone key. Setting one zone key successfully, after POR (Power On Reset) or RESET command, ZKEYST corresponding bit will be changed from 1 to 0 automatically. Once ZKEYST bit changed to zero, it indicates that the related zone key has been set and cannot be modified forever.

• Bit 15 -- 0: Zone 15 -- 0 Key setting flag

#### UID (0x09--0x0f)

It is 56 bits User identification which user defined during personalization. It is recommended that a unique identification number be assigned to each device, for example, QQ number or Telephone number, etc. This UID participates in cryptographic computation of authentication and encryption, will be locked after blowing FUSE.4 to zero.

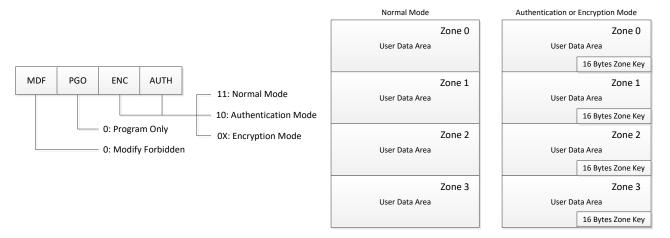

#### ZAM (0x18—0x1F)

8 bytes ZAM (Zone Access Mode) control the access manner of 16 user zones' reading and writing. All ZAM bits are PGO (program only) bit, only can be programed from "1" to "0" and irreversible from "0" to "1". Also all ZAM bits will be locked after blowing FUSE.3 to zero.

| Address      | Bits     | Zone Index | Zone Access Mode      |

|--------------|----------|------------|-----------------------|

|              | Bit[7:4] | 15         | {MDF, PGO, ENC, AUTH} |

| ZAMFE(0x18)  | Bit[3:0] | 14         | {MDF, PGO, ENC, AUTH} |

|              | Bit[7:4] | 13         | {MDF, PGO, ENC, AUTH} |

| ZAMDC(0x19)  | Bit[3:0] | 12         | {MDF, PGO, ENC, AUTH} |

|              | Bit[7:4] | 11         | {MDF, PGO, ENC, AUTH} |

| ZAMBA(0x1a)  | Bit[3:0] | 10         | {MDF, PGO, ENC, AUTH} |

| 741409(0v1b) | Bit[7:4] | 9          | {MDF, PGO, ENC, AUTH} |

| ZAM98(0x1b)  | Bit[3:0] | 8          | {MDF, PGO, ENC, AUTH} |

| ZAM76(0x1c)  | Bit[7:4] | 7          | {MDF, PGO, ENC, AUTH} |

|              | Bit[3:0] | 6          | {MDF, PGO, ENC, AUTH} |

| 74N4E4(0v1d) | Bit[7:4] | 5          | {MDF, PGO, ENC, AUTH} |

| ZAM54(0x1d)  | Bit[3:0] | 4          | {MDF, PGO, ENC, AUTH} |

| 741422(0v1e) | Bit[7:4] | 3          | {MDF, PGO, ENC, AUTH} |

| ZAM32(0x1e)  | Bit[3:0] | 2          | {MDF, PGO, ENC, AUTH} |

| 74N/10(0x1f) | Bit[7:4] | 1          | {MDF, PGO, ENC, AUTH} |

| ZAM10(0x1f)  | Bit[3:0] | 0          | {MDF, PGO, ENC, AUTH} |

- MDF: Modify forbidden, Active Low

- PGO: Program Only, Active Low

- {ENC, AUTH}: 11: normal mode 10: authentication mode 0X: encryption mode

#### KEYA (0x20—0x2f)

Host anti-clone authentication key, always cannot be read. Modifying KEYA is forbidden after blowing FUSE.2 to zero.

### PIN (0x38-0x3f)

User PIN, for authentication of writing configurations and zone keys. It also can be used to user password for checking. User PIN always cannot be read and modifying is forbidden after blowing FUSE.0 to zero.

# **Functional Description**

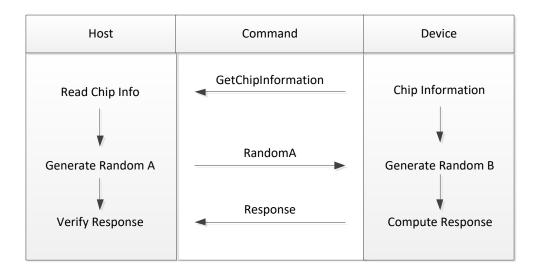

# Host anti-clone authentication

Host anti-clone authentication of DX81 supports a standard challenge-response protocol to simplify programing. At its most basic, the Host system sends a challenge of Random A to the device in the Client, then device will internally generates a true Random B and combines Random A/B, parts of Chip Information with a secret KEYA to calculate the response, after which the host gets the response from device.

The device uses a cryptographic hash algorithm for the combination, which prevents an observer on the bus from deriving the value of the secret KEYA, and allows the recipient to verify that the response is correct by performing the same calculation (combining the same parameters) with a stored copy of the secret KEYA.

Above authentication flow, The Random B of device generated is also combined for cryptographic hash calculation, at the same time parts of Random B sent to the host together with response. After the host got the random response, device firstly recovers the session key with parts of Random B, and then computes the correct response with the same manner as device. So the response host gets from DX81 is dynamic randomized at any time even if the same challenge, which can effectively prevent hacker from capturing the fixed bus data and simulating the response wave directly with

external general MCU to replace DX81 cryptographic calculation.

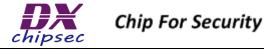

### Password checking and Verify Authentication

Each device includes 5 --17 passwords for authentication, one User PIN and 4 --16 Zone Keys, each user zone has an independent zone key. Only the User PIN authentication passed, configuration memory can be written, and only the Zone Key authentication passed, corresponding user zone can open the window to be accessed.

Firstly the host issues command to get random A, at the same time device temporarily stored the random A. Following random A command, the host must firstly compute the challenge A combined Random A with the stored copy of User PIN or Zone Key, and then send the challenge A together with host generating Random B to device.

Secondly when received challenge A and Random B, device will compute the challenge A at the same manner as host, and then compare with the receiving challenge A. If passed device will continuously compute challenge B and session key, or terminate command and refresh the Status Register.

Thirdly host gets challenge B from device, and then compares the response with own software calculation. If passed host will compute the session key for the following encrypt data transmission.

Verifying authentication realizes not only host authenticates device, but also device to host. Only passed the verification both host and device, the next operation is permitted and authorized.

### **User Memory Zone Access**

DX81 family devices have 4--16 user zones and each zone access is controlled by 4 bits (MDF, PGO, ENC, AUTH) . Following is access mode definition of each zone.

Writing and reading user zone must abide by the user zone access mode about ZAM's setting.

#### MDF

If one user zone's MDF set to zero, this zone will read only and cannot be written.

#### PGO

If one user zone's PGO set to zero, all bits of this zone will be PGO (Program Only) which only can be changed from 1 to 0, writing from 0 to 1 is no effect.

Before configuring one user zone to PGO (Program Only) mode, firstly you must guarantee all bytes of this zone are 0xff, or the AND logic in PGO mode will result in not your expected value.

#### ENC and AUTH

All user zones are default normal mode, and all bytes of one user zone are used to user data area, can be read and written freely. But once one user zone configured authentication or encryption mode, after POR or RESET command, this user zone will be divided into two parts, the last 16 bytes are Zone Key area and the other following rest bytes are user data area.

If one user zone configured authentication or encryption mode, Zone Key Area cannot be read forever. User Data Area, after this zone authenticated successfully, then can be read and written.

# **Electrical Characteristics**

# **Absolute Maximum Ratings**

| Parameter             | Min Max |                      | Unit |

|-----------------------|---------|----------------------|------|

| Supply Voltage        | 2.0     | 5.5                  | V    |

| Operating Temperature | -45     | +85                  | °C   |

| DC Output Current     | Ľ       | 5                    | mA   |

| Voltage on Any Pin    | -0.5    | V <sub>cc</sub> +0.5 | V    |

**Note:** Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Reliability

| Parameter                                        | Min | Typical | Max | Units        |

|--------------------------------------------------|-----|---------|-----|--------------|

| Write Endurance (each byte at 25 <sup>o</sup> C) | 1M  |         |     | Write Cycles |

| Data Retention (at 55 <sup>o</sup> C)            | 10  |         |     | Years        |

# **DC Electrical Characteristic**

| Symbol          | Parameter <sup>[1]</sup> | Min.                  | Тур | Max.                  | Unit | Notes                                         |

|-----------------|--------------------------|-----------------------|-----|-----------------------|------|-----------------------------------------------|

| To              | Operating Temperature    | -45                   |     | 85                    | °C   |                                               |

| V <sub>cc</sub> | Supply Voltage           | 2.0                   | 3.3 | 5.5                   | V    |                                               |

| Icc             | Supply Current           |                       |     | 3                     | mA   | V <sub>CC</sub> = 3.3V, T <sub>A</sub> = 25°C |

|                 |                          |                       |     |                       |      | Device in Sleep mode                          |

|                 |                          |                       |     |                       |      | I2C Interface:                                |

|                 |                          |                       |     |                       |      | SCL and SDA to $V_{\text{CC}}$                |

| I <sub>SB</sub> | Standby Current          |                       |     | 2                     | uA   | SPI Interface:                                |

|                 |                          |                       |     |                       |      | SSEL to $V_{CC}$ ,                            |

|                 |                          |                       |     |                       |      | SCLK, MOSI to GND                             |

|                 |                          |                       |     |                       |      | V <sub>CC</sub> = 2.0V, T <sub>A</sub> = 25°C |

| Vol             | Output Low Voltage       |                       |     | 0.4                   | V    | V <sub>CC</sub> = 3.3V I <sub>OL</sub> =2.1mA |

| V <sub>OH</sub> | Output High Voltage      | Vcc-0.5               |     |                       | V    | I <sub>OH</sub> =400uA                        |

| VIH             | Input High Voltage       | 0.7 * V <sub>CC</sub> |     | VCC+0.5               | V    |                                               |

| VIL             | Input Low Voltage        | -0.7                  |     | 0.3 * V <sub>CC</sub> | V    |                                               |

[1] The parameters are characterized but not 100% tested.

### **AC Electrical Characteristic**

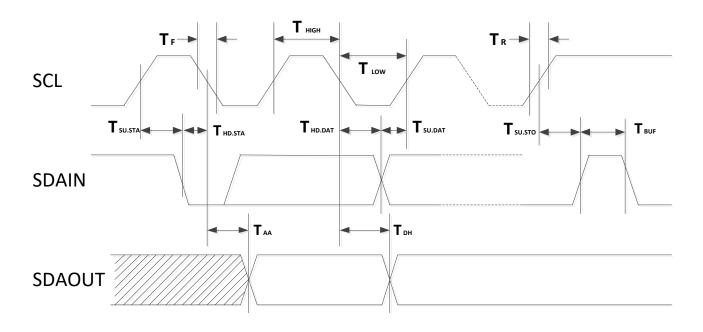

#### **I2C** Timing

#### Industrial: $T_A = -40^{\circ}C \text{ to} + 85^{\circ}C$ , $V_{CC} = 2.0 \approx 5.5V$

| Symbol              | Parameter <sup>[1] [2]</sup>                | Min. | Max. | Unit |

|---------------------|---------------------------------------------|------|------|------|

| F <sub>SCL</sub>    | SCL Clock Frequency                         |      | 1    | MHz  |

| T <sub>LOW</sub>    | SCL Clock Low Period                        | 400  |      | ns   |

| T <sub>HIGH</sub>   | SCL Clock High Period                       | 400  |      | ns   |

| T <sub>SU:STA</sub> | Start Condition Setup Time                  | 250  |      | ns   |

| T <sub>HD:STA</sub> | Start Condition Hold Time                   | 250  |      | ns   |

| T <sub>SU:STO</sub> | Stop Condition Setup Time                   | 250  |      | ns   |

| T <sub>SU:DAT</sub> | Data In Setup Time                          | 100  |      | ns   |

| T <sub>HD:DAT</sub> | Data In Hold Time                           | 10   |      | ns   |

| T <sub>R</sub>      | Rise Time (SCL and SDA)                     |      | 300  | ns   |

| TF                  | Fall Time (SCL and SDA)                     |      | 100  | ns   |

| T <sub>AA</sub>     | SCL Clock Low to SDA Data Out Valid Time    | 50   | 400  | ns   |

| T <sub>DH</sub>     | Data Out Hold Time                          | 50   |      | ns   |

| T <sub>WR</sub>     | Write Cycle Time                            |      | 4    | ms   |

| T <sub>BUF</sub>    | Bus Free Time Before New Transmission Start | 500  |      | ns   |

[1] The parameters are characterized but not 100% tested.

[2] AC measurement conditions:

RL (connects to VCC):  $1.3k\Omega$  (2.0V--5.0V); Input rise and fall times:  $\leq$  50 ns; Input pulse voltages: 0.3\*V<sub>CC</sub> to 0.7\*V<sub>CC</sub>;

times:  $\leq$  50 ns; Timing ref

Timing reference voltages: half V<sub>CC</sub> level;

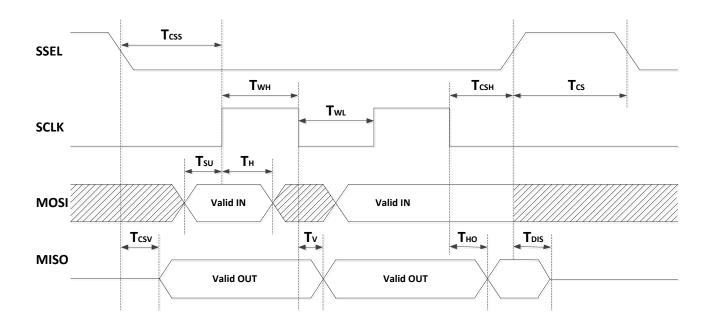

#### **SPI** Timing

#### Industrial: $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{CC} = 2.0 \approx 5.5V$

| Symbol           | Parameter <sup>[1] [2]</sup>      | Min. | Max. | Unit    |

|------------------|-----------------------------------|------|------|---------|

| -                | SCLK Clock Frequency              |      | 10   | MHz     |

| FSCLK            | SCLK Clock Duty Cycle             | 35   | 65   | Percent |

| Т <sub>WH</sub>  | SCLK Clock HIGH Time              | 12   |      | ns      |

| T <sub>WL</sub>  | SCLK Clock LOW Time               | 12   |      | ns      |

| T <sub>CS</sub>  | SSEL HIGH Time                    | 50   |      | ns      |

| T <sub>CSS</sub> | SSEL to SCLK Rising Setup Time    | 20   |      | ns      |

| T <sub>CSH</sub> | SSEL to SCLK Falling Hold Time    | 20   |      |         |

| T <sub>CSV</sub> | SSEL to MISO Valid Time           | 10   |      | ns      |

| Tsu              | Data In to SCLK Rising Setup Time | 8    |      | ns      |

| Тн               | Data In to SCLK Rising Hold Time  | 8    |      | ns      |

| T <sub>RI</sub>  | Input Rise Time                   |      | 1    | us      |

| T <sub>FI</sub>  | Input Fall Time                   |      | 1    | us      |

| Τv               | SCLK falling to MISO valid Time   | 0    | 10   | ns      |

| Т <sub>но</sub>  | MISO to SSEL HIGH Hold Time       | 0    |      | ns      |

| T <sub>DIS</sub> | MISO Output Disable Time          |      | 20   | ns      |

[1] The parameters are characterized but not 100% tested.

[2] AC measurement conditions:

RL (connects to VCC):  $1.3k\Omega$  (2.0V--5.0V);

Input rise and fall times:  $\leq$  50 ns;

Input pulse voltages: 0.3\*V<sub>CC</sub> to 0.7\*V<sub>CC</sub>;

Timing reference voltages: half  $V_{CC}$  level;

Chip For Security

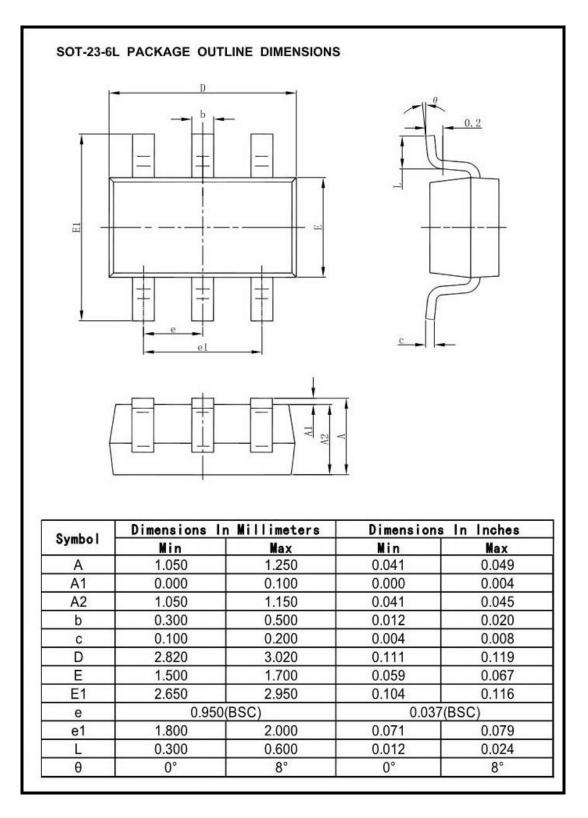

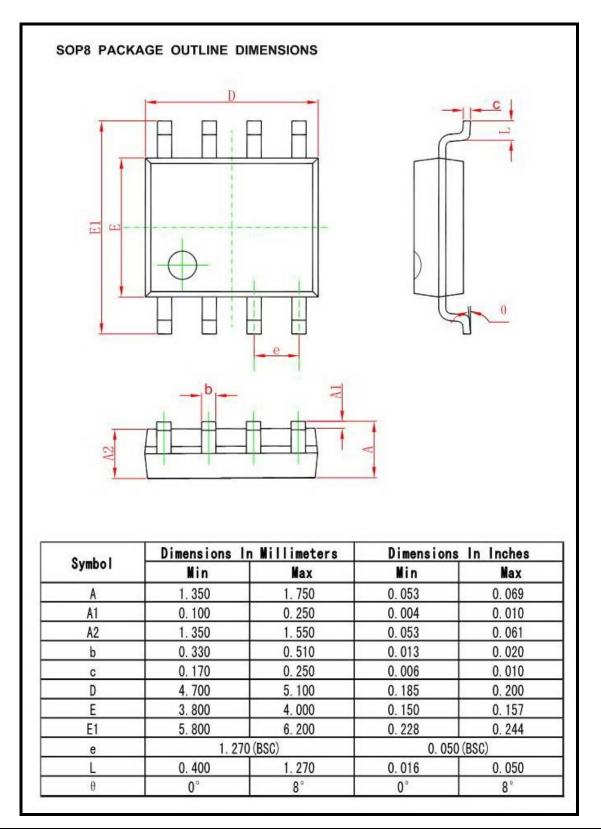

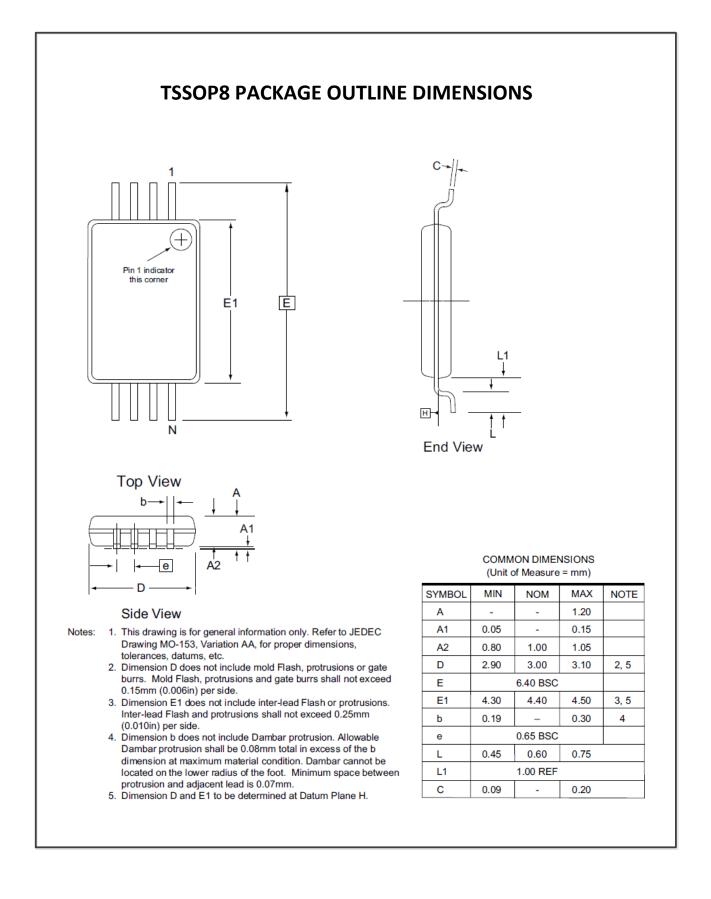

# Package Drawing

### SOP8

### TSSOP8

### UDFN8

### SOT23-5

### SOT23-6