Datasheet

NNC-*EPC001*

# HIGHLY INTEGRATED EEG/ECG/EMG/PPG BIO ELECTRIC SENSOR RISC-V SOC

NNC-EPC001

#### Datasheet

NNC-EPC001

## Features

- Operating Voltage Range: 2.5V to 5V

- Operating Temperature Range: -40°C to 125°C

- Support SIP with BLE DIE

- Power management

- Low power modes: Sleep and Stop modes

- RISC-V core

- 2-pipeline stage

- support branch predictor and prefetch

- support RV32I/E/M/A/C instruction

- Dhrystone 1.41, Coremark 3.34

- support 32-bit ILM and DLM

- support icache

- Memories

- 256kB on-chip FLASH

- 64kB ROM

- 64kB SRAM

- Digital Interfaces

- Quad-SPI FLASH interface

- 2 x UART, with hardware flow control

- 2 x I2C, with hardware flow control

- 2 x I2S, with hardware flow control

- 3 x SPI interfaces

- Digital Function

- 2 x General purpose timers

- Dual timer & watchdog function

- PWM, with hardware flow control

- RTC, with hardware flow control

- DMA, with hardware flow control

- EEG/ECG/EMG signal chain

- Standalone ECG acquisition up to 32 kHz

- Programmable INA gain: 1 to 100

- Input noise: <2.5µVrms (BW=0.1~100HZ, GAIN=6)

- PGA+24BITS ADC AFE

- AC, DC lead-off detect

- RLD driver

- Digital filter:

- -- HPF: 0.25/0.5/1/2.5/10/15/20/25Hz

- -- LPF: 9-11/15-20/25/50/100/150/200/350Hz

- -- Notch: 50Hz

- PPG receiver

- 24-Bit Representation of the Current Input

- Digital ambient subtraction at ADC output

- Noise filtering with programmable bandwidth

- Dynamic range up to 100 dB

- PPG transmitter

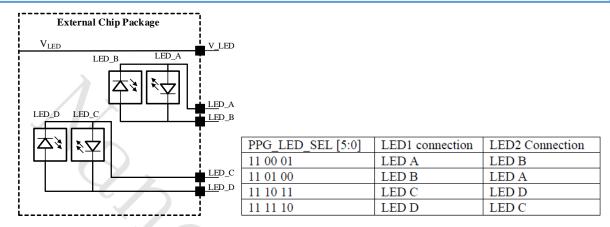

- Four LEDs in common anode configuration

- 8-Bit LED current up to 50 mA

- Programmable LED on-time, duty and width

- Support of two green LED for optimized HRM

- Support the Red LED and IR LED for SpO2

- Support of IR LED for Proximity sensor

- Heart APP inside the SoC

- QT, LVET, PAT

- SDNN, MSSD, SDANN, PNN50

- Heart rate, respiration rate

## Applications

- Brain signal detection system

- Synchronized PPG/ECG for blood pressure estimation

- HRM for wearables, hearables

- Heart-rate variability (HRV)

- Pulse oximetry (SpO2) measurements

Datasheet NNC-EPC001

## Contents

|     |           | ns                               |   |

|-----|-----------|----------------------------------|---|

| Lis | t of Tab  | les                              | 6 |

| Lis | t of Figu | ıres                             | 7 |

| 1.  |           | duction                          |   |

| 2.  | Desci     | ription                          |   |

|     | 2.1       | Block Diagram                    | Э |

| 3.  | Elect     | rical Characteristics            | C |

|     | 3.1       | Absolute maximum ratings         | C |

|     | 3.2       | Recommended operating conditions | C |

|     | 3.3       | ESD Ratings 10                   | C |

| 4.  | Pinou     | Its and pin descriptions1        | 1 |

|     | 4.1       | QFN88L                           | 1 |

|     | 4.1.1     | Pin Diagram                      | 1 |

|     | 4.1.2     |                                  | 2 |

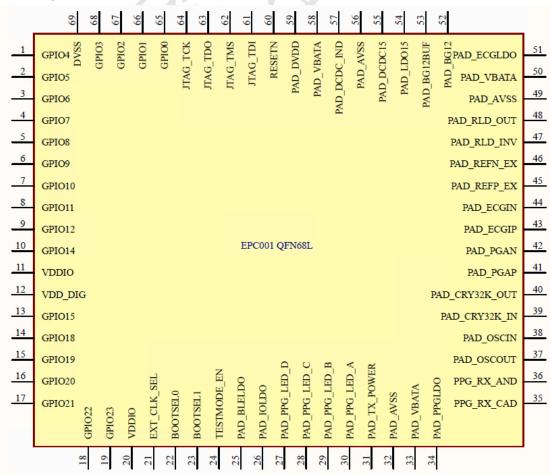

|     | 4.2       | QFN68L                           | 4 |

|     | 4.2.1     |                                  |   |

|     | 4.2.2     | Pin Description1                 | 5 |

| 5.  | Funct     | tional overview                  |   |

|     | 5.1       | Power management1                | 7 |

|     | 5.1.1     | Voltage Regulator                | 7 |

|     | 5.1.2     |                                  |   |

|     | 5.1.3     |                                  |   |

|     | 5.1.4     | Active mode19                    | 9 |

|     | 5.2       | MCU core                         |   |

|     | 5.3       | Memories                         |   |

|     | 5.3.1     |                                  |   |

|     | 5.3.2     |                                  |   |

|     |           |                                  |   |

Nanochap

## Highly Integrated EEG/ECG/EMG/PPG Bio-Electric- Sensor RISC-V SOC

| Datasheet                                                  | NNC- <i>EPC001</i> |

|------------------------------------------------------------|--------------------|

| 5.3.3 ROM                                                  | 22                 |

| 5.4 Boot modes                                             | 22                 |

| 5.5 Clock and start-up                                     | 23                 |

| 5.5.1 Clock Structure                                      | 23                 |

| 5.5.2 Reset Sources                                        | 23                 |

| 5.6 General purpose inputs/outputs (GPIOs)                 | 24                 |

| 5.6.1 GPIO Alternate Functions                             | 24                 |

| 5.6.2 GPIO Modes                                           | 25                 |

| 5.6.3 User Configuration                                   | 25                 |

| 5.7 Direct memory access controller (DMAC)                 | 27                 |

| 5.7.1 Trigger Sources                                      |                    |

| 5.7.2 User Configuration                                   |                    |

| 5.8 Interrupts and events                                  |                    |

| 5.9 Timers and Watchdogs                                   |                    |

| 5.9.1 General-purpose timers                               |                    |

| 5.9.2 Dual-Timer                                           |                    |

| 5.9.3 PWM                                                  |                    |

| 5.9.4 Watchdog timer                                       |                    |

| 5.10 Real-Time Clock (RTC)                                 |                    |

| 5.10.1 User Configuration                                  |                    |

| 5.11 Inter-integrated circuit interface (I <sup>2</sup> C) |                    |

| 5.11.1 User Configuration                                  |                    |

| 5.12 Universal asynchronous receiver/transmitter (UART)    |                    |

| 5.12.1 User Configuration                                  |                    |

| 5.13 Serial peripheral interface (SPI)                     |                    |

| 5.13.1 User Configuration                                  |                    |

| 5.14 Inter-integrated sound interface (I <sup>2</sup> S)   |                    |

| 5.14.1 User Configuration                                  |                    |

| 5.15 Quad-Serial peripheral interface (QuadSPI)            |                    |

| 5.15.1 User Configuration                                  |                    |

| Datasheet NNC-                                                 | EPC001 |

|----------------------------------------------------------------|--------|

| 5.16 ECG module                                                |        |

| 5.16.1 Specifications                                          | 39     |

| 5.16.2 User Configuration                                      | 40     |

| 5.17 PPG module                                                | 43     |

| 5.17.1 Specifications (PPG Rx)                                 | 45     |

| 5.17.2 Specifications (PPG Tx)                                 | 47     |

| 5.17.3 PPG system configuration                                |        |

| 5.17.4 User Configuration                                      |        |

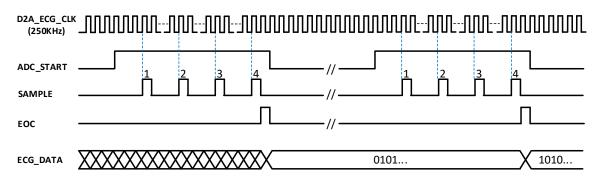

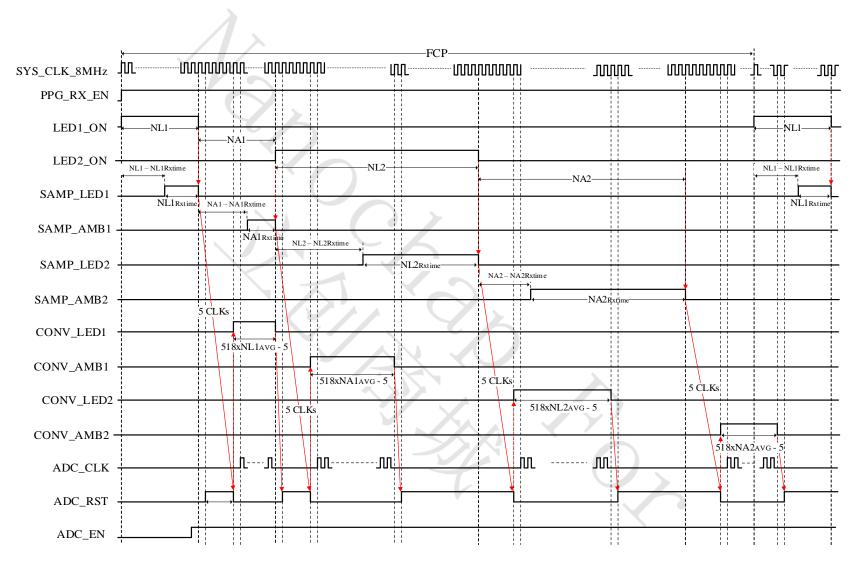

| 5.17.5 Timing Diagram                                          | 49     |

| 5.18 HeartApp module                                           | 51     |

| 5.18.1 User Configuration                                      | 51     |

| 5.19 JTAG debug system                                         | 51     |

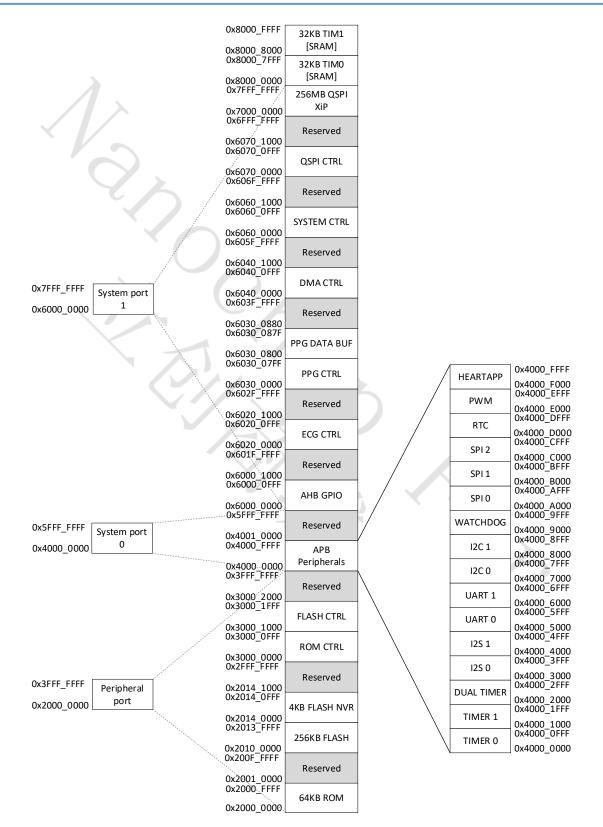

| 6. Memory mapping                                              | 52     |

| 7. Application Example                                         |        |

| 7.20 List of Components                                        |        |

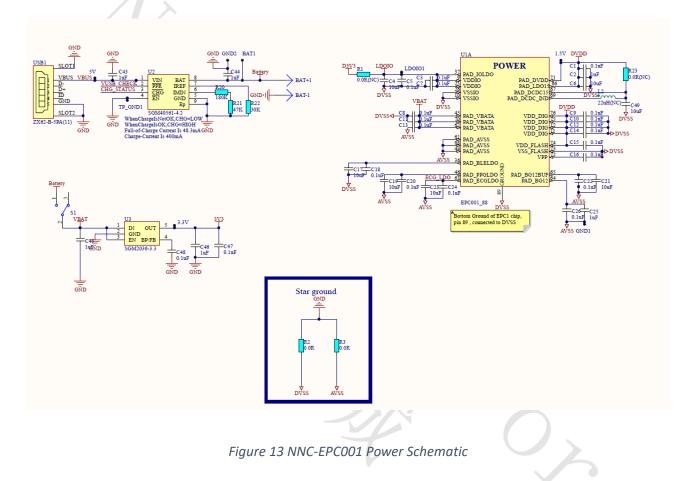

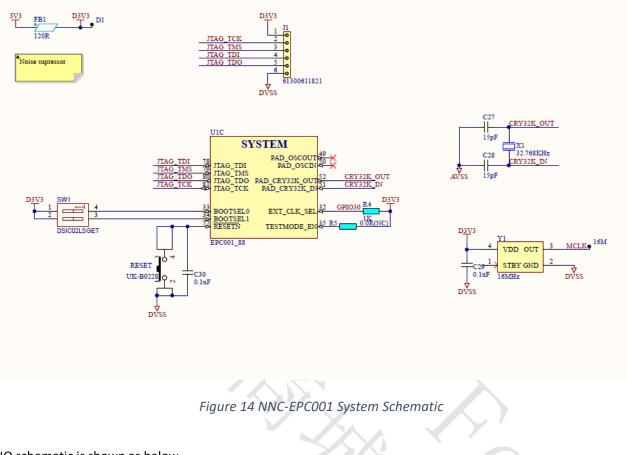

| 7.21 Application Schematic                                     | 56     |

| 8. Package information                                         | 61     |

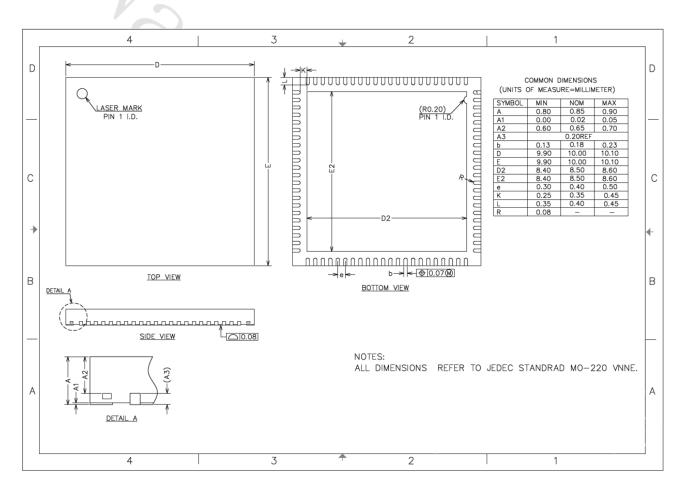

| 8.1 QFN88L                                                     | 61     |

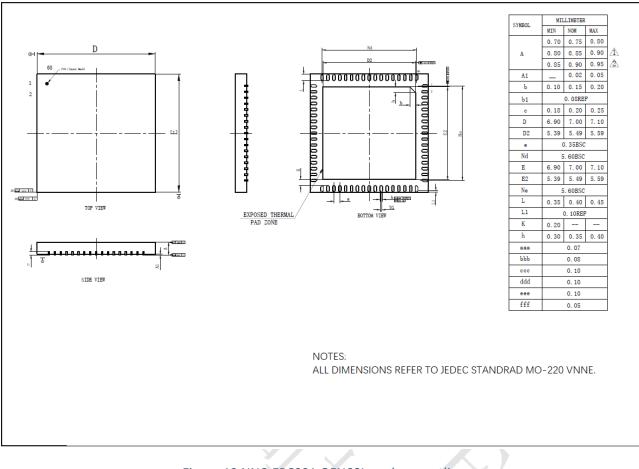

| 8.2 QFN68L                                                     | 61     |

| 9. Order information                                           |        |

| 10. Acronyms                                                   | 64     |

| 11. Revision history                                           | 65     |

| Add package QFN68L and update figures of Application Schematic | 65     |

Datasheet NNC-EPC001

## List of Tables

| Table 1 NNC_EPC001 Absolute maximum ratings         | 10 |

|-----------------------------------------------------|----|

| Table 2 NNC_EPC001 Recommended operating conditions |    |

| Table 3 NNC_EPC001 ESD ratings                      | 10 |

| Table 4 NNC-EPC001 QFN88L pin list                  |    |

| Table 5 NNC-EPC001 QFN68L pin list                  |    |

| Table 6 NNC-EPC001 Flash Timing parameters          | 21 |

| Table 7 NNC-EPC001 Boot selection                   |    |

| Table 8 NNC-EPC001 GPIO alternate functions         |    |

| Table 9 NNC-EPC001 DMA sources                      | 27 |

| Table 10 NNC-EPC001 Interrupt sources               |    |

| Table 11 NNC-EPC001 ECG Specifications              |    |

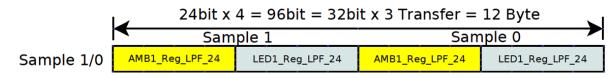

| Table 12 NNC-EPC001 PPG 4-channel data storage      | 44 |

| Table 13 NNC-EPC001 PPG 2-channel data storage      | 45 |

| Table 14 NNC-EPC001 PPG RX Specifications           | 45 |

| Table 15 NNC-EPC001 PPG TX Specifications           |    |

| Table 16 NNC-EPC001 PPG system settings             |    |

| Table 17 NNC-EPC001 Global address map              | 52 |

| Table 18 NNC-EPC001 Component list                  | 55 |

| Table 19 Revision history                           | 65 |

Ty y

. .

02

Datasheet

NNC-*EPC001*

## List of Figures

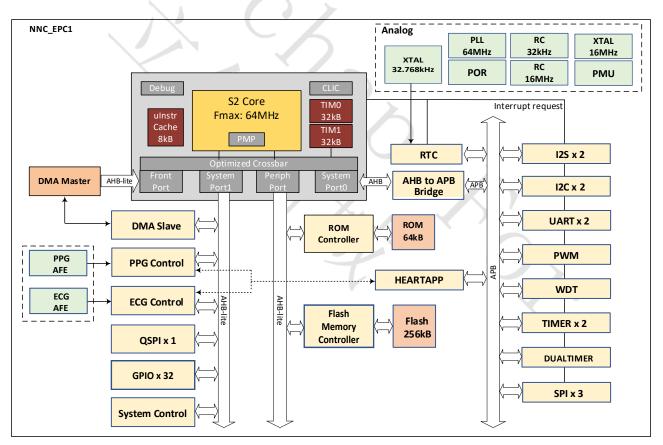

| Figure 1 NNC-EPC001 Block diagram                | 9  |

|--------------------------------------------------|----|

| Figure 2 NNC-EPC001 QFN88L Pin information       | 11 |

| Figure 3 NNC-EPC001 QFN68L Pin information       | 14 |

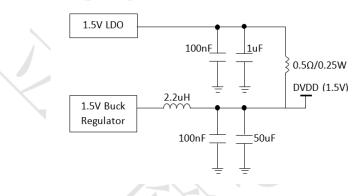

| Figure 4 NNC-EPC001 Voltage regulator            | 17 |

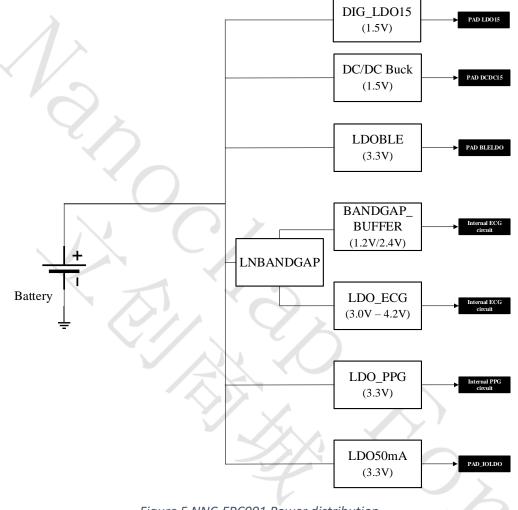

| Figure 5 NNC-EPC001 Power distribution           | 18 |

| Figure 6 NNC-EPC001 Power-saving mode transition | 19 |

| Figure 7 NNC-EPC001 MCU riscv core               | 20 |

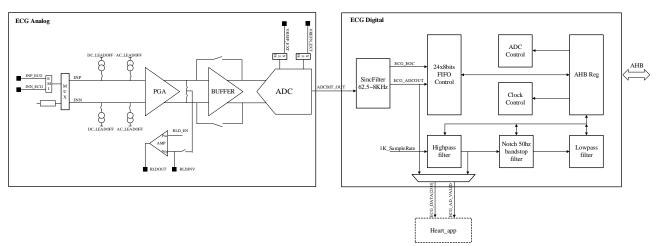

| Figure 8 NNC-EPC001 ECG module                   |    |

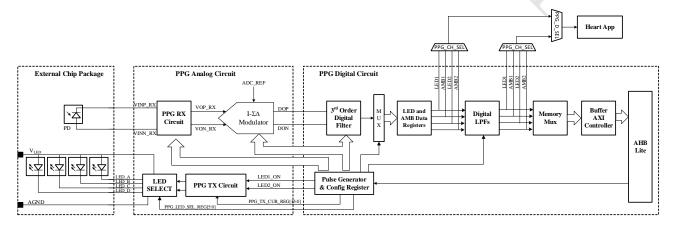

| Figure 9 NNC-EPC001 PPG RX block                 | 43 |

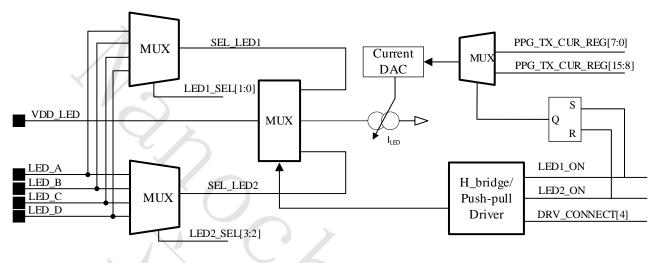

| Figure 10 NNC-EPC001 PPG TX block                | 46 |

| Figure 11 NNC-EPC001 PPG Timing Diagram          | 50 |

| Figure 12 NNC-EPC001 Memory Map                  | 53 |

| Figure 13 NNC-EPC001 Power Schematic             | 56 |

| Figure 14 NNC-EPC001 System Schematic            | 57 |

| Figure 15 NNC-EPC001 IO Schematic                | 58 |

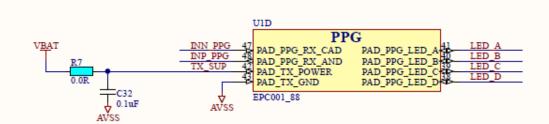

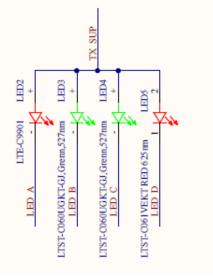

| Figure 16 NNC-EPC001 PPG Schematic               | 59 |

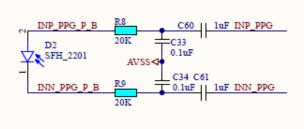

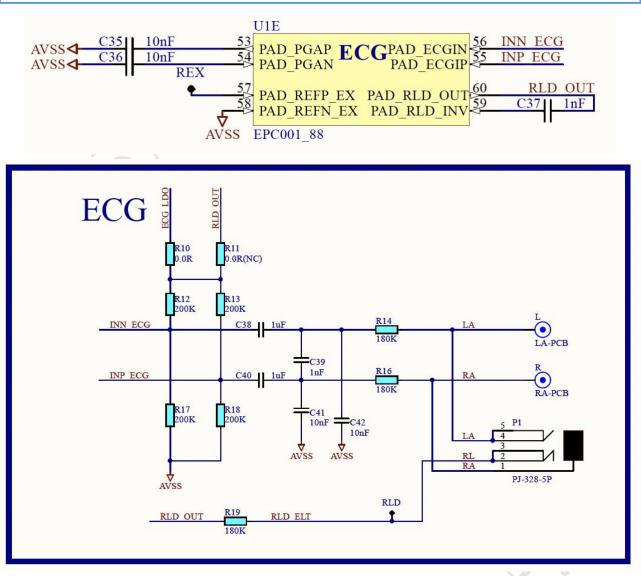

| Figure 17 NNC-EPC001 ECG Schematic               | 60 |

| Figure 18 NNC-EPC001 QFN88L package outline      | 61 |

| Figure 19 NNC-EPC001 QFN68L package outline      | 62 |

V J

0

02

Datasheet

**NNC-***EPC001*

## 1. Introduction

This datasheet provides characteristics and ordering information of the NNC-EPC001.

For information on the Starfive RISC-V core, please refer to the Starfive S2 Manual which available from the www.sifive.com website.

Datasheet

**NNC-EPC001**

## 2. Description

The NNC\_EPC001 is a specialized Bio-electric-sensing SOC. It is integrated with the highly accurate ECG/EEG/EMG/PPG Analog Front-End, which is suitable for bio-electric-sensor application. It integrates outstanding EEG/ECG/EMG/PPG features extraction capability using Heart APP, which makes it suitable for a wide range of wearable products working at low power consumption and high performance. The heart of this SoC is the processor RISC-V CORE(S2).

This powerful MCU and its internal memories make it possible to integrate with different wireless transceivers such as Bluetooth BLE or NFC for transferring measurement data. The NNC\_EPC001 also has a rich peripheral interface which allows the SoC to be used with several different sensors.

#### 2.1 Block Diagram

Figure 1 NNC-EPC001 Block diagram

Datasheet

NNC-*EPC001*

## 3. Electrical Characteristics

#### 3.1 Absolute maximum ratings

|                           | MIN  | MAX | UNIT |

|---------------------------|------|-----|------|

| PAD_VBATA to PAD_AVSS     | -0.3 | 5.5 | V    |

| VDDIO to VSSIO            | -0.3 | 5.5 | V    |

| VDD_DIG to DVSS           | -0.3 | 1.6 | V    |

| VDD_FLASH to VSS_FLASH    | -0.3 | 1.6 | V    |

| Storage temperature, Tstg | -40  | 125 | °C   |

Table 1 NNC\_EPC001 Absolute maximum ratings

#### 3.2 Recommended operating conditions

|                                             | MIN        | NOM          | MAX        | UNIT |

|---------------------------------------------|------------|--------------|------------|------|

| POWER SUPPLY                                |            |              |            |      |

| Analog power supply (PAD_VBAT – PAD_AVSS)   | 2.7        | 3            | 5.5        | V    |

| Digital power supply (VDD_DIG)              |            | 1.5          | 1.6        | V    |

| IO supply (VDDIO - VSSIO)                   | 2.7        | 3            | 5.5        | V    |

| FLASH supply (VDD_FLASH)                    | A.         | 1.5          | 1.6        | V    |

| ANALOG INPUTS                               |            | $\checkmark$ |            | °C   |

| Full-scale differential input voltage range | -vref/gain |              | +vref/gain | V    |

| Input current range                         | 0.5        | (            | 50         | uA   |

| CLOCK INPUT                                 |            |              |            |      |

| External clock input frequency              |            | 32           | · · ·      | KHz  |

| TEMPERATURE RANGE                           |            |              |            |      |

| Operating temperature range                 | -40        |              | 85         | °C   |

Table 2 NNC\_EPC001 Recommended operating conditions

#### 3.3 ESD Ratings

|                                     | VALUE    | UNIT |  |

|-------------------------------------|----------|------|--|

| Electrostatic discharge performance | +/- 2000 | V    |  |

Table 3 NNC\_EPC001 ESD ratings

Datasheet

**NNC-EPC001**

## 4. Pinouts and pin descriptions

- 4.1 QFN88L

- 4.1.1 Pin Diagram

Figure 2 NNC-EPC001 QFN88L Pin information

Datasheet

NNC-*EPC001*

#### 4.1.2 Pin Description

| Pin No. | Pin Name      | Pin Type | Pin Primary Function                    |

|---------|---------------|----------|-----------------------------------------|

| 1       | GPIO7         | I/O      | General Purpose IO7                     |

| 2       | GPIO8         | I/O      | General Purpose IO8                     |

| 3       | GPIO9         | I/O      | General Purpose IO9                     |

| 4       | GPIO10        | I/O      | General Purpose IO10                    |

| 5       | GPIO11        | I/O      | General Purpose IO11                    |

| 6       | GPIO12        | I/O      | General Purpose IO12                    |

| 7       | GPIO13        | I/O      | General Purpose IO13                    |

| 8       | GPIO14        | I/O      | General Purpose IO14                    |

| 9       | VDDIO         | POWER    | Digital IO supply                       |

| 10      | VSSIO         | GND      | Digital IO ground                       |

| 11      | VDD_DIG       | POWER    | Digital logic power                     |

| 12      | VDD_DIG       | POWER    | Digital logic power                     |

| 13      | GPIO15        | I/O      | General Purpose IO15                    |

| 14      | GPIO16        | 1/0      | General Purpose IO16                    |

| 15      | GPIO24        | 1/0      | General Purpose IO24                    |

| 16      | GPIO25        | 1/0      | General Purpose IO25                    |

| 17      | GPIO26        | 1/0      | General Purpose IO26                    |

| 18      | GPIO27        | 1/0      | General Purpose IO27                    |

| 19      | GPIO18        | 0        | BLE – EXT_POR                           |

| 20      | GPIO19        |          | BLE – SPI2_INT                          |

| 21      | GPIO20        | I/O      | BLE – SPI2_MISO                         |

| 22      | GPIO21        | I/O      | BLE – SPI2_MOSI                         |

| 23      | GPIO22        | 1/0      | BLE – SPI2_SCK                          |

| 24      | GPIO23        | I/O      | BLE – SPI2_NSS0                         |

| 25      | VDDIO         | POWER    | Digital IO supply                       |

| 26      | VSSIO         | GND      | Digital IO ground                       |

| 27      | GPIO17        | I/O      | General Purpose IO17                    |

| 28      | GPIO28        | I/O      | General Purpose IO28                    |

| 29      | GPIO29        | I/O      | General Purpose IO29                    |

| 30      | GPIO30        | I/O      | General Purpose IO30                    |

| 31      | GPIO31        | I/O      | General Purpose IO31                    |

| 32      | EXT_CLK_SEL   | 1        | Digital input for external clock select |

| 33      | BOOTSELO      | 1        | Digital input for boot selection bit 0  |

| 34      | BOOTSEL1      | 1        | Digital input for boot selection bit 1  |

| 35      | TESTMODE_EN   | 1        | Digital input to select testmode        |

| 36      | PAD_BLELDO    | POWER    | LDO output for BLE                      |

| 37      | PAD_IOLDO     | POWER    | LDO output for IO                       |

| 38      | PAD_PPG_LED_D | ANA_IN   | Connect to LED anode                    |

## Datasheet

## NNC-*EPC001*

| 39 | PAD_PPG_LED_C  | ANA_IN  | Connect to LED anode                  |

|----|----------------|---------|---------------------------------------|

| 40 | PAD_PPG_LED_B  | ANA_IN  | Connect to LED anode                  |

| 41 | PAD_PPG_LED_A  | ANA_IN  | Connect to LED anode                  |

| 42 | PAD_TX_POWER   | POWER   | Connect to LED to transfer power      |

| 43 | PAD_TX_GND     | GND     | Connect to LED to transfer ground     |

| 44 | PAD_AVSS       | GND     | PPG ground                            |

| 45 | PAD_VBATA      | POWER   | PPG power                             |

| 46 | PAD_PPGLDO     | POWER   | LDO output for PPG                    |

| 47 | PAD_PPG_RX_CAD | ANA_IN  | PPG positive input                    |

| 48 | PAD_PPG_RX_AND | ANA_IN  | PPG negative input                    |

| 49 | PAD_OSCOUT     | ANA_IN  | 16M Crystal output                    |

| 50 | PAD_OSCIN      | ANA_IN  | 16M Crystal input                     |

| 51 | PAD_CRY32K_IN  | ANA_IN  | 32K Crystal input                     |

| 52 | PAD_CRY32K_OUT | ANA_IN  | 32K Crystal output                    |

| 53 | PAD_PGAP       | ANA_OUT | PGA output                            |

| 54 | PAD_PGAN       | ANA_OUT | PGA output                            |

| 55 | PAD_ECGIP      | ANA_IN  | ECG positive input                    |

| 56 | PAD_ECGIN      | ANA_IN  | ECG negative input                    |

| 57 | PAD_REFP_EX    | ANA_IN  | External positive reference           |

| 58 | PAD_REFN_EX    | ANA_IN  | External negative reference           |

| 59 | PAD_RLD_INV    | ANA_IN  | Right leg drive input                 |

| 60 | PAD_RLD_OUT    | ANA_OUT | Right leg drive output                |

| 61 | PAD_AVSS       | GND     | ECG ground                            |

| 62 | PAD_VBATA      | POWER   | ECG power                             |

| 63 | PAD_ECGLDO     | POWER   | LDO output for ECG                    |

| 64 | PAD_BG12       | ANA_OUT | BG Vref output                        |

| 65 | PAD_BG12BUF    | ANA_OUT | BG buffer output                      |

| 66 | PAD_LDO15      | POWER   | 1.5v LDO output for digital           |

| 67 | PAD_DCDC15     | POWER   | 1.5v DCDC output for digital          |

| 68 | PAD_AVSS       | GND     | DCDC ground                           |

| 69 | PAD_DCDC_IND   | ANA_IN  | Connect to external inductor          |

| 70 | PAD_VBATA      | POWER   | DCDC power                            |

| 71 | PAD_DVDD       | POWER   | Digital power (1.5v)                  |

| 72 | VPP            | POWER   | High voltage for Flash                |

| 73 | VSS_FLASH      | GND     | Flash ground                          |

| 74 | VDD_FLASH      | POWER   | Flash power                           |

| 75 | VDD_DIG        | POWER   | Digital logic power                   |

| 76 | VDD_DIG        | POWER   | Digital logic power                   |

| 77 | RESETN         | 1       | External reset pin for digital system |

| 78 | JTAG_TDI       | 1       | JTAG interface                        |

Datasheet

**NNC-EPC001**

| 79                 | JTAG_TMS | 1   | JTAG interface      |

|--------------------|----------|-----|---------------------|

| 80                 | JTAG_TDO | 0   | JTAG interface      |

| 81                 | JTAG_TCK | 1   | JTAG interface      |

| 82                 | GPIO0    | I/O | General Purpose IO0 |

| 83                 | GPIO1    | I/O | General Purpose IO1 |

| 84                 | GPIO2    | I/O | General Purpose IO2 |

| 85                 | GPIO3    | I/O | General Purpose IO3 |

| 86                 | GPIO4    | I/O | General Purpose IO4 |

| 87                 | GPIO5    | I/O | General Purpose IO5 |

| 88                 | GPIO6    | I/O | General Purpose IO6 |

| 89(Thermal<br>pad) | DVSS     | GND | Digital ground      |

Table 4 NNC-EPC001 QFN88L pin list

#### 4.2 QFN68L

4.2.1 Pin Diagram

Figure 3 NNC-EPC001 QFN68L Pin information

Datasheet

NNC-*EPC001*

#### 4.2.2 Pin Description

| Pin No. | Pin Name       | Pin Type | Pin Primary Function                    |

|---------|----------------|----------|-----------------------------------------|

| 1       | GPIO4          | I/O      | General Purpose IO4                     |

| 2       | GPIO5          | I/O      | General Purpose IO5                     |

| 3       | GPIO6          | I/O      | General Purpose IO6                     |

| 4       | GPIO7          | I/O      | General Purpose IO7                     |

| 5       | GPIO8          | I/O      | General Purpose IO8                     |

| 6       | GPIO9          | I/O      | General Purpose IO9                     |

| 7       | GPIO10         | I/O      | General Purpose IO10                    |

| 8       | GPIO11         | I/O      | General Purpose IO11                    |

| 9       | GPIO12         | 1/0      | General Purpose IO12                    |

| 10      | GPIO14         | 1/0      | General Purpose IO14                    |

| 11      | VDDIO          | POWER    | Digital IO supply                       |

| 12      | VDD_DIG        | POWER    | Digital logic power                     |

| 13      | GPIO15         | I/O      | General Purpose IO15                    |

| 14      | GPIO18         | 0        | BLE – EXT_POR                           |

| 15      | GPIO19         |          | BLE – SPI2_INT                          |

| 16      | GPIO20         | 1/0      | BLE – SPI2_MISO                         |

| 17      | GPIO21         | 1/0      | BLE – SPI2_MOSI                         |

| 18      | GPIO22         | 1/0      | BLE – SPI2_SCK                          |

| 19      | GPIO23         | I/O      | BLE – SPI2_NSSO                         |

| 20      | VDDIO          | POWER    | Digital IO supply                       |

| 21      | EXT_CLK_SEL    |          | Digital input for external clock select |

| 22      | BOOTSELO       |          | Digital input for boot selection bit 0  |

| 23      | BOOTSEL1       |          | Digital input for boot selection bit 1  |

| 24      | TESTMODE_EN    |          | Digital input to select testmode        |

| 25      | PAD_BLELDO     | POWER    | LDO output for BLE                      |

| 26      | PAD_IOLDO      | POWER    | LDO output for IO                       |

| 27      | PAD_PPG_LED_D  | ANA_IN   | Connect to LED anode                    |

| 28      | PAD_PPG_LED_C  | ANA_IN   | Connect to LED anode                    |

| 29      | PAD_PPG_LED_B  | ANA_IN   | Connect to LED anode                    |

| 30      | PAD_PPG_LED_A  | ANA_IN   | Connect to LED anode                    |

| 31      | PAD_TX_POWER   | POWER    | Connect to LED to transfer power        |

| 32      | PAD_AVSS       | GND      | PPG ground                              |

| 33      | PAD_VBATA      | POWER    | PPG power                               |

| 34      | PAD_PPGLDO     | POWER    | LDO output for PPG                      |

| 35      | PAD_PPG_RX_CAD | ANA_IN   | PPG positive input                      |

| 36      | PAD_PPG_RX_AND | ANA_IN   | PPG negative input                      |

| 37      | PAD_OSCOUT     | ANA_IN   | 16M Crystal output                      |

| 38      | PAD_OSCIN      | ANA_IN   | 16M Crystal input                       |

## Datasheet

NNC-*EPC001*

| 39         | PAD_CRY32K_IN  | ANA_IN  | 32K Crystal input                     |  |

|------------|----------------|---------|---------------------------------------|--|

| 40         | PAD_CRY32K_OUT | ANA_IN  | 32K Crystal output                    |  |

| 41         | PAD_PGAP       | ANA_OUT | PGA output                            |  |

| 42         | PAD_PGAN       | ANA_OUT | PGA output                            |  |

| 43         | PAD_ECGIP      | ANA_IN  | ECG positive input                    |  |

| 44         | PAD_ECGIN      | ANA_IN  | ECG negative input                    |  |

| 45         | PAD_REFP_EX    | ANA_IN  | External positive reference           |  |

| 46         | PAD_REFN_EX    | ANA_IN  | External negative reference           |  |

| 47         | PAD_RLD_INV    | ANA_IN  | Right leg drive input                 |  |

| 48         | PAD_RLD_OUT    | ANA_OUT | Right leg drive output                |  |

| 49         | PAD_AVSS       | GND     | ECG ground                            |  |

| 50         | PAD_VBATA      | POWER   | ECG power                             |  |

| 51         | PAD_ECGLDO     | POWER   | LDO output for ECG                    |  |

| 52         | PAD_BG12       | ANA_OUT | BG Vref output                        |  |

| 53         | PAD_BG12BUF    | ANA_OUT | BG buffer output                      |  |

| 54         | PAD_LDO15      | POWER   | 1.5v LDO output for digital           |  |

| 55         | PAD_DCDC15     | POWER   | 1.5v DCDC output for digital          |  |

| 56         | PAD_AVSS       | GND     | DCDC ground                           |  |

| 57         | PAD_DCDC_IND   | ANA_IN  | Connect to external inductor          |  |

| 58         | PAD_VBATA      | POWER   | DCDC power                            |  |

| 59         | PAD_DVDD       | POWER   | Digital power (1.5v)                  |  |

| 60         | RESETN         |         | External reset pin for digital system |  |

| 61         | JTAG_TDI       |         | JTAG interface                        |  |

| 62         | JTAG_TMS       |         | JTAG interface                        |  |

| 63         | JTAG_TDO       | 0       | JTAG interface                        |  |

| 64         | JTAG_TCK       | 1       | JTAG interface                        |  |

| 65         | GPIO0          | I/O     | General Purpose IO0                   |  |

| 66         | GPIO1          | I/O     | General Purpose IO1                   |  |

| 67         | GPIO2          | I/O     | General Purpose IO2                   |  |

| 68         | GPIO3          | I/O     | General Purpose IO3                   |  |

| 69(Thermal | DVSS           | GND     | Digital ground                        |  |

| pad)       |                |         |                                       |  |

Table 5 NNC-EPC001 QFN68L pin list

Datasheet

**NNC-EPC001**

## 5. Functional overview

The NNC-EPC001 SOC is a system on chip embedding one MCU (RISC-V core) and multiple ECG/PPG module suitable for high performance bio electric sensor applications.

<u>Figure 1</u> shows the general block diagram of NNC\_EPC001 system.

#### 5.1 Power management

#### 5.1.1 Voltage Regulator

The NNC\_EPC001 is equipped with a linear Low-Dropout regulator (LDO) and a high efficiency step-down DC/DC Buck converter. These blocks provide the digital blocks of the chip with a well-regulated output voltage from a Lithium battery.

Figure 4 NNC-EPC001 Voltage regulator

During the start-up time by default, the digital blocks are powered up by the LDO generating 1.5V. To save battery energy, user can switch from the LDO to the DC/DC converter using software by configuring the system control block, Ana-LDIO control and Ana-DCDC control registers.

#### 5.1.2 Power Supply schemes

Following are the power supply schemes of NNC\_EPC001.

#### LDO50mA:

The Low Dropout Regulator generates a maximum output current of 50mA. It supplies 3.3V for all IOs.

#### LDO\_PPG:

The Low Dropout Regulator supplies 3.3V for the whole PPG system.

#### LDO\_ECG:

The Low Dropout Regulator supplies 3/3.3/3.6/3.9/4.2V for the whole ECG system.

#### BANDGAP\_BUFFER:

The Low noise Bandgap outputs 1.2V/2.4V reference voltage to ECG system.

#### LDO\_BLE:

The Low Dropout Regulator supplies 3.3V.

#### DC/DC Buck Converter:

The high efficiency DC/DC buck converter generates 1.5V output voltage for the digital circuit.

#### LDO15:

The Low Dropout Regulator supplies 1.5V for the digital circuit.

NNC- *EPC001*

REV.C | Page 17 of 65

| ٦ | at | -  | • | h | 0 | ~ | ÷ |  |  |  |

|---|----|----|---|---|---|---|---|--|--|--|

| , | aı | .d | Э |   | E | e | ι |  |  |  |

**NNC-***EPC001*

The figure illustrates the power supply distribution for NNC\_EPC001 chip. Please refer 'Application example component list' section 7.1 for the recommended external parts and connections.

Figure 5 NNC-EPC001 Power distribution

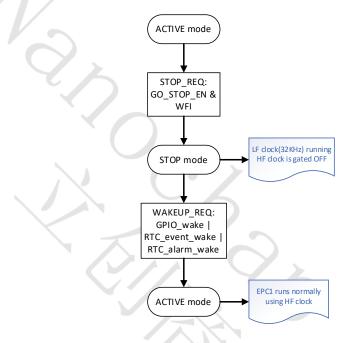

#### 5.1.3 Low-Power modes

The NNC\_EPC001 supports two low-power modes as shown:

Sleep mode:

When CPU issues WFI instruction, the system enters sleep mode. When system is in sleep mode, the clocks of main units inside core will be gated off. The state transition events from sleep to active mode include all interrupts.

#### • Stop mode:

The stop mode can be activated by enabling GO\_STOP\_EN of PMU control register prior to issuing WFI instruction. In this mode all high frequency clocks will be gated off. But the low frequency clock will be always on. Therefore, this mode is also called Power Saving mode. The state transition events from stop to active mode only include:

- o RTC alarm event

- o RTC periodic wakeup event

- o GPIO interrupts

Datasheet NNC-EPC001

#### 5.1.4 Active mode

Upon power on reset, the NNC\_EPC001 will be working in normal active mode, in which all the clocks will be running normally. The power management digital control unit manages the transition from Active mode to Stop(power saving) mode and vice versa.

The figure below illustrates the transition between Active mode and Stop mode.

Figure 6 NNC-EPC001 Power-saving mode transition

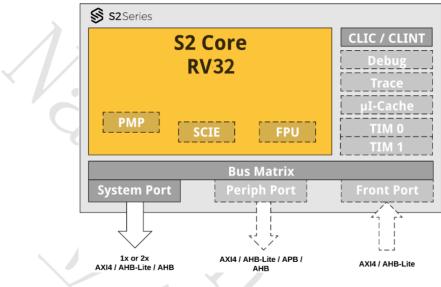

#### 5.2 MCU core

The SiFive S2 Standard Core is a high-performance, full-featured embedded processor designed to address advanced microcontroller applications. It is highly optimized for area and power while still offering class-leading performance. The S2 includes a 32-bit S2 RISC-V core, which has an efficient, single-issue, in-order execution pipeline, with a peak execution rate of one instruction per clock cycle. The S2 core supports machine and user privilege modes, as well as standard Multiply (M) and Compressed (C) RISC-V extensions (RV32IMC). It has the following main features:

- Harvard Architecture with separate CPU instruction fetch and data load/store interfaces

- Integrated 8Kbyte direct mapped uCache for instructions

- Core Local Interrupt Controller (CLIC) to support 64 Level Triggered Interrupts

- 32Kbyte + 32Kbyte Tightly Integrated SRAM Memories

- Physical Memory Protection

- Optimized crossbar interconnect between CPU, TIM, peripherals and external AHB-lite ports which are

- o 2 System AHB-lite Master ports

- 1 Peripheral AHB-lite Master port

- 1 Front AHB-lite Slave port

- A debug unit to support 4 wire JTAG based debugger host connection

Datasheet

**NNC-EPC001**

Below figure shows the block diagram of S2 RISC-V CPU core complex

#### Figure 7 NNC-EPC001 MCU riscv core

#### 5.3 Memories

#### 5.3.1 FLASH

The NNC\_EPC001 includes an embedded Flash memory IP, with x32 configuration, Sector Erase, Chip Erase, and Byte Program capability. It is organized as 64K words/256K bytes main array with Eight Non-Volatile Register sectors (NVR). Each sector has 128 words/512 Bytes.

All sectors are readable/writeable except for NVR Sector 8 which is only readable. Also, the NVR Sector 8 is protected from erase and contains configuration data required to set the configuration registers. The NVR Sectors can only be erased via Sector Erase. Chip Erase will erase the entire Main Array.

The Flash controller supports the following functions:

- The Flash IP can be placed in DEEP SLEEP mode with significantly lowered leakage current in order to save power.

- Unprogrammed destination word check before programming.

- The Flash controller also supports generation of interrupt from two events namely End of Operation and Programming Error.

- The AHB Bus Stalling feature with one outstanding transaction while controller is busy

- There is additional write protection for NVR sectors from 1-8

- Built-in Self Test (BIST) with serial input or output through pads

#### 9.3.1.1 Timing Parameters

The NNC\_EPC001 Flash timing parameters are programmable to support operation across a varying frequency range. These values are calculated in terms of number of clocks based on the operating AHB clock. They have to be initialized in the Timing registers 0~7 before performing any program or erase.

Datasheet

NNC-*EPC001*

The table below shows the timing parameters of NNC\_EPC001 FLASH.

| Details                                         | Parameter       | Unit | Min | Max |

|-------------------------------------------------|-----------------|------|-----|-----|

| Read Cycle Time                                 | Read_access     | ns   | 25  | 25  |

| Wake up time from deep Standby to any operation | Twup            | us   | 3.5 |     |

| Duration of PORb High to any operation          | Trhr            | us   | 3.5 |     |

| Address/Din/CEb to CONFEN High Setup time       | Tcfs            | ns   | 40  |     |

| Address/Din/CEb to CONFEN Low Hold time         | Tcfh            | ns   | 40  |     |

| CONFEN pulse width                              | Tconfen         | ns   | 40  |     |

| PROG/ERASE/CEb/NVR/Address to WEb Setup Time    | Tnvs            | us   | 6   |     |

| Byte Program Time                               | Tprog           | us   | 6   | 7.5 |

| BYTE<3:0>/Address/Data Setup Time               | Tads            | ns   | 15  |     |

| BYTE<3:0>/Address/Data Hold Time                | Tadh            | ns   | 15  |     |

| WEb low to PROG2 high Setup Time                | Tpgs            | us   | 5   | 6.5 |

| PROG2 Low to WEb high hold time                 | Tpgh            | ns   | 15  |     |

| Program Recovery time                           | prog_Trcv       | us   | 5   |     |

| Sector Erase Recovery time                      | ser_Trcv        | us   | 50  |     |

| Chip Erase Recovery time                        | mer_Trcv        | us   | 200 |     |

| Sector Erase Duration                           | ser_Terase      | ms   | 4   | 5   |

| Chip Erase Duration                             | mer_Terase_chip | ms   | 30  | 40  |

| Latency to next operation after PROG/ERASE low  | Trw             | ns   | 100 |     |

Table 6 NNC-EPC001 Flash Timing parameters

#### 9.3.1.2 User Configuration

- 1. Word Program

- a. Set PG bit<0> of control register

- b. Issue word write via direct access interface

- c. Wait for EOP in status register and Clear EOP

- 2. Sector Erase

- a. Set SER bit<1> and SECT\_ADD in control register

- b. Start Erase by writing 1 to STRT bit<16> of control register

- c. Wait for EOP in status register and Clear EOP

- 3. Mass/Chip Erase

- a. Set MER bit<2> of control register

- b. Start Erase by writing 1 to STRT bit<16> of control register

- c. Wait for EOP in status register and Clear EOP

じん

#### Datasheet

NNC-*EPC001*

#### 5.3.2 SRAM

In NNC\_EPC001 core complex, the SRAM is used for instruction cache data memory, instruction cache tag memory, Tightly-Integrated memory (TIM 0) & Tightly-Integrated memory (TIM 1). The NNC\_EPC001 core complex has 64 KB of Tightly-Integrated Memory (TIM) split evenly over two contiguous banks (TIM 0 and TIM 1). Having split TIMs allows for simultaneous access to both banks. When executing code solely from TIM address space, for maximum performance, it is recommended to place code in one TIM and data in the other. If executing code from an off core complex memory device, such as an AHB flash controller, the TIMs can be treated as a single contiguous address space.

Each of the 32KB TIMs are implemented with 2X16K SRAM block.

The NNC\_EPC001 also includes SRAM BIST controller that is based on March C+ algorithm, to support BIST testing through pads.

#### 5.3.3 ROM

The NNC-EPC001 includes 17 ROM IPs. Out of these, 8 ROM blocks whose size is 2048x32bits (i.e., 8Kb) are used as AHB ROM. The remaining 8 ROM blocks whose size is 128x24bits, are used in ECG low pass filter and one other ROM IP with size 256x24bits is used in ECG band stop filter.

The rom controller connected to the peripheral port controls the access of 64Kb AHB ROM (split as eight 8Kb ROM IPs). It also includes ROM BIST controller to perform a readout of all the contents of the ROMs.

#### 5.4 Boot modes

The boot selection pins decide the Reset Vector of CPU, which is the address at which CPU boot upon reset.

Four boot modes can be selected through the BOOTSEL0 and BOOTSEL1 pins, as shown in the following table.

| Boot mode selection |              | Reset Vector     | Boot mode                                      |

|---------------------|--------------|------------------|------------------------------------------------|

| BOOTSEL1 pin        | BOOTSEL0 pin | (Address)        |                                                |

| 0                   | 0            | Flash NVR        | Flash NVR region is selected as boot area for  |

|                     |              | (0x20140000)     | bootloader usage                               |

| 0                   | 1            | Flash Main Array | Flash main memory is selected as boot area for |

|                     |              | (0x20100000)     | application code usage                         |

| 1                   | 0            | SRAM             | Embedded SRAM (TIM0) is selected as boot       |

|                     |              | (0x80000000)     | area for debug usage                           |

| 1                   | 1            | ROM              | Boot from ROM is reserved for future use. Not  |

|                     |              | (0x20000000)     | supported in current NNC_EPC001 version        |

Table 7 NNC-EPC001 Boot selection

Nanochap

Highly Integrated EEG/ECG/EMG/PPG Bio-Electric- Sensor RISC-V SOC

Datasheet NNC-EPC001

#### 5.5 Clock and start-up

#### 5.5.1 Clock Structure

The NNC\_EPC001 has two main clock domains namely the low-frequency (LFCLK) and high-frequency (HFCLK) domain.

The main clocks in these domains are mentioned here:

HFCLK\_RC16M:

It is a 16MHz high-frequency clock generated by a fully-integrated RC Oscillator. After power on reset, this high-speed RC clock will be selected as default HFCLK.

HFCLK\_XTAL16M:

It is a 16MHz high-frequency clock generated by a Crystal Oscillator. In order to set this clock as HFCLK, user need to reset the CLK16M\_SEL bit<1> of PMU system control register1.

HFCLK\_EXT:

It is a high-speed external clock, which can be up to 16MHz. It can be driven using GPIO0 when EXT\_CLK\_SEL pin is pulled to high.

HFCLK\_PLL:

It is a high-speed clock generated by PLL, which can be up to 64MHz. In order to set this clock as HFCLK, user should enable PLL by configuring ANA-PLL system control registers. Also, user need to set the INT\_HFCLK\_SEL bit<3> of PMU system control register1.

LFCLK\_RC32K:

It is a 32KHz low-frequency clock generated by a fully-integrated RC oscillator. After power on reset, this lowspeed RC clock will be selected as default LFCLK.

LFCLK\_XTAL32K:

It is generated by low-speed oscillator with external crystal resonator. It generates an accurate frequency of 32.768KHz. In order to set this clock as LFCLK, user need to reset the LFCLK\_SEL bit<2> of PMU system control register1.

The system clock selection is performed on startup, however the internal RC 16MHz oscillator (HFCLK\_RC16M) is selected as default CPU clock on reset. Several prescalers allow the application to configure the frequency of the AHB and APB clock domains.

#### 5.5.2 Reset Sources

The NNC\_EPC001 system reset is asynchronous reset, where the reset put the system in to the known state without depending on the clock. So, the reset controller of NNC\_EPC001 uses a reset synchronizer for each clock domains. It also uses an ordered proper sequence of reset removal method.

The reset sources are:

- External reset

- Power on reset

- Internal reset requests from different design domains are:

- o system software reset request

- watchdog reset request

- o software reset request for APB peripherals

Datasheet

NNC-*EPC001*

#### 5.6 General purpose inputs/outputs (GPIOs)

The NNC\_EPC001 supports 32 Multifunction GPIOs and 9 Dedicated digital IO's driven through 41 IO Buffers. Most of the GPIO pins can support alternate and analog functions as shown in following table.

| Pin | GPIO Name | Alternate    | Alternate   | Alternate     | Alternate    | Analog       |

|-----|-----------|--------------|-------------|---------------|--------------|--------------|

| No. |           | Function 0   | Function 1  | Function 2    | Function 3   | Function     |

| 82  | GPIO0     | I2C0_SDA     | -           | SPI1_SCK      | HFCLK_EXT    | GPIO_AN_IP   |

| 83  | GPIO1     | I2C0_SCL     | -           | SPI1_MOSI     | -            | GPIO_AN_IN   |

| 84  | GPIO2     | TIMER0_EXTIN | -           | SPI1_MISO     | -            | AN3          |

| 85  | GPIO3     | TIMER1_EXTIN | -           | SPI1_NSS0     | -            | AN2          |

| 86  | GPIO4     | I2S0_CLK     | UART0_RXD   | SPI1_NSS1     | QSPI_SCK     | DCDC_TESTPIN |

| 87  | GPIO5     | 12S0_WS      | UARTO_CTS_N | SPI1_NSS2     | QSPI_BK1_NCS | DCDC_CTRL    |

| 88  | GPIO6     | I2S0_DAT     | UARTO_RTS_N | SPI1_NSS3     | QSPI_BK1_IO0 | PPG_RX_VOUTN |

| 1   | GPIO7     | -            | UART0_TXD   | -             | QSPI_BK1_IO1 | PPG_RX_VOUTP |

| 2   | GPIO8     | -            | -           | <u> </u>      | QSPI_BK1_IO2 | MON_VTUNE    |

| 3   | GPIO9     | SPI0_SCK     |             | - <           | QSPI_BK1_IO3 | TEST_IB50NA  |

| 4   | GPIO10    | SPI0_MOSI    | PWM1        |               | QSPI_BK2_NCS | TEST_IB1U    |

| 5   | GPIO11    | SPI0_MISO    | PWM2        | · / - )       | QSPI_BK2_IO0 | -            |

| 6   | GPIO12    | SPI0_NSS0    | PWM3        |               | QSPI_BK2_IO1 | -            |

| 7   | GPIO13    | SPIO_NSS1    |             | PWM4          | QSPI_BK2_IO2 | -            |

| 8   | GPIO14    | SPI0_NSS2    | I2C1_SDA    | PWM5          | QSPI_BK2_IO3 | -            |

| 13  | GPIO15    | SPI0_NSS3    | I2C1_SCL    | PWM6          | / Y-         | -            |

| 14  | GPIO16    | -            | - ~         |               |              | -            |

| 27  | GPIO17    | -            | -           | -             | - /          | -            |

| 19  | GPIO18    | -            | -           | F -           | _            | 6            |

| 20  | GPIO19    | -            | -           | -             | - ~          | -            |

| 21  | GPIO20    | -            | -           | BLE-SPI2_MISO | -            | -            |

| 22  | GPIO21    | -            | -           | BLE-SPI2_MOSI | -            | -            |

| 23  | GPIO22    | -            | -           | BLE-SPI2_SCK  | -            | -            |

| 24  | GPIO23    | -            | -           | BLE-SPI2_NSS0 | -            | -            |

| 15  | GPIO24    | -            | -           | SPI2_NSS1     | UART1_RXD    | -            |

| 16  | GPIO25    | -            | -           | SPI2_NSS2     | UART1_CTS_N  | -            |

| 17  | GPIO26    | -            | -           | SPI2_NSS3     | UART1_RTS_N  | -            |

| 18  | GPIO27    | -            | -           | -             | UART1_TXD    | -            |

| 28  | GPIO28    | -            | I2S1_CLK    | -             | -            | -            |

| 29  | GPIO29    | -            | 12S1_WS     | -             | -            | -            |

| 30  | GPIO30    | -            | I2S1_DAT    | -             | -            | -            |

| 31  | GPIO31    | -            | -           | -             | -            | -            |

5.6.1 GPIO Alternate Functions

Table 8 NNC-EPC001 GPIO alternate functions

| D | atasheet | NNC- <i>EPC001</i> |

|---|----------|--------------------|

|---|----------|--------------------|

The 9 Dedicated IOs are explained below:

#### RESETN:

RESETN is an active low external reset pin, which will reset the entire chip when asserted.

#### TESTMODE\_EN:

The testmode functions for the IOs are activated using TESTMODE\_EN. When testmode is enabled, the BOOTSEL1 and BOOTSEL0 pins are used to select different testmode functions.

#### JTAG pins:

JTAG\_TCK, JTAG\_TDO, JTAG\_TMS and JTAG\_TDI are the four dedicated pins for JTAG interface.

#### EXT\_CLK\_SEL:

EXT\_CLK\_SEL is dedicated to select external clock. It will enable driving an external high frequency clock through GPIO0.

#### BOOTSEL <1:0>:

BOOTSEL1 and BOOTSEL0 pins are dedicated to select boot mode. This controls the Reset Vector of the CPU.

#### 5.6.2 GPIO Modes

Each of the 32 GPIO pins can be configured in different modes by setting the MODE bits in corresponding GPIO Register as follows:

- 00 Input Mode

- 01 Output Mode

- 10 Alternate function Mode

- 11 Analog Mode

In order to set the function mode these 2 Mode bits are assigned for each GPIO. Therefore, a total of 64-bits spanned across the two 32-bit GPIOL16\_MODE and GPIOH16\_MODE registers respectively. GPIOL16\_MODE specifies the Mode bits for GPIO0 through 15 and GPIOH16\_MODE specifies the Mode bits for GPIO16 through 31.

#### 5.6.3 User Configuration

- 1. Input mode

- a. Set mode bits 00 in the corresponding GPIO MODE register

- b. When configured in this mode, output buffers are disabled to allow values from the PAD to be driven into the input buffers and sampled by the GPIO Datain registers.

- 2. Output mode

- a. Set mode bits 01 in the corresponding GPIO MODE register

- b. When configured in this mode, both input and output buffers are enabled. The PAD is driven by the output buffer through GPIO Dataout Registers and this is driven back via the input buffer to the GPIO Datain Registers.

- 3. Alternate function mode

- a. Set mode bits 10 in the corresponding GPIO MODE register

- b. GPIOL16\_ALTFCN specifies the Alternate Function bits for GPIO0 through 15 and GPIOH16\_ALTFCN specifies the Alternate Function bits for GPIO16 through 31. Set the 2 bits alternate function for the GPIO as follows.

### Datasheet

NNC-*EPC001*

- i. 00 Alternate Function 0

- ii. 01 Alternate Function 1

- iii. 10 Alternate Function 2

- iv. 11 Alternate Function 3

- c. This alternate function setting allows up to 4 different peripheral inputs/outputs to be muxed into one particular IO.

- 4. Analog mode

- a. Set mode bits 11 in the corresponding GPIO MODE register

- b. When configured in this mode, both input and output buffers are disabled to allow the analog signal source/sink to be driven to/from the PAD.

NNC- *EPC001*

#### Datasheet

NNC-*EPC001*

#### 5.7 Direct memory access controller (DMAC)

The DMA controller is compliant with AMBA2.0 AHB-lite Specification. It manages memory-to-memory, memoryto-peripheral and peripheral-to-memory transfers. It has two interfaces; slave interface as well as master interface. The NNC\_EPC001 DMAC slave interface is connected to the System 1 port and the master interface is connected to the Front port.

#### 5.7.1 Trigger Sources

The NNC\_EPC001 DMA controller supports maximum 16 channels. Each channel is connected to dedicated hardware DMA triggers, with support for software trigger as well. The configuration is made by software to set the source address, destination address and transfer data size.

| DMA Channel | Trigger Source |  |

|-------------|----------------|--|

| 15          | ECG            |  |

| 14          | PPG            |  |

| 13          | QSPI           |  |

| 12          | 12C1           |  |

| 11          | 12C0           |  |

| 10          | 1250 / 1251    |  |

| 9           | SPI2 RX        |  |

| 8           | SPI2 TX        |  |

| 7           | SPI1 RX        |  |

| 6           | SPI1 TX        |  |

| 5           | SPIO RX        |  |

| 4           | SPIO TX        |  |

| 3           | UART1 RX       |  |

| 2           | UART1 TX       |  |

| 1           | UARTO RX       |  |

| 0           | UARTO TX       |  |

The 16 DMA Channels is wired to 16 triggering sources as listed below.

Table 9 NNC-EPC001 DMA sources

#### Datasheet NNC-EPC001

- 5.7.2 User Configuration

- 1. Write source address in Channel n Source Address register (SARn)

- 2. Write destination address in Channel n Destination Address register (DARn)

- 3. Configure BLOCK\_TL in Channel n Control register A (CHn\_CTRL\_A), such that BLOCK\_TL = Block transfer size (in bytes) 1

- 4. The DMA transfer mode can be selected by configuring TRGTMDC (Trigger transfer mode control) of Channel n Control register B (CHn\_CTRL\_B)

- 5. If Single Transfer mode, only single data based on hsize will be transferred:

- a. Set TRGTMDC as 00

- b. Configure GRPMC field of CHn\_CTRL\_A register, which indicates whether the single data transfer is from Source or Destination

- 6. If Block Transfer mode, the entire block based on block transfer size will be transferred at one time:

- a. Set TRGTMDC as 10

- 7. If Group Transfer mode, the entire block based on block transfer size will be transferred as several groups:

- a. Set TRGTMDC as 01

- b. Set the GROUP\_LEN = Group length 1. Group length is the No: of bytes to be transferred for each group.

- c. Set SGRPADDRC = 1, if the Source Group Address should start at the same location (as stated in SARn) for each group transaction

- d. Set DGRPADDRC = 1, if the Destination Group Address should start at the same location (as stated in DARn) for each group transaction

- 8. Configure SINC field of CHn\_CTRL\_A register as below:

- a. Set SINC = 00, which increments the source address on every transfer

- b. Set SINC = 01, which decrements the source address on every transfer

- c. Set SINC = 1X, which will use the same source address on every transfer

- 9. Configure DINC field of CHn\_CTRL\_A register as below:

- a. Set DINC = 00, which increments the destination address on every transfer

- b. Set DINC = 01, which decrements the destination address on every transfer

- c. Set DINC = 1X, which will use the same destination address on every transfer

- 10. Set up the Source transfer width and Destination transfer width based on hsize in SRC\_TR\_WIDTH and DST\_TR\_WIDTH of CHn\_CTRL\_A register respectively

- 11. Channel Protection control can be enabled using PROTCTL of CHn\_CTRL\_B register

- 12. Source read data Endian control can be set using SRCDTLGC of CHn\_CTRL\_B register

- 13. Destination write data Endian control can be set using DSTDTLGC of CHn\_CTRL\_B register

- 14. If needed all DMA Interrupts can be enabled using INT\_EN of CHn\_CTRL\_B register

- 15. Finally, user can enable the Global DMA control bit of DMAC Channel Configuration register (DMACCFG) and then set the corresponding channel Enable in Channel n Enable control register (CHn\_EN)

Datasheet

**NNC-***EPC001*

#### 5.8 Interrupts and events

There are 64 interrupt lines supported by the CPU core. All incoming interrupts are synced to the CCXCLK (core complex clock) domain.

| IRQ   | Function        | Description                                                                                                           |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | Timer 0         | Timer 0 timeout interrupt                                                                                             |

| 1     | Timer 1         | Timer 1 timeout interrupt                                                                                             |

| 2     | Dual Timer      | Dual Timer timeout interrupt                                                                                          |

| 3     | I2S 0           | I2S0 Data buffer/ Overrun/ Underrun status interrupt                                                                  |

| 4     | I2S 1           | I2S1 Data buffer/ Overrun/ Underrun status interrupt                                                                  |

| 5     | UART 0          | UARTO Data buffer/ Line/ Modem status interrupt                                                                       |

| 6     | UART 1          | UART1 Data buffer/ Line/ Modem status interrupt                                                                       |

| 7     | I2C 0 Event     | I2C0 Data buffer/ Transfer Event status interrupt                                                                     |

| 8     | I2C 1 Event     | I2C1 Data buffer/ Transfer Event status interrupt                                                                     |

| 9     | Watchdog        | Watchdog Timer timeout interrupt                                                                                      |

| 10    | SPI 0           | SPI0 Data buffer/ Transfer complete/ Overrun/ Underrun status interrupt                                               |

| 11    | SPI 1           | SPI1 Data buffer/ Transfer complete/ Overrun/ Underrun status interrupt                                               |

| 12    | SPI 2           | SPI2 Data buffer/ Transfer complete/ Overrun/ Underrun status interrupt                                               |

| 13    | RTC             | RTC Alarm interrupt/ Period Wakeup Timer interrupt                                                                    |

| 14    | I2C 0 Error     | I2C0 Error status interrupt                                                                                           |

| 15    | I2C 1 Error     | I2C1 Error status interrupt                                                                                           |

| 16    | DMA Ctrl        | DMA Transfer status interrupt                                                                                         |

| 17    | Quad SPI        | Quad SPI Data buffer/ Transfer complete/ Timeout/ Polling status match/ Error status interrupt                        |

| 18    | Flash Ctrl      | End of operation/ Program Error status interrupt                                                                      |

| 19    | PWM             | PWM match status interrupt                                                                                            |

| 20    | HEARTAPP        | Measurement End status interrupt                                                                                      |

| 21    | PPG             | PPG Data buffer status interrupt                                                                                      |

| 22    | ECG             | ECG Data buffer/ ADC EOC/ LP, HP, BS filter Calculation end/<br>Leadoff Detection/ Overrun/ Underrun status interrupt |

| 23    | System ctrl LVD | LVD out status interrupt                                                                                              |

| 24    | System ctrl PLL | PLL status interrupt                                                                                                  |

| 25    | System ctrl BG  | BG status interrupt                                                                                                   |

| 26-31 | -               | -                                                                                                                     |

| 32-63 | GPIO32          | GPIO 0-31 individual interrupts                                                                                       |

Table 10 NNC-EPC001 Interrupt sources

Datasheet

NNC-*EPC001*

#### 5.9 Timers and Watchdogs

The NNC\_EPC001 has two general purpose timers, a dual-timer and a PWM. It also has an independent watchdog timer.

#### 5.9.1 General-purpose timers

The NNC\_EPC001 has two 32-bit general-purpose high frequency down-counters, namely TIMER0 and TIMER1. It can generate interrupt when counter reaches 0. By, default the timers work on APB clock. It also supports counting based on an external pin which can serve as an enable or a clock.

#### 9.9.1.1 User Configuration

- 1. Timer based on internal APB clock

- a. Set Timer interrupt enable, INT\_EN in control register

- b. Config Timer counter CURRENT value & RELOAD value

- c. Start timer using timer enable, TMR\_EN in control register

- 2. Timer based on External clock (GPIO)

- a. To drive clock in external pin of TIMERO, set GPIO2 in Alternate function 0 mode. For TIMER1, set GPIO3 in Alternate function 0 mode

- b. Set Timer interrupt enable, INT\_EN in control register

- c. Config Timer counter CURRENT value & RELOAD value

- d. Set EXT\_CLK and TMR\_EN in control register

- 3. Timer based on External enable (GPIO)

- a. To drive enable in external pin of TIMER0, set GPIO2 in Alternate function 0 mode. For TIMER1, set GPIO3 in Alternate function 0 mode

- b. Set Timer interrupt enable, INT\_EN in control register

- c. Config Timer counter CURRENT value & RELOAD value

- d. Set EXT\_EN and TMR\_EN in control register

#### 5.9.2 Dual-Timer

The dual timer is an APB dual-input timer module consisting of two programmable 32-bit or 16-bit down-counters that can generate interrupts when they reach zero. The operation of each timer module is identical. They operate in three modes which are Free-Running mode, One-shot count mode and Periodic mode.

#### 9.9.2.1 User Configuration

- 1. Select the 16-bit or 32-bit timer operation using TIMER\_SIZE in control register.

- 2. Select the mode of operation by configuring ONE\_SHOT and TIMER\_MODE bits.

- 3. Enable timer interrupt using INT\_EN in control register.

- 4. Load the counter value to the TIMn\_LOAD bits.

- 5. Enable the timer by setting TIMER\_EN in control register.

Datasheet

NNC-*EPC001*

#### 5.9.3 PWM

The PWM is based on a 32-bit Timer counter and inherits all of its features. The PWM function in addition to these features, is based on match register events. The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. The NNC\_EPC001 has 6 PWM output channels. There are seven match registers which allows up to 6 single edge-controlled or 3 double edge-controlled PWM outputs, or a mix of both types.

#### 9.9.3.1 User Configuration

- 1. Write proper GPIO alternate registers: configure GPIO for the 6 PWM outputs

- 2. Enable PWM channels by setting PWMEN of corresponding channel in the PWM control register (PWM\_PCR)

- 3. By default, each channel operates in single edge mode. Can switch to double edge mode by setting PWMSEL in PWM\_PCR.

- 4. Now Load the match register values in PWM Match registers 0~6, which will be loaded in the counters

- 5. Configure PWM Match Control register (PWM\_MCR) to control the pulse output generated in each channel

- 6. Set the 32-bit Prescaler value in PWM\_PR register

- 7. Enable bits in Load Enable register (PWM\_LER), which will activate automatic reload of counter from match register values

- 8. Finally enable PWM Timer by setting CNT\_EN = 1 in PWM Timer control register (PWM\_TCR)

- 9. If needed, the interrupts can be enabled by setting appropriate bits in PWM\_MCR

#### 5.9.4 Watchdog timer

The primary function of the watchdog timer (WDT) module is to perform a controlled system restart after a software problem occurs. The time-out period is user configurable and when the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be configured as an interval timer and can generate interrupts at selected time intervals.

The watchdog interrupt in NNC\_EPC001 is a Non-Maskable Interrupt (NMI) with higher priority. Also, the watchdog register interface has a software-controlled lock to prevent accidental write access in the watchdog registers.

#### 9.9.4.1 User Configuration

- 4. Loading the Watchdog Counter

- d. Unlock watchdog by writing 0x1ACCE551 to Watchdog Lock register

- e. Load the watchdog count by writing to Watchdog Load register

- f. Lock the watchdog by writing 0 to the Watchdog Lock register

- 5. Setting Watchdog for Non Maskable Interrupt (NMI) generation

Enable interrupt in Watchdog Control register to generate NMI after configured count

- 6. Setting Watchdog for RESET generation

- a. Enable reset in Watchdog Control register

- b. Check System Control PMU Status reset information bit, WDRESETREQ

| Datasheet NNC-EPCOC | <b>)1</b> |

|---------------------|-----------|

|                     |           |

- 7. Issuing manual NMI using the Integration Test Register

- a. Write 1 into the ITCR register

- b. Write 2 into ITOP register

- 8. Issuing manual Watchdog Reset using the Integration Test Register

- a. Write 1 into the ITCR register

- b. Write 1 into ITOP register

#### 5.10 Real-Time Clock (RTC)

The Real-Time Clock (RTC) provides an automatic wakeup to manage low-power mode. The RTC is an independent BCD timer/counter. Its main function is to keep track of the current time.

The NNC\_EPC001 RTC has following features:

- Calendar with seconds, minutes, hours (12 or 24 format), week day, date, month and year

- Compensations for 28-, 29-(leap year), 30-, and 31-day months are performed

- Binary or BCD representation of time, calendar and alarm

- Two interrupts are separately software maskable

- o time-of-day clock/calendar with programmable alarm interrupt

- o periodic programmable counter wakeup interrupt

#### 5.10.1 User Configuration

- 1. Calendar Initialization

- a. To generate a 1Hz clock for the calendar counter, program prescaler.

- b. Set INIT bit to 1 and configure DATA\_MODE and HOUR\_MODE in the RTC\_CR register to enter initialization mode.

- c. Load the initial time and date values in the RTC\_TR and RTC\_DR registers.

- d. Exit the initialization mode by clearing the INIT bit.

- e. Note: When INIT\_SYNC\_READY bit in RTC\_SR register is 0, software cannot set INIT bit to trigger another initialization. Also, to read the calendar after initialization, software must check whether the INIT\_SYNC\_READY bit is 1.

- 2. Programming the alarm

- a. Follow the steps in calendar initialization (1), but also program the time alarm RTC\_TAR and date alarm RTC\_DAR registers.

- b. Set ALARM\_EN in RTC\_CR register to enable alarm.

- c. In order to generate interrupt, Set ALARM\_IE in RTC\_IER register.

- 3. Programming the Periodic Wakeup Timer

- a. Program the periodic wakeup input clock-select in RTC\_CR register.

- b. Program the periodic wakeup clock prescaler in RTC\_WPR register.

- c. Program the periodic wakeup timer value in RTC\_WTR register.

- d. Set WUT\_EN in RTC\_CR register to enable the wakeup timer.

- e. In order to generate interrupt, Set WUT\_IE in RTC\_IER register.

Datasheet

NNC-*EPC001*

#### 5.11 Inter-integrated circuit interface (I<sup>2</sup>C)

The NNC\_EPC001 has two I<sup>2</sup>C interfaces (I2C0 & I2C1) which can operate in multi-master or slave modes. Both can support Standard mode (up to 100kbit/s), Fast mode (up to 400kbit/s) and High-Speed mode (up to 3.4Mbit/s). Both support 7-bit and 10-bit addressing modes. They also support data transfer using DMA.

The I2C interface can operate in the following modes for either transmission or reception:

- I2C Slave mode

- I2C Master mode

By default, the I2C interface operates in Slave mode. To switch from default Slave mode to Master mode a Start condition generation is needed. In Master mode, the I2C interface initiates a data transfer and generates the clock signal.

#### 5.11.1 User Configuration

Write proper GPIO alternate registers: configure GPIO for SDA and SCL pins.

- 1. I2C Slave mode

- a. Configure interrupt in Control\_2 register (I2C\_CR2)

- b. Configure PE of Control\_1 register (I2C\_CR1) to enable I2C interface

- c. Configure Own address register (I2C\_OAR) to set I2C slave address

- d. Configure ACK of I2C\_CR1 to set ack bit

- e. Wait for address match interrupt and clear ADDR bit of status register (I2C\_SR)

- f. If acting as a Transmitter, write the transmit data to I2C\_DR register

- g. If acting as a Receiver, wait until RXNE of I2C\_SR is set, then read the received data from I2C\_DR register

- 2. I2C Master mode

- a. Configure interrupt and clock frequency in I2C\_CR2 register

- b. Configure PE of I2C\_CR1 to enable I2C interface

- c. Configure START of I2C\_CR1 to start I2C master

- d. Wait till start bit is generated by master by reading the SB of I2C\_SR register.

- e. Follow further steps below if 7-bit addressing mode:

- i. Write slave address to I2C\_DR

- ii. Wait for address sending by reading ADDR bit of I2C\_SR

- iii. If acting as a transmitter, write the transmit data to I2C\_DR

- iv. If acting as receiver, Wait for RXNE to read the received data from I2C\_DR. Also acknowledge by setting ACK=0 in I2C\_CR1.

- f. Follow further steps below if 10-bit addressing mode:

- i. Write 10-bit address header to I2C\_DR

- ii. Wait for address header sending by reading ADD10 bit of I2C\_SR. Then write the slave address to I2C\_DR.

| Datasheet | NNC- <i>EPC001</i> |

|-----------|--------------------|

|           |                    |

- iii. If acting as a transmitter, wait for address sending by reading ADDR bit of I2C\_SR. And then write the transmit data to I2C\_DR

- iv. If acting as receiver, wait for address sending by reading ADDR bit of I2C\_SR. And then wait for RXNE to read the received data from I2C\_DR. Also acknowledge by setting ACK=0 in I2C\_CR1.

- g. Configure STOP of I2C\_CR1 to stop I2C master

NOTE: By setting DMAEN in I2C control 2 register, DMA transfer can be activated.

### 5.12 Universal asynchronous receiver/transmitter (UART)

The NNC\_EPC001 embeds two universal asynchronous receivers/transmitters (UARTO and UART1). They perform serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU. The NNC\_EPC001 APB UART on power up will be in single character mode, but it can also operate in FIFO mode. They can support up to 115200bps baud rate.

This fully programmable serial interface has the following data characteristics:

- Data can be 5, 6, 7, 8 bits

- Even, odd or no-parity bit generation and detection

- 1, 1.5 or 2-stop bit generation

The NNC\_EPC001 UART also supports an autoflow control mechanism which will eliminate overrun errors. The UART interfaces can be served by the DMA controller.

#### 5.12.1 User Configuration

- 1. Perform the necessary device pin multiplexing setup by configuring GPIO alternate registers for TXD/RXD

- 2. Set the desired baud rate by writing the appropriate clock divisor values to the divisor latch registers (DLL and DLH).

- 3. If the FIFOs will be used, select the desired trigger level and enable the FIFOs by writing the appropriate values to the FIFO control register (FCR). The FIFOEN bit in FCR must be set first, before the other bits in FCR are configured.

- 4. Choose the desired protocol settings by writing the appropriate values to the line control register (LCR).

- 5. If autoflow control is desired, write appropriate values to the modem control register (MCR).

- 6. Different interrupts can be generated by setting appropriate bits in Interrupt Enable register.

- 7. By setting DMA\_MODE in FIFO control register, DMA transfer can be activated.

#### 5.13 Serial peripheral interface (SPI)

The NNC\_EPC001 has three SPI's (SPI0, SPI1 & SPI2), which act as either slave or master in full-duplex, half-duplex and simplex communication modes. The 3-bit baud rate input generator supports 8 master mode frequencies and the frame size is configurable from 1 bit to 16 bits. They have separate transmit/receive 16x16bits FIFOs which supports continuous data transmission in FIFO mode. The SPI clock polarity, clock phase and data shift order are user programmable.

Datasheet NNC-EPC001

The SPI interface support multi-slave communication using four slave chip-select (nss0~nss3). It also supports DMA transfer.

#### 5.13.1 User Configuration

The configuration procedure is almost the same for master and slave. When a standard communication is to be initialized, perform these steps:

- 1. Write proper GPIO alternate registers: configure GPIO for MOSI, MISO, SCK and NSS pins.

- 2. Configure interrupts in interrupt enable register.

- 3. Write to the SPI\_CTRL2 register:

- a. Configure the CHAR\_LEN[3:0] to select the data length for the transfer.

- b. Select NSS port by configuring NSS0\_EN, NSS1\_EN, NSS2\_EN or NSS3\_EN.

- c. Select proper RX data sample phase of master by configuring SAMP\_PHASE[1:0].

- d. Select proper C2T/T2C delay based on slave device requirement using C2T\_DELAY/T2C\_DELAY.

- e. Enable or disable TX/RX DMA in FIFO mode by configuring TXDMA\_EN/RXDMA\_EN.

- 4. Write to the FIFO Control register:

- a. Configure TX\_FIFO\_TH or RX\_FIFO\_TH to define the trigger level threshold.

- b. Clear TX/RX FIFO by setting TX\_FIFO\_CLR/RX\_FIFO\_CLR.

- c. Enable or disable FIFO mode using FIFO\_EN bit.

- 5. Write to the SPI\_CTRL1 register:

- a. Configure the serial clock baud rate using the BAUD\_RATE[2:0].

- b. Configure clock polarity and phase using CPOL and CPHA.

- c. Select full-duplex or half-duplex or simplex communication mode by configuring BIDI\_EN, BIDI\_MODE and UNIDI\_MODE appropriately.

- d. Configure the LSB\_SEL to define the frame format or data shift order.

- e. Select NSS control mode by configuring NSS\_TOGGLE, NSS\_MST\_CTRL, NSS\_MST\_SW.

- f. Select master or slave mode by configuring the MST\_SLV\_SEL.

- g. Enable SPI by setting SPI\_EN.

- 6. Any transmit data should be loaded in Transmitter Holding register (THR) and any received data should be read from Receive Buffer register (RBR).

#### 5.14 Inter-integrated sound interface (I<sup>2</sup>S)

The NNC\_EPC001 has two standard I2S interfaces (I2S0 and I2S1) which can operate as master or slave at halfduplex communication mode. They can be configured to transfer 16, 24 or 32 bits with 16-bit or 32-bit data resolution. They have a programmable clock polarity and they support most audio frequencies (8 kHz, 16 kHz, 22.05 kHz, 32 kHz, 44.1 kHz, 48 kHz, etc.). Data shift order is such that MSB is always send first. By default, the I2S interface operates in Slave mode. Clock and Word-select signals are generated by master.

#### 5.14.1 User Configuration

1. Write proper GPIO alternate registers: configure GPIO for SD, WS and SCK pins.

Nanochap H

Highly Integrated EEG/ECG/EMG/PPG Bio-Electric- Sensor RISC-V SOC

Datasheet

NNC-*EPC001*

- 2. Configure interrupt in I2S interrupt enable register (I2S\_IER)

- 3. Select the data and packet format in I2S Configuration Register (I2S\_CFGR)

- 4. Set I2S\_CFGR.MSTR to 1 for master mode; set I2S\_CFGR.MSTR to 0 for slave mode

- 5. For transmission, follow further steps below:

- a. Set I2S\_CFGR.TXRN to 1

- b. Write the transmit data to data register (I2S\_DR)

- c. The first data written to Tx buffer is the left channel data, and followed by the right channel data

- d. To disable I2S, wait for TXE = 1 in the status register before writing I2S\_CR.EN to 0

- 6. For reception, follow further steps below:

- a. Set I2S\_CFGR.TXRN to 0

- b. Wait for RXNE = 1 in the status register, which indicates data has received in the RX buffer. Number of valid packets is shown in FILLED\_ENTRIES in register I2S\_SR.

- c. Read the received data from data register (I2S\_DR)

- d. To disable I2S, write I2S\_CR.EN to 0, then no more data will be written to RX\_FIFO.

- 7. NOTE: By setting I2S\_CFGR.DMA\_EN, DMA transfer can be activated.

## 5.15 Quad-Serial peripheral interface (QuadSPI)

The QuadSPI is a specialized communication interface targeting single, dual or quad SPI Flash memories. It can operate in any of the three following modes:

- Indirect mode:

- All the operations are performed using the QuadSPI registers

- Status polling mode:

The external Flash memory status register is periodically read and an interrupt can be generated in case of flag setting

Memory-mapped mode:

The external Flash memory is mapped to the device address space and is seen by the system as if it was an internal memory

In indirect mode, it supports a Flash memory capacity of up to 4GB. But in memory-mapped mode the addressable space is limited to 256MB. Both throughput and capacity can be increased two-fold using dual-flash mode, where two QuadSPI flash memories are accessed simultaneously.

The frame format and opcode are user programmable. There is an integrated FIFO (1 bytex32) for reception and transmission. DMA transfer is supported for indirect mode of operations.

#### 5.15.1 User Configuration

Write proper GPIO alternate registers: configure GPIO for IO0, IO1, IO2, IO3, SCK and NCS pins

- 1. Indirect mode

- Set external SPI Flash memory size using FLASH\_SIZE[4:0] in device configuration register (QUADSPI\_DCR).

- b. Specify the number of data bytes to read or write in QUADSPI\_DLR register.

Nanochap Highly II

Datasheet

NNC-*EPC001*