# JXR151T User Manual

版本: V1.2

# 修订记录

| 版本号  | 修订内容                                                | 修订人  | 修订日期      |

|------|-----------------------------------------------------|------|-----------|

| V1.0 | 初始版本                                                | 李妥   | 2021.3.15 |

| V1.1 | 增加包装规格说明                                            | 李妥   | 2021.7.20 |

| V1.2 | 增加 IIC 通信期间的功耗情况<br>补充 transition time 定义中信号电平范围的描述 | 李妥   | 2022.8.25 |

|      |                                                     |      |           |

|      |                                                     |      |           |

|      |                                                     |      |           |

|      |                                                     |      |           |

|      |                                                     |      |           |

|      |                                                     |      | 1>        |

|      |                                                     |      |           |

|      |                                                     | UK.  | i .       |

|      |                                                     | V/SA |           |

|      | N.                                                  |      |           |

# 目 录

| J) | KR151T User Manual                           | 1  |

|----|----------------------------------------------|----|

| 1  | 概述                                           | 5  |

| 2  | 特点                                           | 5  |

| 3  | 结构框图                                         | 6  |

| 4  | 管脚定义                                         | 7  |

|    | 4.1 封装形式                                     | 7  |

|    | 4.2 管脚功能                                     |    |

|    | 绝对电气指标                                       |    |

|    | 推荐操作条件                                       |    |

|    | 频率特性                                         |    |

| 8  | 电气特性                                         |    |

|    | 8.1 直流特性                                     |    |

|    | 8.2 交流特性                                     |    |

| 9  | 寄存器                                          | 11 |

|    | 9.1 寄存器总表                                    | 11 |

|    | 9.2 寄存器详述                                    | 12 |

|    | 9.2.1 时钟及日历寄存器(寄存器 0~6)                      | 12 |

|    | 9.2.2 报警寄存器 (寄存器 8~A)                        |    |

|    | 9.2.3 固定周期计数器控制寄存器(寄存器 B, C)                 |    |

|    | 9.2.4 控制寄存器及标志寄存器(寄存器 D~F)                   |    |

| 1( |                                              |    |

|    | 10.1报警中断                                     |    |

|    | 10.1.1 报警中断时序                                |    |

|    | 10.1.2 报警中断相关寄存器                             |    |

|    | 10.2固定周期中断                                   |    |

|    | 10.2.1 固定周期中断时序                              |    |

|    | 10.2.2 固定周期中断相关寄存器<br>10.3时间更新中断             |    |

|    | 10.3的间更新中断<br>10.3.1 时间更新中断时序                |    |

|    | 10.3.2 时间更新中断相关寄存器                           |    |

| 11 |                                              |    |

| •  | 11.1I <sup>2</sup> C 总线特点                    |    |

|    | 11.2数据传输                                     | ∠1 |

|    | 11.3 起始条件及终止条件                               | 21 |

|    | 11.4设备选择(从地址)                                |    |

|    | 11.5 系统配置                                    |    |

|    | 11.6应答信号                                     |    |

|    | 11.7I <sup>2</sup> C 总线控制                    |    |

|    | 11.7.1 指定地址写操作                               |    |

|    | 11.7.2 指定地址读操作                               |    |

|    | 11.7.3 未指定地址读操作                              |    |

|    | ···· - \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \ |    |

# 图索引

| 图 | 3-1 JXR151T 系统框图                                                    | 6  |

|---|---------------------------------------------------------------------|----|

| 图 | 4-1 JXR151T 封装形式                                                    | 7  |

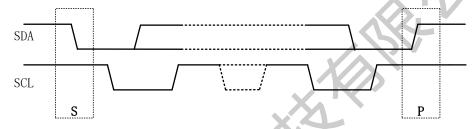

| 图 | 8-1 I <sup>2</sup> C 时序图例                                           | 10 |

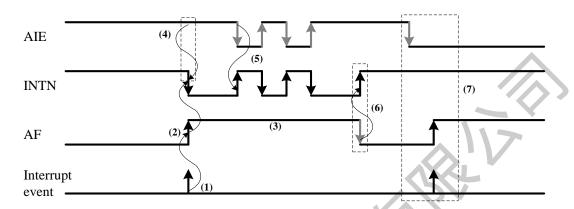

| 图 | 10-1 报警中断时序                                                         | 15 |

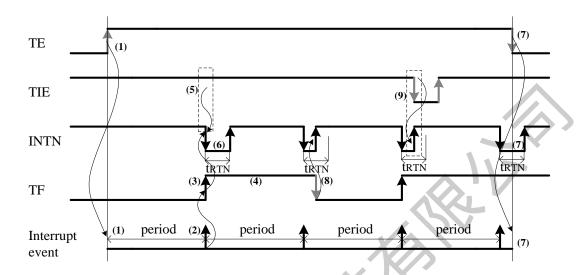

| 图 | 10-2 固定周期中断时序                                                       | 17 |

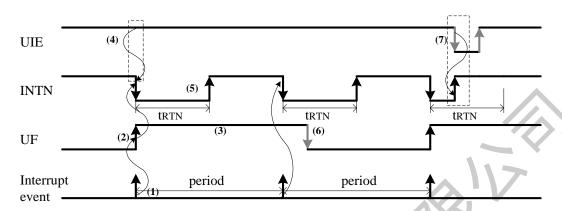

| 图 | 10-3 时间更新中断时序                                                       | 19 |

| 图 | 11-1 I <sup>2</sup> C 起始条件及终止条件                                     | 21 |

| 图 | 11-2 I <sup>2</sup> C 从地址示意                                         |    |

| 图 | 11-3 I <sup>2</sup> C 系统配置                                          | 22 |

| 图 | 11-4 指定地址写操作                                                        | 23 |

|   | 11-5 指定地址读操作                                                        |    |

| 图 | 11-6 未指定地址读操作                                                       | 25 |

|   |                                                                     |    |

|   | 表索引                                                                 |    |

|   | * *****                                                             |    |

| 表 | 4-1 JXR151T 管脚定义                                                    | 7  |

| 表 | 4-1 JXR151T 管脚定义   5-1 绝对最大额定值   6-1 推荐操作条件   7-1 频率特性   8-1 直流电气特性 | 8  |

| 表 | 6-1 推荐操作条件                                                          | 8  |

| 表 | 7-1 频率特性                                                            | 8  |

| 表 | 8-1 直流电气特性                                                          | 9  |

| 表 | 8-2 交流电气特性                                                          | 10 |

| 表 | 9-1 寄存器列表                                                           | 11 |

|   | 9-2 星期寄存器对应表                                                        |    |

|   | 9-3 星期报警模式寄存器 A 对应表                                                 |    |

|   | 9-4 时间更新中断模式选择                                                      |    |

|   | 9-5 FOUT 输出频率选择                                                     |    |

| 表 | 9-6 固定周期中断计数周期选择                                                    | 13 |

|   | 9-7 温补间隔选择                                                          |    |

| 表 | 10-1 报警中断相关寄存器                                                      | 16 |

|   | 10-2 固定周期中断相关寄存器                                                    |    |

|   | 10-3 固定周期中断计数周期及自动复位时间                                              |    |

|   | 10-4 固定周期中断周期示例                                                     |    |

|   | 10-5 时间更新中断相关寄存器                                                    |    |

| 表 | 10-6 时间更新中断模式                                                       | 20 |

#### 1 概述

JXR151T 是一款带有  $I^2$ C 接口的,内建 32.768KHz 温补晶振(DTCXO)的高精度、实时时钟芯片。

该芯片最小计时单位为秒,可实现自动闰年校正;并能提供定时报警中断、固定周期中断、时间更新中断输出以及 32.768KHz/1024Hz/1Hz 时钟输出。

#### 2 特点

- 内置高精度 32.768KHz DTCXO

- 支持高速 I<sup>2</sup>C 总线协议(400KHz)

- 定时报警中断功能(可设定: 星期, 日, 时, 分)

- 固定周期中断功能

- 时间更新中断功能

- 带使能控制的 32.768KHz/1024Hz/1Hz 时钟输出

- 自动闰年调整功能

- 温度补偿电路工作电压范围: 2.2V~5.5V

- 时钟电路工作电压范围: 1.8V~5.5V

- 低电流功耗: 2.3μA@3V(Typ)

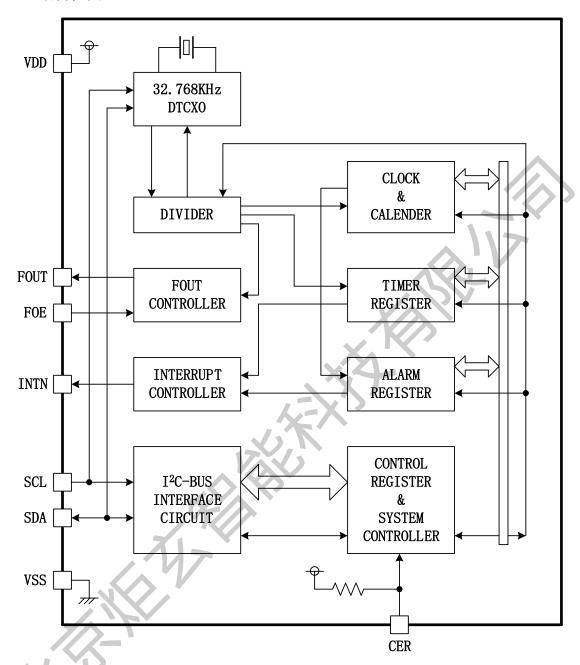

# 3 结构框图

图 3-1 JXR151T 系统框图

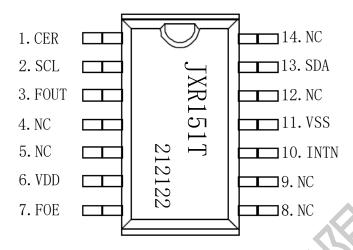

# 4 管脚定义

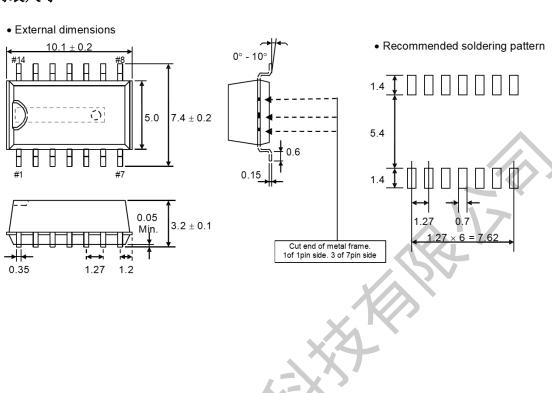

# 4.1 封装形式

图 4-1 JXR151T 封装形式

# 4.2 管脚功能

表 4-1 JXR151T 管脚定义

| Pin name         | I/O    | Function                                     |  |  |  |  |

|------------------|--------|----------------------------------------------|--|--|--|--|

| 1. CER           | IN     | *工厂测试用(无需连接,保持悬空)                            |  |  |  |  |

| 2. SCL           | IN     | I <sup>2</sup> C 总线通信串行时钟输入端                 |  |  |  |  |

| 3. FOUT          | OUT    | 32768Hz 频率输出端口,通过 FOE 控制, FOE=1 时,输出 32768Hz |  |  |  |  |

| 3. 1001          | 001    | 时钟,FOE=0时,输出为高阻态                             |  |  |  |  |

| 4/5/8/9/12/14:NC | 7      | 无需连接,保持悬空                                    |  |  |  |  |

| 6.VDD            | POWER  | 电源正端                                         |  |  |  |  |

| 7. FOE           | IN     | FOUT 输出使能                                    |  |  |  |  |

| 10.INTN          | OUT    | 中断输出端口, N-ch 开漏输出                            |  |  |  |  |

| 11.VSS           | GROUND | 电源接地端                                        |  |  |  |  |

| 13.SDA           | I/O    | I2C 总线通信数据传输端, N-ch 开漏输出                     |  |  |  |  |

# 5 绝对电气指标

表 5-1 绝对最大额定值

| Item      | Symbol            | Condition            | Rating          | Unit |

|-----------|-------------------|----------------------|-----------------|------|

| 电源电压*1    | $V_{\mathrm{DD}}$ | VDD 与 VSS 之间电压       | -0.5 to 6       | V    |

| 输入电压*1,*2 | V <sub>IN</sub>   | FOE, SCL, SDA pins   | -0.5 to VDD+0.3 | V    |

| 输出电压*1,*2 | Vout              | FOUT, SDA, INTN pins | -0.5 to VDD+0.3 | V    |

| 存储温度      | Tstg              | 分散存放, 无包装            | -55 to 150      | °C   |

\*1:各个电气指标在任何时候均不得超出上表中的最大额定值范围,否则会造成相关参数恶化,可靠性降低甚至芯片失效。

\*2: 此处 V<sub>DD</sub> 指推荐操作条件下的 V<sub>DD</sub> 范围。

# 6 推荐操作条件

表 6-1 推荐操作条件

| Item   | Symbol            | Condition | Min. | Тур. | Max. | Unit |

|--------|-------------------|-----------|------|------|------|------|

| 操作电压   | $V_{\mathrm{DD}}$ | 接口电压      | 1.8  | 3.0  | 5.5  | V    |

| 温度补偿电压 | V <sub>TEM</sub>  | 温补电路工作电压  | 2.2  | 3.0  | 5.5  | V    |

| 时钟工作电压 | V <sub>CLK</sub>  | 振荡器模块工作电压 | 1.8  | 3.0  | 5.5  | V    |

| 操作温度   | Topr              |           | -40  | 25   | 85   | °C   |

<sup>\*</sup>任何超出上述表格中推荐范围的操作都可能极大地影响芯片的可靠性。

#### 7 频率特性

表 7-1 频率特性

| Item       | symbol           | Condition                                   | MIN | TYP  | MAX  | Unit                    |

|------------|------------------|---------------------------------------------|-----|------|------|-------------------------|

| 频率稳定性 Δf/f |                  | Ta=0 °C~50 °C, V <sub>DD</sub> =2.2V~5V     |     |      | ±3.0 | ×10 <sup>-6</sup>       |

|            |                  | Ta=-40 °C~85 °C, V <sub>DD</sub> =2.2V~5V   |     |      | ±5.0 | ×10 °                   |

| 电压系数       | $\Delta f/f/V$   | Ta=25 °C, V <sub>DD</sub> =2.2V~5.5V        |     | ±0.5 | ±1.0 | ×10 <sup>-6</sup> /V    |

| 起振时间       | T <sub>STA</sub> | Ta=25 °C, V <sub>DD</sub> =1.8V             |     |      | 0.9  | S                       |

|            | ISTA             | Ta=-40 °C~85 °C, V <sub>DD</sub> =1.8V~5.5V |     |      | 2.0  | S                       |

| 老化         | fa               | Ta=25 °C, V <sub>DD</sub> =3.0V, first year |     |      | ±1.0 | ×10 <sup>-6</sup> /year |

# 8 电气特性

# 8.1 直流特性

表 8-1 直流电气特性

| Item          | Symbol             | Condition                  |                                         | Min.    | Тур. | Max.     | Unit |

|---------------|--------------------|----------------------------|-----------------------------------------|---------|------|----------|------|

| 1. 12-1.44    | $I_{DD1}$          | FOE=GND                    | V <sub>DD</sub> =5V                     |         | 2.4  | 3.2      |      |

| 电流功耗          | $I_{DD2}$          | FOUT=Hi-Z                  | V <sub>DD</sub> =3V                     |         | 2.3  | 3.0      | μА   |

| 由法共和          | I <sub>DD3</sub>   | FOE=VDD                    | V <sub>DD</sub> =5V                     |         | 3.6  |          |      |

| 电流功耗          | $I_{\mathrm{DD4}}$ | FOUT=32.768KHz<br>CL=0pF   | V <sub>DD</sub> =3V                     |         | 2.9  |          | μA   |

| 电流功耗          | $I_{\mathrm{DD5}}$ | FOE=VDD                    | V <sub>DD</sub> =5V                     |         | 7.5  | 17       | 4    |

| 电弧切耗          | $I_{\mathrm{DD6}}$ | FOUT=32.768KHz<br>CL=30pF  | V <sub>DD</sub> =3V                     |         | 6.2  | <b>,</b> | μА   |

| 电流功耗          | $I_{\mathrm{DD7}}$ | IIC 通信期间,V <sub>DD</sub> = | 5V                                      |         |      | 700      | μΑ   |

| 高输入电平         | V <sub>IH</sub>    | CER, FOE, SCL,<br>SDA pins | V <sub>DD</sub> =2.2V~5.5V              | 0.7*VDD |      | VDD      | V    |

| 低输入电平         | V <sub>IL</sub>    | CER, FOE, SCL,<br>SDA pins | V <sub>DD</sub> =2.2V~5.5V              | 0       |      | 0.3*VDD  | V    |

| 高输出电平         | Vон                | FOUT pin                   | Ioн=-1mA                                | VDD-0.3 |      | VDD      | V    |

| <b>居</b> 松山市亚 | ***                | FOUT, INTN pins            | I <sub>OL</sub> =1mA                    | GND     |      | GND+0.3  | V    |

| 低输出电平         | V <sub>OL</sub>    | SDA pin                    | VDD≥2V<br>I <sub>OL</sub> =3mA          | GND     |      | GND+0.3  | V    |

| 输入漏电流         | $I_{LK}$           | FOE, SCL, SDA, VINE        | =V <sub>DD</sub> or GND                 | -0.3    |      | 0.3      | μΑ   |

| 输出漏电流         | Ioz                | INTN, FOUT, SDA, V         | V <sub>IN</sub> =V <sub>DD</sub> or GND | -0.3    |      | 0.3      | μΑ   |

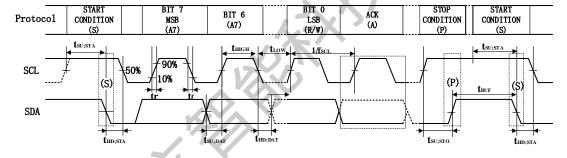

# 8.2 交流特性

表 8-2 交流电气特性

| Item          | Symbol           | Condition                      | Min. | Тур. | Max. | Unit |

|---------------|------------------|--------------------------------|------|------|------|------|

| SCL 时钟频率      | fscl             |                                |      |      | 400  | KHz  |

| 起始条件建立时间      | tsu;sta          |                                | 0.6  |      |      | μS   |

| 起始条件保持时间      | thd;sta          |                                | 0.6  |      |      | μS   |

| 数据传输建立时间      | tsu;dat          |                                | 100  |      |      | nS   |

| 数据传输保持时间      | thd;dat          |                                | 0    |      | 700  | nS   |

| 终止条件建立时间      | tsu;sto          |                                | 0.6  |      | 1    | μS   |

| 总线闲置时间        | t <sub>BUF</sub> | 终止条件到起始条件之间                    | 1.3  |      |      | μS   |

| SCL 低电平时间     | tLow             |                                | 1    |      |      | μS   |

| SCL 高电平时间     | thigh            |                                | 1    |      |      | μS   |

| SCL, SDA 上升时间 | t <sub>r</sub>   |                                |      |      | 0.3  | μS   |

| SCL, SDA 下降时间 | $t_{\mathrm{f}}$ |                                |      | X    | 0.3  | μS   |

| 总线毛刺时长        | tsp              |                                |      |      | 50   | nS   |

| FOUT 输出占空比    | Duty             | 以输出达到 V <sub>DD</sub> 的 50% 计算 | 40   | 50   | 60   | %    |

图 8-1 I<sup>2</sup>C 时序图例

$*I^2C$  数据传输位于起始条件与终止条件之间,数据传输操作必须在 0.95S 时间内完成,超出该时间后, $I^2C$  总线将由内部计时器复位。

#### 9 寄存器

#### 9.1 寄存器总表

表 9-1 寄存器列表

| Address | Function           | Bit7  | Bit6  | Bit5 | Bit4 | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|--------------------|-------|-------|------|------|-------|-------|-------|-------|

| 0       | SEC                | 0     | 40    | 20   | 10   | 8     | 4     | 2     | 1     |

| 1       | MIN                | 0     | 40    | 20   | 10   | 8     | 4     | 2     | 1     |

| 2       | HOUR               | 0     | 0     | 20   | 10   | 8     | 4     | 2     | 1     |

| 3       | WEEK               | 0     | 6     | 5    | 4    | 3     | 2     | 1     | 0     |

| 4       | DAY                | 0     | 0     | 20   | 10   | 8     | 4     | 2     | 1     |

| 5       | MONTH              | 0     | 0     | 0    | 10   | 8     | 4     | 2     | 1     |

| 6       | YEAR               | 80    | 40    | 20   | 10   | 8     | 4     | 2     | 1     |

| 7       | RAM                | •     | •     | •    | •    | •     |       | •     | •     |

| 8       | MIN Alarm          | AE    | 40    | 20   | 10   | 8     | 4     | 2     | 1     |

| 9       | HOUR Alarm         | AE    | •     | 20   | 10   | 8     | 4     | 2     | 1     |

| A       | WEEK Alarm         | AE    | 6     | 5    | 4    | 3     | 2     | 1     | 0     |

| A       | DAY Alarm          | AE    | •     | 20   | 10   | 8     | 4     | 2     | 1     |

| В       | Timer Counter 0    | 128   | 64    | 32   | 16   | 8     | 4     | 2     | 1     |

| C       | Timer Counter 1    | •     | •     | •/   |      | 2048  | 1024  | 512   | 256   |

| D       | Extension Register | 0     | WADA  | USEL | TE   | FSEL1 | FSEL0 | TSEL1 | TSEL0 |

| Е       | Flag Register      | 0     | 0     | UF   | TF   | AF    | 0     | VLF   | VDET  |

| F       | Control Register   | CSEL1 | CSEL0 | UIE  | TIE  | AIE   | 0     | 0     | RESET |

<sup>\*</sup>确保向日历及时钟寄存器中写入合法值,否则芯片将无法执行正确的计时操作。

<sup>\*</sup>标记为⊙的寄存器位是只读位,读取值为"0";标记为●的寄存器位可以作为 RAM 执行读写操作。

<sup>\*</sup>若未设定报警中断功能(AIE="0"),寄存器 8~A 可以作为 RAM 使用。

<sup>\*</sup>若未设定固定周期中断功能(TE=TIE="0"),寄存器 B,C 可以作为 RAM 使用。

<sup>\*</sup>UF, TF, AF, VLF和 VDET 位只允许被写入"0"。

<sup>\*</sup>芯片上电时, CSEL0 位被预设为"1", FSEL1, FSEL0, CSEL1, VLF, UIE, TIE, AIE 位被预设为"0"。

#### 9.2 寄存器详述

#### 9.2.1 时钟及日历寄存器 (寄存器 0~6)

#### • 数据形式

除星期寄存器(寄存器 3)外,数据均为 BCD 码形式。例如,秒寄存器的值"0101 1001"代表当前为 59 秒。

计时方式固定为24小时制。

• 年寄存器及闰年

年寄存器的时间范围是 00~99,99 之后重新回到 00;当年寄存器所代表的值可以被 4 整除时,该年判定为闰年;日历的有效期间为 2000 年~2099 年。

• 星期寄存器

星期寄存器共有 7 个有效位(bit0~bit6),每 1 个有效位代表星期一至星期日中的一天,因此,该寄存器只允许有 1 位为"1"。

| Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 星期  |

|------|------|------|------|------|------|------|-----|

| 0    | 0    | 0    | 0    | 0    | 0    | 4    | 日   |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | _   |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1 1 |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 111 |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 四   |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 五.  |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 六   |

表 9-2 星期寄存器对应表

#### 9.2.2 报警寄存器 (寄存器 8~A)

报警可以设置为每周X的X时X分或每个月X日的X时X分(星期报警模式和日报警模式),报警模式可以通过寄存器D的WADA位设置。

每个报警寄存器都有 AE(Alarm Enable)位(bit7)。当某一个报警寄存器的 AE 位为"0"时,该寄存器设定值需与对应的计时寄存器比较,值一致时输出报警中断,若 AE 位为"1",则忽略其对应的报警寄存器值,即不需要将对应的报警寄存器与计时寄存器比较,始终认为报警寄存器值与对应的计时寄存器值一致。

当选择星期报警模式时,可以同时选择一周中的几天,即寄存器 A 中的 WEEK ALARM 功能 bit0~bit6 可以同时有若干位为"1"。星期报警模式下的对应关系可参考表 9-3。

| Register | Function | bit6 | bit5 | bit4 | bit3 | bit2 | bit1     | bit0 |

|----------|----------|------|------|------|------|------|----------|------|

| A        | 星期报警     | 六    | 五.   | 四    | 111  |      | <u> </u> | 日    |

表 9-3 星期报警模式寄存器 A 对应表

#### 9.2.3 固定周期计数器控制寄存器(寄存器 B, C)

这两个寄存器用来设定固定周期中断的预设倒计数值,当上述两个寄存器中的数值从001h变为000h时,固定周期中断事件发生,TF被置"1"且INTN上输出低电平(若TIE为"1");之后B,C寄存器被重置为预设值,重新开始倒计数过程。

#### 9.2.4 控制寄存器及标志寄存器(寄存器 D~F)

• WADA 位

报警中断模式选择位,当置为"1"时,为日报警模式,当置为"0"时,为星期报警模式。

• USEL 位

用来设定时间更新中断的周期;芯片上电时该位为不定值,使用过程中需手动配置。

表 9-4 时间更新中断模式选择

| USEL | Timing | Auto return time |

|------|--------|------------------|

| 0    | 1Hz    | 500ms            |

| 1    | 1/60Hz | 7.81ms           |

• TE 位

该位置"1"时,固定周期中断的计数器开始倒计数,置"0"时则停止倒计数。

• FSEL 位

用来设定 FOUT 端口输出频率,具体配置情况参考表 9-5。芯片上电后,默认值为"00"。

表 9-5 FOUT 输出频率选择

| FSEL1 | FSEL0 | FOUT frequency     |

|-------|-------|--------------------|

| 0     | 0     | 32.768KHz *Default |

| 0     | 1     | 1024Hz             |

| 1     | 0     | 1Hz                |

| 1 -   | 1     | 32.768KHz          |

• TSEL 位

用来设定固定周期中断的计数周期。

表 9-6 固定周期中断计数周期选择

| TSEL1 | TSEL0 | Source clock |

|-------|-------|--------------|

| 0     | 0     | 4096Hz       |

| 0     | 1     | 64Hz         |

| 1     | 0     | 1Hz          |

| 1     | 1     | 1/60Hz       |

• AF, TF, UF 位

分别为报警中断,固定周期中断,时间更新中断的标志位;当上述中断事件发生时,对应的标志位被置"1"。标志位将维持为"1"直至手动将其清"0",禁止手动将上述标志位置"1"。

#### • AIE, TIE, UIE 位

分别用来设定当报警中断,固定周期中断,时间更新中断事件发生时,INTN 管脚上的中断信号输出情况;该三个 bit 的上电默认值均为"0"。

INTN 管脚上的中断信号输出为报警中断,固定周期中断,时间更新中断的逻辑或,通过中断标志位来判断具体的中断情况,确定中断信号输出。

#### • VLF 位

低电压检测标志位; 当检测到电源电压下降至 1.8V 以下,导致时钟电路无法正常工作时,或检测到上电复位信号时,该位被置"1"。该标志位将维持为"1"直至手动将其清"0",禁止手动将该标志位置"1"。

#### • VDET 位

电压检测标志位; 当检测到电源电压下降至 2.2V 以下,导致温度补偿电路无法正常工作时,该位被置"1"。该标志位将维持为"1"直至手动将其清"0",禁止手动将该标志位置"1"。

#### • CSEL 位

用来设定温度补偿电路启动的时间间隔;芯片上电后,默认值为"01"(2S)

| CSEL1 | CSEL0 | Operation interval |

|-------|-------|--------------------|

| 0     | 0     | 0.5S               |

| 0     | 1     | 2S *Default        |

| 1     | 0     | 10S                |

| 1     | 1     | 30S                |

表 9-7 温补间隔选择

#### • RESET 位

RESET 置"1"时,秒以下寄存器被复位,时钟停止;温度补偿及 VLF/VDET 电压检测功能失效。

在以下三种情况下,被置"1"的 RESET 位会重新清"0":检测到 I<sup>2</sup>C 终止条件,重新开始条件或 0.95S 后 I<sup>2</sup>C 总线复位时。与此同时,VLF/VDET 标志位清"0",重置电源电压检测功能。

#### 10 中断功能

#### 10.1 报警中断

报警中断可以在设定的星期,日,小时,分钟产生报警中断事件。

#### 10.1.1报警中断时序

图 10-1 报警中断时序

- (1) 设定好报警中断对应的小时、分钟、日期或星期信息以及 WADA 寄存器,当设定时间 与当前时间匹配时,产生报警中断事件。

- (2) 报警中断事件产生时, AF 标志位被置为"1"。

- (3) AF 寄存器会保持"1"状态直至手动将其清"0"。

- (4) 报警中断事件发生时,若 AIE="1", INTN 输出低电平;若 AIE="0", INTN 保持为 Hi-Z 状态。

- (5) INTN="0"期间若置 AIE 为"0", INTN 即刻恢复为 Hi-Z 状态; 在报警中断事件发生且 AF 寄存器被清"0"之前, AIE 可以用来控制 INTN 的输出状态。

- (6) 将 AF 寄存器清"0"可以清除报警中断输出, INTN 即刻由"0"变为 Hi-Z 状态。

- (7) 报警中断事件发生时若 AIE="0", INTN 保持 Hi-Z 状态, 不会输出低电平。

#### 10.1.2报警中断相关寄存器

| 耒  | 10-1 | 报警中断相关寄存器 |

|----|------|-----------|

| 1X | TO-T |           |

| Address | Function           | Bit7  | Bit6  | Bit5 | Bit4 | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|--------------------|-------|-------|------|------|-------|-------|-------|-------|

| 8       | MIN Alarm          | AE    | 40    | 20   | 10   | 8     | 4     | 2     | 1     |

| 9       | HOUR Alarm         | AE    | •     | 20   | 10   | 8     | 4     | 2     | 1     |

|         | WEEK Alarm         | AE    | 6     | 5    | 4    | 3     | 2     | 1     | 0     |

| A       | DAY Alarm          | AL    | •     | 20   | 10   | 8     | 4     | 2     | 1     |

| D       | Extension Register | 0     | WADA  | USEL | TE   | FSEL1 | FSEL0 | TSEL1 | TSEL0 |

| Е       | Flag Register      | 0     | 0     | UF   | TF   | AF    | 0     | VLF   | VDET  |

| F       | Control Register   | CSEL1 | CSEL0 | UIE  | TIE  | AIE   | 0     | 0     | RESET |

- 配置报警中断寄存器时,建议首先将 AIE 置"0",以防操作过程中产生不必要的硬件中断。

- WADA 用于选择报警模式, 当置为"1"时, 为日报警模式, 当置为"0"时, 为星期报警模式。

- 报警中断事件的发生会将 AF 标志位置"1",该位将保持为"1"直至手动将其置"0"。

- 报警中断事件发生时, AIE 决定是否产生中断信号输出 (AIE="1",则 INTN="0", AIE="0",则 INTN=Hi-Z)。

- AE 位为"0"表示对应的寄存器需要与时钟或日历寄存器比较; 若 AE 位为"1",则不比较对应的寄存器,即认为该寄存器始终与对应的时钟或日历寄存器匹配。参考下述示例:

- (1) 寄存器 A 设为"80"时,只有分报警和时报警寄存器需要与相应的时钟寄存器对比,忽略星期/日期寄存器;因此,只要时寄存器和分寄存器匹配,每一天都会产生报警中断事件。

- (2) 8, 9, A 三个寄存器中的 AE 位均置为"1"会导致每分钟产生一次报警中断事件。

#### 10.2 固定周期中断

固定周期中断可以在 244.14µS 和 4095min 之间按照某一固定周期产生中断报警事件。

#### 10.2.1 固定周期中断时序

图 10-2 固定周期中断时序

- (1) 当 TE 位写入"1"时,固定周期计数器从预设值开始倒计数。

- (2) 当固定周期计数器从 001h 计数到 000h 时,产生中断事件; 计数器重置为预设值,继续下一次计数。

- (3) 固定周期中断事件发生时, TF 寄存器被置为"1"。

- (4) TF 寄存器会保持"1"状态直至手动将其清"0"。

- (5) 当固定周期中断事件发生时,若 TIE="1", INTN 输出低电平;若 TIE="0", INTN 保持为 Hi-Z 状态。

- (6) INTN 输出低电平时长为 tRTN, 之后会自动恢复 Hi-Z 状态直至下次中断信号输出。

- (7) 当 TE 位写入"0"时,固定周期计数器停止计数,INTN 输出 Hi-Z (若 TE 写"0"发生在 INTN="0"期间,待 tRTN 时间之后,INTN 恢复 Hi-Z 状态)。

- (8) 若在 INTN="0"期间将 TF 清"0", INTN 即刻恢复 Hi-Z 状态。

- (9) TIE 写入"0"时, INTN 即刻恢复 Hi-Z 状态。若在 tRTN 期间再次将 TIE 写为 1, INTN 仍将保持 Hi-Z 状态。

#### 10.2.2 固定周期中断相关寄存器

| 耒   | 10-2 | 固定周期中断相关寄存器 |

|-----|------|-------------|

| 100 | TO-2 |             |

| Address | Function           | Bit7  | Bit6  | Bit5 | Bit4 | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|--------------------|-------|-------|------|------|-------|-------|-------|-------|

| В       | Timer Counter 0    | 128   | 64    | 32   | 16   | 8     | 4     | 2     | 1     |

| С       | Timer Counter 1    | •     | •     | •    | •    | 2048  | 1024  | 512   | 256   |

| D       | Extension Register | 0     | WADA  | USEL | TE   | FSEL1 | FSEL0 | TSEL1 | TSEL0 |

| Е       | Flag Register      | 0     | 0     | UF   | TF   | AF    | 0     | VLF   | VDET  |

| F       | Control Register   | CSEL1 | CSEL0 | UIE  | TIE  | AIE   | 0     | 0     | RESET |

- 配置固定周期中断寄存器时,建议首先将 TE 及 TIE 置"0",以防操作过程中产生不必要的硬件中断。

- TSEL1 和 TSEL0 用来设定固定周期中断的倒计数周期,INTN 管脚上的中断信号自动复位时间与倒计数周期相关。

表 10-3 固定周期中断计数周期及自动复位时间

| TSEL1 | TSEL0 | Source clock | Auto reset time |

|-------|-------|--------------|-----------------|

| 0     | 0     | 4096Hz       | 0.122mS         |

| 0     | 1     | 64Hz         | 7.8125mS        |

| 1     | 0     | 1Hz          | 7.8125mS        |

| 1     | 1     | 1/60Hz       | 7.8125mS        |

- 寄存器 B, C 设定计数器的默认值(001h~FFFh),计数器以 TSEL 设定的计数周期倒计数至 000h 时,产生固定周期中断事件。

- TE 为固定周期计数器的使能控制位, TE="1"时, 计数器开始倒计数; TE="0"时, 计数器 停止计数, 终止固定周期中断功能。

- 固定周期中断事件的发生会将 TF 标志位置"1",该位将保持为"1"直至手动将其置"0"。

- 固定周期中断事件发生时,TIE 决定是否产生中断信号输出(TIE="1",则 INTN="0"; TIE="0",则 INTN=Hi-Z)。

表 10-4 固定周期中断周期示例

| Timer counter set value | Source clock |          |       |         |  |  |  |

|-------------------------|--------------|----------|-------|---------|--|--|--|

| Timer counter set value | 4096Hz       | 64Hz     | 1Hz   | 1/60Hz  |  |  |  |

| 0                       |              |          |       |         |  |  |  |

| 1                       | 244.14μS     | 15.625mS | 1S    | 1min    |  |  |  |

| •••••                   | •••••        | •••••    | ••••• | •••••   |  |  |  |

| 2048                    | 500mS        | 32S      | 2048S | 2048min |  |  |  |

| •••••                   | •••••        | •••••    | ••••• | •••••   |  |  |  |

| 4095                    | 0.9998S      | 63.984S  | 4095S | 4095min |  |  |  |

#### 10.3 时间更新中断

根据设定值,时间更新中断以秒更新或分更新产生中断报警事件。

#### 10.3.1 时间更新中断时序

图 10-3 时间更新中断时序

- (1) USEL 寄存器决定芯片处于秒更新中断还是分更新中断状态,当相应的秒寄存器或分寄存器更新时,产生时间更新中断事件。

- (2) 时间更新中断事件产生时, UF 寄存器被置"1"

- (3) UF 寄存器会保持"1"状态直至手动将其清"0"。

- (4) 时间更新中断事件发生时,若 UIE="1", INTN 输出低电平;若 UIE="0", INTN 保持为 Hi-Z 状态。

- (5) INTN 输出低电平时长为 tRTN,之后会自动恢复 Hi-Z 状态直至下次中断信号输出。

- (6) 若在 INTN="0"期间将 UF 清"0", 待 tRTN 时间之后, INTN 恢复 Hi-Z 状态。

- (7) INTN="0"期间若置 UIE 为"0", INTN 即刻恢复 Hi-Z 状态, 中断信号输出结束。若在 tRTN 期间再次将 UIE 写为 1, INTN 仍将保持 Hi-Z 状态。

#### 10.3.2 时间更新中断相关寄存器

表 10-5 时间更新中断相关寄存器

| Address | Function           | Bit7  | Bit6  | Bit5 | Bit4 | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|--------------------|-------|-------|------|------|-------|-------|-------|-------|

| D       | Extension Register | 0     | WADA  | USEL | TE   | FSEL1 | FSEL0 | TSEL1 | TSEL0 |

| Е       | Flag Register      | 0     | 0     | UF   | TF   | AF    | 0     | VLF   | VDET  |

| F       | Control Register   | CSEL1 | CSEL0 | UIE  | TIE  | AIE   | 0     | 0     | RESET |

- 配置时间更新中断寄存器时,建议首先将 UIE 置"0",以防操作过程中产生不必要的硬件中断。

- USEL 信号用来设定中断模式为秒更新或分更新。

表 10-6 时间更新中断模式

| USEL | Timing | Auto return time |

|------|--------|------------------|

| 0    | 1Hz    | 500ms            |

| 1    | 1/60Hz | 7.81ms           |

- 时间更新中断事件的发生会将 UF 标志位置"1",该位将保持为"1"直至手动将其清"0"。

- 时间更新中断事件发生时,UIE 决定是否产生中断信号输出(UIE="1",则 INTN="0"; UIE="0",则 INTN=Hi-Z)。

#### 11 I2C 总线接口

#### 11.1 I2C 总线特点

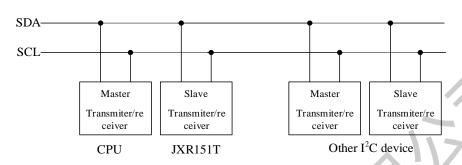

I<sup>2</sup>C 是一种双向通信接口,其信号线 SDA 以及时钟线 SCL 需通过上拉电阻连接至 VDD;连接至 I<sup>2</sup>C 总线的端口必须为开漏结构以便实现多设备的线与连接。

#### 11.2 数据传输

每个 SCL 时钟周期可以传送 1bit 数据。发送数据时,SDA 线上的数据在 SCL 低电平期间改变,接收数据时,SCL 高电平期间可以从数据线 SDA 上得到稳定有效的数据。

#### 11.3 起始条件及终止条件

空闲状态时,SCL 及 SDA 保持为高电平。SCL 高电平期间,SDA 的下降沿作为 I<sup>2</sup>C 通信的起始条件,SCL 高电平期间,SDA 的上升沿作为 I<sup>2</sup>C 通信的终止条件。

图 11-1 I2C 起始条件及终止条件

#### 11.4 设备选择(从地址)

I<sup>2</sup>C 总线设备没有片选信号,主设备通过发送一个唯一固定的设备编号(从地址)来选取相应的从设备,被选从设备发送应答信号来与主设备建立通信。

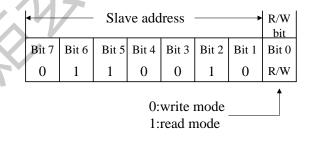

从地址包括 **7bit** 数据**,4bit(Group 1) + 3bit(Group 2)**。**JXR151T** 的从地址为**"0110010"**。通信过程中,从地址与 **R/W** 选择位以 **8bit** 数据的形式发送。

图 11-2 I<sup>2</sup>C 从地址示意

#### 11.5 系统配置

将控制数据传输的设备称为"主设备",被主设备控制的设备称为"从设备";发送数据的设备称为"发送端",接收数据的设备称为"接收端"。

在 JXR151T 系统中,CPU 或其他控制设备为主设备,JXR151T 芯片本身为从设备; 主 从设备均可作为发送端或接收端。

图 11-3 I<sup>2</sup>C 系统配置

### 11.6 应答信号

I<sup>2</sup>C 总线对于起始条件和终止条件之间传输的字节数没有限制。每个字节数据传输完成后,发送端需释放 SDA 总线并提供 1 个 SCL 时钟来接收应答信号。若接收端成功接收 8bit 数据,须在传输最后 1bit 数据的时钟结束之后置 SDA 为"0",发送端将此低电平作为数据传送成功的应答信号;1 个时钟周期之后,接收端释放 SDA 总线,准备接收新的数据。

I<sup>2</sup>C 总线在满足以下条件时终止数据传输:

- (1) 主设备作为发送端时,在接收到从设备的应答信号后,发送终止条件。

- (2) 主设备作为接收端时,在成功接收 8bit 数据后,发送"1"作为应答信号并随即发送终止条件。

#### 11.7 I2C 总线控制

本小节针对 CPU 作为主设备,JXR151T 作为从设备的情况,对 I<sup>2</sup>C 总线通信时序进行描述。

#### 11.7.1 指定地址写操作

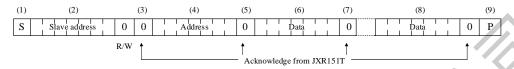

JXR151T 具有地址自动递增功能,设定好操作地址后,只需要连续发送数据即可,地址位可以自动递增。

图 11-4 指定地址写操作

- (1) CPU 发送起始条件[S]。

- (2) CPU 发送 JXR151T 从地址并通过 R/W 位设定为写模式。

- (3) JXR151T产生应答信号。

- (4) CPU 发送写寄存器地址到 JXR151T。

- (5) JXR151T产生应答信号。

- (6) CPU 发送数据至(4)中所指定地址对应的寄存器。

- (7) JXR151T产生应答信号。

- (8) 重复(6)(7)过程,JXR151T中写寄存器的地址会自动递增。

- (9) CPU 发送终止条件[P]。

#### 11.7.2 指定地址读操作

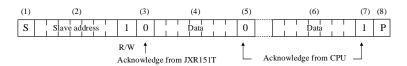

写入寄存器后, CPU 可以通过设置读模式读取寄存器数据。

图 11-5 指定地址读操作

- (1) CPU 发送起始条件[S]。

- (2) CPU 发送 JXR151T 从地址并通过 R/W 位设定为写模式。

- (3) JXR151T产生应答信号。

- (4) CPU 发送读寄存器地址到 JXR151T。

- (5) JXR151T产生应答信号。

- (6) CPU 重新发送起始条件。

- (7) CPU 发送 JXR151T 从地址并通过 R/W 位设定为读模式。

- (8) JXR151T产生应答信号;之后,CPU作为接收端,JXR151T作为发送端。

- (9) JXR151T 发送(4)中所指定地址对应的寄存器中的数据。

- (10)CPU 发送应答信号至 JXR151T。

- (11)重复(9)(10)过程,JXR151T中读寄存器的地址会自动递增。

- (12)CPU 发送应答信号至 JXR151T。

- (13)CPU 发送终止条件[P]。

#### 11.7.3 未指定地址读操作

主设备直接进入读模式可以读取从设备中所有寄存器的内容。若该操作之前进行了读操作,则从已读到的寄存器地址+1 继续读操作;若该操作之前进行了写操作,则从写操作对应的第一个寄存器地址开始进行读操作。

图 11-6 未指定地址读操作

- (1) CPU 发送起始条件[S]。

- (2) CPU 发送 JXR151T 从地址并通过 R/W 位设定为读模式。

- (3) JXR151T产生应答信号;之后,CPU作为接收端,JXR151T作为发送端。

- (4) JXR151T 自动递增寄存器地址,发送寄存器数据。

- (5) CPU 发送应答信号至 JXR151T。

- (6) 重复(4)(5)过程,JXR151T中读寄存器的地址会自动递增

- (7) CPU 发送应答信号至 JXR151T。

- (8) CPU 发送终止条件[P]。

# 附录

# 封装尺寸

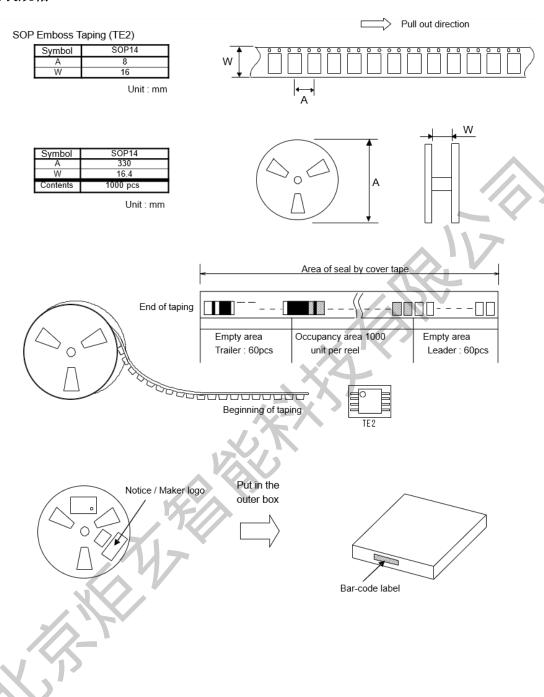

# 包装规格