#### ZHCS095A - MARCH 2011 - REVISED MARCH 2011

采用晶圆级芯片规模封装 (WCSP) 并具有两线式接口的

低功耗、数字温度传感器

查询样品: TMP103

## 特性

- 多器件存取 (MDA):

- 全局读/写操作

- I<sup>2</sup>C™/ SMBus™ 兼容型接口

- 分辨率: 8位

- 准确度: 典型值为 ±1℃ (—40℃ 至 +100℃)

- 低静态电流:

运行模式中的 l<sub>q</sub> 为 3µA (在 0.25Hz 频率条件下)

- 停机模式中为 lq 为 1µA

- 电源范围: 1.4V 至 3.6V

- 数字输出

- 封装: 4 焊球 WCSP (晶圆级芯片规模封装) (DSBGA)

#### 应用

- 手机

- 笔记本电脑

说明

TMP103 是一款采用 4 焊球晶圆级芯片规模封装 (WCSP) 的数字输出温度传感器。 TMP103 读取温度 的分辨率能够达到 1℃。

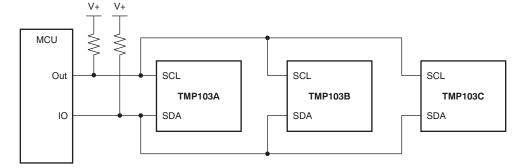

TMP103 具有一个与 I<sup>2</sup>C 和 SMBus 接口均兼容的两线 式接口。此外,该接口还支持多器件存取 (MDA) 命 令,允许主控器与总线上的多个器件同时进行通信,从 而不必向总线上的每个 TMP103 个别发送命令。

最多可以把 8 个 TMP103 并联连接起来,并由主机轻 松地对其进行读取。对于那些具有多个必须加以监视 的温度测量区域的空间受限、功耗敏感型应用而 言,TMP103 是特别理想的选择。

TMP103 的规定工作温度范围为一40℃ 至 +125℃。

典型应用

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SMBus is a trademark of Intel.

I<sup>2</sup>C is a trademark of NXP Semiconductors. All other trademarks are the property of their respective owners. 4

#### ZHCS095A - MARCH 2011 - REVISED MARCH 2011

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PACKAGE/ORDERING INFORMATION (1) |         |              |                       |                    |                    |  |  |

|----------------------------------|---------|--------------|-----------------------|--------------------|--------------------|--|--|

| PRODUCT                          | ADDRESS | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING | ORDERING<br>NUMBER |  |  |

| TMD4 02 A                        | 1110000 |              | VEE                   | TA                 | TMP103AYFFR        |  |  |

| TMP103A                          | 1110000 | DSBGA-4      | YFF                   | ТА                 | TMP103AYFFT        |  |  |

| TMP103B                          | 1110001 | DSBGA-4      | YFF                   | ТВ                 | TMP103BYFFR        |  |  |

| TIMP TU3D                        | 1110001 | DSBGA-4      | TEE                   | IB                 | TMP103BYFFT        |  |  |

| TMP103C                          | 1110010 | DSBGA-4      | YFF                   | тс                 | TMP103CYFFR        |  |  |

| TIMP 103C                        | 1110010 | DSBGA-4      | ĨFF                   | IC IC              | TMP103CYFFT        |  |  |

|                                  | 1110011 | DSBGA-4      | YFF                   | TD                 | TMP103DYFFR        |  |  |

| TMP103D                          | 1110011 | DSBGA-4      | TEE                   | TD                 | TMP103DYFFT        |  |  |

| TMP103E                          | 1110100 | DSBGA-4      | YFF                   | TE                 | TMP103EYFFR        |  |  |

| TMPTUSE                          | 1110100 | DSBGA-4      | TEE                   | IE                 | TMP103EYFFT        |  |  |

|                                  | 1110101 |              | YFF                   | TF                 | TMP103FYFFR        |  |  |

| TMP103F                          | 1110101 | DSBGA-4      | TEE                   | IF                 | TMP103FYFFT        |  |  |

| TMP103G                          | 1110110 | DSBGA-4      | YFF                   | TG                 | TMP103GYFFR        |  |  |

| TIVIF 103G                       | 1110110 | DODGA-4      | ĨſſŦ                  | 16                 | TMP103GYFFT        |  |  |

| TMP103H                          | 1110111 | DSBGA-4      | YFF                   | TH                 | TMP103HYFFR        |  |  |

|                                  |         | DODGA-4      | IFF                   | П                  | TMP103HYFFT        |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device prodict folder at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                              |                            | TMP103             | UNIT |

|------------------------------|----------------------------|--------------------|------|

| Supply Voltage               |                            | 3.6                | V    |

| Input Voltage <sup>(2)</sup> |                            | -0.3 to (V+) + 0.3 | V    |

| Operating Temperature        |                            | -55 to +150        | °C   |

| Storage Temperature          |                            | -60 to +150        | °C   |

| Junction Temper              | rature                     | +150               | °C   |

|                              | Human Body Model (HBM)     | 2000               | V    |

| ESD Rating                   | Charged Device Model (CDM) | 1000               | V    |

|                              | Machine Model (MM)         | 200                | V    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

(2) Input voltage rating applies to all TMP103 input voltages.

ZHCS095A - MARCH 2011 - REVISED MARCH 2011

## THERMAL INFORMATION

|                    |                                              | TMP103 |       |

|--------------------|----------------------------------------------|--------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | YFF    | UNITS |

|                    |                                              | 4      |       |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance       | 160    |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 75     |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance         | 76     | °C/W  |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 3      | C/W   |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 74     |       |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | N/A    |       |

(1) 有关传统和新的热度量的更多信息,请参阅 *IC* 封装热度量 应用报告 SPRA953。

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$  and V+ = +1.4V to +3.6V, unless otherwise noted.

|                                         |                 |                                                            | т        | MP103 |          |        |

|-----------------------------------------|-----------------|------------------------------------------------------------|----------|-------|----------|--------|

| PARAMETER                               |                 | TEST CONDITIONS                                            | MIN      | TYP   | MAX      | UNIT   |

| TEMPERATURE INPUT                       |                 |                                                            |          |       |          |        |

| Range                                   |                 |                                                            | -40      |       | +125     | °C     |

|                                         |                 | -10°C to +100°C, V+ = 1.8V                                 |          | 0     | ±2       | °C     |

| Accuracy (Temperature Error)            |                 | -40°C to +125°C, V+ = 1.8V                                 |          | ±1    | ±3       | °C     |

| vs Supply                               |                 |                                                            |          | ±0.2  | ±0.5     | °C/V   |

| Resolution                              |                 |                                                            |          | 1.0   |          | °C     |

| DIGITAL INPUT/OUTPUT                    |                 |                                                            |          |       |          |        |

| Input Logic Levels VIH                  |                 |                                                            | 0.7 (V+) |       | V+       | V      |

|                                         |                 |                                                            | -0.5     |       | 0.3 (V+) | V      |

| Input Current                           | I <sub>IN</sub> | $0 < V_{IN} < (V+) + 0.3V$                                 |          |       | 1        | μA     |

| Output Logic Levels V <sub>OL</sub> SDA |                 | V+ > 2V, I <sub>OL</sub> = 2mA                             | 0        |       | 0.4      | V      |

|                                         |                 | V+ < 2V, I <sub>OL</sub> = 2mA                             | 0        |       | 0.2 (V+) | V      |

| Resolution                              |                 |                                                            |          | 8     |          | Bit    |

| Conversion Time                         |                 |                                                            |          | 26    | 35       | ms     |

|                                         |                 | CR1 = 0, CR0 = 0 (default)                                 |          | 0.25  |          | Conv/s |

|                                         |                 | CR1 = 0, CR0 = 1                                           |          | 1     |          | Conv/s |

| Conversion Modes                        |                 | CR1 = 1, CR0 = 0                                           |          | 4     |          | Conv/s |

|                                         |                 | CR1 = 1, CR0 = 1                                           |          | 8     |          | Conv/s |

| Timeout Time                            |                 |                                                            |          | 30    | 40       | ms     |

| POWER SUPPLY                            |                 |                                                            |          |       |          |        |

| Operating Supply Range                  |                 |                                                            | +1.4     |       | +3.6     | V      |

|                                         |                 | Serial Bus Inactive, CR1 = 0, CR0 = 0 (default), V+ = 1.8V |          | 1.5   | 3        | μA     |

| Quiescent Current                       | Ι <sub>Q</sub>  | Serial Bus Active, SCL Frequency = 400kHz                  |          | 15    |          | μA     |

|                                         |                 | Serial Bus Active, SCL Frequency = 3.4MHz                  |          | 85    |          | μA     |

| Shutdown Current I <sub>SD</sub>        |                 | Serial Bus Inactive, V+ = 1.8V                             |          | 0.5   | 1        | μA     |

|                                         |                 | Serial Bus Active, SCL Frequency = 400kHz                  |          | 10    |          | μA     |

|                                         |                 | Serial Bus Active, SCL Frequency = 3.4MHz                  |          | 80    |          | μA     |

| TEMPERATURE                             |                 |                                                            |          |       |          |        |

| Specified Range                         |                 |                                                            | -40      |       | +125     | °C     |

| Operating Range                         |                 |                                                            | -55      |       | +150     | °C     |

TEXAS INSTRUMENTS

ZHCS095A-MARCH 2011-REVISED MARCH 2011

www.ti.com.cn

### **PIN CONFIGURATION**

| YFF PACKAGE<br>WCSP-4 (DSBGA-4)<br>(TOP VIEW) |          |          |     |  |  |

|-----------------------------------------------|----------|----------|-----|--|--|

| SCL                                           | В2<br>() | В1<br>() | SDA |  |  |

| GND                                           | A2<br>() | A1       | V+  |  |  |

#### **PIN DESCRIPTIONS**

| P   | IN   |                       |

|-----|------|-----------------------|

| NO. | NAME | DESCRIPTION           |

| A1  | V+   | Supply voltage        |

| A2  | GND  | Ground                |

| B1  | SDA  | Input/output data pin |

| B2  | SCL  | Input clock pin       |

ZHCS095A - MARCH 2011 - REVISED MARCH 2011

#### www.ti.com.cn

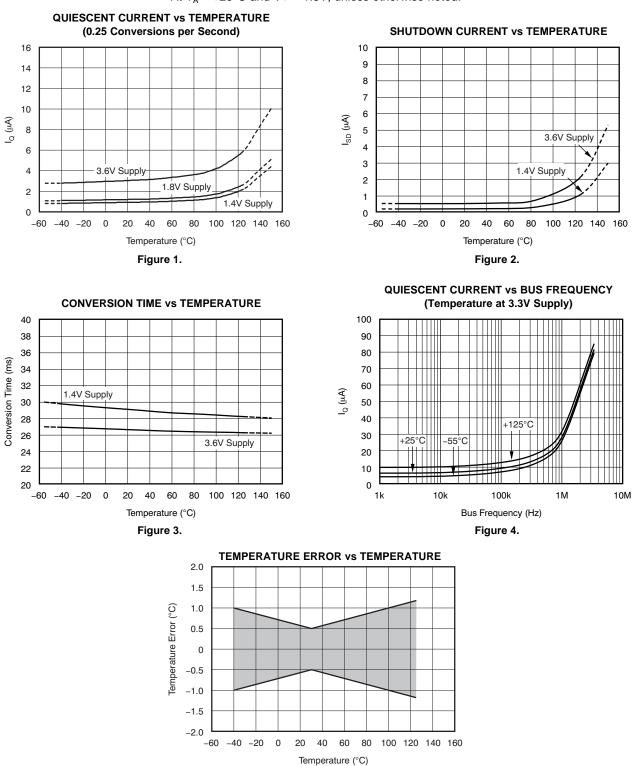

### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$  and V+ = 1.8V, unless otherwise noted.

## **APPLICATION INFORMATION**

### **GENERAL DESCRIPTION**

The TMP103 is a digital output temperature sensor in a wafer chip-scale package (WCSP) that is optimal for thermal management and thermal profiling. The TMP103 includes a two-wire interface that is compatible with both  $l^2$ C and SMBus interfaces. In addition, the TMP103 has the capability of executing multiple device access (MDA) commands that allow multiple TMP103s to respond to a single global bus command. MDA commands reduce communication time and power in a bus that contains multiple TMP103 devices. The TMP103 is specified over a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

The TMP103 serial interface is designed to support up to eight TMP103 devices on a single bus. The TMP103 is offered with eight internal interface addresses. Each unique address option can be used as a location or temperature zone designator. The TMP103 responds to standard I<sup>2</sup>C/SMBus slave protocols that allow the internal registers to be written to or read from on an individual basis. The TMP103 also responds to MDA commands that allow all the devices on the bus to be written to or read from, without having to send the individual address and commands to each device.

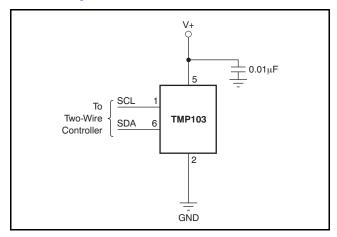

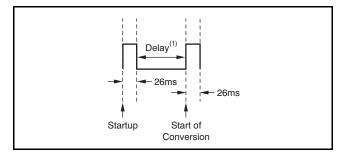

Pull-up resistors are required on SCL and SDA. A  $0.01\mu F$  bypass capacitor is also recommended, as shown in Figure 6.

NOTE: SCL and SDA pins require pull-up resistors.

## Figure 6. Typical Connections

The temperature sensor in the TMP103 is the chip itself. Thermal paths run through the package bumps as well as the package. The lower thermal resistance of metal causes the bumps to provide the primary thermal path.

To maintain accuracy in applications that require air or surface temperature measurement, care should be taken to isolate the package from ambient air temperature.

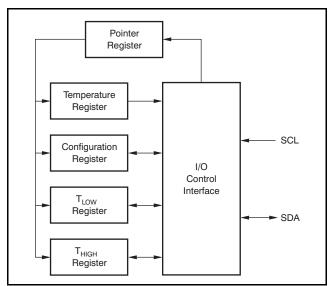

## POINTER REGISTER

Figure 7 shows the internal register structure of the TMP103. The 8-bit Pointer Register of the device is used to address a given data register. The Pointer Register uses the two LSBs to identify which of the data registers should respond to a read or write command. Table 1 identifies the bits of the Pointer Register byte. During a write command, P2 through P7 must always be '0'. Table 2 describes the pointer address of the registers available in the TMP103. Power-up reset value of P1/P0 is '00'. By default, the TMP103 reads the temperature on power-up.

Figure 7. Internal Register Structure

#### Table 1. Pointer Register Byte

| P7 | P6 | P5 | P4 | P3 | P2 | <b>P</b> 1    | P0 |

|----|----|----|----|----|----|---------------|----|

| 0  | 0  | 0  | 0  | 0  | 0  | Register Bits |    |

#### **Table 2. Pointer Addresses**

| P1 | P0 | REGISTER                                |

|----|----|-----------------------------------------|

| 0  | 0  | Temperature Register (Read Only)        |

| 0  | 1  | Configuration Register (Read/Write)     |

| 1  | 0  | T <sub>LOW</sub> Register (Read/Write)  |

| 1  | 1  | T <sub>HIGH</sub> Register (Read/Write) |

#### ZHCS095A - MARCH 2011 - REVISED MARCH 2011

#### **TEMPERATURE REGISTER**

The Temperature Register of the TMP103 is configured as an eight-bit, read-only register that stores the output of the most recent conversion. A single byte must be read to obtain data, and is described in Table 3. The data format for temperature is summarized in Table 4. One LSB equals 1°C.

#### Table 3. Temperature Register

|    |    |    | -  |    | -  |    |    |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| T7 | T6 | T5 | T4 | Т3 | T2 | T1 | то |

Negative numbers are represented in binary twos complement format. Following power-up or reset, the Temperature Register reads 0°C until the first conversion is complete.

| TEMPERATURE (°C) | DIGITAL OUTPUT (BINARY) | HEX |

|------------------|-------------------------|-----|

| 128              | 0111 1111               | 7F  |

| 127              | 0111 1111               | 7F  |

| 100              | 0110 0100               | 64  |

| 80               | 0101 0000               | 50  |

| 75               | 0100 1011               | 4B  |

| 50               | 0011 0010               | 32  |

| 25               | 0001 1001               | 19  |

| 0                | 0000 0000               | 00  |

| -1               | 1111 1111               | FF  |

| -25              | 1110 0111               | E7  |

| -55              | 1100 1001               | C9  |

(1) The resolution for the ADC is 1°C/count, where *count* is equal to the digital output of the ADC.

#### For positive temperatures (for example, +50°C):

Twos complement is not performed on positive numbers. Therefore, simply convert the number to binary code, left-justified format. Denote a positive number with MSB = '0'. Example:  $(+50^{\circ}C)/(1^{\circ}C/count) = 50 = 32h = 0011\ 0010$

For negative temperatures (for example, -25°C):

Generate the twos complement of a negative number by complementing the absolute value binary number and adding 1. Denote a negative number with MSB = '1'.

Example: (|-25°C|)/(1°C/count) = 25 = 19h = 0001 1001

Twos complement format: 1110 0110 + 1 = 1110 0111

## CONFIGURATION REGISTER

The Configuration Register is an eight-bit read/write register used to store bits that control the operational modes of the temperature sensor. Read/write operations are performed MSB first. The format and power-up/reset value of the Configuration Register is shown in Table 5. All registers are updated at the end of the data byte.

Table 5. Configuration and Power-Up/Reset Format

| D7 | D6  | D5  | D4 | D3 | D2 | D1 | D0 |

|----|-----|-----|----|----|----|----|----|

| ID | CR1 | CR0 | FH | FL | LC | M1 | MO |

| 0  | 0   | 0   | 0  | 0  | 0  | 1  | 0  |

## **TEMPERATURE WATCHDOG FUNCTION**

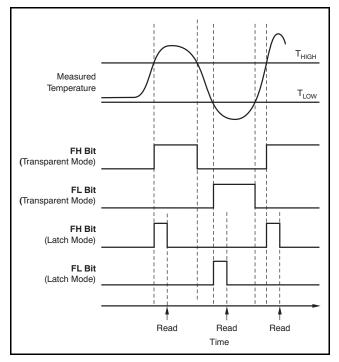

The TMP103 contains a watchdog function that monitors device temperature and compares the result to the values stored in the temperature limit registers ( $T_{HIGH}$  and  $T_{LOW}$ ) in order to determine if the device temperature is within these set limits. If the temperature of the TMP103 becomes greater than the value in the  $T_{HIGH}$  register, then the flag-high bit (FH) in the configuration register is set to '1'. If the temperature falls below value in the  $T_{LOW}$  register, then the flag-low bit (FL) is set to '1'. If both flag bits remain '0', then the temperature is within the temperature window set by the temperature limit registers, as shown in Figure 8.

www.ti.com.cn

The latch bit (LC) in the configuration register is used to latch the value of the flag bits (FH and FL) until the master issues a read command to the configuration register. The flag bits are set to '0' if a read command is received by the TMP103, or if LC = '0' and the temperature is within the temperature limits. The power-on default values for these bits are FH = '0', FL = '0', and LC = '0'.

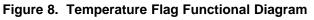

# CONVERSION RATE

The conversion rate bits, CR1 and CR0 located in the Configuration Register, configure the TMP103 for conversion rates of 8Hz, 4Hz, 1Hz, or 0.25Hz (default). The TMP103 has a typical conversion time of 26ms. To achieve different conversion rates, the TMP103 performs a single conversion and then powers down and waits for the appropriate delay set by CR1 and CR0. Table 6 shows the settings for CR1 and CR0.

Table 6. Conversion Rate Settings

| CR1 | CR0 | CONVERSION RATE  |

|-----|-----|------------------|

| 0   | 0   | 0.25Hz (default) |

| 0   | 1   | 1Hz              |

| 1   | 0   | 4Hz              |

| 1   | 1   | 8Hz              |

After power-up or general-call reset, the TMP103 immediately starts a conversion, as shown in Figure 9. The first result is available after 26ms (typical). The active quiescent current during conversion is 40 $\mu$ A (typical at +27°C, V+ = 1.8V). The quiescent current during delay is 1.0 $\mu$ A (typical at +27°C, V+ = 1.8V).

(1) Delay is set by CR1 and CR0.

Figure 9. Conversion Start

# SHUTDOWN MODE (M1 = '0', M0 = '0')

Shutdown mode saves maximum power by shutting down all device circuitry other than the serial interface, reducing current consumption to typically less than  $0.5\mu$ A. Shutdown mode is enabled when bits M1 and M0 (in the Configuration Register) = '00'. The device shuts down when the current conversion is completed.

#### ONE-SHOT (M1 = '0', M0 = '1')

The TMP103 features a One-Shot Temperature Measurement mode. When the device is in Shutdown mode, writing a '01' to bits M1 and M0 starts a single temperature conversion. During the conversion, bits M1 and M0 read '01'. The device returns to the shutdown state at the completion of the single conversion. After the conversion, bits M1 and M0 read '00'. This feature is useful for reducing power consumption in the TMP103 when continuous temperature monitoring is not required.

As a result of the short conversion time, the TMP103 can achieve a higher conversion rate. A single conversion typically takes 26ms and a read can take place in less than 20µs. When using One-Shot mode, 30 or more conversions per second are possible.

#### CONTINUOUS CONVERSION MODE (M1 = '1')

When the TMP103 is in Continuous Conversion mode (M1 = '1'), a single conversion is performed at a rate determined by the conversion rate bits, CR1 and CR0 (in the Configuration Register). The TMP103 performs a single conversion and then powers down and waits for the appropriate delay set by CR1 and CR0. See Table 6 for CR1 and CR0 settings.

#### **TEMPERATURE LIMIT REGISTERS**

The  $T_{HIGH}$  and  $T_{LOW}$  registers are used to store the temperature limit thresholds for the TMP103 watchdog function. At the end of each temperature measurement, the TMP103 compares the temperature results to each of these limits. If the temperature result is greater than the  $T_{HIGH}$  limit, then the FH bit in the configuration register is set to '1'. If the temperature result is less than the  $T_{LOW}$  limit, then the FL bit in the configuration register is set to '1'; see Figure 8.

Table 7 and Table 8 describe the format for the  $T_{HIGH}$  and  $T_{LOW}$  registers. Power-up reset values for  $T_{HIGH}$  and  $T_{LOW}$  are:  $T_{HIGH} = +60^{\circ}$ C and  $T_{LOW} = -10^{\circ}$ C. The format of the data for  $T_{HIGH}$  and  $T_{LOW}$  is the same as for the Temperature Register.

TMP103

#### Table 7. T<sub>HIGH</sub> Register

| ······ • |       |    |    |    |    |    |    |  |

|----------|-------|----|----|----|----|----|----|--|

| D7       | D6 D5 |    | D4 | D3 | D2 | D1 | D0 |  |

| H7       | H6    | H5 | H4 | H3 | H2 | H1 | HO |  |

#### Table 8. T<sub>LOW</sub> Register

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| L7 | L6 | L5 | L4 | L3 | L2 | L1 | L0 |

#### **BUS OVERVIEW**

The device that initiates the transfer is called a *master*, and the devices controlled by the master are *slaves*. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions.

To address a specific device, a START condition is initiated, indicated by pulling the data line (SDA) from a high to low logic level while SCL is high. All slaves on the bus shift in the slave address byte on the rising edge of the clock, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the slave being addressed responds to the master by generating an Acknowledge and pulling SDA low.

Data transfer is then initiated and sent over eight clock pulses followed by an Acknowledge Bit. During data transfer, SDA must remain stable while SCL is high, because any change in SDA while SCL is high is interpreted as a START or STOP signal.

Once all data have been transferred, the master generates a STOP condition indicated by pulling SDA from low to high, while SCL is high.

#### SERIAL INTERFACE

The TMP103 operates as a slave device only on the two-wire bus and SMBus. Connections to the bus are made via the open-drain I/O lines SDA and SCL. The SDA and SCL pins feature integrated spike suppression filters and Schmitt triggers to minimize the effects of input spikes and bus noise. The TMP103 supports the transmission protocol for both fast (1kHz to 400kHz) and high-speed (1kHz to 3.4MHz) modes. All data bytes are transmitted MSB first.

## SERIAL BUS ADDRESS

To communicate with the TMP103, the master must first address slave devices via a slave address byte. The slave address byte consists of seven address bits, and a direction bit that indicates the intent of executing a read or write operation.

The TMP103 is available in eight versions, each with a different slave address, as shown in Table 9. These addresses can be used as either a location or a temperature zone designator.

| PRODUCT | TWO-WIRE<br>ADDRESS | TEMPERATURE<br>ZONE |  |  |  |

|---------|---------------------|---------------------|--|--|--|

| TMP103A | 1110000             | Zone1               |  |  |  |

| TMP103B | 1110001             | Zone2               |  |  |  |

| TMP103C | 1110010             | Zone3               |  |  |  |

| TMP103D | 1110011             | Zone4               |  |  |  |

| TMP103E | 1110100             | Zone5               |  |  |  |

| TMP103F | 1110101             | Zone6               |  |  |  |

| TMP103G | 1110110             | Zone7               |  |  |  |

| TMP103H | 1110111             | Zone8               |  |  |  |

Table 9. Device Slave Addresses

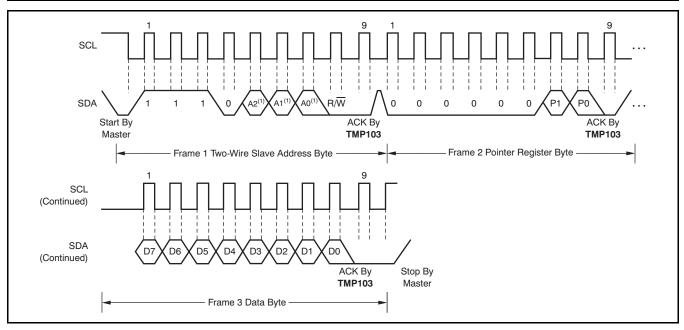

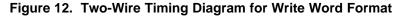

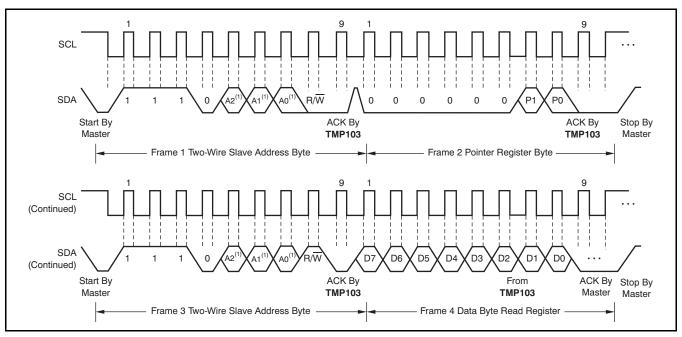

## WRITING/READING OPERATION

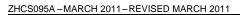

Accessing a particular register on the TMP103 is accomplished by writing the appropriate value to the Pointer Register. The value for the Pointer Register is the first byte transferred after the slave address byte with the R/W bit low. Every write operation to the TMP103 requires a value for the Pointer Register (see Figure 12).

When reading from the TMP103, the last value stored in the Pointer Register by a write operation is used to determine which register is read by a read operation. To change the register pointer for a read operation, a new value must be written to the Pointer Register. This action is accomplished by issuing a slave address byte with the R/W bit low, followed by the Pointer Register byte. No additional data are required. The master can then generate a START condition and send the slave address byte with the R/W bit high to initiate the read command. See Figure 13 for details of this sequence. If repeated reads from the same register are desired, it is not necessary to continually send the Pointer Register bytes; the TMP103 remembers the Pointer Register value until it is changed by the next write operation, or the TMP103 is reset.

## SLAVE MODE OPERATIONS

The TMP103 can operate as a slave receiver or slave transmitter. As a slave device, the TMP103 never drives the SCL line.

### Slave Receiver Mode

The first byte transmitted by the master is the slave address, with the R/W bit low. The TMP103 then acknowledges reception of a valid address. The next byte transmitted by the master is the Pointer Register. The TMP103 then acknowledges reception of the Pointer Register byte. The next byte is written to the register addressed by the Pointer Register. The TMP103 acknowledges reception of the data byte. The master can terminate data transfer by generating a START or STOP condition.

### Slave Transmitter Mode

The first byte transmitted by the master is the slave address, with the R/W bit high. The slave acknowledges reception of a valid slave address. The next byte is transmitted by the slave of the register indicated by the Pointer Register. The master acknowledges reception of the data byte. The master can terminate data transfer by generating a *Not-Acknowledge* on reception of the data byte, or generating a START or STOP condition.

## GENERAL CALL

The TMP103 responds to a two-wire General Call address (0000000) if the eighth bit is '0'. The device acknowledges the General Call address and responds to commands in the second byte. If the second byte is 00000110, the TMP103 internal registers are reset to power-up values. The TMP103 does not support the General Address acquire command.

## HIGH-SPEED (Hs) MODE

In order for the two-wire bus to operate at frequencies above 400kHz, the master device must issue an Hs-mode master code (00001xxx) as the first byte after a START condition to switch the bus to high-speed operation. The TMP103 does not acknowledge this byte, but switches its input filters on SDA and SCL and its output filters on SDA to operate in Hs-mode, allowing transfers at up to 3.4MHz. After the Hs-mode master code has been issued, the master transmits a START condition followed by a two-wire slave address to initiate a data transfer operation. The bus continues to operate in Hs-mode until a STOP condition occurs on the bus. Upon receiving the STOP condition, the TMP103 switches the input and output filters back to the default fast-mode operation.

## TIMEOUT FUNCTION

The TMP103 resets the serial interface if SCL is held low for 30ms (typ). The TMP103 releases the bus if it is pulled low and waits for a START condition. To avoid activating the timeout function, it is necessary to maintain a communication speed of at least 1kHz for SCL operating frequency.

## MULTIPLE DEVICE ACCESS

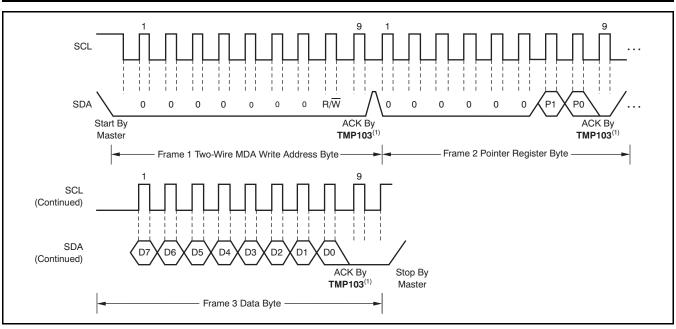

The TMP103 supports Multiple Device Access (MDA), which allows the master to communicate with multiple TMP103 devices on the same bus interface with one interface transaction. MDA commands consist of an MDA read address (00000001) and an MDA write address (00000000). The device acknowledges the MDA address and responds to the command accordingly. In order for MDA to function correctly, different product versions of the TMP103 must be used in the system; see Table 9.

## Multiple Device Access Write

The master transmits an MDA write address followed by the pointer address of the register to be accessed; see Table 2. Following the pointer, all of the TMP103 devices on the bus acknowledge and wait for the next byte of data to be written to the addressed registers. When the data byte is received by the TMP103 devices, they store and acknowledge the transmitted byte. The TMP103s store the same data on all devices on the bus in one transaction; see Figure 14.

## **Multiple Device Access Read**

Note that before an MDA read transaction can begin, the master must first send an MDA write transaction in order to set the appropriate pointer address of the register to be accessed, as stated in the previous section. The master can then transmit an MDA read address followed by a read byte for each TMP103 used on the bus. For example, if a TMP103A and TMP103B are used on the same bus and an MDA read address is sent, the address must be followed by two bytes of data and two master acknowledges. The TMP103A sends data on the first byte and the TMP103B sends data on the second byte. The master must issue an acknowledge for each byte read in order to read all of the TMP103 devices on the bus; see Figure 15. If the master does not acknowledge each byte of data, the TMP103s stop sending subsequent data for any remaining devices.

ZHCS095A - MARCH 2011 - REVISED MARCH 2011

Up to eight TMP103 devices can be on the same bus and respond to MDA commands; see Table 9.

**NOTE:** If the bus contains an incomplete sequence of TMP103 device addresses, the master must transmit all required dummy bytes for the missing device address to allow for normal MDA read operation. For example, if the TMP103A, TMP103B, and TMP103D devices are on the bus, the master must transmit an MDA read address followed by four bytes and four acknowledges in order to complete the MDA read transaction.

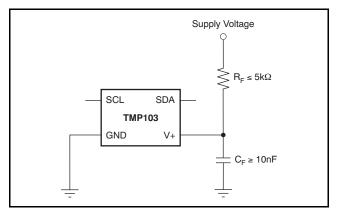

#### NOISE

The TMP103 is a very low-power device and generates very low noise on the supply bus. Applying an RC filter to the V+ pin of the TMP103 can further reduce any noise the TMP103 might propagate to other components.  $R_F$  in Figure 10 should be less than 5k $\Omega$  and  $C_F$  should be greater than 10nF.

Figure 10. Noise Reduction

#### ZHCS095A-MARCH 2011-REVISED MARCH 2011

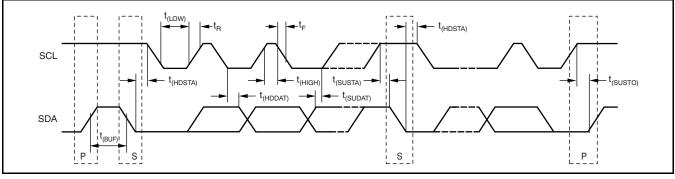

#### TIMING DIAGRAMS

The TMP103 is two-wire and SMBus compatible. Figure 11 to Figure 15 describe the various operations on the TMP103. Parameters for Figure 11 are defined in Table 10. Bus definitions are:

Bus Idle: Both SDA and SCL lines remain high.

**Start Data Transfer:** A change in the state of the SDA line, from high to low, while the SCL line is high, defines a START condition. Each data transfer is initiated with a START condition.

**Stop Data Transfer:** A change in the state of the SDA line from low to high while the SCL line is high defines a STOP condition. Each data transfer is terminated with a repeated START or STOP condition.

**Data Transfer:** The number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device.

Acknowledge: Each receiving device, when addressed, is obliged to generate an Acknowledge bit. A device that acknowledges must pull down the SDA line during the Acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the Acknowledge clock pulse. Setup and hold times must be taken into account. On a master receive, the termination of the data transfer can be signaled bv the master generating а Not-Acknowledge ('1') on the last byte that has been transmitted by the slave.

NOTE: P = STOP, S = START.

#### Figure 11. Two-Wire Timing Diagram

|                      |                                                | FAST  | MODE | HIGH-SPE |      |      |

|----------------------|------------------------------------------------|-------|------|----------|------|------|

|                      | PARAMETER                                      | MIN   | MAX  | MIN      | MAX  | UNIT |

| f <sub>(SCL)</sub>   | SCL Operating Frequency, V <sub>S</sub> > 1.7V | 0.001 | 0.4  | 0.001    | 3.4  | MHz  |

| f <sub>(SCL)</sub>   | SCL Operating Frequency, V <sub>S</sub> < 1.7V | 0.001 | 0.4  | 0.001    | 2.75 | MHz  |

| t <sub>(BUF)</sub>   | Bus Free Time Between STOP and START Condition | 600   |      | 160      |      | ns   |

| t <sub>(HDSTA)</sub> | Hold time after repeated START condition.      |       |      | 100      |      | ns   |

| t <sub>(SUSTA)</sub> | Repeated START Condition Setup Time            | 100   |      | 100      |      | ns   |

| t <sub>(SUSTO)</sub> | STOP Condition Setup Time                      | 100   |      | 100      |      | ns   |

| t <sub>(HDDAT)</sub> | Data Hold Time                                 | 0     |      | 0        |      | ns   |

| t <sub>(SUDAT)</sub> | Data Setup Time                                | 100   |      | 10       |      | ns   |

| t <sub>(LOW)</sub>   | SCL Clock Low Period, V <sub>S</sub> > 1.7V    | 1300  |      | 160      |      | ns   |

| t <sub>(LOW)</sub>   | SCL Clock Low Period, V <sub>S</sub> < 1.7V    | 1300  |      | 200      |      | ns   |

| t <sub>(HIGH)</sub>  | SCL Clock High Period                          | 600   |      | 60       |      | ns   |

| t <sub>F</sub>       | Clock/Data Fall Time                           |       | 300  |          |      | ns   |

| t <sub>R</sub>       | Clock/Data Rise Time                           |       | 300  |          | 160  | ns   |

| t <sub>R</sub>       | Clock/Data Rise Time for SCLK ≤ 100kHz         |       | 1000 |          |      | ns   |

#### Table 10. Timing Diagram Definitions

ZHCS095A - MARCH 2011 - REVISED MARCH 2011

(1) The value of A0, A1, and A2 are determined by the TMP103 version; see Table 9.

(1) The value of A0, A1, and A2 are determined by the TMP103 version; see Table 9.

Figure 13. Two-Wire Timing Diagram for Read Word Format

(1) All TMP103 devices on the bus acknowledge the byte.

Figure 14. Two-Wire Timing Diagram MDA Write Word Format

(1) All TMP103 devices on the bus acknowledge the byte.

(2) The master must issue an acknowledge for each byte read in order to read all of the TMP103 devices on the bus.

(3) Three TMP103 devices used in this case; up to eight devices can be used (see Table 9).

Figure 15. Two-Wire Timing Diagram MDA Read Word Format Using Typical Application (Front Page)

| Cł | nanges from Original (February 2011) to Revision A                                | Page |

|----|-----------------------------------------------------------------------------------|------|

| •  | Changed Package-Lead from WCSP-4 to DSBGA-4 in Package/Ordering Information table | 2    |

# **REVISION HISTORY**

#### TEXAS INSTRUMENTS

www.ti.com.cn

#### 重要声明

德州仪器 (TI)及其下属子公司有权在不事先通知的情况下,随时对所提供的产品和服务进行更正、修改、增强、改进或其它更改,并有权随时中止提供任何产品和服务。客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的 TI 销售条款与条件。

TI 保证其所销售的硬件产品的性能符合 TI 标准保修的适用规范。 仅在 TI 保修的范围内,且 TI 认为有必要时才会使用测试或其它质量控制技术。 除非政府做出了硬性规定,否则没有必要对每种产品的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 产品或服务的组合设备、机器、流程相关的 TI 知识产权中授予的直接 或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服务的许可、授 权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它知识产权方面的许 可。

对于 TI 的数据手册或数据表,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。在复制信息的过程中对内容的篡改属于非法的、欺诈性商业行为。 TI 对此类篡改过的文件不承担任何责任。

在转售 TI 产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关 TI 产品或服务的明示或暗示授权,且这是非法的、 欺诈性商业行为。 TI 对此类虚假陈述不承担任何责任。

可访问以下 URL 地址以获取有关其它 TI 产品和应用解决方案的信息:

产品

| 放大器   | http://www.ti.com.cn/amplifiers       |

|-------|---------------------------------------|

| 数据转换器 | http://www.ti.com.cn/dataconverters   |

| DSP   | http://www.ti.com.cn/dsp              |

| 接口    | http://www.ti.com.cn/interface        |

| 逻辑    | http://www.ti.com.cn/logic            |

| 电源管理  | http://www.ti.com.cn/power            |

| 微控制器  | http://www.ti.com.cn/microcontrollers |

| 应用    |                                       |

| 音频    | http://www.ti.com.cn/audio            |

| 汽车    | http://www.ti.com.cn/automotive       |

| 宽带    | http://www.ti.com.cn/broadband        |

| 数字控制  | http://www.ti.com.cn/control          |

| 光纤网络  | http://www.ti.com.cn/opticalnetwork   |

| 安全    | http://www.ti.com.cn/security         |

| 电话    | http://www.ti.com.cn/telecom          |

| 视频与成像 | http://www.ti.com.cn/video            |

| 无线    | http://www.ti.com.cn/wireless         |

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2006, Texas Instruments Incorporated

10-Dec-2020

## **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TMP103AYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТА                      | Samples |

| TMP103AYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТА                      | Samples |

| TMP103BYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТВ                      | Samples |

| TMP103BYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТВ                      | Samples |

| TMP103CYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | тс                      | Samples |

| TMP103CYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТС                      | Samples |

| TMP103DYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TD                      | Samples |

| TMP103DYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TD                      | Samples |

| TMP103EYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TE                      | Samples |

| TMP103EYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TE                      | Samples |

| TMP103FYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TF                      | Samples |

| TMP103FYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TF                      | Samples |

| TMP103GYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TG                      | Samples |

| TMP103GYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TG                      | Samples |

| TMP103HYFFR      | ACTIVE        | DSBGA        | YFF                | 4    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | ТН                      | Samples |

| TMP103HYFFT      | ACTIVE        | DSBGA        | YFF                | 4    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | TH                      | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

10-Dec-2020

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

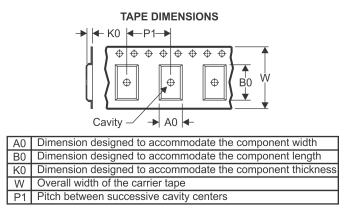

## TAPE AND REEL INFORMATION

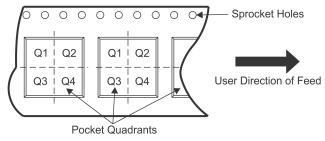

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMP103AYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103AYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103BYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103BYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103CYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103CYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103DYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103DYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103EYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103EYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103FYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103FYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103GYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103GYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103HYFFR | DSBGA           | YFF                | 4    | 3000 | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

| TMP103HYFFT | DSBGA           | YFF                | 4    | 250  | 180.0                    | 8.4                      | 0.85       | 0.85       | 0.64       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

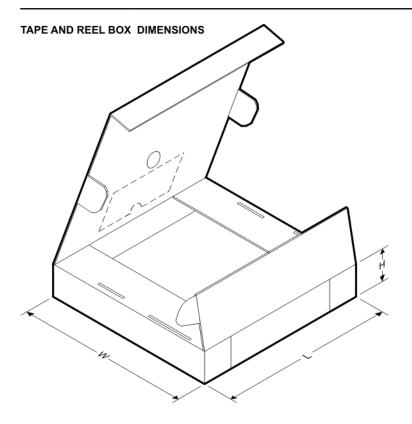

# PACKAGE MATERIALS INFORMATION

22-May-2020

| *All dimensions are nominal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TMP103AYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103AYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103BYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103BYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103CYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103CYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103DYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103DYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103EYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103EYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103FYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103FYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103GYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103GYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

| TMP103HYFFR                 | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |

| TMP103HYFFT                 | DSBGA        | YFF             | 4    | 250  | 182.0       | 182.0      | 20.0        |

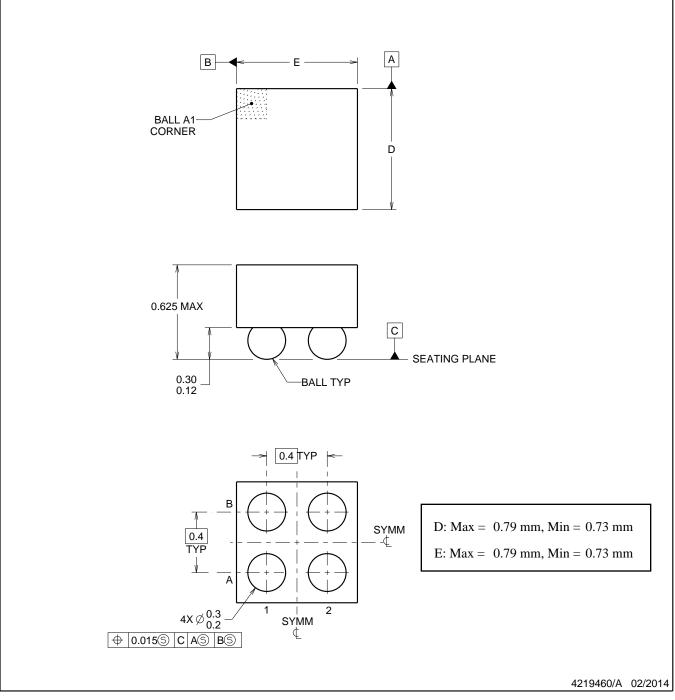

# **YFF0004**

# **PACKAGE OUTLINE**

# DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES:

NanoFree Is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. NanoFree<sup>™</sup> package configuration.

# YFF0004

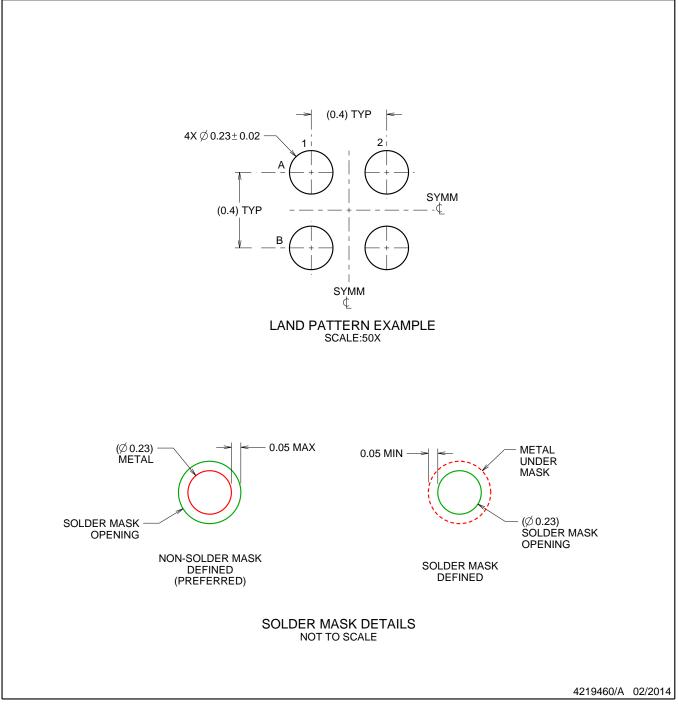

# **EXAMPLE BOARD LAYOUT**

## DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. For more information, see Texas Instruments literature number SBVA017 (www.ti.com/lit/sbva017).

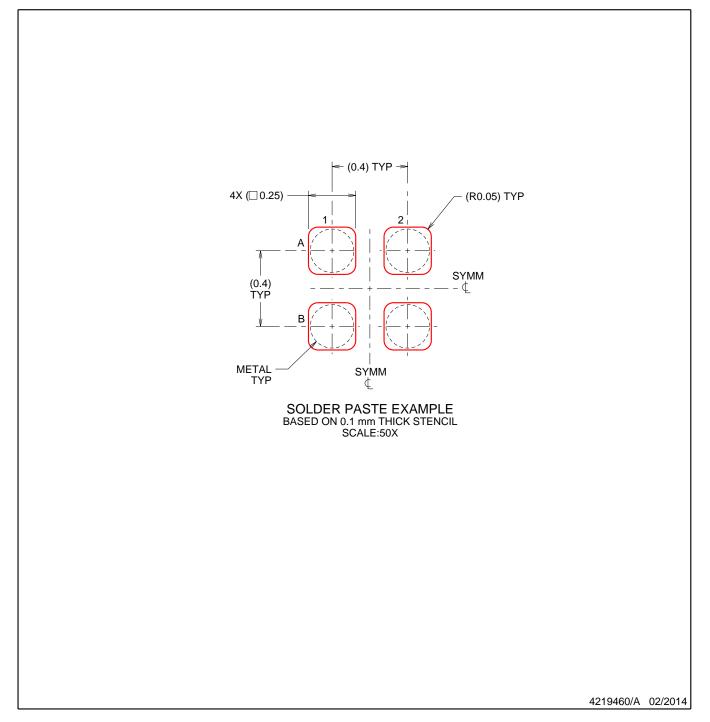

# YFF0004

# **EXAMPLE STENCIL DESIGN**

# DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司