#### **General Description**

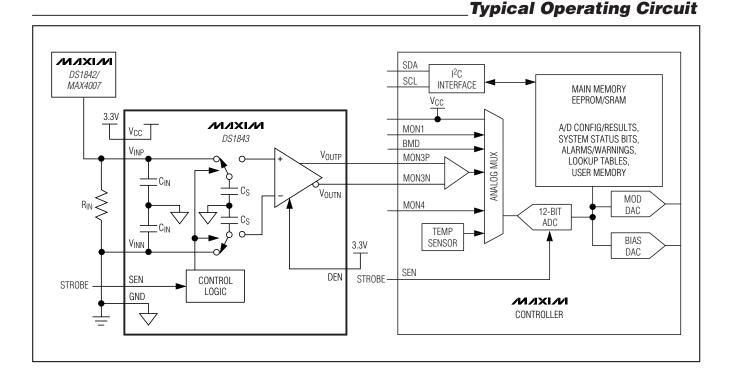

The DS1843 is a sample-and-hold circuit useful for capturing fast signals where board space is constrained. It includes a differential, high-speed switched capacitor input sample stage, offset nulling circuitry, and an output buffer. The DS1843 is optimized for use in optical line transmission (OLT) systems for burst-mode RSSI measurement in conjunction with an external sense resistor.

#### **Applications**

Gigabit Passive Optical Network (GPON) OLT Gigabit Ethernet Passive Optical Network (GEPON) OLT **GPON Optical Network Unit** Sample and Hold

#### Features

- Fast Sample Time < 300ns</p>

- ♦ Hold Time > 100µs

- Low Input Offset

- Buffered Output

- Small, 8-Pin µDFN (2mm x 2mm) Pb-Free Package

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| DS1843D+    | -40°C to +85°C | 8 µDFN      |

| DS1843D+TRL | -40°C to +85°C | 8 µDFN      |

+Denotes a lead(Pb)-free/RoHS-compliant package. TRL = Tape and reel.

Pin Configuration appears at end of data sheet.

or visit Maxim's website at www.maxim-ic.com.

Maxim Integrated Products 1

DS1843

# For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

# **DS1843**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>CC</sub>                    | 0.5V to +6V                       |

|-----------------------------------------------------|-----------------------------------|

| Voltage Range on VOUTP, VOUTN,                      |                                   |

| VINP, VINN, SEN, DEN(                               | 0.5V to (V <sub>CC</sub> + 0.5V)* |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ | ;)                                |

| µDFN (derate 4.8mW/°C above +70°C)                  |                                   |

|                                                     |                                   |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Storage Temperature Range         | 55°C to +125°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

\*Subject to not exceeding +6V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER      | SYMBOL          | CONDITIONS | MIN   | ТҮР | MAX  | UNITS |

|----------------|-----------------|------------|-------|-----|------|-------|

| Supply Voltage | V <sub>CC</sub> | (Note 1)   | +2.97 |     | +5.5 | V     |

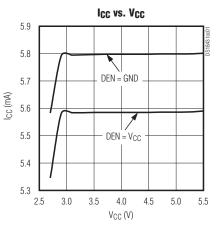

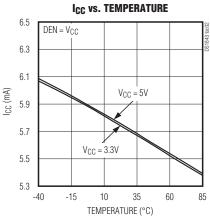

#### DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +2.97V to +5.5V, T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.)

| PARAMETER                      | SYMBOL           | CONDITIONS                                                                  | MIN                      | ТҮР | MAX                      | UNITS |

|--------------------------------|------------------|-----------------------------------------------------------------------------|--------------------------|-----|--------------------------|-------|

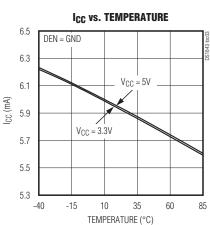

| Supply Current                 | ICC              | (Note 1)                                                                    |                          | 5.7 | 9                        | mA    |

| Input Capacitance              | CIN              | All pins (Note 2)                                                           |                          |     | 7                        | pF    |

| Sample Capacitance             | Cs               | V <sub>INN</sub> and V <sub>INP</sub> (Note 2)                              |                          | 5   |                          | pF    |

| Logic-Input Low                | VIL              | SEN and DEN inputs                                                          |                          |     | 0.3 x<br>V <sub>CC</sub> | V     |

| Logic-Input High               | VIH              | SEN and DEN inputs                                                          | 0.7 x<br>V <sub>CC</sub> |     |                          | V     |

| Input Leakage                  | lin              | $V_{INN}$ or $V_{INP}$ , SEN = 0                                            |                          |     | 1                        | μA    |

| Input Voltage                  | V <sub>IN</sub>  | $V_{IN} = V_{INP} - V_{INN}$                                                | 0                        |     | 1.0                      | V     |

| Output Voltage                 | V <sub>OUT</sub> | $V_{OUT}$ = $V_{OUTP}$ - $V_{OUTN}$ ; 100k $\Omega$ load on each output pin | 0                        |     | 1.0                      | V     |

| Output Impedance               | ROUTMAX          | (Note 2)                                                                    |                          | 1   | 1.3                      | kΩ    |

| Output Capacitive Load         | Cout             | Capacitance for stable operation                                            |                          |     | 50                       | pF    |

| Total Input Referenced Voltage |                  | $V_{CC}$ = 2.9V, 1µs sample time, $V_{IN}$ = 6mV                            |                          | 3.6 | 6.1                      | mV    |

| Offset: Differential           | Vos-DIFF         | Voltco ( $V_{CC} = 2.9V$ to 5.5V)                                           |                          |     | 1                        | mV/V  |

| Total Input Referenced Voltage | VOS-SE           | $V_{CC}$ = 2.9V, 1µs sample time, $V_{IN}$ = 6mV                            |                          | 3.4 | 8                        | mV    |

| Offset: Single-Ended           |                  | Voltco ( $V_{CC} = 2.9V$ to 5.5V)                                           |                          |     | 1                        | mV/V  |

#### AC ELECTRICAL CHARACTERISTICS

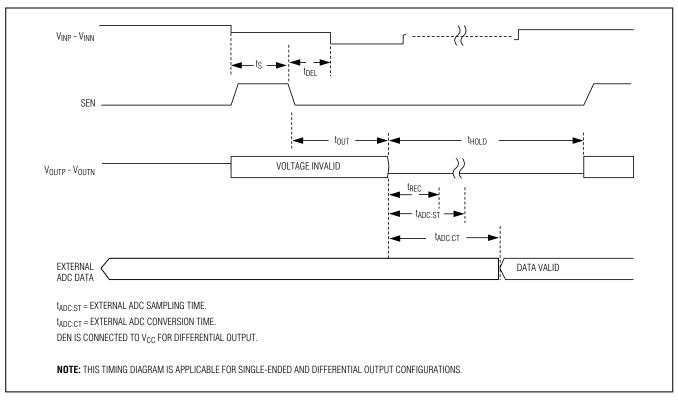

(V<sub>CC</sub> = +2.97V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (See the *Timing Diagram*.)

| PARAMETER                 | SYMBOL           | CONDITIONS                                                                           | MIN  | ТҮР | MAX | UNITS |

|---------------------------|------------------|--------------------------------------------------------------------------------------|------|-----|-----|-------|

| Sample Time Minimum       | ts               | V <sub>OUT</sub> is within 0.4dB (Note 3)                                            | 300  |     |     | ns    |

| Delay Time Minimum        | t <sub>DEL</sub> | (Note 4)                                                                             | 10   |     |     | ns    |

| Output Time               | tout             | Delay from SEN falling edge until valid<br>output at V <sub>OUT</sub> to 1% accuracy |      |     | 2   | μs    |

| Hold Time                 | thold            | (Note 5)                                                                             | tout |     | 100 | μs    |

| Output Step Recovery Time | toro             | 1V step, DEN = high                                                                  |      |     | 2   | 110   |

| (Note 6)                  | <sup>t</sup> REC | 3V step, DEN = high or low                                                           |      |     | 3.5 | μs    |

**Note 1:** All voltages are referenced to ground. Currents entering the IC are specified positive and currents exiting the IC are negative. **Note 2:** Guaranteed by design.

**Note 3:**  $V_{OUT}$  at the end of the 10µs hold time is within specified level of  $V_{IN}$  during the sample window; a 50 $\Omega$  resistor connected in series to both  $V_{INP}$  and  $V_{INN}$  ( $V_{INP} - V_{INN} = 1V$ ). External capacitance to ground for both  $V_{INP}$  and  $V_{INN}$  is approximately 10pF.

Note 4: The sampling capacitor must be removed from the input signal before the input signal changes. Therefore, the SEN pin must be low for a short period of time, t<sub>DEL</sub>, before the input changes.

Note 5:  $V_{OUT}$  at the end of the hold time is within 1% of  $V_{IN}$  during the sample window ( $V_{INP}$  -  $V_{INN}$  = 1V).

**Note 6:** Voltage step applied across V<sub>OUTP</sub> to V<sub>OUTN</sub> through a 5pF capacitor connected to each pin. This models the load presented by an ADC while it is sampling the DS1843's output. See the *Output Buffer* section. Settled within 1% of initial voltage.

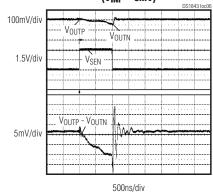

#### **Timing Diagram**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

**DS1843**

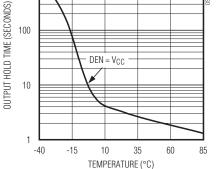

**Typical Operating Characteristics**

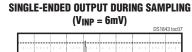

**DIFFERENTIAL OUTPUT DURING SAMPLING**  $(V_{INP} = 6mV)$

DEN = GND

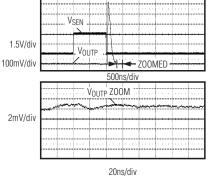

**SINGLE-ENDED OUTPUT, TRANSIENT** WITH 10% V<sub>CC</sub> STEP (V<sub>INP</sub> = 6mV)

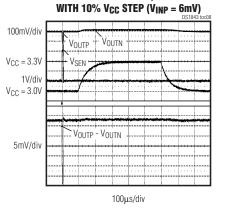

**OUTPUT HOLD TIME vs. TEMPERATURE**

10

1

-40

-15

10

TEMPERATURE (°C)

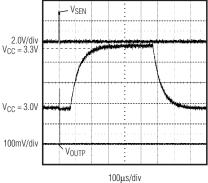

**DIFFERENTIAL OUTPUT, TRANSIENT**

35

60

85

V<sub>OUTN</sub> (200mV/div)

(200mV/div)

-----

---N-h-x-h-x-h-

50ns/div

# **Fast Sample-and-Hold Circuit**

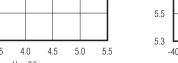

#### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

DS1843

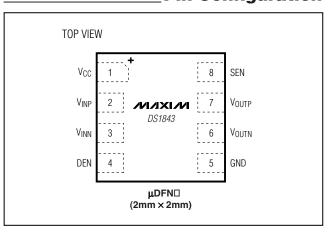

#### \_\_Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                 |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc   | Power-Supply Input                                                                                                                       |

| 2   | VINP  | Positive Voltage Input. Input to sample circuit.                                                                                         |

| 3   | VINN  | Negative Voltage Input. Input to sample circuit.                                                                                         |

| 4   | DEN   | Differential Output Enable. Connect to V <sub>CC</sub> for differential output or GND for single-ended output.                           |

| 5   | GND   | Ground Terminal                                                                                                                          |

| 6   | VOUTN | Sampled Voltage Negative Output. Buffered output of the hold capacitor. Keep unconnected or connect to GND for single-ended output mode. |

| 7   | Voutp | Sampled Voltage Positive Output and Single-Ended Output. Buffered output of the hold capacitor.                                          |

| 8   | SEN   | Sample Enable. Enables input sampling. This input is pulsed.                                                                             |

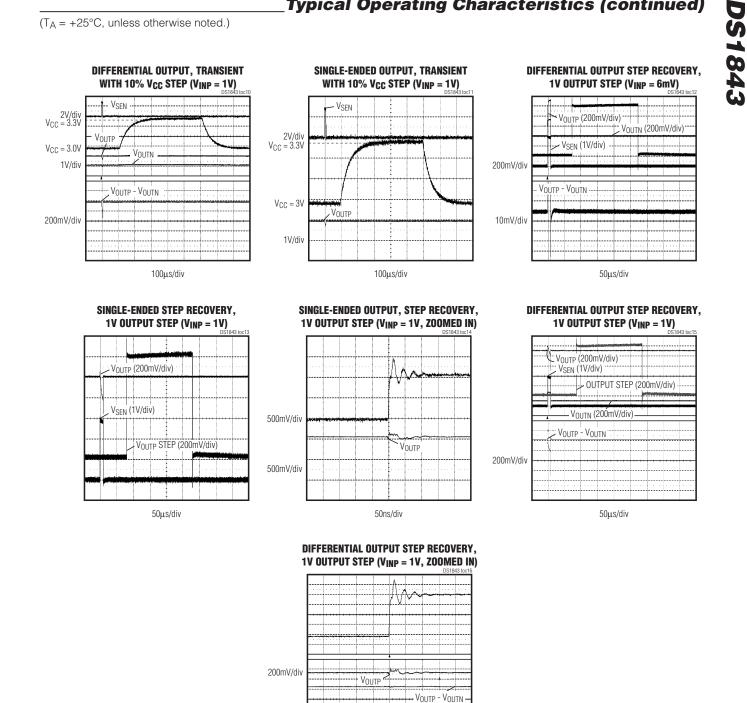

#### **Detailed Description**

The DS1843 consists of a fully differential sampling capacitor, switches, and a differential output buffer. It is designed to operate in fiber optic burst-mode systems; however, it can be used in other applications requiring a fast sample-and-hold circuit. The output can be configured for single-ended operations.

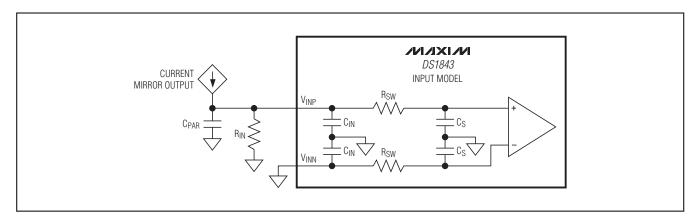

#### **Input Sampling Capacitor**

The input voltage is sampled using a 5pF capacitor on the positive input and another on the negative input. The capacitors are connected to the input when SEN is high. In addition to the sampling capacitors, the inputs also have parasitic capacitance (CIN). These capacitors must fully charge before SEN is switched to low in order to ensure accurate sampling. An RC time constant is created by the resistance of the voltage source connected to the DS1843's input and the capacitances on this node. See the *Applications Information* section for details.

#### **Output Buffer**

After sampling is complete, the sampling capacitor is switched to the output buffer. This buffer requires a small amount of time to settle, t<sub>OUT</sub>. When an ADC is used to measure the DS1843's output, a step occurs at the ADC's input caused by the ADC's internal sampling capacitor. The DS1843's recovery time, t<sub>REC</sub>, is dependent on the size of the ADC's sampling capacitor and the voltage applied across the ADC. To maximize accuracy, the ADC's sampling speed (ADC clock frequency) should be reduced until the ADC's conversion window (t<sub>ADC:ST</sub>, as shown in the *Timing Diagram*) is larger than the DS1843's recovery time. Refer to the ADC's documentation for t<sub>ADC:ST</sub>.

#### Sampling Time and Output Error

As the sampling time (ts) is decreased, the output error increases. The output error is largely dependent on the settling time of the sampling capacitor and, to a lesser degree, the output buffer's gain error and offset voltage. Settling time can be reduced by driving the DS1843 with a lower impedance. In a typical fiber optic application, a current is applied across a 5k $\Omega$  resistor. By using a stronger current source, the resistance and the settling time can be reduced (see the *Applications Information* section for details).

Figure 1. Input Impedances for Settling Time Calculations Diagram

#### **Applications Information**

#### **Power-Supply Decoupling**

To achieve the best results when using the DS1843, decouple the power-supply pin, VCC, with a  $0.01\mu$ F or  $0.1\mu$ F capacitor. Use a high-quality X7R or equivalent ceramic surface-mount capacitor.

#### **DS1843 Estimated Settling Time**

The settling time is dependent on the gain ratio of the current mirror used at the input of the DS1843. For example, the MAX4007 includes a 10:1 ratio current mirror. This requires a 5k $\Omega$  resistor to create a 1V full-scale output with 2mA current input to the MAX4007. This resistor can be decreased to 2.5k $\Omega$  by using the DS1842, which has a 5:1 ratio current mirror.

#### Variable Definitions:

RIN: Input resistor. The current mirror creates a voltage across this resistor.

$R_{SW}$ : Resistance of series switch that connects internal circuitry to input pins after  $t_{IST}$  time.

CIN: 7pF parasitic (ESD) capacitor.

CPAR: External parasitic capacitance. A current mirror's output and typical trace capacitance are less than 10pF.

Cs: 5pF sample capacitor.

t<sub>IST</sub>: Internal settling time based on ts from the AC electrical specification. The minimum ts includes one time constant. t<sub>IST</sub> removes this time constant.

tRC: RC settling time of the input.

Figure 1 shows the simplified diagram of input impedances for settling time calculations. Sample time is divided into two parts: DS1843

tIST: Internal settling time (max 250ns). During this time, voltage VIN (VINP - VINN) rises with a time constant of:

$$R_{IN} \times (C_{IN} + C_{PAR})$$

2) tRC: During this period two things happen:

a. Input  $V_{IN}$  keeps increasing from its value at  $t_{IST}$  to its final value with a new time constant of:

$$\sqrt{\left\{ \left( \mathsf{R}_{\mathsf{IN}} \times \left( \mathsf{C}_{\mathsf{IN}} + \mathsf{C}_{\mathsf{PAR}} \right) \right)^2 + \left( \mathsf{R}_{\mathsf{SW}} \times \mathsf{C}_{\mathsf{S}} \right)^2 \right\}}$$

b. R<sub>SW</sub> and C<sub>S</sub> track this  $V_{IN}$  (input) with a time constant of R<sub>SW</sub> x C<sub>S</sub>, which is 12.5ns (worst case).

#### Example:

Approximate accuracy calculations can be done for an input voltage based on the above impedance values. These calculations can be divided into three parts.

1) Accuracy of input at tIST (250ns):

Accuracy =

$$1 - e^{\frac{-t_1}{\left[R_{IN} \times \left(C_{IN} + C_{PAR}\right)\right]}}$$

where  $t_1 = t_{IST} = 250$ ns.

At tIST the internal circuit tags input impedance. This causes charge redistribution to occur, which causes a dip in the input voltage. The worst-case value of the input voltage at tIST is:

$$V_{IN@t_{IST}} = \left[1 - \frac{C_S}{\left(C_{IN} + C_{PAR} + C_S\right)}\right] \times \left[1 - e^{\left[\frac{-t_{IST}}{R_{IN} \times \left(C_{IN} + C_{PAR}\right)\right]}}\right] \times V_{IN}$$

7

2) Accuracy of internal circuitry between ts - tIST:

Accuracy =  $1 - e^{\frac{-t_2}{(R_{SW} \times C_S)}}$

where  $t_2 = (t_S - t_{IST})$  and  $(R_{SW} \times C_S) \sim = 12ns$ .

3) Total accuracy of input at sampling time, ts:

DS1843

$$\begin{aligned} \text{Accuracy} = & \left[ 1 - \left( 1 - V_{\text{IN} @ t_{\text{IST}}} \right) \times e^{\frac{-t_2}{\text{newRC}}} \right] \times \left[ 1 - e^{\frac{-t_2}{(R_{\text{SW}} \times C_{\text{S}})}} \right] \end{aligned}$$

$$\text{where newRC} = \sqrt{\left\{ \left( R_{\text{IN}} \times \left( C_{\text{IN}} + C_{\text{PAR}} \right) \right)^2 + \left( R_{\text{SW}} \times C_{\text{S}} \right)^2 \right\}}$$

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |  |

|--------------|--------------|----------------|---------------------|--|

| 8 µDFN       | L822+1       | <u>21-0164</u> | <u>90-0005</u>      |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

### Pin Configuration

8