ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

# **4096 × 18 DSP-SYNC™** 先进先出存储器

查询样品: SN74V245-EP

## 特性

- 4096 × 18 位组织阵列

- 7.5ns 读取和写入周期时间

- 3.3V VCC, 5V 输入耐受

- 首字或标准直通时序

- 单一或双寄存器缓冲的空和满标志

- 可轻松扩展深度和宽度

- 异步或同步读取和写入时钟 •

- 带有缺省设置的异步或同步可编程几乎空和近满标 • 志

- 半满标志功能 ٠

- 输出使能将输出数据总线置于高阻抗状态

- 高性能亚微米 CMOS 技术

- DSP 和微控制器接口控制逻辑 ٠

- 提供一个到德州仪器 (TI) TMS320<sup>™</sup> DSP 的 DSP 无粘结接口

- ,此 DSP 封装在 64 引脚薄型四方扁平封装

支持国防、航空航天、和医疗应用

- 受控基线

- 一个组装和测试场所 •

- 一个制造场所

- 支持军用(-55°C 至 125°C)温度范围 •

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

## 说明/订购信息

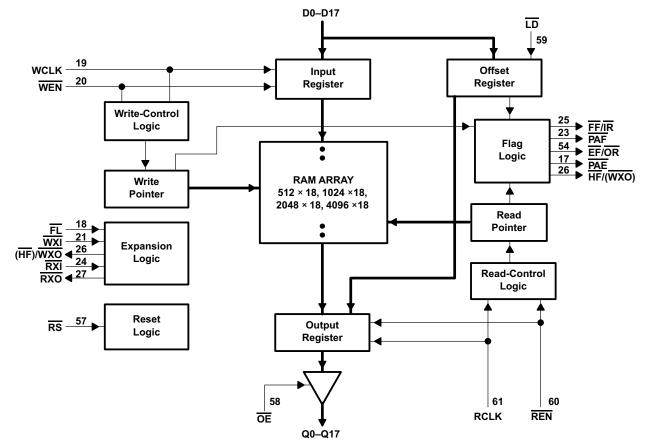

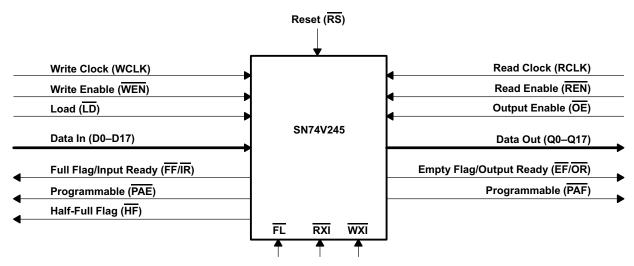

SN74V245 是一款超高速、低功耗 CMOS 计时先进先出 (FIFO) 存储器。 它支持高达 133MHz 的时钟频率并且具 有 5ns 的快速读取访问时间。 这个 DSP 同步 FIFO 存储器特有针对应用中使用的读取和访问控制,例如 DSP 到 处理器通信, DSP 到模拟前端 (AFE) 缓冲, 网络, 视频和数据通信。

SN74V245 是一款同步 FIFO,这表示每个端口采用一个同步接口。所有通过端口传输的数据被选通至由使能引脚 计时的连续(自由运行)端口的低到高转换。 针对每个端口的连续时钟相互独立并可异步或同步。 可对每个端口 的启用进行设置以在 DSP, 微控制器和/或由一个同步接口控制的总线之间提供一个简单接口。一个输出使能 (OE) 输入控制3态输出。

同步 FIFO 有两个固定标志、空标志/输出就绪 (EF/OR) 和满标志/输入就绪 (FF/IR), 和两个可编程标志, 几乎空 (PAE)和近满 (PAF)。 可编程标志的偏移负载由一个简单状态机控制并通过将负载引脚 (LD) 置为有效来启动。 当 FIFO 被用于单器件配置时,一个半满标志 (HF) 可用。

SN74V245 可使用两个时序运行模式: 首字直通 (FWFT) 模式和标准模式。

在 FWFT 模式中,被写入一个空 FIFO 的首字在 RCLK 信号的三次转换后被直接计时至数据输出线路。不必将一 个读取使能 (REN) 置为有效来访问首字。

在标准模式中,被写入到空 FIFO 的首字并不出现在输出输出线路上,除非执行了一个特定的读取操作。 一个包含 激活REN并启用一个上升 RCLK 边沿的读取操作将把字从内部存储器移动至数据输出线路。

通过使用菊花链技术或 FWFT 模式, SN74V245 的深度是可扩展的。 XI和XO引脚被用于扩展 FIFO。 在深度扩展 模式配置中,第一个器件上的首次载入 (FL) 被接地并且针对菊花链上的所有其它器件被设定为高电平。

SN74V245 额定工作温度 -55℃ 至 125℃。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DSP-SYNC. TMS320 are trademarks of Texas Instruments.

# SN74V245-EP

## ZHCSAL6A-DECEMBER 2012-REVISED JANUARY 2013

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **ORDERING INFORMATION**<sup>(1)</sup>

| Tj             | PACKAGE           | ORDERABLE PART NUMBER | TOP-SIDE MARKING | VID NUMBER     |

|----------------|-------------------|-----------------------|------------------|----------------|

| –55°C to 125°C | 64-pin TQFP (PAG) | SN74V245-15PAGEP      | V245-15EP        | V62/13606-01XE |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

# FUNCTIONAL BLOCK DIAGRAM

#### ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

#### PAG PACKAGE (TOP VIEW) D15 🗆 🗆 Q14 48 1 D14 🗆 2 🗆 Q13 47 D13 🗆 3 46 GND D12 🗆 4 45 Q12 5 D11 🗆 44 🗆 Q11 D10 🗆 6 □ V<sub>CC</sub> 43 D9 🗆 🗆 Q10 7 42 D8 🗆 🗆 Q9 8 41 D7 🗆 9 🗅 GND 40 D6 🗆 10 🗆 Q8 39 D5 🗆 11 🗅 Q7 38 D4 🗌 12 37 🗅 Q6 D3 🗆 13 🗅 Q5 36 D2 🗆 14 35 🛛 GND D1 🗌 15 34 🗆 Q4 33 🗆 V<sub>CC</sub> D0 🗆 16

**DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERMINAL |                               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.                           | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D0–D17   | 1-16, 63, 64                  | I   | Data inputs. Data inputs for an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EF/OR    | 54                            | 0   | $ \begin{array}{l} \mbox{Memory-empty/valid-data-available flag. In the standard mode, the \overline{\rm EF} function is selected.\overline{\rm EF} indicates whether the FIFO memory is empty. In FWFT mode, the \overline{\rm OR} function is selected.\overline{\rm OR} indicates whether there is valid data available at the outputs.  $                                                                                                                                                                              |

| FF/IR    | 25                            | ο   | Memory-full/space-available flag. In the standard mode, the $\overline{\text{FF}}$ function is selected. $\overline{\text{FF}}$ indicates whether the FIFO memory is full. In the FWFT mode, the IR function is selected. IR indicates whether there is space available for writing to the FIFO memory.                                                                                                                                                                                                                    |

| FL       | 18                            | I   | Mode selection. In the single-device or width-expansion configuration, $\overline{FL}$ , together with $\overline{WXI}$ and $\overline{RXI}$ , determines if the mode is standard mode or first-word fall-through (FWFT) mode, as well as whether the $\overline{PAE}/\overline{PAF}$ flags are synchronous or asynchronous (see Table 5). In the daisy-chain depth-expansion configuration, $\overline{FL}$ is grounded on the first device (first-load device) and set to high for all other devices in the daisy chain. |

| GND      | 30, 35, 40, 46, 51,<br>55, 62 |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LD       | 59                            | I   | Read/write control. When $\overline{\text{LD}}$ is low, data on the inputs D0–D11 is written to the offset and depth registers on the low-to-high transition of the WCLK, when $\overline{\text{WEN}}$ is low. When $\overline{\text{LD}}$ is low, data on the outputs Q0–Q11 is read from the offset and depth registers on the low-to-high transition of RCLK when $\overline{\text{REN}}$ is low.                                                                                                                       |

| OE       | 58                            | I   | Output enable. When $\overline{OE}$ is low, the data output bus is active. If $\overline{OE}$ is high, the output data bus is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                 |

| PAE      | 17                            | 0   | Programable almost-empty flag. When $\overline{PAE}$ is low, the FIFO is almost empty, based on the offset programmed into the FIFO. The default offset at reset is 127 from empty.                                                                                                                                                                                                                                                                                                                                        |

| PAF      | 23                            | 0   | Programable almost-full flag. When $\overline{PAF}$ is low, the FIFO is almost full, based on the offset programmed into the FIFO. The default offset at reset is 127 from full.                                                                                                                                                                                                                                                                                                                                           |

| TERMINAL FUNCTIONS (continued) |

|--------------------------------|

|--------------------------------|

| TERMINAL        |                                                                        |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------|------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | ME NO. I/O DESCRIPTION                                                 |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Q0–Q17          | 28, 29, 31, 32, 34,<br>36–39, 41, 42, 44,<br>45, 47, 48, 50, 52,<br>53 | ο | Data outputs. Data outputs for an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RCLK            | 61                                                                     | I | Read clock. When $\overline{\text{REN}}$ is low, data is read from the FIFO on a low-to-high transition of RCLK, if the FIFO is not empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| REN             | 60                                                                     | I | Read enable. When REN is low, data is read from the FIFO on every low-to-high transition of RCLK. When REN is high, the output register holds the previous data. Data is not read from the FIFO if EF is low.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RS              | 57                                                                     | I | Reset. When $\overline{\text{RS}}$ is set low, internal read and write pointers are set to the first location of the RAM array, $\overline{\text{FF}}$ and $\overline{\text{PAF}}$ go high, and $\overline{\text{PAE}}$ and $\overline{\text{EF}}$ go low. A reset is required before an initial write after power up.                                                                                                                                                                                                                                                                          |  |

| RXI             | 24                                                                     | I | Read expansion. In the single-device or width-expansion configuration, $\overline{\text{RXI}}$ , together with $\overline{\text{FL}}$ and $\overline{\text{WXI}}$ , determines if the mode is standard mode or FWFT mode, as well as whether the PAE/PAF flags are synchronous or asynchronous (see Table 5). In the daisy-chain depth-expansion configuration, $\overline{\text{RXI}}$ is connected to $\overline{\text{RXO}}$ (read expansion out) of the previous device.                                                                                                                    |  |

| RXO             | 27                                                                     | 0 | Last-location-read flag. In the depth-expansion configuration, a pulse is sent from $\overline{\text{RXO}}$ to $\overline{\text{RXI}}$ of the next device when the last location in the FIFO is read.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>CC</sub> | 22, 33, 43, 49, 56                                                     |   | Supply voltage. +3.3-V power-supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| WCLK            | 19                                                                     | I | Write clock. When $\overline{\text{WEN}}$ is low, data is written into the FIFO on a low-to-high transition of WCLK if the FIFO is not full.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| WEN             | 20                                                                     | I | Write enable. When $\overline{\text{WEN}}$ is low, data is written into the FIFO on every low-to-high transition of WCLK. When $\overline{\text{WEN}}$ is high, the FIFO holds the previous data. Data is not written into the FIFO if $\overline{\text{FF}}$ is low.                                                                                                                                                                                                                                                                                                                           |  |

| WXI             | 21                                                                     | I | $ \begin{array}{l} \hline Width \ expansion. \ In the single-device or width-expansion \ configuration, \ \overline{WXI}, \ together \ with \ \overline{FL} \ and \ \overline{RXI}, \ determines \ if \ the \ mode \ is \ standard \ mode \ or \ FWFT \ mode, \ as \ well \ as \ whether \ the \ \overline{PAE}/\overline{PAF} \ flags \ are \ synchronous \ or \ asynchronous \ (see \ Table 5). \ In \ the \ daisy-chain \ depth-expansion \ configuration, \ \overline{WXI} \ is \ connected \ to \ \overline{WXO} \ (write \ expansion \ out) \ of \ the \ previous \ device. \end{array} $ |  |

| WXO/HF          | 26                                                                     | ο | Half-full flag. In the single-device or width-expansion configuration, the device is more than half full when $\overline{\text{HF}}$ is low. In the depth-expansion configuration, a pulse is sent from $\overline{\text{WXO}}$ to $\overline{\text{WXI}}$ of the next device when the last location in the FIFO is written.                                                                                                                                                                                                                                                                    |  |

www.ti.com.cn

www.ti.com.cn

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                               | VALUE          |

|---------------------------------------------------------------|----------------|

| Supply voltage range, $V_{CC}$                                | –0.5 V to 5 V  |

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$ | ±50 mA         |

| Maximum junction temperature, Tj                              | 150°C          |

| Storage temperature range, T <sub>stg</sub>                   | –65°C to 150°C |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>**

|                 |                                | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Supply voltage                 | 3   | 3.3 | 3.6 | V    |

| V <sub>IH</sub> | High-level input voltage       | 2   |     | 5   | V    |

| V <sub>IL</sub> | Low-level input voltage        |     |     | 0.8 | V    |

| TJ              | Operating junction temperature | -55 |     | 125 | °C   |

All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

## THERMAL INFORMATION

|                         |                                                             | SN74V245 |       |  |

|-------------------------|-------------------------------------------------------------|----------|-------|--|

|                         | THERMAL METRIC <sup>(1)</sup>                               | PAG      | UNITS |  |

|                         |                                                             | 64 PINS  |       |  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 46.1     |       |  |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 5.8      |       |  |

| θ <sub>JB</sub>         | Junction-to-board thermal resistance <sup>(4)</sup>         | 19.7     | °C/M  |  |

| ΨJT                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.2      | °C/W  |  |

| Ψјв                     | Junction-to-board characterization parameter <sup>(6)</sup> | 19.4     |       |  |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | N/A      |       |  |

(1) 有关传统和新的热度量的更多信息,请参阅*IC 封装热度量*应用报告, SPRA953。

- (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环 境热阻。

- (3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

- (5) 结至顶部特征参数,Ψ<sub>JT</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参数以便获得 θ<sub>JA</sub>。

- (6) 结至电路板特征参数, ψ<sub>JB</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第6章和第7章)中 描述的程序从仿真数据中 提取出该参数以便获得 θ<sub>JA</sub>。

(7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得 结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准 测试,但可在 ANSI SEMI

- (7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。不存在特定的 JEDEC 标准 测试,但可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

# RUMENTS

www.ti.com.cn

## ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                     | TEST CONDITIONS                                                                                   | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OH</sub>  | High-level output voltage     | V <sub>CC</sub> = 3 V, I <sub>OH</sub> = -2 mA                                                    | 2.4 |     |     | V    |

| V <sub>OL</sub>  | Low-level output voltage      | V <sub>CC</sub> = 3 V, I <sub>OL</sub> = 8 mA                                                     |     |     | 0.4 | V    |

| I <sub>I</sub>   | Input current                 | $V_{CC} = 3.6 \text{ V}, \text{ V}_{I} = V_{CC} \text{ to } 0.4 \text{ V}$                        |     |     | ±1  | μA   |

| I <sub>oz</sub>  | High-impedance output current | $V_{CC} = 3.6 \text{ V}, \overline{\text{OE}} \ge V_{IH}, V_O = V_{CC} \text{ to } 0.4 \text{ V}$ |     |     | ±10 | μA   |

| I <sub>CC1</sub> | Supply current                | $V_{CC}$ = 3.3 V, See $^{(1)},\ ^{(2)}$ and $^{(3)}$                                              |     |     | 35  | mA   |

| I <sub>CC2</sub> |                               | $V_{CC}$ = 3.6 V, See $^{(1)}$ and $^{(4)}$                                                       |     |     | 5   | mA   |

| C <sub>IN</sub>  | Input capacitance             | V <sub>I</sub> = 0, T <sub>A</sub> = 25°C, f = 1 MHz                                              |     | 10  |     | pF   |

| C <sub>OUT</sub> |                               | $V_{O} = 0$ , $T_{A} = 25^{\circ}C$ , f = 1 MHz, Output deslected, ( $\overline{OE} \ge V_{IH}$ ) |     | 10  |     | pF   |

Tested with outputs disabled  $(I_{OUT} = 0)$ . (1)

RCLK and WCLK switch at 20 MHz and data inputs switch at 10 MHz. (2)

- (3)

- Typical  $I_{CC1} = 2.04 + 0.88 \times f_{SW} + 0.02 \times CL \times f_{SW}$  (in mA). These equations are valid under the following conditions:  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $f_{SW} = \text{WCLK}$  frequency = RCLK frequency (in MHz, using TTL levels), data switching at  $f_{SW}/2$ ,  $C_L$  = capacitive load (in pF).

- All inputs = (V<sub>CC</sub> 0.2 V) or (GND + 0.2 V), except RCLK and WCLK, which switch at 20 MHz. (4)

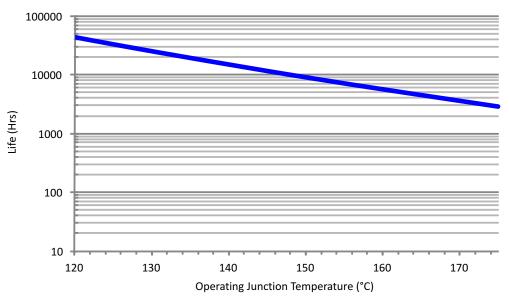

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

- Silicon operating life design goal is 100,000 hrs at 106°C junction temperature (does not include package interconnect (2) life).

- The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the (3) dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

#### Figure 1. Electromigration Fail Mode Derating Chart

ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

# TIMING REQUIREMENTS

|                    |                                                                                 | MIN  | MAX  | UNIT |

|--------------------|---------------------------------------------------------------------------------|------|------|------|

| f <sub>clock</sub> | Clock cycle frequency                                                           |      | 66.7 | MHz  |

| t <sub>A</sub>     | Data access time                                                                | 1    | 11   | ns   |

| t <sub>CLK</sub>   | Clock cycle time                                                                | 16   |      | ns   |

| t <sub>CLKH</sub>  | Clock high time                                                                 | 7    |      | ns   |

| t <sub>CLKL</sub>  | Clock low time                                                                  | 7    |      | ns   |

| t <sub>DS</sub>    | Data setup time                                                                 | 5    |      | ns   |

| t <sub>DH</sub>    | Data hold time                                                                  | 2    |      | ns   |

| t <sub>ENS</sub>   | Enable setup time                                                               | 5    |      | ns   |

| t <sub>ENH</sub>   | Enable hold time                                                                | 2    |      | ns   |

| t <sub>LDS</sub>   | Load setup time                                                                 | 5    |      | ns   |

| t <sub>LDH</sub>   | Load hold time                                                                  | 2    |      | ns   |

| t <sub>RS</sub>    | Reset pulse width <sup>(1)</sup>                                                | 16   |      | ns   |

| t <sub>RSS</sub>   | Reset setup time                                                                | 10.5 |      | ns   |

| t <sub>RSR</sub>   | Reset recovery time                                                             | 10.5 |      | ns   |

| t <sub>RSF</sub>   | Reset to flag and output time                                                   |      | 16   | ns   |

| t <sub>OLZ</sub>   | Output enable to output in low Z                                                | 0    |      | ns   |

| t <sub>OE</sub>    | Output enable to output valid                                                   | 1.5  | 9    | ns   |

| t <sub>OHZ</sub>   | Output enable to output in high Z                                               | 1.5  | 9    | ns   |

| t <sub>WFF</sub>   | Write clock to Full flag                                                        |      | 11   | ns   |

| t <sub>REF</sub>   | Read clock to Empty flag                                                        |      | 11   | ns   |

| t <sub>PAFA</sub>  | Clock to asynchronous programmable Almost-Full flag                             |      | 21   | ns   |

| t <sub>PAFS</sub>  | Write clock to synchronous programmable Almost-Full flag                        |      | 11   | ns   |

| t <sub>PAEA</sub>  | Clock to asynchronous programmable Almost-Empty flag                            |      | 21   | ns   |

| t <sub>PAES</sub>  | Read clock to synchronous programmable Almost-Empty flag                        |      | 11   | ns   |

| t <sub>HF</sub>    | Clock to Half-Full flag                                                         |      | 21   | ns   |

| t <sub>XO</sub>    | Clock to expansion out                                                          |      | 11   | ns   |

| t <sub>XI</sub>    | Expansion in pulse duration                                                     | 7    |      | ns   |

| t <sub>XIS</sub>   | Expansion in setup time                                                         | 6    |      | ns   |

| t <sub>SKEW1</sub> | Skew time between read clock and write clock for FF/IR and EF/OR                | 6.5  |      | ns   |

| t <sub>SKEW2</sub> | Skew time between read clock and write clock for PAE and PAF (synchronous only) | 18.5 |      | ns   |

(1) Pulse durations less than minimum values are not allowed.

# AC TEST CONDITIONS

| At left constitions                             |              |  |  |  |

|-------------------------------------------------|--------------|--|--|--|

| Input Pulse Levels                              | GND to 3.0 V |  |  |  |

| Input Rise/Fall Times                           | 3 ns         |  |  |  |

| Input Timing Reference Levels                   | 1.5 V        |  |  |  |

| Output Reference Levels                         | 1.5 V        |  |  |  |

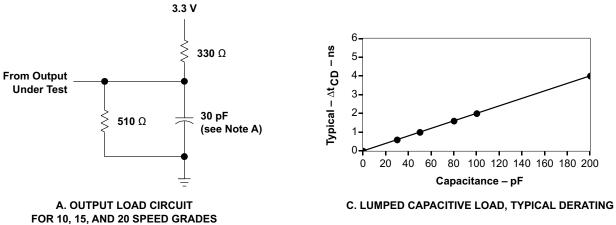

| Output Load for t <sub>CLK</sub> = 10 ns, 15 ns | See A        |  |  |  |

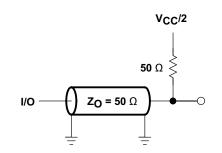

| Output Load for t <sub>CLK</sub> = 7.5 ns       | See B and C  |  |  |  |

#### B. AC TEST LOAD FOR 7.5 SPEED GRADE

PARAMETER MEASUREMENT INFORMATION

FOR 10, 15, AND 20 SPEED GRADA. Includes probe and jig capacitance

Includes probe and jig capacitance

## Figure 2. Load Circuits

www.ti.com.cn

ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

## DETAILED DESCRIPTION

## **INPUTS:**

## DATA IN (D0-D17)

Data inputs for 18-bit-wide data.

## CONTROLS:

## RESET (RS)

Reset is accomplished when  $\overline{\text{RS}}$  is taken low. During reset, both internal read and write pointers are set to the first location. A reset is required after power up before a write operation can take place. The half-full flag ( $\overline{\text{HF}}$ ) and programmable almost-full flag ( $\overline{\text{PAF}}$ ) is reset to high after  $t_{\text{RSF}}$ . The programmable almost-empty flag ( $\overline{\text{PAE}}$ ) is reset to high. The empty flag ( $\overline{\text{EF}}$ ) resets to low in standard mode, but resets to high in FWFT mode. During reset, the output register is initialized to all zeros, and the offset registers are initialized to their default values.

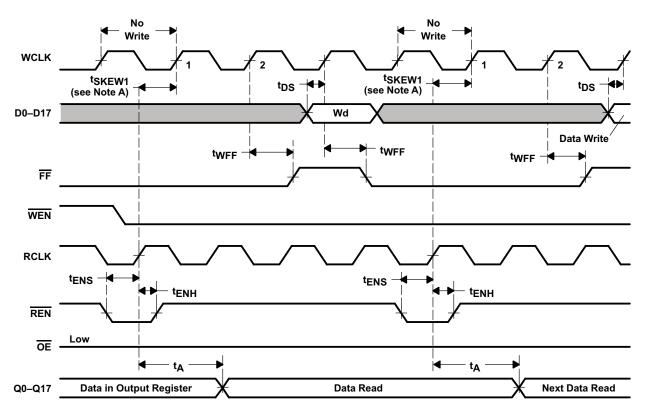

## WRITE CLOCK (WCLK)

A write cycle is initiated on the low-to-high transition of WCLK. Data setup and hold times must be met with respect to the low-to-high transition of WCLK.

The write and read clocks can be asynchronous or coincident.

## WRITE ENABLE (WEN)

When  $\overline{\text{WEN}}$  is low, data can be loaded into the FIFO RAM array on the rising edge of every WCLK cycle if the device is not full. Data is stored in the RAM array sequentially and independently of any ongoing read operation.

When  $\overline{\text{WEN}}$  is high, no new data is written in the RAM array on each WCLK cycle.

To prevent data overflow in the standard mode, FF goes low, inhibiting further write operations. Upon completion of a valid read cycle, FF goes high, allowing a write to occur. The FF flag is updated on the rising edge of WCLK.

To prevent data overflow in the FWFT mode,  $\overline{IR}$  goes high, inhibiting further write operations. Upon completion of a valid read cycle,  $\overline{IR}$  goes low, allowing a write to occur. The  $\overline{IR}$  flag is updated on the rising edge of WCLK.

WEN is ignored when the FIFO is full in either FWFT or standard mode.

#### READ CLOCK (RCLK)

Data can be read on the outputs on the low-to-high transition of RCLK when  $\overline{OE}$  is low.

The write and read clocks can be asynchronous or coincident.

## READ ENABLE (REN)

When REN is low, data is loaded from the RAM array into the output register on the rising edge of every RCLK cycle if the device is not empty.

When  $\overline{\text{REN}}$  is high, the output register holds the previous data and no new data is loaded into the output register. Data outputs Q0–Qn maintain the previous data value.

In the standard <u>mode</u>, every word accessed at Qn, including the first word written to an empty FIFO, must be requested using REN. When the last word has been read from the FIFO, the empty flag (EF) goes low, inhibiting further read operations. REN is ignored when the FIFO is empty. After a write is performed, EF goes high, allowing a read to occur. The EF flag is updated on the rising edge of RCLK.

In the FWFT mode, the first word written to an empty FIFO automatically goes to the outputs Qn, on the third valid low-to-high transition of RCLK +  $t_{SKEW}$  after the first write. REN need not be asserted low. To access all other words, a read must be executed using REN. The RCLK low-to-high transition after the last word has been read from the FIFO, output ready (OR) goes high with a true read (RCLK with REN low), inhibiting further read operations. REN is ignored when the FIFO is empty.

## OUTPUT ENABLE (OE)

When  $\overline{OE}$  is low, the parallel output buffers transmit data from the output register. When  $\overline{OE}$  is high, the Q-output data bus is in the high-impedance state.

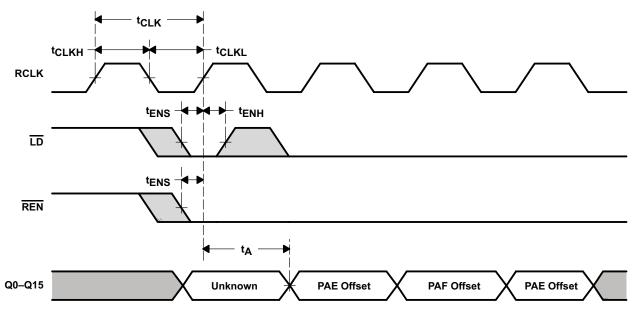

## LOAD (LD)

The SN74V245 contains two 12-bit offset registers with data on the inputs, or read on the outputs. When  $\overline{\text{LD}}$  is low and WEN is low, data on the inputs D0–D11 is written into the empty offset register on the first low-to-high transition of the write clock (WCLK). When LD and WEN are held low, data is written into the full offset register on the second low-to-high transition of WCLK (see Table 1, Table 2 and Table 3). The third transition of WCLK again writes to the empty-offset register.

However, writing to all offset registers need not occur at one time. One or two offset registers can be written and then, by bringing LD high, the FIFO is returned to normal read/write operation. When LD is low, and WEN is low, the next offset register in sequence is written.

| LD | WEN | WCLK | SELECTION <sup>(1)</sup>                                    |

|----|-----|------|-------------------------------------------------------------|

| L  | L   | Ť    | Writing to offset registers:<br>Empty offset<br>Full offset |

| L  | Н   | ↑    | No operation                                                |

| Н  | L   | ↑    | Write into FIFO                                             |

| Н  | Н   | ↑    | No operation                                                |

Table 1. Writing to Offset Registers

The same selection sequence applies to reading from the registers. REN is enabled and read is performed on the low-to-high transition of RCLK.

| Table 2. Empty Offset Register Location and Default Values <sup>(1)</sup> | I) |

|---------------------------------------------------------------------------|----|

|---------------------------------------------------------------------------|----|

| 17       | 12 11            | 0     |

|----------|------------------|-------|

|          | Empty Offset Reg | ister |

| Not used | Default value    |       |

|          | 007FH            |       |

(1) Any bits of the offset register not being programmed should be set to zero.

| Table 3. Full Offset Registe | r Location and | Default Values <sup>(1)</sup> |

|------------------------------|----------------|-------------------------------|

|------------------------------|----------------|-------------------------------|

| 17 12    | 11 0                 |

|----------|----------------------|

|          | Full Offset Register |

| Not used | Default value        |

|          | 007FH                |

(1) Any bits of the offset register not being programmed should be set to zero.

When LD is low and WEN is high, the WCLK input is disabled; then, a signal at this input can neither increment the write-offset-register pointer, nor execute a write.

The contents of the offset registers can be read on the output lines when  $\overline{\text{LD}}$  is low and  $\overline{\text{REN}}$  is low; then, data can be read on the low-to-high transition of RCLK. Reading the control registers employs a dedicated read-offset-register pointer (the read and write pointers operate independently). Offset register content can be read out in the standard mode only. It is inhibited in the FWFT mode.

A read from and a write to the offset registers should not be performed simultaneously.

## FIRST LOAD (FL)

For the singl<u>e-d</u>evice mode, see Table 6 for additional information. In the daisy-chain depth-expansion configuration, FL is grounded to indicate it is the first device loaded and is set high for all other devices in the daisy chain (see Operating Configurations for further details).

#### www.ti.com.cn

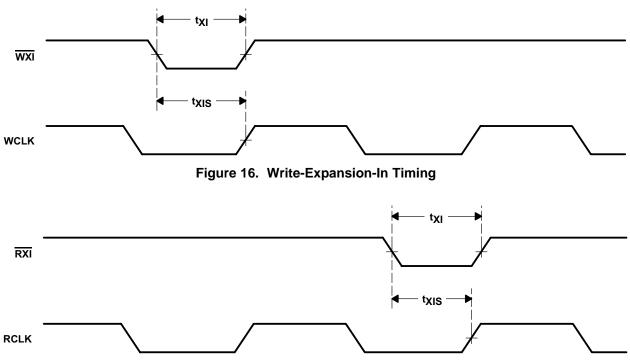

#### WRITE EXPANSION INPUT (WXI)

This is a dual-purpose pin. For single-device mode, see Table 6 for additional information.  $\overline{WXI}$  is connected to write expansion out ( $\overline{WXO}$ ) of the previous device in the daisy-chain depth-expansion mode.

## READ EXPANSION INPUT (RXI)

This is a dual-purpose pin. For single-device mode, see Table 6 for additional information.  $\overline{RXI}$  is connected to read expansion out ( $\overline{RXO}$ ) of the previous device in the daisy-chain depth-expansion mode.

#### OUTPUTS:

## FULL FLAG/INPUT READY (FF/IR)

This is a dual-purpose pin. In FWFT mode, the input ready (IR) function is selected. IR goes low when memory space is available for writing data. When there is no free space left, IR goes high, inhibiting further write operations.

In standard mode, the  $\overline{FF}$  function is selected. When the FIFO is full,  $\overline{FF}$  goes low, inhibiting further write operations. When  $\overline{FF}$  is high, the FIFO is not full. If no reads are performed after a reset,  $\overline{FF}$  goes low after D writes to the FIFO. D = 4096.

$\overline{IR}$  goes high after D writes to the FIFO. D = 4097. The additional word in FWFT mode is due to the capacity of the memory plus output register.

FF/IR is synchronous and updated on the rising edge of WCLK.

## EMPTY FLAG/OUTPUT READY (EF/OR)

This is a dual-purpose pin. In FWFT mode, the OR function is selected. OR goes low at the same time the first word written to an empty FIFO appears valid on the outputs. OR stays low after the RCLK low-to-high transition that shifts the last word from the FIFO memory to the outputs. OR goes high only with a true read (RCLK with REN low). The previous data stays at the outputs, indicating that the last word was read. Further data reads are inhibited until OR goes low again.

In the standard mode, the  $\overline{EF}$  function is selected. When the FIFO is empty,  $\overline{EF}$  goes low, inhibiting further read operations. When  $\overline{EF}$  is high, the FIFO is not empty.

EF/OR is synchronous and updated on the rising edge of RCLK.

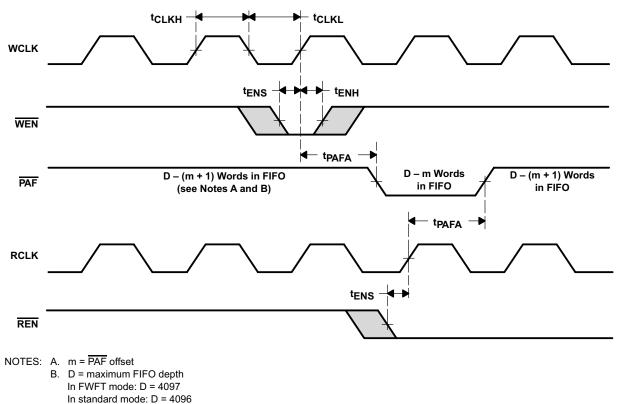

## PROGRAMMABLE ALMOST-FULL FLAG (PAF)

PAF goes low when the FIFO reaches the almost-full condition. In FWFT mode, if no reads are performed, PAF goes low after 4097 - m. Default values for m are in Table 4 and Table 5.

In standard mode, if no reads are performed after reset ( $\overline{RS}$ ),  $\overline{PAF}$  goes low after 4096 – m writes. The offset m is defined in Table 3.

If asynchronous PAF configuration is selected, PAF is asserted low on the low-to-high transition of WCLK. PAF is reset to high on the low-to-high transition of RCLK. If synchronous PAF configuration is selected (see Table 6), PAF is updated on the rising edge of WCLK.

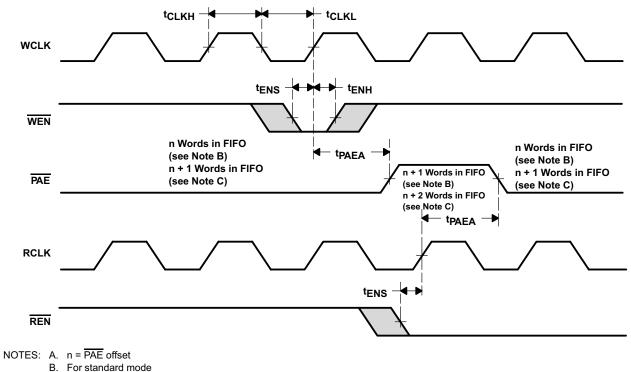

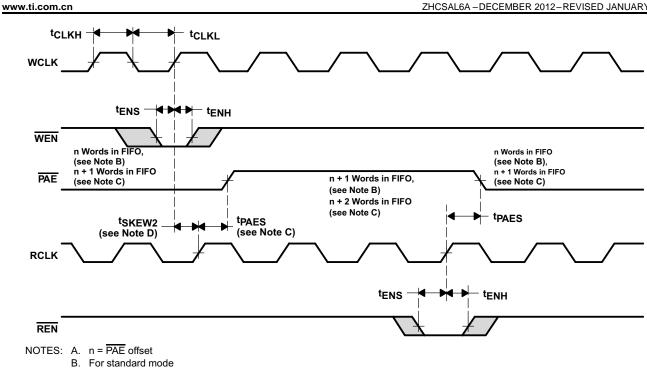

### PROGRAMMABLE ALMOST-EMPTY FLAG (PAE)

PAE goes low when the FIFO reaches the almost-empty condition. In FWFT mode, PAE goes low when there are n + 1 words, or fewer, in the FIFO. In standard mode, PAE goes low when there are n words or fewer in the FIFO. The offset n is defined as the empty offset. The default values for n are noted in Table 4 and Table 5.

If there is no empty offset specified, PAE is low when the device is 127 away from completely empty.

If asynchronous PAE configuration is selected, PAE is asserted low on the low-to-high transition of the read clock (RCLK). PAE is reset to high on the low-to-high transition of the write clock (WCLK). If synchronous PAE configuration is selected (see Table 6), PAE is updated on the rising edge of RCLK.

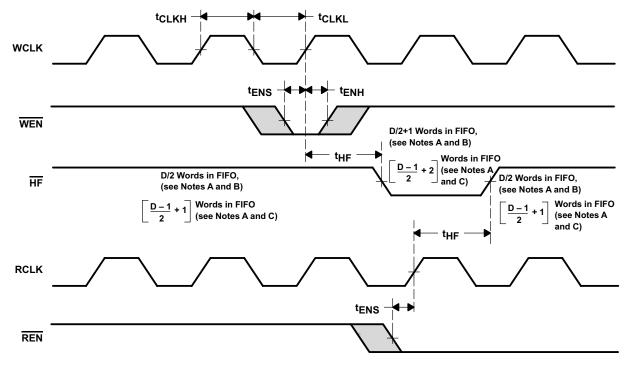

## WRITE EXPANSION OUT/HALF-FULL FLAG (WXO/HF)

This is a dual-purpose output. In the single-device and width-expansion mode, when write expansion in  $(\overline{WXI})$  and/or read expansion in  $(\overline{RXI})$  are grounded, this output acts as an indication of a half-full memory.

After one-half of the memory is filled, and at the low-to-high transition of the next write cycle, the half-full flag (HF) goes low and remains set until the difference between the write pointer and read pointer is less than or equal to one-half of the total memory of the device. HF is then reset to high by the low-to-high transition of the read clock (RCLK). HF is asynchronous.

In the daisy-chain depth-expansion mode,  $\overline{WXI}$  is connected to  $\overline{WXO}$  of the previous device. This output acts as a signal to the next device in the daisy chain by providing a pulse when the previous device writes to the last location of memory.

## READ EXPANSION OUT (RXO)

In the daisy-chain depth-expansion configuration, read expansion in  $(\overline{RXI})$  is connected to read expansion out  $(\overline{RXO})$  of the previous device. This output acts as a signal to the next device in the daisy chain by providing a pulse when the previous device reads from the last location of memory.

## DATA OUTPUTS (Q0–Q17)

Q0–Q17 are data outputs for 18-bit-wide data.

## FUNCTIONAL DESCRIPTION

## TIMING MODES:

## STANDARD vs FIRST-WORD FALL-THROUGH (FWFT) MODE

The SN74V245 supports two different timing modes. The selection of the mode of operation is determined during configuration at reset (RS). During an RS operation, the first load (FL), read expansion input (RXI), and write-expansion input (WXI) pins are used to select the timing mode as shown in Table 6. In standard mode, the first word written to an empty FIFO does not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating read enable (REN) and enabling a rising read clock (RCLK) edge, shifts the word from internal memory to the data output lines. In FWFT mode, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A REN does not have to be asserted to access the first word.

Various signals, both input and output signals, operate differently, depending on which timing mode is in effect.

## FIRST-WORD FALL-THROUGH MODE (FWFT)

In this mode, status flags IR, PAF, HF, PAE, and OR operate in the manner outlined in Table 4. To write data into the FIFO, WEN must be low. Data presented to the data-in lines is clocked into the FIFO on subsequent transitions of WCLK. After the first write is performed, the output ready (OR) flag goes low. Subsequent writes continue to fill the FIFO. PAE goes high after n + 2 words have been loaded into the FIFO, where n is the empty offset value. The default setting for this value is stated in the footnote of Table 4. This parameter also is user programmable. See the Programmable Flag Offset Loading section.

If data continues to be written into the FIFO, and no read operations are taking place,  $\overline{HF}$  switches to low when the 2050th word is written into the FIFO. Continuing to write data into the FIFO causes PAF to go low. Again, if no reads are performed,  $\overline{PAF}$  goes low after 4097 – m writes, where m is the full offset value. The default setting for this value is stated in the footnote of Table 4.

When the FIFO is full, the input ready ( $\overline{IR}$ ) flag goes high, inhibiting further write operations. If no reads are performed after a reset,  $\overline{IR}$  goes high after D writes to the FIFO. D = 4097. The additional word in FWFT mode is due to the capacity of the memory plus output register.

ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

If the <u>FIFO</u> is full, the first read operation causes the  $\overline{IR}$  flag to go low. Subsequent read operations cause  $\overline{PAF}$  and  $\overline{HF}$  to <u>go</u> high at the conditions described in <u>Table 4</u>. If further read operations occur without write operations, PAE goes low when there are n + 1 words in the FIFO, where n is the empty offset value. If there is no empty offset specified,  $\overline{PAE}$  is low when the device is 128 away from empty. Continuing read operations cause the FIFO to be empty. When the last word has been read from the FIFO, OR goes high, inhibiting further read operations. REN is ignored when the FIFO is empty.

| NUMBER OF WORDS IN FIFO             | ĪR | PAF | HF | PAE | OR |

|-------------------------------------|----|-----|----|-----|----|

| 0                                   | L  | Н   | Н  | L   | Н  |

| 1 to (n+1) <sup>(1)</sup>           | L  | Н   | Н  | L   | L  |

| (n+2) to 2049                       | L  | Н   | Н  | Н   | L  |

| 2050 to [4097–(m+1)] <sup>(2)</sup> | L  | Н   | L  | Н   | L  |

| (4097–m) to 4096                    | L  | L   | L  | Н   | L  |

| 4097                                | Н  | L   | L  | Н   | L  |

#### Table 4. Status Flags for FWFT Mode

(1) n = Empty offset = 127

(2) m = Full offset = 127

#### STANDARD MODE

In this mode, status flags  $\overline{FF}$ ,  $\overline{PAF}$ ,  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{EF}$  operate in the manner outlined in Table 5. To write data into the FIFO, write enable (WEN) must be low. Data presented to the data-in lines is clocked into the FIFO on subsequent transitions of the write clock (WCLK). After the first write is performed, the empty flag ( $\overline{EF}$ ) goes high. Subsequent writes continue to fill the FIFO. The programmable almost-empty flag ( $\overline{PAE}$ ) goes high after n + 1 words have been loaded into the FIFO, where n is the empty offset value. The default setting for this value is stated in the footnote of Table 5. This parameter also is user programmable. See the Programmable Flag Offset Loading section.

If data continues to be written into the FIFO, and no read operations are taking place, the half-full flag (HF) switches to low when the 2049th word is written into the FIFO. Continuing to write data into the FIFO causes the programmable almost-full flag (PAF) to go low. Again, if no reads are performed, PAF goes low after 4096 – m writes. Offset m is the full offset value. This parameter also is user programmable. See the Programmable Flag Offset Loading section. If there is no full offset specified, PAF is low when the device is 127 away from full.

When the FIFO is full, the full flag ( $\overline{FF}$ ) goes low, inhibiting further write operations. If no reads are performed after a reset,  $\overline{FF}$  goes low after D writes to the FIFO. D = 4096.

If the FIFO is <u>full</u>, the first read operation causes FF to go high. Subsequent read operations cause PAF and the half-full flag (HF) to go high under the conditions described in Table 5. If further read operations occur, without write operations, the programmable almost-empty flag (PAE) goes low when there are n words in the FIFO, where n is the empty offset value. If there is no empty offset specified, PAE is low when the device is 127 away from completely empty. Continuing read operations cause the FIFO to be empty. When the last word has been read from the FIFO, EF goes low, inhibiting further read operations. REN is ignored when the FIFO is empty.

| NUMBER OF WORDS IN FIFO             | FF | PAF | HF | PAE | EF |  |  |  |  |  |

|-------------------------------------|----|-----|----|-----|----|--|--|--|--|--|

| 0                                   | Н  | Н   | Н  | L   | L  |  |  |  |  |  |

| 1 to n <sup>(1)</sup>               | Н  | Н   | Н  | L   | Н  |  |  |  |  |  |

| (n+1) to 2048                       | Н  | Н   | Н  | Н   | Н  |  |  |  |  |  |

| 2049 to [4096–(m+1)] <sup>(2)</sup> | Н  | Н   | L  | Н   | Н  |  |  |  |  |  |

| (4096–m) to 4095                    | Н  | L   | L  | Н   | Н  |  |  |  |  |  |

| 4096                                | L  | L   | L  | Н   | Н  |  |  |  |  |  |

| Table 5. Status | Flags for | Standard Mode |

|-----------------|-----------|---------------|

|-----------------|-----------|---------------|

(1) n = Empty offset = 127

(2) m = Full offset = 127

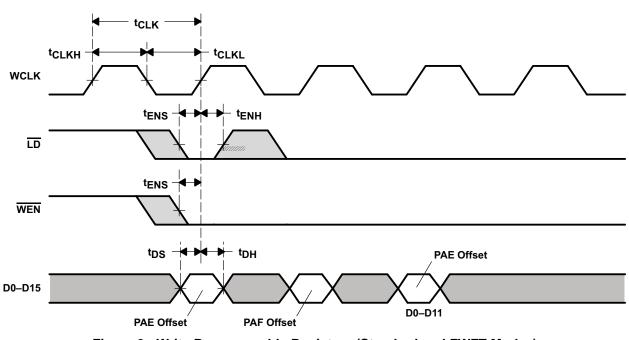

## PROGRAMMABLE FLAG LOADING

Full- and empty-flag offset values can be user programmable. The SN74V245 has internal registers for these offsets. Default settings are stated in the footnotes of Table 4 and Table 5. Offset values are loaded into the FIFO using the data input lines D0–D11. To load the offset registers, the load (LD) pin and WEN pin must be held low. Data present on D0–D11 is transferred to the empty offset register on the first low-to-high transition of WCLK. By continuing to hold the LD and WEN pins low, data present on D0–D11 is transferred into the full offset register on the next transition of the WCLK. The third transition again writes to the empty offset registers can be written and then, by bringing the LD pin high, the FIFO is returned to normal read/write operation. When the LD pin and WEN pin and WEN again are set low, the next offset register in sequence is written.

The contents of the offset registers can be read on the data output lines Q0–Q11 when the  $\overline{\text{LD}}$  pin is set low, and  $\overline{\text{REN}}$  is set low. Data then can be read on the next low-to-high transition of RCLK. The first transition of RCLK presents the empty offset value to the data output lines. The next transition of RCLK presents the full offset value. Offset register content can be read in the standard mode only. It cannot be read in the FWFT mode.

## SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The SN74V245 can be configured during the configuration-at-reset cycle (see Table 6) with either asynchronous or synchronous timing for PAE and PAF flags.

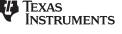

If asynchronous PAE/PAF configuration is selected (see Table 6), the PAE is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK. Similarly, the PAF is asserted low on the low-to-high transition of WCLK, and PAF is reset to high on the low-to-high transition of RCLK. For detailed timing diagrams, see Figure 11 for asynchronous PAE timing and Figure 12 for asynchronous PAF timing.

If synchronous PAE/PAF configuration is selected, PAE is asserted and updated on the rising edge of RCLK only, but not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only, but not RCLK. For detailed timing diagrams, see Figure 20 for synchronous PAE timing and Figure 21 for synchronous PAF timing.

| FL               | RXI | WXI | EF/OR                                          | FF/IR                                        | PAE, PAF     | FIFO TIMING MODE |

|------------------|-----|-----|------------------------------------------------|----------------------------------------------|--------------|------------------|

| 0                | 0   | 0   | Single register-buffered empty flag            | Single register-buffered full flag           | Asynchronous | Standard         |

| 0                | 0   | 1   | Triple register-buffered output-<br>ready flag | Double register-buffered input ready flag    | Asynchronous | FWFT             |

| 0                | 1   | 0   | Double register-buffered empty flag            | Double register-buffered full flag           | Asynchronous | Standard         |

| 0 <sup>(1)</sup> | 1   | 1   | Single register-buffered empty flag            | Single register-buffered full flag           | Asynchronous | Standard         |

| 1                | 0   | 0   | Single register-buffered empty flag            | Single register-buffered full<br>flag        | Synchronous  | Standard         |

| 1                | 0   | 1   | Triple register-buffered output-<br>ready flag | Double register-buffered input<br>ready flag | Synchronous  | FWFT             |

| 1                | 1   | 0   | Double register-buffered empty flag            | Double register-buffered full flag           | Synchronous  | Standard         |

| 1 <sup>(2)</sup> | 1   | 1   | Single register-buffered empty flag            | Single register-buffered full flag           | Asynchronous | Standard         |

#### Table 6. Truth Table for Configuration at Reset

(1) In daisy-chain depth expansion, FL is held low for the first-load device. The RXI and WXI inputs are driven by the corresponding RXO and WXO outputs of the preceding device.

(2) In daisy-chain depth expansion, FL is held high for members of the expansion other than the first-load device. The RXI and WXI inputs are driven by the corresponding RXO and WXO outputs of the preceding device.

#### **REGISTER-BUFFERED FLAG OUTPUT SELECTION**

The SN74V245 can be configured during the configuration-at-reset cycle (see Table 8) with single, double, or triple register-buffered flag output signals. The various combinations available are described in Table 7 and Table 8. In general, going from single to double or triple register-buffered flag outputs removes the possibility of metastable flag indications on boundary states (empty or full conditions). The tradeoff is the addition of clock-cycle delays for the respective flag to be asserted. Not all combinations of register-buffered flag outputs are supported. Register-buffered outputs apply to the empty flag and full flag only. Partial flags are not affected. Table 7 and Table 8 summarize the options available.

| OUTPUT READY | INPUT READY |               | PROC | GRAMMING AT I | RESET | FLAG TIMING          |  |  |  |  |  |

|--------------|-------------|---------------|------|---------------|-------|----------------------|--|--|--|--|--|

| (OR)         | (OR) (IR)   | PARTIAL FLAGS | FL   | RXI           | WXI   | DIAGRAMS             |  |  |  |  |  |

| Triple       | Double      | Asynchronous  | 0    | 0             | 1     | Figure 25            |  |  |  |  |  |

| Triple       | Double      | Synchronous   | 1    | 0             | 1     | Figure 18, Figure 19 |  |  |  |  |  |

## Table 7. Register-Buffered Flag Output Options, FWFT Mode

#### Table 8. Register-Buffered Flag Output Options, Standard Mode

| EMPTY FLAG FULL FLAG       |                            | PRO                          | GRAMMING AT |     |     |                         |

|----------------------------|----------------------------|------------------------------|-------------|-----|-----|-------------------------|

| (EF)<br>BUFFERED<br>OUTPUT | BUFFERED BUFFERED TIMING N | PARTIAL FLAGS<br>TIMING MODE | FL          | RXI | WXI | FLAG TIMING<br>DIAGRAMS |

| Single                     | Single                     | Asynchronous                 | 0           | 0   | 0   | Figure 7, Figure 8      |

| Single                     | Single                     | Synchronous                  | 1           | 0   | 0   | Figure 7, Figure 8      |

| Double                     | Double                     | Asynchronous                 | 0           | 1   | 0   | Figure 22, Figure 24    |

| Double                     | Double                     | Synchronous                  | 1           | 1   | 0   | Figure 22, Figure 24    |

# SN74V245-EP

ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

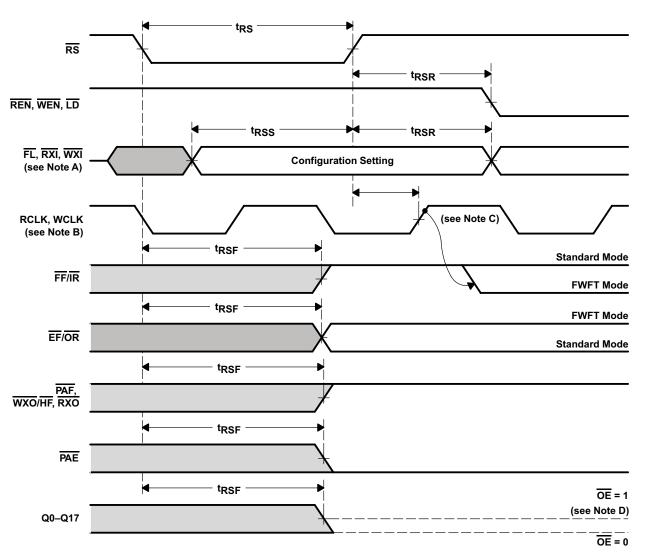

NOTES: A. Single-device mode (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0). FL, RXI, WXI should be static (tied to V<sub>CC</sub> or GND).

- B. The clocks (RCLK, WCLK) can be free-running asynchronously or coincidentally.

C. In FWFT mode, IR goes low based on the WCLK edge after reset.

- D. After reset, the outputs are low if  $\overline{OE} = 0$  and 3-state if  $\overline{OE} = 1$ .

## Figure 3. Reset Timing

www.ti.com.cn

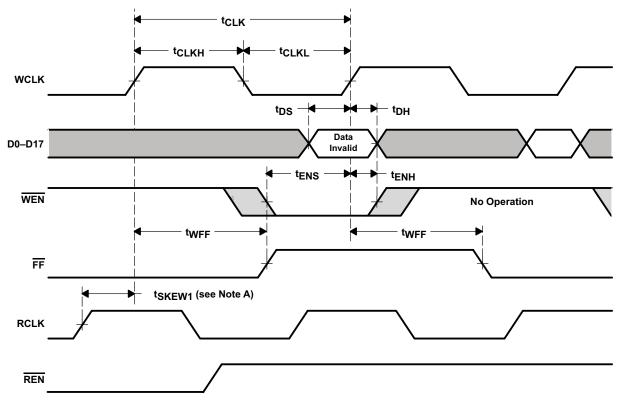

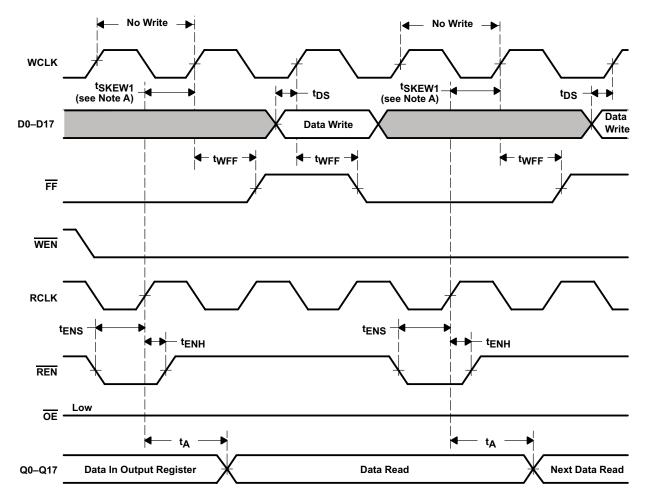

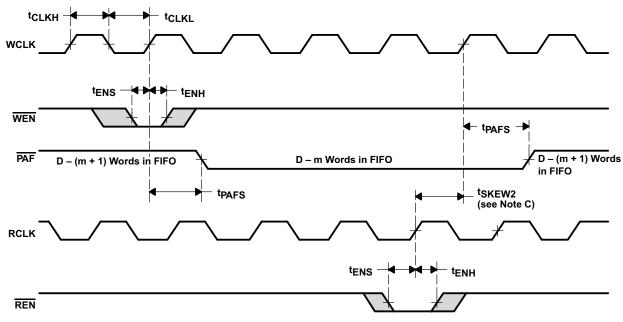

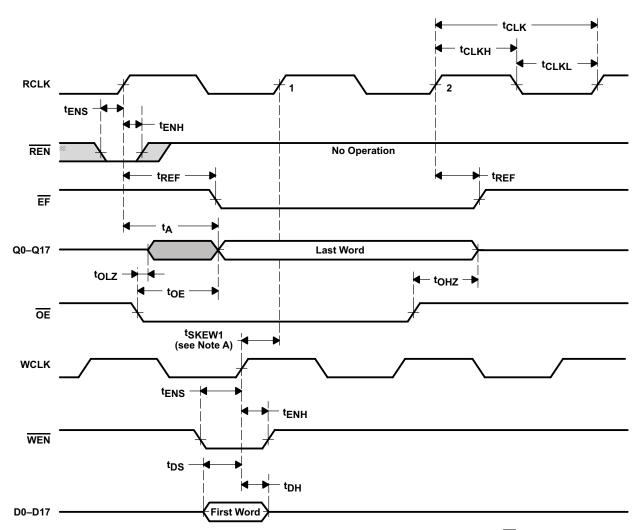

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, FF might not change state until the next WCLK edge.

B. Select standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

Figure 4. Write-Cycle Timing With Single Register-Buffered FF (Standard Mode)

www.ti.com.cn

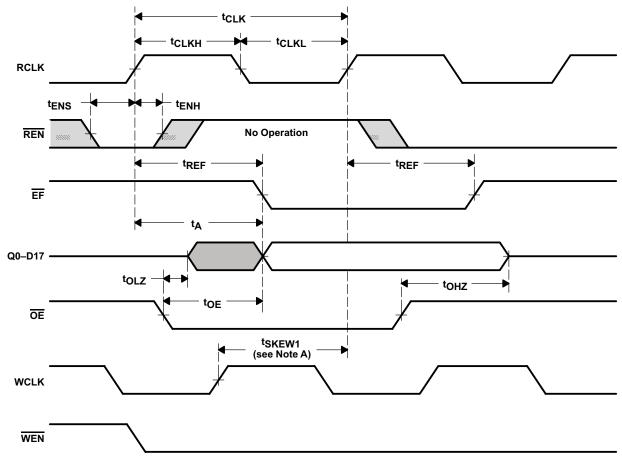

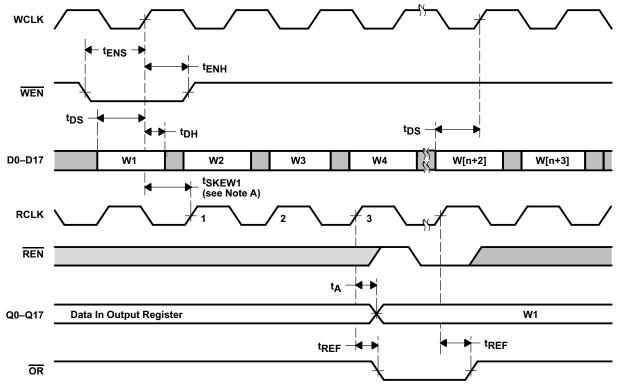

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge to ensure that EF goes high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, EF might not change state until the next RCLK edge.

B. Select standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

Figure 5. Read-Cycle Timing With Single Register-Buffered EF (Standard Mode)

ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

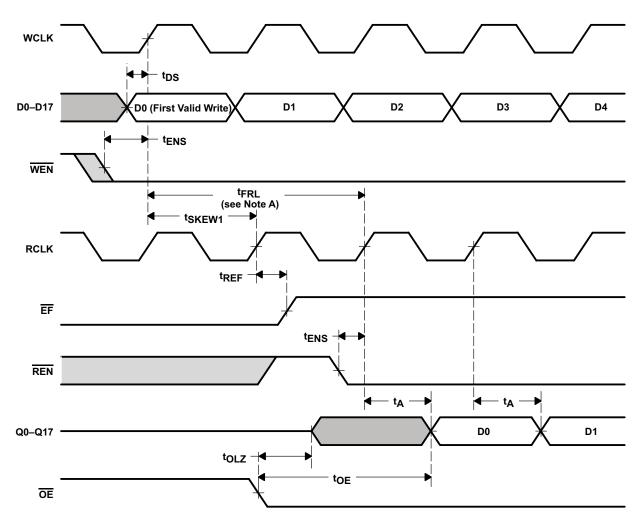

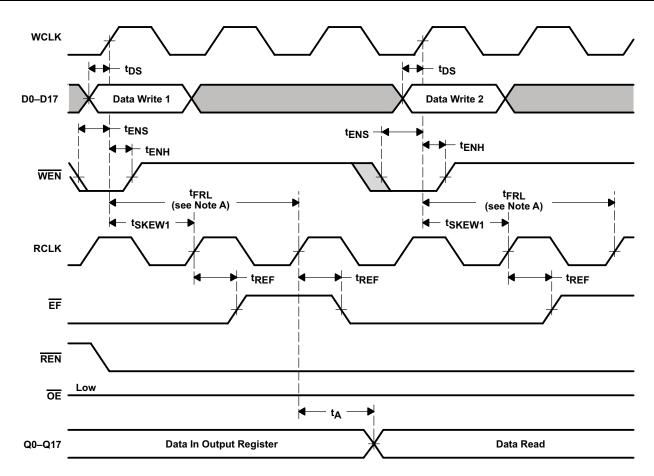

- NOTES: A. When t<sub>SKEW1</sub> is at the minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW1</sub>. When t<sub>SKEW1</sub> is less than the minimum specification, t<sub>FRL</sub> (maximum) = either (2 ×t<sub>CLK</sub>) + t<sub>SKEW1</sub> or t<sub>CLK</sub> + t<sub>SKEW1</sub>. The latency timing applies only at the empty boundary (EF is low).

- B. The first word always is available the cycle after EF goes high.

C. Select standard mode by setting (FL, RXI, WXI) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

### Figure 6. First-Data-Word Latency with Single Register-Buffered EF (Standard Mode)

www.ti.com.cn

- NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, FF might not change state until the next WCLK edge.

- B. Select standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

## Figure 7. Single Register-Buffered Full-Flag Timing (Standard Mode)

## SN74V245-EP

ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

NOTES: A. When t<sub>SKEW1</sub> is at the minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW1</sub>. When t<sub>SKEW1</sub> is less than the minimum specification, t<sub>FRL</sub> (maximum) = either (2 × t<sub>CLK</sub>) + t<sub>SKEW1</sub> or t<sub>CLK</sub> + t<sub>SKEW1</sub>. The latency timing applies only at the empty boundary (EF is low).

B. Select standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

#### Figure 8. Single Register-Buffered Empty Flag Timing (Standard Mode)

www.ti.com.cn

Figure 10. Read Programmable Registers (Standard Mode)

ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

- C. PAF is asserted to low on WCLK transition and reset to high on RCLK transition.

D. Select asynchronous modes by setting (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (0,1,1) or (1,1,1) during reset.

Figure 11. Asynchronous Programmable Almost-Empty-Flag Timing (Standard and FWFT Modes)

ÈXAS **NSTRUMENTS**

www.ti.com.cn

- C. For FWFT mode

- D. PAE is asserted low on RCLK transition and reset to high on WCLK transition.

E. Select the asynchronous modes by setting (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (0,1,1) or (1,1,1) during reset.

Figure 12. Asynchronous Programmable Almost-Full-Flag Timing (Standard and FWFT Modes)

ZHCSAL6A – DECEMBER 2012–REVISED JANUARY 2013

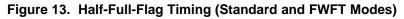

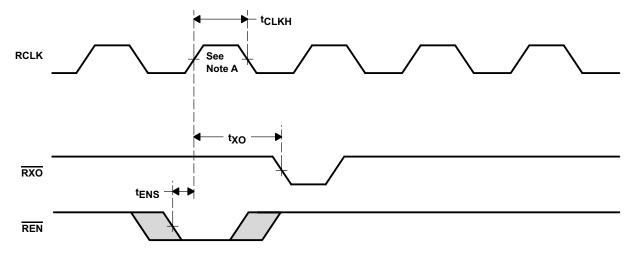

NOTES: A. D = maximum FIFO depth

- In FWFT mode: D = 4097 In standard mode: D = 4096

- B. For standard mode

- C. For FWFT mode

- D. Select single-device mode by setting  $(\overline{FL}, \overline{RXI}, \overline{WXI}) = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) \text{ or } (1,1,0) \text{ during reset.}$

NOTE A: Write to last physical location.

# SN74V245-EP

ZHCSAL6A-DECEMBER 2012-REVISED JANUARY 2013

www.ti.com.cn

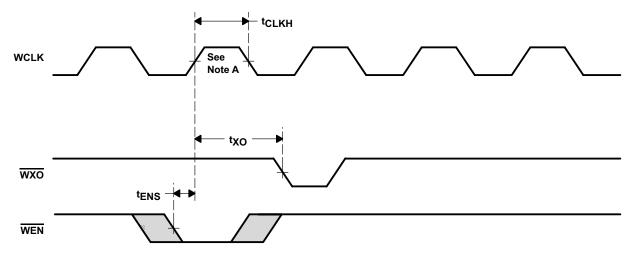

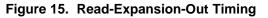

NOTE A: Read from last physical location.

Figure 17. Read-Expansion-In Timing

#### ZHCSAL6A - DECEMBER 2012 - REVISED JANUARY 2013

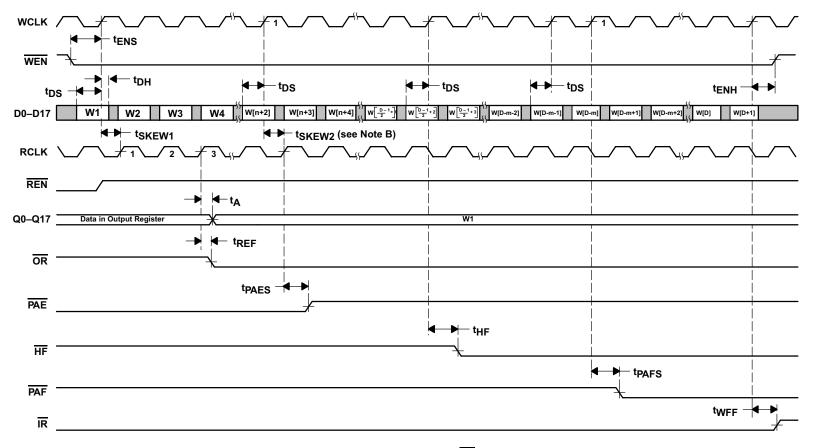

NOTES: A. t SKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge for OR to go low after two RCLK cycles plus t<sub>REF</sub>. If the time between the rising edge of WLCK and the rising edge of RCLK is less than t SKEW1, the OR deassertion might be delayed one extra RCLK cycle.

- B. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for PAE to go high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than tSKEW2, the PAE deassertion might be delayed one extra RCLK cycle.

- C. LD is high, OE is low.

- D.  $n = \overline{PAE}$  offset,  $m = \overline{PAF}$  offset, D = maximum FIFO depth = 4097 words

- E. Select synchronous FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (1,0,1) during reset.

## Figure 18. Write Timing With Synchronous Programmable Flags (FWFT Mode)

# SN74V245-EP

#### ZHCSAL6A-DECEMBER 2012-REVISED JANUARY 2013

www.ti.com.cn

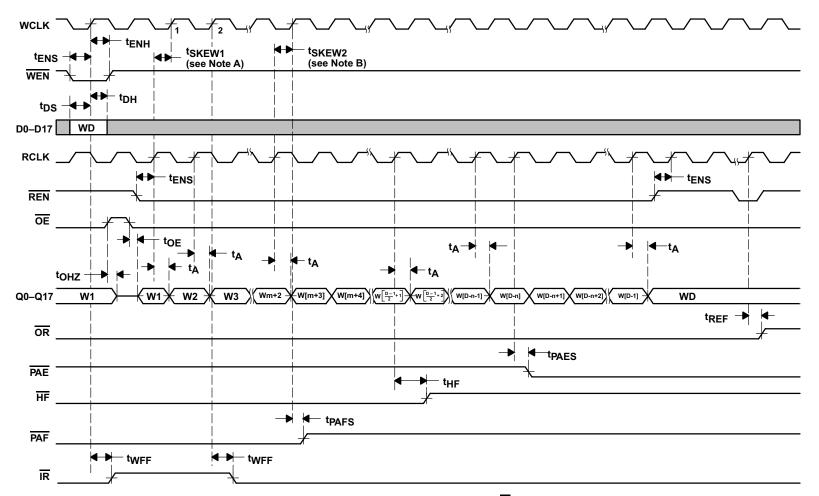

- NOTES: A. tSKEW1 is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that IR goes low after one WCLK plus tWFF. If the time between the rising edge of RLCK and the rising edge of WCLK is less than tSKEW1, the IR assertion might be delayed an extra WCLK cycle.

- B. t<sub>SKEW2</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to go high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW2</sub>, the PAF deassertion time may be delayed an extra WCLK cycle.

- C. LD is high.

- D. n = PAE offset, m = PAF offset, D = maximum FIFO depth = 4097 words

- E. Select synchronous FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (1,0,1) during reset.

#### Figure 19. Read Timing With Synchronous Programmable Flags (FWFT Mode)

- C. For FWFT mode

- D.  $t_{SKEW2}$  is the minimum time between a rising WCLK edge and a rising RCLK edge for  $\overline{PAE}$  to go high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW2</sub>, the PAE deassertion might be delayed one extra RCLK cycle.

- E. PAE is asserted and updated on the rising edge of RCLK only.

F. Select synchronous modes by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during reset.

## Figure 20. Synchronous Programmable Almost-Empty-Flag Timing (Standard and FWFT Modes)

www.ti.com.cn

- NOTES: A.  $m = \overline{PAF}$  offset

- B. D = maximum FIFO depth

- In FWFT mode: D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235, and 4097 for the SN74V245. In standard mode: D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the SN74V235, and 4096 for the SN74V245.

- C. t<sub>SKEW2</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to go high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than tSKEW2, the PAF deassertion time might be delayed an extra WCLK cycle.

- D. PAF is asserted and updated on the rising edge of WCLK only.

E. Select synchronous modes by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during reset.

## Figure 21. Synchronous Programmable Almost-Full-Flag Timing (Standard and FWFT Modes)

ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high after one WCLK cycle plus t<sub>WFF</sub>. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, the FF deassertion time might be delayed an extra WCLK cycle.

B. LD is high.

C. Select double register-buffered standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,1,0) or (1,1,0) during reset.

Figure 22. Double Register-Buffered Full-Flag Timing (Standard Mode)

www.ti.com.cn

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that  $\overline{FF}$  goes high after one WCLK cycle plus t<sub>RFF</sub>. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, the  $\overline{FF}$  deassertion might be delayed an extra WCLK cycle.

- B. LD is high.

- C. Select double register-buffered standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,1,0) or (1,1,0) during reset.

Figure 23. Write-Cycle Timing With Double Register-Buffered FF (Standard Mode)

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge to ensure that EF goes high after one RCLK cycle plus t<sub>REF</sub>. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, the EF deassertion might be delayed an extra RCLK cycle.

B. LD is high.

C. Select double register-buffered standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,1,0) or (1,1,0) during reset.

Figure 24. Read-Cycle Timing With Double Register-Buffered EF (Standard Timing)

# SN74V245-EP

## ZHCSAL6A-DECEMBER 2012-REVISED JANUARY 2013

www.ti.com.cn

NSTRUMENTS

EXAS

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge for OR to go high during the current cycle. If the time between the rising edge of WLCK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, the OR deassertion might be delayed one extra RCLK cycle.

B.  $\overline{\text{LD}}$  is high,  $\overline{\text{OE}}$  is low.

C. Select FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,1) or (1,0,1) during reset.

Figure 25. OR-Flag Timing and First Word Fall Through When FIFO is Empty (FWFT mode)

#### ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

## **OPERATING CONFIGURATIONS**

## SINGLE-DEVICE CONFIGURATION

A single SN74V245 can be used when the application requirements are for 4096 words or fewer. These FIFOs are in a single-device configuration when the first load (FL), write expansion in (WXI) and read expansion in (RXI) control inputs are configured as (FL, RXI, WXI = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0) during reset (see Figure 26).

Figure 26. Block Diagram of Single 4096 x 18 Synchronous FIFO

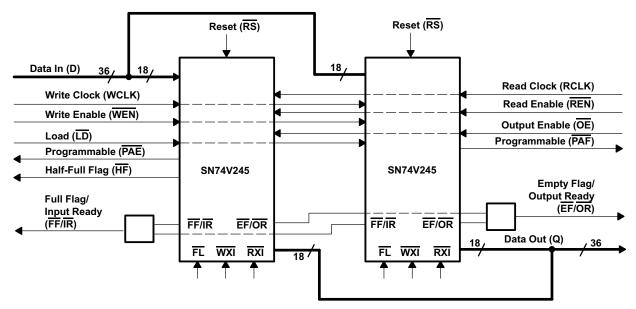

## WIDTH-EXPANSION CONFIGURATION

Word width may be increased simply by connecting together the control signals of multiple devices. Status flags can be detected from any one device. The exceptions are the empty flag/output ready and full flag/input ready. Because of variations in skew between RCLK and WCLK, it is possible for flag assertion and deassertion to vary by one cycle between FIFOs. To avoid problems, the user must create composite flags by gating the empty flags/output ready of every FIFO, and separately gating all full flags/input ready. Figure 27 demonstrates a 36-word width by using two SN74V245 memories. Any word width can be attained by adding additional SN74V245 memories. These FIFOs are in a single-device configuration when the first load (FL), write expansion in (WXI), and read expansion in (RXI) control inputs are configured as (FL, RXI, WXI = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0) during reset (see Figure 27).

NOTE A: Do not connect any output control signals directly together.

# Figure 27. Block Diagram of 4096 × 36 Synchronous FIFO Memory Used in a Width-Expansion Configuration

ZHCSAL6A – DECEMBER 2012 – REVISED JANUARY 2013

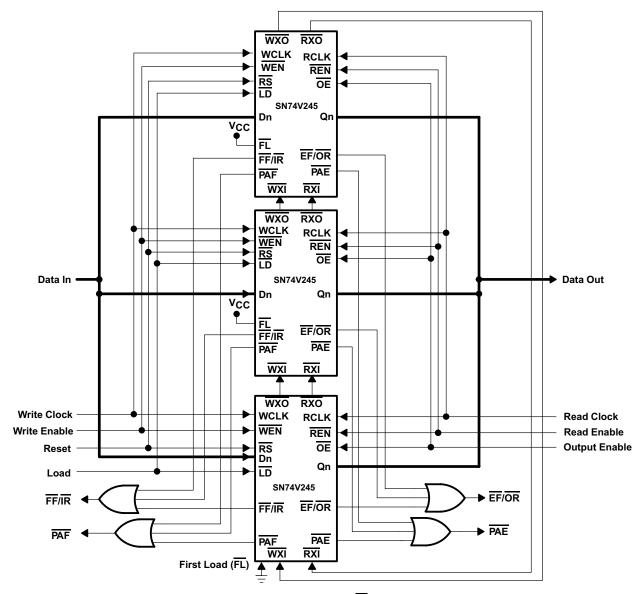

# DEPTH-EXPANSION CONFIGURATION, DAISY-CHAIN TECHNIQUE (WITH PROGRAMMABLE FLAGS)

These devices can be adapted easily to applications requiring more than 4096 words of buffering. Figure 28 shows depth expansion using three SN74V245 memories. Maximum depth is limited only by signal loading.

NOTES: A. The first device must be designated by grounding the first load (FL) control input.

- B. All other devices must have  $\overline{FL}$  in the high state.

- C. The write expansion out  $(\overline{WXO})$  pin of each device must be tied to the write expansion in  $(\overline{WXO})$  pin of the next device.

- D. The read expansion out (RXO) pin of each device must be tied to the read expansion in (RXI) pin of the next device.

- E. All load (LD) pins are tied together.

- F. The half-full flag (HF) is not available in this depth-expansion configuration.

- G. EF, FF, PAE, and PAF are created with composite flags by ORing together every respective flag for monitoring. The composite PAE and PAF flags are not precise.

- H. In daisy-chain mode, the flag outputs are single-register buffered and the partial flags are in asynchronous timing mode.

# Figure 28. Block Diagram of 12288 × 18 Synchronous FIFO Memory With Programmable Flags Used in Depth-Expansion Configuration

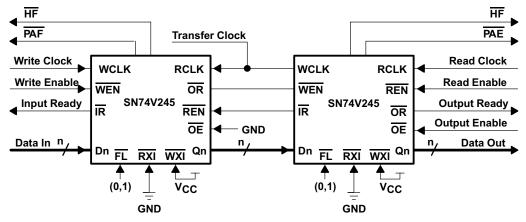

## **DEPTH-EXPANSION CONFIGURATION (FWFT MODE)**

In FWFT mode, the FIFOs can be connected in series (the data outputs of one FIFO connected to the data inputs of the next) with no external logic necessary. The resulting configuration provides a total depth equivalent to the sum of the depths associated with each single FIFO. NO TAG shows a depth expansion using two SN74V245 memories.

Care should be taken to select FWFT mode during master reset for all FIFOs in the depth expansion configuration. The first word written to an empty configuration passes from one FIFO to the next (ripple down) until it finally appears at the outputs of the last FIFO in the chain. No read operation is necessary, but the RCLK of each FIFO must be free running. Each time the data word appears at the outputs of one FIFO, that device's OR line goes low, enabling a write to the next FIFO in line.

For an empty expansion configuration, the amount of time it takes for  $\overline{OR}$  of the last FIFO in the chain to go low (i.e., valid data to appear on the last FIFO's outputs) after a word has been written to the first FIFO is the sum of the delays for each individual FIFO:

$$(N - 1) \times (4 \times \text{transfer clock}) + 3 \times T_{\text{RCLK}}$$

(1)

(2)

FXAS

**ISTRUMENTS**

www.ti.com.cn

Where: N is the number of FIFOs in the expansion and  $T_{RCLK}$  is the RCLK period. Extra cycles should be added for the possibility that the  $t_{SKEW1}$  specification is not met between WCLK and transfer clock, or RCLK and transfer clock, for the OR flag.

The ripple-down delay is noticeable only for the first word written to an empty depth-expansion configuration. There is no delay evident for subsequent words written to the configuration.

The first free location created by reading from a full depth-expansion configuration bubbles up from the last FIFO to the previous one until finally it moves into the first FIFO of the chain. Each time a free location is created in one FIFO of the chain, that FIFO's IR line goes low, enabling the preceding FIFO to write a word to fill it.

For a full expansion configuration, the amount of time it takes for IR of the first FIFO in the chain to go low after a word has been read from the last FIFO is the sum of the delays for each individual FIFO:

$(N - 1) \times (3 \times \text{transfer clock}) + 2T_{\text{WCLK}}$

Where: N is the number of FIFOs in the expansion and  $T_{WCLK}$  is the WCLK period. Extra cycles should be added for the possibility that the  $t_{SKEW1}$  specification is not met between RCLK and transfer clock, or WCLK and transfer clock, for the IR flag.

The transfer clock line should be tied to either WCLK or RCLK, whichever is faster. Both these actions result in data moving, as quickly as possible, to the end of the chain and free locations to the beginning of the chain.

10-Dec-2020

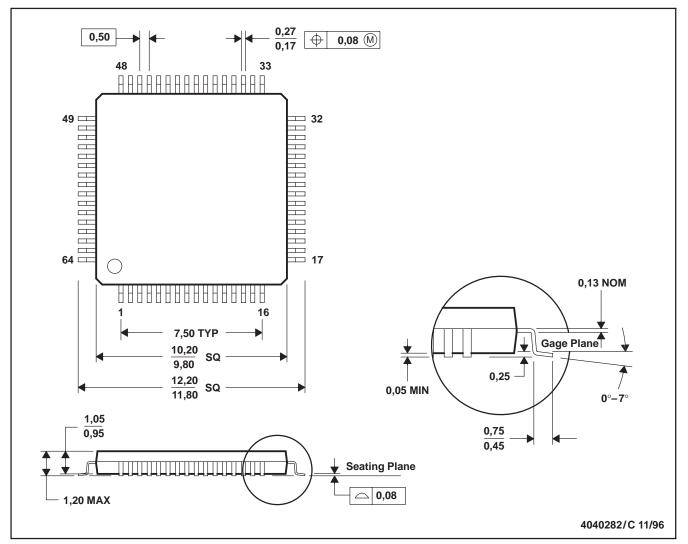

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| SN74V245-15PAGEP | ACTIVE        | TQFP         | PAG                | 64   | 160            | RoHS & Green    | NIPDAU                               | Level-3-260C-168 HR  | -55 to 125   | V245-15EP               | Samples |

| V62/13606-01XE   | ACTIVE        | TQFP         | PAG                | 64   | 160            | RoHS & Green    | NIPDAU                               | Level-3-260C-168 HR  | -55 to 125   | V245-15EP               | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.