LMH6580, LMH6581

www.ti.com

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

# LMH6580/LMH6581 8x4 500 MHz Analog Crosspoint Switch, Gain of 1,

## Gain of 2

Check for Samples: LMH6580, LMH6581

## **FEATURES**

- 8 Inputs and 4 Outputs

- 48-pin TQFP Package

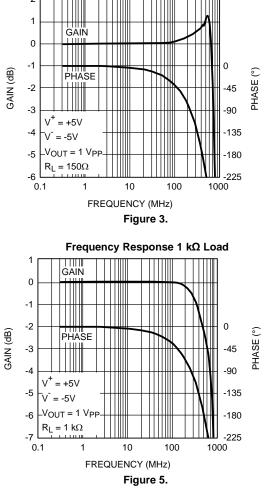

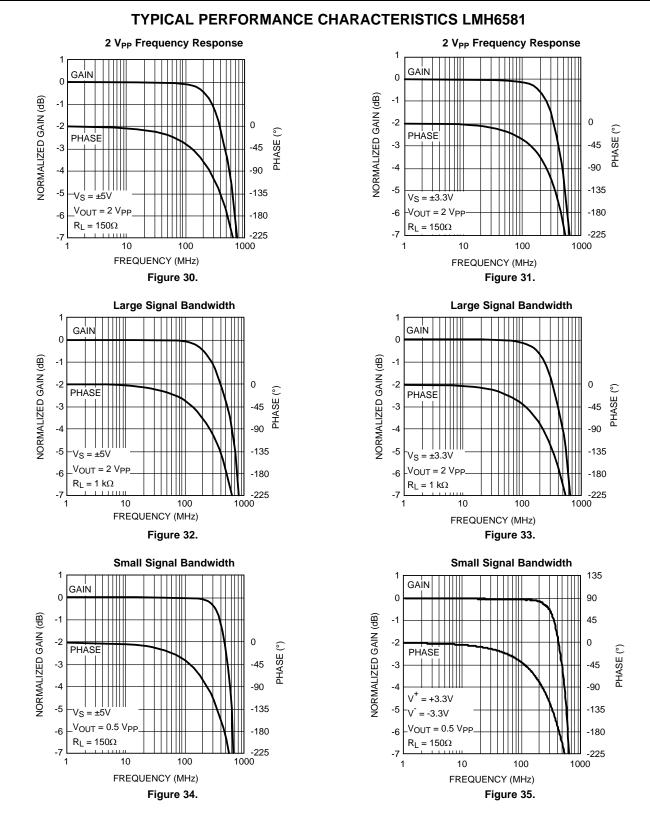

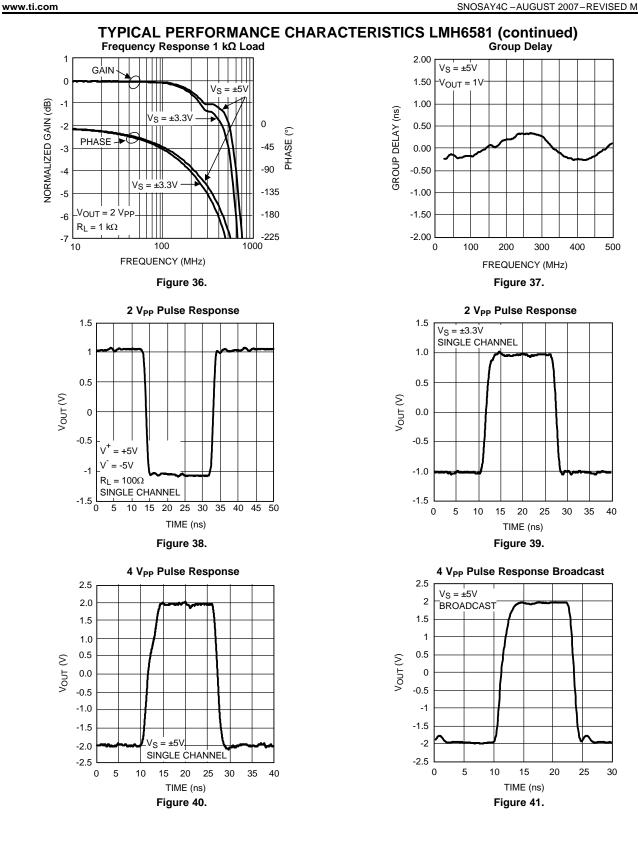

- -3 dB Bandwidth ( $V_{OUT} = 2 V_{PP}$ ,  $R_L = 1 k\Omega$ ) 500 MHz

- -3 dB Bandwidth (V<sub>OUT</sub> = 2 V<sub>PP</sub>, R<sub>L</sub> = 150 $\Omega$ ) 450 MHz

- Fast Slew Rate 2100 V/µs

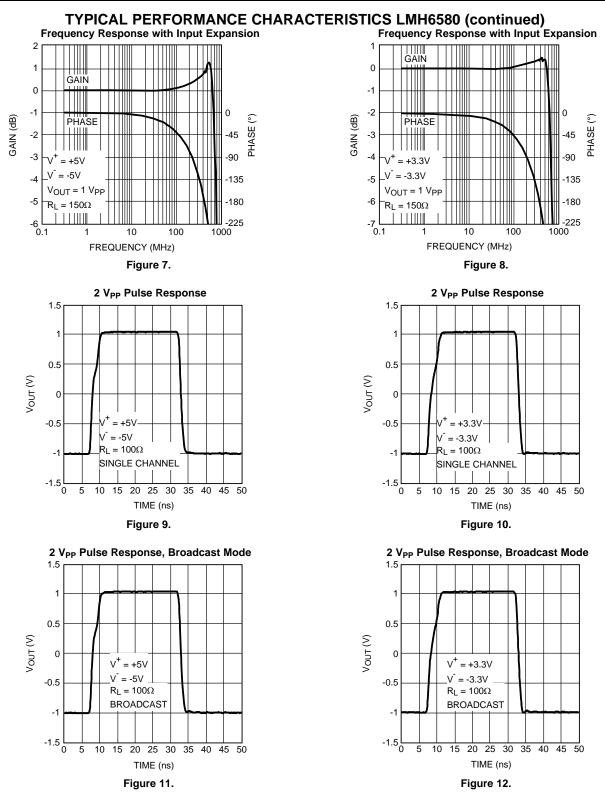

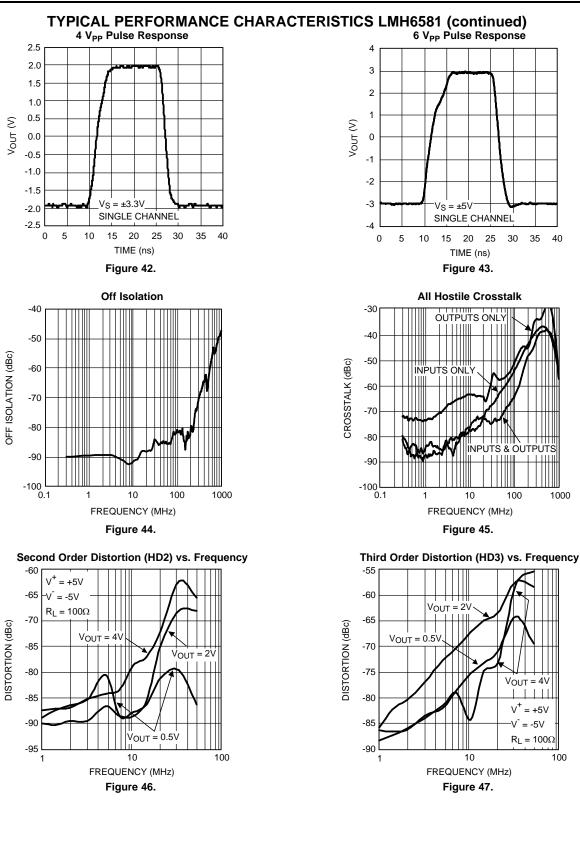

- Channel to Channel Crosstalk (10/100 MHz) -70/ -52 dBc

- All Hostile Crosstalk (10/100 MHz) -55/-45 dBc

- Easy to Use Serial Programming 4 Wire Bus

- **Two Programming Modes Serial & Addressed** Modes

- Symmetrical Pinout Facilitates Expansion.

- Output Current ±70 mA

- Two Gain Options  $A_V = 1$  or  $A_V = 2$

## APPLICATIONS

- Studio Monitoring/Production Video Systems

- **Conference Room Multimedia Video Systems**

- KVM (Keyboard Video Mouse) Systems

- Security/Surveillance Systems

- **Multi-Antenna Diversity Radio**

- Video Test Equipment

- **Medical Imaging**

- Wide-Band Routers & Switches

## DESCRIPTION

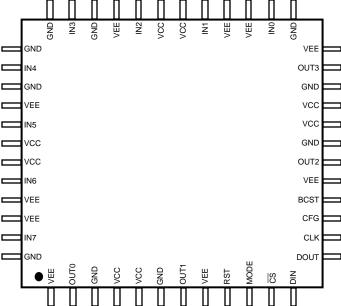

The LMH<sup>™</sup> family of products is joined by the LMH6580 and the LMH6581, high speed, nonanalog, crosspoint switches. blocking. The LMH6580/LMH6581 are designed for high speed, DC coupled, analog signals such as high resolution video (UXGA and higher). The LMH6580/LMH6581 each has eight inputs and four outputs. The non-blocking architecture allows any output to be connected to any input, including an input that is already selected. With fully buffered inputs the LMH6580/LMH6581 can be impedance matched to nearly any source impedance. The buffered outputs of the LMH6580/LMH6581 can drive up to two back terminated video loads (75Ω load). The outputs and inputs also feature high impedance inactive states allowing high performance input and output expansion for array sizes such as 8 x 8 or 16 x 4 by combining two devices. The LMH6580/LMH6581 are controlled with a 4 pin serial interface that can be configured as a 3 wire interface. Both serial mode and addressed modes are available.

The LMH6580/LMH6581 come in 48-pin TQFP packages. They also have diagonally symmetrical pin assignments to facilitate double sided board layouts and easy pin connections for expansion.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. LMH is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### **Connection Diagram**

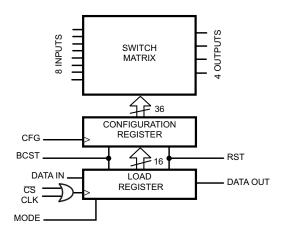

### **Block Diagram**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

INSTRUMENTS

Texas

#### www.ti.com

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

| ESD Tolerance <sup>(3)</sup> | Human Body Model                 | 2000V                            |

|------------------------------|----------------------------------|----------------------------------|

|                              | Machine Model                    | 200V                             |

| Vs                           |                                  | ±6V                              |

| I <sub>IN</sub> (Input Pins) | ±20 mA                           |                                  |

| I <sub>OUT</sub>             |                                  | See <sup>(4)</sup>               |

| Input Voltage Range          |                                  | V <sup>-</sup> to V <sup>+</sup> |

| Maximum Junction Temperature |                                  | +150°C                           |

| Storage Temperature Range    |                                  | −65°C to +150°C                  |

| Soldering Information        | Infrared or Convection (20 sec.) | 235°C                            |

|                              | Wave Soldering (10 sec.)         | 260°C                            |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see ±3.3V Electrical Characteristics and ±5V Electrical Characteristics.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

(3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(4) The maximum output current ( $I_{OUT}$ ) is determined by device power dissipation limitations. The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

#### **OPERATING RATINGS**<sup>(1)</sup>

| Temperature Range <sup>(2)</sup> | -40°C to +85°C  |        |

|----------------------------------|-----------------|--------|

| Supply Voltage Range             | ±3V to ±5.5V    |        |

| Thermal Resistance 48-Pin TQFP   | θ <sub>JA</sub> | 44°C/W |

|                                  | θ <sub>JC</sub> | 12°C/W |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see ±3.3V Electrical Characteristics and ±5V Electrical Characteristics.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/|\theta_{JA}|$ . All numbers apply for packages soldered directly onto a PC Board.

#### ±3.3V ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

Unless otherwise specified, typical conditions are:  $T_A = 25^{\circ}C$ ,  $A_V = +2$ ,  $V_S = \pm 3.3V$ ,  $R_L = 100\Omega$ ; **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter            | Conditions                                                                                                                     | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-------|

| Frequency      | / Domain Performance |                                                                                                                                | ·                  | *                  |                    |       |

| SSBW           | -3 dB Bandwidth      | $V_{OUT} = 0.5 V_{PP}$                                                                                                         |                    | 425                |                    |       |

| LSBW           | _                    | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> ,<br>LMH6581 V <sub>OUT</sub> = 2 V <sub>PP</sub> , R <sub>L</sub> = 1 k $\Omega$ |                    | 500                |                    | MHz   |

|                |                      | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> , LMH6581 V <sub>OUT</sub> = 2 V <sub>PP</sub> , R <sub>L</sub> = 150 $\Omega$    |                    | 450                |                    |       |

| GF             | 0.1 dB Gain Flatness | LMH6580 V <sub>OUT</sub> = 1 V <sub>PP</sub> ,<br>LMH6581 V <sub>OUT</sub> = 2 V <sub>PP</sub> , R <sub>L</sub> = 150 $\Omega$ |                    | 70                 |                    | MHz   |

| Time Dom       | ain Response         |                                                                                                                                |                    |                    |                    |       |

| t <sub>r</sub> | Rise Time            | LMH6580 1V Step, LMH6581<br>2V Step, 10% to 90%                                                                                |                    | 3.1                |                    | ns    |

| t <sub>f</sub> | Fall Time            | LMH6580 1V Step, LMH6581<br>2V Step, 10% to 90%                                                                                |                    | 1.4                |                    | ns    |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. No ensured parametric performance is indicated in the electrical tables under conditions different than those tested.

(2) Room Temperature limits are 100% production tested at 25°C. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

Copyright © 2007–2013, Texas Instruments Incorporated

EXAS

## ±3.3V ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (continued)

Unless otherwise specified, typical conditions are:  $T_A = 25^{\circ}C$ ,  $A_V = +2$ ,  $V_S = \pm 3.3V$ ,  $R_L = 100\Omega$ ; **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                        | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units   |

|-------------------|-------------------------------------|---------------------------------------------------|--------------------|--------------------|--------------------|---------|

| OS                | Overshoot                           | 2V Step                                           |                    | <1                 |                    | %       |

| SR                | Slew Rate                           | LMH6580, 2 $V_{PP}$ , 40% to 60% <sup>(4)</sup>   |                    | 900                |                    | V/µs    |

|                   | Slew Rate                           | LMH6581, 2 $V_{PP}$ , 40% to 60% $^{(4)}$         |                    | 1700               |                    | V/µs    |

| t <sub>s</sub>    | Settling Time                       | 2V Step, V <sub>OUT</sub> within 0.5%             |                    | 7                  |                    | ns      |

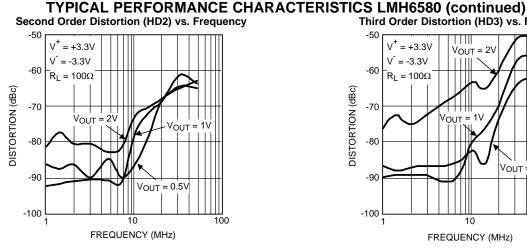

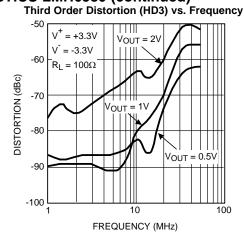

| Distortion        | And Noise Response                  |                                                   | ·                  |                    |                    |         |

| HD2               | 2 <sup>nd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 10 MHz                        |                    | -76                |                    | dBc     |

| HD3               | 3 <sup>rd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 10 MHz                        |                    | -76                |                    | dBc     |

| e <sub>n</sub>    | Input Referred Voltage Noise        | >1 MHz                                            |                    | 12                 |                    | nV/ √Hz |

| i <sub>n</sub>    | Input Referred Noise Current        | >1 MHz                                            |                    | 2                  |                    | pA/ √Hz |

| XTLK              | Crosstalk                           | All Hostile, f = 100 MHz                          |                    | -45                |                    | dBc     |

| ISOL              | Off Isolation                       | f = 100 MHz                                       |                    | -60                |                    | dBc     |

| Static, DC        | Performance                         |                                                   |                    |                    | l                  |         |

| A <sub>V</sub>    | Gain                                | LMH6581                                           | 1.986              | 2.00               | 2.014              |         |

|                   |                                     | LMH6580                                           | 0.994              | 1.00               | 1.005              |         |

| V <sub>OS</sub>   | Input Offset Voltage                |                                                   |                    | ±3                 | ±17                | mV      |

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift  | See <sup>(5)</sup>                                |                    | 38                 |                    | µV/°C   |

| IB                | Input Bias Current                  | Non-Inverting <sup>(6)</sup>                      |                    | -5                 |                    | μA      |

| TCIB              | Input Bias Current Average Drift    | Non-Inverting <sup>(5)</sup>                      |                    | -12                |                    | nA/°C   |

| Vo                | Output Voltage Range                | LMH6581, R <sub>L</sub> = 100Ω                    | ±1.8               | ±2.1               |                    |         |

| 0                 |                                     | LMH6580, R <sub>L</sub> = 100Ω                    | ±1.24              | ±1.3               |                    | V       |

| Vo                | Output Voltage Range                | LMH6581, $R_{L} = \infty \Omega$ , <sup>(7)</sup> | ±2.08              | ±2.2               |                    |         |

| 0                 |                                     | LMH6580 R <sub>L</sub> = ∞Ω,                      | ±1.25              | ±1.3               |                    | V       |

| PSRR              | Power Supply Rejection Ratio        |                                                   |                    | -45                |                    | dBc     |

| I <sub>CC</sub>   | Positive Supply Current             | R <sub>L</sub> = ∞                                |                    | 50                 | 60                 | mA      |

| I <sub>EE</sub>   | Negative Supply Current             | $R_L = \infty$                                    |                    | 50                 | 56                 | mA      |

|                   | Tri State Supply Current            | RST Pin > 2.0V                                    |                    | 10                 | 13                 | mA      |

| Miscellane        | eous Performance                    |                                                   |                    |                    |                    |         |

| R <sub>IN</sub>   | Input Resistance                    | Non-Inverting                                     |                    | 100                |                    | kΩ      |

| C <sub>IN</sub>   | Input Capacitance                   | Non-Inverting                                     |                    | 1                  |                    | pF      |

| R <sub>O</sub>    | Output Resistance Enabled           | Closed Loop, Enabled                              |                    | 300                |                    | mΩ      |

| R <sub>o</sub>    | Output Resistance Disabled          | LMH6580                                           |                    | 50                 |                    |         |

| 0                 |                                     | LMH6581                                           | 1100               | 1350               | 1500               | kΩ      |

| CMVR              | Input Common Mode Voltage<br>Range  |                                                   |                    | ±1.3               |                    | V       |

| lo                | Output Current                      | Sourcing, $V_0 = 0 V$                             |                    | ±50                |                    | mA      |

| Digital Co        |                                     |                                                   |                    | Į                  | ļ                  | -       |

| V <sub>IH</sub>   | Input Voltage High                  |                                                   | 2.0                |                    |                    | V       |

| VIL               | Input Voltage Low                   |                                                   |                    |                    | 0.8                | V       |

| V <sub>OH</sub>   | Output Voltage High                 |                                                   |                    | >2.0               |                    | V       |

| V <sub>OL</sub>   | Output Voltage Low                  |                                                   |                    | <0.4               |                    | V       |

| 01                | Switching Time                      |                                                   |                    | 15                 |                    | ns      |

| Ts                | Setup Time                          |                                                   |                    | 7                  |                    | ns      |

| T <sub>H</sub>    | Hold Time                           |                                                   |                    | 7                  |                    | ns      |

Slew Rate is the average of the rising and falling edges. (4)

Drift determined by dividing the change in parameter at temperature extremes by the total temperature change. Negative input current implies current flowing out of the device.

(5) (6)

(7) This parameter is specified by design and/or characterization and is not tested in production.

4 Submit Documentation Feedback

www.ti.com

#### ±5V ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

Unless otherwise specified, typical conditions are:  $T_A = 25^{\circ}C$ ,  $A_V = +2$ ,  $V_S = \pm 5V$ ,  $R_L = 100\Omega$ ; **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                                                                                                                                                                               | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units   |

|-------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------|

| Frequency         | y Domain Performance                | <u>"</u>                                                                                                                                                                                                 | 1                  |                    |                    |         |

| SSBW              | −3 dB Bandwidth                     | $V_{OUT} = 0.5 V_{PP}^{(4)}$                                                                                                                                                                             |                    | 450                |                    |         |

|                   | _                                   | $      LMH6580 \ V_{OUT} = 1 \ V_{PP}, \\ LMH6581 \ V_{OUT} = 2 \ V_{PP}, \ R_L = 1 \ k\Omega $                                                                                                          |                    | 500                |                    | MHz     |

| LSBW              | _                                   | $\label{eq:limit} \begin{array}{l} \text{LMH6580 V}_{\text{OUT}} = 1 \ \text{V}_{\text{PP}}, \\ \text{LMH6581 V}_{\text{OUT}} = 2 \ \text{V}_{\text{PP}}, \ \text{R}_{\text{L}} = 150\Omega \end{array}$ |                    | 450                |                    |         |

| GF                | 0.1 dB Gain Flatness                | LMH6580, $V_{OUT}$ = 1 $V_{PP}$ ,<br>LMH6581, $V_{OUT}$ = 2 $V_{PP}$ , $R_L$ = 150 $\Omega$                                                                                                              |                    | 100                |                    | MHz     |

| DG                | Differential Gain                   | R <sub>L</sub> = 150Ω, 3.58 MHz/4.43 MHz                                                                                                                                                                 |                    | .05                |                    | %       |

| DP                | Differential Phase                  | R <sub>L</sub> = 150Ω, 3.58 MHz/4.43 MHz                                                                                                                                                                 |                    | .05                |                    | deg     |

| Time Dom          | ain Response                        |                                                                                                                                                                                                          |                    |                    |                    |         |

| t <sub>r</sub>    | Rise Time                           | LMH6580 2V, Step, 10% to 90%                                                                                                                                                                             |                    | 2.8                |                    |         |

|                   |                                     | LMH6581 2V, Step, 10% to 90%                                                                                                                                                                             |                    | 1.2                |                    | ns      |

| t <sub>f</sub>    | Fall Time                           | 2V Step, 10% to 90%                                                                                                                                                                                      |                    | 1.6                |                    | ns      |

| OS                | Overshoot                           | 2V Step                                                                                                                                                                                                  |                    | <1                 |                    | %       |

| SR                | Slew Rate                           | LMH6580, 2 V <sub>PP</sub> , 40% to 60% <sup>(5)</sup>                                                                                                                                                   |                    | 1200               |                    | V/µs    |

| SR                | Slew Rate                           | LMH6581, 6 V <sub>PP</sub> , 40% to 60% <sup>(5)</sup>                                                                                                                                                   |                    | 2100               |                    | V/µs    |

| t <sub>s</sub>    | Settling Time                       | 2V Step, V <sub>OUT</sub> Within 0.5%                                                                                                                                                                    |                    | 6                  |                    | ns      |

| Distortion        | And Noise Response                  |                                                                                                                                                                                                          |                    |                    |                    |         |

| HD2               | 2 <sup>nd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 5 MHz                                                                                                                                                                                |                    | -80                |                    | dBc     |

| HD3               | 3 <sup>rd</sup> Harmonic Distortion | 2 V <sub>PP</sub> , 5 MHz                                                                                                                                                                                |                    | -70                |                    | dBc     |

| en                | Input Referred Voltage Noise        | >1 MHz                                                                                                                                                                                                   |                    | 12                 |                    | nV/ √Hz |

| i <sub>n</sub>    | Input Referred Noise Current        | >1 MHz                                                                                                                                                                                                   |                    | 2                  |                    | pA/ √Hz |

| XTLK              | Cross Talk                          | All Hostile, f = 100 MHz                                                                                                                                                                                 |                    | -45                |                    | dBc     |

|                   |                                     | Channel to Channel, f = 100 MHz                                                                                                                                                                          |                    | -52                |                    | dBc     |

| ISOL              | Off Isolation                       | f = 100 MHz                                                                                                                                                                                              |                    | -65                |                    | dBc     |

| Static, DC        | Performance                         |                                                                                                                                                                                                          |                    |                    |                    |         |

| A <sub>V</sub>    | Gain                                | LMH6581                                                                                                                                                                                                  | 1.986              | 2.00               | 2.014              |         |

|                   |                                     | LMH6580                                                                                                                                                                                                  | 0.995              | 1.00               | 1.005              |         |

| V <sub>os</sub>   | Input Offset Voltage                |                                                                                                                                                                                                          |                    | ±2                 | ±17                | mV      |

| TCV <sub>os</sub> | Input Offset Voltage Average Drift  | See <sup>(6)</sup>                                                                                                                                                                                       |                    | 38                 |                    | µV/°C   |

| I <sub>B</sub>    | Input Bias Current                  | Non-Inverting <sup>(7)</sup>                                                                                                                                                                             |                    | -5                 | ±12                | μA      |

| TCIB              | Input Bias Current Average Drift    | Non-Inverting <sup>(6)</sup>                                                                                                                                                                             |                    | -12                |                    | nA/°C   |

| Vo                | Output Voltage Range                | LMH681, R <sub>L</sub> = 100Ω                                                                                                                                                                            | ±3.4               | ±3.6               |                    |         |

|                   |                                     | LMH6580, R <sub>L</sub> = 100Ω                                                                                                                                                                           | ±2.9               | ±3.0               |                    | V       |

| Vo                | Output Voltage Range                | LMH6581, R <sub>L</sub> = ∞Ω                                                                                                                                                                             | ±3.7               | ±3.9               |                    |         |

|                   |                                     | LMH6580, $R_L = \infty \Omega$                                                                                                                                                                           | ±2.9               | ±3.0               |                    | V       |

| PSRR              | Power Supply Rejection Ratio        | DC                                                                                                                                                                                                       | -42                | -45                |                    | dBc     |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. No ensured parametric performance is indicated in the electrical tables under conditions different than those tested.

(2) Room Temperature limits are 100% production tested at 25°C. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

(4) This parameter is specified by design and/or characterization and is not tested in production.

(5) Slew Rate is the average of the rising and falling edges.

(6) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(7) Negative input current implies current flowing out of the device.

Copyright © 2007–2013, Texas Instruments Incorporated

www.ti.com

## ±5V ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (continued)

Unless otherwise specified, typical conditions are:  $T_A = 25^{\circ}C$ ,  $A_V = +2$ ,  $V_S = \pm 5V$ ,  $R_L = 100\Omega$ ; **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter                          | Conditions                    | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units |  |

|-----------------|------------------------------------|-------------------------------|--------------------|--------------------|--------------------|-------|--|

| XTLK            | DC Crosstalk Rejection             | DC, Channel to Channel        | -62                | -90                |                    | dBc   |  |

| OISO            | DC Off Isloation                   | DC                            | -60                | -90                |                    | dBc   |  |

| I <sub>CC</sub> | Positive Supply Current            | R <sub>L</sub> = ∞            |                    | 54                 | 66                 | mA    |  |

| I <sub>EE</sub> | Negative Supply Current            | R <sub>L</sub> = ∞            |                    | 50                 | 62                 | mA    |  |

|                 | Tri State Supply Current           | RST Pin > 2.0V                |                    | 14                 | 17                 | mA    |  |

| Miscellane      | ous Performance                    |                               |                    |                    |                    |       |  |

| R <sub>IN</sub> | Input Resistance                   | Non-Inverting                 |                    | 100                |                    | kΩ    |  |

| C <sub>IN</sub> | Input Capacitance                  | Non-Inverting                 |                    | 1                  |                    | pF    |  |

| R <sub>O</sub>  | Output Resistance Enabled          | Closed Loop, Enabled          |                    | 300                |                    | mΩ    |  |

| R <sub>O</sub>  | Output Resistance Disabled         | LMH6580, Resistance to Ground |                    | 50                 |                    | kΩ    |  |

|                 |                                    | LMH6581, Resistance to Ground | 1100               | 1300               | 1500               | K12   |  |

| CMVR            | Input Common Mode Voltage<br>Range |                               |                    | ±3.0               |                    | V     |  |

| I <sub>O</sub>  | Output Current                     | Sourcing, $V_0 = 0 V$         | ±60                | ±70                |                    | mA    |  |

| Digital Co      | ntrol                              |                               |                    |                    |                    |       |  |

| VIH             | Input Voltage High                 |                               | 2.0                |                    |                    | V     |  |

| VIL             | Input Voltage Low                  |                               |                    |                    | 0.8                | V     |  |

| V <sub>OH</sub> | Output Voltage High                |                               |                    | >2.4               |                    | V     |  |

| V <sub>OL</sub> | Output Voltage Low                 |                               |                    | <0.4               |                    | V     |  |

|                 | Switching Time                     |                               |                    | 15                 |                    | ns    |  |

| T <sub>S</sub>  | Setup Time                         |                               |                    | 5                  |                    | ns    |  |

| Т <sub>Н</sub>  | Hold Time                          |                               |                    | 5                  |                    | ns    |  |

Copyright © 2007–2013, Texas Instruments Incorporated

SNOSAY4C -AUGUST 2007-REVISED MAY 2013

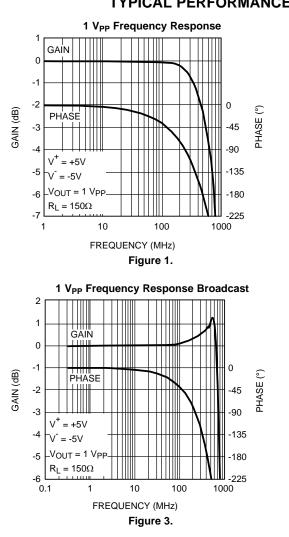

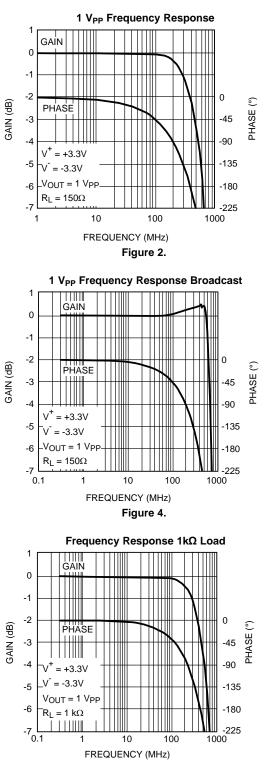

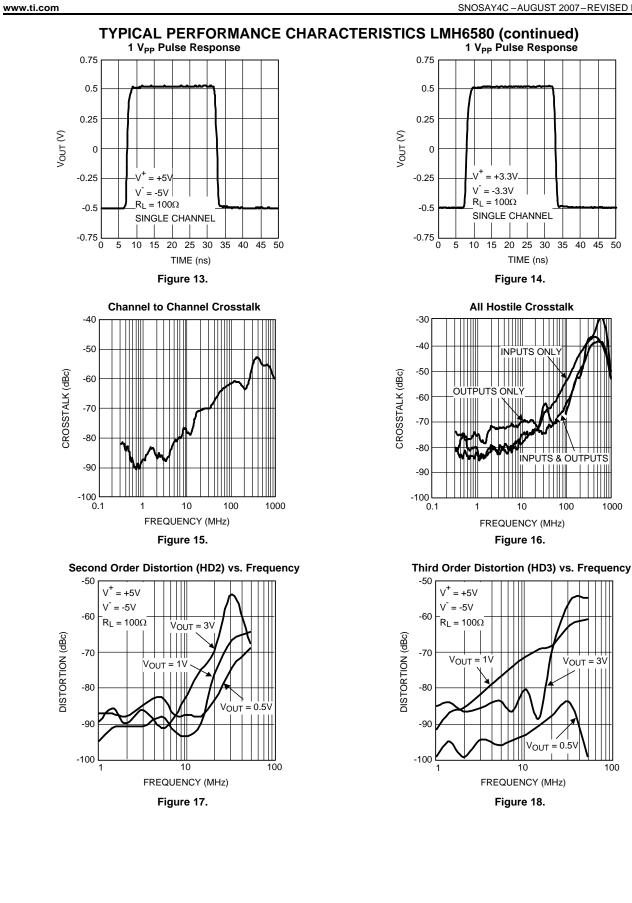

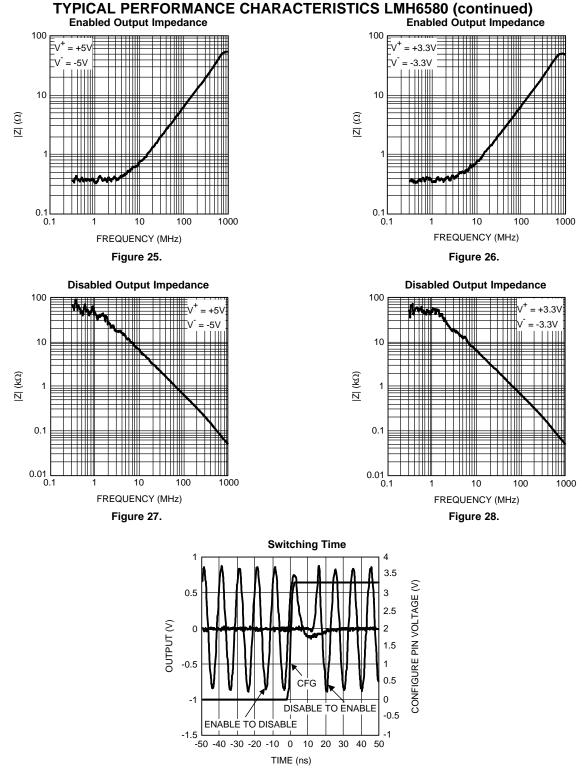

TYPICAL PERFORMANCE CHARACTERISTICS LMH6580

Figure 6.

#### SNOSAY4C-AUGUST 2007-REVISED MAY 2013

8

Copyright © 2007-2013, Texas Instruments Incorporated

#### SNOSAY4C-AUGUST 2007-REVISED MAY 2013

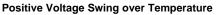

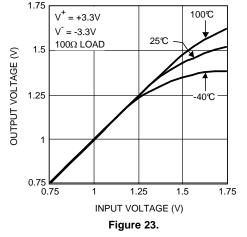

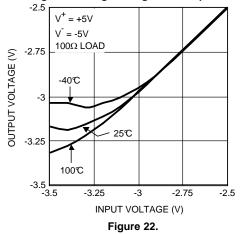

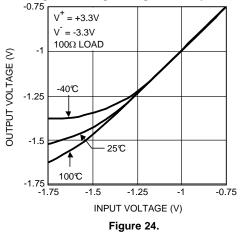

Figure 19.

Negative Voltage Swing over Temperature

**Negative Voltage Swing over Temperature**

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

#### SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

www.ti.com

Copyright © 2007-2013, Texas Instruments Incorporated

#### SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

Copyright © 2007–2013, Texas Instruments Incorporated

### **APPLICATION INFORMATION**

#### INTRODUCTION

The LMH6580/LMH6581 are high speed, fully buffered, non- blocking, analog crosspoint switches. Having fully buffered inputs allows the LMH6580/LMH6581 to accept signals from low or high impedance sources without the worry of loading the signal source. The fully buffered outputs will drive  $75\Omega$  or  $50\Omega$  back terminated transmission lines with no external components other than the termination resistor. When disabled, the outputs are in a high impedance state. The LMH6580/LMH6581 can have any input connected to any (or all) output(s). Conversely, a given output can have only one associated input.

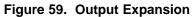

#### INPUT AND OUTPUT EXPANSION

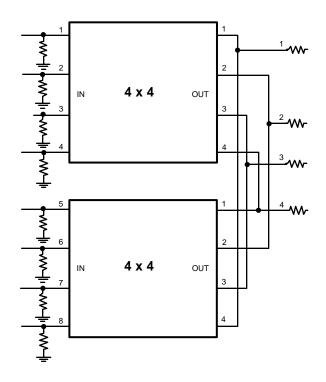

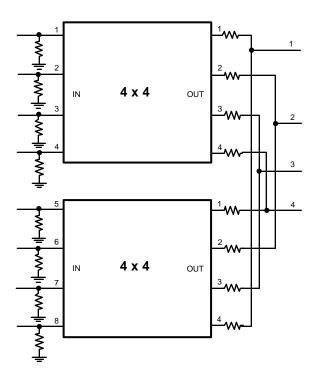

The LMH6580/LMH6581 have high impedance inactive states for both inputs and outputs allowing maximum flexibility for crosspoint expansion. In addition the LMH6580/LMH6581 employ diagonal symmetry in pin assignments. The diagonal symmetry makes it easy to use direct pin to pin vias when the parts are mounted on opposite sides of a board. As an example two LMH6580/LMH6581 chips can be combined on one board to form either an 8 x 8 crosspoint or a 16 x 4 crosspoint. To make an 8 x 8 crosspoint all 8 input pins would be tied together (Input 0 on side 1 to input 7 on side 2 and so on) while the 4 output pins on each chip would be left separate. To make the 16 x 4 crosspoint, the 4 outputs would be tied together while all 16 inputs would remain independent. In the 16 x 4 configuration it is important not to have 2 connected outputs active at the same time. With the 8 x 8 configuration, on the other hand, having two connected inputs active is a valid state. Crosspoint expansion as detailed above has the advantage that the signal will go through only one crosspoint. Expansion methods that have cascaded stages will suffer bandwidth loss far greater than the small loading effect of parallel expansion.

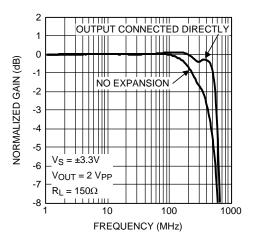

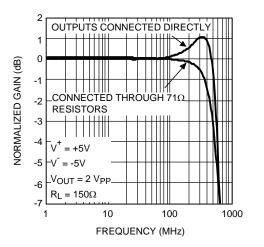

Output expansion as shown in Figure 59 is very straight forward. Connecting the inputs of two crosspoint switches has a very minor impact on performance. Input expansion requires more planning. Input expansion, as show in Figure 60 and Figure 61 gives the option of two ways to connect the outputs of the crosspoint switches. In Figure 60 the crosspoint switch outputs are connected directly together and share one termination resistor. This is the easiest configuration to implement and has only one drawback. Because the disabled output of the unused crosspoint (only one output can be active at a time) has a small amount of capacitance, the frequency response of the active crosspoint will show peaking. This is illustrated in Figure 62 and Figure 63. In most cases this small amount of peaking is not a problem.

As illustrated in Figure 61 each crosspoint output can be given its own termination resistor. This results in a frequency response nearly identical to the non expansion case. There is one drawback for the gain of 2 crosspoint, and that is gain error. With a 75 $\Omega$  termination resistor the 1250 $\Omega$  resistance of the disabled crosspoint output will cause a gain error. In order to counter act this the termination resistors of both crosspoints should be adjusted to approximately 80 $\Omega$ . This will provide very good matching, but the gain accuracy of the system will now be dependent on the process variations of the crosspoint resistors which have a variability of approximately  $\pm 20\%$ .

Figure 60. Input Expansion with Shared Termination Resistors

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

Figure 61. Input Expansion with Separate Termination Resistors

Figure 62. Input Expansion Frequency Response

SNOSAY4C-AUGUST 2007-REVISED MAY 2013

Figure 63. Input Expansion Frequency Response

### DRIVING CAPACITIVE LOADS

Capacitive output loading applications will benefit from the use of a series output resistor  $R_{OUT}$ . Capacitive loads of 5 pF to 120 pF are the most critical, causing ringing, frequency response peaking and possible oscillation. Since most capacitive loading is due to undesired parasitic capacitances the values of the capacitive loading will not usually be known exactly. It is best to start with a conservative value of  $R_{OUT}$  and decrease the value until the bandwidth shows slight peaking. At this point the value of the isloation resistor will be determined by whether flat frequency response or maximum bandwidth is the desired goal. Smaller values of  $R_{OUT}$  will produce some peaking, but maximum bandwidth. Larger resistor values will decrease bandwidth and suppress peaking.

As starting values, a capacitive load of 5 pF should have around 75  $\Omega$  of isolation resistance. A value of 120 pF would require around 12 $\Omega$ . When driving transmission lines, the output termination resistor is normally sufficient.

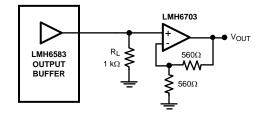

#### USING OUTPUT BUFFERING TO ENHANCE BANDWIDTH AND INCREASE REBIABILITY

The LMH6580/LMH6581 crosspoint switch can offer enhanced bandwidth and reliability with the use of external buffers on the outputs. The bandwidth is increased by unloading the outputs and driving the high impedance of an external buffer. See the Frequency Response 1 k $\Omega$  Load curve in Typical Performance section for an example of bandwidth achieved with less loading on the outputs. For this technique to provide maximum benefit a very high speed amplifier such as the LMH6703 should be used. As shown in Figure 64 the resistor R<sub>L</sub> is placed between the crosspoint output and the buffer amplifier. This resistor will provide a load for the crosspoint output buffer and reduce peaking caused by the buffer input capacitance. A recommended value for R<sub>L</sub> is 500 $\Omega$  to 1000 $\Omega$ . Higher values of R<sub>L</sub> will give higher bandwidth, but also higher peaking. The optimum value of R<sub>L</sub> will depend greatly on board layout and the input capacitance of the buffer amplifier.

Besides offering enhanced bandwidth performance using an external buffer provides greater system reliability. The first advantage is to reduce thermal loading on the crosspoint switch. This reduced die temperature will increase the life of the crosspoint. The second advantage is enhanced ESD reliability. It is very difficult to build high speed devices that can withstand all possible ESD events. With external buffers the crosspoint switch is isolated from ESD events on the external system connectors.

Figure 64. Buffered Output

#### CROSSTALK

www.ti.com

When designing a large system such as a video router crosstalk can be a very serious problem. Extensive testing in our lab has shown that most crosstalk is related to board layout rather than occurring in the crosspoint switch. There are many ways to reduce board related crosstalk. Using controlled impedance lines is an important step. Using well decoupled power and ground planes will help as well. When crosstalk does occur within the crosspoint switch itself it is often due to signals coupling into the power supply pins. Using appropriate supply bypassing will help to reduce this mode of coupling. Another suggestion is to place as much grounded copper as possible between input and output signal traces. Care must be taken, though, not to influence the signal trace impedances by placing shielding copper too closely. One other caveat to consider is that as shielding materials come closer to the signal trace the trace needs to be smaller to keep the impedance from falling too low. Using thin signal traces will result in unacceptable losses due to trace resistance. This effect becomes even more pronounced at higher frequencies due to the skin effect. The skin effect reduces the effective thickness of the trace as frequency increases. Resistive losses make crosstalk worse because as the desired signal is attenuated with higher frequencies crosstalk increases at higher frequencies.

#### DIGITAL CONTROL

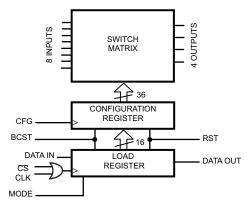

Figure 65. Block Diagram

| Pin Name | Level Sensitive | Edge Triggered | Triggered by     |

|----------|-----------------|----------------|------------------|

| CLK      | Yes             |                |                  |

| CS       |                 | Yes            | CLK rising edge  |

| DATA IN  |                 | Yes            | CLK falling edge |

| DATA OUT |                 | Yes            | CLK rising edge  |

| CFG      | Yes             |                |                  |

| MODE     | Yes             |                |                  |

| RST      | Yes             |                |                  |

| BCST     | Yes             |                |                  |

Table 1. Logic Pins

There are two modes for programing the LMH6580/LMH6581, Serial Mode and Addressed Mode. The LMH6580/LMH6581 have internal control registers that store the programming states of the crosspoint switch. The logic is two staged to allow for maximum programming flexibility. The first stage of the control logic is tied directly to the crosspoint switching matrix. This logic consists of one register for each output that stores the on/off state and the address of which input to connect to. These registers are not directly accessible to the user. The second level of logic is another bank of registers identical to the first, but set up as shift registers. These registers are accessed by the user via the serial input bus.

The LMH6580/LMH6581 is programmed via a serial input bus with the support of four other digital control pins. The Serial bus consists of a clock pin (CLK), a serial data in pin (DIN), and a serial data out pin ( $D_{OUT}$ ). The serial bus is gated by a chip select pin (CS). The chip select pin is active low. While the chip select pin is high all data on the serial input pin and clock pins is ignored. When the chip select pin is brought low the internal logic is set to begin receiving data by the first positive transition (0 to 1) of the clock signal. The chip select pin must be

Copyright © 2007-2013, Texas Instruments Incorporated

brought low at least 5 ns before the first rising edge of the clock signal. The first data bit is clocked in on the next negative transition (1 to 0) of the clock signal. All input data is read from the bus on the negative edge of the clock signal. Once the last valid data has been clocked in, either the chip select pin must go high or, the clock signal must stop. Otherwise invalid data will be clocked into the chip. The data clocked into the chip is not transferred to the crosspoint matrix until the CFG pin is pulsed high. This is the case regardless of the state of the MODE pin. The CFG pin is not dependent on the state of the Chip select pin. If no new data is clocked into the chip subsequent pulses on the CFG pin will have no effect on device operation.

The programming format of the incoming serial data is selected by the MODE pin. When the MODE pin is HIGH the crosspoint can be programmed one output at a time by entering a string of data that contains the address of the output that is going to be changed (Addressed Mode). When the mode pin is LOW the crosspoint is in Serial Mode. In this mode the crosspoint accepts a 16 bit array of data that programs all of the outputs. In both modes the data fed into the chip does not change the chip operation until the Configure pin is pulsed high. The configure and mode pins are independent of the chip select pin.

#### THREE WIRE VS. FOUR WIRE CONTROL

There are two ways to connect the serial data pins. The first way is to control all four pins separately, and the second option is to connect the CFG and the CS pins together for a 3 wire interface. The benefit of the 4-wire interface is that the chip can be configured independently using the CS pin. This would be an advantage in a system with multiple crosspoint chips where all of them could be programmed ahead of time and then configured simultaneously. The 4-wire solution is also helpful in a system that has a free running clock on the CLK pin. In this case, the CS pin needs to be brought high after the last valid data bit to prevent invalid data from being clocked into the chip.

The 3-wire option provides the advantage of one less pin to control at the expense of having less flexibility with the configure pin. One way around this loss of flexibility would be if the clock signal is generated by an FPGA or microcontroller where the clock signal can be stopped after the data is clocked in. In this case the Chip select function is provided by the presence or absence of the clock signal.

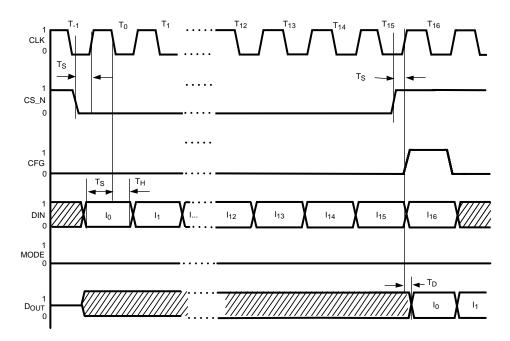

#### SERIAL PROGRAMMING MODE

Serial programming mode is the mode selected by bringing the MODE pin low. In this mode a stream of 16-bits programs all four outputs of the crosspoint. The data is fed to the chip as shown in Table 2 and Table 3 (two tables are required to show the entire data frame). The table is arranged such that the first bit clocked into the crosspoint register is labeled bit number 0. The register labeled Load Register in Figure 65 is a shift register. If the chip select pin is left low after the valid data is shifted into the chip and if the clock signal keeps running then additional data will be shifted into the register, and the desired data will be shifted out.

Also illustrated is the timing relationships for the digital pins in Figure 66. It is important to note that all the pin timing relationships are important, not just the data and clock pins. One example is that the Chip Select pin (CS) must transition low before the first rising edge of the clock signal. This allows the internal timing circuits to synchronize to allow data to be accepted on the next falling edge. The chip select pin must then transition high after the final data bit has been clocked in and before another clock signal positive edge occurs to prevent invalid data from being clocked into the chip. Another way to accomplish the same thing is to strobe the clock pin with only the desired number of pulses starting and ending with clock in the low condition. The configure (CFG) pin timing is not so critical, but it does need to be kept low until all data has been shifted into the crosspoint registers.

Copyright © 2007–2013, Texas Instruments Incorporated

FXAS

**NSTRUMENTS**

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

Figure 66. Timing Diagram for Serial Mode

| Table 2. Serial Mode Data Frame (First Two Words) |

|---------------------------------------------------|

|---------------------------------------------------|

| Output 0             |   |     |               | Output 1 |     |        |         |

|----------------------|---|-----|---------------|----------|-----|--------|---------|

| Input Address On = 0 |   |     | Input Address |          |     | On = 0 |         |

| LSB                  |   | MSB | Off = 1       | LSB      | LSB |        | Off = 1 |

| 0                    | 1 | 2   | 3             | 4        | 5   | 6      | 7       |

(1) Off = TRI-STATE, Bit 0 is first bit clocked into device.

#### Table 3. Serial Mode Data Frame (Continued)

| Output 2             |   |     |               | Output 3 |    |        |         |

|----------------------|---|-----|---------------|----------|----|--------|---------|

| Input Address On = 0 |   |     | Input Address |          |    | On = 0 |         |

| LSB                  |   | MSB | Off = 1       | LSB      |    | MSB    | Off = 1 |

| 8                    | 9 | 10  | 11            | 12       | 13 | 14     | 15      |

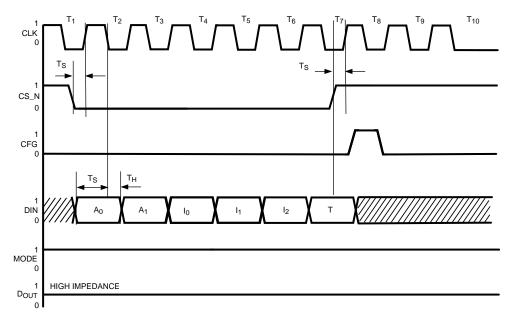

#### ADDRESSED PROGRAMMING MODE

Addressed programming mode makes it possible to change only one output register at a time. To utilize this mode the mode pin must be High. All other pins function the same as in serial programming mode except that the word clocked in is 5 bits and is directed only at the output specified. In addressed mode the data format is shown below in Table 4.

Also illustrated is the timing relationships for the digital pins in Figure 67. It is important to note that all the pin timing relationships are important, not just the data and clock pins. One example is that the Chip Select pin (CS) must transition low before the first rising edge of the clock signal. This allows the internal timing circuits to synchronize to allow data to be accepted on the next falling edge. The chip select pin must then transition high after the final data bit has been clocked in and before another clock signal positive edge occurs to prevent invalid data from being clocked into the chip. Also, in addressed mode is it necessary for the clock signal to make a low to high transition after the chip select pin has been brought high. If there is not a low to high transition of the clock after the chip select pin goes high subsequent data wil not be loaded into the chip properly. The configure (CFG) pin timing is not critical, but it does need to be kept low until all data has been shifted into the crosspoint registers.

Copyright © 2007-2013, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

Figure 67. Timing Diagram for Addressed Mode

| Output Address |     | Input Address |   |     | TRI-STATE               |

|----------------|-----|---------------|---|-----|-------------------------|

| LSB            | MSB | LSB           |   | MSB | 1 = TRI-STATE<br>0 = On |

| 0              | 1   | 2             | 3 | 4   | 5                       |

Table 4. Addressed Mode Word Format<sup>(1)</sup>

(1) Bit 0 is first bit clocked into device.

#### DAISY CHAIN OPTION IN SERIAL MODE

The LMH6580/LMH6581 supports daisy chaining of the serial data stream between multiple chips. This feature is available only in the Serial Programming Mode. To use this feature serial data is clocked into the first chip  $D_{IN}$  pin, and the next chip  $D_{IN}$  pin is connected to the  $D_{OUT}$  pin of the first chip. Both chips may share a chip select signal, or the second chip can be enabled separately. When the chip select pin goes low on both chips a double length word is clocked into the first chip. As the first word is clocking into the first chip the second chip is receiving the data that was originally in the shift register of the first chip (invalid data). When a full 16 bits have been clocked into the first chip the next clock cycle begins moving the first frame of the new configuration data into the second chip. With a full 32 clock cycles both chips have valid data and the chip select pin of both chips should be brought high to prevent the data from overshooting. A configure pulse will activate the new configuration on both chips simultaneously, or each chip can be configured separately. The mode, chip select, configure and clock pins of both chips can be tied together and driven from the same sources.

#### SPECIAL CONTROL PINS

The LMH6580/LMH6581 have two special control pins that function independent of the serial control bus. One of these pins is the reset (RST) pin. The RST pin is active high meaning that at logic 1 level the chip is configured with all outputs disabled and in a high impedance state. The RST pin programs all the registers with input address 0 and all the outputs are turned off. In this configuration the device draws only 11mA. The RST pin can be used as a shutdown function to reduce power consumption. The other special control pin is the broadcast (BCST) pin. The BCST pin is also active high and sets all the outputs to the on state connected to input 0. This is sometimes referred to as broadcast mode, where input 0 is broadcast to all eight outputs.

LMH6580, LMH6581

SNOSAY4C - AUGUST 2007 - REVISED MAY 2013

www.ti.com

#### THERMAL MANAGEMENT

The LMH6580/LMH6581 are high performance devices that produce a significant amount of heat. With ±5V supplies, the LMH6580/LMH6581 will dissipate approximately 0.5 W of idling power with all outputs enabled. Idling power is calculated based on the typical supply current of 50 mA and a 10V supply voltage. This power dissipation will vary within the range of 0.4 W to 0.6 W due to process variations. In addition, each equivalent video load (150 $\Omega$ ) connected to the outputs should be budgeted 30 mW of power. For a typical application with one video load for each output this would be a total power of 0.62 W. With a  $\theta_{JA}$  of 44 °C/W this will result in the silicon being 27°C over the ambient temperature. A more aggressive application would be two video loads per output which would result in 0.74 W of power dissipation. This would result in a 33°C temperature rise. For heavier loading, the TQFP package thermal performance can be significantly enhanced with an external heat sink and by providing for moving air ventilation. Also, be sure to calculate the increase in ambient temperature from all devices operating in the system case. Because of the high power output of this device, thermal management should be considered very early in the design process. Generous passive venting and vertical board orientation may avoid the need for fan cooling or heat sinks. Also, the LMH6580/LMH6581 can be operated with a ±3.3V power supply. This will cut power dissipation substantially while only reducing bandwidth by about 10% (2 V<sub>PP</sub> output). The LMH6580/LMH6581 are fully characterized and factory tested at the ±3.3V power supply condition for applications where reduced power is desired.

#### PRINTED CIRCUIT LAYOUT

Generally, a good high frequency layout will keep power supply and ground traces away from the input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillations (see Application Note OA-15 for more information). If digital control lines must cross analog signal lines (particularly inputs) it is best if they cross perpendicularly. Texas Instruments suggests the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization:

Device LMH6580 Package 48–Pin Evaluation Board Part Number LMH730164EF

26

## **REVISION HISTORY**

| Cł | Changes from Revision B (April 2013) to Revision C Pa |    |  |  |  |  |  |

|----|-------------------------------------------------------|----|--|--|--|--|--|

| •  | Changed layout of National Data Sheet to TI format    | 25 |  |  |  |  |  |

Copyright © 2007–2013, Texas Instruments Incorporated

www.ti.com

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LMH6580VS/NOPB   | ACTIVE        | TQFP         | PFB                | 48   | 250            | RoHS & Green    | SN                                   | Level-3-260C-168 HR  | -40 to 85    | LMH6580<br>VS           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### Texas Instruments

www.ti.com

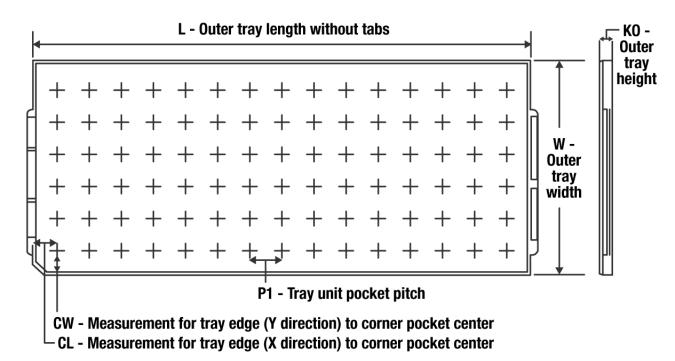

#### TRAY

5-Jan-2022

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device         | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | K0<br>(µm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|----------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| LMH6580VS/NOPB | PFB             | TQFP            | 48   | 250 | 10 x 25              | 150                        | 315    | 135.9     | 7620       | 12.2       | 11.1       | 11.25      |

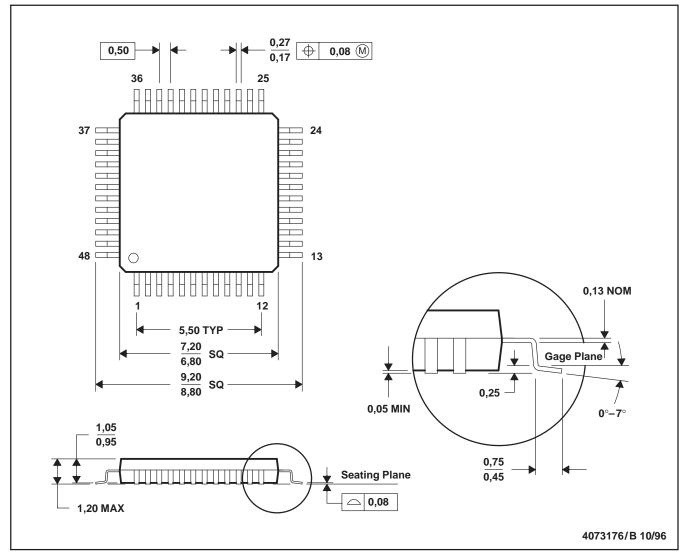

## **MECHANICAL DATA**

MTQF019A - JANUARY 1995 - REVISED JANUARY 1998

#### PFB (S-PQFP-G48)

PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

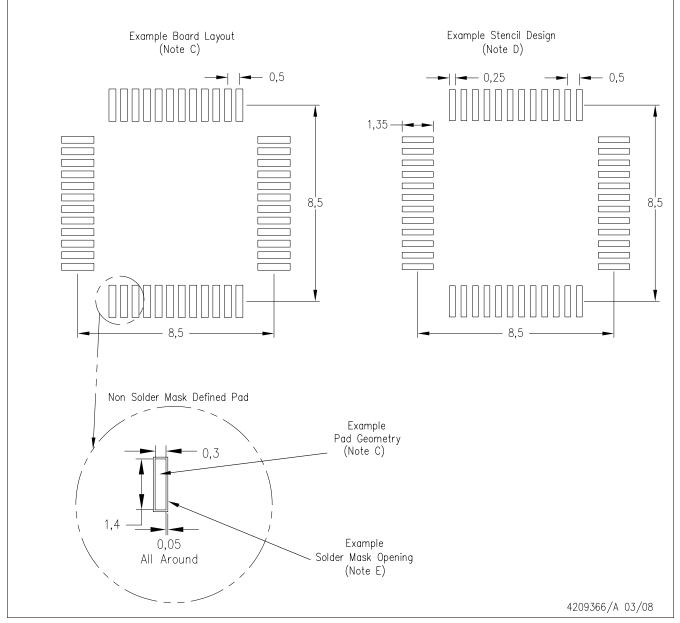

PFB (S-PQFP-G48)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated