ZHCSCB2A - JANUARY 2014-REVISED MARCH 2014

LM3699

# LM3699 高效白光发光二极管 (LED) 驱动器

## 特性

- 驱动并联高压 LED 灯串用于显示或键区照明

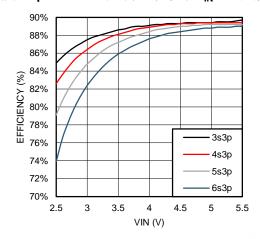

- 升压转换器效率高达 90%

- 四个用户可选满量程电流设置 (20.2mA, 18.6mA, 17.0mA, 15.4mA)

- 快速调光使能端子 (ILOW)

- 简单脉宽调制 (PWM) 占空比控制

- 24V 过压保护阀值

- 固定 1MHz 开关频率

- 集成型 1A/40V 金属氧化物半导体场效应晶体管 (MOSFET)

- 三个灌电流端子

- 自适应升压输出至 LED 电压

- 热关断保护

- 29mm<sup>2</sup> 总体解决方案尺寸

## 应用范围

- 用于智能手机照明的电源

- 显示或键区照明

## 3 说明

LM3699 是一款三灯串, 高效、由 PWM 控制的电源, 用于智能手机的显示背光或键区 LED。 具有集成 1A,40V MOSFET 的高压电感升压转换器为三个串联 LED 灯串供电。 升压输出自动调节到 LED 正向电 压,以最大限度地减少净空电压并有效地改进 LED 效 率。

ILOW 端子提供一个在照相机闪光灯运行时快速减少 LED 亮度的方法。

LM3699 具有集成过压、过流和过热保护。

此器件在 2.7V 至 5.5V 的输入电压范围和 -40℃ 至 85°C 的温度范围内运行。

器件信息

| HH 11 1H 76. |                              |                 |  |  |  |  |

|--------------|------------------------------|-----------------|--|--|--|--|

| 订货编号         | 封装                           | 封装尺寸            |  |  |  |  |

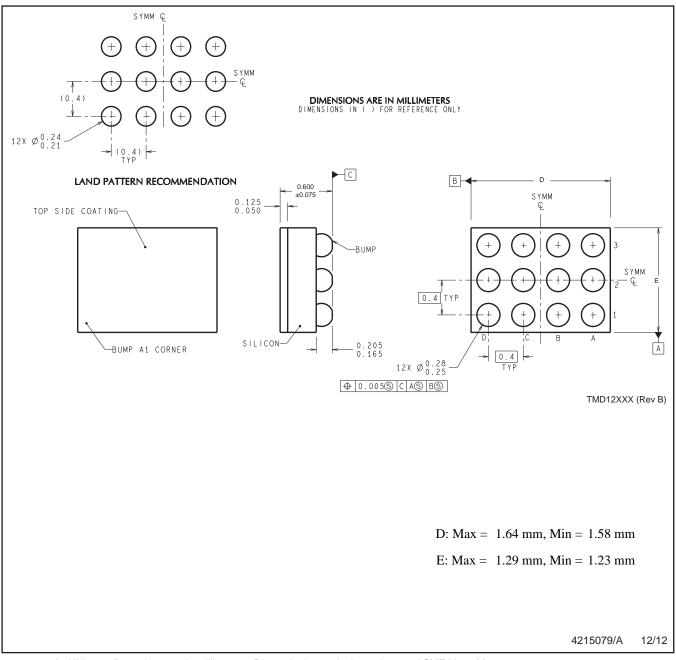

| LM3699YFQ    | 芯片级球状引脚栅格<br>阵列 (DSBGA) (12) | 1.64mm x 1.29mm |  |  |  |  |

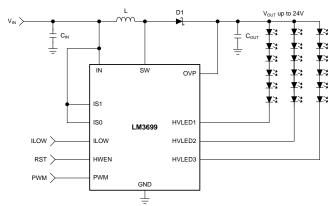

## 简化电路原理图

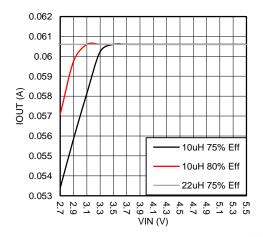

## 在使用 10µH 电感器时,升压效率与 V<sub>IN</sub> 之间的关系

|   |                                      | 目录 |    |                                      |    |

|---|--------------------------------------|----|----|--------------------------------------|----|

| 1 | 特性                                   | 1  |    | 7.3 Feature Description              | 8  |

| 2 | 应用范围                                 | 1  |    | 7.4 Device Functional Modes          | 9  |

| 3 | 说明                                   | 1  | 8  | Application and Implementation       | 10 |

| 4 | 修订历史记录                               |    |    | 8.1 Application Information          | 10 |

| 5 | Terminal Configuration and Functions |    |    | 8.2 Typical Application              | 10 |

| 6 | Specifications                       |    | 9  | Power Supply Recommendations         | 15 |

| • | 6.1 Absolute Maximum Ratings         |    | 10 | Layout                               | 16 |

|   | 6.2 Handling Ratings                 |    |    | 10.1 Layout Guidelines               | 16 |

|   | 6.3 Recommended Operating Conditions |    |    | 10.2 Layout Example                  | 18 |

|   | 6.4 Thermal Information              |    | 11 | 器件和文档支持                              | 19 |

|   | 6.5 Electrical Characteristics       | 5  |    | 11.1 器件支持                            | 19 |

|   | 6.6 Typical Characteristics          | 7  |    | 11.2 Trademarks                      | 19 |

| 7 | Detailed Description                 |    |    | 11.3 Electrostatic Discharge Caution | 19 |

|   | 7.1 Overview                         |    |    | 11.4 Glossary                        | 19 |

|   | 7.2 Functional Block Diagram         |    | 12 | 机械封装和可订购信息                           | 19 |

# 4 修订历史记录

| CI | hanges from Original (January 2014) to Revision A | Pag |

|----|---------------------------------------------------|-----|

| •  | 已更改 更改为全新的 TI 数据表格式:添加处理额定值表以及器件和文档支持部分           |     |

| •  | Added new scope shot                              | 1   |

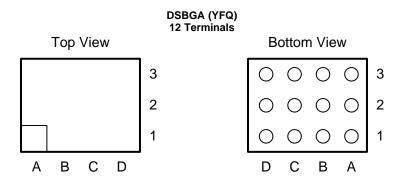

# 5 Terminal Configuration and Functions

### **Terminal Functions**

| TE     | RMINAL | DESCRIPTION                                                                                                                                                                                              |  |  |  |  |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NUMBER | NAME   | DESCRIPTION                                                                                                                                                                                              |  |  |  |  |

| A1     | PWM    | PWM brightness control input. PWM is a high-impedance input and cannot be left floating.                                                                                                                 |  |  |  |  |

| A2     | IS0    | Current select input 1. This is a high-impedance input and cannot be left floating. ISO can be connected to IN or GND.                                                                                   |  |  |  |  |

| А3     | HWEN   | Hardware enable input. Drive this terminal high to enable the device. Drive this terminal low to force the device into a low-power shutdown. HWEN is a high-impedance input and cannot be left floating. |  |  |  |  |

| B1     | HVLED1 | Input terminal to high-voltage current sink 1 (24 V max). The boost converter regulates the minimum of HVLED1, HVLED2, and HVLED3 to $V_{HR}$ .                                                          |  |  |  |  |

| B2     | IS1    | Current select input 2. This is a high-impedance input and cannot be left floating. IS1 can be connected to IN or GND.                                                                                   |  |  |  |  |

| В3     | IN     | Input voltage connection. Bypass IN to GND with a minimum 2.2-µF ceramic capacitor.                                                                                                                      |  |  |  |  |

| C1     | HVLED2 | Input terminal to high-voltage current sink 2 (24 V max). The boost converter regulates the minimum of HVLED1, HVLED2, and HVLED3 to $V_{HR}$ .                                                          |  |  |  |  |

| C2     | ILOW   | Low level current enable. Drive this terminal high to reduce LED current by approximately 95%. ILOW is a high-impedance input and cannot be left floating. If not used connect to GND.                   |  |  |  |  |

| C3     | GND    | Ground.                                                                                                                                                                                                  |  |  |  |  |

| D1     | HVLED3 | Input terminal to high-voltage current sink 3 (24 V max). The boost converter regulates the minimum of HVLED1, HVLED2, and HVLED3 to $V_{HR}$ .                                                          |  |  |  |  |

| D2     | OVP    | Overvoltage sense input. Connect OVP to the positive terminal of the inductive boost output capacitor $(C_{\text{OUT}})$ .                                                                               |  |  |  |  |

| D3     | SW     | Drain connection for the internal NFET. Connect SW to the junction of the inductor and the Schottky diode anode.                                                                                         |  |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                                                                             | MIN        | MAX       | UNIT |

|-------------------------------------------------------------------------------------------------------------|------------|-----------|------|

| V <sub>IN</sub> to GND                                                                                      | -0.3V      | 6         |      |

| V <sub>SW</sub> , V <sub>OVP</sub> , V <sub>HVLED1</sub> , V <sub>HVLED2</sub> , V <sub>HVLED3</sub> to GND | -0.3V      | 45        | V    |

| V <sub>IS1</sub> , V <sub>IS0</sub> , V <sub>ILOW</sub> , V <sub>PWM</sub> to GND                           | -0.3V      | 6         | V    |

| V <sub>HWEN</sub> to GND                                                                                    | -0.3V      | 6         |      |

| Continuous power dissipation                                                                                | Internally | / Limited |      |

| Maximum lead temperature (soldering)                                                                        | 260 (peak) |           | °C   |

| Junction temperature (T <sub>J-MAX</sub> )                                                                  |            | 150       |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2) All voltages are with respect to the potential at the GND terminal.

## 6.2 Handling Ratings

|                            |                                           | MIN | MAX  | UNIT |

|----------------------------|-------------------------------------------|-----|------|------|

|                            | Storage temperature range                 | -65 | 150  | °C   |

| ESD Ratings <sup>(1)</sup> | Human body model (HBM) <sup>(2)</sup>     |     | 2.0  | kV   |

| ESD Ratings (*)            | Charged device model (CDM) <sup>(3)</sup> |     | 1500 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                                                             | MIN | MAX | UNIT       |

|-------------------------------------------------------------------------------------------------------------|-----|-----|------------|

| V <sub>IN</sub> to GND                                                                                      | 2.7 | 5.5 | \ <i>/</i> |

| V <sub>SW</sub> , V <sub>OVP</sub> , V <sub>HVLED1</sub> , V <sub>VHLED2</sub> , V <sub>VHLED3</sub> to GND | 0   | 24  | V          |

| Junction temperature (T <sub>J</sub> ) <sup>(1)(2)</sup>                                                    | -40 | 125 | °C         |

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>= 140°C (typ) and disengages at T<sub>J</sub> = 125°C (typ).

#### 6.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>          | DSBGA<br>(12 TERMINALS) | UNIT |

|-----------------|----------------------------------------|-------------------------|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 55                      | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

## 6.5 Electrical Characteristics

Limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ) and  $V_{IN} = 3.6\text{V}$ , unless otherwise specified. (1)(2)

| SYMBOL                    | PARAMETER                                                                                 | TEST CONDITIONS                                                                                                                                      | MIN   | TYP  | MAX   | UNIT |

|---------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| General                   |                                                                                           |                                                                                                                                                      |       |      |       |      |

|                           |                                                                                           | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V, HWEN = GND                                                                                                          |       |      | 3.0   |      |

| I <sub>SHDN</sub>         | Shutdown current                                                                          | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ HWEN} = \text{GND},$<br>$\text{T}_{\text{A}} = 25^{\circ}\text{C}$                 |       | 1    |       | μΑ   |

| <b>T</b>                  | Thermal shutdown                                                                          |                                                                                                                                                      |       | 140  |       | °C   |

| T <sub>SD</sub>           | Hysteresis                                                                                |                                                                                                                                                      |       | 15   |       | 30   |

| Boost Conver              | rter                                                                                      |                                                                                                                                                      |       |      |       |      |

|                           |                                                                                           | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ ILOW} = \text{GND},$ $\text{ISO} = \text{IS1} = \text{VIN},$ PWM Duty Cycle = 100% | 18.38 |      | 22.02 |      |

|                           |                                                                                           | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ , ILOW = GND, IS0 = IS1 = VIN, PWM Duty Cycle = 100% $T_A = 25^{\circ}\text{C}$           |       | 20.2 |       |      |

|                           | Output current                                                                            | ILOW = GND, IS0 = IS1 = VIN,<br>PWM Duty Cycle = 100%<br>T <sub>A</sub> = 25°C                                                                       | 18.7  |      | 21.58 |      |

| I <sub>HVLED(1/2/3)</sub> | regulation (HVLED1,<br>HVLED2, HVLED3)                                                    | ILOW = GND, IS0 = IS1 = VIN,<br>PWM Duty Cycle = 100%,<br>T <sub>A</sub> = 25°C                                                                      |       | 20.2 |       | mA   |

|                           |                                                                                           | $3.0 \text{ V} \le \text{V}_{\text{IN}} \le 4.5 \text{ V}$ , ILOW = GND, IS0 = IS1 = VIN, PWM Duty Cycle = 100% $T_A = 25^{\circ}\text{C}$           | 18.63 |      | 21.58 |      |

|                           |                                                                                           | $3.0 \text{ V} \le \text{V}_{\text{IN}} \le 4.5 \text{ V}$ , ILOW = GND, IS0 = IS1 = VIN, PWM Duty Cycle = 100% $T_A = 25^{\circ}\text{C}$           |       | 20.2 |       |      |

|                           | HVLED matching<br>(HVLED1 to HVLED2<br>or HVLED2 to HVLED3<br>or HVLED1 to<br>HVLED3) (3) | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ , ILOW = GND, ISO = IS1 = VIN, PWM Duty Cycle = 100%                                      | -2.5% |      | 2.5%  |      |

| I <sub>MATCH_HV</sub>     |                                                                                           | ILOW = GND, IS0 = IS1 = VIN,<br>PWM Duty Cycle = 100%, T <sub>A</sub> =<br>25°C                                                                      | -2%   |      | 1.7%  |      |

|                           |                                                                                           | $3.0 \text{ V} \le \text{V}_{\text{IN}} \le 4.5 \text{ V}$ , ILOW = GND, IS0 = IS1 = VIN, PWM Duty Cycle = 100%                                      | -2.5% |      | 2.5%  |      |

| $V_{REG\_CS}$             | Regulated current sink headroom voltage                                                   | ILOW = GND, IS0 = IS1 = VIN,<br>PWM Duty Cycle = 100%,<br>T <sub>A</sub> = 25°C                                                                      |       | 400  |       |      |

|                           | Minimum current sink                                                                      | I <sub>LED</sub> = 95% of nominal, ILOW =<br>GND, IS0 = IS1 = VIN, PWM Duty<br>Cycle = 100%                                                          |       |      | 275   | mV   |

| V <sub>HR_MIN</sub>       | headroom voltage for<br>HVLED current sinks                                               | $I_{LED}$ = 95% of nominal, ILOW =<br>GND, IS0 = IS1 = VIN, PWM Duty<br>Cycle = 100%<br>$T_A$ = 25°C                                                 |       | 190  |       |      |

| R <sub>DSON</sub>         | NMOS switch on resistance                                                                 | I <sub>SW</sub> = 500 mA, T <sub>A</sub> = 25°C                                                                                                      |       | 0.3  |       | Ω    |

|                           | NMOS Switch Current                                                                       |                                                                                                                                                      | 880   |      | 1120  | m ^  |

| CL_BOOST                  | Limit                                                                                     | T <sub>A</sub> = 25°C                                                                                                                                |       | 1000 |       | mA   |

<sup>(1)</sup> All voltages are with respect to the potential at the GND terminal.

<sup>(2)</sup> Minimum (Min) and Maximum (Max) limits are verified by design, test, or statistical analysis. Typical (Typ) numbers are not verified, but do represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: V<sub>IN</sub> = 3.6 V and T<sub>A</sub> = 25°C.

do represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: V<sub>IN</sub> = 3.6 V and T<sub>A</sub> = 25°C.

(3) LED current sink matching in the high-voltage current sinks (HVLED1, HVLED2, and HVLED3) is given as the maximum matching value between any two current sinks, where the matching between any two high-voltage current sinks (X and Y) is given as (I<sub>HVLEDX</sub> (or I<sub>HVLEDY</sub>) - I<sub>AVE(X-Y)</sub>)/(I<sub>AVE(X-Y)</sub>) x 100.

## **Electrical Characteristics (continued)**

Limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{\text{A}} \le 85^{\circ}\text{C}$ ) and  $V_{\text{IN}} = 3.6\text{V}$ , unless otherwise specified. (1)(2)

| SYMBOL                                               | PARAMETER                        | TEST CONDITIONS                                             | MIN                      | TYP  | MAX      | UNIT |  |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------------|--------------------------|------|----------|------|--|

|                                                      | _                                | ON threshold, 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V               | 23                       |      | 25       |      |  |

| $V_{OVP}$                                            | Output overvoltage protection    | ON threshold, T <sub>A</sub> = 25°C                         |                          | 24   |          | V    |  |

|                                                      | protoction                       | Hysteresis, T <sub>A</sub> = 25°C                           |                          | 0.7  |          |      |  |

|                                                      | Curitabina fraguanay             | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 900                      |      | 1100     | kHz  |  |

| $f_{SW}$                                             | Switching frequency              | T <sub>A</sub> = 25°C                                       |                          | 1000 |          | KHZ  |  |

| D <sub>MAX</sub>                                     | Maximum duty cycle               | T <sub>A</sub> = 25°C                                       |                          | 94%  |          |      |  |

| HWEN Input                                           |                                  |                                                             |                          |      |          |      |  |

| V                                                    | Input logic low                  | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 0                        | 0    |          | V    |  |

| $V_{HWEN}$                                           | Input logic high                 | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | <sub>N</sub> ≤ 5.5 V 1.2 |      | $V_{IN}$ |      |  |

| PWM Input                                            |                                  |                                                             |                          |      |          |      |  |

| V <sub>PWM_L</sub>                                   | Input logic low                  | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 0 0.4                    |      | 0.4      |      |  |

| V <sub>PWM_H</sub>                                   | Input logic high                 | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 1.31                     |      | $V_{IN}$ | V    |  |

| t <sub>PWM</sub>                                     | Minimum PWM input pulse detected | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             |                          |      | 0.75     | μs   |  |

| IS1, IS0, ILOV                                       | V Inputs                         |                                                             |                          |      |          |      |  |

| $V_{IL}$                                             | Input logic low                  | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 0                        |      | 0.4      | V    |  |

| $V_{IH}$                                             | Input logic high                 | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                             | 1.29 V <sub>IN</sub>     |      | $V_{IN}$ | V    |  |

| Internal POR                                         | Threshold                        |                                                             |                          |      |          |      |  |

|                                                      | DOD react release                | V <sub>IN</sub> ramp time = 100 μs                          | 1.7 2.1                  |      | 2.1      |      |  |

| V <sub>POR</sub> POR reset release voltage threshold |                                  | V <sub>IN</sub> ramp time = 100 μs<br>T <sub>A</sub> = 25°C | 1.9                      |      |          | V    |  |

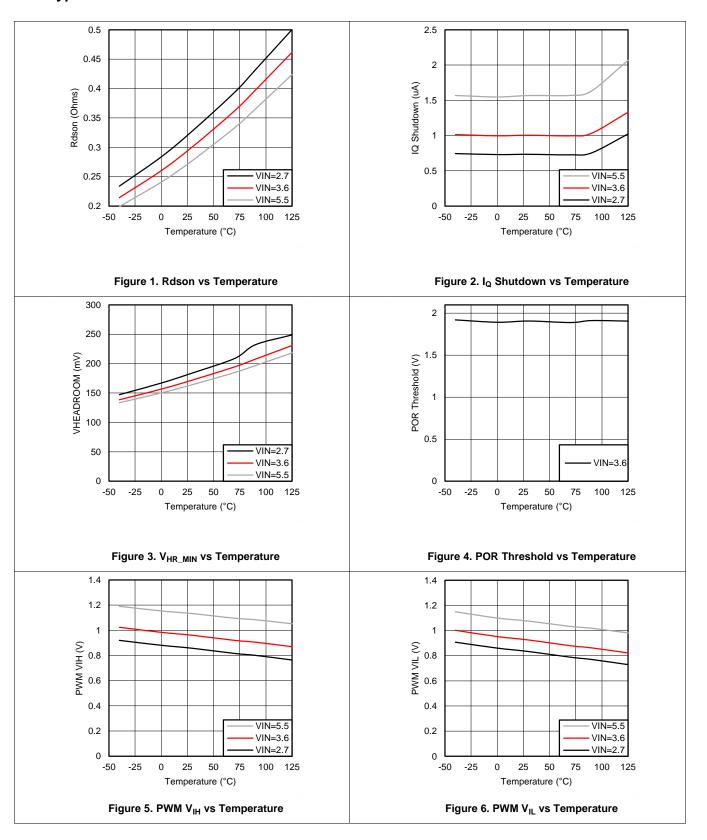

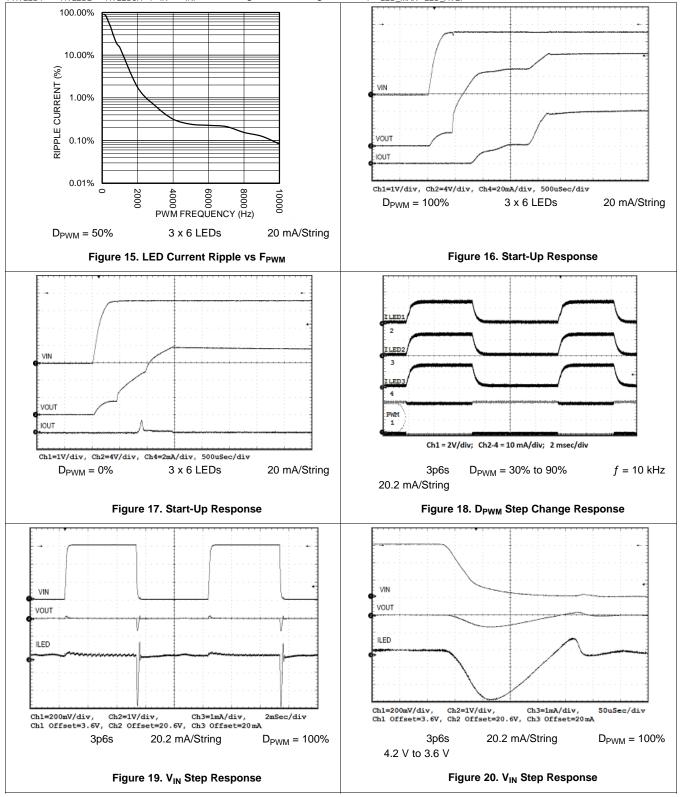

## 6.6 Typical Characteristics

## 7 Detailed Description

#### 7.1 Overview

The LM3699 provides power for three high-voltage LED strings. The high-voltage LED strings are powered from an integrated boost converter. The LED current is directly controlled by a Pulse Width Modulation (PWM) input.

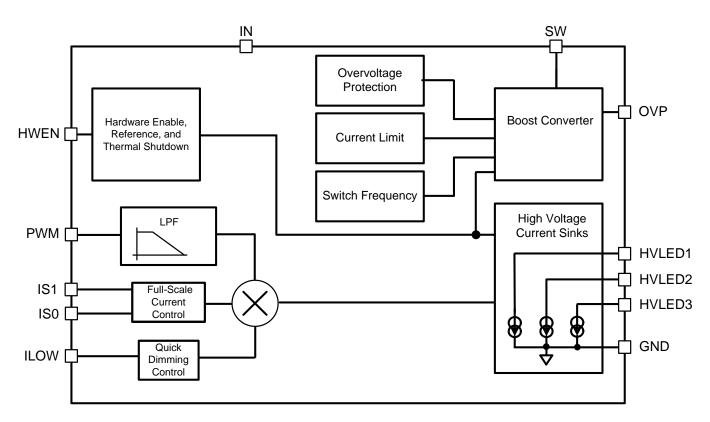

### 7.2 Functional Block Diagram

### 7.3 Feature Description

## 7.3.1 PWM Input

The active high PWM input is filtered by an internal low-pass filter, then converted to an analog control voltage to set the current level on the current sink outputs. The PWM input is high-impedance and cannot be left floating.

#### 7.3.1.1 PWM Input Frequency Range

The usable input frequency range for the PWM input is governed on the low end by the cutoff frequency of the internal low-pass filter (540 Hz, Q=0.33) and on the high end by the propagation delays through the internal logic. For frequencies below 2 kHz the current ripple begins to become a larger portion of the DC LED current. Additionally, at lower PWM frequencies the boost output voltage ripple increases, causing a non-linear response from the PWM duty cycle to the average LED current due to the response time of the boost. For the best response of current vs. duty cycle, the PWM input frequency should be kept between 2 kHz and 100 kHz.

#### 7.3.1.2 PWM Low Detect

The LM3699 incorporates a feature to detect when the PWM input duty cycle is near zero. This feature requires that the minimum PWM input pulse width be greater than  $t_{PWM}$  (see Electrical Characteristics ). A PWM input pulse width less than  $t_{PWM}$  can result in the current sink outputs turning on and off resulting in flicker on the LEDs.

## **Feature Description (continued)**

## 7.3.2 HWEN Input

HWEN is the global hardware enable to the LM3699 and must be driven high to enable the device. HWEN is a high-impedance input, so it cannot be left floating. When HWEN is driven low the LM3699 is placed in shutdown, and the boost converter and all the HVLED current sinks are turned off.

### 7.3.3 Current Select Inputs (IS1 And IS0)

The current select inputs IS1 and IS0 select the maximum full-scale current (ifs). These digital inputs are static and must not change state when HWEN  $> V_{IL}$ . IS1 and IS0 are high-impedance inputs so they cannot be left floating. The terminals IS1 and IS0 can be connected directly to IN or GND and do not require an external pullup/pulldown resistor. The full-scale current is set according to Table 1:

Table 1. Full-Scale Current vs Current Select Inputs IS1 and IS0

| IS1 | IS0 | FULL-SCALE CURRENT (ifs) (mA) |

|-----|-----|-------------------------------|

| 0   | 0   | 15.4                          |

| 0   | 1   | 17.0                          |

| 1   | 0   | 18.6                          |

| 1   | 1   | 20.2                          |

### 7.3.4 ILOW Input

The ILOW feature provides a way to quickly reduce the LED current. This feature can be used to dim the LCD backlight during camera flash operation without changing the PWM duty cycle. ILOW is a high-impedance input so it cannot be left floating. When ILOW is driven high, the high-voltage current sink outputs are approximately equal to (ifs x  $D_{PWM}$  x 5%). When ILOW is driven low, the high-voltage current sinks are a function of the full-scale current setting and the PWM input duty cycle. If ILOW is not required the input should be connected to GND.

### 7.3.5 Thermal Shutdown

The LM3699 contains a thermal shutdown protection. In the event the die temperature reaches 140°C (typ), the boost converter and current sink outputs shut down until the die temperature drops to typically 125°C.

#### 7.4 Device Functional Modes

#### 7.4.1 Operation with an Unused Current Sink

If one of the current sink outputs is not connected to a LED string the terminal must be connected to V<sub>IN</sub>. This ensures that the boost converter regulates the headroom voltage on the highest voltage LED string.

## 8 Application and Implementation

## 8.1 Application Information

**Table 2. Recommended Components**

| COMPONENT | MANUFACTURER | VALUE    | PART NUMBER      | SIZE (mm)       | CURRENT/VOLTAGE<br>RATING (RESISTANCE) |

|-----------|--------------|----------|------------------|-----------------|----------------------------------------|

| L         | TDK          | 10 µH    | VLF302512MT-100M | 2.5 x 3.0 x 1.2 | 620 mA/0.25 Ω                          |

| COUT      | TDK          | 1.0 µF   | C2012X5R1E105    | 0805            | 25V                                    |

| CIN       | TDK          | 2.2 µF   | C1005X5R1A225    | 0402            | 10V                                    |

| Diode     | On-Semi      | Schottky | NSR0240V2T1G     | SOD-523         | 40V, 250 mA                            |

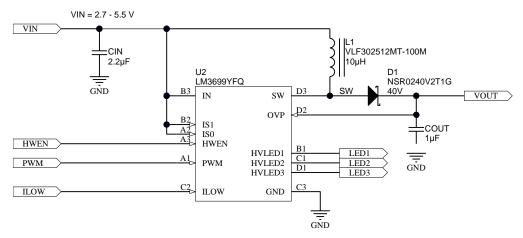

## 8.2 Typical Application

Figure 7. LM3699 Simplified Schematic

## 8.2.1 Design Requirements

**Table 3. Design Parameters**

| DESIGN PARAMETER                              | EXAMPLE VALUE |  |  |  |  |

|-----------------------------------------------|---------------|--|--|--|--|

| Full-scale current setting                    | 20.2 mA       |  |  |  |  |

| Minimum input voltage                         | 2.7 V         |  |  |  |  |

| LED series/parallel configuration             | 6s3p          |  |  |  |  |

| LED maximum forward voltage (V <sub>f</sub> ) | 3.5 V         |  |  |  |  |

| Efficiency                                    | 75%           |  |  |  |  |

## 8.2.2 Detailed Design Procedure

## 8.2.2.1 Step-by-Step Design Procedure

The designer needs to know the following:

- Full-scale current setting

- Minimum input voltage

- LED series/parallel configuration

- LED maximum forward voltage (V<sub>f</sub>)

- LM3699 efficiency for LED configuration

The full-scale current setting, number of series LEDs, and minimum input voltage are needed in order to calculate the peak input current, maximum output voltage, and maximum required output power. This information guides the designer to determine if the LM3699 can support the required output power and make the appropriate inductor selection for the application.

The LM3699 Boost converter output voltage ( $V_{OUT}$ ) is calculated as follows: number of series LEDs x  $V_f$  + 0.4V

The LM3699 Boost converter output current ( $I_{OUT}$ ) is calculated as follows: number of parallel LED strings x full-scale current

The LM3699 peak input current (I<sub>IN PK</sub>) is calculated as follows:

$$\begin{split} &V_{OUT} \times I_{OUT} \ / \ Minimum \ V_{IN} \ / \ Efficiency \\ &V_{OUT} = 21.4 \ V = 6 \times 3.5 \ V + 0.4 \ V \\ &I_{OUT} = 0.0606 \ A = 0.0202 \ A \times 3 \\ &I_{IN\_PK} > 0.640 \ A = 21.4 \ V \times 0.0606 \ A \ / \ 2.7 \ V \ / \ 0.75 \end{split}$$

## 8.2.2.2 Maximum Output Power

The maximum output power of the device is governed by two factors: the peak current limit ( $I_{CL} = 880$  mA min) and the maximum output voltage ( $V_{OUT}$ ). When the application causes either of these limits to be reached, it is possible that the proper current regulation and matching between LED current strings will not be met.

#### 8.2.2.2.1 Peak Current Limited

In the case of a peak current limited situation, when the peak of the inductor current hits the LM3699 current limit, the NFET switch turns off for the remainder of the switching period. If this happens each switching cycle the LM3699 regulates the peak of the inductor current instead of the headroom across the current sinks. This can result in the dropout of the current sinks, and the LED current dropping below its programmed level.

The peak current ( $I_{PEAK}$ ) in a boost converter is dependent on the value of the inductor, total LED current in the boost ( $I_{OUT}$ ), the boost output voltage ( $V_{OUT}$ ) (which is the highest voltage LED string +  $V_{HR}$ ), the input voltage ( $V_{IN}$ ), the switching frequency ( $f_{SW}$ ), and the efficiency (Output Power/Input Power). Additionally, the peak current is different depending on whether the inductor current is continuous during the entire switching period (CCM), or discontinuous (DCM) where it goes to 0 before the switching period ends. For CCM, the peak inductor current is given by:

$$I_{PEAK} = \frac{I_{OUT} \times V_{OUT}}{V_{IN} \times efficiency} + \left[ \frac{V_{IN}}{2 \times f_{SW} \times L} \times \left( 1 - \frac{V_{IN} \times efficiency}{V_{OUT}} \right) \right]$$

(2)

For DCM the peak inductor current is given by:

$$I_{PEAK} = \sqrt{\frac{2 \times I_{OUT}}{f_{SW} \times L \times efficiency}} \times \left(V_{OUT} - V_{IN} \times efficiency\right)$$

(3)

To determine which mode the circuit is operating in (CCM or DCM) a calculation must be done to test whether the inductor current ripple is less than the anticipated input current ( $I_{IN}$ ). If  $\Delta I_L$  is less than  $I_{IN}$ , then the device is operating in CCM. If  $\Delta I_L$  is greater than  $I_{IN}$  then the device is operating in DCM.

$$\frac{I_{\text{OUT}} \times V_{\text{OUT}}}{V_{\text{IN}} \times \text{efficiency}} > \frac{V_{\text{IN}}}{f_{\text{SW}} \times L} \times \left(1 - \frac{V_{\text{IN}} \times \text{efficiency}}{V_{\text{OUT}}}\right) \tag{4}$$

Typically at currents high enough to reach the LM3699 peak current limit, the device operates in CCM.

Figure 8 shows the output current derating for a  $10-\mu H$  and a  $22-\mu H$  inductor using 75% and 80% efficiency estimates. These plots take equations (2) and (3) from above and plot  $I_{OUT}$  with varying  $V_{IN}$  using a constant peak current of 880 mA ( $I_{CL\_MIN}$ ) and 1-MHz switching frequency. Using these curves can help the user understand the impact of  $V_{IN}$ , inductance, and efficiency on the maximum output current. A  $10-\mu H$  inductor can typically be a smaller device with lower on resistance, but the peak currents will be higher. A  $22-\mu H$  inductor provides for lower peak currents, but to match the DC resistance of a  $10-\mu H$  inductor requires a larger sized device.

Figure 8. Maximum Output Power Vs Inductance And Efficiency

#### 8.2.2.2.2 Output Voltage Limited

If a output voltage limited situation occurs, when the boost output voltage hits the LM3699 OVP threshold, the NFET turns off and stays off until the output voltage falls below the hysteresis level (typically 1 V below the OVP threshold). This results in the boost converter regulating the output voltage to the OVP threshold, causing the current sinks to go into dropout. The LM3699 OVP setting supports LED strings up to 6 series LEDs ( $V_{fmax} = 3.5$  V).

#### 8.2.2.3 Boost Inductor Selection

The boost converter operates using either a 10-µH or 22-µH inductor. The inductor selected must have a saturation current greater than the peak operating current.

#### 8.2.2.4 Output Capacitor Selection

The LM3699 inductive boost converter requires a 1.0-µF X5R or X7R 50V (0805 size) ceramic capacitor to filter the output voltage. Pay careful attention to the capacitor tolerance and DC bias response. Smaller body-size 1.0-µF ceramic capacitors or 25-V, 1.0-µF ceramic capacitors can be used, but for proper operation the degradation in capacitance due to tolerance, DC bias, and temperature should stay above 0.4 µF. This might require placing two devices in parallel in order to maintain the required output capacitance over the device operating range and series LED configuration.

#### 8.2.2.5 Schottky Diode Selection

The Schottky diode must have a reverse breakdown voltage greater than the LM3699's maximum output voltage. Additionally, the diode must have an average current rating high enough to handle the LM3699's maximum output current, and at the same time the diode peak current rating must be high enough to handle the peak inductor current. Schottky diodes are required due to their lower forward voltage drop (0.3 V to 0.5 V) and their fast recovery time.

#### 8.2.2.6 Input Capacitor Selection

The LM3699 inductive boost converter requires a 2.2-µF X5R or X7R ceramic capacitor to filter the input voltage. The input capacitor filters the inductor current ripple and the internal MOSFET driver currents during turnon of the internal power switch.

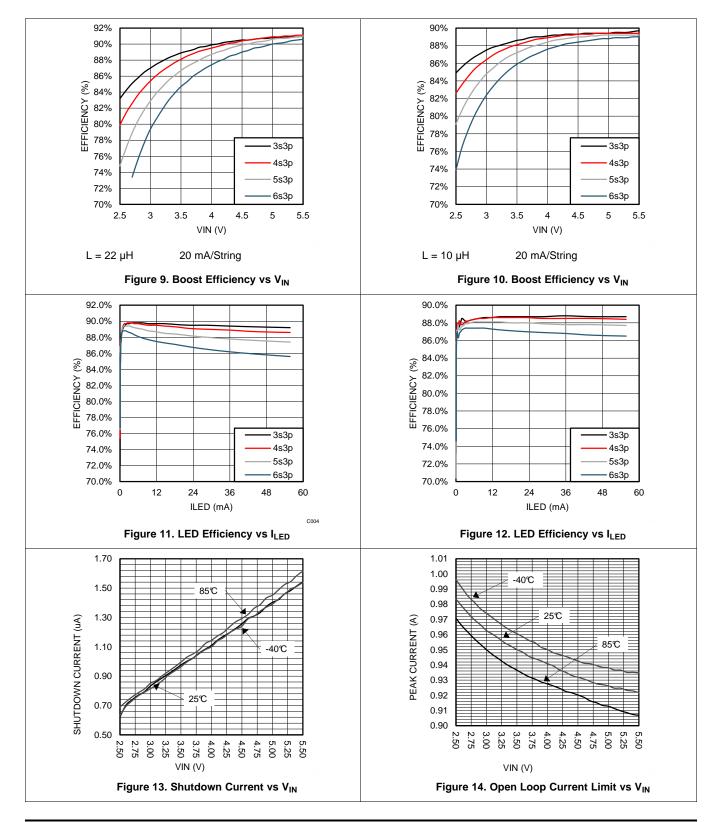

## 8.2.3 Application Performance Plots

$V_{IN}$  = 3.6 V, LEDs are WLEDs part # SML-312WBCW(A), Typical Application Circuit with L = TDK (VLF302512, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A$  = 25°C unless otherwise specified. Efficiency is given as ( $V_{OUT} \times (I_{HVLED1} + I_{HVLED2} + I_{HVLED3}))/(V_{IN} \times I_{IN})$ , matching curves are given as ( $V_{IN} \times I_{IN} = I_{IN} \times I_{IN} = I_{IN}$

$V_{IN} = 3.6 \text{ V, LEDs are WLEDs part } \# \text{SML-312WBCW(A), Typical Application Circuit with L} = \text{TDK (VLF302512, 10 } \mu\text{H, 22 } \mu\text{H} \\ \text{where specified), Schottky} = \text{On-Semi (NSR0240V2T1G), T}_{A} = 25^{\circ}\text{C unless otherwise specified. Efficiency is given as (V}_{OUT} \times (I_{HVLED1} + I_{HVLED2} + I_{HVLED3}))/(V_{IN} \times I_{IN}), \text{ matching curves are given as } (\Delta I_{LED\_MAX}/I_{LED\_AVE}).$

$V_{IN}$  = 3.6 V, LEDs are WLEDs part # SML-312WBCW(A), Typical Application Circuit with L = TDK (VLF302512, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A$  = 25°C unless otherwise specified. Efficiency is given as ( $V_{OUT} \times (I_{HVLED2} + I_{HVLED3}))/(V_{IN} \times I_{IN})$ , matching curves are given as ( $V_{IN} \times I_{IN} \times I_{IN}$ ).

## 9 Power Supply Recommendations

The LM3699 is designed to operate from an input voltage supply range of 2.7 V to 5.5 V. The input supply connection must be properly designed to support the LM3699 maximum peak current limit.

## 10 Layout

## 10.1 Layout Guidelines

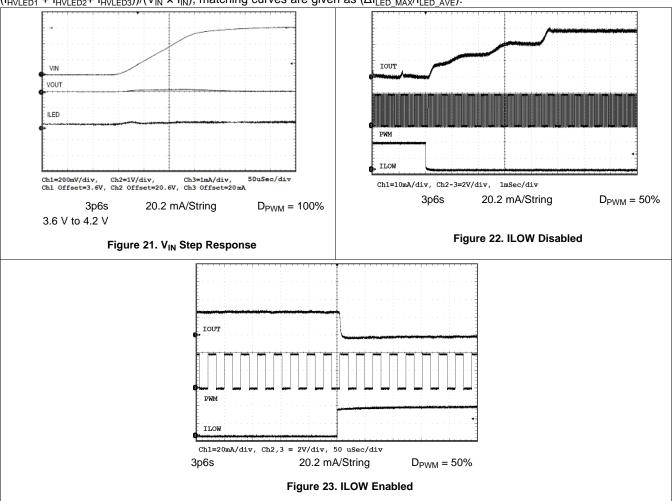

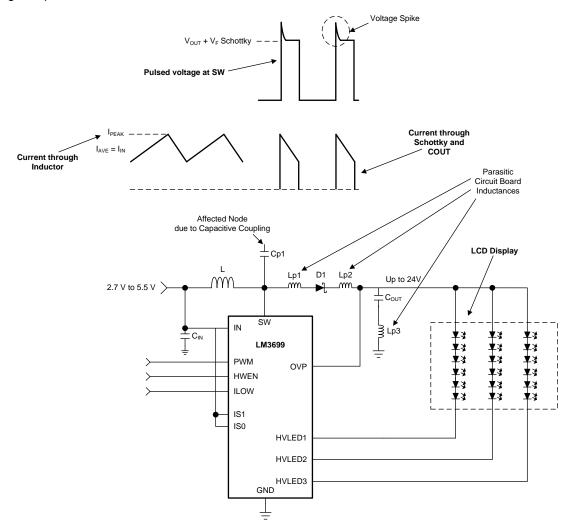

The LM3699 inductive boost converter sees a high switched voltage (up to 24 V) at the SW terminal, as well as a step current (up to 1 A) through the Schottky diode and output capacitor each switching cycle. The high switching voltage can create interference into nearby nodes due to electric field coupling (I = CdV/dt). The large step current through the diode and the output capacitor can cause a large voltage spike at the SW and OVP terminals due to parasitic inductance in the step current conducting path (V = Ldi/dt). Board layout guidelines are geared towards minimizing this electric field coupling and conducted noise. Figure 24 highlights these two noise-generating components.

Figure 24. LM3699 Inductive Boost Converter Showing Pulsed Voltage At SW (High dv/dt) And Current Through Schottky And C<sub>OUT</sub> (High di/dt)

The following list details the main (layout sensitive) areas of the LM3699 inductive boost converter in order of decreasing importance:

### 1. Output Capacitor

- Schottky Cathode to C<sub>OUT</sub>+

- COUT- to GND

#### 2. Schottky Diode

- SW Terminal to Schottky Anode

- Schottky Cathode to C<sub>OUT</sub>+

#### **Layout Guidelines (continued)**

- 3. Inductor

- SW Node PCB capacitance to other traces

- 4. Input Capacitor

- CIN+ to IN terminal

#### 10.1.1 Boost Output Capacitor Placement

Because the output capacitor is in the path of the inductor current discharge path, a high-current step from 0 to  $I_{PEAK}$  occurs each time the switch turns off and the Schottky diode turns on. Any inductance along this series path from the cathode of the diode through  $C_{OUT}$  and back into the LM3699 GND terminal contributes to voltage spikes ( $V_{SPIKE} = LP_x di/dt$ ) at SW and OUT. These spikes can potentially over-voltage the SW terminal, or feed through to GND. To avoid this,  $C_{OUT}+$  must be connected as close as possible to the Cathode of the Schottky diode, and  $C_{OUT}-$  must be connected as close as possible to the LM3699 GND terminal. The best placement for  $C_{OUT}$  is on the same layer as the LM3699 so as to avoid any vias that can add excessive series inductance.

## 10.1.2 Schottky Diode Placement

In the boost circuit of the device the Schottky diode is in the path of the inductor current discharge. As a result the Schottky diode sees a high-current step from 0 to  $I_{PEAK}$  each time the switch turns off and the diode turns on. Any inductance in series with the diode may cause a voltage spike ( $V_{SPIKE} = LP_x di/dt$ ) at SW and OUT. This can potentially over-voltage the SW terminal, or feed through to  $V_{OUT}$  and through the output capacitor and into GND. Connecting the anode of the diode as close as possible to the SW terminal and the cathode of the diode as close as possible to  $C_{OUT}$ + reduces the inductance ( $LP_x$ ) and minimize these voltage spikes.

#### 10.1.3 Inductor Placement

The node where the inductor connects to the LM3699 SW terminal has 2 issues. First, a large switched voltage (0 to V<sub>OUT</sub> + VF\_SCHOTTKY) appears on this node every switching cycle. This switched voltage can be capacitively coupled into nearby nodes. Second, there is a relatively large current (input current) on the traces connecting the input supply to the inductor and connecting the inductor to the SW terminal. Any resistance in this path can cause voltage drops that can negatively affect efficiency and reduce the input operating voltage range.

To reduce the capacitive coupling of the signal on SW into nearby traces, the SW terminal-to-inductor connection must be minimized in area. This limits the PCB capacitance from SW to other traces. Additionally, high-impedance nodes that are more susceptible to electric field coupling need to be routed away from SW and not directly adjacent or beneath. This is especially true for traces such as IS1, IS0, ILOW, HWEN, and PWM. A GND plane placed directly below SW greatly reduce the capacitance from SW into nearby traces.

Lastly, limit the trace resistance of the VBATT-to-inductor connection and from the inductor-to-SW connection, by use of short, wide traces.

### 10.1.4 Boost Input Capacitor Placement

For the LM3699 boost converter, the input capacitor filters the inductor current ripple and the internal MOSFET driver currents during turnon of the internal power switch. The driver current requirement can range from 50 mA at 2.7 V to over 200 mA at 5.5 V with fast durations of approximately 10 ns to 20 ns. This appears as high di/dt current pulses coming from the input capacitor each time the switch turns on. Close placement of the input capacitor to the IN terminal and to the GND terminal is critical since any series inductance between IN and  $C_{IN}$ + or  $C_{IN}$ - and GND can create voltage spikes that could appear on the  $V_{IN}$  supply line and in the GND plane.

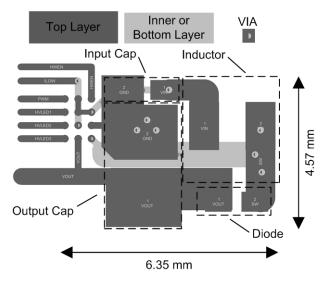

## 10.2 Layout Example

Figure 25 requires two PCB layers and is optimized for the GND connection.

Figure 25. LM3699 GND Optimized Layout Example

## 11 器件和文档支持

## 11.1 器件支持

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 11.2 Trademarks

All trademarks are the property of their respective owners.

### 11.3 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms and definitions.

### 12 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 要获得这份数据表的浏览器版本,请查阅左侧导航栏。

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                      |         |

| LM3699YFQR       | ACTIVE | DSBGA        | YFQ                | 12   | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | D9                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

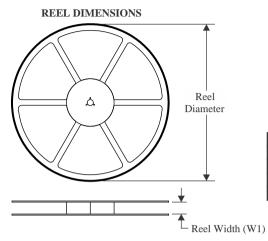

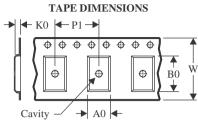

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

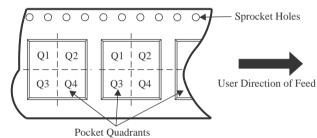

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3699YFQR | DSBGA           | YFQ                | 12 | 3000 | 178.0                    | 8.4                      | 1.35       | 1.75       | 0.76       | 4.0        | 8.0       | Q1               |

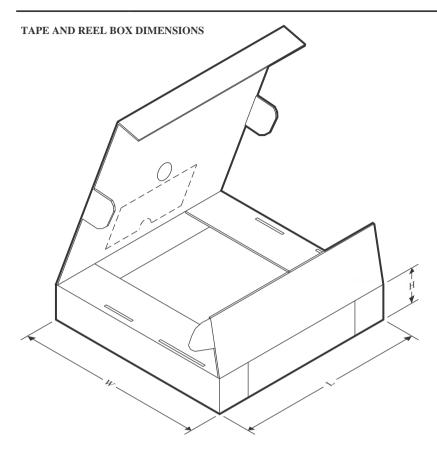

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

## \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| LM3699YFQR | DSBGA        | YFQ             | 12   | 3000 | 208.0       | 191.0      | 35.0        |  |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司