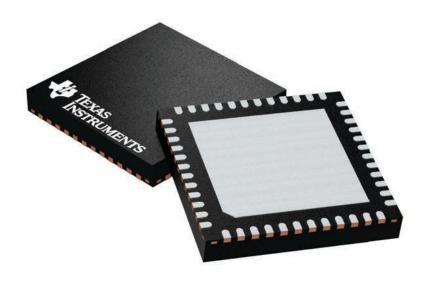

**TPS65400**

ZHCSD04E - NOVEMBER 2014 - REVISED MARCH 2022

# TPS65400 具有 PMBus/I<sup>2</sup>C 接口、4.5V 至 18V 输入、灵活的电源管理单元

# 1 特性

- 每个开关稳压器的效率高达 95%

- 开关稳压器规格:

**TEXAS**

INSTRUMENTS

- 输入电压范围: 4.5V 至 18V

- V<sub>OUT</sub> 范围: 0.6V-90%V<sub>IN</sub>

- SW1、SW2 IOUT: 4A (最大值)

- SW3、SW4 I<sub>OUT</sub>:2A(最大值)

- 预偏置启动算法可最大限度地减小启动期间的电压 骤降

- 内部欠压锁定 (UVLO)、过流保护 (OCP)、过压保 护 (OVP) 和过热保护 (OTP)

- 符合 AECQ-100 1 级标准

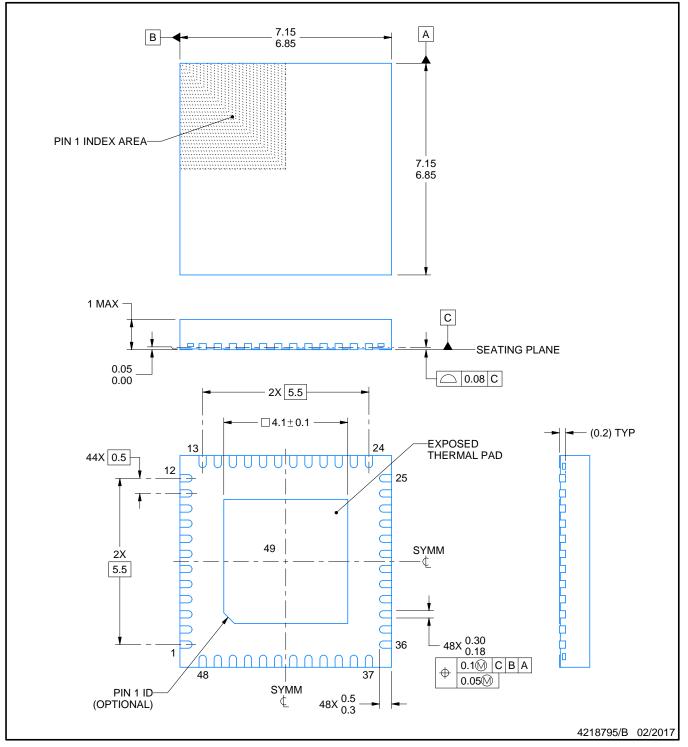

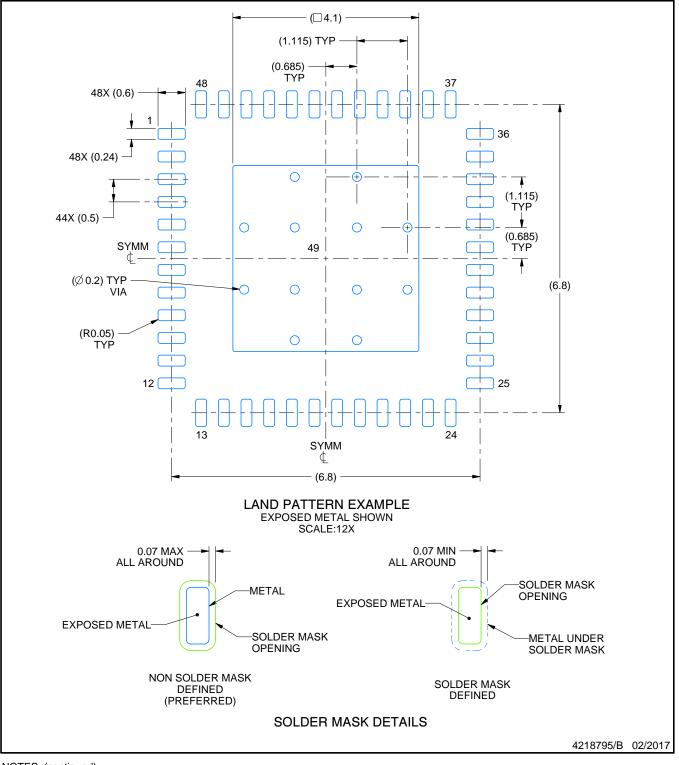

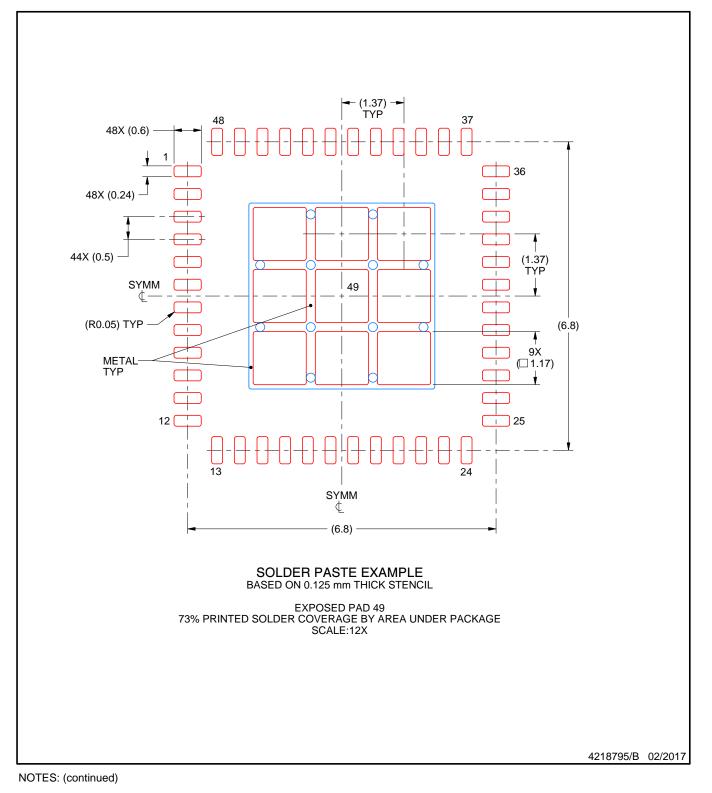

- 热增强型 7mm × 7mm 48 引脚 0.5mm 间距 VQFN 封装

- 引脚访问特性:

- 通过外部反馈电阻器可调节 Vout

- 通过每个开关的精密使能引脚实现时序控制

- 通过电阻器在 275 kHz 至 2.2 MHz 范围内调节 PWM 开关频率

- 时钟同步输入和时钟输出

- 通过外部电容器实现软启动延迟

- 必要时可通过在 SW1 和 SW2 之间以及 SW3 和 SW4 之间进行电流共享来满足高电流需求

- PMBus 运行时控制和状态

- 通过调整 VRFF 可实现运行时电压定位

- 启用和禁用每个开关

- 故障和状态监控

- 用户可配置的 PMBus/l<sup>2</sup>C 选项,保存在 EEPROM 中

- 电源导通和关断时序控制

- 可基于固定延时时间或依赖 PGOOD 实现时序 控制

- 可通过 VREF 配置实现初始电压定位

- 可针对每个开关调节 PWM 频率

- 可针对每个开关单独进行 PWM 相位对齐以最大 限度地减小纹波和电容器尺寸

- 可调节每个稳压器的电流限值以优化电感器的尺 寸和成本

- 软启动时间

# 2 应用

- 小型蜂窝基站 (BTS) (例如:微微蜂窝和微蜂 窝);宏BTS(使用多个PMU)

- 以太网供电 (PoE) 通信基础设备

- 汽车信息娱乐系统和远程信息处理

- 为 DSP 和 MCU 供电

- 工业和工厂自动化

- 要求小尺寸、高效率、高工作环境温度和灵活电源 管理的系统

## 3 说明

TPS65400 是一款集成型电源管理单元 (PMU),针对 对小尺寸和高电源转换效率有要求的应用进行了优化, 使得小型空间受限类设备能够在高温环境下工作而无需 制冷。此器件可借助优化的稳压器组合从中间配电总线 进行单级转换,从而在系统级别实现高能效。

### **哭**件信息

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

|----------|-------------------|-----------------|

| TPS65400 | VQFN (48)         | 7.00mm × 7.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

# **Table of Contents**

| 1 | 特性                                              | 1 |

|---|-------------------------------------------------|---|

|   | 应用                                              | 1 |

|   | 说明                                              | 1 |

|   | Revision History                                | 2 |

|   | 说明(续)                                           |   |

|   | Pin Configuration and Functions                 |   |

|   | Specifications                                  |   |

|   | 7.1 Absolute Maximum Ratings                    |   |

|   | 7.2 ESD Ratings                                 | 6 |

|   | 7.3 Recommended Operating Conditions            | 6 |

|   | 7.4 Thermal Information                         | 7 |

|   | 7.5 Electrical Characteristics                  | 7 |

|   | 7.6 System Characteristics                      |   |

|   | 7.7 Operational Parameters1                     |   |

|   | 7.8 Package Dissipation Ratings1                |   |

|   | 7.9 Typical Characteristics: System Efficiency1 |   |

| 8 | Detailed Description1                           |   |

|   | 8.1 Overview1                                   |   |

|   | 8.2 Functional Block Diagrams1                  |   |

|   | 8.3 Feature Description1                        | 4 |

| 8.4 Device Functional Modes             | 20              |

|-----------------------------------------|-----------------|

| 8.5 Programming                         |                 |

|                                         |                 |

| 8.6 Register Maps                       |                 |

| 9 Application and Implementation        |                 |

| 9.1 Application Information             | <mark>55</mark> |

| 9.2 Typical Applications                | <mark>56</mark> |

| 10 Power Supply Recommendations         | 68              |

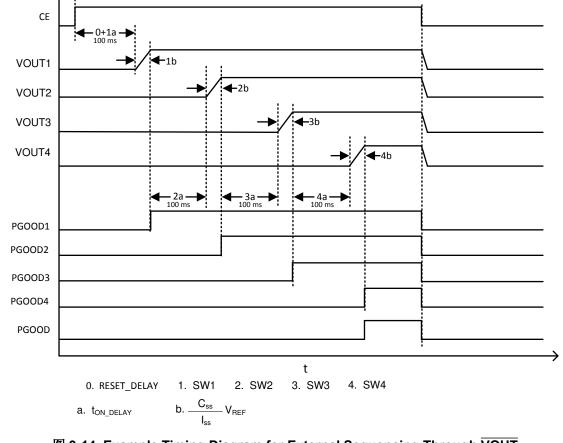

| 11 Layout                               | 69              |

| 11.1 Layout Guidelines                  |                 |

| 11.2 Layout Example                     |                 |

| 12 Device and Documentation Support     |                 |

| 12.1 Documentation Support              |                 |

| 12.2 接收文档更新通知                           |                 |

| 12.3 术语表                                | 71              |

| 12.4 Trademarks                         |                 |

| 12.5 Electrostatic Discharge Caution    | 71              |

| 12.6 术语表                                | 71              |

| 13 Mechanical, Packaging, and Orderable |                 |

| Information                             | 71              |

|                                         |                 |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| Changes from Revision D (July 2018) to Revision E (March 20                                                              | 2) Page |

|--------------------------------------------------------------------------------------------------------------------------|---------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式。                                                                                               |         |

|                                                                                                                          |         |

| Changes from Revision C (May 2018) to Revision D (July 2018                                                              | Page    |

| Changes from Revision C (May 2018) to Revision D (July 2018) <ul> <li>Added soldering and storage temperature</li> </ul> |         |

• Updated the default timing for  $t_{ON\_DELAY}$  and  $t_{OFF\_DELAY}$  to 5 ms in the *External Sequencing* section......15

# 5 说明(续)

**TPS65400** 实现了兼容 **PMBus-I<sup>2</sup>C** 的数字接口。此接口可在运行时更改稳定电压、电源时序、相位交错、工作频率以及读回工作状态等,从而帮助内核芯片优化系统性能。

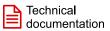

TPS65400 包含 4 个具有集成式场效应晶体管 (FET) 的高电流降压开关稳压器 (SW1、SW2、SW3 和 SW4)。 这些开关电源专门用于为大电流数字电路 (例如处理器、现场可编程门阵列 (FPGA)、专用集成电路 (ASIC)、存 储器和数字输入/输出 (I/O))供电。SW1 和 SW2 支持 4A 电流,而 SW3 和 SW4 支持 2A 电流。每个稳压器的开 关频率可单独调节至高达 2.2 MHz。

每个开关均具有可编程的限流功能,因此可为无需最大电流能力的特定应用配置优化电感器额定值。

TPS65400 可由 4.5V 和 18V 之间的单输入电压轨供电,因此非常适合由 5V 或 12V 中间电源配电母线供电运行的应用。

可使用单独的使能端子或者通过 I<sup>2</sup>C 总线将时序编程到板载 EEPROM 中来满足时序要求。输出电压可通过外部 电阻网络进行设置,VREF 的可编程范围介于 0.6 V 到 1.87 V 之间(阶跃为 10 mV)。所有控制和状态信息均可 通过兼容 PMBus 的 I<sup>2</sup>C 总线进行访问。

TPS65400 具有高度的灵活性,可通过 I<sup>2</sup>C 总线提供全方位的监视和控制,同时还能够为不使用 I<sup>2</sup>C 的系统提供 电压以及基于外部元件实现的可编程性。

## **6** Pin Configuration and Functions

A. Thermal pad must be soldered to PCB as SW3 and SW4 power ground.

图 6-1. 48-Pin VQFN RGZ Package (Top View)

#### 表 6-1. Pin Functions

| PIN      |     | Bootstrap pin for the high-side MOSFET gate drive for SW1 |

|----------|-----|-----------------------------------------------------------|

| NAME NO. | NO. | DESCRIPTION                                               |

| CB1      | 1   | Bootstrap pin for the high-side MOSFET gate drive for SW1 |

Copyright © 2022 Texas Instruments Incorporated

## 表 6-1. Pin Functions (continued)

| PIN                                                                                                                                                                                                                                                                             |     |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                                                                                                                                                                                                                                            | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                                                                                                                                                                                                                 | 2   |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SW1                                                                                                                                                                                                                                                                             | 3   | Switch pin for SW1                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                 | 4   |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PVIN1                                                                                                                                                                                                                                                                           | 5   | Power input for the buck switching regulator SW1                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PVIN2                                                                                                                                                                                                                                                                           | 6   | Power input for SW2                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| PGND1                                                                                                                                                                                                                                                                           | 7   | Power ground for buck converters                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PGND2                                                                                                                                                                                                                                                                           | 8   | Power ground for buck converters                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                 | 9   |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SW2                                                                                                                                                                                                                                                                             | 10  | Switch pin for SW2                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                 | 11  |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| CB2                                                                                                                                                                                                                                                                             | 12  | Bootstrap pin for the SW2 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ENSW2                                                                                                                                                                                                                                                                           | 13  | Enable input pin for SW2. Active high. A 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                        |  |  |  |

| VFB2                                                                                                                                                                                                                                                                            | 14  | Feedback input pin for SW2                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| COMP2                                                                                                                                                                                                                                                                           | 15  | Compensation pin for external compensation network for SW2. Pulling this line high to VDDA configures the SW1 controller to control both SW1 and SW2.                                                                                                                                                                                                                                   |  |  |  |

| SS2/PG2                                                                                                                                                                                                                                                                         | 16  | Soft start for SW2 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD2 signal instead.                                                                                                                                                                                                            |  |  |  |

| PGOOD                                                                                                                                                                                                                                                                           | 17  | Default PGOOD signal is for all switchers. It can be changed according to ( <i>D2h</i> ) <i>PIN_CONFIG_00</i> . If all switchers are disabled, PGOOD is low.                                                                                                                                                                                                                            |  |  |  |

| VDDG                                                                                                                                                                                                                                                                            | 18  | Supply for gate drives. Bypass locally to PGND.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VDDA                                                                                                                                                                                                                                                                            | 19  | Output of internal regulator for analog controls                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VDDD                                                                                                                                                                                                                                                                            | 20  | 3.3-V output of internal regulator digital controls                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| AGND                                                                                                                                                                                                                                                                            | 21  | Ground connection for analog controls                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VIN                                                                                                                                                                                                                                                                             | 22  | Analog V <sub>IN</sub> . Power input pin for the VDDD, VDDA, and VGATE subregulator power                                                                                                                                                                                                                                                                                               |  |  |  |

| CE 23 Chip enables. Internal pullup current will default to high if the pin is left floating. Con<br>output to pull low to disable. Driving with a push-pull output is not recommended. V<br>are shutdown to minimize power, and functions are disabled. Configuration is reloa |     | Chip enables. Internal pullup current will default to high if the pin is left floating. Connect to an open-drain output to pull low to disable. Driving with a push-pull output is not recommended. When low, internal regulators are shutdown to minimize power, and functions are disabled. Configuration is reloaded from EEPROM as part of the power-up sequence when CE goes high. |  |  |  |

| SS3/PG3                                                                                                                                                                                                                                                                         | 24  | Soft-start for SW3 (default). A capacitor is used to set the startup time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD3 signal instead.                                                                                                                                                                                                             |  |  |  |

| COMP3                                                                                                                                                                                                                                                                           | 25  | Compensation pin for external compensation network for SW3                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VFB3                                                                                                                                                                                                                                                                            | 26  | Feedback input pin for SW3                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ENSW3                                                                                                                                                                                                                                                                           | 27  | Enable input pin for SW3. Active high. A 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                        |  |  |  |

| CB3                                                                                                                                                                                                                                                                             | 28  | Bootstrap pin for SW3 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SW3                                                                                                                                                                                                                                                                             | 29  | Switch pin for SW3. The maximum rated output current is 2 A.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PVIN3                                                                                                                                                                                                                                                                           | 30  | Power input for buck switching regulator SW3                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PVIN4                                                                                                                                                                                                                                                                           | 31  | Power input for SW4                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| SW4                                                                                                                                                                                                                                                                             | 32  | Switch pin for SW4. The maximum rated output current is 2 A.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CB4                                                                                                                                                                                                                                                                             | 33  | Bootstrap pin for SW4 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ENSW4                                                                                                                                                                                                                                                                           | 34  | Enable input pin for SW4. Active high. A 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                        |  |  |  |

| VFB4                                                                                                                                                                                                                                                                            | 35  | Feedback input pin for SW4                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| COMP4                                                                                                                                                                                                                                                                           | 36  | Compensation pin for external compensation network for SW4. Pulling this line high to VDDA configures the SW3 controller to control both SW3 and SW4.                                                                                                                                                                                                                                   |  |  |  |

| SS4/PG4                                                                                                                                                                                                                                                                         | 37  | Soft start for SW4 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD4 signal instead.                                                                                                                                                                                                            |  |  |  |

| I2CADDR                                                                                                                                                                                                                                                                         | 38  | Select I <sup>2</sup> C address with a resistor to AGND.                                                                                                                                                                                                                                                                                                                                |  |  |  |

## 表 6-1. Pin Functions (continued)

| PIN                                                                                                                                                                                                 |                                                                        | DESCRIPTION                                                                                                                     |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                                                                                | NO.                                                                    | DESCRIPTION                                                                                                                     |  |  |

| RST_N                                                                                                                                                                                               | 39                                                                     | Reset of digital logic. When low, all switchers are disabled. Configuration is reloaded from EEPROM when RESET_N is deasserted. |  |  |

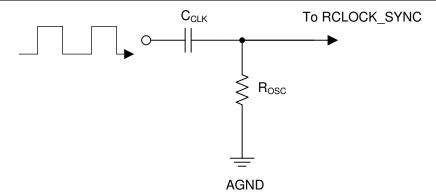

| RCLOCK_SYNC                                                                                                                                                                                         | 40                                                                     | Resistor for setting primary clock frequency from 275 kHz to 2.2 MHz or for clock sync                                          |  |  |

| I2CALERT 41 Open-drain output that is pulled low for 200 μs when a timeout condition is detected by the I <sup>2</sup> C watchdog on either SDA or SCL.                                             |                                                                        |                                                                                                                                 |  |  |

| SDA                                                                                                                                                                                                 | 42                                                                     | input/output pin for I <sup>2</sup> C bus                                                                                       |  |  |

| SCL                                                                                                                                                                                                 | 43                                                                     | r input pin for I <sup>2</sup> C bus                                                                                            |  |  |

| CLK_OUT                                                                                                                                                                                             | LK_OUT 44 Clock output signal. Open-collector output, requires pull up |                                                                                                                                 |  |  |

| SS1/PG1       45       Soft start for SW1 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured through l <sup>2</sup> C to display the PGOOD1 signal instead. |                                                                        |                                                                                                                                 |  |  |

| COMP1                                                                                                                                                                                               | 46 Compensation pin for external compensation network for SW1          |                                                                                                                                 |  |  |

| VFB1                                                                                                                                                                                                | 47 Feedback input pin for SW1                                          |                                                                                                                                 |  |  |

| ENSW1/ENSEQ                                                                                                                                                                                         | 48                                                                     | Enable input pin for SW1. Active high. A 2-µA internal pullup current is inside.                                                |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

|                     |                                                                                 | MIN   | MAX         | UNIT |

|---------------------|---------------------------------------------------------------------------------|-------|-------------|------|

|                     | PVIN1, PVIN2, PVIN3, PVIN4, VIN                                                 | - 0.3 | 20.0        | V    |

| Maximum lead        | CB1, CB2, CB3, CB4 referenced to SWx                                            | - 0.3 | 7.5         | V    |

|                     | CLK_OUT, VFB1, VFB2, VFB3, VFB4, RST_N, I2CALERT, CLK_OUT, I2CADDR, RCLOCK_SYNC |       | VDDD or 3.6 | V    |

| Input voltage       | SW1, SW2, SW3, SW4                                                              | - 1.0 | 20.0        | V    |

| Input voltage       | VDDA, VDDG                                                                      | - 0.3 | 7.5         | V    |

|                     | PGOOD, SS1/PG1, SS2/PG2, SS3/PG3, SS4/PG4, COMP1, COMP2, COMP3, COMP4, CE       | - 0.3 | VDDA or 7.5 | V    |

|                     | VDDD                                                                            | - 0.3 | 3.6         | V    |

|                     | SCL, SDA, ENSW1, ENSW2, ENSW3, ENSW4                                            | - 0.3 | 4.0         | V    |

| Junction temper     | ature, T <sub>J-max</sub>                                                       |       | 150         | °C   |

| Maximum lead t      | emperature (soldering, 10 s)                                                    |       | 260         | °C   |

| Storage temperation | ature, T <sub>stg</sub>                                                         | - 55  | 150         | °C   |

|                     |                                                                                 |       |             |      |

over operating free-air temperature (unless otherwise noted) (1)

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |               |                                                                                          | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±750  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                                                                                               | MIN   | MAX  | UNIT |

|-----------------|---------------------------------------------------------------------------------------------------------------|-------|------|------|

|                 | PVIN1, PVIN2, PVIN3, PVIN4, VIN                                                                               | - 0.3 | 18.0 | V    |

|                 | CB1, CB2, CB3, CB4 referenced to SWx                                                                          | - 0.3 | 7.0  | V    |

|                 | ENSW1, ENSW2, ENSW3, ENSW4, SCL, SDA, CLK_OUT, RST_N, SCL, SDA, I2CALERT, CLK_OUT, I2CADDR, RCLOCK_SYNC, VDDD | - 0.3 | 3.3  | V    |

| Input voltage   | SW1, SW2, SW3, SW4                                                                                            | - 1.0 | 18.0 | V    |

| Input voltage   | VDDA, VDDG                                                                                                    | - 0.3 | 7.0  | V    |

|                 | PGOOD, SS1/PG1, SS2/PG2, SS3/PG3, SS4/PG4, COMP1, COMP2, COMP3, COMP4, CE                                     | - 0.3 | 7.0  | V    |

|                 | VFB1, VFB2, VFB3, VFB4                                                                                        | 0.6   | 1.87 | V    |

| Load current    | I <sub>OUT1</sub> , I <sub>OUT2</sub>                                                                         | 0     | 4    | А    |

| Load current    | IOUT3, IOUT4                                                                                                  | 0     | 2    | А    |

| Junction temper | rature                                                                                                        | - 40  | 125  | °C   |

## 7.4 Thermal Information

|                        |                                              | TPS65400   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                        |                                              | 48 PINS    |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 29.8       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 14.9       | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 6.3        | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ψ JB                   | Junction-to-board characterization parameter | 6.3        | °C/W |

| R <sub>0 JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.8        | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

## 7.5 Electrical Characteristics

$V_{IN}$  = 12 V, Frequency = 500 kHz,  $T_J$  = -40°C to 125°C, typical values are at  $T_J$  = 25°C, unless otherwise indicated

|                                           | PARAMETER                                                             | TEST CONDITIONS                                           | MIN   | TYP | MAX  | UNIT |

|-------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------|-------|-----|------|------|

| SWITCHER 1 A                              | AND SWITCHER 2                                                        |                                                           |       |     |      |      |

| I <sub>limit1</sub> , I <sub>limit2</sub> | SW1, SW2 high-side current limit adjustment range                     |                                                           | 2     |     | 6    | А    |

| I <sub>limit-accuracy</sub>               | Accuracy to nominal current limit value                               | I <sub>limit</sub> = 4 A, 5 A, 6 A                        | - 25% |     | 25%  |      |

| R <sub>dson</sub> HS                      | SW1, SW2 HS Rds(on)                                                   |                                                           |       | 66  |      | mΩ   |

| R <sub>dson</sub> LS                      | SW1, SW2 LS Rds(on)                                                   |                                                           |       | 42  |      | mΩ   |

| SWITCHER 3 A                              | AND SWITCHER 4                                                        |                                                           |       |     |      |      |

| I <sub>limit3</sub> , I <sub>limit4</sub> | SW3 and SW4 current limit                                             |                                                           | 0.5   |     | 3    | А    |

| Ilimit accuracy                           | Accuracy to nominal current limit value                               | I <sub>limit</sub> = 1 A, 2 A, 3 A                        | - 25% |     | 25%  |      |

| R <sub>dson</sub> HS                      | SW3 and SW4 HS Rds(on)                                                |                                                           |       | 120 |      | mΩ   |

| R <sub>dson</sub> LS                      | SW3/4 LS Rds(on)                                                      |                                                           |       | 90  |      | mΩ   |

| FEEDBACK A                                | ND ERROR AMPLIFIERS FOR SW1 - S                                       | W4                                                        |       |     |      |      |

| VFB                                       | Accuracy                                                              | V <sub>REF</sub> = 1 V                                    | - 1%  |     | 1%   |      |

| V <sub>REFn</sub>                         | Error amplifier reference voltage                                     | Default value                                             |       | 800 |      | mV   |

| V <sub>REF_STEP</sub>                     | I <sup>2</sup> C programmable V <sub>REF</sub> step size              |                                                           |       | 10  |      | mV   |

| Gm                                        | Error amplifier transconductance                                      |                                                           | 95    | 133 | 165  | μS   |

| I <sub>sink</sub>                         | Sink                                                                  |                                                           |       | 12  |      | μA   |

| I <sub>source</sub>                       | Source                                                                |                                                           |       | 12  |      | μA   |

| PWM SWITCH                                | ING CHARACTERISTICS                                                   |                                                           |       |     | · ·  |      |

| Phase_err12 <sup>(1)</sup>                | Phase error between SW1 and SW2                                       | F <sub>sw</sub> = 1.1 MHz                                 |       | 5°  |      |      |

| Phase_err34 <sup>(1)</sup>                | Phase error between SW3 and SW4                                       | F <sub>sw</sub> = 1.1 MHz                                 |       | 5°  |      |      |

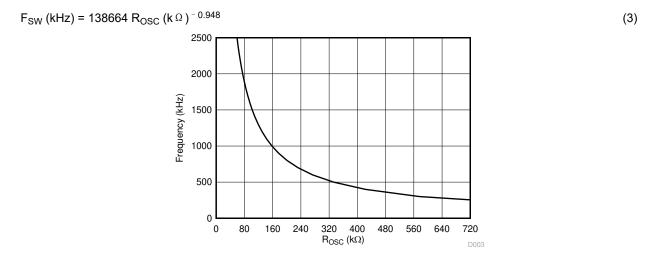

| F <sub>sw</sub>                           | Resistor-configurable PWM switching configuration                     |                                                           | 275   |     | 2200 | kHz  |

| F <sub>sw-accuracy</sub>                  | PWM switching frequency accuracy                                      | R <sub>OSC</sub> = 165 k Ω<br>(F <sub>sw</sub> = 1.1 MHz) | - 10% |     | 10%  |      |

| V <sub>rclock_sync</sub>                  | Voltage reference for RCLOCK_SYNC                                     |                                                           |       | 0.8 |      | V    |

| t <sub>ON_min</sub>                       | Lower duty cycle limit                                                |                                                           |       | 80  | 150  | ns   |

| t <sub>OFF_min</sub>                      | Minimum off-time limit (constrains the maximum achievable duty cycle) |                                                           |       | 150 |      | ns   |

| CLOCK SYNC                                |                                                                       |                                                           |       |     | i    |      |

| V_H <sub>SYNC</sub>                       | High signal threshold                                                 |                                                           | 2.6   |     |      | V    |

|                            | requency = 500 kHz, T <sub>J</sub> = - 40°C to 12<br>PARAMETER                           | TEST CONDITIONS                                               | MIN      | TYP                   | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|-----------------------|------|------|

| V_L <sub>SYNC</sub>        | Low signal threshold                                                                     |                                                               |          |                       | 1    | V    |

| ICLKOUT                    | Max current sink/source for CLK_OUT                                                      |                                                               |          | 2                     |      | mA   |

| t <sub>min SYNC</sub>      | Minimum detectable time for sync pulse                                                   |                                                               |          |                       | 150  | ns   |

| F <sub>SYNC</sub>          | Frequency synchronization range                                                          |                                                               | 275      |                       | 2200 | kHz  |

| T <sub>SYNC_DELAY</sub>    | Delay between input pulse to<br>RCLOCK_SYNC and rising edge of<br>CLK OUT and PWM output |                                                               |          | 20                    |      | ns   |

| TIMING CHAF                | RACTERISTICS                                                                             |                                                               |          |                       |      |      |

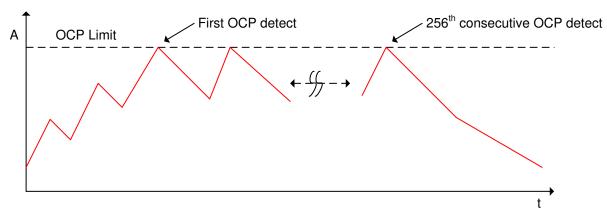

| t <sub>restart</sub>       | Delay for restart during repeated OCP condition                                          |                                                               |          | 20                    |      | ms   |

| INTERNAL RE                | EGULATORS AND UVLO                                                                       |                                                               |          |                       | I    |      |

|                            |                                                                                          | V <sub>in</sub> > 6.6 V                                       |          | 6.1                   |      |      |

| V <sub>DDA</sub>           | Internal subregulator output                                                             | 4.5 V < V <sub>in</sub> 6.6 V                                 | <u>ا</u> | / <sub>in</sub> - 0.1 |      | V    |

| V <sub>DDD</sub>           | Output of internal subregulator                                                          |                                                               |          | 3.2                   |      | V    |

|                            | Output of internal regulator for gate                                                    | V <sub>in</sub> > 6.6 V                                       |          | 6.1                   |      |      |

| V <sub>DDG</sub>           | drivers                                                                                  | 4.5 V < V <sub>in</sub> 6.6 V                                 |          | / <sub>in</sub> - 0.1 |      | V    |

| I <sub>VIN</sub>           | Quiescent non-switching, no load current                                                 | CE high, V <sub>FB</sub> >> V <sub>REF</sub> , (no switching) |          | 8                     |      | mA   |

| I <sub>SD</sub>            | Quiescent shutdown current                                                               | CE low                                                        |          | 12                    | 27   | μA   |

| V <sub>IN_UVLO</sub>       | Input voltage UVLO                                                                       | Rising                                                        |          | 4.25                  | 4.48 | V    |

| V <sub>IN_UVLO</sub>       | Input voltage UVLO                                                                       | Falling                                                       | 3.4      | 3.75                  |      | V    |

|                            | Wx, RST_N, SSx, PG                                                                       |                                                               |          |                       | I    |      |

| R_L <sub>PGOOD</sub>       | Resistance of PGOOD outputs when low                                                     |                                                               |          | 500                   |      | Ω    |

| V_OL <sub>PGOOD</sub>      | Logic output low voltage                                                                 | I_OL = 100 µA                                                 |          |                       | 0.1  | V    |

| I <sub>SS</sub>            | Soft-start current                                                                       |                                                               | 4.1      | 5.6                   | 7.3  | μA   |

| V <sub>EN</sub>            | Enable logic high threshold (for ENSW1, ENSW2, ENSW3, ENSW4)                             | V <sub>EN</sub> rising                                        | 1.12     | 1.20                  | 1.28 | V    |

| V <sub>EN_L</sub>          | Enable logic low threshold (for ENSW1,<br>EN_L ENSW2, ENSW3, ENSW4)                      | V <sub>EN</sub> falling                                       | 0.97     | 1.07                  |      | V    |

| V <sub>EN_HYS</sub>        | Enable hysteresis (for ENSW1, ENSW2, ENSW3, ENSW4)                                       | V <sub>EN</sub> falling                                       |          | 130                   |      | mV   |

| I <sub>EN</sub>            | ENSWx pin pullup current                                                                 | V <sub>EN</sub> = 0                                           |          | 2                     |      | μA   |

| I <sub>CE</sub>            | CE pin pullup current                                                                    | V <sub>CE</sub> = 0                                           |          | 2                     |      | μA   |

| V <sub>IH_CE</sub>         | Logic input high for CE                                                                  |                                                               | 1.3      |                       |      | V    |

| V <sub>IL_CE</sub>         | Logic input low CE                                                                       |                                                               |          |                       | 0.4  | V    |

| V <sub>IH_RSTN</sub>       | Logic input high RST_N                                                                   |                                                               | 1.3      |                       |      | V    |

| V <sub>IL_RSTN</sub>       | Logic input low RST_N                                                                    |                                                               |          |                       | 0.4  | V    |

| I <sup>2</sup> C MODULE    | (SDA, SCL, I2CALERT, I2CADDR)                                                            | ·                                                             |          |                       | I    |      |

| V_IL <sub>I2C</sub>        | Logic input low SCL, SDA                                                                 |                                                               |          |                       | 0.8  | V    |

| V_IH <sub>I2C</sub>        | Logic input high for SCL, SDA                                                            |                                                               | 2.1      |                       |      | V    |

| R_L <sub>I2C</sub>         | ON resistance of I <sup>2</sup> C pins (SDA, SCL, I2CALERT) to GND                       | I2CALERT = 1                                                  |          | 85                    |      | Ω    |

| V_OL <sub>I2C</sub>        | Logic output low voltage for SCL, SDA, I2CALERT pins                                     | I_OL = 350 µA                                                 |          |                       | 0.1  | V    |

| I <sub>LEAK</sub>          | Input leakage current                                                                    | SDA, SCL = 3.3 V                                              |          |                       | 1    | μA   |

| I <sub>I2CADDR</sub>       | Source current of I2CADDR pin                                                            | VDDD = 3.3 V, V <sub>IN</sub> > 4.5 V                         |          | 20                    |      | μA   |

| t <sub>TIMEOUT</sub>       | Timeout detection on SDA or SCL low                                                      |                                                               |          | 30                    |      | ms   |

| t <sub>TIMEOUT</sub> PULSE | Duration of timeout pulse on I2CALERT                                                    |                                                               |          | 200                   |      | μs   |

$V_{IN}$  = 12 V, Frequency = 500 kHz,  $T_J$  = -40°C to 125°C, typical values are at  $T_J$  = 25°C, unless otherwise indicated

|                                         | PARAMETER                                                  | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT                  |

|-----------------------------------------|------------------------------------------------------------|-----------------------------------|-----|-----|-----|-----------------------|

| FAULTS                                  |                                                            |                                   | •   |     |     |                       |

| T <sub>TSD</sub> <sup>(2)</sup>         | Thermal shutdown threshold                                 |                                   |     | 160 |     | °C                    |

| T <sub>TSD_restart</sub> <sup>(2)</sup> | Thermal shutdown hysteresis                                |                                   |     | 20  |     | °C                    |

| M                                       | OVP threshold rising (fault latched, PGOOD asserted)       | 0.6V < V <sub>REF</sub> < 1.87 V  |     | 111 |     | % of $V_{\text{REF}}$ |

| V <sub>FB_OVP</sub>                     | OVP threshold falling (fault cleared, PGOOD deasserted)    | 0.6 V < V <sub>REF</sub> < 1.87 V |     | 104 |     | % of $V_{\text{REF}}$ |

| t <sub>ovpsdown</sub>                   | Time after OVP before protection activation and PGOOD fall |                                   |     | 55  | 95  | μs                    |

| M                                       | Undervoltage threshold (PGOOD deasserted)                  | 0.6 V < V <sub>REF</sub> < 1.87 V |     | 92  |     | % of $V_{\text{REF}}$ |

| V <sub>FB UVP</sub>                     | Undervoltage threshold (PGOOD asserted)                    | 0.6 V < V <sub>REF</sub> < 1.87 V |     | 83  |     | % of $V_{\text{REF}}$ |

| t <sub>UVPSDOWN</sub>                   | Time after UVP before PGOOD fall                           |                                   |     | 55  | 95  | μs                    |

(1) Specified by design

(2) Specified by lab validation

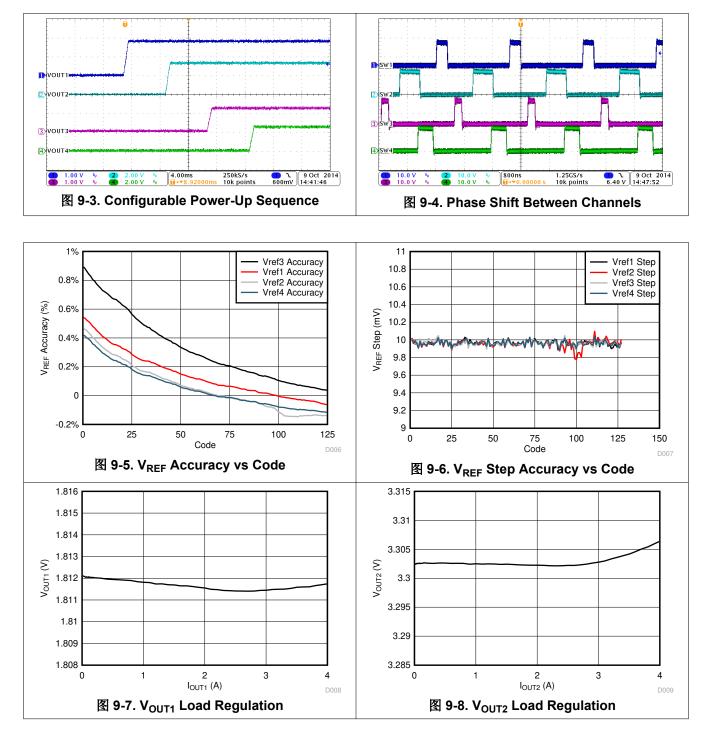

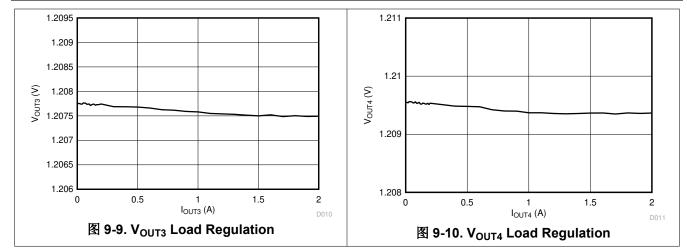

### 7.6 System Characteristics

The following specification table entries are specified by the design (component values provided in the typical application circuit are used). These parameters are not specified by production testing. minimum and max values apply over the full operating ambient temperature range ( $-40^{\circ}C \leq T_J \leq 125^{\circ}C$ ), over the V<sub>IN</sub> range = 5 to 12 V, and I<sub>OUT</sub> range unless otherwise specified. L = 3.3 µH, DCR = 10.4 m  $\Omega$ , V<sub>OUT</sub> = 1.2 V, 1% FB resistor.

|                                   | PARAMETER                                                                            | TEST CONDITIONS                                                          | MIN   | TYP | MAX | UNIT |

|-----------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|-----|-----|------|

| V <sub>LINEREG</sub>              | Line regulation                                                                      |                                                                          |       | 0.1 |     | %/V  |

| V <sub>LOADREG</sub>              | Load regulation                                                                      |                                                                          |       | 0.1 |     | %/A  |

| t <sub>r</sub>                    | VOUT step duration (t <sub>r</sub> )                                                 | For 50-mV step                                                           |       | 30  |     | μs   |

| t <sub>s</sub>                    | VOUT step settling time $(t_s)$                                                      | For 50-mV step                                                           |       | 30  |     | μs   |

| V <sub>OVUV</sub>                 | VOUT step overshoot/undershoot                                                       | For 50-mV step                                                           |       | 6   |     | mV   |

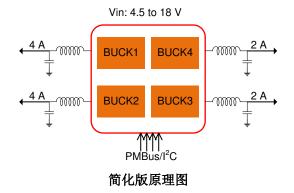

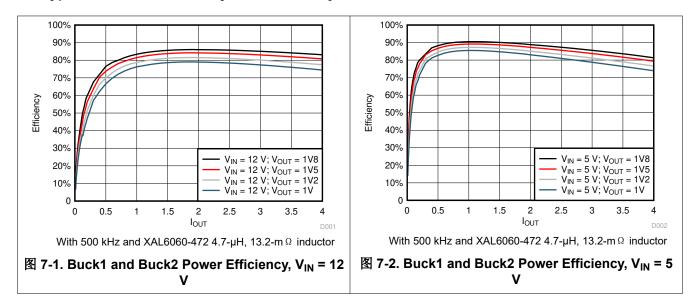

|                                   |                                                                                      | $V_{IN} = 5 V, V_O = 1.2 V, I_{OUT} = 4 A, f_{sw} = 500 \text{ kHz}$     |       | 77% |     |      |

|                                   | Efficiency (SW1 and SW2)                                                             | $V_{IN}$ = 12 V, $V_{O}$ = 1.2 V, $I_{OUT}$ = 4 A,<br>$f_{sw}$ = 500 kHz |       | 76% |     |      |

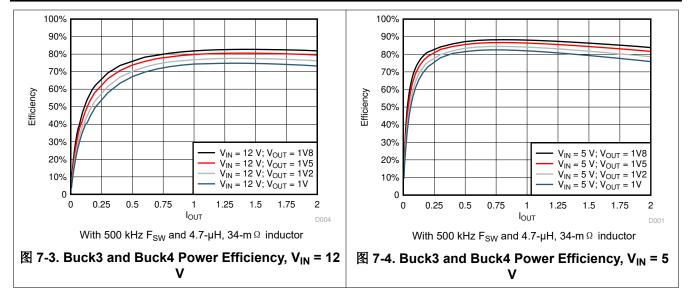

|                                   | Efficiency (SM/2 and SM/4)                                                           | $V_{IN} = 5 V, V_O = 1.2 V, I_{OUT} = 2 A, f_{sw} = 500 \text{ kHz}$     |       | 77% |     |      |

|                                   | Efficiency (SW3 and SW4)                                                             | $V_{IN}$ = 12 V, $V_{O}$ = 1.2 V, $I_{OUT}$ = 2 A,<br>$f_{sw}$ = 500 kHz |       | 74% |     |      |

| IOUT <sub>match</sub>             | Average ( <sup>(1)</sup> ) current sharing<br>accuracy (SW1 and SW2, SW3 and<br>SW4) | I <sub>load</sub> = I <sub>OUTmax</sub>                                  |       | 20% |     |      |

| IPK <sub>match</sub>              | Peak current ( <sup>(2)</sup> ) sharing accuracy (SW1 and SW2, SW3 and SW4)          | I <sub>load</sub> = I <sub>OUTmax</sub>                                  |       |     | 20% |      |

| t <sub>acc</sub>                  | Timing accuracy for delays and restarts                                              |                                                                          | - 10% |     | 10% |      |

| t <sub>reset_delay</sub>          | Time after RSTn or CE is released for power sequence to begin                        | Default value                                                            |       | 1   |     | ms   |

| t <sub>reset_delay_max</sub><br>0 | Minimum delay after reset is<br>released for power sequence to<br>begin              | t <sub>reset_delay</sub> set to 0 ms                                     |       |     | 1.1 | ms   |

(1) Average current sharing accuracy is highly dependent on the matching of the inductor and capacitor.

(2) Peak current sharing accuracy refers to the max inductor current in each phase.

## 7.7 Operational Parameters

Values recommended that ensure proper system behavior

|                            | PARAMETER                                       | MIN | TYP MAX                  |     |

|----------------------------|-------------------------------------------------|-----|--------------------------|-----|

| C <sub>A</sub>             | Stabilization capacitor to be connected to VDDA |     | 4.7                      | μF  |

| C <sub>D</sub>             | Stabilization capacitor to be connected to VDDD |     | 3.3                      | μF  |

| C <sub>G</sub>             | Stabilization capacitor to be connected to VDDG |     | 10                       | μF  |

| Vin1, Vin2, Vin3, Vin4     | SW1 to SW4 input voltage                        | 4.5 | 18                       | 3 V |

| Vout1, Vout2, Vout3, Vout4 | SW1 to SW4 output voltage                       | 0.6 | 90% o<br>V <sub>it</sub> | -   |

### 7.8 Package Dissipation Ratings

| PACKAGE | R <sub>0 JA</sub> (°C/W) <sup>(1)</sup> | T <sub>A</sub> = 25°C | T <sub>A</sub> = 55°C | T <sub>A</sub> = 85°C |

|---------|-----------------------------------------|-----------------------|-----------------------|-----------------------|

| RGZ     | 29.8                                    | 4.5 W                 | 3.14 W                | 1.77 W                |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

#### 7.9 Typical Characteristics: System Efficiency

# 8 Detailed Description

## 8.1 Overview

The TPS65400 is an integrated PMU optimized for applications that require small form factor and high-power conversion efficiency enabling small space-constrained equipment with high-ambient operating temperature without cooling. It provides high-power efficiency at a system level by enabling a single-stage conversion from an intermediate distribution bus with an optimized combination of regulators.

The TPS65400 consists of four high-current buck-switching regulators (SW1, SW2, SW3, and SW4) with integrated FETs. The switching power supplies are intended for powering high-current digital circuits such as the processor, FPGA, ASIC, memory, and digital I/Os. SW1 and SW2 support 4 A each, and SW3 and SW4 support 2 A each. Each regulator's switching frequency is independently adjustable up to 2.2 MHz.

Current limit programmability on each switcher enables optimization of inductor ratings for a particular application configuration not requiring the maximum current capability.

The TPS65400 can be powered from a single-input voltage rail between 4.5 and 18 V, making it suitable for applications running off a 5- or 12-V intermediate power distribution bus.

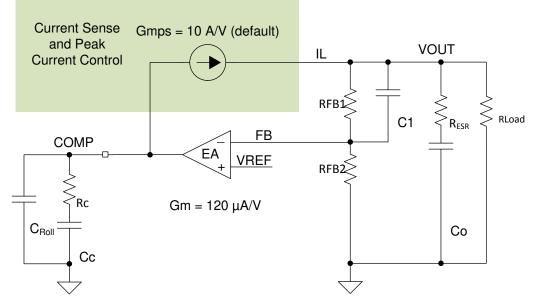

Sequencing requirements can be met using the individual enable pins or by programming the sequence through the  $I^2C$  bus into the onboard EEPROM. Output voltages can be set through external resistor networks and VREF can be programmed from 0.6 to 1.87 V in 10-mV steps. All control and status info can be accessed through a PMBus-compatible  $I^2C$  bus.

The TPS65400 provides a high level of flexibility for monitoring and control through the  $I^2C$  bus while providing the option of programmability through the use of external components and voltage levels for systems not using  $I^2C$ .

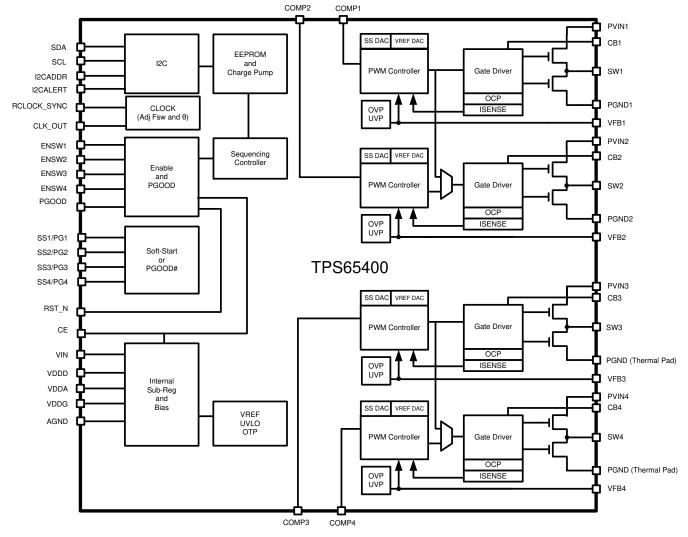

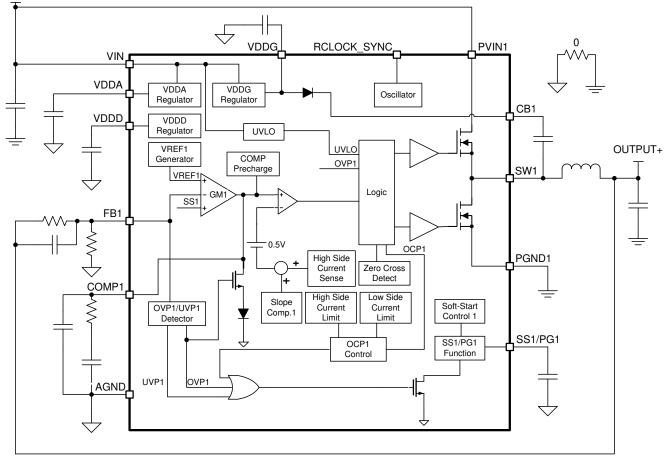

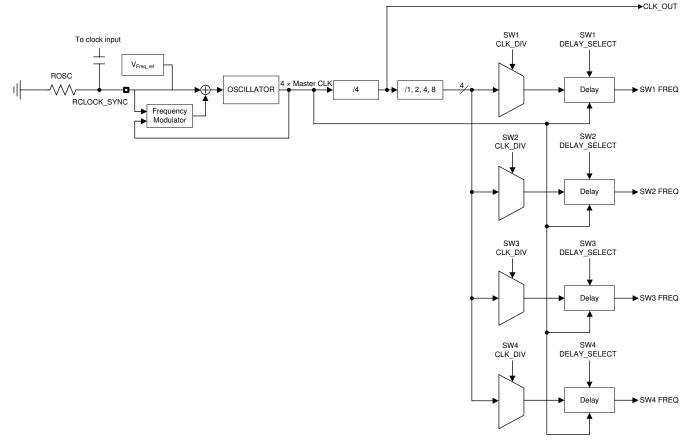

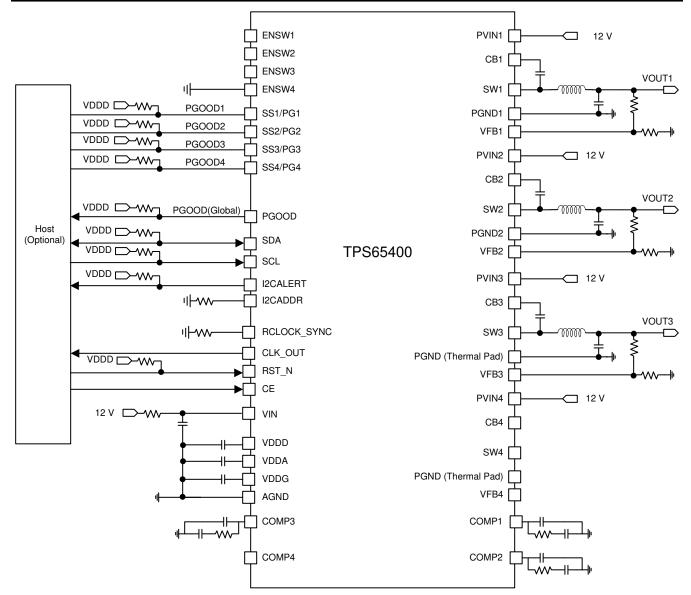

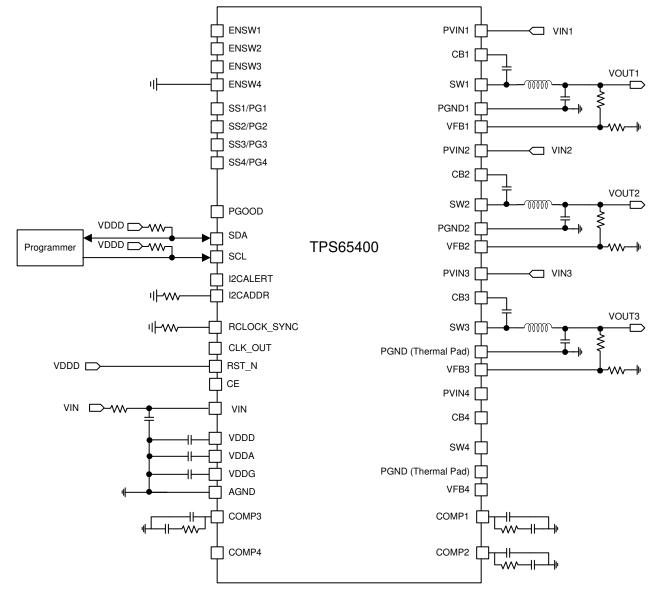

### 8.2 Functional Block Diagrams

图 8-1. TPS65400 Functional Block Diagram

#### TPS65400 ZHCSD04E - NOVEMBER 2014 - REVISED MARCH 2022

#### INPUT+

A. All other switchers follow the same pattern

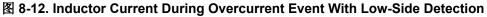

## 8.3 Feature Description

## 8.3.1 Startup Timing and Power Sequencing

### 8.3.1.1 Startup Timing

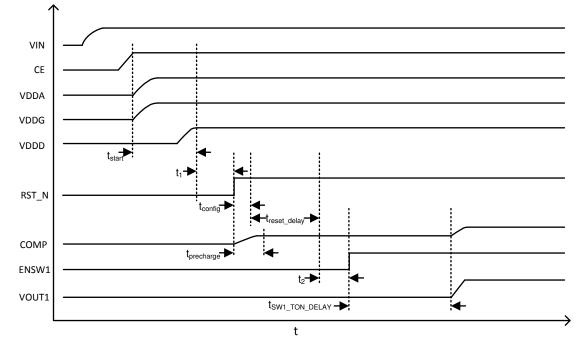

$[\mbox{8-3}]$  shows the startup timing of the TPS65400. Upon power-up or the rising edge of CE, the internal power rails VDDA, VDDG, and VDDD startup during the time labeled t<sub>start</sub>. Following t<sub>start</sub>, a delay of t<sub>1</sub> follows (which is defined by the user through the timing of RST\_N). During time t<sub>start</sub> and t<sub>1</sub>, the COMP terminal is internally discharged through a 2-k  $\Omega$  resistor. At the rising edge of RST\_N, the TPS65400 begins two actions:

- 1. The TPS65400 begins its precharge of the COMP terminal (indicated by t<sub>precharge</sub>). The length of t<sub>precharge</sub> needed to precharge the COMP terminal depends on the time constant of the R and C components. The internal precharge voltage source remains on even during normal operation, preventing the COMP terminal from falling below 0.6 V except during faults (OVP, OCP, and so forth).

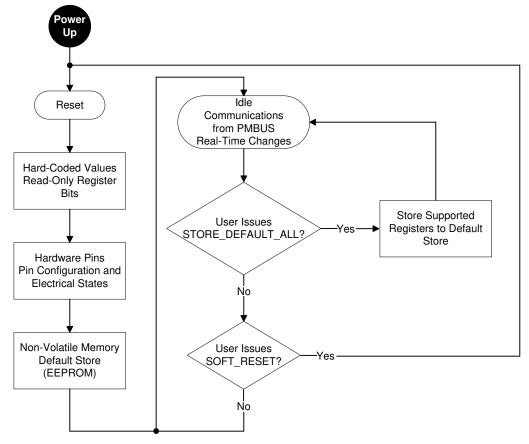

- 2. The TPS65400 begins its configuration sequence (indicated by t<sub>config</sub>), and loads parameters from the EEPROM. Parameters to be set include Vout, switching frequency, soft-start timing, and current limit.

After  $t_{config}$  is complete,  $t_{reset\_delay}$  begins. The length of  $t_{reset\_delay}$  is user-configurable through PMBus register DCh. After  $t_{reset\_delay}$  is complete, the TPS65400 begins its startup sequence. The startup sequence is EEPROM-configurable, so any of the four switchers could be the first to startup with a configurable delay. In this particular example, SW1 is configured to startup first after a delay of  $t_{SW1\_TON\_DELAY}$ , which is configurable through PMBus register (DDh) TON\_TOFF\_DELAY.

A. PGOOD1 and ENSW2 are tied together externally, and t<sub>ON\_DELAY1</sub> and t<sub>ON\_DELAY2</sub> are configured through PMBus.

#### 图 8-3. Timing Showing Startup from CE

To summarize, the length of time from rising edge of CE to soft-start of the first switcher in the sequence is:

$$t_{CE \text{ to } SS} = t_{\text{start}} + t_1 + t_{\text{config}} + t_{\text{reset delay}} + t_2 + t_{\text{SW1 ON DELAY}}$$

(1)

The delays,  $t_{reset\_delay}$  and  $t_{SW1\_ON\_DELAY}$ , are both configurable through PMBus. The delay,  $t_{config}$ , is typically 1.1 ms. The delays,  $t_1$  and  $t_2$ , are determined by the user-defined timing of RST\_N and ENSW1. They can both be set to 0 by pulling RST\_N high before the end of  $t_{start}$  and ENSW1 high before the end of  $t_{reset\_delay}$ . One simple way to do this would be to tie both signals to VDDD.

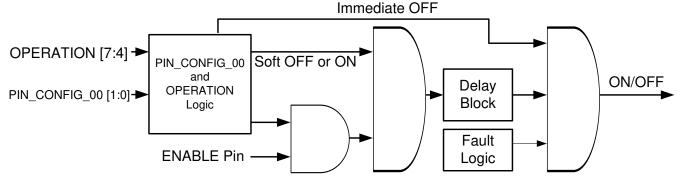

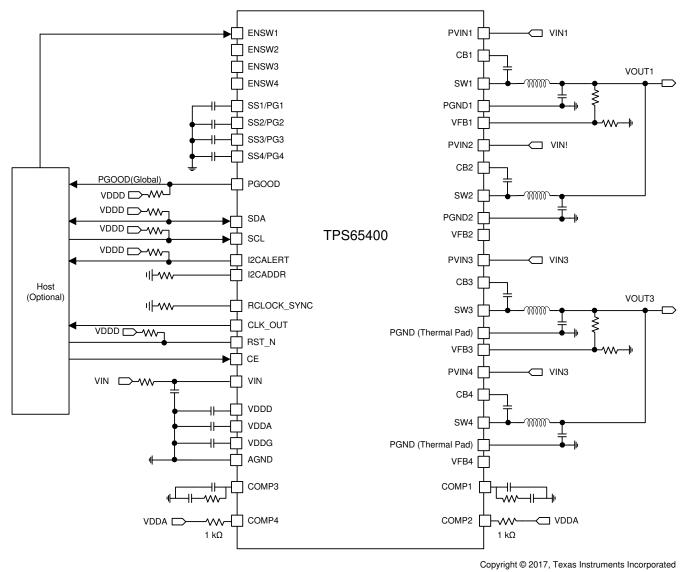

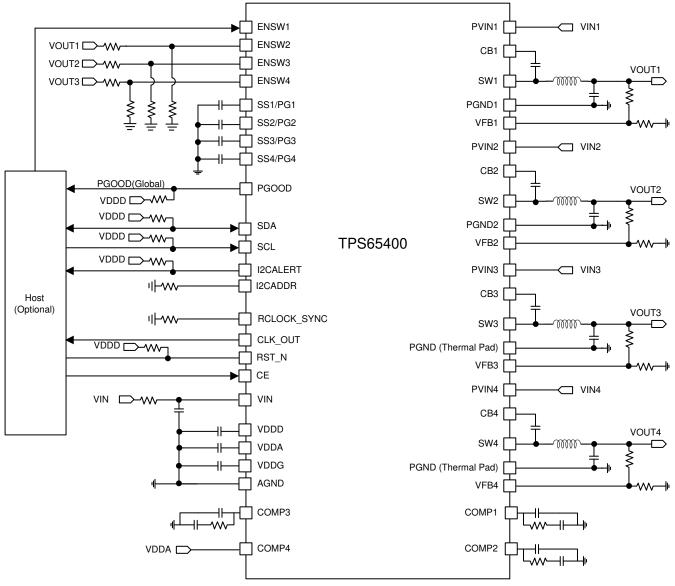

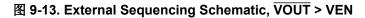

#### 8.3.1.2 External Sequencing

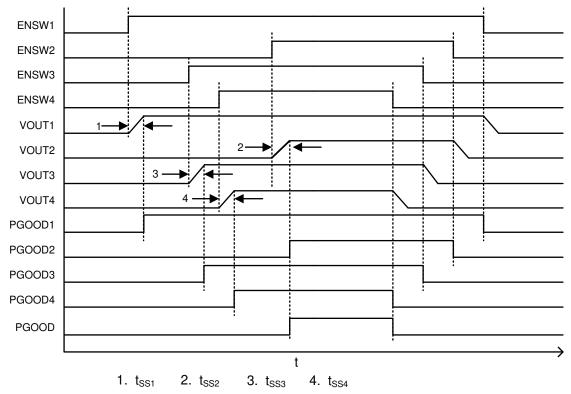

To use external sequencing, either connect all the enable pins (ENSW1, ENSW2, ENSW3, and ENSW4) to an external sequencing controller, or connect them to PGOOD outputs as shown in  $\boxtimes$  8-4. By default, t<sub>ON\_DELAY</sub> and t<sub>OFF\_DELAY</sub> are both set to 5 ms. This allows the user complete flexibility of sequencing order and timing with the ENSWx pins without modifying any of the default settings in the TPS65400.

A. Default behavior (external sequencing)

### 图 8-4. Example of Sequencing Where Timing is Controlled by an External Sequencer With ENSWx Pins

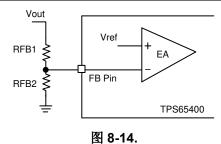

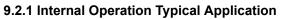

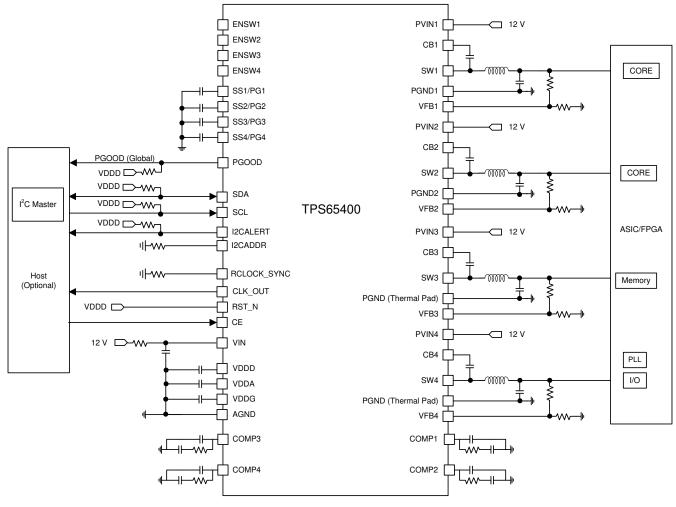

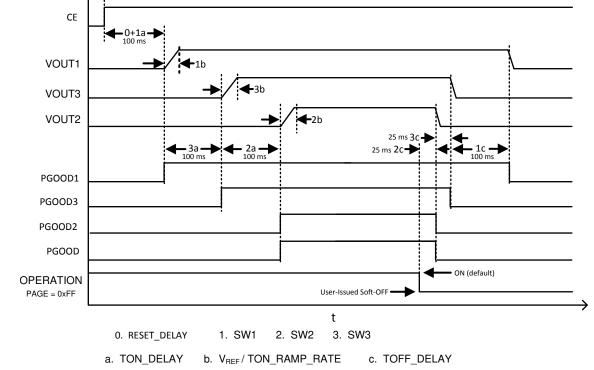

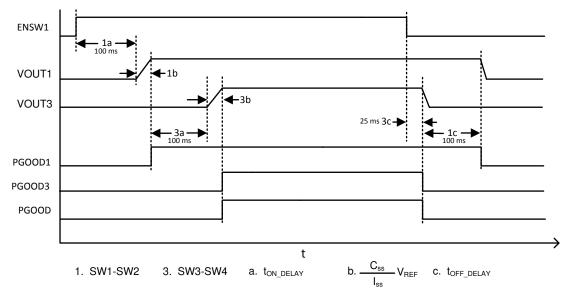

### 8.3.1.3 Internal Sequencing

The default settings for SEQUENCE\_ORDER (see (*D5h SEQUENCE\_ORDER*)) effectively disable sequencing by setting all switchers to start at the same time. Therefore, to use internal sequencing, the default values for SEQUENCE\_ORDER must be changed to the desired sequence. In addition, the user can configure the start or stop sequence to have a dependence on the PGOOD output of the previous switcher, or to wait for a set delay. If configured to have a dependence on PGOOD, the soft-start for the next switcher begins after PGOOD of the previous goes high and the wait time determined by  $t_{ON_DELAY}$  is complete. If configured to wait for a set delay, the wait time determined by  $t_{ON_DELAY}$  begins immediately upon the enabling of the previous switcher.

In addition, each supply can be disabled such that it is bypassed in the power-up sequence. For example, if the sequence is SW1-SW2-SW3-SW4, and SW2 is disabled, then SW3 will be powered up after SW1. The initial configuration of the TPS65400 (for first-time power-up) needs to be done using one of the methods described in  $\ddagger 8.3.14$ .

### 8.3.2 UVLO and Precision Enables

The TPS65400 implements a UVLO function that prevents startup when the voltage at VIN (terminal 22) is below 4 V. In most applications, VIN and all of the power rails (PVIN1, PVIN2, PVIN3, and PVIN4) are tied to the same source and this single UVLO function is sufficient. However, in some applications, the power rails may be tied to different input voltages, and there is the possibility that the TPS65400 may attempt to startup a switcher even when its associated PVINx rail has not reached a high-enough voltage. In these cases, the precision enable threshold on each ENSWx can be used to precisely set the startup threshold for each individual switcher with a simple resistor divider to PVINx.

In cases where a single UVLO threshold is needed for all four switchers, but at a different level than 4 V, the TPS65400 can be configured for single-terminal enable (PMBus register D2h, bits 0:1 = 10) where the ENSW1/ ENSEQ terminal is used as a sequence enable terminal. Then, a resistor divider to the appropriate PVINx rail can be used to set a precise UVLO threshold that applies to all four switchers.

#### 8.3.3 Soft-Start and Prebiased Startup

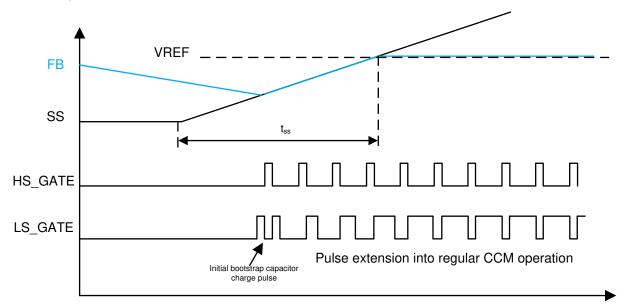

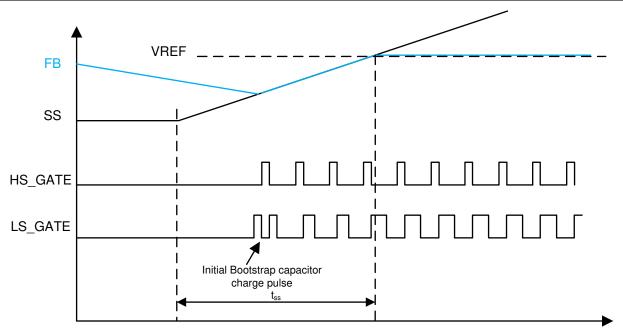

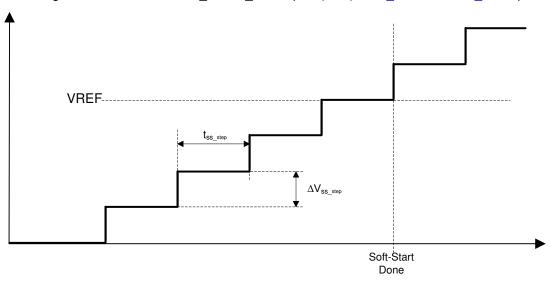

The TPS65400 implements a soft-start function that minimizes discharge of the output when starting up in a prebiased condition. Soft-start time,  $t_{SS}$ , is set by  $t_{ON\_TRANSITION\_RATE}$  (digital soft-start) or by a capacitor connected to the corresponding SSx pin (analog soft-start). In this setup, the SSx pin sources a 5-µA current charging the capacitor, and the voltage at the SSx pin limits the reference voltage at the input of the error amplifier.

At the beginning of the soft-start, the soft-start input to the error amplifier is set to 0. The SSx input is raised gradually and reaches its target value during the time  $t_{ss}$ . If  $V_{FB} > V_{SS}$ , then no switching occurs. After the Soft-Start signal crosses VFB, the switching begins. The first switching pulse is on the low-side FET, which charges the high-side bootstrap capacitor. The unit runs in discontinuous conduction mode (DCM) with the zero-cross detector enabled on the low side (diode emulation). The high-side FET is pulsed according to the error amplifier output on the COMP pin. If the IC is configured for continuous conduction mode (CCM) operation (default), the low-side FET pulses gradually transition to normal CCM operation; at each successive switching cycle, the low-side gate pulse is gradually ramped until full synchronous switching occurs. At this point, the switcher enters normal CCM operation.

图 8-5. Soft-Start Under Prebiased Condition and CCM Mode Programmed

### 8.3.3.1 Analog Soft-Start (Default) and Digital Soft-Start