# LMH6505 Wideband, Low Power, Linear-in-dB, Variable Gain Amplifier

Check for Samples: LMH6505

#### FEATURES

- $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $R_F = 1 k\Omega$ ,  $R_G = 100\Omega$ ,  $R_L = 100\Omega$ ,  $A_V = A_{VMAX} = 9.4 V/V$ , Typical Values Unless Specified.

- -3 dB BW 150 MHz

- Gain Control BW 100 MHz

- Adjustment Range (<10 MHz) 80 dB

- Gain Matching (Limit) ±0.50 dB

- Supply Voltage Range 7V to 12V

- Slew Rate (Inverting) 1500 V/µs

- Supply Current (No Load) 11 mA

- Linear Output Current ±60 mA

- Output Voltage Swing ±2.4V

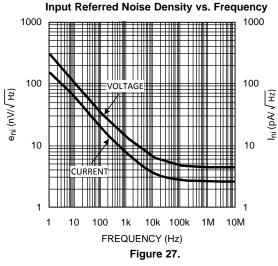

- Input Noise Voltage 4.4 nV/√Hz

- Input Noise Current 2.6 pA/√Hz

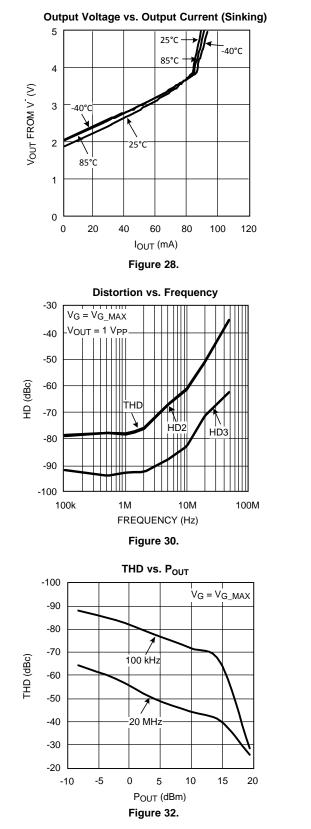

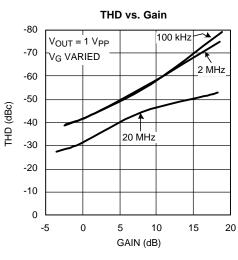

- THD (20 MHz,  $R_L = 100\Omega$ ,  $V_O = 2 V_{PP}$ ) -45 dBc

### **APPLICATIONS**

- Variable Attenuator

- AGC

- Voltage Controlled Filter

- Video Imaging Processing

### DESCRIPTION

The LMH6505 is a wideband DC coupled voltage controlled gain stage followed by a high speed current feedback operational amplifier which can directly drive a low impedance load. The gain adjustment range is 80 dB for up to 10 MHz which is accomplished by varying the gain control input voltage,  $V_{\rm G}$ .

Maximum gain is set by external components, and the gain can be reduced all the way to cutoff. Power consumption is 110 mW with a speed of 150 MHz and a gain control bandwidth (BW) of 100 MHz. Output referred DC offset voltage is less than 55 mV over the entire gain control voltage range. Device-todevice gain matching is within  $\pm 0.5$  dB at maximum gain. Furthermore, gain is tested and ensured over a wide range. The output current feedback op amp allows high frequency large signals (Slew Rate = 1500 V/µs) and can also drive a heavy load current (60 mA) ensured. Near ideal input characteristics (i.e. low input bias current, low offset, low pin 3 resistance) enable the device to be easily configured as an inverting amplifier as well.

To provide ease of use when working with a single supply, the  $V_G$  range is set to be from 0V to +2V relative to the ground pin potential (pin 4).  $V_G$  input impedance is high in order to ease drive requirement. In single supply operation, the ground pin is tied to a "virtual" half supply.

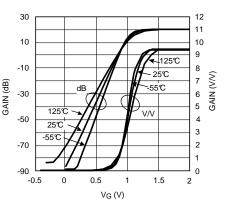

The LMH6505's gain control is linear in dB for a large portion of the total gain control range from 0 dB down to -85 dB at 25°C, as shown below. This makes the device suitable for AGC applications. For linear gain control applications, see the LMH6503 datasheet.

The LMH6505 is available in either the 8-Pin SOIC or the 8-Pin VSSOP package. The combination of minimal external components and small outline packages allows the LMH6505 to be used in spaceconstrained applications.

Figure 1. Gain vs. V<sub>G</sub>

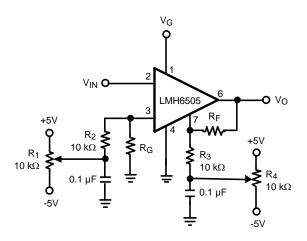

#### **Typical Application**

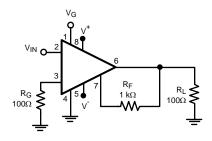

Figure 2.  $A_{VMAX} = 9.4 V/V$

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

### LMH6505

SNOSAT4E - DECEMBER 2005-REVISED APRIL 2013

www.ti.com

RUMENTS

XAS

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### Absolute Maximum Ratings<sup>(1)(2)</sup>

| ESD Tolerance <sup>(3)</sup>                       |                                            |

|----------------------------------------------------|--------------------------------------------|

| Human Body Model                                   | 2000V                                      |

| Machine Model                                      | 200V                                       |

| Input Current                                      | ±10 mA                                     |

| Output Current <sup>(4)</sup>                      | 120 mA                                     |

| Supply Voltages (V <sup>+</sup> - V <sup>-</sup> ) | 12.6V                                      |

| Voltage at Input/ Output pins                      | V <sup>+</sup> +0.8V, V <sup>-</sup> -0.8V |

| Storage Temperature Range                          | −65°C to 150°C                             |

| Junction Temperature                               | 150°C                                      |

| Soldering Information:                             |                                            |

| Infrared or Convection (20 sec)                    | 235°C                                      |

| Wave Soldering (10 sec)                            | 260°C                                      |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(4) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations or value specified, whichever is lower.

### Operating Ratings<sup>(1)</sup>

| Supply Voltages (V <sup>+</sup> - V <sup>-</sup> ) | 7V to 12V          |                    |

|----------------------------------------------------|--------------------|--------------------|

| Temperature Range <sup>(2)</sup>                   | −40°C to +85°C     |                    |

| Thermal Resistance:                                | (θ <sub>JC</sub> ) | (θ <sub>JA</sub> ) |

| 8 -Pin SOIC                                        | 60                 | 165                |

| 8-Pin VSSOP                                        | 65                 | 235                |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

www.ti.com

#### Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, all limits are ensured for  $T_J = 25^{\circ}C$ ,  $V_S = \pm 5V$ ,  $A_{VMAX} = 9.4 \text{ V/V}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = \pm 0.1V$ ,  $R_L = 100\Omega$ ,  $V_G = +2V$ . **Boldface** limits apply at the temperature extremes.

| Symbol                                                                         | Parameter                | Conditions                                                | Min<br>(2) | Тур<br>(3) | Max<br>(2) | Units |

|--------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------|------------|------------|------------|-------|

| Frequency                                                                      | Domain Response          |                                                           |            |            | l          |       |

| BW                                                                             | -3 dB Bandwidth          | $V_{OUT} < 1 V_{PP}$                                      |            | 150        |            |       |

|                                                                                |                          | $V_{OUT} < 4 V_{PP}, A_{VMAX} = 100$                      |            | 38         |            | MHz   |

| GF                                                                             | Gain Flatness            | $V_{OUT} < 1 V_{PP}$<br>0.9V $\leq V_G \leq 2V$ , ±0.2 dB |            | 40         |            | MHz   |

| Att Range Flat Band (Relative to Max Gain)<br>Attenuation Range <sup>(4)</sup> |                          | ±0.2 dB Flatness, f < 30 MHz                              |            | 26         |            | dB    |

|                                                                                |                          | ±0.1 dB Flatness, f < 30 MHz                              |            | 9.5        |            | UD UD |

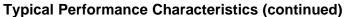

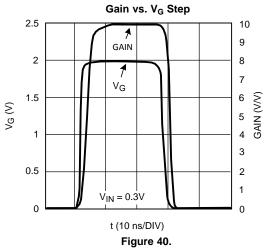

| BW<br>Control                                                                  | Gain control Bandwidth   | $V_{\rm G} = 1V^{(5)}$                                    |            | 100        |            | MHz   |

| CT (dB)                                                                        | Feed-through             | V <sub>G</sub> = 0V, 30 MHz<br>(Output/Input)             |            | -51        |            | dB    |

| GR                                                                             | Gain Adjustment Range    | justment Range f < 10 MHz                                 |            |            |            |       |

|                                                                                |                          |                                                           | 71         |            | dB         |       |

| Time Dom                                                                       | ain Response             | •                                                         |            |            |            |       |

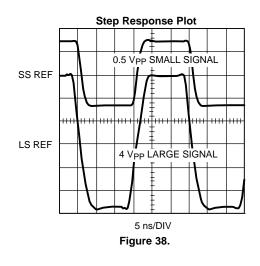

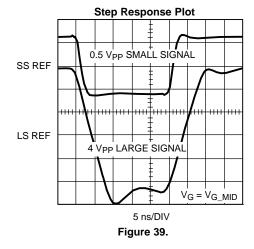

| t <sub>r</sub> , t <sub>f</sub>                                                | Rise and Fall Time       | 0.5V Step                                                 |            | 2.1        |            | ns    |

| OS %                                                                           | Overshoot                |                                                           |            | 10         |            | %     |

| SR                                                                             | Slew Rate <sup>(6)</sup> | Non Inverting                                             |            | 900        |            | 1///  |

|                                                                                |                          | Inverting                                                 |            | 1500       |            | V/µs  |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No ensured specification of parametric performance is indicated in the Electrical Tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using the Statistical Quality Control (SQC) method.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(4) Flat Band Attenuation (Relative To Max Gain) Range Definition: Specified as the attenuation range from maximum which allows gain flatness specified (either ±0.2 dB or ±0.1 dB), relative to A<sub>VMAX</sub> gain. For example, for f < 30 MHz, here are the Flat Band Attenuation ranges:</p>

$\pm 0.2$  dB: 19.7 dB down to -6.3 dB = 26 dB range

±0.1 dB: 19.7 dB down to 10.2 dB = 9.5 dB range

(5) Gain control frequency response schematic:

(6) Slew rate is the average of the rising and falling slew rates.

www.ti.com

STRUMENTS

EXAS

### Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are ensured for  $T_J = 25^{\circ}C$ ,  $V_S = \pm 5V$ ,  $A_{VMAX} = 9.4 \text{ V/V}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = \pm 0.1V$ ,  $R_L = 100\Omega$ ,  $V_G = +2V$ . **Boldface** limits apply at the temperature extremes.

| Symbol                | Parameter                                        | Conditions                              | Min<br>(2)            | Тур<br>(3) | Max<br>(2)           | Units              |

|-----------------------|--------------------------------------------------|-----------------------------------------|-----------------------|------------|----------------------|--------------------|

| Distortion            | & Noise Performance                              |                                         |                       |            | I                    |                    |

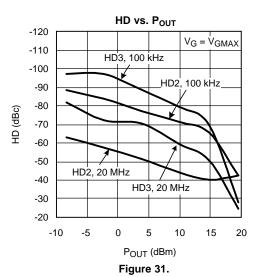

| HD2                   | 2 <sup>nd</sup> Harmonic Distortion              | 2V <sub>PP</sub> , 20 MHz               |                       | -47        |                      |                    |

| HD3                   | 3 <sup>rd</sup> Harmonic Distortion              |                                         |                       | -61        |                      | dBc                |

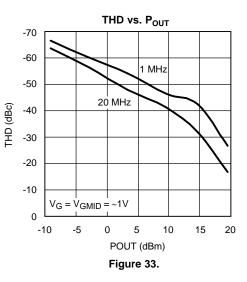

| THD                   | Total Harmonic Distortion                        |                                         |                       | -45        |                      |                    |

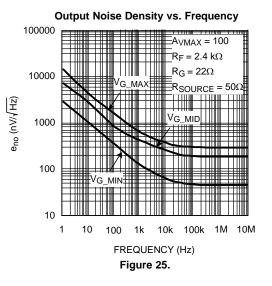

| En tot                | Total Equivalent Input Noise                     | $f > 1 MHz, R_{SOURCE} = 50\Omega$      |                       | 4.4        |                      | nV/√ <del>Hz</del> |

| I <sub>N</sub>        | Input Noise Current                              | f > 1 MHz                               |                       | 2.6        |                      | pA/√Hz             |

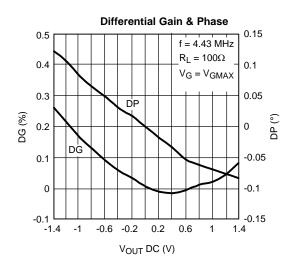

| DG                    | Differential Gain                                | f = 4.43 MHz, R <sub>L</sub> = 100Ω     |                       | 0.30       |                      | %                  |

| DP                    | Differential Phase                               |                                         |                       | 0.15       |                      | deg                |

| DC & Misc             | ellaneous Performance                            |                                         |                       |            |                      |                    |

| GACCU                 | Gain Accuracy                                    | $V_{G} = 2.0 V$                         |                       | 0          | ±0.50                |                    |

|                       | (See Application Information)                    | 0.8V < V <sub>G</sub> < 2V              |                       | +0.1/-0.53 | +4.3/-3.9            | dB                 |

| G Match               | Gain Matching                                    | V <sub>G</sub> = 2.0V                   |                       | _          | ±0.50                |                    |

|                       | (See Application Information)                    | 0.8V < V <sub>G</sub> < 2V              |                       | _          | +4.2/-4.0            | dB                 |

| К                     | Gain Multiplier<br>(See Application Information) |                                         | 0.890<br><b>0.830</b> | 0.940      | 0.990<br><b>1.04</b> | V/V                |

| V <sub>IN</sub> NL    | Input Voltage Range                              | R <sub>G</sub> Open                     |                       | ±3         |                      |                    |

| V <sub>IN</sub> L     |                                                  | R <sub>G</sub> = 100Ω                   | ±0.60<br><b>±0.50</b> | ±0.74      |                      | V                  |

| I <sub>RG_MAX</sub>   | R <sub>G</sub> Current                           | Pin 3                                   | ±6.0<br><b>±5.0</b>   | ±7.4       |                      | mA                 |

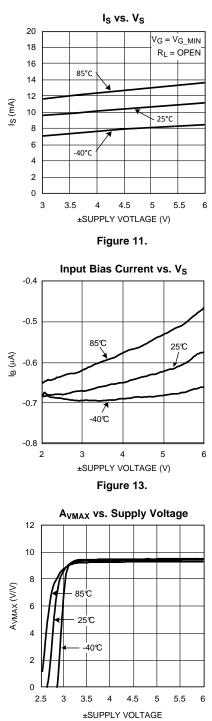

| I <sub>BIAS</sub>     | Bias Current                                     | Pin 2 <sup>(7)</sup>                    |                       | -0.6       | -2.5<br><b>-2.6</b>  | μA                 |

| TC I <sub>BIAS</sub>  | Bias Current Drift                               | Pin 2 <sup>(8)</sup>                    |                       | 1.28       |                      | nA/°C              |

| R <sub>IN</sub>       | Input Resistance                                 | Pin 2                                   |                       | 7          |                      | MΩ                 |

| C <sub>IN</sub>       | Input Capacitance                                | Pin 2                                   |                       | 2.8        |                      | pF                 |

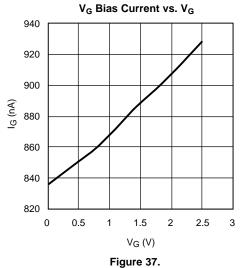

| I <sub>VG</sub>       | V <sub>G</sub> Bias Current                      | Pin 1, $V_{G} = 2V^{(7)}$               |                       | 0.9        |                      | μA                 |

| TC I <sub>VG</sub>    | V <sub>G</sub> Bias Drift                        | Pin 1 <sup>(8)</sup>                    |                       | 10         |                      | pA/°C              |

| R <sub>VG</sub>       | V <sub>G</sub> Input Resistance                  | Pin 1                                   |                       | 25         |                      | MΩ                 |

| C <sub>VG</sub>       | V <sub>G</sub> Input Capacitance                 | Pin 1                                   |                       | 2.8        |                      | pF                 |

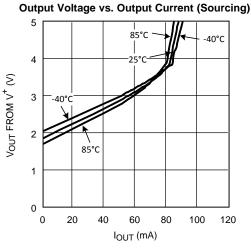

| V <sub>OUT</sub> L    | Output Voltage Range                             | $R_L = 100\Omega$                       | ±2.1<br><b>±1.9</b>   | ±2.4       |                      | V                  |

| V <sub>OUT</sub> NL   |                                                  | R <sub>L</sub> = Open                   |                       | ±3.1       |                      |                    |

| R <sub>OUT</sub>      | Output Impedance                                 | DC                                      |                       | 0.12       |                      | Ω                  |

| I <sub>OUT</sub>      | Output Current                                   | $V_{OUT} = \pm 4V$ from Rails           | ±60<br><b>±40</b>     | ±80        |                      | mA                 |

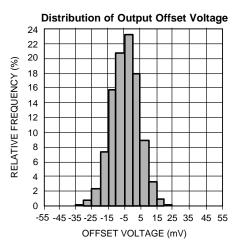

| V <sub>O OFFSET</sub> | Output Offset Voltage                            | 0V < V <sub>G</sub> < 2V                |                       | ±10        | ±55<br><b>±70</b>    | mV                 |

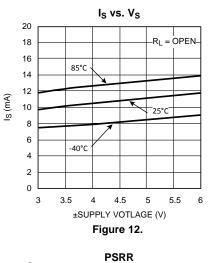

| +PSRR                 | +Power Supply Rejection Ratio                    | Input Referred, 1V change, $V_G = 2.2V$ | -65                   | -72        |                      | dB                 |

| -PSRR                 | -Power Supply Rejection Ratio                    | Input Referred, 1V change, $V_G = 2.2V$ | -65                   | -75        |                      | dB                 |

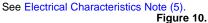

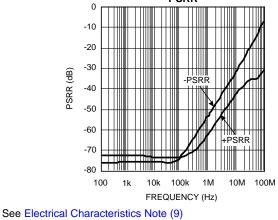

| I <sub>S</sub>        | Supply Current                                   | No Load                                 | 9.5<br><b>7.5</b>     | 11         | 14<br><b>16</b>      | mA                 |

(7)

Positive current corresponds to current flowing into the device. Drift is determined by dividing the change in parameter distribution at temperature extremes by the total temperature change. (8)

+PSRR definition:  $[|\Delta V_{OUT}/\Delta V^+| / A_V]$ , -PSRR definition:  $[|\Delta V_{OUT}/\Delta V^-| / A_V]$  with 0.1V input voltage.  $\Delta V_{OUT}$  is the change in output voltage with offset shift subtracted out. (9)

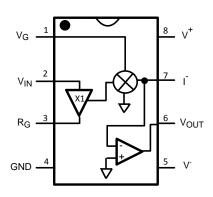

**Connection Diagram**

Figure 3. 8-Pin SOIC/VSSOP Top View

www.ti.com

#### **Typical Performance Characteristics**

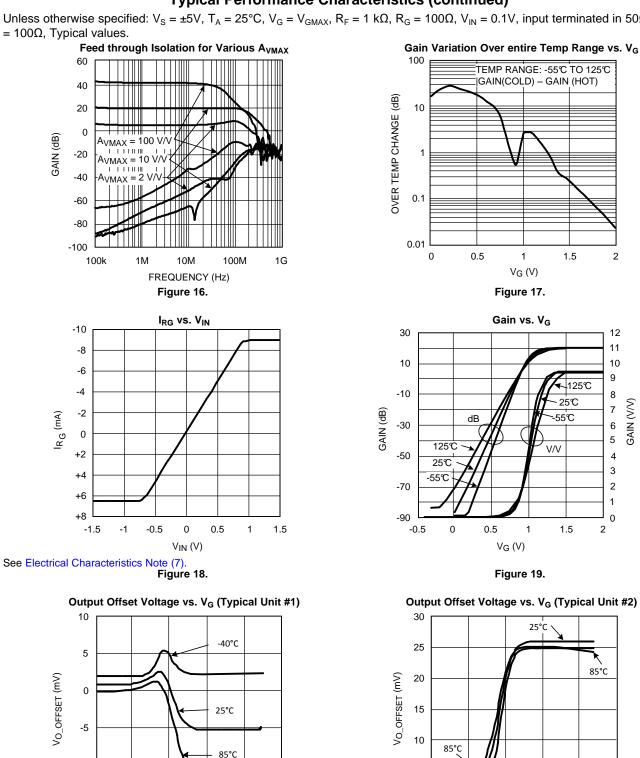

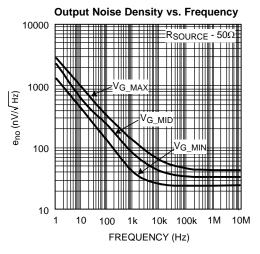

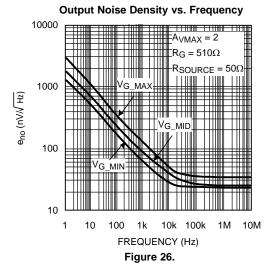

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 k\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L = 100\Omega$ , Typical values.

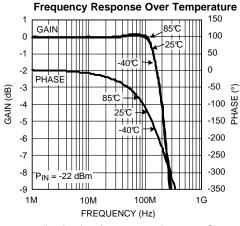

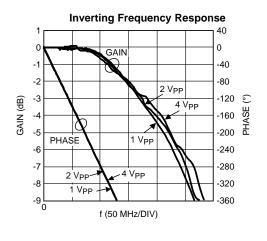

Gain/Phase normalized to low frequency value at 25°C. Figure 4.

f (50 MHz/DIV)

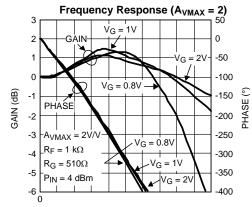

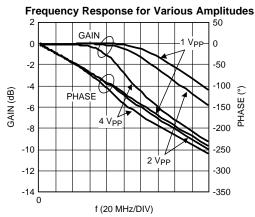

Gain/Phase normalized to low frequency value at each setting. Figure 6.

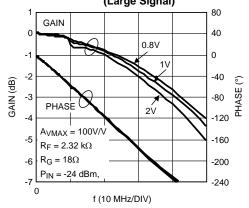

Gain/Phase normalized to low frequency value at each setting. Figure 8.

Gain/Phase normalized to low frequency value at each setting. Figure 5.

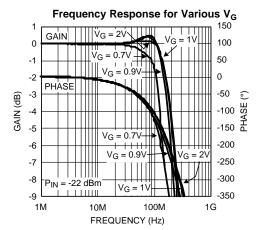

Gain/Phase normalized to low frequency value at each setting. Figure 9.

### SNOSAT4E – DECEMBER 2005 – REVISED APRIL 2013

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L = 100\Omega$ , Typical values.

Figure 15.

2

12 11

10

9

8

6

5

4

3

2

1

0 2

2.5

GAIN (V/V) 7

www.ti.com

#### **Typical Performance Characteristics (continued)**

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L$ =  $100\Omega$ , Typical values.

-10

-15

8

0

0.5

1

1.5

$V_{G}(V)$

Figure 20.

2

2.5

Copyright © 2005–2013, Texas Instruments Incorporated

2

1.5

$V_{G}(V)$

Figure 21.

-40°C

1

0.5

5

0 0

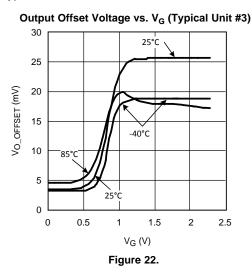

# Typical Performance Characteristics (continued)

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L = 100\Omega$ , Typical values.

SNOSAT4E - DECEMBER 2005 - REVISED APRIL 2013

Figure 23.

www.ti.com

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L = 100\Omega$ , Typical values.

Figure 29.

# SNOSAT4E – DECEMBER 2005 – REVISED APRIL 2013

Figure 35.

www.ti.com

### **Typical Performance Characteristics (continued)**

Unless otherwise specified:  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_G = V_{GMAX}$ ,  $R_F = 1 \text{ k}\Omega$ ,  $R_G = 100\Omega$ ,  $V_{IN} = 0.1V$ , input terminated in 50 $\Omega$ .  $R_L = 100\Omega$ , Typical values.

#### **GENERAL DESCRIPTION**

The key features of the LMH6505 are:

Low power

www.ti.com

- Broad voltage controlled gain and attenuation range (from A<sub>VMAX</sub> down to complete cutoff)

- Bandwidth independent, resistor programmable gain range (R<sub>G</sub>)

- Broad signal and gain control bandwidths

- Frequency response may be adjusted with R<sub>F</sub>

- High impedance signal and gain control inputs

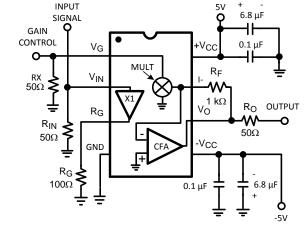

The LMH6505 combines a closed loop input buffer ("X1" Block in Figure 41), a voltage controlled variable gain cell ("MULT" Block) and an output amplifier ("CFA" Block). The input buffer is a transconductance stage whose gain is set by the gain setting resistor, R<sub>G</sub>. The output amplifier is a current feedback op amp and is configured as a transimpedance stage whose gain is set by, and is equal to, the feedback resistor, R<sub>F</sub>. The maximum gain, A<sub>VMAX</sub>, of the LMH6505 is defined by the ratio: K · R<sub>F</sub>/R<sub>G</sub> where "K" is the gain multiplier with a nominal value of 0.940. As the gain control input ( $V_G$ ) changes over its 0 to 2V range, the gain is adjusted over a range of about 80 dB relative to the maximum set gain.

Figure 41. LMH6505 Typical Application and Block Diagram

#### SETTING THE LMH6505 MAXIMUM GAIN

$$A_{VMAX} = \frac{R_F}{R_G} \cdot K$$

Although the LMH6505 is specified at  $A_{VMAX} = 9.4 V/V$ , the recommended  $A_{VMAX}$  varies between 2 and 100. Higher gains are possible but usually impractical due to output offsets, noise and distortion. When varying AVMAX several tradeoffs are made:

R<sub>G</sub>: determines the input voltage range

R<sub>F</sub>: determines overall bandwidth

The amount of current which the input buffer can source/sink into R<sub>G</sub> is limited and is given in the I<sub>RG MAX</sub> specification. This sets the maximum input voltage:

$$V_{IN}$$

(MAX) =  $I_{R_c MAX} \cdot R_G$

APPLICATION INFORMATION

SNOSAT4E - DECEMBER 2005 - REVISED APRIL 2013

(1)

ISTRUMENTS

As the  $I_{RG\_MAX}$  limit is approached with increasing the input voltage or with the lowering of  $R_G$ , the device's harmonic distortion will increase. Changes in  $R_F$  will have a dramatic effect on the small signal bandwidth. The output amplifier of the LMH6505 is a current feedback amplifier (CFA) and its bandwidth is determined by  $R_F$ . As with any CFA, doubling the feedback resistor will roughly cut the bandwidth of the device in half.

For more about CFAs, see the basic tutorial, OA-20, *Current Feedback Myths Debunked*, (literature number SNOA376), or a more rigorous analysis, OA-13, *Current Feedback Amplifier Loop Gain Analysis and Performance Enhancements*, (literature number SNOA366).

#### **OTHER CONFIGURATIONS**

1. Single Supply Operation

The LMH6505 can be configured for use in a single supply environment. Doing so requires the following:

- (a) Bias pin 4 and R<sub>G</sub> to a "virtual half supply" somewhere close to the middle of V<sup>+</sup> and V<sup>-</sup> range. The other end of R<sub>G</sub> is tied to pin 3. The "virtual half supply" needs to be capable of sinking and sourcing the expected current flow through R<sub>G</sub>.

- (b) Ensure that  $V_G$  can be adjusted from 0V to 2V above the "virtual half supply".

- (c) Bias the input (pin 2) to make sure that it stays within the range of 2V above V<sup>-</sup> to 2V below V<sup>+</sup>. See the Input Voltage Range specification in the Electrical Characteristics table. This can be accomplished by either DC biasing the input and AC coupling the input signal, or alternatively, by direct coupling if the output of the driving stage is also biased to half supply.

Arranged this way, the LMH6505 will respond to the current flowing through  $R_G$ . The gain control relationship will be similar to the split supply arrangement with  $V_G$  measured with reference to pin 4. Keep in mind that the circuit described above will also center the output voltage to the "virtual half supply voltage."

2. Arbitrarily Referenced Input Signal

Having a wide input voltage range on the input (pin 2) ( $\pm$ 3V typical), the LMH6505 can be configured to control the gain on signals which are not referenced to ground (e.g. Half Supply biased circuits). This node will be called the "reference node". In such cases, the other end of R<sub>G</sub> which is the side not tied to pin 3 can be tied to this reference node so that R<sub>G</sub> will "look at" the difference between the signal and this reference only. Keep in mind that the reference node needs to source and sink the current flowing through R<sub>G</sub>.

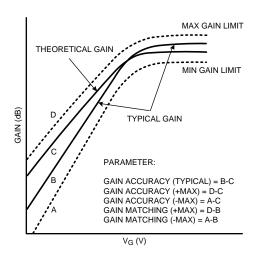

#### GAIN ACCURACY

Gain accuracy is defined as the actual gain compared against the theoretical gain at a certain  $V_G$ , the results of which are expressed in dB. (See Figure 42).

Theoretical gain is given by:

$$A(V/V) = K \quad x \frac{R_F}{R_G} \times \frac{1}{1 + e^{\left[\frac{N - V_G}{V_C}\right]}}$$

where

- K = 0.940 (nominal) N = 1.01V

- V<sub>C</sub> = 79 mV at room temperature

(3)

For a  $V_G$  range, the value specified in the tables represents the worst case accuracy over the entire range. The "Typical" value would be the difference between the "Typical Gain" and the "Theoretical Gain." The "Max" value would be the worst case difference between the actual gain and the "Theoretical Gain" for the entire population.

#### GAIN MATCHING

As Figure 42 shows, gain matching is the limit on gain variation at a certain  $V_G$ , expressed in dB, and is specified as "±Max" only. There is no "Typical." For a  $V_G$  range, the value specified represents the worst case matching over the entire range. The "Max" value would be the worst case difference between the actual gain and the typical gain for the entire population.

Figure 42. LMH6505 Gain Accuracy & Gain Matching Defined

#### GAIN PARTITIONING

If high levels of gain are needed, gain partitioning should be considered:

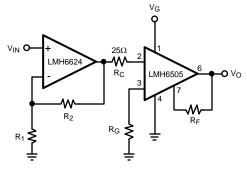

Figure 43. Gain Partitioning

The maximum gain range for this circuit is given by the following equation:

MAXIMUM GAIN =

$$\left[1 + \frac{R_2}{R_1}\right] \cdot \left[\frac{R_F}{R_G}\right] \cdot K$$

(4)

The LMH6624 is a low noise wideband voltage feedback amplifier. Setting  $R_2$  at 909 $\Omega$  and  $R_1$  at 100 $\Omega$  produces a gain of 20 dB. Setting  $R_F$  at 1000 $\Omega$  as recommended and  $R_G$  at 50 $\Omega$ , produces a gain of about 26 dB in the LMH6505. The total gain of this circuit is therefore approximately 46 dB. It is important to understand that when partitioning to obtain high levels of gain, very small signal levels will drive the amplifiers to full scale output. For example, with 46 dB of gain, a 20 mV signal at the input will drive the output of the LMH6624 to 200 mV and the output of the LMH6505 to 4V. Accordingly, the designer must carefully consider the contributions of each stage to the overall characteristics. Through gain partitioning time, and loading effects of each amplifier to achieve improved overall performance.

www.ti.com

#### LMH6505 GAIN CONTROL RANGE AND MINIMUM GAIN

Before discussing Gain Control Range, it is important to understand the issues which limit it. The minimum gain of the LMH6505 is theoretically zero, but in practical circuits it is limited by the amount of feedthrough, here defined as the gain when  $V_G = 0V$ . Capacitive coupling through the board and package, as well as coupling through the supplies, will determine the amount of feedthrough. Even at DC, the input signal will not be completely rejected. At high frequencies feedthrough will get worse because of its capacitive nature. At frequencies below 10 MHz, the feed through will be less than -60 dB and therefore, it can be said that with  $A_{VMAX} = 20$  dB, the gain control range is 80 dB.

#### LMH6505 GAIN CONTROL FUNCTION

In the plot, Gain vs.  $V_G$  (Figure 19), we can see the gain as a function of the control voltage. The "Gain (V/V)" plot, sometimes referred to as the S-curve, is the linear (V/V) gain. This is a hyperbolic tangent relationship and is given by Equation 3. The "Gain (dB)" plots the gain in dB and is linear over a wide range of gains. Because of this, the LMH6505 gain control is referred to as "linear-in-dB."

For applications where the LMH6505 will be used at the heart of a closed loop AGC circuit, the S-curve control characteristic provides a broad linear (in dB) control range with soft limiting at the highest gains where large changes in control voltage result in small changes in gain. For applications requiring a fully linear (in dB) control characteristic, use the LMH6505 at half gain and below ( $V_G \le 1V$ ).

#### GAIN STABILITY

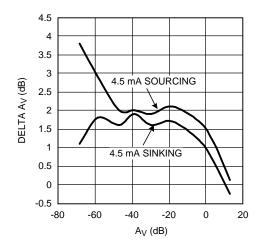

The LMH6505 architecture allows complete attenuation of the output signal from full gain to complete cutoff. This is achieved by having the gain control signal  $V_G$  "throttle" the signal which gets through to the final stage and which results in the output signal. As a consequence, the  $R_G$  pin's (pin 3) average current (DC current) influences the operating point of this "throttle" circuit and affects the LMH6505's gain slightly. Figure 44 below, shows this effect as a function of the gain set by  $V_G$ .

Figure 44. LMH6505 Gain Variation over R<sub>G</sub> DC Current Capability vs. Gain

This plot shows the expected gain variation for the maximum  $R_G$  DC current capability (±4.5 mA). For example, with gain ( $A_V$ ) set to -60 dB, if the  $R_G$  pin DC current is increased to 4.5 mA sourcing, one would expect to see the gain increase by about 3 dB (to -57 dB). Conversely, 4.5 mA DC sinking current through  $R_G$  would increase gain by 1.75 dB (to -58.25 dB). As you can see from Figure 44 above, the effect is most pronounced with reduced gain and is limited to less than 3.75 dB variation maximum.

If the application is expected to experience  $R_G$  DC current variation and the LMH6505 gain variation is beyond acceptable limits, please refer to the LMH6502 (Differential Linear in dB variable gain amplifier) datasheet instead at http://www.ti.com/lit/gpn/LMH6502.

#### SNOSAT4E – DECEMBER 2005 – REVISED APRIL 2013

#### AVOIDING OVERDRIVE OF THE LMH6505 GAIN CONTROL INPUT

There is an additional requirement for the LMH6505 Gain Control Input (V<sub>G</sub>): V<sub>G</sub> must not exceed +2.3V (with ±5V supplies). The gain control circuitry may saturate and the gain may actually be reduced. In applications where V<sub>G</sub> is being driven from a DAC, this can easily be addressed in the software. If there is a linear loop driving V<sub>G</sub>, such as an AGC loop, other methods of limiting the input voltage should be implemented. One simple solution is to place a 2.2:1 resistive divider on the V<sub>G</sub> input. If the device driving this divider is operating off of ±5V supplies as well, its output will not exceed 5V and through the divider V<sub>G</sub> can not exceed 2.3V.

#### **IMPROVING THE LMH6505 LARGE SIGNAL PERFORMANCE**

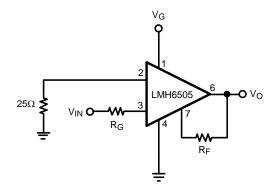

Figure 45 illustrates an inverting gain scheme for the LMH6505.

Figure 45. Inverting Amplifier

The input signal is applied through the  $R_G$  resistor. The  $V_{IN}$  pin should be grounded through a 25 $\Omega$  resistor. The maximum gain range of this configuration is given in the following equation:

$$A_{VMAX} = -\left[\frac{R_F}{R_G}\right] \cdot K$$

(5)

The inverting slew rate of the LMH6505 is much higher than that of the non-inverting slew rate. This  $\approx 2X$  performance improvement comes about because in the non-inverting configuration the slew rate of the overall amplifier is limited by the input buffer. In the inverting circuit, the input buffer remains at a fixed voltage and does not affect slew rate.

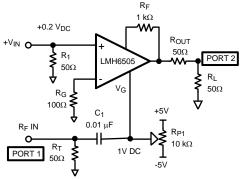

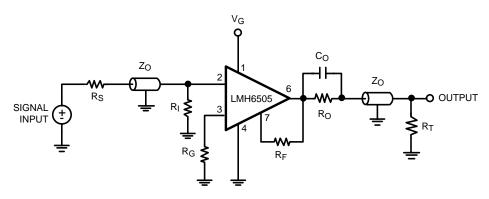

#### TRANSMISSION LINE MATCHING

One method for matching the characteristic impedance of a transmission line is to place the appropriate resistor at the input or output of the amplifier. Figure 46 shows a typical circuit configuration for matching transmission lines.

Figure 46. Transmission Line Matching

### LMH6505

SNOSAT4E - DECEMBER 2005-REVISED APRIL 2013

www.ti.com

The resistors  $R_S$ ,  $R_I$ ,  $R_O$ , and  $R_T$  are equal to the characteristic impedance,  $Z_O$ , of the transmission line or cable. Use  $C_O$  to match the output transmission line over a greater frequency range. It compensates for the increase of the op amp's output impedance with frequency.

#### MINIMIZING PARASITIC EFFECTS ON SMALL SIGNAL BANDWIDTH

The best way to minimize parasitic effects is to use surface mount components and to minimize lead lengths and component distance from the LMH6505. For designs utilizing through-hole components, specifically axial resistors, resistor self-capacitance should be considered. For example, the average magnitude of parasitic capacitance of RN55D 1% metal film resistors is about 0.15 pF with variations of as much as 0.1 pF between lots. Given the LMH6505's extended bandwidth, these small parasitic reactance variations can cause measurable frequency response variations in the highest octave. We therefore recommend the use of surface mount resistors to minimize these parasitic reactance effects.

#### RECOMMENDATIONS

Here are some recommendations to avoid problems and to get the best performance:

- Do not place a capacitor across R<sub>F</sub>. However, an appropriately chosen series RC combination can be used to shape the frequency response.

- Keep traces connecting R<sub>F</sub> separated and as short as possible.

- Place a small resistor (20-50Ω) between the output and C<sub>L</sub>.

- Cut away the ground plane, if any, under R<sub>G</sub>.

- Keep decoupling capacitors as close as possible to the LMH6505.

- Connect pin 2 through a minimum resistance of 25Ω.

#### ADJUSTING OFFSETS AND DC LEVEL SHIFTING

Offsets can be broken into two parts: an input-referred term and an output-referred term. These errors can be trimmed using the circuit in Figure 47. First set  $V_G$  to 0V and adjust the trim pot  $R_4$  to null the offset voltage at the output. This will eliminate the output stage offsets. Next set  $V_G$  to 2V and adjust the trim pot  $R_1$  to null the offset voltage at the voltage at the output. This will eliminate the input stage offsets.

Figure 47. Offset Adjust Circuit

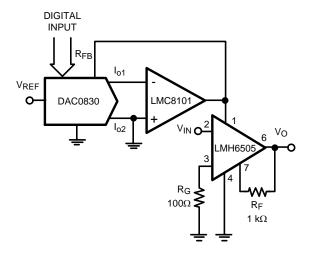

#### DIGITAL GAIN CONTROL

Digitally variable gain control can be easily realized by driving the LMH6505 gain control input with a digital-toanalog converter (DAC). Figure 48 illustrates such an application. This circuit employs TI's eight-bit DAC0830, the LMC8101 MOS input op amp (Rail-to-Rail Input/Output), and the LMH6505 VGA. With  $V_{REF}$  set to 2V, the circuit provides up to 80 dB of gain control in 256 steps with up to 0.05% full scale resolution. The maximum gain of this circuit is 20 dB.

SNOSAT4E - DECEMBER 2005 - REVISED APRIL 2013

Figure 48. Digital Gain Control

#### **USING THE LMH6505 IN AGC APPLICATIONS**

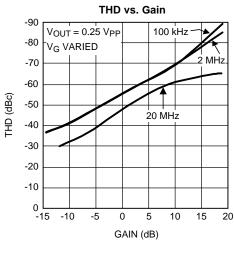

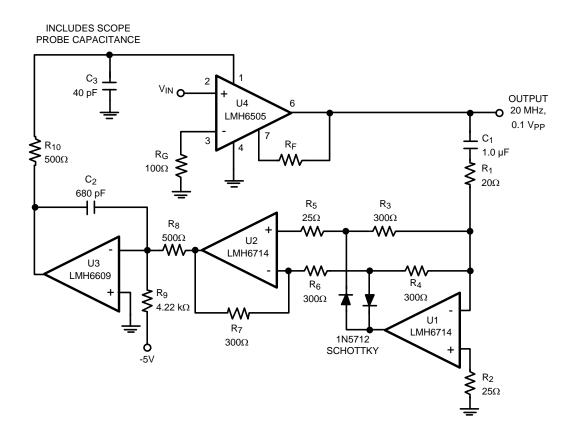

In AGC applications, the control loop forces the LMH6505 to have a fixed output amplitude. The input amplitude will vary over a wide range and this can be the issue that limits dynamic range. At high input amplitudes, the distortion due to the input buffer driving R<sub>G</sub> may exceed that which is produced by the output amplifier driving the load. In the plot, THD vs. Gain, total harmonic distortion (THD) is plotted over a gain range of nearly 35 dB for a fixed output amplitude of 0.25 V<sub>PP</sub> in the specified configuration,  $R_F = 1 k\Omega$ ,  $R_G = 100\Omega$ . When the gain is adjusted to -15 dB (i.e. 35 dB down from A<sub>VMAX</sub>), the input amplitude would be 1.41 V<sub>PP</sub> and we can see the distortion is at its worst at this gain. If the output amplitude of the AGC were to be raised above 0.25 V<sub>PP</sub>, the input amplitudes for gains 40 dB down from AVMAX would be even higher and the distortion would degrade further. It is for this reason that we recommend lower output amplitudes if wide gain ranges are desired. Using a post-amp like the LMH6714/LMH6720/LMH6722 family or the LMH6702 would be the best way to preserve dynamic range and yield output amplitudes much higher than 100 mV<sub>PP</sub>. Another way of addressing distortion performance and its limitations on dynamic range, would be to raise the value of R<sub>G</sub>. Just like any other highspeed amplifier, by increasing the load resistance, and therefore decreasing the demanded load current, the distortion performance will be improved in most cases. With an increased R<sub>G</sub>, R<sub>F</sub> will also have to be increased to keep the same AVMAX and this will decrease the overall bandwidth. It may be possible to insert a series RC combination across  $R_F$  in order to counteract the negative effect on BW when a large  $R_F$  is used.

#### AUTOMATIC GAIN CONTROL (AGC)

#### Fast Response AGC Loop

The AGC circuit shown in Figure 49 will correct a 6 dB input amplitude step in 100 ns. The circuit includes a two op amp precision rectifier amplitude detector (U1 and U2), and an integrator (U3) to provide high loop gain at low frequencies. The output amplitude is set by  $R_9$ . The following are some suggestions for building fast AGC loops: Precision rectifiers work best with large output signals. Accuracy is improved by blocking DC offsets, as shown in Figure 49.

www.ti.com

Figure 49. Automatic Gain Control Circuit

Signal frequencies must not reach the gain control port of the LMH6505, or the output signal will be distorted (modulated by itself). A fast settling AGC needs additional filtering beyond the integrator stage to block signal frequencies. This is provided in Figure 49 by a simple R-C filter ( $R_{10}$  and  $C_3$ ); better distortion performance can be achieved with a more complex filter. These filters should be scaled with the input signal frequency. Loops with slower response time, which means longer integration time constants, may not need the  $R_{10} - C_3$  filter.

Checking the loop stability can be done by monitoring the V<sub>G</sub> voltage while applying a step change in input signal amplitude. Changing the input signal amplitude can be easily done with an arbitrary waveform generator.

SNOSAT4E - DECEMBER 2005 - REVISED APRIL 2013

#### **CIRCUIT LAYOUT CONSIDERATIONS & EVALUATION BOARDS**

A good high frequency PCB layout including ground plane construction and power supply bypassing close to the package is critical to achieving full performance. The amplifier is sensitive to stray capacitance to ground at the l input (pin 7) so it is best to keep the node trace area small. Shunt capacitance across the feedback resistor should not be used to compensate for this effect. Capacitance to ground should be minimized by removing the ground plane from under the body of  $R_G$ . Parasitic or load capacitance directly on the output (pin 6) degrades phase margin leading to frequency response peaking.

The LMH6505 is fully stable when driving a 100 $\Omega$  load. With reduced load (e.g. 1k.) there is a possibility of instability at very high frequencies beyond 400 MHz especially with a capacitive load. When the LMH6505 is connected to a light load as such, it is recommended to add a snubber network to the output (e.g. 100 $\Omega$  and 39 pF in series tied between the LMH6505 output and ground). C<sub>L</sub> can also be isolated from the output by placing a small resistor in series with the output (pin 6).

Component parasitics also influence high frequency results. Therefore it is recommended to use metal film resistors such as RN55D or leadless components such as surface mount devices. High profile sockets are not recommended.

Texas Instruments suggests the following evaluation board as a guide for high frequency layout and as an aid in device testing and characterization:

| Device  | Package | Evaluation Board<br>Part Number |

|---------|---------|---------------------------------|

| LMH6505 | SOIC    | LMH730066                       |

### **REVISION HISTORY**

| Cł | hanges from Revision D (April 2013) to Revision E  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 21   |

Copyright © 2005–2013, Texas Instruments Incorporated

www.ti.com

#### **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                    |              |                         |         |

| LMH6505MA/NOPB   | ACTIVE        | SOIC         | D                  | 8    | 95             | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 85    | LMH65<br>05MA           | Samples |

| LMH6505MAX/NOPB  | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 85    | LMH65<br>05MA           | Samples |

| LMH6505MM/NOPB   | ACTIVE        | VSSOP        | DGK                | 8    | 1000           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 85    | AZ2A                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### PACKAGE OPTION ADDENDUM

10-Dec-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

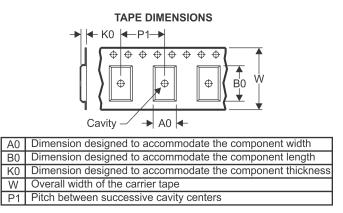

#### TAPE AND REEL INFORMATION

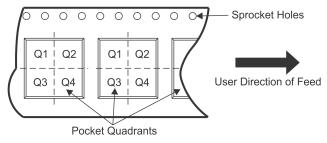

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMH6505MAX/NOPB             | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LMH6505MM/NOPB              | VSSOP           | DGK                | 8 | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

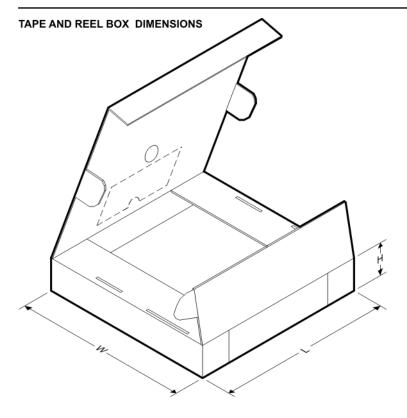

# PACKAGE MATERIALS INFORMATION

5-Jan-2022

\*All dimensions are nominal

| Device          | Package Type | Package Type Package Drawing |   | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|------------------------------|---|------|-------------|------------|-------------|

| LMH6505MAX/NOPB | SOIC         | D                            | 8 | 2500 | 367.0       | 367.0      | 35.0        |

| LMH6505MM/NOPB  | VSSOP        | DGK                          | 8 | 1000 | 208.0       | 191.0      | 35.0        |

5-Jan-2022

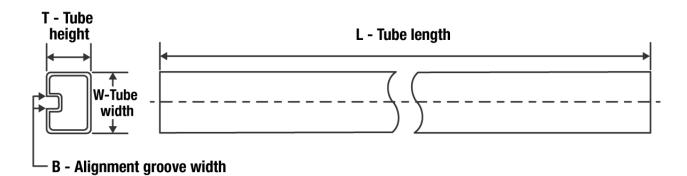

### TUBE

#### \*All dimensions are nominal

| Device         | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LMH6505MA/NOPB | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

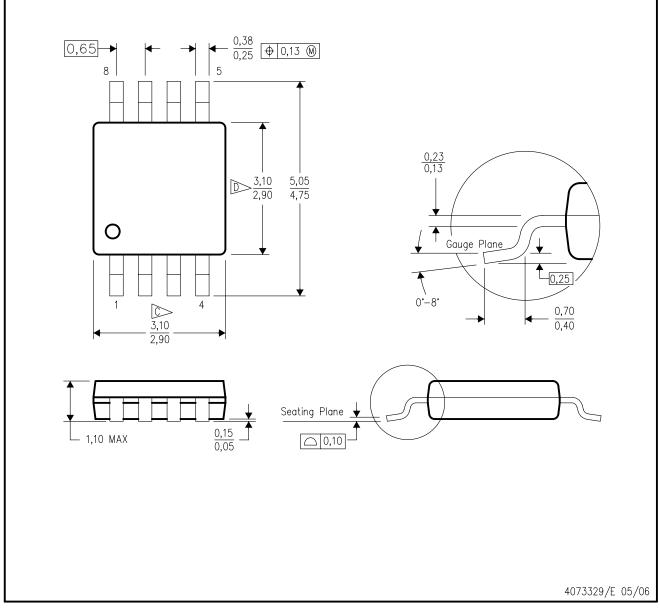

# D0008A

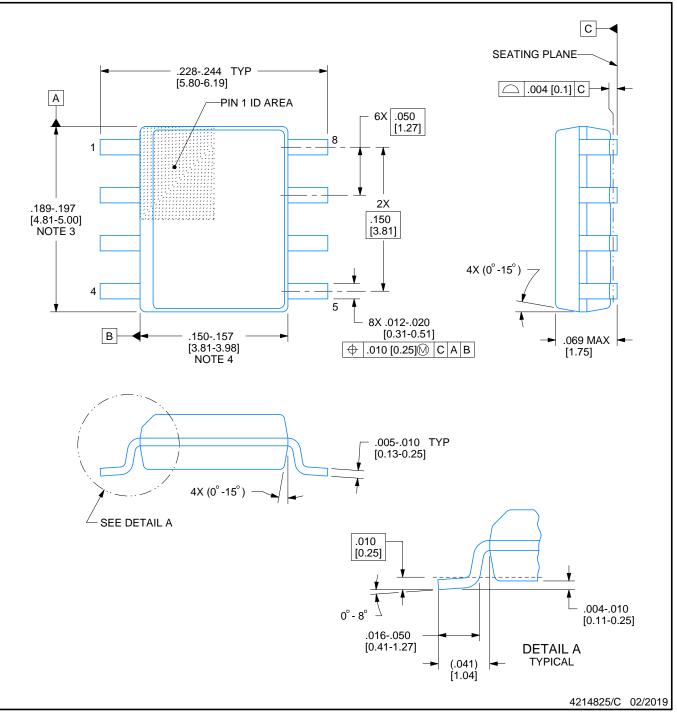

# **PACKAGE OUTLINE**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

# D0008A

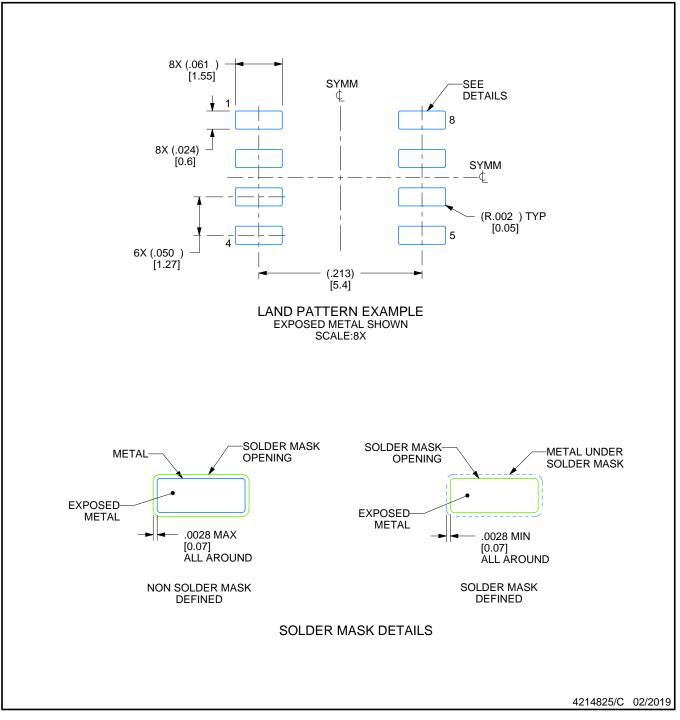

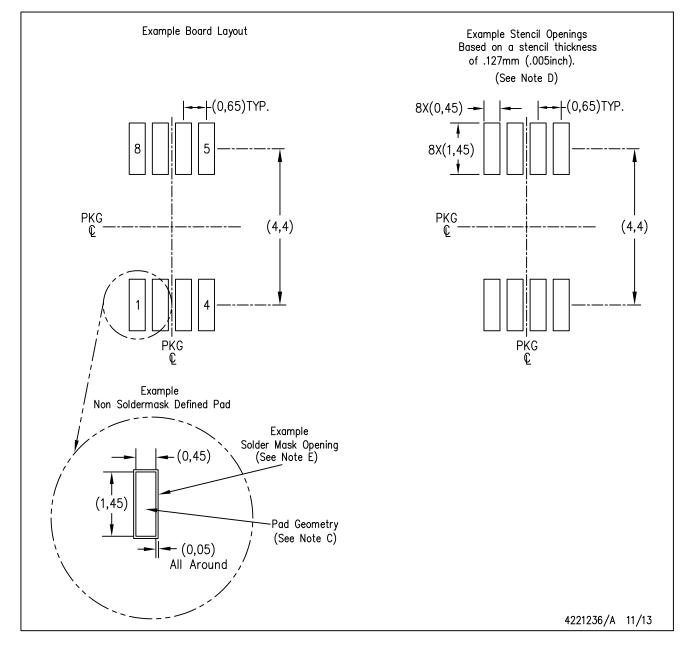

# **EXAMPLE BOARD LAYOUT**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

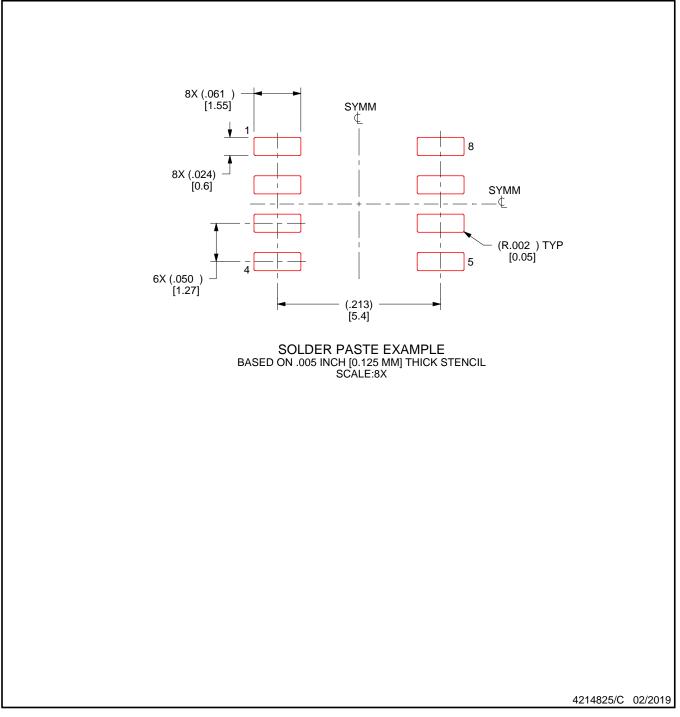

# D0008A

# **EXAMPLE STENCIL DESIGN**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

# DGK (S-PDSO-G8)

### PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated