Sample &

Buy

TPS2552D, TPS2553D

ZHCSFI7-SEPTEMBER 2016

# TPS255xD 高精度可调式限流配电开关

Technical

Documents

## 1 特性

- 最大负载电流可达 1.5A

- 1.7A 电流下的电流限制精度为 ±6% (典型值)

- 满足 USB 限流要求

- 与 TPS2550/51 向后兼容

- 可调电流限制值,75mA-1700mA(典型值)

- 恒流(TPS2552D和TPS2553D)

- TPS2552D(支持低电流)和 TPS2553D(支持高 电流)

- 快速过流响应 2µs (典型值)

- 85mΩ 高侧金属氧化物半导体场效应晶体管 (MOSFET)(DBV 封装)

- 反向输入-输出电压保护

- 工作范围: 2.7V 至 6.5V

- 内置软启动

- 15kV ESD 保护,符合 IEC 61000-4-2 标准(带外 部电容)

- UL列表 文件号E169910 和 NEMKO IEC60950-1am1 ed2.0

- 请见TI 开关系列产品

## 2 应用

- USB 端口/集线器

- 数字电视

- 机顶盒

- 网络语音 (VOIP) 电话

## 3 说明

Tools &

Software

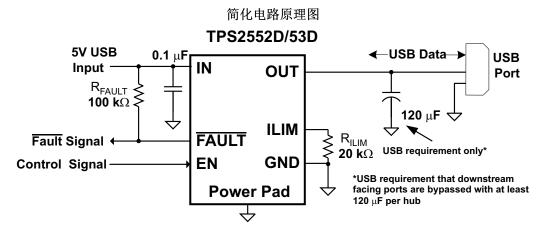

**TPS2552D**和 **TPS2553D** 配电开关专门用于 电流 限制精度有要求或者会遇到重电容负载和短路的应用,并可提供高达 1.5A 的持续负载电流。这些器件借助一个外部电阻器提供一个 75mA至 1.7A (典型值)间的可编程电流限制阈值。在更高电流限制设置上可实现严格至 ±6% 的电流限制精度。对电源开关的上升和下降次数进行控制以大大降低接通/切断期间的电流冲击。

Support &

Community

**.**...

当输出负载超过电流限制阈值时,TPS2552D/3D器件 会通过使用恒流模式将输出电流限制到安全水平。当输 出电压被驱动至高于输入电压时,内部反向电压比较器 将禁用电源开关以保护此开关输入端的器件。在过流和 反向电压情况下,FAULT 输出被置为低电平。

## 器件信息<mark>(1)</mark>

| 器件型号     | 封装         | 封装尺寸(标称值)       |

|----------|------------|-----------------|

| TPS2552D | SOT-23 (6) | 2.90mm x 1.60mm |

| TPS2553D | SOT-23 (6) | 2.90mm x 1.60mm |

|          |            |                 |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Copyright © 2016, Texas Instruments Incorporated

## 目录

| 1 | 特性   | 1                                 |  |  |  |  |  |  |

|---|------|-----------------------------------|--|--|--|--|--|--|

| 2 | 应用   |                                   |  |  |  |  |  |  |

| 3 | 说明   | 1                                 |  |  |  |  |  |  |

| 4 | 修订   | 历史记录 2                            |  |  |  |  |  |  |

| 5 | Dev  | ice Comparison Table 3            |  |  |  |  |  |  |

| 6 | Pin  | Pin Configuration and Functions 4 |  |  |  |  |  |  |

| 7 | Spe  | cifications5                      |  |  |  |  |  |  |

|   | 7.1  | Absolute Maximum Ratings 5        |  |  |  |  |  |  |

|   | 7.2  | ESD Ratings 5                     |  |  |  |  |  |  |

|   | 7.3  | Recommended Operating Conditions5 |  |  |  |  |  |  |

|   | 7.4  | Thermal Information 6             |  |  |  |  |  |  |

|   | 7.5  | Electrical Characteristics7       |  |  |  |  |  |  |

|   | 7.6  | Typical Characteristics 8         |  |  |  |  |  |  |

| 8 | Para | ameter Measurement Information 11 |  |  |  |  |  |  |

| 9 | Deta | ailed Description 13              |  |  |  |  |  |  |

|   | 9.1  | Overview 13                       |  |  |  |  |  |  |

|   | 9.2  | Functional Block Diagram 13       |  |  |  |  |  |  |

|   | 9.3  | Feature Description 13            |  |  |  |  |  |  |

|   | 9.4  | Device Functional Modes 14        |  |  |  |  |  |  |

|   | 9.5  | Programming 15                    |  |  |  |  |  |  |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期         | 修订版本 | 注释     |  |  |

|------------|------|--------|--|--|

| 2016 年 9 月 | *    | 最初发布版本 |  |  |

#### www.ti.com.cn

**NSTRUMENTS**

**EXAS**

| 10 | Appl | ication and Implementation                 | 17   |

|----|------|--------------------------------------------|------|

|    | 10.1 | Application Information                    | . 17 |

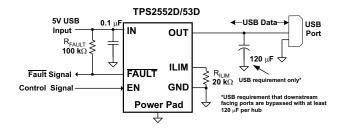

|    | 10.2 | Typical Applications                       | . 17 |

| 11 | Pow  | er Supply Recommendations                  | 25   |

|    | 11.1 | Self-Powered and Bus-Powered Hubs          | . 25 |

|    |      | Low-Power Bus-Powered and High-Power Bus-  |      |

|    | F    | Powered Functions                          | . 25 |

|    | 11.3 | Power Dissipation and Junction Temperature | 25   |

12.1 Layout Guidelines ...... 26 12.2 Layout Example ..... 26 13 器件和文档支持 ...... 27 13.2 相关链接...... 27 13.3 接收文档更新通知 ...... 27 13.4 社区资源...... 27 13.6 静电放电警告...... 27 13.7 Glossary...... 27 14 机械、封装和可订购信息...... 27

# 5 Device Comparison Table

| GENERAL SWITCH CATALOG |                                                  |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                    |                        |  |  |  |

|------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|------------------------|--|--|--|

| 33 mΩ, single          | 80 mΩ, single<br>+ + + + + + + + + + + + + + + + | 80 mΩ, dual<br>τPs2042B 500 mA<br>TPS2045B 550 mA<br>TPS205E 550 mA<br>TPS205C 1 A<br>TPS2066 1 A<br>TPS2066 1.5 A<br>TPS2064 1.5 A | 80 mΩ, dual           Image: Constraint of the state of the | 80 mQ, triple | <b>80 mΩ, quad</b> | <b>80 mΩ, quad</b><br> |  |  |  |

Texas Instruments

www.ti.com.cn

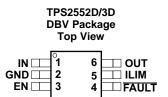

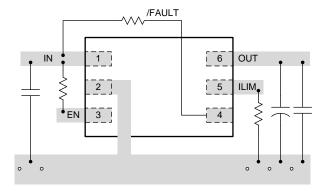

## 6 Pin Configuration and Functions

EN = Active Low for the TPS2552D

EN = Active High for the TPS2553D

## **Pin Functions**

|          | PIN      |                       |                                                                                                                                                                                |                                                                                                                              |  |  |

|----------|----------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | TPS2552D | TPS2552D TPS2553D I/O |                                                                                                                                                                                | DESCRIPTION                                                                                                                  |  |  |

| NANE     | DBV      | DBV                   | I       Enable input, logic low turns on power switch         I       Enable input, logic high turns on power switch         Ground connection; connect externally to PowerPAD |                                                                                                                              |  |  |

| EN       | 3        | -                     | I Enable input, logic low turns on power switch                                                                                                                                |                                                                                                                              |  |  |

| EN       | -        | 3                     | I                                                                                                                                                                              | Enable input, logic high turns on power switch                                                                               |  |  |

| GND      | 2        | 2                     |                                                                                                                                                                                | Ground connection; connect externally to PowerPAD                                                                            |  |  |

| IN       | 1        | 1                     | I                                                                                                                                                                              | Input voltage; connect a 0.1 $\mu F$ or greater ceramic capacitor from IN to GND as close to the IC as possible.             |  |  |

| FAULT    | 4        | 4                     | 0                                                                                                                                                                              | Active-low open-drain output, asserted during overcurrent, overtemperature, or reverse-voltage conditions.                   |  |  |

| OUT      | 6        | 6                     | 0                                                                                                                                                                              | Power-switch output                                                                                                          |  |  |

| ILIM     | 5        | 5                     | 0                                                                                                                                                                              | External resistor used to set current-limit threshold;<br>recommended 15 k $\Omega \le R_{ILIM} \le 232 k\Omega$ .           |  |  |

| PowerPAD | _        | _                     |                                                                                                                                                                                | Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect PowerPAD to GND pin externally. |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                  |                                           | MIN                         | MAX | UNIT |

|------------------|-------------------------------------------|-----------------------------|-----|------|

|                  | Voltage range on IN, OUT, EN, ILIM, FAULT | -0.3                        | 7   | V    |

|                  | Voltage range from IN to OUT              | -7                          | 7   | V    |

| Ιo               | Continuous output current                 | Internally Limited          |     |      |

|                  | Continuous total power dissipation        | See the Thermal Information |     |      |

|                  | Continuous FAULT sink current             | 0                           | 25  | mA   |

|                  | ILIM source current                       | 0                           | 1   | mA   |

| $T_J$            | Maximum junction temperature              | -40                         | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                       | -65                         | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Voltages are referenced to GND unless otherwise noted.

## 7.2 ESD Ratings

|                    |                         |                                                                                          | VALUE  | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|--------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |        | V    |

| (202)              |                         | IEC 61000-4-2 contact discharge <sup>(3)</sup>                                           | ±8000  |      |

|                    |                         | IEC 61000-4-2 air-gap discharge <sup>(3)</sup>                                           | ±15000 |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

(3) Surges per EN61000-4-2. 1999 applied to output terminals of EVM. These are passing test levels, not failure threshold.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                          |                                                | MIN | NOM MAX | UNIT |

|-------------------|------------------------------------------|------------------------------------------------|-----|---------|------|

| V <sub>IN</sub>   | Input voltage, IN                        |                                                | 2.7 | 6.5     | V    |

| VEN               | Frankla valtana                          | TPS2552D                                       | 0   | 6.5     | V    |

| V <sub>EN</sub>   | Enable voltage                           | TPS2553D                                       | 0   | 6.5     | V    |

| V <sub>EN</sub>   | Enable voltage                           |                                                | 0   | 6.5     | V    |

| V <sub>IH</sub>   | High-level input volta                   | ge on EN                                       | 1.1 |         | V    |

| V <sub>IL</sub>   | Low-level input voltage                  | ge on EN                                       |     | 0.66    | v    |

|                   | Continuous output current, OUT           | –40 °C ≤ T <sub>J</sub> ≤ 125 °C               | 0   | 1.2     | ٨    |

| IOUT              |                                          | –40 °C ≤ T <sub>J</sub> ≤ 105 °C               | 0   | 1.5     | A    |

| R <sub>ILIM</sub> | Current-limit threshol                   | d resistor range (nominal 1%) from ILIM to GND | 15  | 232     | KΩ   |

| I <sub>O</sub>    | Continuous FAULT s                       | ink current                                    | 0   | 10      | mA   |

|                   | Input de-coupling capacitance, IN to GND |                                                | 0.1 |         | μF   |

|                   | Operating virtual                        | I <sub>OUT</sub> ≤ 1.2 A                       | -40 | 125     |      |

| TJ                | junction<br>temperature <sup>(1)</sup>   | I <sub>OUT</sub> ≤ 1.5 A                       | -40 | 105     | °C   |

(1) See "Dissipation Rating Table" and "Power Dissipation and Junction Temperature" sections for details on how to calculate maximum junction temperature for specific applications and packages.

## TPS2552D, TPS2553D

ZHCSFI7-SEPTEMBER 2016

www.ti.com.cn

## 7.4 Thermal Information

|                       |                                              | TPS2552D | TPS2553D |      |

|-----------------------|----------------------------------------------|----------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBV      | DBV      | UNIT |

|                       |                                              | 6 PINS   | 6 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 182.6    | 182.6    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 122.2    | 122.2    | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 29.4     | 29.4     | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 20.8     | 20.8     | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 28.9     | 28.9     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A      | N/A      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

版权 © 2016, Texas Instruments Incorporated

## 7.5 Electrical Characteristics

|                     | PARAMETER                                                                      |                                                        | TEST                                           | CONDITIONS <sup>(1)</sup>                             |                       | MIN  | TYP  | MAX  | UNIT |

|---------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|-----------------------|------|------|------|------|

| POWE                | R SWITCH                                                                       |                                                        |                                                |                                                       |                       |      |      |      |      |

|                     |                                                                                | DBV package, T <sub>J</sub> = 2                        | 5°C                                            |                                                       |                       |      | 85   | 95   |      |

|                     |                                                                                | DBV package, –40°C ≤T <sub>J</sub> ≤125°C              |                                                |                                                       |                       |      |      | 135  |      |

| r <sub>DS(on)</sub> | Static drain-source on-state resistance                                        | DRV package, T <sub>1</sub> = 25°C                     |                                                |                                                       |                       | 100  | 115  | mΩ   |      |

| 20(01)              |                                                                                | DRV package, –40°C ≤TJ ≤105°C                          |                                                |                                                       |                       |      | 140  |      |      |

|                     |                                                                                | DRV package, $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ |                                                |                                                       |                       |      |      | 150  |      |

|                     |                                                                                | V <sub>IN</sub> = 6.5 V                                | 0                                              |                                                       |                       |      | 1.1  | 1.5  |      |

| t <sub>r</sub>      | Rise time, output                                                              |                                                        | $C_{i} = 1 \mu F_{i}F_{i}$                     | R. = 100 O                                            |                       |      | 0.7  | 1    |      |

|                     |                                                                                |                                                        | 6.5 V (see 图 20)                               |                                                       |                       | 0.2  |      | 0.5  | ms   |

| t <sub>f</sub>      | Fall time, output                                                              | $V_{IN} = 2.5 V$                                       |                                                |                                                       |                       | 0.2  |      | 0.5  |      |

| ENABL               |                                                                                | 11 <b>N</b> -                                          |                                                |                                                       |                       |      |      |      |      |

|                     | Enable pin turn on/off threshold                                               |                                                        |                                                |                                                       |                       | 0.66 |      | 1.1  | V    |

| I <sub>EN</sub>     | Input current                                                                  | $V_{\rm EN} = 0 V \text{ or } 65 V V$                  | = 0 V or 6.5 V, V <sub>EN</sub> = 0 V or 6.5 V |                                                       |                       |      |      | 0.5  | μA   |

| t <sub>on</sub>     | Turnon time                                                                    | VEN = 0 V 01 0.0 V, V                                  | EN - 0 1 01                                    | 0.0 1                                                 |                       | -0.5 |      | 3    | ms   |

| t <sub>off</sub>    | Turnoff time                                                                   | $C_L = 1 \ \mu F, R_L = 100 \ G$                       | Ω, (see <u>8</u> 2                             | 0)                                                    |                       |      |      | 3    | ms   |

|                     |                                                                                |                                                        |                                                |                                                       |                       |      |      | 0    |      |

|                     |                                                                                |                                                        |                                                | R <sub>ILIM</sub> = 15 kΩ                             | –40°C ≤T, ≤105°C      | 1610 | 1700 | 1800 |      |

|                     |                                                                                |                                                        |                                                | . 1LIM - 10 102                                       | $T_{1} = 25^{\circ}C$ | 1215 | 1295 | 1375 |      |

|                     |                                                                                |                                                        |                                                | $R_{ILIM} = 20 \ k\Omega$                             | -40°C ≤T, ≤125°C      | 1213 | 1295 | 1375 |      |

|                     | Current-limit threshold (Maximum DC or                                         |                                                        | ered to                                        |                                                       | $T_1 = 25^{\circ}C$   | 490  | 520  | 550  | mA   |

| OS                  | load) and Short-circuit current, OUT cor                                       | nnected to GND                                         | $R_{IIIM} = 49.9 \text{ k}\Omega$              | –40°C ≤T, ≤125°C                                      | 475                   | 520  | 565  | ША   |      |

|                     |                                                                                |                                                        |                                                | P = 210 kO                                            | -40 C 31j 3125 C      | 110  | 130  | 150  |      |

|                     |                                                                                |                                                        |                                                | $R_{ILIM} = 210 \text{ k}\Omega$<br>ILIM shorted to I | N                     | 50   | 75   | 100  |      |

|                     | Deenenee time to short size it                                                 | V EV (200 201)                                         |                                                | ILIW SHOTED TO I                                      | IN                    | 50   | 2    | 100  |      |

|                     | Response time to short circuit                                                 | V <sub>IN</sub> = 5 V (see 图 21)                       |                                                |                                                       |                       |      | 2    |      | μS   |

| REVER               |                                                                                |                                                        |                                                |                                                       |                       |      |      |      |      |

|                     | Reverse-voltage comparator trip point<br>(V <sub>OUT</sub> – V <sub>IN</sub> ) |                                                        |                                                |                                                       |                       | 95   | 135  | 190  | mV   |

|                     | Time from reverse-voltage condition to<br>MOSFET turn off                      | V <sub>IN</sub> = 5 V                                  |                                                |                                                       |                       | 3    | 5    | 7    | ms   |

| SUPPL               | Y CURRENT                                                                      |                                                        |                                                |                                                       |                       |      |      |      |      |

| I <sub>IN_off</sub> | Supply current, low-level output                                               | $V_{IN}$ = 6.5 V, No load                              | on OUT, V <sub>E</sub>                         | <sub>N</sub> = 0 V                                    |                       |      | 0.1  | 1    | μA   |

|                     | Supply surrent high lavel sutput                                               |                                                        |                                                | $R_{ILIM} = 20 \ k\Omega$                             |                       |      | 120  | 150  | μA   |

| I <sub>IN_on</sub>  | Supply current, high-level output                                              | $V_{IN} = 6.5 V$ , No load                             | 011001                                         | $R_{ILIM} = 210 \ k\Omega$                            |                       |      | 100  | 130  | μA   |

| I <sub>REV</sub>    | Reverse leakage current                                                        | $V_{OUT} = 6.5 \text{ V}, V_{IN} = 0$                  | V                                              | T <sub>J</sub> = 25 °C                                |                       |      | 0.01 | 1    | μA   |

| UNDE                | RVOLTAGE LOCKOUT                                                               | ·                                                      |                                                |                                                       |                       |      |      |      |      |

| UVLO                | Low-level input voltage, IN                                                    | V <sub>IN</sub> rising                                 |                                                |                                                       |                       |      | 2.35 | 2.45 | V    |

|                     | Hysteresis, IN                                                                 | T <sub>J</sub> = 25 °C                                 |                                                |                                                       |                       |      | 25   |      | mV   |

| FAULT               | FLAG                                                                           |                                                        |                                                |                                                       |                       |      |      | I    |      |

| V <sub>OL</sub>     | Output low voltage, FAULT                                                      | I <sub>/FAULT</sub> = 1 mA                             |                                                |                                                       |                       |      |      | 180  | mV   |

|                     | Off-state leakage                                                              | V <sub>/FAULT</sub> = 6.5 V                            |                                                |                                                       |                       |      |      | 1    | μA   |

|                     |                                                                                | FAULT assertion or o                                   | de-assertion                                   | due to overcurren                                     | t condition           | 5    | 7.5  | 10   | ms   |

|                     | FAULT deglitch                                                                 | FAULT assertion or o                                   | de-assertion                                   | due to reverse-vo                                     | Itage condition       | 2    | 4    | 6    | ms   |

| THERM               | MAL SHUTDOWN                                                                   | •                                                      |                                                |                                                       |                       | +    |      |      |      |

|                     | Thermal shutdown threshold                                                     |                                                        |                                                |                                                       |                       | 155  |      |      | °C   |

|                     |                                                                                | 1                                                      |                                                |                                                       |                       |      |      |      |      |

|                     | Thermal shutdown threshold in<br>current-limit                                 |                                                        |                                                |                                                       |                       | 135  |      |      | °C   |

(1) Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

TPS2552D, TPS2553D ZHCSFI7-SEPTEMBER 2016 TEXAS INSTRUMENTS

www.ti.com.cn

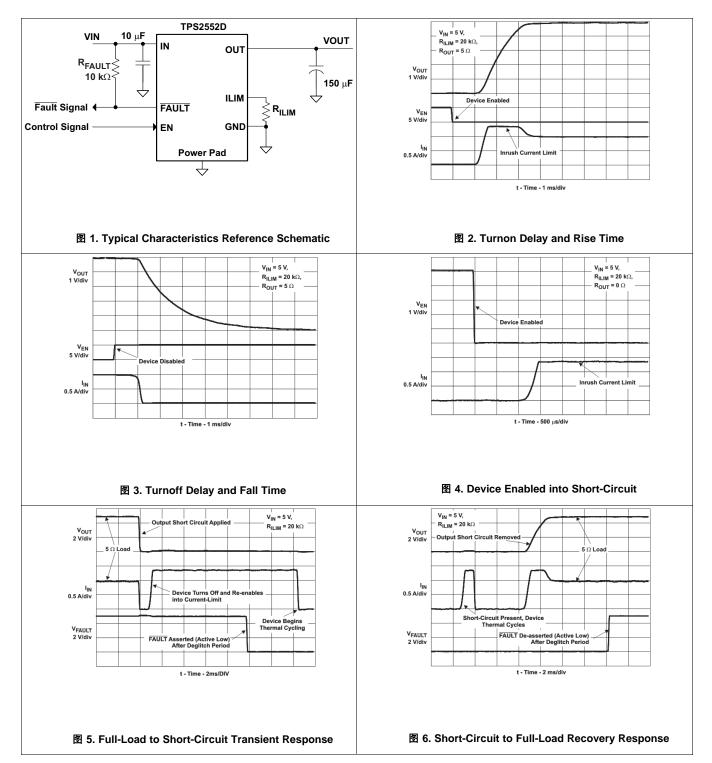

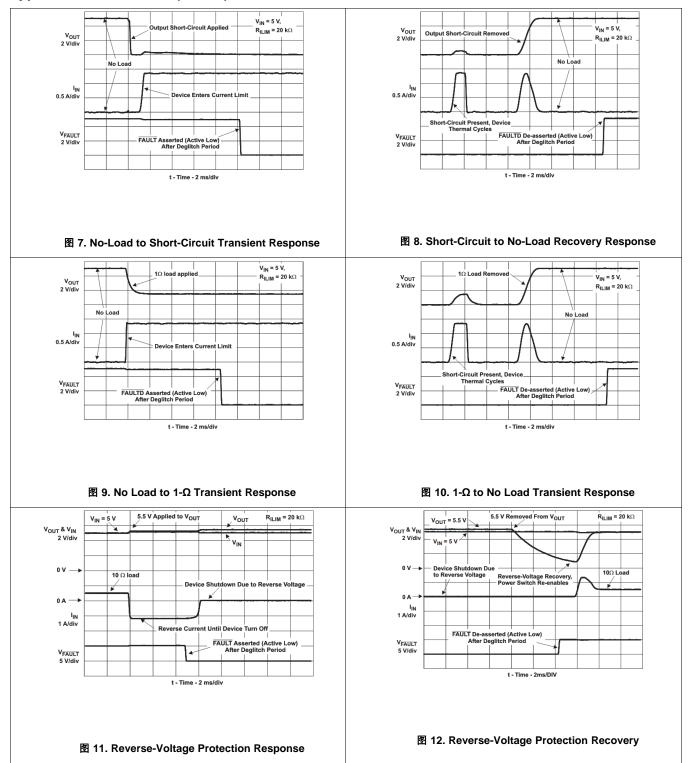

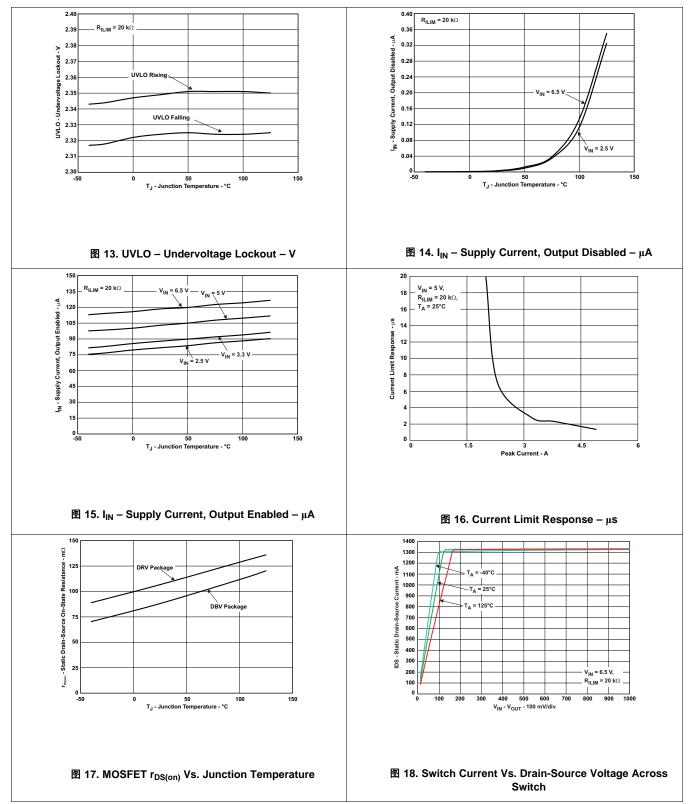

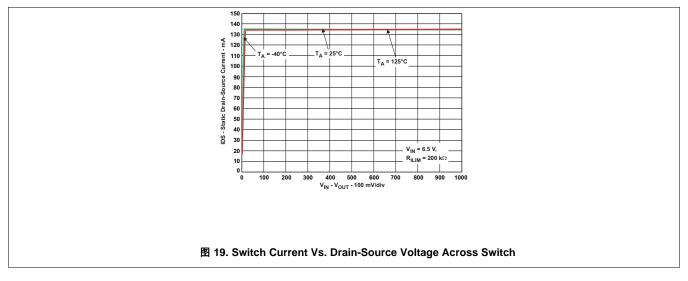

## 7.6 Typical Characteristics

## Typical Characteristics (接下页)

# Typical Characteristics (接下页)

## Typical Characteristics (接下页)

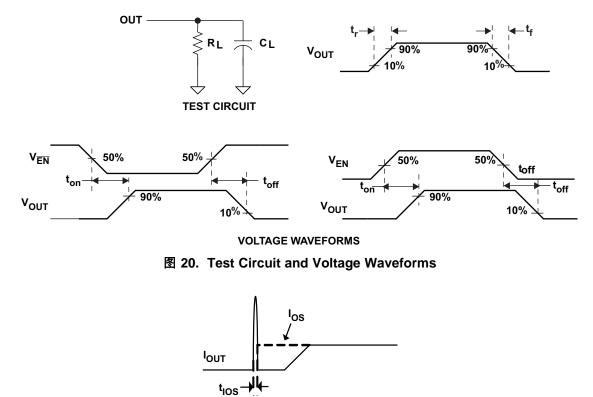

## 8 Parameter Measurement Information

图 21. Response Time to Short Circuit Waveform

TEXAS INSTRUMENTS

www.ti.com.cn

## Parameter Measurement Information (接下页)

图 22. Output Voltage Vs. Current-Limit Threshold

## 9 Detailed Description

## 9.1 Overview

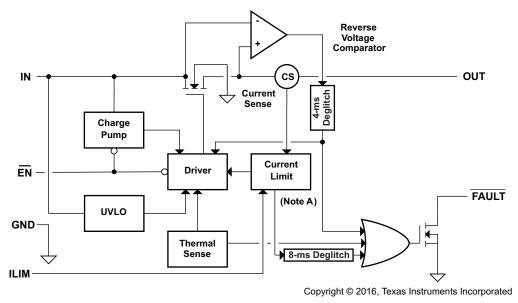

The TPS2552D and TPS2553D are current-limited, power-distribution switches using N-channel MOSFETs for applications where short circuits or heavy capacitive loads will be encountered and provide up to 1.5 A of continuous load current. These devices allow the user to program the current-limit threshold between 75 mA and 1.7 A (typ) via an external resistor. Additional device shutdown features include overtemperature protection and reverse-voltage protection. The device incorporates an internal charge pump and gate drive circuitry necessary to drive the N-channel MOSFET. The charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V and requires little supply current. The driver controls the gate voltage to limit large current and voltage surges and provides built-in soft-start functionality. There are two device families that handle overcurrent situations differently. The TPS255xD family enters constant-current mode when the load exceeds the current-limit threshold.

## 9.2 Functional Block Diagram

A. TPS255x parts enter constant current mode during current limit condition

## 9.3 Feature Description

### 9.3.1 Overcurrent Conditions

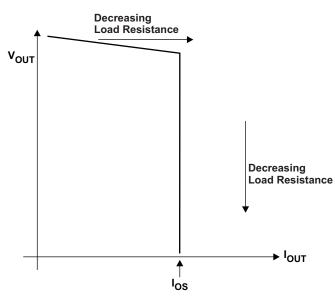

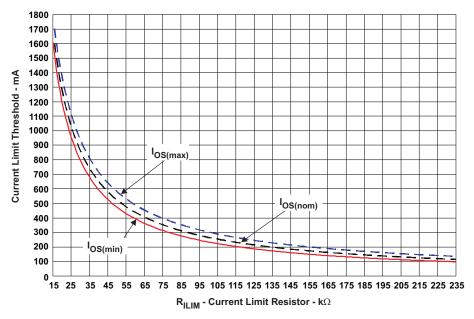

The TPS2552D and TPS2553D respiond to overcurrent conditions by limiting their output current to the  $I_{OS}$  levels shown in  $\mathbb{Z}$  23. When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur.

The first condition is when a short circuit or partial short circuit is present when the device is powered-up or enabled. The output voltage is held near zero potential with respect to ground and the TPS2552D and TPS2553D ramps the output current to  $I_{OS}$ . The TPS2552D and TPS2553D devices limits the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

The second condition is when a short circuit, partial short circuit, or transient overload occurs while the device is enabled and powered on. The device responds to the overcurrent condition within time  $t_{IOS}$  (see B 21). The current-sense amplifier is overdriven during this time and momentarily disables the internal current-limit MOSFET. The current-sense amplifier recovers and limits the output current to  $I_{OS}$ . Similar to the previous case, the TPS2552D and TPS2553D devices limit the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

## Feature Description (接下页)

The TPS2552D/53D thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. The device turns off when the junction temperature exceeds  $135^{\circ}C$  (typ) while in current limit. The device remains off until the junction temperature cools  $10^{\circ}C$  (typ) and then restarts. The TPS2552D/53D cycle on/off until the overload is removed (see  $\mathbb{E}$  6 and  $\mathbb{E}$  8).

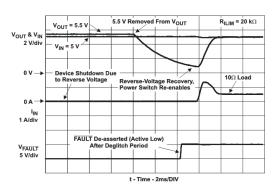

### 9.3.2 Reverse-Voltage Protection

The reverse-voltage protection feature turns off the N-channel MOSFET whenever the output voltage exceeds the input voltage by 135 mV (typ) for 4-ms (typ).A reverse current of  $(V_{OUT} - V_{IN})/r_{DS(on)}$ ) are present when this occurs. This prevents damage to devices on the input side of the TPS2552D/53D by preventing significant current from sinking into the input capacitance. The TPS2552D/53D devices allow the N-channel MOSFET to turn on once the output voltage goes below the input voltage for the same 4-ms deglitch time. The reverse-voltage comparator also asserts the FAULT output (active-low) after 4-ms.

## 9.3.3 FAULT Response

The FAULT open-drain output is asserted (active low) during an overcurrent, overtemperature or reverse-voltage condition. The TPS2552D/53D asserts the FAULT signal until the fault condition is removed and the device resumes normal operation. The TPS2552D/53D are designed to eliminate false FAULT reporting by using an internal delay "deglitch" circuit for overcurrent (7.5-ms typ) and reverse-voltage (4-ms typ) conditions without the need for external circuitry. This ensures that FAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. The deglitch circuitry delays entering and leaving fault conditions. Overtemperature conditions are not deglitched and assert the FAULT signal immediately.

## 9.3.4 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage drop from large current surges.

### 9.3.5 ENABLE

The logic enable controls the power switch, bias for the charge pump, driver, and other circuits to reduce the supply current. The supply current is reduced to less than  $1-\mu A$  when a logic high is present on EN or when a logic low is present on EN. A logic low input on EN or a logic high input on EN enables the driver, A logic high input on EN enables the driver, control circuits, and power switch. The enable input is compatible with both TTL and CMOS logic levels.

### 9.3.6 Thermal Sense

The TPS2552D/53D self-protection features use two independent thermal sensing circuits that monitor the operating temperature of the power switch and disable operation if the temperature exceeds recommended operating conditions. The TPS2552D/53D devices operate in constant-current mode during an overcurrent conditions, which increases the voltage drop across power-switch. The power dissipation in the package is proportional to the voltage drop across the power switch, which increases the junction temperature during an overcurrent condition. The first thermal sensor turns off the power switch when the die temperature exceeds 135°C (min) and the part is in current limit. Hysteresis is built into the thermal sensor, and the switch turns on after the device has cooled approximately 10°C.

The TPS2552D/3D also have a second ambient thermal sensor. The ambient thermal sensor turns off the powerswitch when the die temperature exceeds 155°C (min) regardless of whether the power switch is in current limit and will turn on the power switch after the device has cooled approximately 10°C. The TPS2552D/53D families continue to cycle off and on until the fault is removed.

The open-drain fault reporting output FAULT is asserted (active low) immediately during an overtemperature shutdown condition.

## 9.4 Device Functional Modes

There are no other functional modes.

## 9.5 Programming

## 9.5.1 Programming the Current-Limit Threshold

The overcurrent threshold is user programmable via an external resistor. The TPS2552D/53D use an internal regulation loop to provide a regulated voltage on the ILIM pin. The current-limit threshold is proportional to the current sourced out of ILIM. The recommended 1% resistor range for  $R_{ILIM}$  is 15 k $\Omega \leq R_{ILIM} \leq 232$  k $\Omega$  to ensure stability of the internal regulation loop. Many applications require that the minimum current limit is above a certain current level or that the maximum current limit is below a certain current level, so it is important to consider the tolerance of the overcurrent threshold when selecting a value for  $R_{ILIM}$ . The following equations and  $\mathbb{Z}$  23 can be used to calculate the resulting overcurrent threshold for a given external resistor value ( $R_{ILIM}$ ).  $\mathbb{Z}$  23 includes current-limit tolerance due to variations caused by temperature and process. However, the equations do not account for tolerance due to external resistor variation, so it is important to account for this tolerance when selecting  $R_{ILIM}$ . The traces routing the  $R_{ILIM}$  resistor to the TPS2552D/53D should be as short as possible to reduce parasitic effects on the current-limit accuracy.

R<sub>ILIM</sub> can be selected to provide a current-limit threshold that occurs 1) above a minimum load current or 2) below a maximum load current.

To design above a minimum current-limit threshold, find the intersection of  $R_{ILIM}$  and the maximum desired load current on the  $I_{OS(min)}$  curve and choose a value of  $R_{ILIM}$  below this value. Programming the current limit above a minimum threshold is important to ensure start up into full load or heavy capacitive loads. The resulting maximum current-limit threshold is the intersection of the selected value of  $R_{ILIM}$  and the  $I_{OS(max)}$  curve.

To design below a maximum current-limit threshold, find the intersection of  $R_{ILIM}$  and the maximum desired load current on the  $I_{OS(max)}$  curve and choose a value of  $R_{ILIM}$  above this value. Programming the current limit below a maximum threshold is important to avoid current limiting upstream power supplies causing the input voltage bus to droop. The resulting minimum current-limit threshold is the intersection of the selected value of  $R_{ILIM}$  and the  $I_{OS(min)}$  curve.

Current-Limit Threshold Equations (I<sub>OS</sub>):

$$I_{OSmax}(mA) = \frac{22980V}{R_{ILIM}^{0.94}k\Omega}$$

$$I_{OSnom}(mA) = \frac{23950V}{R_{ILIM}^{0.977}k\Omega}$$

$$I_{OSmin}(mA) = \frac{25230V}{R_{ILIM}^{1.016}k\Omega}$$

where 15 k $\Omega \leq R_{ILIM} \leq 232 \text{ k}\Omega$ .

While the maximum recommended value of RILIM is 232 k $\Omega$ , there is one additional configuration that allows for a lower current-limit threshold. The ILIM pin may be connected directly to IN to provide a 75 mA (typ) current-limit threshold. Additional low-ESR ceramic capacitance may be necessary from IN to GND in this configuration to prevent unwanted noise from coupling into the sensitive ILIM circuitry.

(1)

TEXAS INSTRUMENTS

www.ti.com.cn

## Programming (接下页)

图 23. Current-Limit Threshold vs R<sub>ILIM</sub>

## **10** Application and Implementation

## 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## **10.1** Application Information

### 10.1.1 Constant-Current and Impact on Output Voltage

During normal operation the N-channel MOSFET is fully enhanced, and  $V_{OUT} = V_{IN} - (I_{OUT} \times r_{DS(on)})$ . The voltage drop across the MOSFET is relatively small compared to  $V_{IN}$ , and  $V_{OUT} \neq V_{IN}$ .

The TPS2552D/53D devices limit current to the programmed current-limit threshold set to  $R_{ILIM}$  by operating the N-channel MOSFET in the linear mode. During current-limit operation, the N-channel MOSFET is no longer fullyenhanced and the resistance of the device increases. This allows the device to effectively regulate the current to the current-limit threshold. The effect of increasing the resistance of the MOSFET is that the voltage drop across the device is no longer negligible ( $V_{IN} \neq V_{OUT}$ ), and  $V_{OUT}$  decreases. The amount that  $V_{OUT}$  decreases is proportional to the magnitude of the overload condition. The expected  $V_{OUT}$  can be calculated by  $I_{OS} \times R_{LOAD}$ , where  $I_{OS}$  is the current-limit threshold and  $R_{LOAD}$  is the magnitude of the overload condition. For example, if  $I_{OS}$ is programmed to 1 A and a 1  $\Omega$  overload condition is applied, the resulting  $V_{OUT}$  is 1 V.

The TPS2552D/53D devices assert the FAULT flag after the deglitch period and continue to regulate the current to the current-limit threshold indefinitely. In practical circuits, the power dissipation in the package will increase the die temperature above the overtemperature shutdown threshold (135°C min), and the device will turn off until the die temperature decreases by the hysteresis of the thermal shutdown circuit (10°C typ). The device will turn on and continue to thermal cycle until the overload condition is removed. The TPS2552D/53D devices resume normal operation once the overload condition is removed.

## **10.2 Typical Applications**

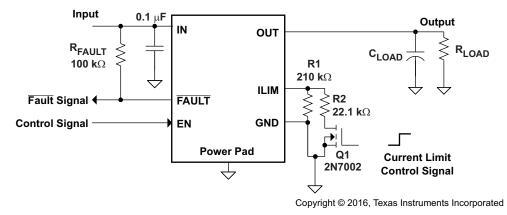

### 10.2.1 Two-Level Current-Limit Circuit

Some applications require different current-limit thresholds depending on external system conditions. 24 shows an implementation for an externally controlled, two-level current-limit circuit. The current-limit threshold is set by the total resistance from ILIM to GND (see the *Programming the Current-Limit Threshold* section). A logic-level input enables/disables MOSFET Q1 and changes the current-limit threshold by modifying the total resistance from ILIM to GND. Additional MOSFET/resistor combinations can be used in parallel to Q1/R2 to increase the number of additional current-limit levels.

注 ILIM should never be driven directly with an external signal.

## Typical Applications (接下页)

### 图 24. Two-Level Current-Limit Circuit

## 10.2.1.1 Design Requirements

For this example, use the parameters shown in 表 1.

## 表 1. Design Requirements

| PARAMETER                     | VALUE   |

|-------------------------------|---------|

| Input voltage                 | 5 V     |

| Output voltage                | 5 V     |

| Above a minimum current limit | 1000 mA |

| Below a maximum current limit | 500 mA  |

### 10.2.1.2 Detailed Design Procedures

### 10.2.1.2.1 Designing Above a Minimum Current Limit

Some applications require that current limiting cannot occur below a certain threshold. For this example, assume that 1 A must be delivered to the load so that the minimum desired current-limit threshold is 1000 mA. Use the  $I_{OS}$  equations and  $\mathbb{Z}$  23 to select R<sub>ILIM</sub>.

$$\begin{split} &I_{OSmin}(mA) = 1000mA \\ &I_{OSmin}(mA) = \frac{25230V}{R_{ILIM}^{1016}k\Omega} \\ &R_{ILIM}(k\Omega) = \left(\frac{25230V}{I_{OSmin}mA}\right)^{\frac{1}{1.016}} \\ &R_{ILIM}(k\Omega) = 24k\Omega \end{split}$$

(2)

Select the closest 1% resistor less than the calculated value:  $R_{ILIM} = 23.7 \text{ k}\Omega$ . This sets the minimum current-limit threshold at 1 A . Use the I<sub>OS</sub> equations,  $\mathbb{Z}$  23, and the previously calculated value for  $R_{ILIM}$  to calculate the maximum resulting current-limit threshold.

$$R_{ILIM}(k\Omega) = 23.7k\Omega$$

$$I_{OSmax}(mA) = \frac{22980V}{R_{ILIM}^{0.94}k\Omega}$$

$$I_{OSmax}(mA) = \frac{22980V}{23.7^{0.94}k\Omega}$$

$$I_{OSmax}(mA) = 1172.4mA$$

The resulting maximum current-limit threshold is 1172.4 mA with a 23.7 k $\Omega$  resistor.

(3)

#### 10.2.1.2.2 Designing Below a Maximum Current Limit

Some applications require that current limiting must occur below a certain threshold. For this example, assume that the desired upper current-limit threshold must be below 500 mA to protect an up-stream power supply. Use the  $I_{OS}$  equations and  $\mathbb{Z}$  23 to select  $R_{ILIM}$ .

$$I_{OSmax}(mA) = 500mA$$

$$I_{OSmax}(mA) = \frac{22980V}{R_{ILIM}^{0.94}k\Omega}$$

$$R_{ILIM}(k\Omega) = \left(\frac{22980V}{I_{OSmax}mA}\right)^{\frac{1}{0.94}}$$

$$R_{ILIM}(k\Omega) = 58.7k\Omega$$

(4)

Select the closest 1% resistor greater than the calculated value:  $R_{ILIM} = 59 \text{ k}\Omega$ . This sets the maximum current-limit threshold at 500 mA . Use the  $I_{OS}$  equations,  $\mathbb{Z}$  23, and the previously calculated value for  $R_{ILIM}$  to calculate the minimum resulting current-limit threshold.

$$R_{ILIM}(K\Omega) = 59K\Omega$$

$$I_{OSmin}(mA) = \frac{25230V}{R_{ILIM}^{1.016}k\Omega}$$

$$I_{OSmin}(mA) = \frac{25230V}{59^{1.016}k\Omega}$$

$$I_{OSmin}(mA) = 400.6mA$$

(5)

The resulting minimum current-limit threshold is 400.6 mA with a 59 k $\Omega$  resistor.

#### 10.2.1.2.3 Accounting for Resistor Tolerance

The previous sections described the selection of  $R_{ILIM}$  given certain application requirements and the importance of understanding the current-limit threshold tolerance. The analysis focused only on the TPS2552D/53D performance and assumed an exact resistor value. However, resistors sold in quantity are not exact and are bounded by an upper and lower tolerance centered around a nominal resistance. The additional  $R_{ILIM}$  resistance tolerance directly affects the current-limit threshold accuracy at a system level. The following table shows a process that accounts for worst-case resistor tolerance assuming 1% resistor values. Step one follows the selection process outlined in the application examples above. Step two determines the upper and lower resistance bounds of the selected resistor. Step three uses the upper and lower resistor bounds in the I<sub>OS</sub> equations to calculate the threshold limits. It is important to use tighter tolerance resistors, e.g. 0.5% or 0.1%, when precision current limiting is desired.

| DESIRED                          | IDEAL            | CLOSEST             | RESISTOR    | TOLERANCE     | ACTUAL LIMITS   |                 |                 |  |  |

|----------------------------------|------------------|---------------------|-------------|---------------|-----------------|-----------------|-----------------|--|--|

| NOMINAL<br>CURRENT LIMIT<br>(mA) | RESISTOR<br>(kΩ) | 1% RESISTOR<br>(kΩ) | 1% LOW (kΩ) | 1% HIGHT (kΩ) | IOS MIN<br>(mA) | IOS NOM<br>(mA) | IOS MAX<br>(mA) |  |  |

| 75                               |                  | SHORT ILIM          | to IN       |               | 50.0            | 75.0            | 100.0           |  |  |

| 120                              | 226.1            | 226                 | 223.7       | 228.3         | 101.3           | 120.0           | 142.1           |  |  |

| 200                              | 134.0            | 133                 | 131.7       | 134.3         | 173.7           | 201.5           | 233.9           |  |  |

| 300                              | 88.5             | 88.7                | 87.8        | 89.6          | 262.1           | 299.4           | 342.3           |  |  |

| 400                              | 65.9             | 66.5                | 65.8        | 67.2          | 351.2           | 396.7           | 448.7           |  |  |

| 500                              | 52.5             | 52.3                | 51.8        | 52.8          | 448.3           | 501.6           | 562.4           |  |  |

| 600                              | 43.5             | 43.2                | 42.8        | 43.6          | 544.3           | 604.6           | 673.1           |  |  |

| 700                              | 37.2             | 37.4                | 37.0        | 37.8          | 630.2           | 696.0           | 770.8           |  |  |

| 800                              | 32.4             | 32.4                | 32.1        | 32.7          | 729.1           | 800.8           | 882.1           |  |  |

| 900                              | 28.7             | 28.7                | 28.4        | 29.0          | 824.7           | 901.5           | 988.7           |  |  |

| 1000                             | 25.8             | 26.1                | 25.8        | 26.4          | 908.3           | 989.1           | 1081.0          |  |  |

| 1100                             | 23.4             | 23.2                | 23.0        | 23.4          | 1023.7          | 1109.7          | 1207.5          |  |  |

| 1200                             | 21.4             | 21.5                | 21.3        | 21.7          | 1106.0          | 1195.4          | 1297.1          |  |  |

| 1300                             | 19.7             | 19.6                | 19.4        | 19.8          | 1215.1          | 1308.5          | 1414.9          |  |  |

| 1400                             | 18.3             | 18.2                | 18.0        | 18.4          | 1310.1          | 1406.7          | 1517.0          |  |  |

| 1500                             | 17.0             | 16.9                | 16.7        | 17.1          | 1412.5          | 1512.4          | 1626.4          |  |  |

| 1600                             | 16.0             | 15.8                | 15.6        | 16.0          | 1512.5          | 1615.2          | 1732.7          |  |  |

| 1700                             | 15.0             | 15.0                | 14.9        | 15.2          | 1594.5          | 1699.3          | 1819.4          |  |  |

### 表 2. Common R<sub>ILIM</sub> Resistor Selections

### 10.2.1.2.4 Input and Output Capacitance

Input and output capacitance improves the performance of the device; the actual capacitance should be optimized for the particular application. For all applications, a  $0.1\mu$ F or greater ceramic bypass capacitor between IN and GND is recommended as close to the device as possible for local noise de-coupling. This precaution reduces ringing on the input due to power-supply transients. Additional input capacitance may be needed on the input to reduce voltage overshoot from exceeding the absolute maximum voltage of the device during heavy transient conditions. This is especially important during bench testing when long, inductive cables are used to connect the evaluation board to the bench power-supply.

Placing a high-value electrolytic capacitor on the output pin is recommended when large transient currents are expected on the output.

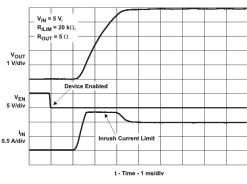

### 10.2.1.3 Application Curves

图 25. Turn on Delay and Rise Time

**NSTRUMENTS**

**Texas**

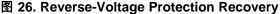

### 10.2.2 Auto-Retry Functionality

Some applications require that an overcurrent condition disables the part momentarily during a fault condition and re-enables after a pre-set time. This *auto-retry* functionality can be implemented with an external resistor and capacitor. During a fault condition, FAULT pulls low disabling the part. The part is disabled when EN is pulled low, and FAULT goes high impedance allowing  $C_{RETRY}$  to begin charging. The part re-enables when the voltage on EN reaches the turnon threshold, and the auto-retry time is determined by the resistor/capacitor time constant. The device continues to cycle in this manner until the fault condition is removed.

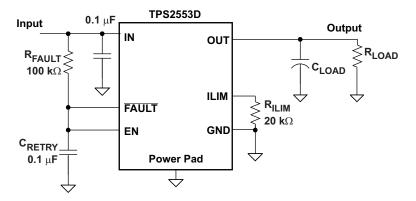

图 27. Auto-Retry Functionality

Some applications require auto-retry functionality and the ability to enable/disable with an external logic signal. 28 shows how an external logic signal can drive EN through R<sub>FAULT</sub> and maintain auto-retry functionality. The resistor/capacitor time constant determines the auto-retry time-out period.

图 28. Auto-Retry Functionality With External EN Signal

## 10.2.2.1 Design Requirements

For this example, use the parameters shown in  $\frac{1}{5}$  3.

## 表 3. Design Requirements

| PARAMETER      | VALUE   |

|----------------|---------|

| Input voltage  | 5 V     |

| Output voltage | 5 V     |

| Current        | 1200 mA |

ZHCSFI7-SEPTEMBER 2016

www.ti.com.cn

## 10.2.2.2 Detailed Design Procedure

Refer to Programming the Current-Limit Threshold section for the current limit setting. For auto-retry functionality, once FAULT asserted, EN pull low, TPS2553D is disabled, FAULT des-asserted,  $C_{RETRY}$  is slowly charged to EN logic high via  $R_{FAULT}$ , then enable, after deglitch time, FAULT asserted again. In the event of an over-load, TPS2553D cycles and has output average current. ON-time with output current is decided by FAULT deglitch time. OFF-time without output current is decided by  $R_{FAULT} \times C_{RETRY}$  constant time to EN logic high and  $t_{on}$  time. Therefore, set the  $R_{FAULT} \times C_{RETRY}$  to get the desired output average current during overload.

## 10.2.3 Typical Application as USB Power Switch

## 图 29. Typical Application as USB Power Switch

### 10.2.3.1 Design Requirements

For this example, use the parameters shown in 表 4.

### 表 4. Design Requirements

| PARAMETER      | VALUE   |

|----------------|---------|

| Input voltage  | 5 V     |

| Output voltage | 5 V     |

| Current        | 1200 mA |

### 10.2.3.1.1 USB Power-Distribution Requirements

USB can be implemented in several ways regardless of the type of USB device being developed. Several powerdistribution features must be implemented.

- SPHs must:

- Current limit downstream ports

- Report overcurrent conditions

- BPHs must:

- Enable/disable power to downstream ports

- Power up at <100 mA</li>

- Limit inrush current (<44  $\Omega$  and 10  $\mu$ F)

- Functions must:

- Limit inrush currents

- Power up at <100 mA</li>

The feature set of the TPS2552D/53D meets each of these requirements. The integrated current limiting and overcurrent reporting is required by self-powered hubs. The logic-level enable and controlled rise times meet the need of both input and output ports on bus-powered hubs and the input ports for bus-powered functions.

### 10.2.3.2 Detailed Design Procedure

#### 10.2.3.2.1 Universal Serial Bus (USB) Power-Distribution Requirements

One application for this device is for current limiting in universal serial bus (USB) applications. The original USB interface was a 12-Mb/s or 1.5-Mb/s, multiplexed serial bus designed for low-to-medium bandwidth PC peripherals (e.g., keyboards, printers, scanners, and mice). As the demand for more bandwidth increased, the USB 2.0 standard was introduced increasing the maximum data rate to 480-Mb/s. The four-wire USB interface is conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub across long cables. Each function must provide its own regulated 3.3 V from the 5-V input or its own internal power supply. The USB specification classifies two different classes of devices depending on its maximum current draw. A device classified as low-power can draw up to 100 mA as defined by the standard. A device classified as high-power can draw up to 500 mA. It is important that the minimum current-limit threshold of the current-limiting power-switch exceed the maximum current-limit draw of the intended application. The latest USB standard should always be referenced when considering the current-limit threshold

The USB specification defines two types of devices as hubs and functions. A USB hub is a device that contains multiple ports for different USB devices to connect and can be self-powered (SPH) or bus-powered (BPH). A function is a USB device that is able to transmit or receive data or control information over the bus. A USB function can be embedded in a USB hub. A USB function can be one of three types included in the list below.

- Low-power, bus-powered function

- High-power, bus-powered function

- Self-powered function

SPHs and BPHs distribute data and power to downstream functions. The TPS2552D/53D have higher current capabilities than required for a single USB port allowing it to power multiple downstream ports.

## **11 Power Supply Recommendations**

## 11.1 Self-Powered and Bus-Powered Hubs

A SPH has a local power supply that powers embedded functions and downstream ports. This power supply must provide between 4.75 V to 5.25 V to downstream facing devices under full-load and no-load conditions. SPHs are required to have current-limit protection and must report overcurrent conditions to the USB controller. Typical SPHs are desktop PCs, monitors, printers, and stand-alone hubs.

A BPH obtains all power from an upstream port and often contains an embedded function. It must power up with less than 100 mA. The BPH usually has one embedded function, and power is always available to the controller of the hub. If the embedded function and hub require more than 100 mA on power up, the power to the embedded function may need to be kept off until enumeration is completed. This is accomplished by removing power or by shutting off the clock to the embedded function. Power switching the embedded function is not necessary if the aggregate power draw for the function and controller is less than 100 mA. The total current drawn by the bus-powered device is the sum of the current to the controller, the embedded function, and the downstream ports, and it is limited to 500 mA from an upstream port.

## 11.2 Low-Power Bus-Powered and High-Power Bus-Powered Functions

Both low-power and high-power bus-powered functions obtain all power from upstream ports. Low-power functions always draw less than 100 mA; high-power functions must draw less than 100 mA at power up and can draw up to 500 mA after enumeration. If the load of the function is more than the parallel combination of 44  $\Omega$  and 10  $\mu$ F at power up, the device must implement inrush current limiting.

## **11.3** Power Dissipation and Junction Temperature

The low on-resistance of the N-channel MOSFET allows small surface-mount packages to pass large currents. It is good design practice to estimate power dissipation and junction temperature. The below analysis gives an approximation for calculating junction temperature based on the power dissipation in the package. However, it is important to note that thermal analysis is strongly dependent on additional system level factors. Such factors include air flow, board layout, copper thickness and surface area, and proximity to other devices dissipating power. Good thermal design practice must include all system level factors in addition to individual component analysis.

Begin by determining the  $r_{DS(on)}$  of the N-channel MOSFET relative to the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{DS(on)}$  from the typical characteristics graph. Using this value, the power dissipation can be calculated using  $\Delta \pm 6$ .

$P_D = r_{DS(on)} \times I_{OUT}^2$

where

- P<sub>D</sub> = Total power dissipation (W)

- $r_{DS(on)}$  = Power switch on-resistance ( $\Omega$ )

- I<sub>OUT</sub> = Maximum current-limit threshold (A)

- This step calculates the total power dissipation of the N-channel MOSFET.

Finally, calculate the junction temperature:

$T_{J} = P_{D} \times \theta_{JA} + T_{A}$

where

- T<sub>A</sub> = Ambient temperature (°C)

- θ<sub>JA</sub> = Thermal resistance (°C/W)

- P<sub>D</sub> = Total power dissipation (W)

(7)

(6)

Compare the calculated junction temperature with the initial estimate. If they are not within a few degrees, repeat the calculation using the "refined"  $r_{DS(on)}$  from the previous calculation as the new estimate. Two or three iterations are generally sufficient to achieve the desired result. The final junction temperature is highly dependent on thermal resistance  $\theta_{JA}$ , and thermal resistance is highly dependent on the individual package and board layout. The *Thermal Information Table* provides example thermal resistances for specific packages and board layouts.

## 12 Layout

## 12.1 Layout Guidelines

- TI recommends placing the 100-nF bypass capacitor near the IN and GND pins, and make the connections using a low-inductance trace.

- TI recommends placing a high-value electrolytic capacitor and a 100-nF bypass capacitor on the output pin is recommended when large transient currents are expected on the output.

- The traces routing the RILIM resistor to the device should be as short as possible to reduce parasitic effects on the current limit accuracy.

- The PowerPAD should be directly connected to PCB ground plane using wide and short copper trace.

## 12.2 Layout Example

图 30. Layout Recommendation

## 13 器件和文档支持

## 13.1 器件支持

有关 TI 开关产品组合的信息,请访问此处。

## 13.2 相关链接

下面的表格列出了快速访问链接。范围包括技术文档、支持与社区资源、工具和软件,以及样片或购买的快速访问。

| 器件       | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|----------|-------|-------|-------|-------|-------|

| TPS2552D | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| TPS2553D | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

#### 表 5. 相关链接

## 13.3 接收文档更新通知

如需接收文档更新通知,请访问 www.ti.com.cn 网站上的器件产品文件夹。点击右上角的提醒我 (Alert me) 注册 后,即可每周定期收到已更改的产品信息。有关更改的详细信息,请查阅已修订文档中包含的修订历史记录。

### 13.4 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 13.5 商标

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 13.6 静电放电警告

这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

## 13.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 14 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对 本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type |         | Pins |      | Eco Plan     | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|--------------|---------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)          | Ball material | (3)                |              | (4/5)          |         |

| TPS2552DDBVR     | ACTIVE | SOT-23       | DBV     | 6    | 3000 | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | 15IL           | Samples |

| TPS2552DDBVT     | ACTIVE | SOT-23       | DBV     | 6    | 250  | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | 15IL           | Samples |

| TPS2553DDBVR     | ACTIVE | SOT-23       | DBV     | 6    | 3000 | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | 15JL           | Samples |

| TPS2553DDBVT     | ACTIVE | SOT-23       | DBV     | 6    | 250  | RoHS & Green | NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | 15JL           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

10-Dec-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

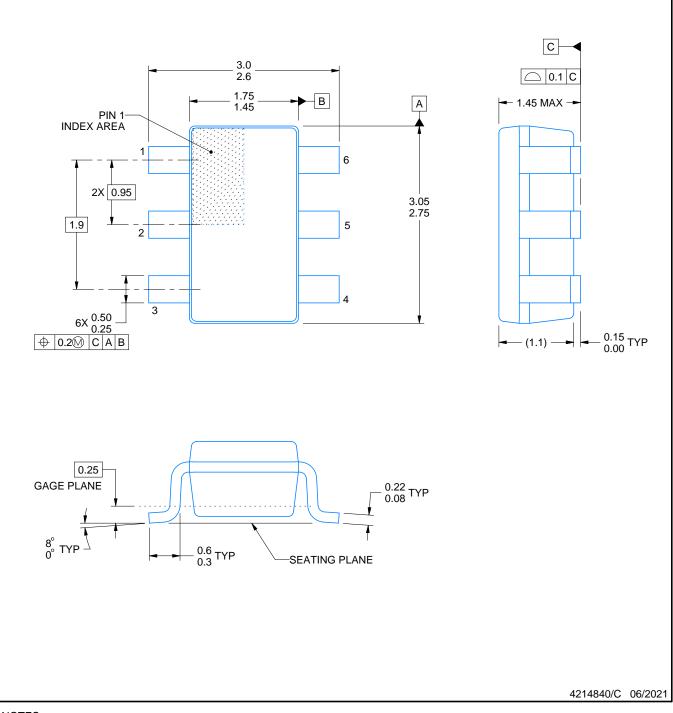

# **DBV0006A**

# **PACKAGE OUTLINE**

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation. 5. Refernce JEDEC MO-178.

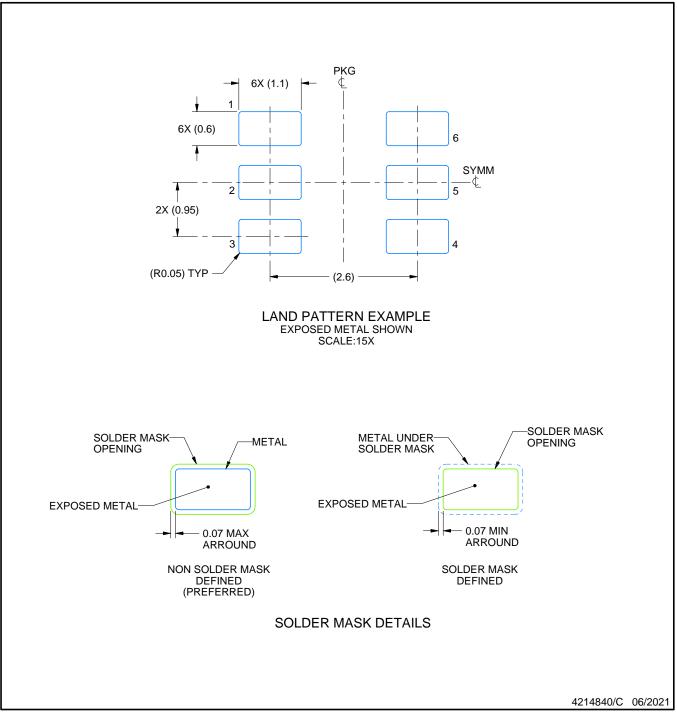

# **DBV0006A**

# **EXAMPLE BOARD LAYOUT**

## SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

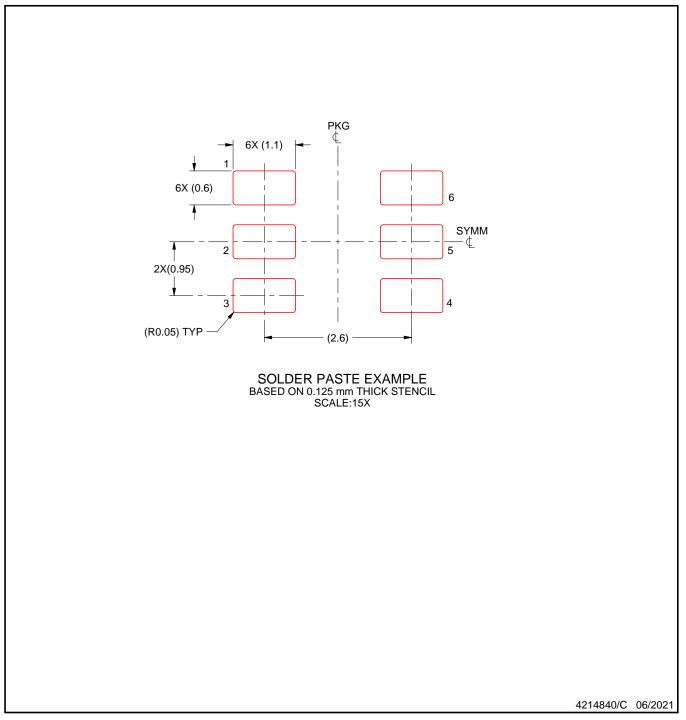

# **DBV0006A**

# **EXAMPLE STENCIL DESIGN**

## SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没 有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可 将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知 识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https:www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款 的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司