LMX2491

ZHCSFL5A - OCTOBER 2016-REVISED JANUARY 2017

## LMX2491 具有斜坡/线性调频生成功能的 6.4GHz 低噪声 RF PLL

#### 特性

- -227dBc/Hz 标准化锁相环 (PLL) 噪声

- 500MHz 至 6.4GHz 宽带 PLL

- 3.15V 至 5.25V 电荷泵 PLL 电源

- 多用途斜坡/超宽带信号源生成功能

- 200MHz 最大相位检测器频率

- 频移键控/相移键控 (FSK/PSK) 调制引脚

- 数字锁检测

- 3.3V 单电源供电

#### 应用

- 调频连续波 (FMCW) 雷达

- 军用雷达

- 微波回程

- 测试和测量

- 卫星通信

- 无线基础设施

- 适用于高速模数转换器/数模转换器 (ADC/DAC) 的 采样时钟

#### 3 说明

LMX2491 器件是一款具有斜坡/线性调频生成功能的低 噪声 6.4GHz 宽带  $\Delta$ - $\Sigma$  分数 N PLL。它由一个相位频 率检测器、可编程电荷泵以及适用于外部 VCO 的高频 输入组成。LMX2491 广泛支持各类灵活的斜坡功能, 包括 FSK、PSK 和多达 8 段的可配置分段线性 FM 调 制配置文件。该器件具有精密 PLL 分辨率和快速斜升 功能,相位检测器速率高达 200MHz。LMX2491 允许 读回其任一寄存器。LMX2491 可由 3.3V 单电源供电 运行。此外,该器件支持电压高达 5.25V 的电荷泵, 无需使用外部放大器即可提供相位噪声性能得到改善的 简易解决方案。

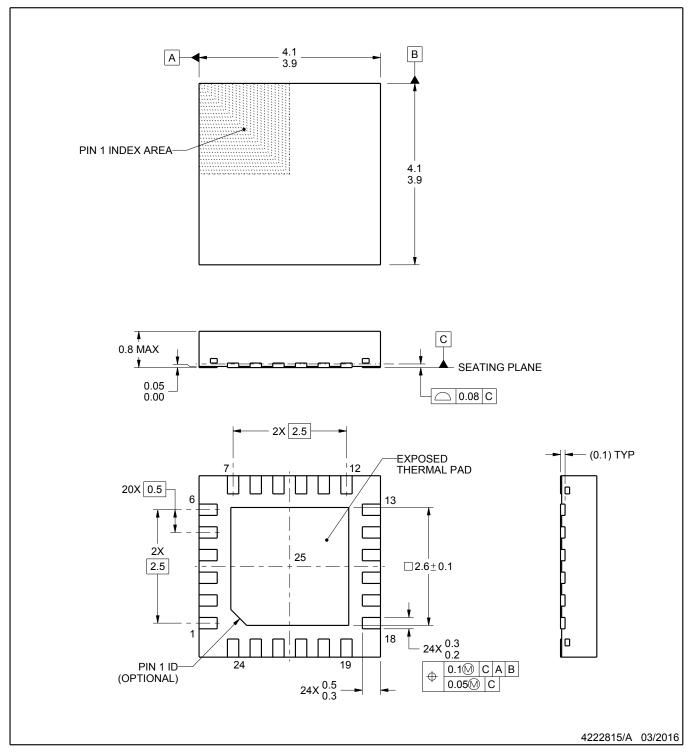

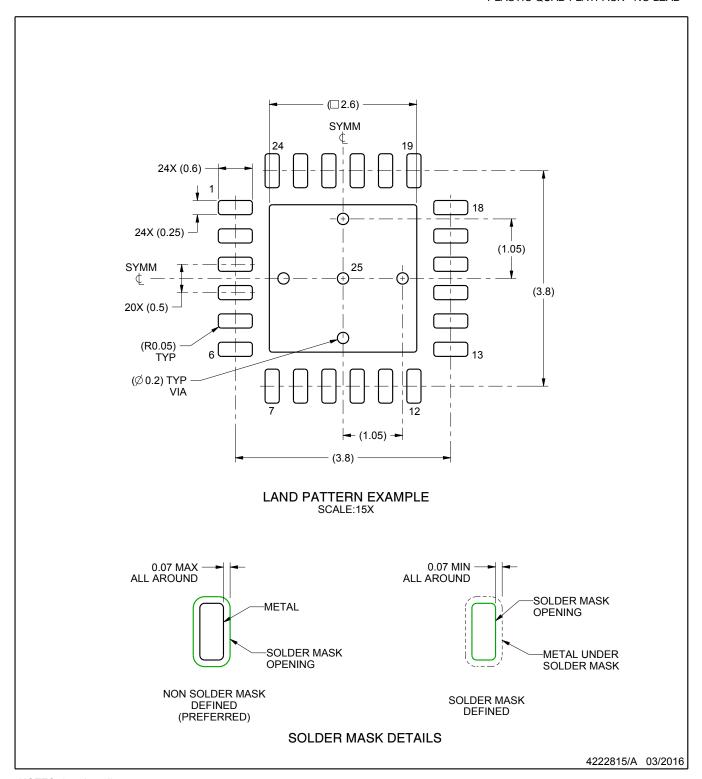

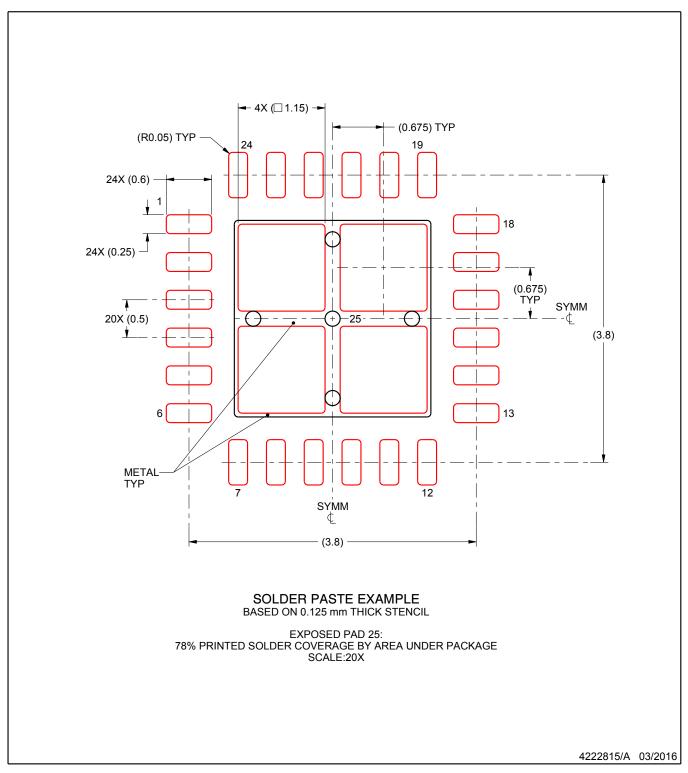

#### 器件信息

| 器件编号    | 封装        | 封装尺寸 (标称值)      |

|---------|-----------|-----------------|

| LMX2491 | WQFN (24) | 4.00mm x 4.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

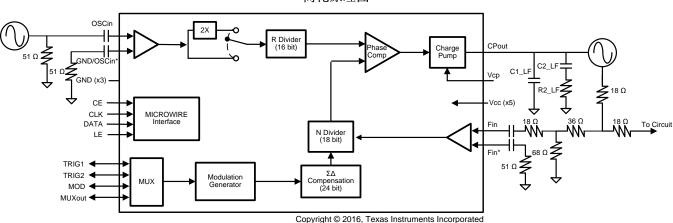

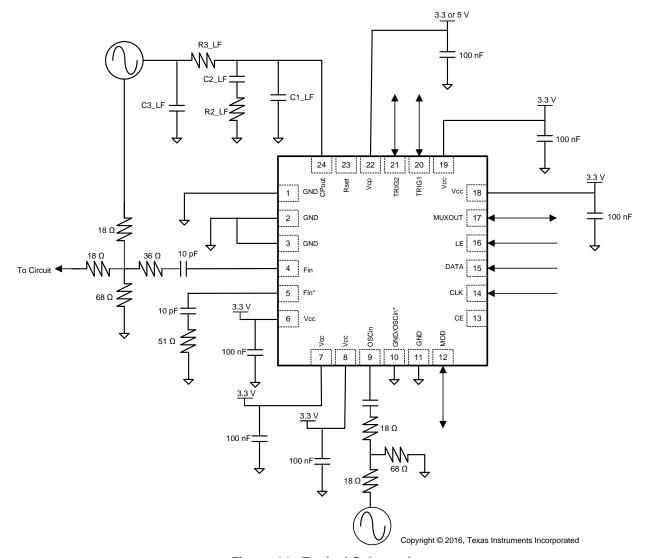

#### 简化原理图

#### 目录 2 Register Maps......14 Applications and Implementation ...... 27 4 修订历史记录 ...... 2 Pin Configuration and Functions ...... 3 5 Specifications......4 Power Supply Recommendations ...... 39 Absolute Maximum Ratings ...... 4 10 Layout...... 39 Storage Conditions...... 4 6.3 ESD Ratings......4 10.2 Layout Example ...... 40 Recommended Operating Conditions ...... 4 器件和文档支持......41 器件支持 .......41 Electrical Characteristics ...... 5 文档支持 .......41 Timing Requirements, Programming Interface (CLK, 11.3 接收文档更新通知 .......41 6.8 Typical Characteristics ...... 6 社区资源......41 商标......41 Detailed Description ......9 Overview .......9 静电放电警告.......41 Glossary......41 Functional Block Diagram ......9 12 机械、封装和可订购信息......41 Feature Description......9

### 4 修订历史记录

| Changes from Original (October 2016) to Revision A                | Page |

|-------------------------------------------------------------------|------|

| Deleted Charge pump output pin from the table                     | 4    |

| Changed to Supply voltage                                         |      |

| Changed to I/O input voltage                                      | 4    |

| Changed to Power down current                                     | 5    |

| Changed DATA field bit description                                | 6    |

| Added new plots in Typical Characteristics                        | 7    |

| Changed Table 1 title                                             | 9    |

| Added CMP0 and CMP1 definition. Changed Equation 1 description.   | 12   |

| Added Register Readback                                           | 13   |

| Added MSB bit description                                         | 14   |

| Changed the format in Window and f <sub>PD</sub> Frequency column | 21   |

| Changed to correct register bits location                         | 23   |

| Changed to correct value                                          | 25   |

| Added correct start time                                          | 26   |

| Added design details and plots in Typical Application             | 27   |

|                                                                   |      |

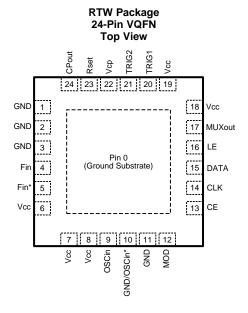

### 5 Pin Configuration and Functions

#### **Pin Functions**

| TERMINAL |                | TVDE         | DECODINE                                                                                                                                                                                    |  |

|----------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.      | NAME           | TYPE         | DESCRIPTION                                                                                                                                                                                 |  |

| 0        | DAP            | GND          | Die Attach Pad. Connect to PCB ground plane.                                                                                                                                                |  |

| 1        | GND            | GND          | Ground for charge pump.                                                                                                                                                                     |  |

| 2, 3     | GND            | GND          | round for Fin Buffer                                                                                                                                                                        |  |

| 4, 5     | Fin<br>Fin*    | Input        | complimentary high frequency input pins. Should be AC-coupled. If driving single-ended, inpedance as seen from Fin and Fin* pins looking outwards from the part should be roughly the lame. |  |

| 6        | Vcc            | Supply       | Power Supply for Fin Buffer                                                                                                                                                                 |  |

| 7        | Vcc            | Supply       | Supply for On-chip LDOs                                                                                                                                                                     |  |

| 8        | Vcc            | Supply       | Supply for OSCin Buffer                                                                                                                                                                     |  |

| 9        | OSCin          | Input        | Reference Frequency Input                                                                                                                                                                   |  |

| 10       | GND/<br>OSCin* | GND/Input    | Complimentary input for OSCin.  If not used, it is recommended to match the termination as seen from the OSCin terminal looking outwards. However, this may also be grounded as well.       |  |

| 11       | GND            | GND          | Ground for OSCin Buffer                                                                                                                                                                     |  |

| 12       | MOD            | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                              |  |

| 13       | CE             | Input        | Chip Enable                                                                                                                                                                                 |  |

| 14       | CLK            | GND          | Serial Programming Clock.                                                                                                                                                                   |  |

| 15       | DATA           | GND          | Serial Programming Data                                                                                                                                                                     |  |

| 16       | LE             | Input        | Serial Programming Latch Enable                                                                                                                                                             |  |

| 17       | MUXout         | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                              |  |

| 18       | Vcc            | Supply       | Supply for delta sigma engine.                                                                                                                                                              |  |

| 19       | Vcc            | Supply       | Supply for general circuitry.                                                                                                                                                               |  |

| 20       | TRIG1          | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                              |  |

| 21       | TRIG2          | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                              |  |

| 22       | Vcp            | Supply       | Power Supply for the charge pump.                                                                                                                                                           |  |

| 23       | Rset           | NC           | No connect.                                                                                                                                                                                 |  |

| 24       | CPout          | Output       | Charge Pump Output                                                                                                                                                                          |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                       |                                     | MIN             | MAX                   | UNIT |

|-----------------------|-------------------------------------|-----------------|-----------------------|------|

| V <sub>CP</sub>       | Supply voltage for charge pump      | V <sub>CC</sub> | 5.5                   | V    |

| V <sub>CC</sub>       | Supply voltage                      | -0.3            | 3.6                   | V    |

| V <sub>IN</sub>       | I/O input voltage                   | -0.3            | V <sub>CC</sub> + 0.3 | V    |

| T <sub>Solder</sub>   | Lead temperature (solder 4 seconds) |                 | 260                   | °C   |

| T <sub>Junction</sub> | Junction temperature                |                 | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 Storage Conditions

applicable before the DMD is installed in the final product

|                  |                         | MIN | MAX | UNIT |

|------------------|-------------------------|-----|-----|------|

| T <sub>stg</sub> | DMD storage temperature | -65 | 150 | °C   |

| $T_{DP}$         | Storage dew point       |     | 3   | ٥°   |

#### 6.3 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| \/                 | Floatroatatia diaaharaa | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2500 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                  | MIN             | NOM | MAX  | UNIT |

|-----------------|----------------------------|-----------------|-----|------|------|

| V <sub>CC</sub> | Supply voltage             | 3.15            | 3.3 | 3.45 | V    |

| $V_{CP}$        | Charge pump supply voltage | V <sub>CC</sub> |     | 5.25 | V    |

| T <sub>A</sub>  | Ambient temperature        | -40             |     | 85   | °C   |

| $T_{J}$         | Junction temperature       | -40             |     | 125  | °C   |

#### 6.5 Thermal Information

|                      |                                              | LMX2491    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTW (VQFN) | UNIT |

|                      |                                              | 24 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 39.4       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 7.1        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 20         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.6 Electrical Characteristics

$3.15~\text{V} \leq \text{V}_{\text{CC}} \leq 3.45~\text{V},~\text{V}_{\text{CC}} \leq \text{V}_{\text{CP}} \leq 5.25~\text{V},~-40~\text{°C} \leq \text{T}_{\text{A}} \leq 85~\text{°C},~\text{except as specified}.~\text{Typical values are at V}_{\text{CC}} = \text{V}_{\text{CP}} = 3.3~\text{V},~\text{V}_{\text{CC}} \leq \text{V}_{\text{CP}} \leq 5.25~\text{V},~\text{C}_{\text{CP}} \leq 5.25~\text{V},~\text{C}_{\text{CP}} \leq 85~\text{°C},~\text{except as specified}.$

|                        | PARAMETER                                 | TEST CO                                  | ONDITIONS                                        | MIN                   | TYP             | MAX                   | UNIT            |

|------------------------|-------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------|-----------------|-----------------------|-----------------|

|                        |                                           |                                          | f <sub>PD</sub> = 10 MHz                         |                       | 45              |                       |                 |

|                        |                                           | All Vcc pins                             | f <sub>PD</sub> = 100 MHz                        |                       | 50              |                       |                 |

|                        | Current consumption                       |                                          | f <sub>PD</sub> = 200 MHz                        |                       | 55              |                       | mA              |

| I <sub>CC</sub>        |                                           |                                          | $K_{PD} = 0.1 \text{ mA}$                        |                       | 2               |                       |                 |

|                        |                                           | Vcp pin                                  | K <sub>PD</sub> = 1.6 mA                         |                       | 10              |                       |                 |

|                        |                                           |                                          | K <sub>PD</sub> = 3.1 mA                         |                       | 19              |                       |                 |

| I <sub>CC</sub> PD     | Power down current                        | POWERDOWN                                |                                                  |                       | 3               |                       |                 |

|                        |                                           | OSC_DIFFR = 0,                           | doubler disabled                                 | 10                    |                 | 600                   |                 |

|                        | Frequency for OSCin                       | OSC_DIFFR = 0,                           | doubler enabled                                  | 10                    |                 | 300                   |                 |

| f <sub>OSCin</sub>     | terminal                                  | OSC_DIFFR = 1,                           | doubler disabled                                 | 10                    |                 | 1200                  | MHz             |

|                        |                                           | OSC_DIFFR = 1,                           | doubler enabled                                  | 10                    |                 | 600                   |                 |

| V <sub>OSCin</sub>     | Voltage for OSCin pin <sup>(1)</sup>      |                                          |                                                  | 0.5                   |                 | V <sub>CC</sub> - 0.5 | V <sub>PP</sub> |

| f <sub>Fin</sub>       | Frequency for Fin pin                     |                                          |                                                  | 500                   |                 | 6400                  | MHz             |

| P <sub>Fin</sub>       | Power for Fin pin                         | Single-ended ope                         | Single-ended operation                           |                       |                 | 5                     | dBm             |

| f <sub>PD</sub>        | Phase detector frequency                  |                                          |                                                  |                       |                 | 200                   | MHz             |

| PN1Hz                  | PLL figure of merit <sup>(2)</sup>        |                                          |                                                  |                       | -227            |                       | dBc/Hz          |

| PN10kHz                | Normalized PLL 1/f noise <sup>(2)</sup>   | Normalized to 10 GHz carrier.            | Normalized to 10-kHz offset for a 1-GHz carrier. |                       | -120            |                       | dBc/Hz          |

| I <sub>CPout</sub> TRI | Charge pump leakage tri-<br>state leakage |                                          |                                                  |                       |                 | 10                    | nA              |

| I <sub>CPout</sub> MM  | Charge pump mismatch (3)                  | V <sub>CPout</sub> = V <sub>CP</sub> / 2 |                                                  |                       | 5%              |                       |                 |

|                        |                                           |                                          | CPG = 1X                                         |                       | 0.1             |                       |                 |

| I <sub>CPout</sub>     | Charge pump current                       | $V_{CPout} = V_{CP} / 2$                 |                                                  |                       |                 |                       | mA              |

|                        |                                           |                                          | CPG = 31X                                        |                       | 3.1             |                       |                 |

| LOGIC OU               | TPUT TERMINALS (MUXout,                   | TRIG1, TRIG2, MO                         | DD)                                              |                       |                 | <u> </u>              |                 |

| V <sub>OH</sub>        | Output high voltage                       |                                          |                                                  | 0.8 × V <sub>CC</sub> | V <sub>CC</sub> |                       | V               |

| V <sub>OL</sub>        | Output low voltage                        |                                          |                                                  |                       | 0               | 0.2 × V <sub>CC</sub> | V               |

| LOGIC INP              | UT TERMINALS (CE, CLK, DA                 | ATA, LE, MUXout                          | TRIG1, TRIG2, MO                                 | D)                    |                 | *                     |                 |

| V <sub>IH</sub>        | Input high voltage                        |                                          |                                                  | 1.4                   |                 | V <sub>CC</sub>       | V               |

| V <sub>IL</sub>        | Input low voltage                         |                                          |                                                  |                       |                 | 0.6                   | V               |

| I <sub>IH</sub>        | Input leakage current                     |                                          |                                                  | -5                    | 1               | 5                     | μA              |

| t <sub>CE</sub> LOW    | Chip enable low time                      |                                          |                                                  | 5                     |                 |                       | μs              |

|                        |                                           |                                          |                                                  |                       |                 |                       |                 |

<sup>(1)</sup> For optimal phase noise performance, higher input voltage and a slew rate of at least 3 V/ns is recommended

PLL Noise Metrics are measured with a clean OSCin signal with a high slew rate using a wide loop bandwidth. The noise metrics model the PLL noise for an infinite loop bandwidth as:

PLL\_Total = 10 × log( 10<sup>PLL\_Flat / 10</sup> + 10<sup>PLL\_Flicker(Offset) / 10</sup>)

PLL\_Flat = PN1Hz + 20 × log(N) + 10 × log(f<sub>PD</sub> / 1 Hz)

PLL\_Flicker = PN10kHz - 10 × log(Offset / 10 kHz) + 20 × log(f<sub>VCO</sub> / 1 GHz)

(3) Charge pump mismatch varies as a function of charge pump voltage. Consult typical performance characteristics to see this variation.

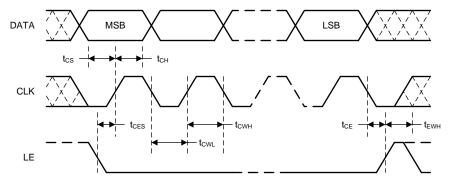

#### 6.7 Timing Requirements, Programming Interface (CLK, DATA, LE)

|                  |                            | MIN | TYP | MAX | UNIT |

|------------------|----------------------------|-----|-----|-----|------|

| t <sub>CE</sub>  | Clock to LE low time       | 10  |     |     | ns   |

| t <sub>CS</sub>  | Data to clock setup time   | 4   |     |     | ns   |

| t <sub>CH</sub>  | Data to clock hold time    | 4   |     |     | ns   |

| t <sub>CWH</sub> | Clock pulse width high     | 10  |     |     | ns   |

| t <sub>CWL</sub> | Clock pulse width low      | 10  |     |     | ns   |

| t <sub>CES</sub> | Enable to clock setup time | 10  |     |     | ns   |

| t <sub>EWH</sub> | Enable pulse width high    | 10  |     |     | ns   |

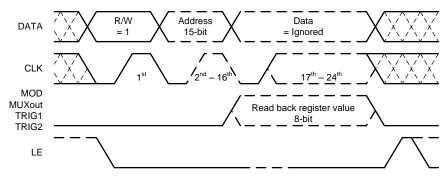

Figure 1. Serial Data Input Timing

There are several other considerations for programming:

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the LE signal, the data is sent from the shift register to an actual counter.

- If no LE signal is given after the last data bit and the clock is kept toggling, then these bits are read into the next lower register. This eliminates the need to send the address each time.

- A slew rate of at least 30 V/µs is recommended for the CLK, DATA, and LE signals

- Timing specs also apply to readback. Readback can be done through the MUXout, TRIG1, TRIG2, or MOD terminals.

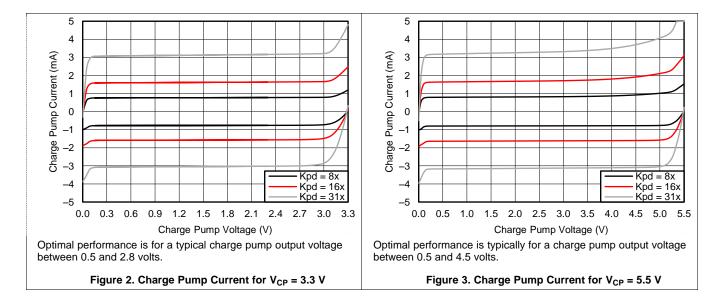

#### 6.8 Typical Characteristics

### **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

### **Typical Characteristics (continued)**

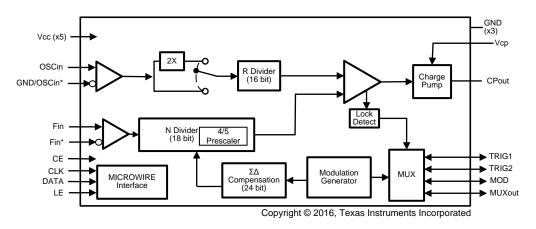

#### 7 Detailed Description

#### 7.1 Overview

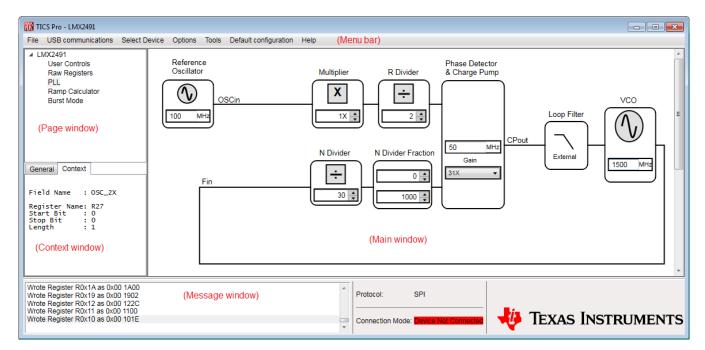

The LMX2491 is a microwave PLL, consisting of a reference input and divider, high frequency input and divider, charge pump, ramp generator, and other digital logic. The Vcc power supply pins run at a nominal 3.3 volts, while the charge pump supply pin, Vcp, operates anywhere from  $V_{CC}$  to 5 volts. The device is designed to operate with an external loop filter and VCO. Modulation is achieved by manipulating the MASH engine.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 OSCin Input

The reference can be applied in several ways. If using a differential input, this must be terminated differentially with a  $100-\Omega$  resistance and AC-coupled to the OSCin and GND/OSCin\* terminals. If driving this single-ended, then the GND/OSCin\* terminal may be grounded, although better performance is attained by connecting the GND/OSCin\* terminal through a series resistance and capacitance to ground to match the OSCin terminal impedance.

#### 7.3.2 OSCin Doubler

The OSCin doubler allows the input signal to the OSCin to be doubled to have higher phase detector frequencies. This works by clocking on both the rising and falling edges of the input signal, so it therefore requires a 50% input duty cycle.

#### 7.3.3 R Divider

The R counter is 16 bits divides the OSCin signal from 1 to 65535. If DIFF\_R = 0, then any value can be chosen in this range. If DIFF\_R = 1, then the divide is restricted to 2, 4, 8, and 16, but allows for higher OSCin frequencies.

#### 7.3.4 PLL N Divider

The 16-bit N divider divides the signal at the Fin terminal down to the phase detector frequency. It contains a 4/5 prescaler that creates minimum divide restrictions, but allows the N value to increment in values of one.

Table 1. Allowable Minimum N Divider Values

| MODULATOR ORDER                   | MINIMUM N DIVIDE |

|-----------------------------------|------------------|

| Integer Mode, 1st-Order Modulator | 16               |

| 2nd-Order Modulator               | 17               |

| 3rd-Order Modulator               | 19               |

| 4th-Order Modulator               | 25               |

#### 7.3.5 Fractional Circuitry

The fractional circuitry controls the N divider with delta sigma modulation that supports a programmable first, second, third, and fourth-order modulator. The fractional denominator is a fully programmable 24-bit denominator that can support any value from 1, 2, ...,  $2^{24}$ , with the exception when the device is running one of the ramps, and in this case it is a fixed size of  $2^{24}$ .

#### 7.3.6 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the R and N dividers and generates a correction voltage corresponding to the phase error. This voltage is converted to a correction current by the charge pump. The phase detector frequency,  $f_{PD}$ , can be calculated as follows:  $f_{PD} = f_{OSC_{in}} \times OSC_{2X} / R$ .

The charge pump supply voltage on this device,  $V_{CP}$ , can be either run at the  $V_{CC}$  voltage, or up to 5.25 volts to get higher tuning voltages to present to the VCO.

#### 7.3.7 External Loop Filter

The loop filter is external to the device and is application specific. Texas Instruments website has details on this at www.ti.com.

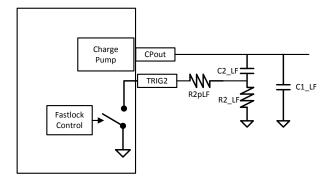

#### 7.3.8 Fastlock and Cycle Slip Reduction

This PLL has a Fastlock and a cycle slipping reduction feature. The user can enable these two features by programming FL\_TOC to a non-zero value. Every time PLL\_N (the feedback divider, register R17 and R16) is written, the Fastlock feature engages for the prescribed time set in FL\_TOC. There are 3 actions that can be enabled while the counter is running:

- 1. Change the charge pump current to the desired higher value FL\_CPG. Typically this value would be set to the maximum at 31x. This increases the loop bandwidth and hence reduces lock time.

- 2. Change the phase detector frequency with FL\_CSR to reduce cycle slipping. The phase detector frequency can be reduced by a factor 2 or 4 to reduce cycle slipping.

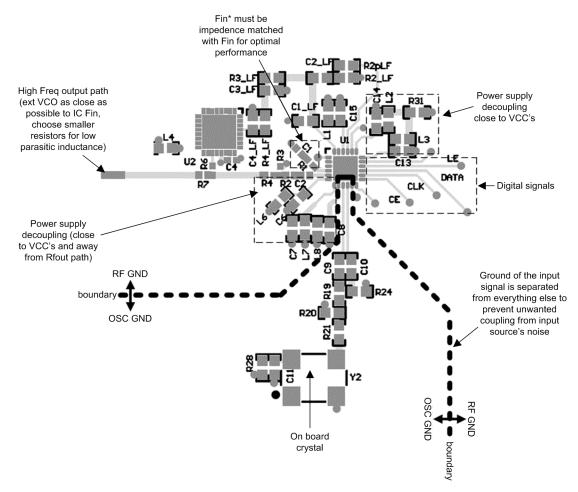

- 3. The loop filter can be configured to have a switchable R2 resistor to increase loop bandwidth and hence reduce lock time. A resistor R2pLF is added in parallel to R2\_LF and connected to the a terminal on the PLL to use the internal switch. Any of the terminal MUXout, MOD, TRIG1,or TRIG2 can be configured for the function. The terminal configuration is set as *Output TOC Running*. Also set the terminal as *output inverted OD* (OD for open-drain) so the output will be high impedance in normal operation and act as ground in Fastlock. The suggested schematic for that feature is shown in Figure 12.

Figure 12. Suggested Schematic to Enable the Variable Loop Bandwidth Filter In Fastlock Mode

Table 2. Fastlock Settings: Charge Pump Gain and Fastlock Pin Status

| PARAMETER                                    | NORMAL OPERATION | FASTLOCK OPERATION |

|----------------------------------------------|------------------|--------------------|

| Charge Pump Gain                             | CPG              | FL_CPG             |

| Device Pin<br>(TRIG1, TRIG2, MOD, or MUXout) | High Impedance   | Grounded           |

The resistor and the charge pump current are changed simultaneously so that the phase margin remains the same while the loop bandwidth is by a factor of K as shown in the following table:

Table 3. Suggested Equations to Calculate R2pLF

|        | PARAMETER                    | CALCULATION                      |

|--------|------------------------------|----------------------------------|

| FL_CPG | Charge Pump Gain in Fastlock | Typically use the highest value. |

| K      | Loop Bandwidth Multiplier    | K = sqrt(FL_CPG / CPG)           |

| R2pLF  | External Resistor            | R2 / (K - 1)                     |

Cycle slip reduction is another method that can also be used to speed up lock time by reducing cycle slipping. Cycle slipping typically occurs when the phase detector frequency exceeds about 100x the loop bandwidth of the PLL. Cycle slip reduction works in a different way than fastlock. To use this, the phase detector frequency is decreased while the charge pump current is simultaneously increased by the same factor. Although the loop bandwidth is unchanged, the ratio of the phase detector frequency to the loop bandwidth is, and this is helpful for cases when the phase detector frequency is high. Because cycle slip reduction changes the phase detector rate, it also impacts other things that are based on the phase detector rate, such as the fastlock timeout-counter and ramping controls.

#### 7.3.9 Lock Detect and Charge Pump Voltage Monitor

The LMX2491 offers two methods to determine if the PLL is in lock: charge pump voltage monitoring and digital lock detect. These features can be used individually or in conjunction to give a reliable indication of when the PLL is in lock. The output of this detection can be routed to the TRIG1, TRIG2, MOD, or MUXout terminals.

#### 7.3.9.1 Charge Pump Voltage Monitor

The charge pump voltage monitor allows the user to set low (CMP\_THR\_LOW) and high (CMP\_THR\_HIGH) thresholds for a comparator that monitors the charge pump output voltage.

Table 4. Desired Comparator Threshold Register Settings for Two Charge Pump Supplies

| V <sub>CP</sub> | THRESHOLD                                  | SUGGESTED LEVEL    |  |

|-----------------|--------------------------------------------|--------------------|--|

| 3.3 V           | CPM_THR_LOW<br>= (Vthresh + 0.08) / 0.085  | 6 for 0.5-V limit  |  |

| 3.3 V           | CPM_THR_HIGH<br>= (Vthresh - 0.96) / 0.044 | 42 for 2.8-V limit |  |

| 5.0 V           | CPM_THR_LOW<br>= (Vthresh + 0.056) / 0.137 | 4 for 0.5-V limit  |  |

| 5.0 V           | CPM_THR_HIGH<br>= (Vthresh -1.23) / 0.071  | 46 for 4.5-V limit |  |

#### 7.3.9.2 Digital Lock Detect

Digital lock detect works by comparing the phase error as presented to the phase detector. If the phase error plus the delay as specified by the PFD\_DLY bit is outside the tolerance as specified by DLD\_TOL, then this comparison would be considered to be an error, otherwise passing. The DLD\_ERR\_CNT specifies how may errors are necessary to cause the circuit to consider the PLL to be unlocked. The DLD\_PASS\_CNT specifies how many passing comparisons are necessary to cause the PLL to be considered to be locked and also resets the count for the errors. The DLD\_TOL value should be set to no more than half of a phase detector period plus the PFD\_DLY value. The DLD\_ERR\_CNT and DLD\_PASS\_CNT values can be decreased to make the circuit more sensitive. If the circuit is too sensitive, then chattering can occur and the DLD\_ERR\_CNT, DLD\_PASS\_CNT, or DLD\_TOL values should be increased.

#### NOTE

If the OSCin signal goes away and there is no noise or self-oscillation at the OSCin pin, then it is possible for the digital lock detect to indicate a locked state when the PLL really is not in lock. If this is a concern, then digital lock detect can be combined with charge pump voltage monitor to detect this situation.

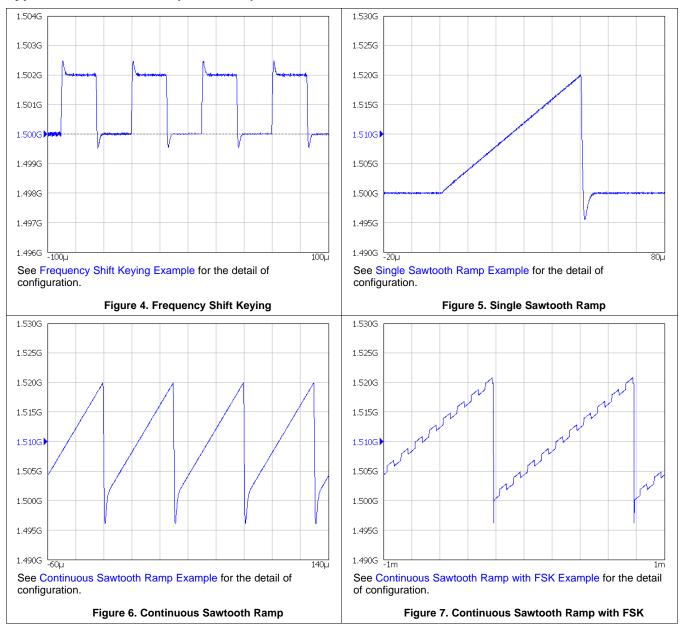

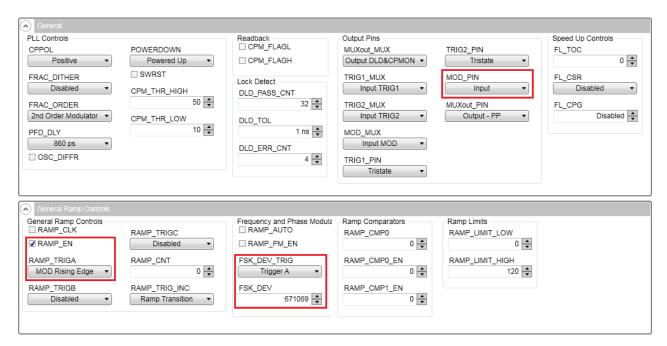

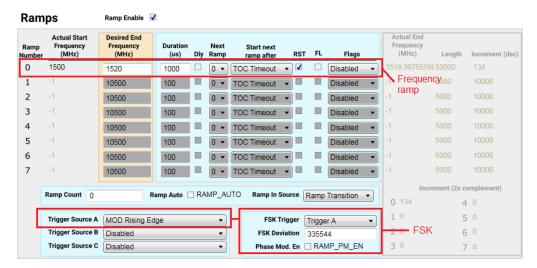

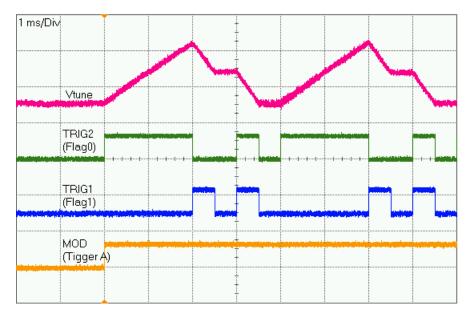

#### 7.3.10 FSK/PSK Modulation

Two-level FSK or PSK modulation can be created whenever a trigger event, as defined by the FSK\_TRIG field is detected. This trigger can be defined as a transition on a terminal (TRIG1, TRIG2, MOD, or MUXout) or done purely in software. The RAMP\_PM\_EN bit defines the modulation to be either FSK or PSK and the FSK\_DEV register determines the amount of the deviation. Remember that the FSK\_DEV[32:0] field is programmed as the 2's complement of the actual desired FSK\_DEV value. This modulation can be added to the modulation created from the ramping functions as well.

Table 5. How to Obtain Deviation for Two Types of Modulation

| RAMP_PM_EN | MODULATION TYPE | DEVIATION                                   |

|------------|-----------------|---------------------------------------------|

| 0          | 2 Level FSK     | f <sub>PD</sub> × FSK_DEV / 2 <sup>24</sup> |

| 1          | 2 Level PSK     | 360° × FSK_DEV / 2 <sup>24</sup>            |

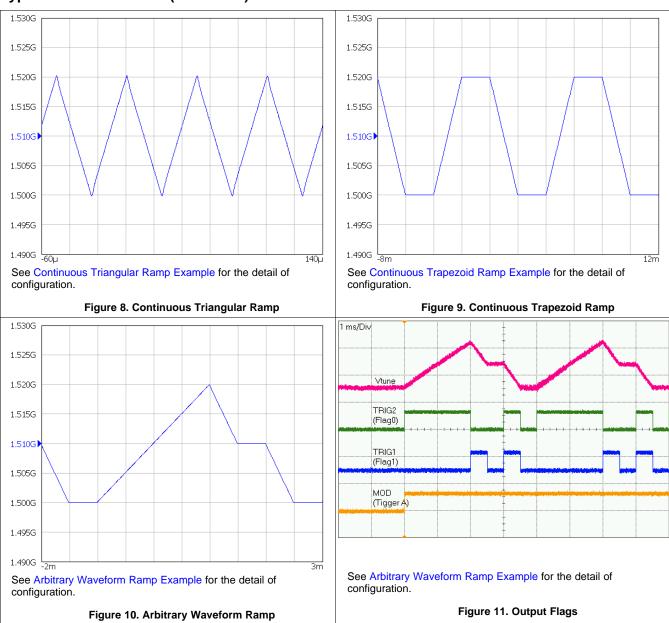

#### 7.3.11 Ramping Functions

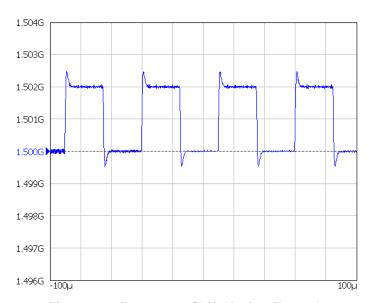

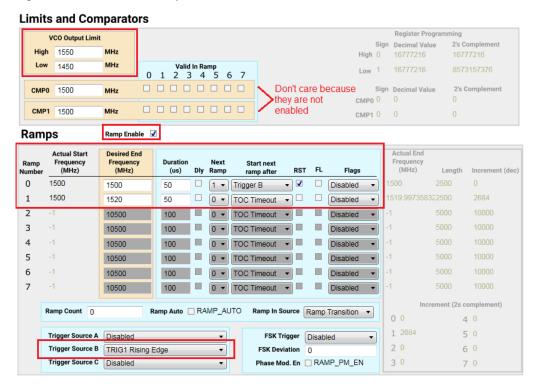

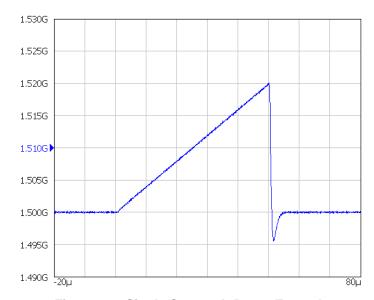

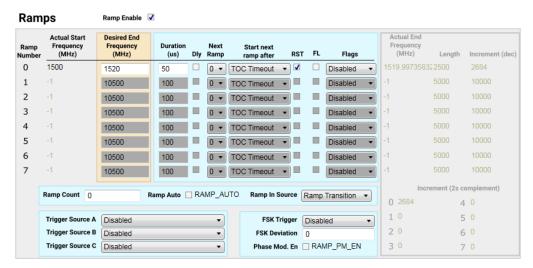

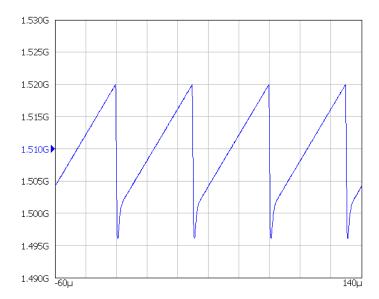

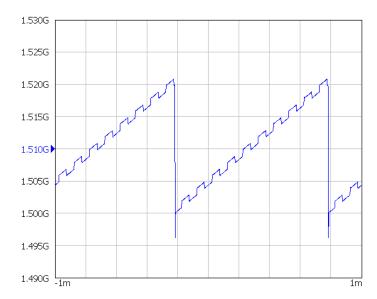

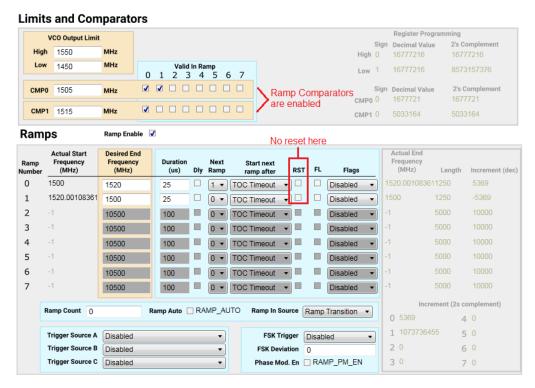

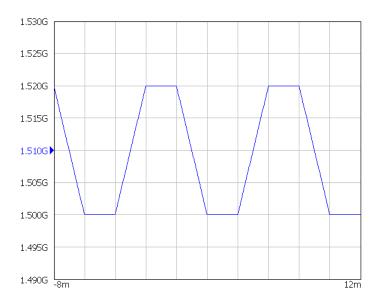

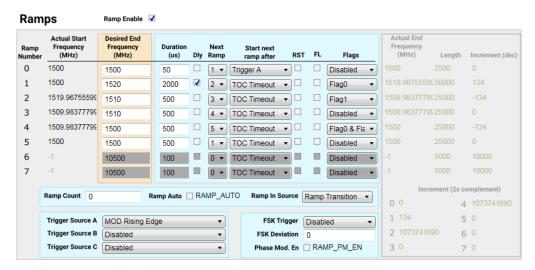

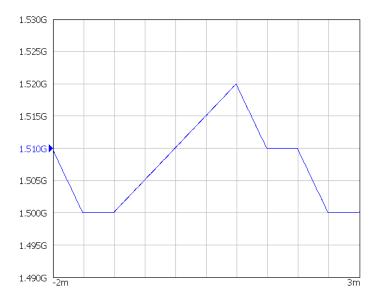

The LMX2491 supports a broad and flexible class of FMCW modulation formed by up to 8 linear ramps. When the ramping function is running, the denominator is fixed to a forced value of  $2^{24} = 16777216$ . The waveform always starts at RAMP0 when the LSB of the PLL\_N (R16) is written to. After it is set up, it starts at the initial frequency and have piecewise linear frequency modulation that deviates from this initial frequency as specified by the modulation. Each of the eight ramps can be individually programmed. Various settings are as follows:

Table 6. Register Descriptions of the Ramping Function

| RAMP<br>CHARACTERISTIC | PROGRAMMING FIELD<br>NAME           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ramp Length            | RAMPx_LEN<br>RAMPx_DLY              | The user programs the length of the ramp in phase detector cycles. If RAMPx_DLY = 1, then each count of RAMPx_LEN is actually two phase detector cycles.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Ramp Slope             | RAMPx_LEN<br>RAMPx_DLY<br>RAMPx_INC | The user does not directly program slope of the line, but rather this is done by defining how long the ramp is and how much the fractional numerator is increased per phase detector cycle. The value for RAMPx_INC is calculated by taking the total expected increase in the frequency, expressed in terms of how much the fractional numerator increases, and dividing it by RAMPx_LEN. The value programmed into RAMPx_INC is actually the two's complement of the desired mathematical value. |  |  |  |  |

| Trigger for Next Ramp  | RAMPx_NEXT_TRIG                     | The event that triggers the next ramp can be defined to be the ramp finishing or can wait for a trigger as defined by Trigger A, Trigger B, or Trigger C.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Next Ramp              | RAMPx_NEXT                          | This sets the ramp that follows. Waveforms are constructed by defining a charamp segments. To make the waveform repeat, make RAMPx_NEXT point the first ramp in the pattern.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Ramp Fastlock          | RAMPx_FL                            | This allows the ramp to use a different charge pump current or use Fastlock                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Ramp Flags             | RAMPx_FLAG                          | This allows the ramp to set a flag that can be routed to external terminals to trigger other devices.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

#### 7.3.11.1 Ramp Count

If it is desired that the ramping waveform keep repeating, then all that is needed is to make the RAMPx\_NEXT of the final ramp equal to the first ramp. This runs until the RAMP\_EN bit is set to zero. If this is not desired, then one can use the RAMP\_COUNT to specify how may times the specified pattern is to repeat.

#### 7.3.11.2 Ramp Comparators and Ramp Limits

The ramp comparators and ramp limits use programable thresholds to allow the device to detect whenever the modulated waveform frequency crosses a limit as set by the user. The difference between these is that comparators set a flag to alert the user while a ramp limits prevent the frequency from going beyond the prescribed threshold. In either case, these thresholds are expressed by programming the Extended\_Fractional\_Numerator. CMP0 and CMP1 are two separated comparators but they work in the same fashion.

Extended Fractional Numerator = Fractional Numerator + (N - N\*) x 2<sup>24</sup>

(1)

In Equation 1, N\* is the PLL feedback value without ramping. Fractional Numerator and N are the new values as defined by the threshold frequency. The actual value programmed is the 2's complement of Extended Fractional Numerator.

Table 7 Register Descriptions of Ramp Comparators and Limits

|    | rabio i regioto | - Boodingtions of Kamp Comparators and Ellinto |

|----|-----------------|------------------------------------------------|

| PE | PROGRAMMING BIT | THRESHOLD                                      |

|    | DAMP LIMIT LOW  | Lawrent Carlo                                  |

| TYPE                | PROGRAMMING BIT        | THRESHOLD                                                                                                                                                                                                                                                                      |

|---------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Down Limite         | RAMP_LIMIT_LOW         | Lower Limit                                                                                                                                                                                                                                                                    |

| Ramp Limits         | RAMP_LIMIT_HIGH        | Upper Limit                                                                                                                                                                                                                                                                    |

| Ramp<br>Comparators | RAMP_CMP0<br>RAMP_CMP1 | For the ramp comparators, if the ramp is increasing and exceeds the value as specified by RAMP_CMPx, then the flag goes high, otherwise it is low. If the ramp is decreasing and goes below the value as specified by RAMP_CMPx, then the flag goes high, otherwise it is low. |

#### 7.3.12 Power-on-reset (POR)

The power-on-reset circuitry sets all the registers to a default state when the device is powered up. This same reset can be done by programming SWRST = 1. In the programming section, the power on reset state is given for all the programmable fields.

#### 7.3.13 Register Readback

The LMX2491 allows any of its registers to be read back, MOD, MUXout, TRIG1 or TRIG2 pin can be programmed to support register-readback serial-data output. To read back a certain register value, follow the following steps:

- 1. Set the R/W bit to 1; the data field contents are ignored.

- 2. Send the register to the device; readback serial data will be output starting at the 17<sup>th</sup> clock cycle.

Figure 13. Register Readback Timing Diagram

#### 7.4 Device Functional Modes

The two primary ways to use the LMX2491 are to run it to generate a set of frequencies

#### 7.4.1 Continuous Frequency Generator

In this mode, the LMX2491 generates a single frequency that only changes when the N divider is programmed to a new value. In this mode, the RAMP EN bit is set to 0 and the ramping controls are not used. The fractional denominator can be programmed to any value from 1 to 16777216. In this kind of application, the PLL is tuned to different channels, but at each channel, the goal is to generate a stable fixed frequency.

#### 7.4.1.1 Integer Mode Operation

In integer mode operation, the VCO frequency needs to be an integer multiple of the phase detector frequency. This can be the case when the output frequency or frequencies are nicely related to the input frequency. As a rule of thumb, if this an be done with a phase detector of as high as the lesser of 10 MHz or the OSCin frequency, then this makes sense. To operate the device in integer mode, disable the fractional circuitry by programming the fractional order (FRAC\_ORDER), dithering (FRAC\_DITH), and numerator (FRAC\_NUM) to zero.

#### **Device Functional Modes (continued)**

#### 7.4.1.2 Fractional Mode Operation

In fractional mode, the output frequency does not need to be an integer multiple of the phase detector frequency. This makes sense when the channel spacing is more narrow or the input and output frequencies are not nicely related. There are several programmable controls for this such as the modulator order, fractional dithering, fractional numerator, and fractional denominator. There are many trade-offs with choosing these, but here are some guidelines

**Table 8. Fractional Mode Register Descriptions and Recommendations**

| PARAMETER                               | FIELD NAME           | HOW TO CHOOSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fractional Numerator and<br>Denominator | FRAC_NUM<br>FRAC_DEN | The first step is to find the fractional denominator. To do this, find the frequency that divides the phase detector frequency by the channel spacing. For instance, if the output ranges from 5000 to 5050 in 5-MHz steps and the phase detector is 100 MHz, then the fractional denominator is 100 MHz / $5 = 20$ . So for a an output of 5015 MHz, the N divider would be $50 + 3/20$ . In this case, the fractional numerator is 3 and the fractional denominator is 20. Sometimes when dithering is used, it makes sense to express this as a larger equivalent fraction. Note that if ramping is active, the fractional denominator is forced to $2^{24}$ . |

| Fractional Order                        | FRAC_ORDER           | There are many trade-offs, but in general try either the 2nd or 3rd-order modulator as starting points. The 3rd-order modulator may give lower main spurs, but may generate others. Also if dithering is involved, it can generate phase noise.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Dithering                               | FRAC_DITH            | Dithering can reduce some fractional spurs, but add noise. Consult application note AN-1879 Fractional N Frequency Synthesis for more details on this.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### 7.4.2 Modulated Waveform Generator

In this mode, the device can generate a broad class of frequency sweeping waveforms. The user can specify up to 8 linear segments to generate these waveforms. When the ramping function is running, the denominator is fixed to a forced value of  $2^{24} = 16777216$

In addition to the ramping functions, there is also the capability to use a terminal to add phase or frequency modulation that can be done by itself or added on top of the waveforms created by the ramp generation functions.

#### 7.5 Programming

#### 7.5.1 Loading Registers

The device is programmed using several 24-bit registers. Each register consists of a data field, an address field, and a R/W bit. The MSB is the R/W bit. 0 means register write while 1 means register read. The following 15 bits of the register are the address, followed by the next 8 bits of data. The user has the option to pull the LE terminal high after this data, or keep sending data and it applies this data to the next lower register. So instead of sending three registers of 24 bits each, one could send a single 40-bit register with the 16 bits of address and 24 bits of data. For that matter, the entire device could be programmed as a single register if desired.

#### 7.6 Register Maps

Registers are programmed in REVERSE order from highest to lowest. Registers NOT shown in this table or marked as reserved can be written as all 0s unless otherwise stated. The POR value is the power on reset value that is assigned when the device is powered up or the SWRST bit is asserted.

Table 9. Register Map

| REGI   | STER      | D7 | D7 D6 D5 D4 D3 D2 D1 D0      |   |   |   | POR |   |   |      |

|--------|-----------|----|------------------------------|---|---|---|-----|---|---|------|

| 0      | 0         | 0  | 0                            | 0 | 1 | 1 | 0   | 0 | 0 | 0x18 |

| 1      | 0x1       |    | Reserved                     |   |   |   |     |   |   |      |

| 2      | 0x2       | 0  | 0 0 0 0 SWRST POWERDOWN[1:0] |   |   |   |     |   |   | 0x00 |

| 3 - 15 | 0x3 - 0xF |    | Reserved                     |   |   |   |     |   |   |      |

| 16     | 0x10      |    | PLL_N[7:0]                   |   |   |   |     |   |   |      |

### **Register Maps (continued)**

**Table 9. Register Map (continued)**

|                      |                                                                                                                                                                                     |                                                                                                                                                                                  | 510 01 1108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | jiotoi iliap                 | (OOIIIIII                                | <i>-</i>        |                   |                   |              |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|-----------------|-------------------|-------------------|--------------|

| ISTER                | D7                                                                                                                                                                                  | D6                                                                                                                                                                               | D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D4                           | D3                                       | D2              | D1                | D0                | POR          |

| 0x11                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PLL_N                        | l[15:8]                                  |                 |                   |                   | 0x00         |

| 0x12                 | 0                                                                                                                                                                                   | FRA                                                                                                                                                                              | AC_ORDER[                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2:0]                         | FRAC_DI                                  | THER[1:0]       | PLL_N             | I[17:16]          | 0x00         |

| 0x13                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_N                       | IUM[7:0]                                 |                 |                   |                   | 0x00         |

| 0x14                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_N                       | UM[15:8]                                 |                 |                   |                   | 0x00         |

| 0x15                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_NU                      | JM[23:16]                                |                 |                   |                   | 0x00         |

| 0x16                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_D                       | DEN[7:0]                                 |                 |                   |                   | 0x00         |

| 0x17                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_D                       | EN[15:8]                                 |                 |                   |                   | 0x00         |

| 0x18                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRAC_DE                      | EN[23:16]                                |                 |                   |                   | 0x00         |

| 0x19                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PLL_I                        | R[7:0]                                   |                 |                   |                   | 0x04         |

| 0x1A                 |                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PLL_F                        | R[15:8]                                  |                 |                   |                   | 0x00         |

| 0x1B                 | 0                                                                                                                                                                                   | FL_CS                                                                                                                                                                            | R[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PFD_D                        | LY[1:0]                                  | PLL_R_<br>DIFF  | 0                 | OSC_2X            | 0x08         |

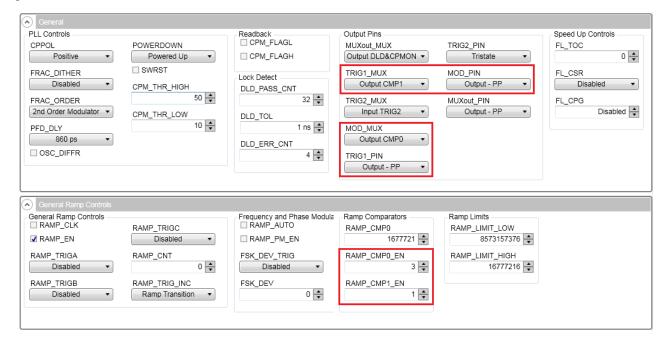

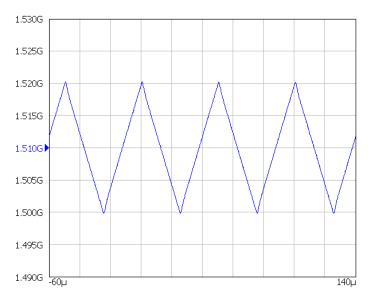

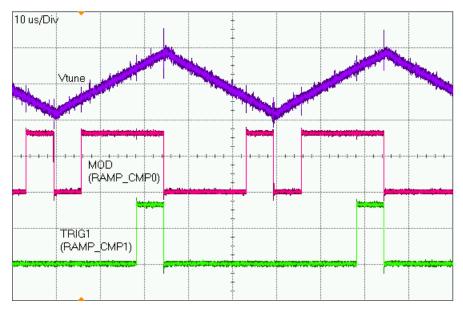

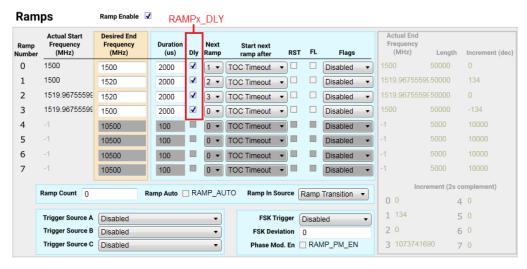

| 0x1C                 | 0                                                                                                                                                                                   | 0                                                                                                                                                                                | CPPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |                                          | CPG[4:0]        |                   |                   | 0x00         |