SNLS318D - JANUARY 2010 - REVISED APRIL 2013

# DS99R124Q 5 - 43 MHz 18-bit Color FPD-Link II to FPD-Link Converter

Check for Samples: DS99R124Q

# **FEATURES**

- 5 43 MHz Support (140 Mbps to 1.2 Gbps Serial Link)

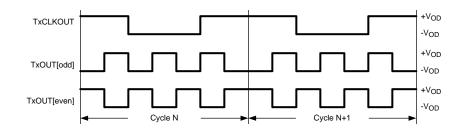

- 4-Channel (3 data + 1 Clock) FPD-Link LVDS Outputs

- 3 Low-Speed Over-Sampled LVCMOS Outputs •

- AC Coupled STP Interconnect up to 10 Meters in Length

- Integrated Input Termination •

- @ Speed Link BIST Mode and Reporting Pin

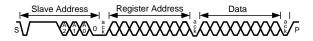

- **Optional I2C Compatible Serial Control Bus**

- RGB666 + VS, HS, DE Converted from 1 Pair

- **Power Down Mode Minimizes Power** Dissipation

- FAST Random Data Lock; no Reference Clock Required

- Adjustable Input Receive Equalization

- LOCK (Real Time Link Status) Reporting Pin .

- Low EMI FPD-Link Output •

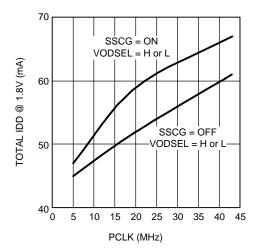

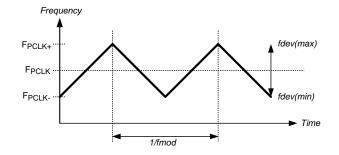

- SSCG Option for Lower EMI

- 1.8V or 3.3V Compatible I/O Interface

- Automotive Grade Product: AEC-Q100 Grade 2 Qualified

- >8 kV HBM and ISO 10605 ESD Rating

# APPLICATIONS

- Automotive Display for Navigation

- Automotive Display for Entertainment

# DESCRIPTION

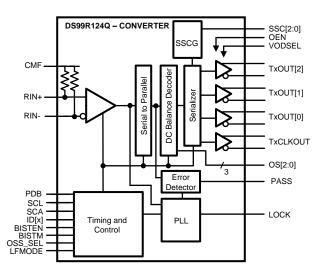

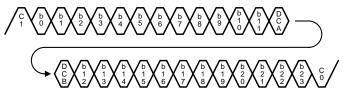

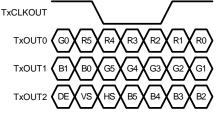

The DS99R124Q converts FPD-Link II to FPD-Link. It translates a high-speed serialized interface with an embedded clock over a single pair (FPD-Link II) to three LVDS data/control streams and one LVDS clock pair (FPD-Link). This serial bus scheme greatly eases system design by eliminating skew problems between clock and data, reduces the number of connector pins, reduces the interconnect size, weight, and cost, and overall eases PCB layout. In addition, internal DC balanced decoding is used to support AC-coupled interconnects.

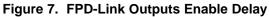

The DS99R124Q converter recovers the data (RGB) and control signals and extracts the clock from a serial stream (FPD-Link II). It is able to lock to the incoming data stream without the use of a training sequence or special SYNC patterns and does not require a reference clock. A link status (LOCK) output signal is provided.

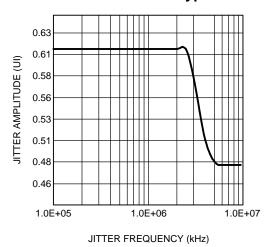

Adjustable input equalization of the serial input stream provides compensation for transmission medium losses of the cable and reduces the mediuminduced deterministic jitter. EMI is minimized by the use of low voltage differential signaling, output state select feature, and additional output spread spectrum generation.

With fewer wires to the physical interface of the display, FPD-Link output with LVDS technology is ideal for high speed, low power and low EMI data transfer.

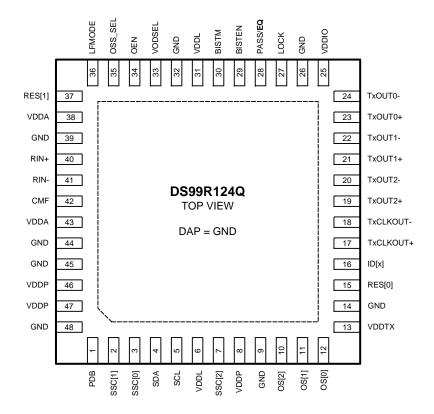

The DS99R124Q is offered in a 48-pin WQFN package and is specified over the automotive AEC-Q100 Grade 2 temperature range of -40°C to +105°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

TEXAS INSTRUMENTS

SNLS318D - JANUARY 2010 - REVISED APRIL 2013

www.ti.com

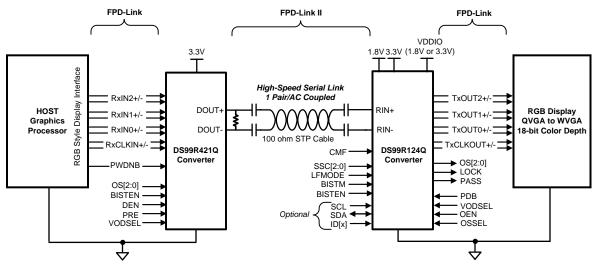

### **Applications Diagram**

Figure 1.

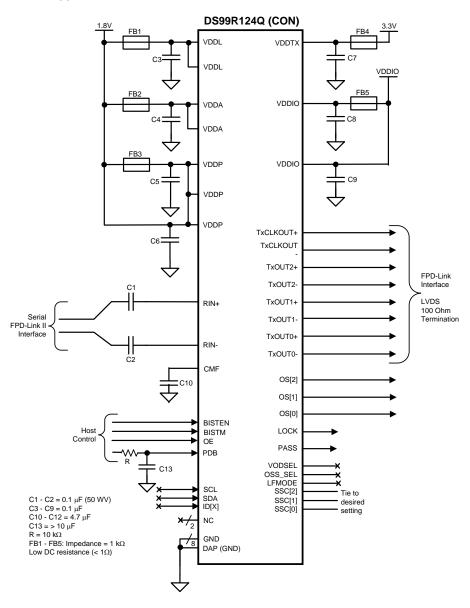

### DS99R124Q Pin Diagram

DS99R124Q

www.ti.com

#### SNLS318D-JANUARY 2010-REVISED APRIL 2013

| PIN | DESCRIPTIONS |

|-----|--------------|

|-----|--------------|

|                      | D:n #           |                                    |                                                                                                                                                                                                                                                         |

|----------------------|-----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | Pin #           | I/O, Type                          | Description                                                                                                                                                                                                                                             |

| FPD-Link II In       | 1               |                                    |                                                                                                                                                                                                                                                         |

| RIN+                 | 40              | I, LVDS                            | True input<br>The input must be AC coupled with a 100 nF capacitor. Internal termination.                                                                                                                                                               |

| RIN-                 | 41              | I, LVDS                            | Inverting input<br>The input must be AC coupled with a 100 nF capacitor. Internal termination.                                                                                                                                                          |

| CMF                  | 42              | I, Analog                          | Common-Mode Filter VCM center-tap is a virtual ground which maybe ac-coupled to ground to increase receiver common mode noise immunity. Recommended value is 4.7 $\mu$ F or higher.                                                                     |

| FPD-Link Outp        | out Interface   |                                    | •                                                                                                                                                                                                                                                       |

| TxOUT[2:0]+          | 19, 21, 23      | O, LVDS                            | True LVDS Data Output This pair should have a 100 $\Omega$ termination for standard LVDS levels.                                                                                                                                                        |

| TxOUT[2:0]-          | 20, 22, 24      | O, LVDS                            | Inverting LVDS Data Output This pair should have a 100 $\Omega$ termination for standard LVDS levels.                                                                                                                                                   |

| TxCLKOUT+            | 17              | O, LVDS                            | True LVDS Clock Output This pair should have a 100 $\Omega$ termination for standard LVDS levels.                                                                                                                                                       |

| TxCLKOUT-            | 18              | O, LVDS                            | Inverting LVDS Clock Output This pair should have a 100 $\Omega$ termination for standard LVDS levels.                                                                                                                                                  |

| LVCMOS Outp          | outs            |                                    |                                                                                                                                                                                                                                                         |

| OS[2:0]              | 10, 11, 12      | O, LVMOS                           | Over-Sampled Low Frequency Outputs<br>These bits map to the DS99R421's OS[2:0] over-sampled low-frequency inputs. Signals must<br>be slower the TxCLK/5. On the DS90UR241 these map to the DIN[23:21] inputs. OS0 =<br>DIN21, OS1 = DIN22, OS2 = DIN23. |

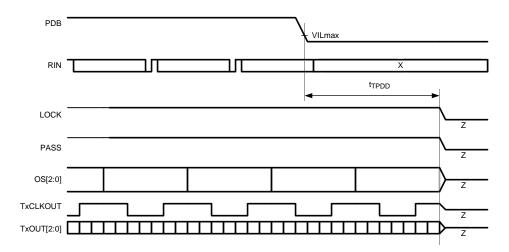

| LOCK                 | 27              | O, LVMOS                           | LOCK Status Output<br>LOCK = 1, PLL is locked, outputs are active.<br>LOCK = 0, PLL is unlocked, output states determined by OSS_SEL.<br>Maybe used as a Link Status or to flag when the Video Data is active (ON/OFF).                                 |

| Control and C        | onfiguration    | 1                                  |                                                                                                                                                                                                                                                         |

| PDB                  | 1               | I, LVCMOS<br>w/ pull-down          | Power Down Mode Input<br>PDB = 1, Device is enabled (normal operation)<br>PDB = 0, Device is in power-down, the output are controlled by the settings. Control registers<br>are <b>RESET</b> .                                                          |

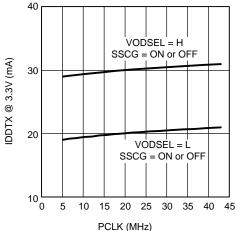

| VODSEL               | 33              | I, LVCMOS<br>w/ pull-down          | Differential Driver Output Voltage Select<br>VODSEL = 1, LVDS VOD is ±400 mV, 800 mVp-p (typ) — Long Cable / De-E Applications<br>VODSEL = 0, LVDS VOD is ±250 mV, 500 mVp-p (typ)<br>See Table 2                                                       |

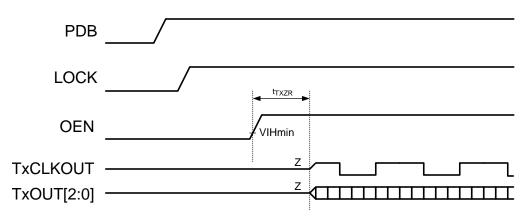

| OEN                  | 34              | I, LVCMOS<br>w/ pull-down          | Output Enable Input<br>OEN = 1, FPD-Link outputs are enabled (active).<br>OEN = 0, FPD-Link outputs are TRI-STATE.                                                                                                                                      |

| OSS_SEL              | 35              | I, LVCMOS<br>w/ pull-down          | Output Sleep State Select Input<br>See Table 1                                                                                                                                                                                                          |

| LFMODE               | 36              | I, LVCMOS<br>w/ pull-down          | Low Frequency Mode — Pin or Register Control<br>LF_MODE = 1, low frequency mode (TxCLKOUT = 5-20 MHz)<br>LF_MODE = 0, high frequency mode (TxCLKOUT = 20-43 MHz)                                                                                        |

| SSC[2:0]             | 7, 2, 3         | I, LVCMOS<br>w/ pull-down          | Spread Spectrum Clock Generation (SSCG) Range Select<br>See Table 3 and Table 4                                                                                                                                                                         |

| RES[1:0]             | 37, 15          | I, LVCMOS<br>w/ pull-down          | Reserved<br>Tie Low                                                                                                                                                                                                                                     |

|                      | te, use a 10 kΩ | Ω pull up to VDD                   | IO; for a Low State, the IO includes an internal pull down. The STRAP pin is read upon power-<br>listed along with shared LVCMOS Output name in square bracket.                                                                                         |

| EQ                   | 28 [PASS]       | STRAP<br>I, LVCMOS<br>w/ pull-down | EQ Gain Control of FPD-Link II Input<br>EQ = 1, EQ gain is enabled (~13 dB)<br>EQ = 0, EQ gain is disabled (~1.625 dB)                                                                                                                                  |

| <b>Optional BIST</b> | Mode            | 4 -                                |                                                                                                                                                                                                                                                         |

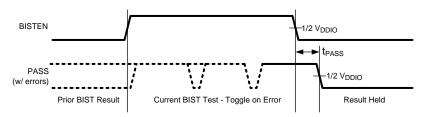

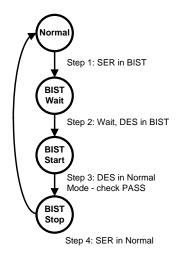

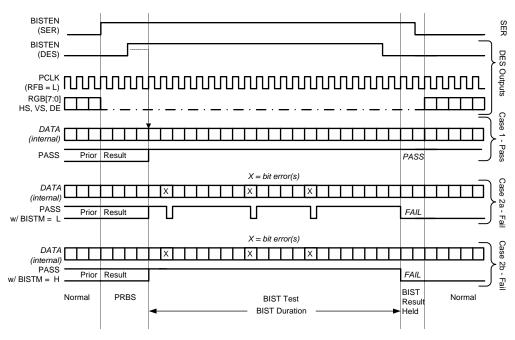

| BISTEN               | 29              | I, LVCMOS<br>w/ pull-down          | BIST Enable Input – Optional<br>BISTEN = 1, BIST Mode is enabled.<br>BISTEN = 0, normal mode.                                                                                                                                                           |

#### TEXAS INSTRUMENTS

www.ti.com

#### **PIN DESCRIPTIONS (continued)**

| Pin Name              | Pin #                               | I/O, Type                 | Description                                                                                                                                                       |

|-----------------------|-------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BISTM                 | 30                                  | I, LVCMOS<br>w/ pull-down | BIST Mode Input – Optional<br>BISTM = 1, selects Payload Error Mode<br>BISTM = 0, selects Pass / Fail Result-Only Mode                                            |

| PASS                  | 28                                  | O, LVCMOS                 | PASS Output (BIST Mode) – Optional<br>PASS = 1, no errors detected<br>PASS = 0, errors detected<br>Leave open if unused. Route to a test point (pad) recommended. |

| <b>Optional Seria</b> | I Bus Control                       | Interface                 |                                                                                                                                                                   |

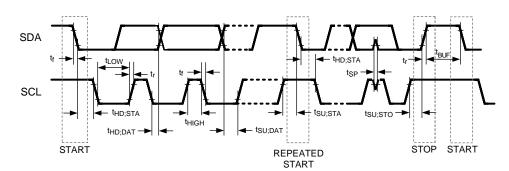

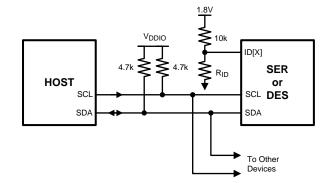

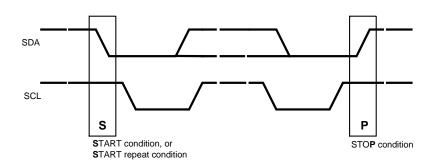

| SCL                   | 5                                   | I, LVCMOS                 | Serial Control Bus Clock Input - Optional SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                                                        |

| SDA                   | 4                                   | I/O, LVCMOS<br>Open Drain | Serial Control Bus Data Input / Output - Optional<br>SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                                             |

| ID[x]                 | 16                                  | I, Analog                 | Serial Control Bus Device ID Address Select — Optional Resistor to Ground and 10 k $\Omega$ pull-up to 1.8V rail. See Table 5.                                    |

| Power and Gr          | ound                                |                           |                                                                                                                                                                   |

| VDDL                  | 6, 31                               | Power                     | Logic Power, 1.8 V ±5%                                                                                                                                            |

| VDDA                  | 38, 43                              | Power                     | Analog Power, 1.8 V ±5%                                                                                                                                           |

| VDDP                  | 8, 46, 47                           | Power                     | SSC Generator Power, 1.8 V ±5%                                                                                                                                    |

| VDDTX                 | 13                                  | Power                     | FPD-Link Power, 3.3 V ±10%                                                                                                                                        |

| VDDIO                 | 25                                  | Power                     | LVCMOS I/O Power, 1.8 V ±5% OR 3.3 V ±10%                                                                                                                         |

| GND                   | 9, 14, 26,<br>32, 39, 44,<br>45, 48 | Ground                    | Ground                                                                                                                                                            |

| DAP                   | DAP                                 | Ground                    | DAP is the large metal contact at the bottom side, located at the center of the WQFN package. <b>Connected to the ground plane</b> (GND) with at least 9 vias.    |

# **Block Diagram**

8

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings<sup>(1)(2)</sup>

| ···· J-                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Supply Voltage – V <sub>DDn</sub> (1.8V)              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3V to +2.5V           |

| Supply Voltage – V <sub>DDTX</sub> (3.3V)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3V to +4.0V           |

| Supply Voltage – V <sub>DDIO</sub>                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3V to +4.0V           |

| LVCMOS I/O Voltage                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3V to +(VDDIO + 0.3V) |

| Receiver Input Voltage                                | $\begin{array}{c} eq:spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spec$ | -0.3V to (VDD + 0.3V)    |

| LVDS Output Voltage                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3V to (VDDTX + 0.3V)  |

| Junction Temperature                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | +150°C                   |

| Storage Temperature                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | −65°C to +150°C          |

| Lead Temperature<br>(Soldering, 4s)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | +260°C                   |

| 48L RHS Package                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Maximum Power Dissipation Capacity at                 | Derate above 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1/ θ <sub>JA</sub> °C/W  |

| 25°C                                                  | θ <sub>JA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27.7 °C/W                |

|                                                       | θ <sub>JC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.0 °C/W                 |

| ESD Rating (IEC, powered-up only), $R_D =$            | Air Discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ≥±30 kV                  |

| 330Ω, C <sub>S</sub> = 150pF                          | Contact Discharge (R <sub>IN+</sub> , R <sub>IN</sub> -)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ≥±6 kV                   |

| ESD Rating (ISO10605), $R_D = 330\Omega$ , $C_S =$    | Air Discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ≥±15 kV                  |

| 150 & 330pF                                           | Contact Discharge (R <sub>IN+</sub> , R <sub>IN</sub> -)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ≥±8 kV                   |

| ESD Rating (ISO10605), $R_D = 2k\Omega$ , $C_S = 150$ | Air Discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ≥±15 kV                  |

| & 330pF                                               | Contact Discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ≥±8 kV                   |

| ESD Rating (HBM)                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ≥±8 kV                   |

| ESD Rating (CDM)                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ≥±1.25 kV                |

| ESD Rating (MM)                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ≥±250 V                  |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

(1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

#### **Recommended Operating Conditions**

|                                                  | Min  | Nom | Max  | Units             |

|--------------------------------------------------|------|-----|------|-------------------|

| Supply Voltage (V <sub>DDn</sub> )               | 1.71 | 1.8 | 1.89 | V                 |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       | 1.71 | 1.8 | 1.89 | V                 |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       | 3.0  | 3.3 | 3.6  | V                 |

| Operating Free Air Temperature (T <sub>A</sub> ) | -40  | +25 | +105 | °C                |

| TxCLK Clock Frequency                            | 5    |     | 43   | MHz               |

| Supply Noise <sup>(1)</sup>                      |      |     | 100  | mV <sub>P-P</sub> |

(1) Supply noise testing was done with minimum capacitors on the PCB. A sinusoidal signal is AC coupled to the  $V_{DDn}$  (1.8V) supply with amplitude = 100 mVp-p measured at the device  $V_{DDn}$  pins. Bit error rate testing of input to the Ser and output of the Des with 10 meter cable shows no error when the noise frequency on the Ser is less than 750 kHz. The Des on the other hand shows no error when the noise frequency is less than 400 kHz.

www.ti.com

STRUMENTS

**EXAS**

### **DC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)(3)

| Symbol             | Parameter                       | Cond                                                      | ditions                       | Pin/Freq.                     | Min                      | Тур               | Max                        | Units |

|--------------------|---------------------------------|-----------------------------------------------------------|-------------------------------|-------------------------------|--------------------------|-------------------|----------------------------|-------|

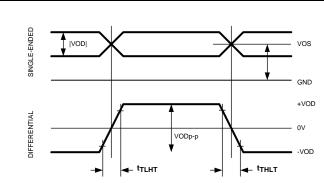

| FPD-Link L         | VDS Output                      |                                                           |                               | ·                             | 1 I                      |                   |                            |       |

|                    | Differential                    |                                                           | VODSEL = L                    |                               | 100                      | 250               | 400                        | mV    |

| V <sub>OD</sub>    | Output Voltage                  |                                                           | VODSEL = H                    |                               | 200                      | 400               | 600                        | mV    |

|                    | Differential                    |                                                           | VODSEL = L                    |                               |                          | 500               |                            | mVp-p |

| V <sub>ODp-p</sub> | Output Voltage<br>A-B           |                                                           | VODSEL = H                    |                               |                          | 800               |                            | mVp-p |

| ∆V <sub>OD</sub>   | Output Voltage<br>Unbalance     | R <sub>L</sub> = 100Ω                                     |                               | TxCLKOUT+,<br>TxCLKOUT-,      |                          | 1                 | 50                         | mV    |

| \/                 | Offset Voltage                  |                                                           | VODSEL = L                    | TxOUT[2:0]+,<br>TxOUT[2:0]-   | 1.0                      | 1.2               | 1.5                        | V     |

| V <sub>OS</sub>    | Oliset voltage                  |                                                           | VODSEL = H                    |                               |                          | 1.2               |                            | V     |

| ΔV <sub>OS</sub>   | Offset Voltage<br>Unbalance     |                                                           |                               | -                             |                          | 1                 | 50                         | mV    |

| los                | Output Short<br>Circuit Current | Vout = GND                                                |                               |                               |                          | -5                |                            | mA    |

| oz                 | Output TRI-<br>STATE<br>Current | OEN = GND,<br>Vout =V <sub>DDTX</sub> , or GND            |                               |                               | -10                      |                   | +10                        | μA    |

| 3.3 V I/O LV       | CMOS DC SPEC                    | IFICATIONS – V <sub>D</sub>                               | <sub>DIO</sub> = 3.0 to 3.6V  |                               |                          |                   |                            |       |

| V <sub>IH</sub>    | High Level<br>Input Voltage     |                                                           |                               | PDB,<br>VODSEL,               | 2.2                      |                   | V <sub>DDIO</sub>          | V     |

| V <sub>IL</sub>    | Low Level<br>Input Voltage      |                                                           | OEN,<br>OSS_SEL,<br>LFMODE,   | GND                           |                          | 0.8               | V                          |       |

| IN                 | Input Current                   | $V_{IN} = 0V \text{ or } V_{DDIO}$                        | 0                             | SSC[2:0],<br>BISTEN,<br>BISTM | -15                      | ±1                | +15                        | μA    |

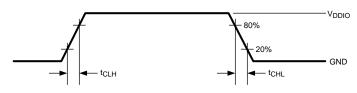

| V <sub>OH</sub>    | High Level<br>Output Voltage    | I <sub>OH</sub> = −0.5 mA                                 |                               |                               | V <sub>DDIO</sub> - 0.2  | V <sub>DDIO</sub> |                            | V     |

| V <sub>OL</sub>    | Low Level<br>Output Voltage     | I <sub>OL</sub> = +0.5 mA                                 |                               | LOCK, PASS,                   |                          | GND               | 0.2                        | V     |

| los                | Output Short<br>Circuit Current | V <sub>OUT</sub> = 0V                                     |                               | OS[2:0]                       |                          | -10               |                            | mA    |

| I <sub>oz</sub>    | TRI-STATE<br>Output Current     | PDB = 0V, OSS_<br>V <sub>OUT</sub> = 0V or V <sub>D</sub> |                               |                               | -10                      |                   | +10                        | μA    |

| 1.8 V 1/O LV       | CMOS DC SPEC                    | IFICATIONS – V <sub>D</sub>                               | <sub>DIO</sub> = 1.71 to 1.89 | V                             |                          |                   |                            |       |

| V <sub>IH</sub>    | High Level<br>Input Voltage     |                                                           |                               | PDB,<br>VODSEL,               | 0.7<br>V <sub>DDIO</sub> |                   | V <sub>DDIO</sub>          | V     |

| V <sub>IL</sub>    | Low Level<br>Input Voltage      |                                                           |                               | OEN,<br>OSS_SEL,<br>LFMODE,   | GND                      |                   | 0.35*<br>V <sub>DDIO</sub> | V     |

| I <sub>IN</sub>    | Input Current                   | $V_{IN} = 0V \text{ or } V_{DDIG}$                        | 0                             | SSC[2:0],<br>BISTEN,<br>BISTM | -10                      | ±1                | +10                        | μA    |

(1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.