ZHCSAX4A – FEBRUARY 2013–REVISED FEBRUARY 2013

# USB 充电端口控制器和电源开关

查询样品: TPS2544

# 特性

- 符合 USB 电池充电规范 1.2 的 D+/D- 充电下游端

口 (CDP) / 专用充电端口 (DCP) 模式

- 符合中国电信业标准 YD/T 1591-2009 的 D+/D- 短 接模式

- 通过自动选择来支持非 BC1.2 充电模式

- D+/D-分配器模式 2.0V/2.7V 和 2.7/2.0V

- D+/D-1.2V 模式

- 支持睡眠模式充电和鼠标/键盘唤醒

- 针对未连接至 CDP 端口的器件的自动 SDP/CDP 切换

- 与 USB 2.0 和 3.0 电源开关要求兼容

- 集成型 73mΩ(典型值)高侧金属氧化物半导体场 效应晶体管 (MOSFET)

- 可调电流限制高达 3A (典型值)

- 工作电压范围: 4.5V 至 5.5V

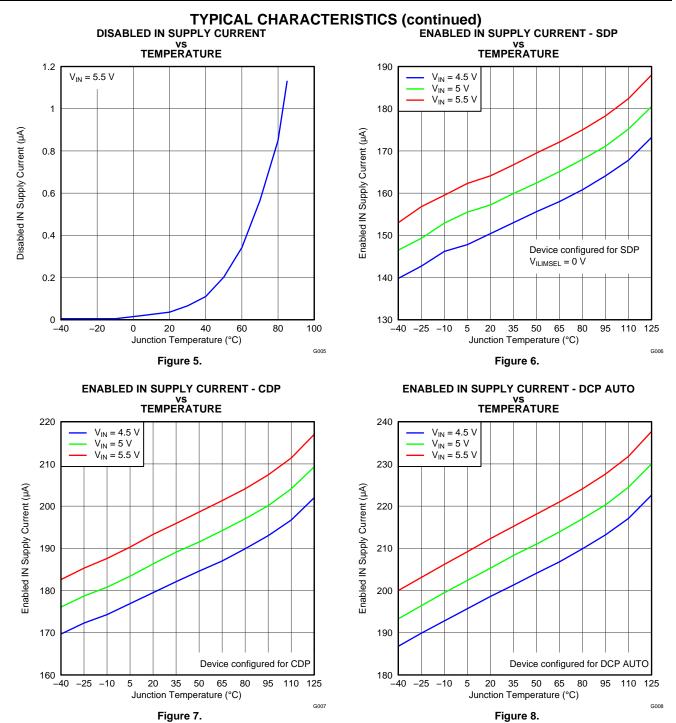

- 最大器件电流

- 当器件被禁用时为 2µA

- 当器件被启用时为 270µA

- 与 TPS2543 和 TPS2546 插槽和物料清单 (BOM) 兼容

- 采用 16 引脚四方扁平无引线 (QFN) (3 x 3) 封装

- DM/DP 引脚上 8KV 静电放电 (ESD) 额定值

- 符合 UL 规范且 CB 档案编号E169910

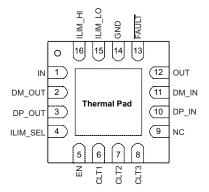

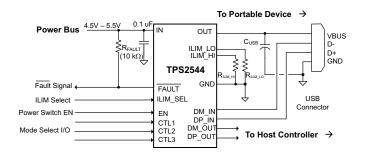

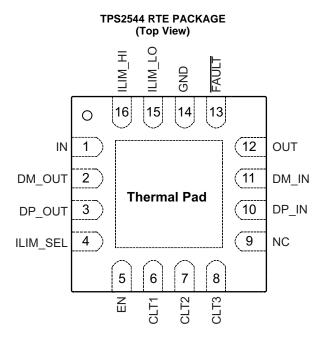

## TPS2544 封装和典型应用图

# 应用范围

- USB 端口(主机和集线器)

- 笔记本和台式机

- 通用墙式充电适配器

## 说明

TPS2544 是一款具有集成的 USB 2.0 高速数据线路 (D+/D-) 开关的 USB 充电端口控制器和电源开关。 TPS2544 在 D+/D-上提供电气签名以支持器件特性部 分中所列出的充电体系。 德州仪器 (TI) 使用 TPS2544 来测试常见手机、平板电脑和媒体器件的充电以确保与 BC1.2 和非 BC1.2 兼容器件的兼容性。 除了为常见器 件充电, TPS2544 还支持带有鼠标/键盘的系统唤 醒(从 S3 唤醒);在低速和高速情况下都支持。

**TPS2544 73m**Ω 配电开关用于有可能遇到高电容负载 和短路的应用。两个可编程电流阀值为设置电流限值 提供了灵活性。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TPS2544

### ZHCSAX4A-FEBRUARY 2013-REVISED FEBRUARY 2013

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| T <sub>A</sub> | PACKAGE | DEVICE  | TOP-SIDE MARKING |  |

|----------------|---------|---------|------------------|--|

| –40°C to 85°C  | QFN16   | TPS2544 | 2544             |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**<sup>(1)</sup>

over operating free-air temperature range, voltages are referenced to GND (unless otherwise noted)

|                                       |                                                                  | LIMIT                     | UNIT |

|---------------------------------------|------------------------------------------------------------------|---------------------------|------|

|                                       | IN, EN, ILIM_LO, ILIM_HI, FAULT, ILIM_SEL, CTL1, CTL2, CTL3, OUT | -0.3 to 7                 |      |

| Voltage range                         | IN to OUT                                                        | -7 to 7                   | V    |

|                                       | DP_IN, DM_IN, DP_OUT, DM_OUT                                     | -0.3 to (IN + 0.3) or 5.7 |      |

| Input clamp current                   | DP_IN, DM_IN, DP_OUT, DM_OUT                                     | ±20                       | mA   |

| Continuous current in SDP or CDP mode | DP_IN to DP_OUT or DM_IN to DM_OUT                               | ±100                      | mA   |

| Continuous current in BC1.2 DCP mode  | DP_IN to DM_IN                                                   | ±50                       | mA   |

| Continuous output current             | OUT                                                              | Internally limited        |      |

| Continuous output sink current        | FAULT                                                            | 25                        | mA   |

| Continuous output source current      | ILIM_LO, ILIM_HI                                                 | Internally limited        | mA   |

|                                       | НВМ                                                              | 2                         | kV   |

| ESD rating                            | HBM wrt GND and each other, DP_IN, DM_IN, OUT                    | 8                         | ĸv   |

|                                       | CDM                                                              | 500                       | V    |

| Operating junction temperature, $T_J$ |                                                                  | -40 to Internally limited | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## THERMAL INFORMATION

|                    | THERMAL METRIC <sup>(1)</sup>                | TPS2546      |               |

|--------------------|----------------------------------------------|--------------|---------------|

|                    |                                              | RTE (16 PIN) | UNITS         |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance       | 53.4         |               |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 51.4         |               |

| $\theta_{JB}$      | Junction-to-board thermal resistance         | 17.2         | 8 <b>0</b> AM |

| ΨJT                | Junction-to-top characterization parameter   | 3.7          | °C/W          |

| $\Psi_{JB}$        | Junction-to-board characterization parameter | 20.7         |               |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | 3.9          |               |

(1) 有关传统和新的热度量的更多信息,请参阅IC 封装热度量应用报告, SPRA953。

#### ZHCSAX4A - FEBRUARY 2013 - REVISED FEBRUARY 2013

# **RECOMMENDED OPERATING CONDITIONS**

voltages are referenced to GND (unless otherwise noted)

|                      |                                                                                         | MIN  | NOM | MAX      | UNIT |

|----------------------|-----------------------------------------------------------------------------------------|------|-----|----------|------|

| V <sub>IN</sub>      | Input voltage, IN                                                                       | 4.5  |     | 5.5      | V    |

|                      | Input voltage, logic-level inputs, EN, CTL1, CTL2, CTL3, ILIM_SEL                       | 0    |     | 5.5      | V    |

|                      | Input voltage, data line inputs, DP_IN, DM_IN, DP_OUT, DM_OUT                           | 0    |     | $V_{IN}$ | V    |

| V <sub>IH</sub>      | High-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                | 1.8  |     |          | V    |

| V <sub>IL</sub>      | Low-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                 |      |     | 0.8      | V    |

|                      | Continuous current, data line inputs, SDP or CDP mode, DP_IN to DP_OUT, DM_IN to DM_OUT |      |     | ±30      | mA   |

|                      | Continuous current, data line inputs, BC1.2 DCP mode, DP_IN to DM_IN                    |      |     | ±15      | mA   |

| IOUT                 | Continuous output current, OUT                                                          | 0    |     | 2.5      | А    |

|                      | Continuous output sink current, FAULT                                                   | 0    |     | 10       | mA   |

| R <sub>ILIM_XX</sub> | Current-limit set resistors                                                             | 16.9 |     | 750      | kΩ   |

| TJ                   | Operating virtual junction temperature                                                  | -40  |     | 125      | °C   |

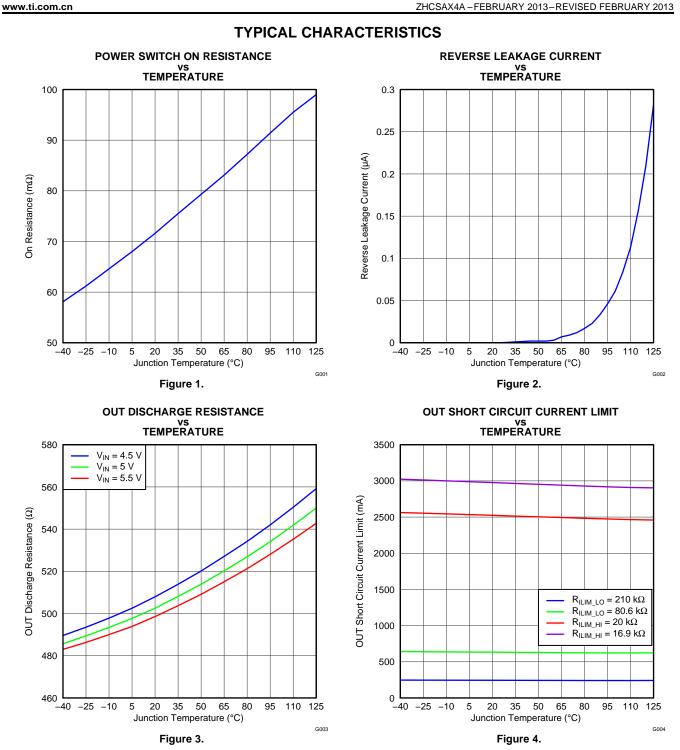

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}$ C,  $4.5V \le V_{IN} \le 5.5$  V,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $_{FAULT} = 10 \text{ k}\Omega$ ,  $R_{ILIM\_HI} = 20 \text{ k}\Omega$ ,  $R_{ILIM\_LO} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                    | TEST CONDITIONS                                                                                                            | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER               | SWITCH                       |                                                                                                                            |      |      |      |      |

|                     |                              | $T_{J} = 25^{\circ}C, I_{OUT} = 2 A$                                                                                       |      | 73   | 84   |      |

| R <sub>DS(on)</sub> | On resistance <sup>(1)</sup> | $-40^{\circ}C \le T_{J} \le 85^{\circ}C, I_{OUT} = 2 A$                                                                    |      | 73   | 105  | mΩ   |

|                     |                              | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ , $I_{OUT} = 2 \text{ A}$                                                        |      | 73   | 120  |      |

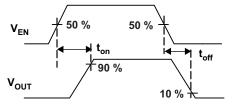

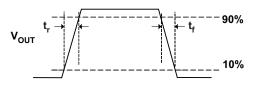

| t <sub>r</sub>      | OUT voltage rise time        | $V_{IN} = 5 \text{ V}, \text{ C}_{L} = 1 \mu\text{F}, \text{ R}_{L} = 100 \Omega \text{ (see Figure 20 and } \mu\text{F})$ | 0.7  | 1.0  | 1.60 |      |

| t <sub>f</sub>      | OUT voltage fall time        | Figure 21)                                                                                                                 | 0.2  | 0.35 | 0.5  | ms   |

| t <sub>on</sub>     | OUT voltage turn-on time     | $V_{IN} = 5V, C_I = 1 \ \mu F, R_I = 100 \ \Omega$ (see Figure 20 and                                                      |      | 2.7  | 4    |      |

| t <sub>off</sub>    | OUT voltage turn-off time    | Figure 22)                                                                                                                 |      | 1.7  | 3    | ms   |

| I <sub>REV</sub>    | Reverse leakage current      | $V_{OUT} = 5.5 \text{ V}, V_{IN} = V_{EN} = 0 \text{ V}, -40 \le T_J \le 85^{\circ}\text{C},$<br>Measure I <sub>OUT</sub>  |      |      | 2    | μA   |

| DISCHA              | RGE                          |                                                                                                                            |      |      |      |      |

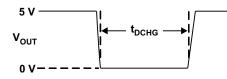

| R <sub>DCHG</sub>   | OUT discharge resistance     | V <sub>OUT</sub> = 4 V, V <sub>EN</sub> = 0 V                                                                              | 400  | 500  | 630  | Ω    |

| t <sub>DCHG</sub>   | OUT discharge hold time      | Time V <sub>OUT</sub> < 0.7 V (see Figure 23)                                                                              | 1.30 | 2.0  | 2.9  | s    |

(1) Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account separately.

www.ti.com.cn

# ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}$ C,  $4.5V \le V_{IN} \le 5.5$  V,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $_{FAULT} = 10 \text{ k}\Omega$ ,  $R_{ILIM\_HI} = 20 \text{ k}\Omega$ ,  $R_{ILIM\_LO} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                                             | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNIT |

|---------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| EN, ILIN            | ISEL, CTL1, CTL2, CTL3 INPUTS                         |                                                                                                          |      |      |      |      |

|                     | Input pin rising logic threshold voltage              |                                                                                                          | 1    | 1.35 | 1.70 | V    |

|                     | Input pin falling logic threshold voltage             |                                                                                                          | 0.85 | 1.15 | 1.45 |      |

|                     | Hysteresis <sup>(2)</sup>                             |                                                                                                          |      | 200  |      | mV   |

|                     | Input current                                         | Pin voltage = 0 V or 5.5 V                                                                               | -0.5 |      | 0.5  | μA   |

| ILIMSEL             | _ CURRENT LIMIT                                       |                                                                                                          |      |      |      |      |

|                     |                                                       | $V_{ILIM\_SEL} = 0 V, R_{ILIM\_LO} = 210 k\Omega$                                                        | 205  | 240  | 275  |      |

|                     |                                                       | $V_{ILIM\_SEL} = 0 V, R_{ILIM\_LO} = 80.6 k\Omega$                                                       | 575  | 625  | 680  |      |

| los                 | OUT short circuit current limit <sup>(3)</sup>        | $V_{ILIM\_SEL} = 0 V, R_{ILIM\_LO} = 22.1 k\Omega$                                                       | 2120 | 2275 | 2430 | mA   |

|                     |                                                       | $V_{ILIM\_SEL} = V_{IN}, R_{ILIM\_HI} = 20 \text{ k}\Omega$                                              | 2340 | 2510 | 2685 |      |

|                     |                                                       | $V_{ILIM\_SEL} = V_{IN}, R_{ILIM\_HI} = 16.9 \text{ k}\Omega$                                            | 2770 | 2970 | 3170 |      |

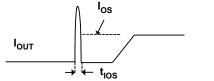

| t <sub>IOS</sub>    | Response time to OUT short-<br>circuit <sup>(2)</sup> | $V_{\text{IN}}$ = 5.0 V, R = 0.1Ω, lead length = 2 inches (see Figure 24)                                |      | 1.5  |      | μs   |

| SUPPL               | Y CURRENT                                             | ·                                                                                                        |      |      |      |      |

| I <sub>IN_OFF</sub> | Disabled IN supply current                            | $V_{\text{EN}} = 0 \text{ V}, V_{\text{OUT}} = 0 \text{ V}, -40 \le T_{\text{J}} \le 85^{\circ}\text{C}$ |      | 0.1  | 2    | μA   |

|                     |                                                       | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = 0 V, V_{ILIM\_SEL} = 0 V$                                      |      | 165  | 220  |      |

|                     |                                                       | $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}, V_{ILIM_SEL} = 0 V$                                            |      | 175  | 230  |      |

| I <sub>IN_ON</sub>  | Enabled IN supply current                             | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = 0V, V_{ILIM\_SEL} = V_{IN}$                                    |      | 185  | 240  | μA   |

|                     |                                                       | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = VIN, V_{ILIM\_SEL} = V_{IN}$                                   |      | 195  | 250  |      |

|                     |                                                       | $V_{CTL1} = 0V, V_{CTL2} = V_{CTL3} = V_{IN}$                                                            |      | 215  | 270  |      |

| UNDER               | VOLTAGE LOCKOUT                                       |                                                                                                          | E    |      |      |      |

| V <sub>UVLO</sub>   | IN rising UVLO threshold voltage                      |                                                                                                          | 3.9  | 4.1  | 4.3  | V    |

|                     | Hysteresis <sup>(2)</sup>                             |                                                                                                          |      | 100  |      | mV   |

| FAULT               |                                                       | 1                                                                                                        |      |      |      |      |

|                     | Output low voltage                                    | $I_{\overline{FAULT}} = 1 \text{ mA}$                                                                    |      |      | 100  | mV   |

|                     | Off-state leakage                                     | $V_{\overline{FAULT}} = 5.5 V$                                                                           |      |      | 1    | μA   |

|                     | Over current FAULT rising and<br>falling deglitch     |                                                                                                          | 5    | 8.2  | 12   | ms   |

| THERM               | AL SHUTDOWN                                           |                                                                                                          |      |      |      |      |

|                     | Thermal shutdown threshold                            |                                                                                                          | 155  |      |      |      |

|                     | Thermal shutdown threshold in<br>current-limit        |                                                                                                          | 135  |      |      | °C   |

|                     | Hysteresis <sup>(2)</sup>                             |                                                                                                          |      | 20   |      |      |

(2) These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty. Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account

(3) separately.

www.ti.com.cn

## ELECTRICAL CHARACTERISTICS, HIGH-BANDWIDTH SWITCH

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 V \le V_{IN} \le 5.5 V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $\overline{_{FAULT}} = 10 \text{ k}\Omega$ ,  $R_{ILIM\_HI} = 20 \text{ k}\Omega$ ,  $R_{ILIM\_LO} = 80.6 \text{ k}\Omega$ , Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                   | PARAMETER                                                                              | TEST CONDITIONS                                                                                                                                                                                           | MIN | TYP  | MAX  | UNIT |

|-------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| HIGH-BA           | ANDWIDTH ANALOG SWITCH                                                                 |                                                                                                                                                                                                           |     |      |      |      |

|                   | DP/DM switch on resistance                                                             | $V_{DP/DM_OUT} = 0 V, I_{DP/DM_IN} = 30 mA$                                                                                                                                                               |     | 2    | 4    | Ω    |

|                   | DP/DM switch on resistance                                                             | $V_{DP/DM_OUT} = 2.4 \text{ V}, I_{DP/DM_IN} = -15 \text{ mA}$                                                                                                                                            |     | 3    | 6    | Ω    |

|                   | Switch resistance mismatch between                                                     | $V_{DP/DM_OUT} = 0 V, I_{DP/DM_IN} = 30 mA$                                                                                                                                                               |     | 0.05 | 0.15 | 0    |

|                   | DP / DM channels                                                                       | $V_{DP/DM_OUT} = 2.4 \text{ V}, I_{DP/DM_IN} = -15 \text{ mA}$                                                                                                                                            |     | 0.05 | 0.15 | Ω    |

|                   | DP/DM switch off-state capacitance <sup>(1)</sup>                                      | $\label{eq:VEN} \begin{array}{l} V_{\text{EN}} = 0 \ \text{V}, \ \text{V}_{\text{DP/DM\_IN}} = 0.3 \ \text{V}, \ \text{V}_{\text{ac}} = 0.6 \ \text{V}_{\text{pk-pk}}, \\ f = 1 \ \text{MHz} \end{array}$ |     | 3    | 3.6  | pF   |

|                   | DP/DM switch on-state capacitance <sup>(2)</sup>                                       | $V_{DP/DM_{IN}} = 0.3 V$ , $V_{ac} = 0.6 V_{pk-pk}$ , f = 1 MHz                                                                                                                                           |     | 5.4  | 6.2  | pF   |

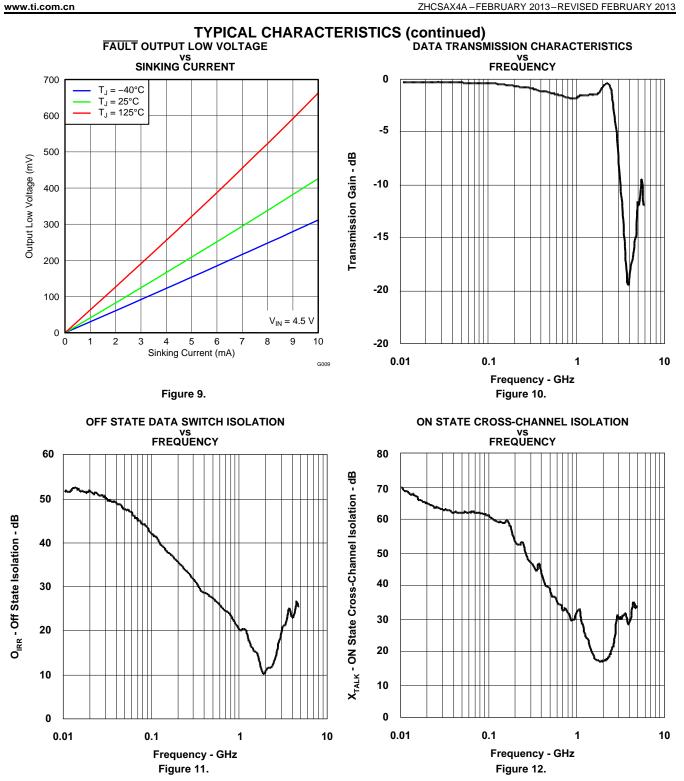

| O <sub>IRR</sub>  | Off-state isolation <sup>(3)</sup>                                                     | V <sub>EN</sub> = 0 V, f = 250 MHz                                                                                                                                                                        |     | 33   |      | dB   |

| X <sub>TALK</sub> | On-state cross channel isolation <sup>(3)</sup>                                        | f = 250 MHz                                                                                                                                                                                               |     | 52   |      | dB   |

|                   | Off state leakage current                                                              | $V_{EN} = 0 \text{ V},  V_{DP/DM_IN} = 3.6 \text{ V},  V_{DP/DM_OUT} = 0 \text{ V},$ measure $I_{DP/DM_OUT}$                                                                                              |     | 0.1  | 1.5  | μA   |

| BW                | Bandwidth (-3dB) <sup>(3)</sup>                                                        | R <sub>L</sub> = 50 Ω                                                                                                                                                                                     |     | 2.6  |      | GHz  |

| t <sub>pd</sub>   | Propagation delay <sup>(3)</sup>                                                       |                                                                                                                                                                                                           |     | 0.25 |      | ns   |

| t <sub>SK</sub>   | Skew between opposite transitions of the same port $(t_{\text{PHL}} - t_{\text{PLH}})$ |                                                                                                                                                                                                           |     | 0.1  | 0.2  | ns   |

(1) The resistance in series with the parasitic capacitance to GND is typically 250  $\Omega$ .

(2) The resistance in series with the parasitic capacitance to GND is typically 150  $\Omega$

(3) These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS, CHARGING CONTROLLER**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}$ C,  $4.5 V \le V_{IN} \le 5.5 V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = 0 V$ ,  $V_{CTL2} = V_{CTL3} = V_{IN}$ . R FAULT = 10 k $\Omega$ ,  $R_{ILIM\_HI} = 20 k\Omega$ ,  $R_{ILIM\_LO} = 80.6 k\Omega$ , Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                                                                 | TEST CONDITIONS                                                    | MIN  | TYP  | MAX  | UNIT |  |

|---------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|--|

| SHORTED             | MODE (BC1.2 DCP)                                                          | VCTL1 = VIN, VCTL2 = VCTL3 = 0V                                    |      |      |      |      |  |

|                     | DP_IN / DM_IN shorting resistance                                         |                                                                    |      | 125  | 200  | Ω    |  |

| 1.2V Mode           |                                                                           |                                                                    |      |      |      |      |  |

|                     | DP_IN /DM_IN output voltage                                               |                                                                    | 1.19 | 1.25 | 1.31 | V    |  |

|                     | DP_IN /DM_IN output impedance                                             |                                                                    | 60   | 75   | 94   | kΩ   |  |

| DIVIDER1            | IODE                                                                      |                                                                    |      |      |      |      |  |

|                     | DP_IN Divider1 output voltage                                             |                                                                    | 1.9  | 2.0  | 2.1  | V    |  |

|                     | DM_IN Divider1 output voltage                                             |                                                                    | 2.57 | 2.7  | 2.84 | V    |  |

|                     | DP_IN output impedance                                                    |                                                                    | 8    | 10.5 | 12.5 | kΩ   |  |

|                     | DM_IN output impedance                                                    |                                                                    | 8    | 10.5 | 12.5 | kΩ   |  |

| DIVIDER2            | IODE                                                                      | IOUT = 1A                                                          |      |      |      |      |  |

|                     | DP_IN Divider2 output voltage                                             |                                                                    | 2.57 | 2.7  | 2.84 | V    |  |

|                     | DM_IN Divider2 output voltage                                             |                                                                    | 1.9  | 2.0  | 2.1  | V    |  |

|                     | DP_IN output impedance                                                    |                                                                    | 8    | 10.5 | 12.5 | kΩ   |  |

|                     | DM_IN output impedance                                                    |                                                                    | 8    | 10.5 | 12.5 | kΩ   |  |

| CHARGING            | DOWNSTREAM PORT                                                           | VCTL1 = VCTL2 = VCTL3 = VIN                                        |      |      |      |      |  |

| V <sub>DM_SRC</sub> | DM_IN CDP output voltage                                                  | V <sub>DP_IN</sub> = 0.6 V,<br>-250 μA < I <sub>DM_IN</sub> < 0 μA | 0.5  | 0.6  | 0.7  | V    |  |

| $V_{DAT\_REF}$      | DP_IN rising lower window threshold for<br>V <sub>DM_SRC</sub> activation |                                                                    | 0.25 |      | 0.4  | V    |  |

|                     | Hysteresis <sup>(1)</sup>                                                 |                                                                    |      | 50   |      | mV   |  |

| $V_{LGC\_SRC}$      | DP_IN rising upper window threshold for $V_{DM_SRC}$ de-activation        |                                                                    | 0.8  |      | 1    | V    |  |

|                     | hysteresis <sup>(1)</sup>                                                 |                                                                    |      | 100  |      | mV   |  |

| IDP SINK            | DP_IN sink current                                                        | V <sub>DP IN</sub> = 0.6 V                                         | 40   | 70   | 100  | μA   |  |

(1) These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

Copyright © 2013, Texas Instruments Incorporated

www.ti.com.cn

ZHCSAX4A-FEBRUARY 2013-REVISED FEBRUARY 2013

TYPICAL CHARACTERISTICS (continued)

EYE DIAGRAM USING USB COMPLIANCE TEST PATTERN (with no switch)

EYE DIAGRAM USING USB COMPLIANCE TEST PATTERN (with data switch)

0.5 0.5 0.4 0.4 0.3 0.3 0.2 0.2 Differential Signal (V) Differential Signal (V) 0.1 0.1 0 0 -0.1 -0.1 -0.2 -0.2 -0.3 -0.3 -0.4 -0.4 -0.5 -0.5 0.2 0.4 0.6 0.8 1.2 1.4 1.6 1.8 2 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 0 1 Time (ns) Time (ns) G013 G014 Figure 13. Figure 14. **TURN-ON RESPONSE TURN-OFF RESPONSE** V<sub>OUT</sub> V<sub>OUT</sub> 2 V/div 2 V/div  $V_{EN}$ 5 V/div  $\mathsf{V}_{\mathsf{EN}}$ 5 V/div  $R_{LOAD} = 5 \Omega$ C<sub>LOAD</sub> = 150 μF  $R_{LOAD}$  = 5  $\Omega$  $C_{LOAD}$  = 150  $\mu$ F I<sub>IN</sub> I<sub>IN</sub> 500 mA/div 500 mA/div t - Time - 1 ms/div t - Time - 1 ms/div G021 G022 Figure 15. Figure 16.

www.ti.com.cn

# PARAMETER MEASUREMENT DESCRIPTION

Figure 20. OUT Rise/Fall Test Load

Figure 22. Enable Timing, Active High Enable

Figure 21. Power-On and Off Timing

Figure 24. Output Short Circuit Parameters

#### ZHCSAX4A-FEBRUARY 2013-REVISED FEBRUARY 2013

# **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| NO. | NAME     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                           |  |

|-----|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | IN       | Р                   | Input voltage and supply voltage; connect 0.1 $\mu F$ or greater ceramic capacitor from IN to GND as close to the device as possible                                                                                                  |  |

| 2   | DM_OUT   | I/O                 | - data line to USB host controller                                                                                                                                                                                                    |  |

| 3   | DP_OUT   | I/O                 | D+ data line to USB host controller                                                                                                                                                                                                   |  |

| 4   | ILIM_SEL | I                   | Logic-level input signal used to control the charging mode current limit threshold; see the control truth table. Can be tied directly to IN or GND without pull-up or pull-down resistor.                                             |  |

| 5   | EN       | I                   | Logic-level input for turning the power switch and the signal switches on/off; logic low turns off the signal and power switches and holds OUT in discharge. Can be tied directly to IN or GND without pull-up or pull-down resistor. |  |

| 6   | CTL1     | I                   |                                                                                                                                                                                                                                       |  |

| 7   | CTL2     | I                   | Logic-level inputs used to control the charging mode and the signal switches; see the control truth table.<br>Can be tied directly to IN or GND without pull-up or pull-down resistor.                                                |  |

| 8   | CTL3     | I                   |                                                                                                                                                                                                                                       |  |

| 9   | -        | N/C                 | Connect to GND or leave open                                                                                                                                                                                                          |  |

| 10  | DP_IN    | I/O                 | D+ data line to downstream connector                                                                                                                                                                                                  |  |

| 11  | DM_IN    | I/O                 | D- data line to downstream connector                                                                                                                                                                                                  |  |

| 12  | OUT      | Р                   | Power-switch output                                                                                                                                                                                                                   |  |

| 13  | FAULT    | 0                   | Active-low open-drain output, asserted during over-temperature or current limit conditions                                                                                                                                            |  |

| 14  | GND      | Р                   | Ground connection                                                                                                                                                                                                                     |  |

| 15  | ILIM_LO  | Ι                   | External resistor connection used to set the low current-limit threshold. A resistor to ILIM_LO is optional; see Current-Limit Settings in DETAILED DESCRIPTION.                                                                      |  |

| 16  | ILIM_HI  | Ι                   | External resistor connection used to set the high current-limit threshold                                                                                                                                                             |  |

| NA  | PowerPAD |                     | Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect to GND plane.                                                                                                                            |  |

(1) G = Ground, I = Input, O = Output, P = Power, N/C = No Connect

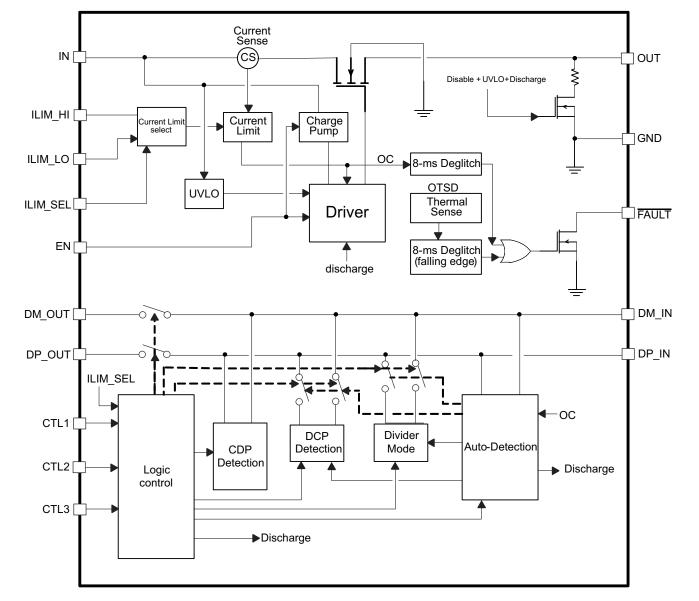

# **TPS2544 FUNCTIONAL BLOCK DIAGRAM**

www.ti.com.cn

ZHCSAX4A – FEBRUARY 2013 – REVISED FEBRUARY 2013

# DETAILED DESCRIPTION

# Overview

The following overview references various industry standards. It is always recommended to consult the most upto-date standard to ensure the most recent and accurate information. Rechargeable portable equipment requires an external power source to charge its batteries. USB ports are a convenient location for charging because of an available 5V power source. Universally accepted standards are required to make sure host and client-side devices operate together in a system to ensure power management requirements are met. Traditionally, host ports following the USB 2.0 specification must provide at least 500mA to downstream client-side devices. Because multiple USB devices can be attached to a single USB port through a bus-powered hub, it is the responsibility of the client-side device to negotiate its power allotment from the host to ensure the total current draw does not exceed 500mA. In general, each USB device is granted 100mA and may request more current in 100mA unit steps up to 500mA. The host may grant or deny based on the available current. A USB 3.0 host port not only provides higher data rate than USB 2.0 port but also raises the unit load from 100mA to 150mA. It is also required to provide a minimum current of 900mA to downstream client-side devices.

Additionally, the success of USB has made the mini-USB connector a popular choice for wall adapter cables. This allows a portable device to charge from both a wall adapter and USB port with only one connector. As USB charging has gained popularity, the 500mA minimum defined by USB 2.0 or 900mA for USB 3.0 has become insufficient for many handset and personal media players which need a higher charging rate. Wall adapters can provide much more current than 500mA/900mA. Several new standards have been introduced defining protocol handshaking methods that allow host and client devices to acknowledge and draw additional current beyond the 500mA/900mA minimum defined by USB 2.0/3.0 while still using a single micro-USB input connector.

The TPS2544 supports four of the most common USB charging schemes found in popular hand-held media and cellular devices:

- USB Battery Charging Specification BC1.2

- Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider Mode

- 1.2V Mode

YD/T 1591-2009 is a subset of BC1.2 spec. supported by vast majority of devices that implement USB changing. Divider and 1.2V charging schemes are supported in devices from specific yet popular device makers.

BC1.2 lists three different port types as listed below.

- Standard Downstream Port (SDP)

- Charging Downstream Port (CDP)

- Dedicated Charging Port (DCP)

BC1.2 defines a charging port as a downstream facing USB port that provides power for charging portable equipment, under this definition CDP and DCP are defined as charging ports

Table 1 shows the differences between these ports.

| PORT TYPE     | SUPPORT USB<br>2.0 COMMUNICATION | MAX. ALLOWABLE CURRENT<br>DRAW BY PORTABLE DEVICE (A) |  |  |  |  |  |  |

|---------------|----------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| SDP (USB 2.0) | Yes                              | 0.5                                                   |  |  |  |  |  |  |

| SDP (USB 3.0) | Yes                              | 0.9                                                   |  |  |  |  |  |  |

| CDP           | Yes                              | 1.5                                                   |  |  |  |  |  |  |

| DCP           | No                               | 1.5                                                   |  |  |  |  |  |  |

#### Table 1. Operating Modes

## Standard Downstream Port (SDP) USB 2.0/USB 3.0

An SDP is a traditional USB port that follows USB 2.0/3.0 protocol and supplies a minimum of 500mA/900mA per port. USB 2.0/3.0 communications is supported, and the host controller must be active to allow charging. TPS2544 supports SDP mode in system power state S0 when system is completely powered ON and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state please refer to device truth table.

Copyright © 2013, Texas Instruments Incorporated

www.ti.com.cn

# **Charging Downstream Port (CDP)**

A CDP is a USB port that follows USB BC1.2 and supplies a minimum of 1.5A per port. It provides power and meets USB 2.0 requirements for device enumeration. USB 2.0 communications is supported, and the host controller must be active to allow charging. What separates a CDP from an SDP is the host-charge handshaking logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 client device and allows for additional current draw by the client device.

The CDP hand-shaking process is done in two steps. During step one the portable equipment outputs a nominal 0.6V output on its D+ line and reads the voltage input on its D- line. The portable device concludes it is connected to an SDP if the voltage is less than the nominal data detect voltage of 0.3V. The portable device concludes that it is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3V and optionally less than 0.8V.

The second step is necessary for portable equipment to determine if it is connected to CDP or DCP. The portable device outputs a nominal 0.6V output on its D- line and reads the voltage input on its D+ line. The portable device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect voltage of 0.3V. The portable device concludes it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3V.

TPS2544 supports CDP mode in system power state S0 when system is completely powered ON and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state please refer to device truth table.

# **Dedicated Charging Port (DCP)**

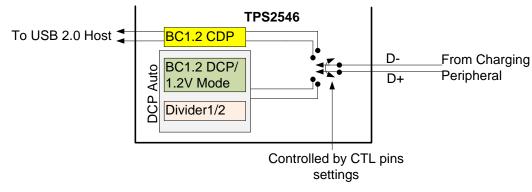

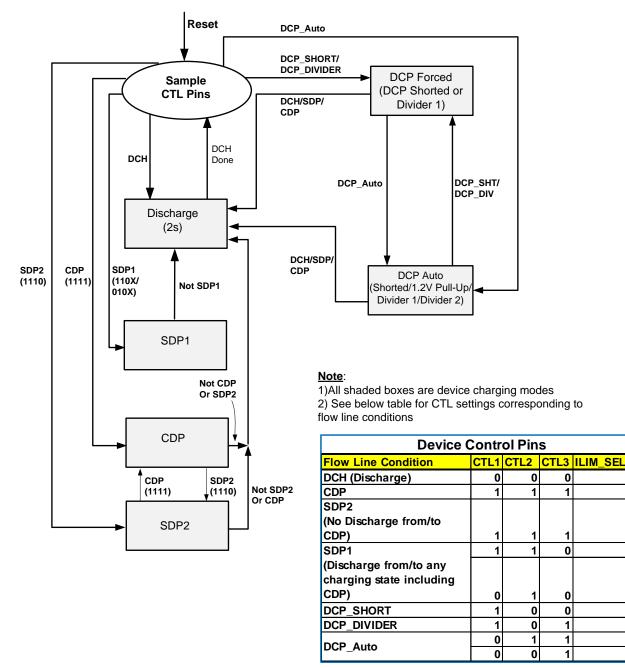

A DCP only provides power but does not support data connection to an upstream port. As shown in following sections, a DCP is identified by the electrical characteristics of its data lines. The TPS2544 emulates DCP in two charging states, namely DCP Forced and DCP Auto as shown in Figure 32. In DCP Forced state the device will support one of the two DCP charging schemes, namely Divider1 or Shorted. In the DCP Auto state, the device charge detection state machine is activated to selectively implement charging schemes involved with the Shorted, Divider1, Divider2, and 1.2V modes. Shorted DCP mode complies with BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, while the Divider and 1.2V modes are employed to charge devices that do not comply with BC1.2 DCP standard.

## DCP BC1.2 and YD/T 1591-2009

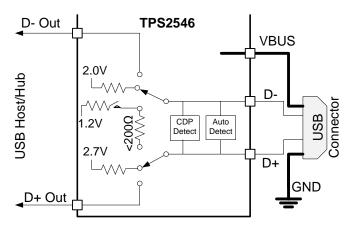

Both standards define that the D+ and D- data lines should be shorted together with a maximum series impedance of 200  $\Omega$ . This is shown in Figure 25.

Figure 25. DCP Supporting BC1.2/YD/T 1591-2009

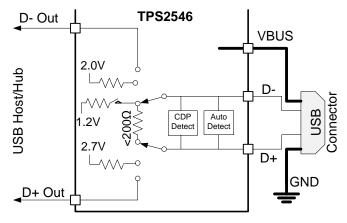

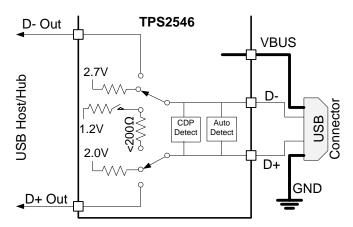

## **DCP Divider Charging Scheme**

There are two Divider charging scheme supported by the device, Divider1 and Divider2 as shown in Figure 26 and Figure 27. In Divider1 charging scheme the device applies 2.0V and 2.7V to D+ and D- data line respectively. This is reversed in Divider2 mode.

Figure 26. DCP Divider1 Charging Scheme

Figure 27. Divider2 Charging Scheme

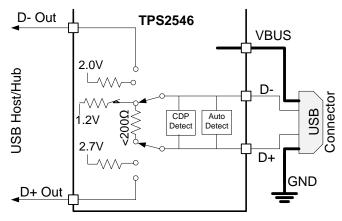

### DCP 1.2V Charging Scheme

1.2V charging scheme is used by some handheld devices to enable fast charging at 2.0A. TPS2544 supports this scheme in the DCP-Auto mode before the device enters BC1.2 shorted mode. To simulate this charging scheme D+/D- lines are shorted and pulled-up to 1.2V for fixed duration then device moves to DCP shorted mode as defined in BC1.2 spec. This is shown inFigure 28

Figure 28. DCP 1.2V Charging Scheme

# DCP Auto Mode

As mentioned above the TPS2544 integrates an auto-detect state machine that supports all the above DCP charging schemes. It starts in Divider1 scheme, however if a BC1.2 or YD/T 1591-2009 compliant device is attached, the TPS2544 responds by discharging OUT, turning back on the power switch and operating in 1.2V mode briefly and then moving to BC1.2 DCP mode. It then stays in that mode until the device releases the data line, in which case it goes back to Divider1 scheme. When a Divider1 compliant device is attached the TPS2544 will stay in Divider1 state.

Also, the TPS2544 will automatically switch between the Divider1 and Divider2 schemes based on charging current drawn by the connected device. Initially the device will set the data lines to Divider1 scheme. If charging current of >750mA is measured by the TPS2544 it switches to Divider2 scheme and test to see if the peripheral device will still charge at a high current. If it does then it stays in Divider2 scheme otherwise it will revert to Divider1 scheme.

Figure 29. DCP Auto Mode

# DCP Forced Shorted / DCP Forced Divider1

In this mode the device is permanently set to one of the DCP schemes (BC1.2/ YD/T 1591-2009 or Divider1) as commanded by its control pin setting per device truth table.

# High-Bandwidth Data Line Switch

The TPS2544 passes the D+ and D- data lines through the device to enable monitoring and handshaking while supporting charging operation. A wide bandwidth signal switch is used, allowing data to pass through the device without corrupting signal integrity. The data line switches are turned on in any of CDP or SDP operating modes. The EN input also needs to be at logic High for the data line switches to be enabled.

## NOTE

- 1. While in CDP mode, the data switches are ON even while CDP handshaking is occurring.

- 2. The data line switches are OFF if EN or all CTL pins are held low, or if in DCP mode. They are not automatically turned off if the power switch (IN to OUT) is in current limit.

- 3. The data switches are for USB 2.0 differential pair only. In the case of a USB 3.0 host, the super speed differential pairs must be routed directly to the USB connector without passing through the TPS2544.

- 4. Data switches are OFF during OUT (VBUS) discharge

## **Device Operation**

www.ti.com.cn

Please refer to the simplified device state diagram in Figure 30. Power-on-reset (POR) holds device in initial state while output is held in discharge mode. Any POR event will take the device back to initial state. After POR clears, device goes to the next state depending on the CTL lines as shown in Figure 30.

Figure 30. TPS2544 Charging States

# **Output Discharge**

To allow a charging port to renegotiate current with a portable device, TPS2544 uses the OUT discharge function. It proceeds by turning off the power switch while discharging OUT, then turning back on the power switch to reassert the OUT voltage. This discharge function is automatically applied as shown in device state diagram.

Х

0

X

Х

Х

Х

Х

# Wake on USB Feature (Mouse/Keyboard Wake Feature)

## **USB 2.0 Background Information**

The TPS2544 data lines interface with USB 2.0 devices. USB 2.0 defines three types of devices according to data rate. These devices and their characteristics relevant to TPS2544 Wake on USB operation are shown below

Low-speed USB devices

- 1.5 Mb/s

- · Wired mice and keyboards are examples

- No devices that need battery charging

- All signaling performed at 2.0V and 0.8V hi/lo logic levels

- D- high to signal connect and when placed into suspend

- D- high when not transmitting data packets

Full-speed USB devices

- 12 Mb/s

- Wireless mice and keyboards are examples

- · Legacy phones and music players are examples

- Some legacy devices that need battery charging

- All signaling performed at 2.0V and 0.8V hi/lo logic levels

- D+ high to signal connect and when placed into suspend

- D+ high when not transmitting data packets

High-speed USB devices

- 480 Mb/s

- Tablets, phones and music players are examples

- Many devices that need battery charging

- Connect and suspend signaling performed at 2.0V and 0.8V hi/lo logic levels

- Data packet signaling performed a logic levels below 0.8V

- D+ high to signal connect and when placed into suspend (same as a full-speed device)

- D+ and D- low when not transmitting data packets

## Wake On USB

Wake on USB is the ability of a wake configured USB device to wake a computer system from its S3 sleep state back to its S0 working state. Wake on USB requires the data lines to be connected to the system USB host before the system is placed into its S3 sleep state and remain continuously connected until they are used to wake the system.

The TPS2544 supports low and high speed HID (human interface device like mouse/key board) wake function. There are two scenarios under which wake on mouse are supported by the TPS2544. The specific CTL pin changes that the TPS2544 will override are shown below. The information is presented as CTL1, CTL2, CTL3. The ILIM\_SEL pin plays no role

- 1. 111 (CDP/SDP2) to 011 (DCP-Auto)

- 2. 010 (SDP1) to 011 (DCP-Auto)

Note that the 110 (SDP1) to 011 (DCP-Auto) transition is not supported. This is done for practical reasons since the transition involves changes to two CTL pins. Depending on which CTL pin changes first, the device will see either a temporary 111 or 010 command. The 010 command is safe but the 111 command will cause an OUT discharge as the TPS2544 will instead proceed to the 111 state.

#### USB Slow-Speed / Full-Speed Device Recognition

TPS2544 is capable of detecting LS or FS device attachment when TPS2544 is in SDP or CDP mode. Per USB spec when no device is attached, the D+ and D- lines are near ground level. When a low speed compliant device is attached to the TPS2544 charging port, D- line will be pulled high in its idle state (mouse/keyboard not activated). However when a FS device is attached the opposite is true in its idle state, i.e. D+ is pulled high and D- remains at ground level.

TPS2544 monitors both D+ and D- lines while CTL pin settings are in CDP or SDP mode to detect LS or FS HID device attachment. To support HID sleep wake, TPS2544 must first determine that it is attached to a LS or FS device when system is in S0 power state. TPS2544 does this as described above. While supporting a LS HID wake is straight forward, supporting FS HID requires making a distinction between a FS and a HS device. This is because a high speed device will always present itself initially as a full speed device (by a 1.5K pull up resistor on D+). The negotiation for high speed then makes the distinction whereby the 1.5K pull up resistor gets removed.

TPS2544 handles the distinction between a FS and HS device at connect by memorizing if the D+ line goes low after connect. A HS device after connect will always undergo negotiation for HS which will require the  $1.5K\Omega$  resistor pull-up on D+ to be removed. To memorize a FS device, TPS2544 requires the device to remain connected for at least 60 sec while system is in S0 mode before placing it in sleep or S3 mode. *If system is placed in sleep mode earlier than the 60 sec window, a FS device may not get recognized and hence could fail to wake system from* S3.This requirement does not apply for LS device.

#### No CTL Pin Timing Requirement After Wake Event and Transition from S3 to S0

Unlike the TPS2543, there is no CTL pin timing requirement for the TPS2544 when the wake configured USB device wakes the system from S3 back to S0. The TPS2543 requires the CTL pins to transition from the DCP-Auto setting back to the SDP/CDP setting within 64ms of the attached USB device signaling a wake event (e.g. mouse clicked or keyboard key pressed). No such timing condition exists for the TPS2544.

# Device Truth Table (TT)

Device TT lists all valid bias combinations for the three control pins CTL1-3 and ILIM\_SEL pin and their corresponding charging mode. It is important to note that the TT *purposely* omits matching charging modes of the TPS2544 with global power states (S0-S5) as device is agnostic to system power states. The TPS2544 monitors its CTL inputs and will transition to whatever charging state it is commanded to go to (except when LS/FS HID device is detected). For example if sleep charging is desired when system is in standby or hibernate state then user must set TPS2544 CTL pins to correspond to DCP\_Auto charging mode per below table. When system is put back to operation mode then set control pins to correspond to SDP or CDP mode and so on.

| CTL1 | CTL2 | CTL3 | ILIM_SEL | MODE                | CURRENT<br>LIMIT<br>SETTING | COMMENT                                                                 |

|------|------|------|----------|---------------------|-----------------------------|-------------------------------------------------------------------------|

| 0    | 0    | 0    | 0        | Discharge           | NA                          | OUT held low                                                            |

| 0    | 0    | 0    | 1        | Discharge           | NA                          | OUT held low                                                            |

| 0    | Х    | 1    | Х        | DCP_Auto            | ILIM_HI                     | Data Lines Disconnected                                                 |

| 0    | 1    | 0    | 0        | SDP1                | ILIM_LO                     | Data Linco anno stad                                                    |

| 0    | 1    | 0    | 1        | SDP1                | ILIM_HI                     | Data Lines connected                                                    |

| 0    | 1    | 1    | 0        | DCP_Auto            | ILIM_HI                     | Data Lines Disconnected                                                 |

| 0    | 1    | 1    | 1        | DCP_Auto            | ILIM_HI                     | Data Lines Disconnected                                                 |

| 1    | 0    | 0    | 0        | DCP _Shorted        | ILIM_LO                     | Device Forestite stavis DOD DOL 0 shareis a reads                       |

| 1    | 0    | 0    | 1        | DCP_Shorted         | ILIM_HI                     | <ul> <li>Device Forced to stay in DCP BC1.2 charging mode</li> </ul>    |

| 1    | 0    | 1    | 0        | DCP / Divider1      | ILIM_LO                     | Device Forestite stavis DOD Divident Observice Made                     |

| 1    | 0    | 1    | 1        | DCP / Divider1      | ILIM_HI                     | <ul> <li>Device Forced to stay in DCP Divider1 Charging Mode</li> </ul> |

| 1    | 1    | 0    | 0        | SDP1                | ILIM_LO                     |                                                                         |

| 1    | 1    | 0    | 1        | SDP1                | ILIM_HI                     | Data Lines Connected                                                    |

| 1    | 1    | 1    | 0        | SDP2 <sup>(1)</sup> | ILIM_LO                     |                                                                         |

| 1    | 1    | 1    | 1        | CDP <sup>(1)</sup>  | ILIM_HI                     | Data Lines Connected                                                    |

#### Table 2. Truth Table

(1) No OUT discharge when changing between 1111 and 1110.

Table 3 can be used as an *aid* to program the TPS2544 per system states however not restricted to below settings only.

| SYSTEM<br>GLOBAL<br>POWER<br>STATE | TPS2544 CHARGING MODE             | CTL1 | CTL2 | CTL3 | ILIM_SEL | CURRENT LIMIT<br>SETTING |

|------------------------------------|-----------------------------------|------|------|------|----------|--------------------------|

| S0                                 | SDP1                              | 1    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

| S0                                 | SDP2, no discharge to / from CDP  | 1    | 1    | 1    | 0        | ILIM_LO                  |

| S0                                 | CDP                               | 1    | 1    | 1    | 1        | ILIM_HI                  |

| S3/S4/S5                           | Auto mode                         | 0    | 0    | 1    | 0        | ILIM_HI                  |

| S3                                 | Auto mode, keyboard/mouse wake-up | 0    | 1    | 1    | 0        | ILIM_HI                  |

| S3                                 | SDP1, keyboard/mouse wake-up      | 0    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

## Table 3. Control Pin Settings Matched to System Power States

# CDP/SDP Auto Switch

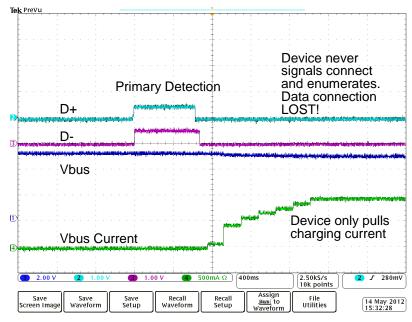

TPS2544 is equipped with a CDP/SDP auto-switch feature to support some popular phones in the market that are not compliant to the BC1.2 specification, as they fail to establish data connection in CDP mode. These phones use primary detection (used to distinguish between an SDP and different types of Charging Ports) to only identify ports as SDP (data / no charge) or DCP (no data / charge). They do not recognize CDP (data /charge) ports. When connected to a CDP port, these phones classify the port as a DCP and will only charge. Since charging ports are configured as CDP when the computer is in S0, users do not get the expected data connection. See Figure 39

**STRUMENTS**

ZHCSAX4A-FEBRUARY 2013-REVISED FEBRUARY 2013

Figure 31. CDP/SDP Auto

To remedy this problem TPS2544 employs a CDP/SDP Auto Switch scheme to ensure these BC1.2 non-compliant phones will establish data connection by following below steps:

- The TPS2544 will determine when a non-compliant phone has wrongly classified a CDP port as a DCP port and has not made a data connection

- The TPS2544 will then automatically do a OUT (VBUS) discharge and reconfigure the port as an SDP

- This allows the phone to discover it is now connected to an SDP and establish a data connection

- The TPS2544 will then switch automatically back to CDP without doing an OUT (VBUS) discharge

- The phone will continue to operate like it is connected to a SDP since OUT (VBUS) was not interrupted

- The port is now ready in CDP if a new device is attached

## **Over-Current Protection**

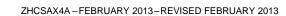

When an over-current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before VIN has been applied. The TPS2544 senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for nominally one to two microseconds before the current-limit circuit can react. The device operates in constant-current mode after the current-limit circuit has responded. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting. The device will remain off until the junction temperature cools approximately 20°C and will then re-start. The device will continue to cycle on/off until the over-current condition is removed.

(1)

# **Current-Limit Settings**

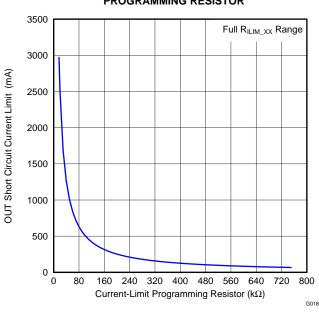

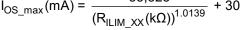

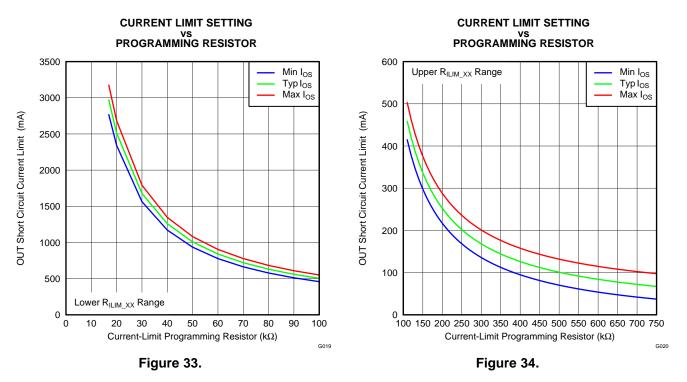

The TPS2544 has two independent current limit settings that are each programmed externally with a resistor. The ILIM\_HI setting is programmed with  $R_{ILIM_HI}$  connected between ILIM\_HI and GND. The ILIM\_LO setting is programmed with  $R_{ILIM_LO}$  connected between ILIM\_LO and GND. Consult the Device Truth Table (Table 2) to see when each current limit is used. Both settings have the same relation between the current limit and the programming resistor.

R<sub>ILIM LO</sub> is optional and the ILIM\_LO pin may be left unconnected if the following condition is met:

• ILIM\_SEL is always set high

The following equation programs the typical current limit:

$$I_{OS\_typ}(mA) = \frac{50,250}{R_{ILIM\_XX}(k\Omega)}$$

$R_{ILIM XX}$  corresponds to either  $R_{ILIM HI}$  or  $R_{ILIM LO}$  as appropriate.

#### TYPICAL CURRENT LIMIT SETTING vs PROGRAMMING RESISTOR

Figure 32.

(3)

#### ZHCSAX4A-FEBRUARY 2013-REVISED FEBRUARY 2013

Many applications require that the current limit meet specific tolerance limits. When designing to these tolerance limits, both the tolerance of the TPS2544 current limit and the tolerance of the external programming resistor must be taken into account. The following equations approximate the TPS2544 minimum / maximum current limits to within a few mA and are appropriate for design purposes. The equations do not constitute part of TI's published device specifications for purposes of TI's product warranty. These equations assume an ideal - no variation - external programming resistor. To take resistor tolerance into account, first determine the minimum / maximum resistor values based on its tolerance specifications and use these values in the equations. Because of the inverse relation between the current limit and the programming resistor, use the maximum resistor value in the  $I_{OS min}$  equation.

$$I_{OS\_min}(mA) = \frac{45,271}{(R_{ILIM\_XX}(k\Omega))^{0.98437}} - 30$$

(2)

$$I_{OS\_min}(mA) = \frac{55,325}{55,325} + 30$$

The traces routing the  $R_{ILIM_XX}$  resistors should be a sufficiently low resistance as to not affect the current-limit accuracy. The ground connection for the  $R_{ILIM_XX}$  resistors is also very important. The resistors need to reference back to the TPS2544 GND pin. Follow normal board layout practices to ensure that current flow from other parts of the board does not impact the ground potential between the resistors and the TPS2544 GND pin.

# **FAULT Response**

The FAULT open-drain output is asserted (active low) during an over-temperature or current limit condition. The output remains asserted until the fault condition is removed. The TPS2544 is designed to eliminate false FAULT reporting by using an internal deglitch circuit for current limit conditions without the need for external circuitry. This ensures that FAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. Over-temperature conditions are not deglitched and assert the FAULT signal immediately.

## Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted oscillations on the output due to input voltage drop from large current surges.

# **Thermal Sense**

The TPS2544 protects itself with two independent thermal sensing circuits that monitor the operating temperature of the power distribution switch and disables operation if the temperature exceeds recommended operating conditions. The device operates in constant-current mode during an over-current condition, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, so the junction temperature rises during an over-current condition. The first thermal sensor turns off the power switch when the die temperature exceeds 135°C and the part is in current limit. The second thermal sensor turns off the power switch when the die temperature exceeds 155°C regardless of whether the power switch is in current limit. Hysteresis is built into both thermal sensors, and the switch turns on after the device has cooled by approximately 20°C. The switch continues to cycle off and on until the fault is removed. The open-drain false reporting output FAULT is asserted (active low) during an over-temperature shutdown condition.

# **REVISION HISTORY**

. .

| Cr | nanges from Original (February 2013) to Revision A | Page    | Э |

|----|----------------------------------------------------|---------|---|

| •  | 将器件状态从:预览改为:生产                                     | ····· · | 1 |

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS2544RTER      | ACTIVE        | WQFN         | RTE                | 16   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | 2544                    | Samples |

| TPS2544RTET      | ACTIVE        | WQFN         | RTE                | 16   | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | 2544                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

Texas

STRUMENTS

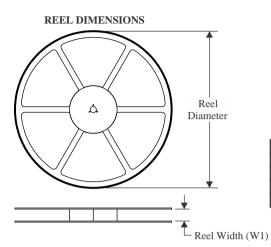

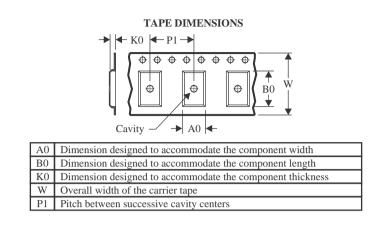

# TAPE AND REEL INFORMATION

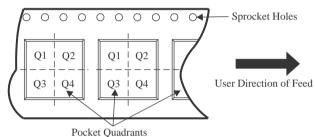

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS2544RTER                 | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2544RTET                 | WQFN            | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com

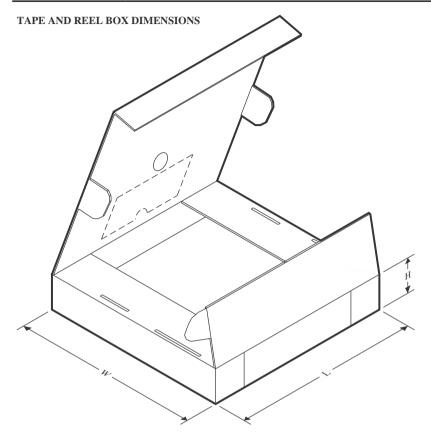

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2544RTER | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS2544RTET | WQFN         | RTE             | 16   | 250  | 210.0       | 185.0      | 35.0        |

# **RTE 16**

3 x 3, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# **RTE0016C**

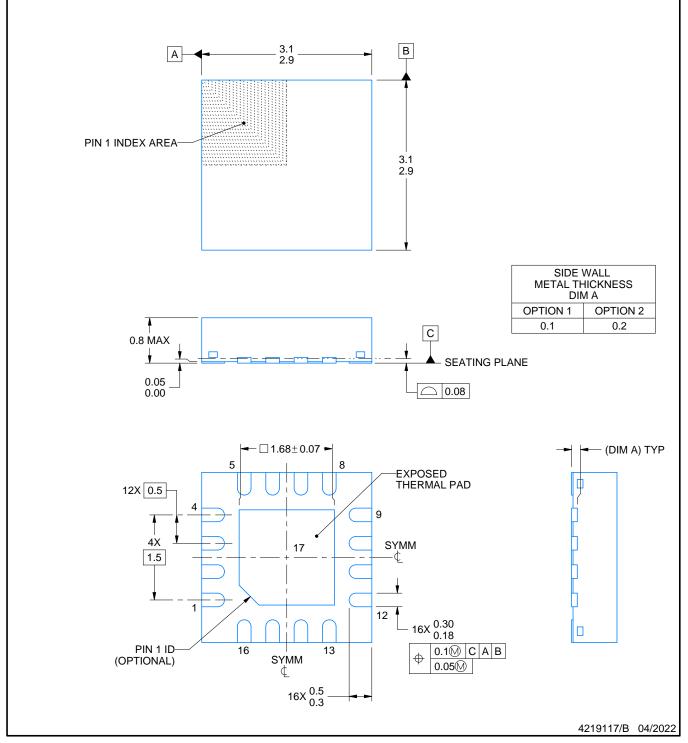

# **PACKAGE OUTLINE**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

# **RTE0016C**

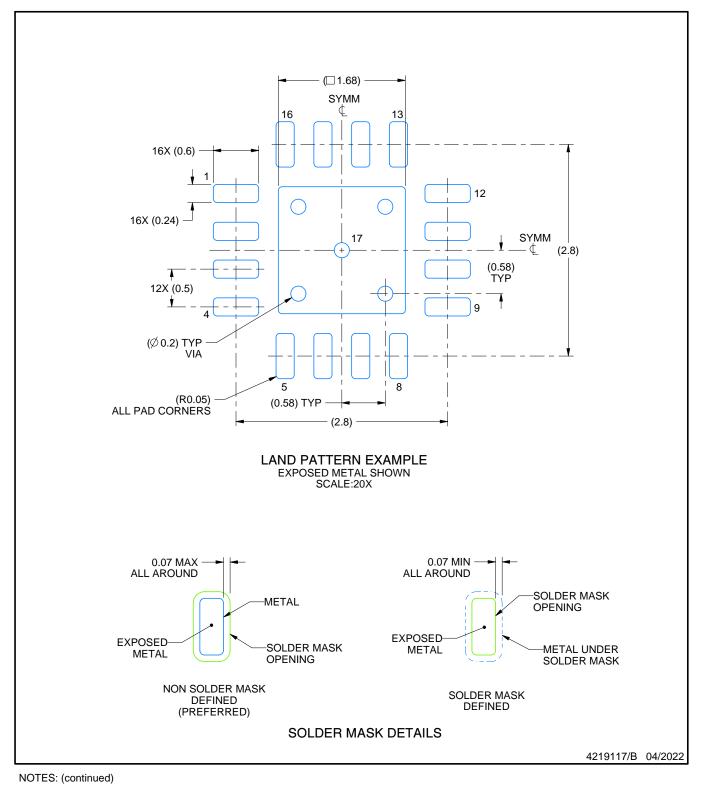

# **EXAMPLE BOARD LAYOUT**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# **RTE0016C**

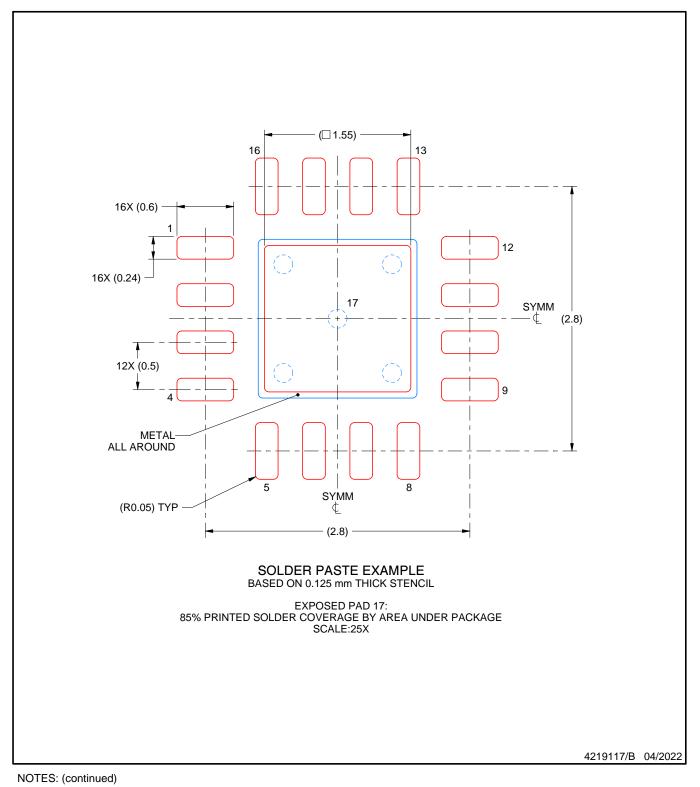

# **EXAMPLE STENCIL DESIGN**

# WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司