ZHCSBI0C -MARCH 2013-REVISED OCTOBER 2014

LM3279

# LM3279 适用于 3G 和 4G RF 功率放大器、具有 MIPI<sup>®</sup>RFFE 接口的 降压-升压转换器

### 1 特性

- MIPI®RFFE 数字控制接口

- 具有内部无缝转换的高效脉冲频率调制 (PFM) 和脉 宽调制 (PWM) 模式

- 由单节锂离子电池供电运行: 2.7V 至 5.5V

- 可调节输出电压:

- RFFE 数字控制: 0.4V 至 4.2V

- 模拟控制: 0.5V 至 4.2V

- V<sub>BATT</sub> ≥ 3.2V, V<sub>OUT</sub> = 3.6V 时的最大负载能力为 1A

- 2.4MHz (典型值) 开关频率

- 无缝降压-升压模式转换

- 快速输出电压转换: 20µs 内可由 0.8V 转换至 4V

- 高效率: 95%(典型值)(V<sub>BATT</sub>= 3.7V、 V<sub>OUT</sub>= 3.3V、电流为 300mA)

- 输入过流限制

- 输出过压钳位

- 内部补偿

### 2 应用

- 3G/4G 智能手机

- RF PC 卡

- 平板电脑、电子书阅读器

- 电池供电类 RF 器件

### 3 说明

LM3279 是一款降压-升压 DC/DC 转换器,专为生成高于或低于给定输入电压的输出电压而设计,尤其适用于便携式应用中由单节锂离子电池供电的功率放大器。

LM3279 具有四种运行模式: 脉宽调制 (PWM)、脉频调制 (PFM)、待机模式和关断模式。在正常情况下,LM3279 在 2.4MHz 典型开关频率下以完全同步的PWM 模式运行,可在降压与升压运行状态之间实现无缝切换。节能 PFM 模式提高了低功耗 RF 传输模式期间的效率,并且节省了流耗。对于高传输功率,此器件运行在 PWM 降压或升压模式下,而此器件可在低功耗传输期间在 PWM 和 PFM 模式之间转换。LM3279可通过内置的 MIPI PFFE 数字控制接口或外部 MCU的模拟控制接口进行控制,其设计具有灵活性。

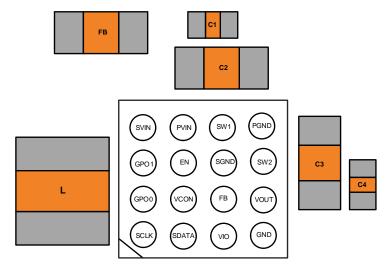

功率转换器拓扑结构可通过使用一个小型封装,外壳尺寸电感器和两个表面贴装电容器来实现尽可能小的总体解决方案尺寸。

LM3279 针对降压和升压模式运行而进行了内部补偿,从而提供了最佳的瞬态响应。

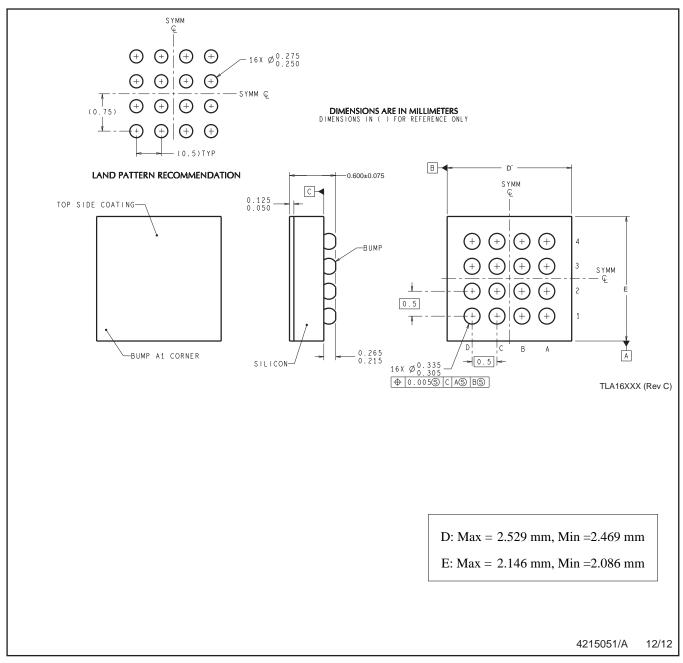

### 器件信息<sup>(1)</sup>

| 器件型号   | 封装         | 封装尺寸(最大值)         |

|--------|------------|-------------------|

| LM3279 | DSBGA (16) | 2.529mm x 2.146mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

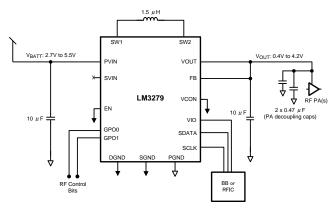

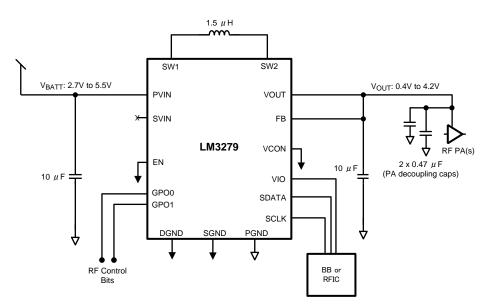

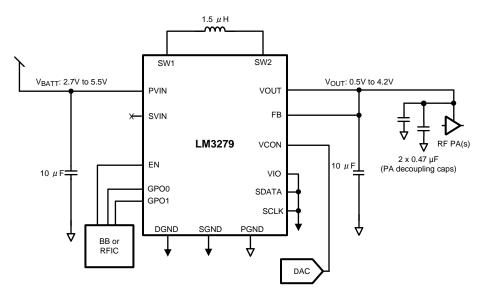

### 简化电路原理图

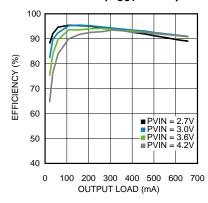

### PWM 效率 (V<sub>OUT</sub>= 2.4V)

|   | 目录                                                 | 表  |                                     |                  |

|---|----------------------------------------------------|----|-------------------------------------|------------------|

| 1 | 特性1                                                |    | 7.4 Device Functional Modes         | 15               |

| 2 | 应用 1                                               |    | 7.5 Programming                     | 16               |

| 3 | 说明1                                                |    | 7.6 Registers                       | 19               |

| 4 | 修订历史记录 2                                           | 8  | Application and Implementation      | <mark>2</mark> 1 |

| 5 | Pin Configuration and Functions                    |    | 8.1 Application Information         | <mark>2</mark> 1 |

| 6 | Specifications4                                    |    | 8.2 Typical Application             | 21               |

| U | 6.1 Absolute Maximum Ratings                       | 9  | Power Supply Recommendations        | <mark>2</mark> 4 |

|   | 6.2 Handling Ratings                               | 10 | Layout                              | 25               |

|   | 6.3 Recommended Operating Conditions               |    | 10.1 Layout Guidelines              | 25               |

|   | 6.4 Thermal Information                            |    | 10.2 Layout Examples                | 26               |

|   | 6.5 Electrical Characteristics                     |    | 10.3 DSBGA Package Assembly And Use | 30               |

|   | 6.6 System Characteristics 6                       |    | 10.4 Manufacturing Considerations   | 30               |

|   | 6.7 System Characteristics Recommended Capacitance | 11 | 器件和文档支持                             | <mark>3</mark> 1 |

|   | Specifications7                                    |    | 11.1 器件支持                           | 31               |

|   | 6.8 Typical Performance Characteristics9           |    | 11.2 文档支持                           | 31               |

| 7 | Detailed Description 12                            |    | 11.3 商标                             | 31               |

|   | 7.1 Overview 12                                    |    | 11.4 静电放电警告                         | 31               |

|   | 7.2 Functional Block Diagram 13                    |    | 11.5 Glossary                       | 31               |

|   | 7.3 Feature Description                            | 12 | 机械、封装和可订购信息                         | <mark>3</mark> 1 |

### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Revision B (November 2013) to Revision C Page ● 已添加 器件信息表和处理额定值表,特性 描述,器件功能模式,应用和实施,电源相关建议,布局,器件和文档支持以及机械、封装和可订购信息部分;已将一些曲线移至应用曲线部分。 1 Changes from Revision A (May 2013) to Revision B Page ● 已更改 模拟控制: 0.6V 至 0.5V 1 • Changed 0.2V ≤ VCON ≤ 1.4V to 0.167V ≤ VCON ≤ 1.4V 6 • Changed 0.2 V to 0.167 V 6 • Changed 2.00 from max. to typ. 7 • Changed 0.2V (min.) to 1.4V (max. typ.) to 0.167V (min.) to 1.4V (max. typ.); from 0.6V to 4.2V output to from 0.5V to 4.2V output 14 • Added (default) 19

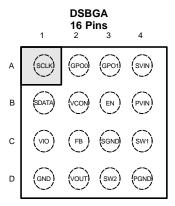

### **5 Pin Configuration and Functions**

Top View (Bumps Down)

### **Pin Functions**

| PIN    |       |        |                                                                                                                                                                                                                                                                                                                                                          |

|--------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME  | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |

| A1     | SCLK  | IN     | Digital control interface (DCON) RFFE Bus clock input. Typically connected to RFFE master on RF or Baseband IC. SCLK must be held low when VIO is not applied.                                                                                                                                                                                           |

| B1     | SDATA | I/O    | Digital control interface (DCON) RFFE Bus data input/output. Typically connected to RFFE master on RF or Baseband IC. SDATA must be held low when VIO is not applied.                                                                                                                                                                                    |

| C1     | VIO   | IN     | Digital control interface (DCON) 1.8-V supply input. VIO functions as the RFFE interface reference voltage. VIO also functions as a reset and enable input to LM3279. Bypass capacitor should be connected between VIO and GND. Typically connected to voltage regulator controlled by RF or Baseband IC. When VIO = HIGH, EN shall be connected to GND. |

| D1     | GND   | Ground | Digital Ground.                                                                                                                                                                                                                                                                                                                                          |

| A2     | GPO0  | I/O    | Multipurpose GPIO. When VIO = HIGH, GPO0 is a general purpose output for configuring RF front end circuitry. When the GPO0 control bit in Register 02 is set to 1, the output is driven to a 1.8-V (VIO) high logic level. The output is pulled to a low logic level when the GPO0 control bit is set to 0. (Input has an internal pull-up resistor.)    |

| B2     | VCON  | IN     | Voltage Control Analog input. When EN = HIGH, VCON controls the output voltage in PWM and PFM modes. When in Digital control, VCON can be left as no connect or connected to system ground.                                                                                                                                                              |

| C2     | FB    | Ground | Feedback input to inverting input of error amplifier. Connect output voltage directly to this node at load point.                                                                                                                                                                                                                                        |

| D2     | VOUT  | PWR    | Regulated output voltage of LM3279. Connect this to a 10- $\mu F$ ceramic output filter capacitor to GND.                                                                                                                                                                                                                                                |

| А3     | GPO1  | I/O    | Multipurpose GPIO. When VIO = HIGH, GPO1 is a general purpose output for configuring RF front end circuitry. When the GPO1 control bit in Register 02 is set to 1, the output is driven to a 1.8-V (VIO) high logic level. The output is pulled to a low logic level when the GPO1 control bit is set to 0. (Input has an internal pull-up resistor.)    |

| В3     | EN    | IN     | Enable Pin. Pulling this pin higher than 1.2 V enables part to function in analog control mode. VIO must be tied to ground.                                                                                                                                                                                                                              |

| C3     | SGND  | Ground | Signal Ground for analog circuits and control circuitry.                                                                                                                                                                                                                                                                                                 |

| D3     | SW2   | PWR    | Switch pin for Internal Power Switches M3 and M4. Connect inductor between SW1 and SW2.                                                                                                                                                                                                                                                                  |

| A4     | SVIN  | PWR    | SVIN is no connect. Analog supply is internally connected to PVIN.                                                                                                                                                                                                                                                                                       |

| B4     | PVIN  | PWR    | Power MOSFET input and power current input pin. Optional low-pass filtering may help reduce radiated EMI and noise during buck and buck-boost modes.                                                                                                                                                                                                     |

| C4     | SW1   | PWR    | Switch pin for Internal Power Switches M1 and M2. Connect inductor between SW1 and SW2.                                                                                                                                                                                                                                                                  |

| D4     | PGND  | Ground | Power Ground for Power MOSFETs and gate drive circuitry.                                                                                                                                                                                                                                                                                                 |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                              | MIN           | MAX                | UNIT |

|--------------------------------------------------------------|---------------|--------------------|------|

| PVIN, VOUT to GND                                            | -0.2          | 6                  |      |

| PGND to SGND, GND                                            | PGND -0.2     | 0.2                |      |

| VIO, SDATA, SCLK, EN, VCON, GPO1/GPO0 to SGND, GND           | -0.2          | 6                  | V    |

| FB to PGND                                                   | -0.2          | 6                  | V    |

| SW1, SW2                                                     | (PGND -0.2V)  | 6                  |      |

| Continuous power dissipation (3)                             | Internally li | Internally limited |      |

| Maximum operating junction temperature (T <sub>J-MAX</sub> ) |               | 150                | °C   |

| Maximum lead temperature (soldering)                         | See (4        | See (4)            |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pins.

### 6.2 Handling Ratings

|                    |                          |                                                                             | MIN | MAX  | UNIT |

|--------------------|--------------------------|-----------------------------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>   | Storage temperature rang | Storage temperature range                                                   |     | 150  | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | 0   | 1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)(2)

| gg                                                             |     |     |       |      |  |  |

|----------------------------------------------------------------|-----|-----|-------|------|--|--|

|                                                                | MIN | NOM | MAX   | UNIT |  |  |

| Input voltage                                                  | 2.7 |     | 5.5   | V    |  |  |

| Output voltage (digital control)                               | 0.4 |     | 4.212 | V    |  |  |

| Recommended current load                                       | 0   |     | 1000  | mA   |  |  |

| Operating ambient temperature (T <sub>A</sub> ) <sup>(3)</sup> | -30 |     | 85    | °C   |  |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pins.

<sup>(3)</sup> Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and disengages at T<sub>J</sub> = 125°C (typ.).

<sup>(4)</sup> For detailed soldering specifications and information, please refer to Texas Instruments Application Note 1112: DSBGA Wafer Level Chip Scale Package (SNVA009).

<sup>(3)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

### 6.4 Thermal Information

|                      |                                              | DSBGA   |      |

|----------------------|----------------------------------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YZR     | UNIT |

|                      |                                              | 16 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 70.1    |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 14.4    |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 10      | °C/M |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.7     | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 10      |      |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics(1)

Limits are for  $T_A = T_J = 25$ °C, and specifications apply to the LM3279 Typical Application Circuits with: PVIN = 3.8 V, VIO or EN = 1.8 V, unless otherwise specified.

|                                 | PARAMETER                                                                                                                                                                                                       | TEST CONDITIONS                                                                                                               | MIN       | TYP   | MAX        | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|-------|------------|------|

|                                 | Minimum ED valte as                                                                                                                                                                                             | V <sub>SET</sub> = 0Bh                                                                                                        | 0.35      | 0.40  | 0.45       |      |

| $V_{FB,MIN}$                    | Minimum FB voltage                                                                                                                                                                                              | VCON = 0.167 V                                                                                                                | 0.43      | 0.5   | 0.570      |      |

|                                 | M : 50 %                                                                                                                                                                                                        | V <sub>SET</sub> = 75h                                                                                                        | 4.122     | 4.212 | 4.302      | V    |

| $V_{FB,MAX}$                    | Maximum FB voltage                                                                                                                                                                                              | VCON = 1.4 V                                                                                                                  | 4.11      | 4.2   | 4.29       |      |

| I <sub>Q_PWM</sub>              | DC bias current in PVIN, SVIN                                                                                                                                                                                   | No switching $^{(2)}$ FB = HIGH<br>Max limits = $-30^{\circ}$ C $\leq$ T <sub>J</sub> = T <sub>A</sub> $\leq$ 85 $^{\circ}$ C |           | 1.4   | 2          | mA   |

| I <sub>SHDN</sub>               | Shutdown supply current $VIO = EN = 0 \text{ V}, VCON = 0 \text{ V}, \\ SW1 = SW2 = V_{OUT} = 0 \text{ V} \\ Max \text{ limits} = -30^{\circ}\text{C} \leq T_{\text{J}} = T_{\text{A}} \leq 85^{\circ}\text{C}$ |                                                                                                                               |           | 0.2   | 2          | μΑ   |

| I <sub>Q STBY</sub>             | Standby supply current                                                                                                                                                                                          | VIO = 1.8 V, V <sub>SET_CTRL</sub> = 02h,<br>SW1 = SW2 = V <sub>OUT</sub> = 0 V                                               |           | 1.2   |            | mA   |

| I <sub>LIM_L</sub>              | Input current limit (large)                                                                                                                                                                                     | Open Loop (3) VCON = 1.2 V                                                                                                    | 1500      | 1700  |            | A    |

| I <sub>LIM_S</sub>              | Input current limit (small)                                                                                                                                                                                     | Open Loop (3) VCON = 0.2 V                                                                                                    | 700       | 850   |            | mA   |

| $f_{OSC\_PWM}$                  | Internal oscillator frequency                                                                                                                                                                                   | PWM Min and Max limits = $-30^{\circ}$ C $\leq T_J = T_A \leq 85^{\circ}$ C                                                   | 2.1       | 2.4   | 2.7        | MHz  |

| f <sub>SCLK</sub>               | SCLK clock frequency                                                                                                                                                                                            |                                                                                                                               | 0.032     |       | 26         |      |

| I <sub>VIO-IN</sub>             | VIO voltage average input current                                                                                                                                                                               | VIO = 1.8 V, Average during 26-MHz write                                                                                      |           |       | 1.25       | mA   |

|                                 | I <sub>SDATA</sub>                                                                                                                                                                                              | VIN = 0.2*VIO                                                                                                                 | -2        |       | 1          |      |

| I <sub>IL</sub>                 | I <sub>SCLK</sub>                                                                                                                                                                                               | VIIV = 0.2 VIO                                                                                                                | -1        |       | 1          | μA   |

| L                               | I <sub>SDATA</sub>                                                                                                                                                                                              | VIN = 0.8*VIO                                                                                                                 | -2        |       | 10         | μΑ   |

| I <sub>IH</sub>                 | I <sub>SCLK</sub>                                                                                                                                                                                               | VIIV = 0.0 VIO                                                                                                                | -1        |       | 10         |      |

| $V_{\text{IH}}$                 | Input high-level threshold EN, GPO0, GPO1                                                                                                                                                                       | Min and May limits 2000 c.T. T < 0500                                                                                         | 1.2       |       |            | V    |

| $V_{IL}$                        | Input low-level threshold EN, GPO0, GPO1                                                                                                                                                                        | Min and Max limits = $-30$ °C ≤ T <sub>J</sub> = T <sub>A</sub> ≤ 85°C                                                        |           |       | 0.6        | V    |

| V <sub>IH-SDATA</sub> ,<br>SCLK | Input high-level threshold SDATA, SCLK                                                                                                                                                                          |                                                                                                                               | 0.4*VIO   |       | 0.7*VIO    |      |

| V <sub>IL-SDATA</sub> ,<br>SCLK | Input low-level threshold SDATA, SCLK                                                                                                                                                                           |                                                                                                                               | 0.3*VIO   |       | 0.6*VIO    | V    |

| V <sub>OH-SDATA</sub>           | Output high-level threshold SDATA                                                                                                                                                                               | I <sub>SDATA</sub> = −2 mA                                                                                                    | 0.8*VIO   |       | VIO + 0.01 | v    |

| V <sub>OL-SDATA</sub>           | Output low-level threshold SDATA                                                                                                                                                                                | I <sub>SDATA</sub> = 2 mA                                                                                                     |           |       | 0.2*VIO    |      |

| V <sub>OH-GPO</sub>             | Output high-level threshold GPO                                                                                                                                                                                 | I <sub>OUT</sub> = ±200 μA                                                                                                    | VIO-0.15V |       | VIO+0.1V   |      |

| $V_{OL\text{-}GPO}$             | Output low-level threshold GPO                                                                                                                                                                                  | I <sub>OUT</sub> = ±200 μA                                                                                                    | -0.4      |       | 0.3        | V    |

| V <sub>SET-LSB</sub>            | Output voltage LSB                                                                                                                                                                                              | V <sub>SET_CTRL</sub> = 40h to 41h                                                                                            |           | 36    |            | mV   |

| $I_{EN}$                        | EN pin pulldown current                                                                                                                                                                                         | VIO = 0 V                                                                                                                     |           | 5     | 10         | μΑ   |

<sup>(1)</sup> Min and Max limits are specified by design, test, or statistical analysis.

<sup>(2)</sup> I<sub>Q</sub> specified here is when the part is not switching.

<sup>3)</sup> The parameters in the electrical characteristics table are tested under open loop conditions at P<sub>VIN</sub> = 3.8 V. For performance over the input voltage range and closed loop results refer to the datasheet curves.

### Electrical Characteristics<sup>(1)</sup> (continued)

Limits are for  $T_A = T_J = 25$ °C, and specifications apply to the LM3279 Typical Application Circuits with: PVIN = 3.8 V, VIO or EN = 1.8 V, unless otherwise specified.

|                          | PARAMETER                               | TEST CONDITIONS                                                                                                                                                 | MIN | TYP | MAX | UNIT |

|--------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Gain                     | Internal gain (4)                       | 0.167 V ≤ VCON ≤ 1.4 V                                                                                                                                          |     | 3   |     | V/V  |

| I <sub>CON</sub>         | VCON pin input leakage                  | EN = 3.8 V                                                                                                                                                      | -1  |     | 1   |      |

| I <sub>OUT_LEAKAGE</sub> | Leakage into VOUT pin of the buck-boost | EN = 0, $V_{OUT} \le 4.2 \text{ V}$ , $V_{BATT} \le 5.5 \text{ V}$<br>Max limits = $-30^{\circ}\text{C} \le \text{T}_{J} = \text{T}_{A} \le 85^{\circ}\text{C}$ |     |     | 5   | μΑ   |

<sup>(4)</sup> When using analog control (EN = HIGH) to calculate  $V_{OUT}$ , use the following equation:  $V_{OUT} = VCON \times 3$ .

### 6.6 System Characteristics

The following spec table entries are specified by design and verifications, providing the component values in the typical application circuits are used: L = 1.5  $\mu$ H, DFE201610C-1R5M (2016)/TOKO; C<sub>IN</sub> and C<sub>OUT</sub> each = 10  $\mu$ F 6.3 V, C105A106MQ5NUNC (0402)/Samsung; PA decoupling cap emulation = 0.47  $\mu$ F, GRM033R60J474ME90 (0201)/Murata. **These parameters are not verified by production testing.** Typical limits are T<sub>A</sub> = 25°C. Min and Max limits apply over the full ambient temperature range (-30°C  $\leq$  T<sub>A</sub>  $\leq$  85°C) and over the V<sub>IN</sub> range = 2.7 V to 5.5 V, unless otherwise specified.

| PARAMETER                           |                                                        | TEST CONDITIONS                                                                                                                                                                                                                   | MIN   | TYP | MAX  | UNIT |  |

|-------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|--|

| T <sub>ON</sub>                     | Turn-on time (time for output to reach 0V→90% × 3.4 V) | $V_{BATT} = 3.8 \text{ V}, \text{ VIO} = 1.8 \text{ V}, \text{ RFFE write } V_{SET} = 3.42 \text{ V} $ $V_{SET\_CTRL} = 5\text{Fh}, I_{OUT} = 0\text{mA}$ $EN = L \text{ to H}, V_{BATT} = 3.8 \text{ V}, VCON = 1.14 \text{ V},$ |       | 35  | 50   | μs   |  |

|                                     |                                                        | $I_{OUT} = 0 \text{ mA}$ $V_{BATT} \ge 3 \text{ V}, V_{OUT} = 3.8 \text{ V}$                                                                                                                                                      | 750   |     |      |      |  |

| I <sub>OUT_MAX</sub>                | Max output current                                     | $V_{BATT} \ge 3.2 \text{ V}, V_{OUT} = 4.2 \text{ V}$                                                                                                                                                                             | 650   |     |      | mA   |  |

| _                                   |                                                        | Boost (% M4 on)                                                                                                                                                                                                                   |       |     | 50%  |      |  |

| D <sub>MAX</sub> Maximum duty cycle |                                                        | Buck (% M1 on)                                                                                                                                                                                                                    |       |     | 100% |      |  |

| F <sub>OSC_PFM</sub>                | Internal oscillator frequency                          | PFM: $V_{OUT} = 0.6V$ , $P_{VIN} = 3.7 V$<br>$I_{OUT} = 13 \text{ mA}$                                                                                                                                                            |       | 63  |      | kHz  |  |

| C <sub>L</sub>                      | Load capacitance                                       | Half speed readback SCLK = 13 MHz, not including LM3279 capacitance. $T_A = 25^{\circ}C$                                                                                                                                          | 10    |     | 50   | pF   |  |

| C <sub>VCON</sub>                   | VCON input capacitance                                 | VCON = 1V, Test frequency = 100 kHz, T <sub>A</sub> = 25°C                                                                                                                                                                        |       |     | 10   | pF   |  |

| VCON_LIN                            | VCON linearity                                         | 0.167 V ≤ VCON ≤ 1.4 V                                                                                                                                                                                                            | -2.5% |     | 2.5% |      |  |

| VIO                                 | VIO I/O voltage level                                  | 1.8V Bus, T <sub>A</sub> = 25°C                                                                                                                                                                                                   | 1.65  | 1.8 | 1.95 | V    |  |

|                                     | Ripple voltage                                         | $V_{BATT} \ge 3.2 \text{ V}, 0.6 \le V_{OUT} \le 4.2 \text{ V}, 0 \text{ mA} \le I_{OUT} \le 430 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                            |       | 15  | 50   |      |  |

| $V_{O\_RIPPLE}$                     | PFM ripple                                             | $V_{OUT} = 0.6 \text{ V}, I_{OUT} = 5\text{mA}$                                                                                                                                                                                   |       | 40  |      | mV   |  |

|                                     | Ripple voltage in mode transition                      | $V_{BATT} = 3 \text{ V to 5 V}, Tr = Tf = 30s$<br>3.3 V \leq V_{OUT} \leq 4.2 V                                                                                                                                                   |       |     | 50   |      |  |

| 437                                 | Line regulation                                        | V <sub>BATT</sub> = 3.2 V to 4.9 V, V <sub>OUT</sub> = 3.5 V,<br>PWM Operation                                                                                                                                                    |       |     | 10   | mV   |  |

| ΔV <sub>OUT</sub>                   | Load regulation                                        | $I_{OUT}$ = 0 mA to 500 mA, $V_{BATT}$ = 3.2 V to 4.9 V, PWM Operation                                                                                                                                                            |       |     | 20   | mv   |  |

| line to                             | Line transitation                                      | $V_{BATT}$ = 3.6 V to 4.2 V, Tr = Tf = 10 μs, $V_{OUT}$ = 3.5 V, $R_{LOAD}$ = 11.4 Ω, PWM                                                                                                                                         | -100  |     | 100  | \/   |  |

| Line_tr                             | Line transient response                                | $V_{BATT}$ = 3.6 V to 4.2 V, $Tr$ = $Tf$ = 10 $\mu$ s, $V_{OUT}$ = 0.8 V, $R_{LOAD}$ = 20 $\Omega$ , $PFM$                                                                                                                        | -5    |     | 5    | mV   |  |

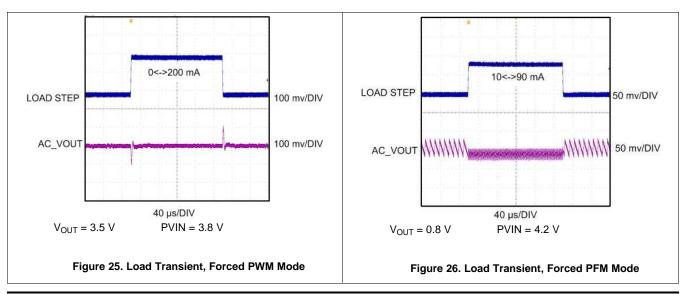

| Load tr                             | Load transient response                                | $I_{OUT}$ = 1 mA to 200 mA, Tr = Tf = 1 $\mu$ s, $V_{BATT}$ = 4.2 V, $V_{OUT}$ = 3.5 V, PWM                                                                                                                                       | -100  |     | 100  | mV   |  |

| LUAU_II                             | Load transient response                                | $I_{OUT}$ = 10 mA to 90 mA, Tr = Tf = 1 $\mu$ s, $V_{BATT}$ = 4.2 V, $V_{OUT}$ = 0.8 V, PFM                                                                                                                                       | -10   |     | 10   | IIIV |  |

### **System Characteristics (continued)**

The following spec table entries are specified by design and verifications, providing the component values in the typical application circuits are used: L = 1.5  $\mu$ H, DFE201610C-1R5M (2016)/TOKO; C<sub>IN</sub> and C<sub>OUT</sub> each = 10  $\mu$ F 6.3 V, C105A106MQ5NUNC (0402)/Samsung; PA decoupling cap emulation = 0.47  $\mu$ F, GRM033R60J474ME90 (0201)/Murata. These parameters are not verified by production testing. Typical limits are T<sub>A</sub> = 25°C. Min and Max limits apply over the full ambient temperature range (-30°C  $\leq$  T<sub>A</sub>  $\leq$  85°C) and over the V<sub>IN</sub> range = 2.7 V to 5.5 V, unless otherwise specified.

| PARAMETER             |                                               | TEST CONDITIONS MIN TYP M                                                                       |     | MAX | UNIT |     |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|------|-----|

|                       | VOUT transient response overshoot             |                                                                                                 |     | 200 |      | mV  |

| $V_{OUT\_TR}$         | VOUT transient response rise time             | $V_{BATT}$ = 3.2 V to 4.2 V,<br>$V_{OUT}$ = 1.6 V to 3.4 V, Tr = Tf = 1 μs,<br>$R_{LOAD}$ = 5 Ω |     |     | 20   |     |

|                       | VOUT transient response fall time             | TILOAD - V 12                                                                                   |     |     | 50   | μs  |

|                       |                                               | $V_{BATT} = 3 \text{ V}, V_{OUT} = 1.9 \text{ V},$<br>$I_{OUT} = 20 \text{ mA (PWM)}$           |     | 77% |      |     |

|                       |                                               | $V_{BATT} = 3 \text{ V}, V_{OUT} = 2.41 \text{ V},$<br>$I_{OUT} = 60 \text{ mA (PWM)}$          |     | 91% |      |     |

|                       |                                               | $V_{BATT} = 3 \text{ V}, V_{OUT} = 2.71 \text{ V},$<br>$I_{OUT} = 200 \text{ mA (PWM)}$         |     | 94% |      | μs  |

|                       | Efficiency                                    | $V_{BATT} = 3 \text{ V}, V_{OUT} = 3.31 \text{ V},$<br>$I_{OUT} = 480 \text{ mA (PWM)}$         |     | 93% |      |     |

|                       |                                               | $V_{BATT}$ = 3.8 V, $V_{OUT}$ = 0.60 V,<br>$I_{OUT}$ = 10 mA (PFM)                              |     | 57% |      |     |

| η                     |                                               | $V_{BATT} = 3.8 \text{ V}, V_{OUT} = 1 \text{ V},$<br>$I_{OUT} = 20 \text{ mA (PFM)}$           |     | 75% |      |     |

|                       |                                               | $V_{BATT}$ = 3.8 V, $V_{OUT}$ = 1.9 V,<br>$I_{OUT}$ = 20 mA (PWM)                               |     | 68% |      |     |

|                       |                                               | $V_{BATT}$ = 3.8 V, $V_{OUT}$ = 2.41 V,<br>$I_{OUT}$ = 70 mA (PWM)                              |     | 88% |      |     |

|                       |                                               | $V_{BATT}$ = 3.8 V, $V_{OUT}$ = 2.71 V,<br>$I_{OUT}$ = 200 mA (PWM)                             |     | 94% |      |     |

|                       |                                               | $V_{BATT}$ = 3.8 V, $V_{OUT}$ = 3.31 V,<br>$I_{OUT}$ = 480 mA (PWM)                             |     | 94% |      |     |

|                       |                                               | $V_{BATT} = 3 \text{ V}, V_{OUT} = 3.6 \text{ V},$<br>$I_{OUT} = 200 \text{ mA (PWM)}$          |     | 94% |      |     |

| T <sub>S</sub>        | Data setup time                               | T <sub>A</sub> = 25°C                                                                           | 1   |     |      |     |

| T <sub>H</sub>        | Data hold time                                |                                                                                                 | 5   |     |      | ns  |

| T <sub>SDATAOTR</sub> | SDATA output transition time (rise/fall time) | VIO range = 1.65 V to 1.95 V, T <sub>A</sub> = 25°C                                             | 2.1 |     | 6.5  | 113 |

### 6.7 System Characteristics Recommended Capacitance Specifications

| BUS   | MIN (μF) | TYP (μF) | MAX (μF) |

|-------|----------|----------|----------|

| VBATT | 4.7      | 10       |          |

| VOUT  | 3.0      |          | 13       |

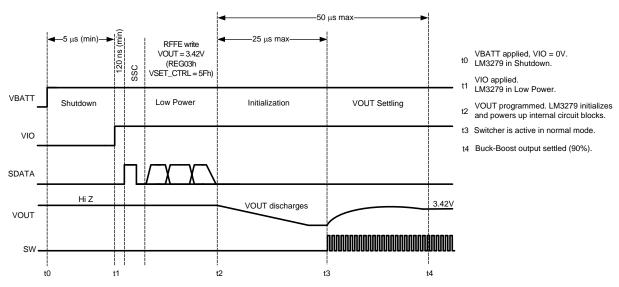

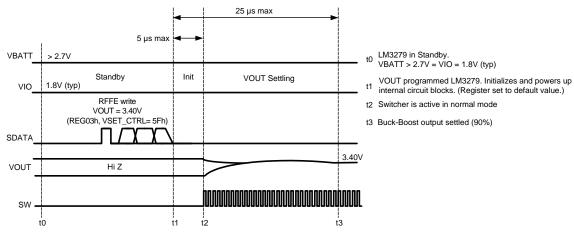

Figure 1. Cold Power-Up

Figure 2. Standby To Active

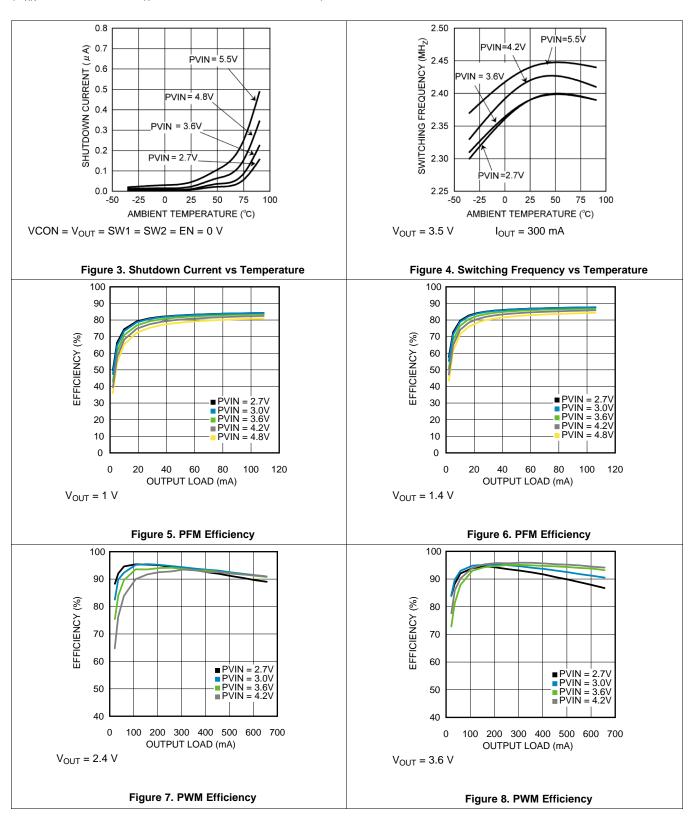

### 6.8 Typical Performance Characteristics

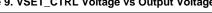

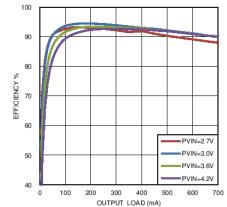

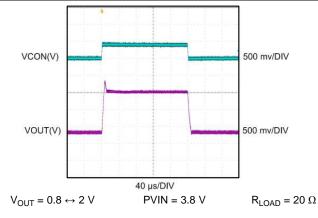

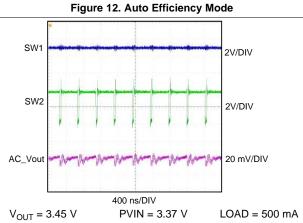

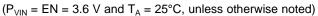

$(P_{VIN} = EN = 3.6 \text{ V} \text{ and } T_A = 25^{\circ}\text{C}, \text{ unless otherwise noted})$

## **ISTRUMENTS**

### **Typical Performance Characteristics (continued)**

$(P_{VIN} = EN = 3.6 \text{ V} \text{ and } T_A = 25^{\circ}\text{C}, \text{ unless otherwise noted})$

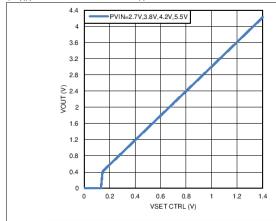

No Load, RFFE Digital Control Mode

$V_{OUT} = 1.5 V$

Figure 9. VSET\_CTRL Voltage vs Output Voltage

$V_{OUT} = 2.5 V$

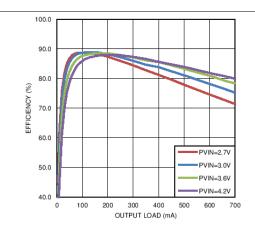

100 90 80 EFFICIENCY 70 60 50 PVIN=3.6V

OUTPUT LOAD (mA)

600

Figure 10. Auto Efficiency Mode

$V_{OUT} = 3.4 \text{ V}$

100 200 300 400

Figure 11. Auto Efficiency Mode

Figure 13. V<sub>OUT</sub> Transient

Figure 14. Boost Mode Operation

### **Typical Performance Characteristics (continued)**

### 7 Detailed Description

### 7.1 Overview

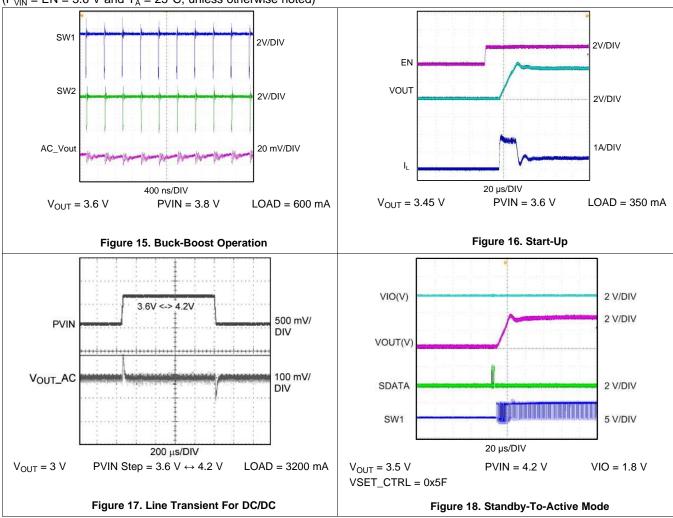

The LM3279 buck-boost converter provides high-efficiency, low-noise power for RF power amplifiers (PAs) in mobile phones, portable communicators and similar battery powered RF devices. It is designed to allow the RF PA to operate at maximum efficiency for a wide range of power levels from a single Li-lon battery cell. The capability of LM3279 to provide an output voltage lower than as well as higher than the input battery voltage enables the PA to operate with high linearity for a wide range of battery voltages, thereby extending the usable voltage range of the battery. The converter feedback loop is internally compensated for both buck and boost operation, and the architecture is such that it provides seamless transition between buck and boost mode of operation. The LM3279 operates in energy-saving Pulse Frequency Modulation (PFM) mode for increased efficiencies and current savings during low-power RF transmission modes. The output voltage is dynamically programmable from 0.4 V to 4.2 V by either programming the VSET value in register 00h, or adjusting the voltage on the control pin VCON. The fast output voltage transient response of LM3279 makes it suitable for adaptively adjusting the PA supply voltage depending on its transmitting power which improves systems efficiency and prolongs battery life

Additional features include current-overload protection, output overvoltage clamp, and thermal-overload shutdown.

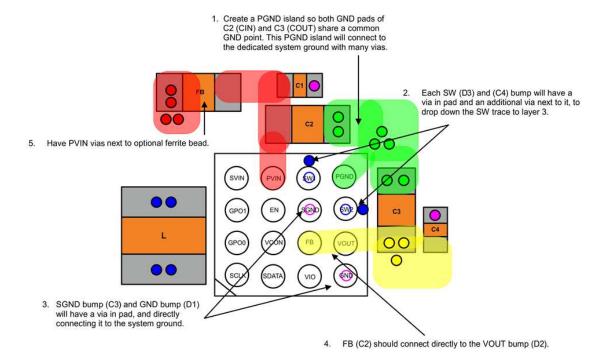

The LM3279 is constructed using a chip-scale 16-bump DSBGA package that offers the smallest possible size for space-critical applications such as cell phones where board area is an important design consideration. Use of a high switching frequency (2.4 MHz, typ.) reduces the size of external components. As shown in Figure 24 and Figure 27, only three external power components are required for circuit operation. Use of a DSBGA package requires special design considerations for implementation. (See *DSBGA Package Assembly And Use* in the *Layout* section.) Its fine bump-pitch requires careful board design and precision assembly equipment. Use of this package is best suited for opaque-case applications where its edges are not subjected to high-intensity ambient red or infrared light. In addition, the system controller should set VIO = LOW (or EN if system implementation with analog VCON) during power-up and other low supply-voltage conditions.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Dynamically Adjustable Output Voltage

The LM3279 features a dynamically adjustable output voltage to eliminate the need for external feedback resistors. The output can be set from 0.4 V to 4.2 V by either programming the VSET value in register 00h, or by changing the voltage on the analog VCON pin when implementing analog control. This feature is useful in cell-phone RF PA applications where peak power is needed only when the handset is far away from the base station or when data is being transmitted. In other instances, the transmitting power can be reduced. Hence, the supply voltage to the PA can be reduced, promoting longer battery life. In order to adaptively adjust the supply voltage to the PA in real time in a cell-phone application, the output-voltage transition should be fast enough in order to meet the RF transmit signal specifications. The LM3279 offers ultra-fast output-voltage transition without drawing very large currents from the battery supply. For a current limit of 1700 mA (typ.), the output voltage can transition from 0.6 V to 3.4 V in less than 20  $\mu$ s with a load resistance of 5  $\Omega$  at  $V_{BATT}$  = 3.8 V.

### **Feature Description (continued)**

### 7.3.2 Seamless Mode Transition

In a typical non-inverting buck-boost converter, all four power switches M1 through M4 are switched every cycle. This operation increases MOSFET drive losses and lowers the converter efficiency. The LM3279 switches only two power switches every cycle to improve converter efficiency. Hence, it operates either as buck converter or a boost converter depending upon the input and output voltage conditions. This creates a boundary between the buck and boost mode of operation. When the input battery voltage is close to the set output voltage, the converter automatically switches to a four-switch operation seamlessly such that the output voltage does not see any perturbations at the mode boundary. The excellent mode-transition capability of the LM3279 enables lownoise output with highest efficiency. Internal feedback loop compensation ensures stable operation in buck, boost, and buck-boost modes, as well as during mode transitions.

### 7.3.3 Setting The Output Voltage

The output voltage can be set by two methods: via Analog Control or Digital Control.

In the Analog Control method, the VCON pin is an external analog control input pin. It can be enabled (EN = HIGH) or disabled (EN = LOW). An analog voltage is provided by an external MCU (either a D/A or averaged PWM output) to the VCON pin. The range of this signal is 0.167V (min.) to 1.4V (max. typ.) to provide the full range of the possible output voltage. This signal is internally amplified by a gain of 3 to go from 0.5V to 4.2V output.

For the Digital Control method, the output voltage is set by writing a 7-bit value to reg 00h, bits 0 through 6. Programming a value 00h will force the LM3279 into low-power mode where the entire device except the RFFE interface is turned off. Programming register 00h with the value 02h will place the LM3279 into Standby mode where the SW pin is tri-stated. Values programmed above 0Bh will determine the output voltage from 0.4 V to 4.212 V in 36 mV (typ.) increments.

The output voltage quickly adjusts to the new output voltage value within 20 microseconds both in the positive and negative directions. To accomplish this, the LM3279 buck-boost output can both source and sink current. In the positive direction the buck may assume a 100-percent duty cycle or enter boost mode at up to 50% duty cycle to provide the required current. In the negative direction, the synchronous rectifier (NFET) will remain on to sink current from the output capacitor.

### 7.3.4 General Purpose Outputs

The LM3279 provides two general-purpose outputs to control the RF front-end circuitry. These outputs have a maximum output voltage of 1.8 V. These bits are set by writing to register 02h bits 6 (GPO1) and bit 7 (GPO0).

### 7.3.5 VCON<sub>ON</sub>

When EN = HIGH, the output is disabled when VCON is below 125 mV (typ.). It is enabled when VCON is above 150 mV (typ.). The threshold has 25 mV (typ.) of hysteresis.

### 7.3.6 R<sub>DSON</sub> Management

The LM3279 has a unique  $R_{DSON}$ -management function to improve efficiency in both the low-output voltage and high-output voltage conditions. For VSET < 2.1 V (typ.) or VCON < 0.7 V (typ.), the device uses only a small part of the PMOSFET M1 to minimize drive loss of the PMOSFET. When VSET > 2.175 V or VCON > 0.725 V, a large PMOSFET is also used along with the small PMOSFET. The threshold has a 25 mV of hysteresis. For RF PAs, the current consumption typically increases with its supply voltage; thus, higher supply voltage for a PA also means higher power delivered to it. Hence, adding a large PMOSFET for VSET > 2.175 V or VCON > 0.725 V reduces the conduction losses, thereby achieving high efficiency. The LM3279 can also provide output voltages higher than the battery voltage. This boost mode of operation is typically used when the battery voltage has discharged to a low voltage that is not sufficient to provide the required linearity in the PA. A special  $R_{DSON}$ -management scheme is designed for operation well into boost mode so that an auxiliary PMOSFET switch is also turned on along with Large and Small PMOSFET switches, effectively reducing the  $R_{DSON}$  of M1 to a very low value in order to keep the efficiency maximum. Since M1 conducts all the time in boost mode, reducing the  $R_{DSON}$  of M1 achieves significant improvement in efficiency.

### Feature Description (continued)

### 7.3.7 Supply Current Limit

A current limit feature allows the LM3279 to protect itself and external components during overload conditions. In Pulse Width Modulation (PWM) mode, a 1700 mA (typ.) cycle-by-cycle current limit is normally used when  $V_{OUT}$  is above 2.1 V (typ.) and an 850 mA (typ.) limit is used when  $V_{OUT}$  is below 2.1 V (typ.). If an excessive load pulls the output voltage down to approximately 0.30 V, the device switches to a timed current-limit mode, and the current limit in this mode is 850 mA (typ.), independent of the set  $V_{OUT}$  voltage. In timed current limit mode, the internal PMOSFET switch M1 is turned off after the current limit is hit, and the beginning of the next cycle is inhibited for 3.5  $\mu$ s to force the instantaneous inductor current to ramp down to a safe value.

### 7.3.8 Reverse Current Limit

Since the LM3279 features a dynamically adjustable output voltage, the inductor current can build up to high values in either direction depending on the output voltage transient. For a low-to-high output voltage transient, the inductor current flows from SW1 pin to SW2 pin; this current is limited by the current-limit feature monitoring of MOSFET M1. For a high-to-low output voltage transient, the inductor current flows from SW2 pin to SW1 pin and this current needs to be limited to protect the LM3279 as well as the external components. A reverse current limit feature allows monitoring the reverse inductor current that also flows through MOSFET M2. A -1.2 A (typ.) cycle-by-cycle current limit is used to limit the reverse current. When the reverse current hits the reverse current limit during a PWM cycle, MOSFET M2 is turned off, and MOSFET M1 and M4 are turned on, for the rest of that switching cycle. This allows the inductor to build current in the opposite direction thereby limiting the reverse current. It should be noted that the power MOSFET switches M3 and M4 do not have their own current limiting circuits and are dependent on the current-limit operation implemented for power MOSFETs M1 and M2 to protect them. The implication of this is that any external forcing of voltage/current on SW2 pin or misuse of SW2 pin may be detrimental to the part and may damage the internal circuits.

### 7.3.9 VCON Overvoltage Clamp

The LM3279 features an internal clamp on the analog VCON pin voltage to limit the output voltage to a maximum safe value. The VCON voltage is internally switched to a reference voltage of approximately 1.6 V when the VCON pin voltage exceeds 1.6 V. This limits the output voltage to approximately 4.8 V and protects the part from overvoltage stress. When implementing digital control, the VSET inherently limits the output voltage to the required range.

### 7.3.10 Thermal Overload Protection

The LM3279 has a thermal overload protection function that operates to protect itself from short-term misuse and overload conditions. When the junction temperature exceeds around 150°C, the device inhibits operation. All power MOSFET switches are turned off in PWM mode. When the temperature drops below 125°C, normal operation resumes. Prolonged operation in thermal overload conditions may damage the device and is considered bad practice.

### 7.4 Device Functional Modes

### 7.4.1 Enable And Shutdown Mode

Setting the VIO and EN digital pins low (< 0.6 V) places the LM3279 in shutdown mode (0.01  $\mu$ A typ. for VIO or EN = 0 V). During shutdown, the output of LM3279 is in tri-state mode. Setting VIO or EN high (>1.2 V) enables normal operation. VIO and EN should be set low to turn off the LM3279 during power-up and undervoltage conditions when the power supply ( $V_{BATT}$ ) is less than the 2.7V minimum operating voltage. When VIO is HIGH, EN must be GND, and when EN = HIGH, VIO must be GND. When EN goes logic low  $\rightarrow$ logic high, for the first 20  $\mu$ s the dump-switch M6 turns ON to discharge the output capacitor. The duration of M6 being ON is about 20  $\mu$ s. This enables discharge of (an initially charged) output capacitor to voltages much less than 4.2 V. The switcher feedback-control loops continues the discharge process (if need be) so that the charge in the output capacitor is regulated to the correct output voltage value. When VIO is applied, the default values are loaded into the control registers.

### **Device Functional Modes (continued)**

### 7.4.2 Low-Power Mode

The low-power mode is a very low current state where the VIO voltage remains at 1.8 V, and the RFFE interface continues to operate. Here, the current drawn from the  $V_{BATT}$  is < 0.1  $\mu$ A (typ.). This mode can be entered by writing a value of 00h into register 00h (VSET Control Register) or by programming PWR\_MODE[1:0] to 10b (bits 6 and 7 of register 1Ch PM-TRIG Register).

During low power mode, the LM3279 maintains the previous programmable register settings upon resuming normal operation.

### 7.4.3 Standby Mode

The standby mode is a mode where the switching is stopped and the power control circuit is off, but the control and the RFFE interface continue to operate. The VIO voltage remains at 1.8 V. Here, the current drawn from the  $V_{BATT}$  is 1 mA (typ.). This mode can be entered by writing a value of 02h into register 00h (VSET Control Register) when the PWR\_MODE bits are set to normal operation 00b (bits 6 and 7 of register 1Ch PM-TRIG Register).

In this mode the SW pins are tri-stated.

### 7.4.4 PFM Mode

The LM3279 enters PFM mode and operates with reduced switching frequency and supply current to maintain very high efficiencies for light-load operation. The conditions for entering and exiting the PFM and PWM mode are provided in Table 1. In PFM mode, the LM3279 will support up to 100 mA max. In Analog Control Mode the PWM/PFM mode transition has a 60 mV  $V_{OUT}$  hysteresis.

For STATE\_CTRL[1:0] = 10, the PWM/PFM load current threshold has a 30 mA hysteresis.

During output voltage transients, the LM3279 will automatically shift temporarily to PWM mode before settling to the final output voltage in either PFM or PWM mode depending on the conditions in Table 1.

| STATE_CTRL<br>[1:0] or GPO1,<br>GPO0 | ANALOG CONTROL (EN = HIGH, EXTERNAL DAC CONNECTED TO VCON)                              | DIGITAL CONTROL (VIO = HIGH, V <sub>SET_CTRL</sub> IN REGISTER 00h PROGRAMMED VIA RFFE)                 |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| 00                                   | Ford                                                                                    | rced PFM                                                                                                |  |  |  |  |

| 01                                   | PWM if VCON > 0.5V; PFM if VCON < 0.5V                                                  | PWM if V <sub>SET_CTRL</sub> ≥ 29h; PFM if V <sub>SET_CTRL</sub> < 29h                                  |  |  |  |  |

| 10                                   | PWM if VCON > 0.7V OR load >130 mA;<br>PFM if VCON < 0.7V AND I <sub>OUT</sub> < 100 mA | PWM if $V_{SET\_CTRL} \ge 39h$ OR load > 130 mA;<br>PFM if $V_{SET\_CTRL} < 39h$ AND $I_{OUT} < 100$ mA |  |  |  |  |

| 11                                   | Forced PWM                                                                              |                                                                                                         |  |  |  |  |

**Table 1. PWM-PFM Operation Truth Table**

### 7.5 Programming

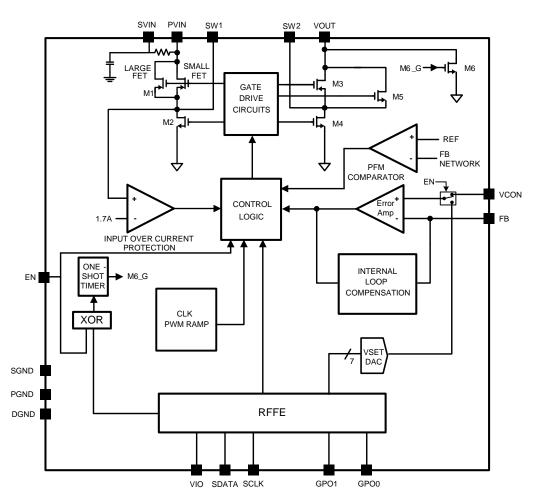

### 7.5.1 Digital Control Serial Bus Interface

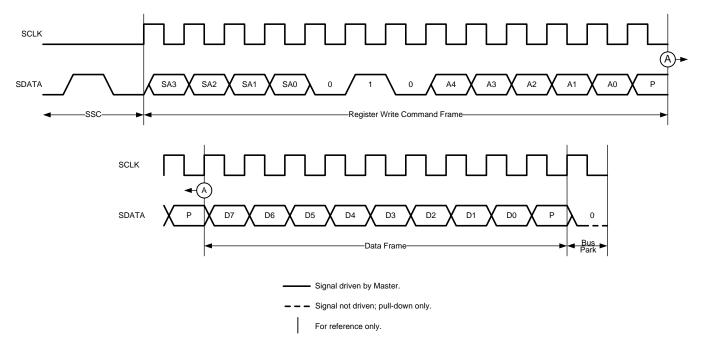

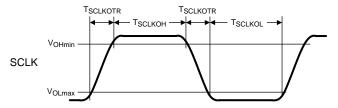

The Digital Control Serial Bus Interface provides MIPI RF Front-End Control Interface-compatible access to the programmable functions and registers on the device. When VIO voltage supply is applied to the Bus, it enables the Slave interface and resets the user-defined Slave registers to the default settings. The LM3279 uses a three-pin digital interface; two for bidirectional communications between the ICs connected to the Bus, along with an interface voltage reference VIO that also acts as asynchronous enable and reset. When VIO voltage supply is applied to the Bus, it enables the Slave interface and resets the user-defined Slave registers to the default settings. The device can be set to power-down mode via the asynchronous VIO signal or by setting the appropriate register via Serial Bus Interface. The two communication lines are serial data (SDATA) and clock (SCLK). SCLK and SDATA must be held low until VIO is present. The LM3279 connects as a slave on a single-master Serial Bus Interface.

The SDATA signal is bidirectional, driven by the Master or a Slave. Data is written on the rising edge (transition from logical level zero to logical level one) of the SCLK signal by both Master and Slaves. Master and Slave both read the data on the falling edge (transition from logical level one to logical level zero) of the SCLK signal. A logic-low level applied to VIO signal powers off the digital interface.

### **Programming (continued)**

Programming the VSET\_CTRL register dynamically adjusts the Buck-Boost output voltage. The feedback voltage changes from  $V_{FB,MIN}$  to  $V_{FB,MAX}$  depending upon the register value. The digital interface is also used to program the LM3279 for PWM or into PWM and PFM mode.

### 7.5.2 Supported Command Sequences

Figure 19. Register 0 Write

Figure 20. Register Write

### **Programming (continued)**

Figure 21. Register Read

### 7.5.3 Device Enumeration

The interface component recognizes broadcast Slave Address (SID) of 0000b and is configured, via internal interface signals, with a Unique SID address (USID) and a Group SID address (GSID). The USID is set to 0101b and GSID set to 0000b. The register-set component will typically set the USID to a fixed value; however, it is also possible to construct a register-set component that allows the USID to be programmed via the RFFE bus.

### 7.5.4 I/O

This RFFE interface supports a 1.8-V VIO supply level. A power-on reset circuit will be included that resets the RFFE interface and register-set components when VIO is removed.

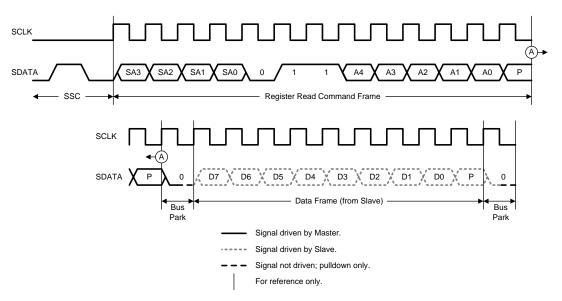

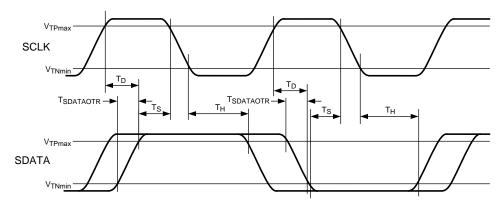

### 7.5.5 Control Interface Timing Parameters

Figure 22. Clock Timing

### **Programming (continued)**

Figure 23. Setup And Hold Timing

### 7.6 Registers

### 7.6.1 Programmable Registers

| ADDRESS | REGISTER CONTENTS |                 |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|---------|-------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 00h     |                   |                 | VSET_CTRL                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|         | Bits              | Name            | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         | 7                 | Reserved        | Reserved bit. Default = 0.                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|         | 6:0               | VSET_CTRL[6:0]  | DC-DC voltage control bits. $V_{SET\_CTRL} = 00h$ (default)puts the part into a low power mode. $V_{SET\_CTRL} = \bar{0}2h$ puts the part in a standby mode. $V_{SET\_CTRL} = 0Bh$ corresponds to 0.4 V and 75h corresponds to 4.212 V. |  |  |  |  |  |  |  |

| 01h     | STATE_CTRL        |                 |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|         | Bits              | Name            | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         | 7:6               | STATE_CTRL[1:0] | PWM and PFM state control bits.<br>00b = Force PFM<br>$01b = PFM if V_{OUT} < 1.5 $ (default)<br>$10b = PFM if V_{OUT} < 2.1 $ and $I_{OUT} < 100 $ mA<br>11b = Force PWM                                                               |  |  |  |  |  |  |  |

|         | 5:0 Reserved      |                 |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 02h     | GPO_CTRL          |                 |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|         | Bits              | Name            | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         | 7                 | GPO0            | GPO0 control bit.  0b = Output set to low level (default)  1b = Output set to high level                                                                                                                                                |  |  |  |  |  |  |  |

|         | 6                 | GPO1            | GPO1 control bit.  0b = Output set to low level (default)  1b = Output set to high level                                                                                                                                                |  |  |  |  |  |  |  |

| 03h-1Bh | RESERVED          |                 |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|         | Bits              | Name            | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         |                   |                 | Reserved registers for configuration, test, and trim.                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 1Ch     |                   |                 | PM_TRIG                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|         | Bits              | Name            | Description                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         | 7:6               | PWR_MODE[1:0]   | Power Mode Bits.  00b = Normal operation  01b = Default settings (default)  10b = Low power  11b = Reserved                                                                                                                             |  |  |  |  |  |  |  |

|         | 5:0               | TRIG_REG[5:0]   | Reserved for trigger bits.                                                                                                                                                                                                              |  |  |  |  |  |  |  |

### **Registers (continued)**

| ADDRESS | REGISTER CONTENTS |                      |                                                                                                                                                      |  |  |  |  |  |  |  |  |

|---------|-------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1Dh     | PRODUCT_ID        |                      |                                                                                                                                                      |  |  |  |  |  |  |  |  |

|         | Bits              | Name                 | Description                                                                                                                                          |  |  |  |  |  |  |  |  |

|         | 7:0               | PRODUCT_ID[7:0]      | Product identification bits. Set to A0h.                                                                                                             |  |  |  |  |  |  |  |  |

| 1Eh     |                   |                      | MANUFACTURER_ID                                                                                                                                      |  |  |  |  |  |  |  |  |

|         | Bits              | Name                 | Description                                                                                                                                          |  |  |  |  |  |  |  |  |

|         | 7:0               | MANUFACTURER_ID[7:0] | Manufacturer identification bits. 7:0 1Eh are LSB for TI.                                                                                            |  |  |  |  |  |  |  |  |

| 1Fh     |                   |                      | USID                                                                                                                                                 |  |  |  |  |  |  |  |  |

|         | Bits              | Name                 | Description                                                                                                                                          |  |  |  |  |  |  |  |  |

|         | 7:6               | SPARE[1:0]           | This is a read-only register that is reserved and yields a value of 00b at readback. Potentially used in future for extending manufacturer ID field. |  |  |  |  |  |  |  |  |

|         | 5:4               | MANUFACTURER_ID[5:4] | Manufacturer identification bits.<br>5:4 01h are MSB for TI.                                                                                         |  |  |  |  |  |  |  |  |

|         | 3:0               | USID[3:0]            | Unique slave identifier. Default 0101b.                                                                                                              |  |  |  |  |  |  |  |  |

### 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

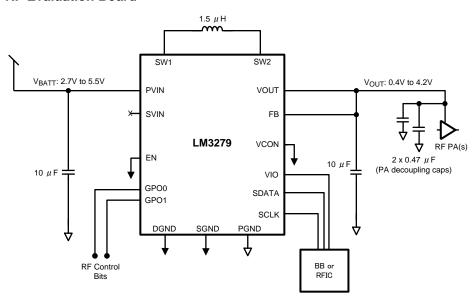

### 8.1 Application Information

The LM3279 is a high-efficiency buck boost DC-DC converter optimized to power 3G/4G power amplifier in cell phones, portable communication devices, or other battery-powered RF devices. The device is designed to operate from an input supply voltage between 2.7 V and 5.5 V with a maximum load current of 1 A. It operates in PWM mode for medium-to-heavy load conditions and in PFM mode for light load conditions to optimize for best efficiency, transient performance, and output voltage ripple at varying load conditions. In PWM mode the LM3279 converter operates with nominal switching frequency of 2.4 MHz, thus enabling use of smaller size capacitors and inductor. The converter operates in PFM mode at lighter load conditions to maintain high efficiency. The LM3279 switches between PFM and PWM based on load current and /or the output voltage, and Figure 24 shows one of many application configurations for LM3279. A battery-connected system provides input supply to LM3279 which in turn very efficiently converts this input to a variable output with superior transient response and output noise, thereby saving the 3G/4G power amplifiers from having to operate from a higher supply voltage, such as a direct connection to a battery. This results in significant power dissipation savings and consequently cooler operation and also lower current consumption for the power amplifier without sacrificing its RF performance. In applications where low voltage battery operation is a significant feature; the buck-boost can seamlessly transition to boost and power the 3G/4G PA for high peak-to-average ratio signals as well.

To control the output voltage there are two methods in which the LM3279 can be used: Analog Control where an analog control voltage (VCON) which is equal to VOUT/3 need to feed into the LM3279 from an external DAC. In the digital mode RFFE signaling is used to control the register address 0x00 to set the output voltage, and the LM3279 acts as a slave device on the RFFE bus.

### 8.2 Typical Application

### 8.2.1 Typical Application Circuit: Digital Control

Figure 24. LM3279 Digital Control

### **Typical Application (continued)**

### 8.2.1.1 Design Requirements

The LM3279 buck-boost converter has internal loop compensation. Therefore, the external LC filter has to be selected according to the internal compensation. Nevertheless, it's important to consider, that the effective inductance, due to inductor tolerance and current derating can vary between 20% and –30%. The same for the capacitance of the output filter: the effective capacitance can vary between 20% and –50% of the specified datasheet value, due to capacitor tolerance and bias voltage. For this reason Table 3 and Table 4 show the typical inductor and capacitor used with the LM3279 device.

### 8.2.1.2 Detailed Design Procedure

### 8.2.1.2.1 Output Current Capability

The typical LM3279 load capability vs. input voltage is as shown in Table 2. There are 3 distinct regions of current capability. In the low output-voltage region,  $V_{OUT} < 2.1 \text{ V}$  (also known as the  $R_{DSON}$ -managed region), the output-current capability is determined by the current capability of the  $R_{DSON}$ -managed MOSFET, typically 600 mA. When the output voltage is greater than 2.1 V, and in buck mode, the current capability increases to 1400 mA as determined by the overcurrent limit setting and the magnitude of ripple current. While in boost-mode operation, the output-current capability is determined by the output-input voltage ratio. It is expected for the typical RF PA to have an approximate resistive load characteristic. Refer to Table 2 for output current capability.

Table 2. Output Voltage vs Maximum Output Current Derating

| V <sub>OUT</sub> (V) | V <sub>IN</sub> (V) | MAXIMUM I <sub>OUT</sub> CAPABILITY (mA) |  |  |  |  |

|----------------------|---------------------|------------------------------------------|--|--|--|--|

| 4.2                  | ≤ 3                 | 450                                      |  |  |  |  |

| 4.2                  | > 3                 | 650                                      |  |  |  |  |

|                      | ≥ 2.5               | 500                                      |  |  |  |  |

| 3.8                  | ≥ 2.7               | 750                                      |  |  |  |  |

|                      | ≥ 3                 | 950                                      |  |  |  |  |

|                      | ≥ 2.5               | 750                                      |  |  |  |  |

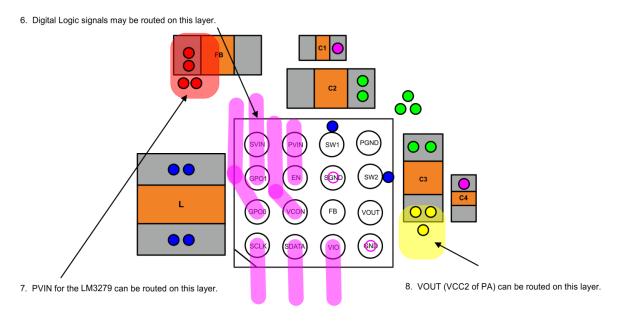

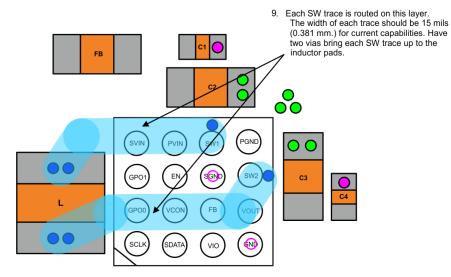

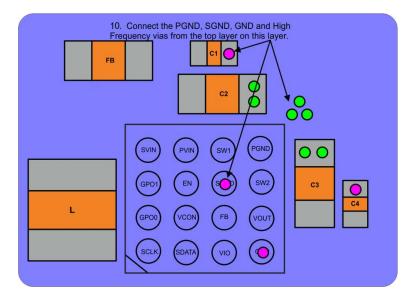

| 3.4                  | ≥ 2.7               | 950                                      |  |  |  |  |