LMK00334

ZHCSCZ5E - DECEMBER 2013 - REVISED JANUARY 2022

# LMK00334 四路输出 PCle 第1代至第5代时钟缓冲器和电平转换器

# 1 特性

- 3:1 输入多路复用器

- 两个通用输入运行频率高达 400MHz, 且接受 LVPECL、LVDS、CML、SSTL、HSTL、HCSL 或单端时钟

- 单个晶体输入可接受 10MHz 至 40MHz 的晶体 或单端时钟

- 分为两组,每组具有两路差分输出

- HCSL 或 Hi-Z (可选)

- 100MHz 时 PCIe 第5代的附加 RMS 相位抖 动:

- 15fs RMS ( 典型值 )

- 高 PSRR: 156.25MHz 时为 -72 dBc

- 通过同步使能输入提供 LVCMOS 输出 ٠

- 由引脚控制的配置 ٠

- V<sub>CC</sub>内核电源:3.3V±5%

- 三个独立的 V<sub>CCO</sub> 输出电源: 3.3V、2.5V ± 5%

- 工业温度范围:-40°C 至 +105°C

- 32 引脚 WQFN (5 mm × 5 mm)

## 2 应用

- 数据中心交换机 •

- 核心路由器

- 服务器、计算、PCIe Gen 3.0 至 5.0

- 远程无线电单元和基带单元

# 3 说明

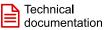

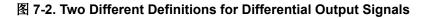

LMK00334 器件是一款 4 路输出 HCSL 扇出缓冲器, 旨在用于高频、低抖动时钟、数据分配和电平转换。它 能够为 ADC、DAC、多千兆以太网、XAUI、光纤通 道、SATA/SAS、SONET/SDH、CPRI 和高频背板分 配参考时钟。

可从两个通用输入或一个晶振输入中选择输入时钟。所 选择的输入时钟被分配到由两个 HCSL 输出和一个 LVCMOS 输出组成的两个组。LVCMOS 输出具有同步 使能输入,在使能或禁用后可实现无短脉冲运行。 LMK00334 由一个 3.3V 内核电源和三个独立的 3.3V 或 2.5V 输出电源供电运行。

LMK00334 具有高性能、多用途和高功效特性,因此 堪称替代固定输出缓冲器器件的理想选择,同时还能增 加系统中的时序余裕。

|      |      | * * |      | 141  |

|------|------|-----|------|------|

| 器    | Ø÷.  | 信言  | Ħ    | (11) |

| fin' | FT ' | 17  | APA- | · ·  |

| 器件型号     | 封装        | 封装尺寸(标称值)       |  |  |  |  |

|----------|-----------|-----------------|--|--|--|--|

| LMK00334 | WQFN (32) | 5.00mm × 5.00mm |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

LMK00334 功能框图

# **Table of Contents**

| 1 | 特性                                               | 1              |

|---|--------------------------------------------------|----------------|

| 2 | 应用                                               |                |

| 3 | 说明                                               | 1              |

|   | Revision History                                 |                |

|   | Pin Configuration and Functions                  |                |

| 6 | Specifications                                   | 4              |

|   | 6.1 Absolute Maximum Ratings                     | 4              |

|   | 6.2 ESD Ratings                                  | 4              |

|   | 6.3 Recommended Operating Conditions             |                |

|   | 6.4 Thermal Information                          |                |

|   | 6.5 Electrical Characteristics                   | 5              |

|   | 6.6 Timing Requirements, Propagation Delay, and  |                |

|   | Output Skew                                      | <mark>8</mark> |

|   | 6.7 Typical Characteristics                      |                |

| 7 | Parameter Measurement Information                | 12             |

|   | 7.1 Differential Voltage Measurement Terminology |                |

| 8 | Detailed Description                             |                |

|   | 8.1 Overview                                     |                |

|   | 8.2 Functional Block Diagram                     |                |

|   | 8.3 Feature Description                          |                |

|   | 8.4 Device Functional Modes                      | 15             |

| 9 Application and Implementation               | 16 |

|------------------------------------------------|----|

| 9.1 Application Information                    |    |

| 9.2 Typical Application                        |    |

| 10 Power Supply Recommendations                |    |

| 10.1 Current Consumption and Power Dissipation |    |

| Calculations                                   | 21 |

| 10.2 Power Supply Bypassing                    |    |

| 11 Layout                                      |    |

| 11.1 Layout Guidelines                         |    |

| 11.2 Layout Example                            |    |

| 11.3 Thermal Management                        |    |

| 12 Device and Documentation Support            |    |

| 12.1 Documentation Support                     |    |

| 12.2 接收文档更新通知                                  |    |

| 12.3 支持资源                                      |    |

| 12.4 Trademarks                                |    |

| 12.5 Electrostatic Discharge Caution           |    |

| 12.6 术语表                                       |    |

| 13 Mechanical, Packaging, and Orderable        |    |

| Information                                    | 26 |

|                                                |    |

# **4 Revision History**

| C | hanges from Revision D (July 2021) to Revision E (January 2022)                              | Page      |

|---|----------------------------------------------------------------------------------------------|-----------|

| • | 更改了数据表标题                                                                                     | 1         |

| • | 添加了指向 <i>应用</i> 部分的链接                                                                        |           |

| • | 向 <i>说明</i> 部分添加了文本                                                                          |           |

| • | Added example board layout to Packaging Information section                                  | 26        |

| С | hanges from Revision C (July 2017) to Revision D (July 2021)                                 | Page      |

| • | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                      |           |

| • | 在数据表中添加了 PCIe 第 5.0 代                                                                        |           |

| • | Corrected PN in 图 9-4 and 图 9-5 to LMK00334                                                  |           |

| С | hanges from Revision B (May 2017) to Revision C (July 2017)                                  | Page      |

| • | Added PCIe 4.0 compliance data                                                               |           |

| C | hanges from Revision A (October 2014) to Revision B (May 2017)                               | Page      |

| • | 已将整个数据表中的 CLKout_EN 引脚更改为 CLKout_EN                                                          |           |

| • | Add pins 28 and 32 to the <i>Pin Functions</i> table                                         | 3         |

| • | Moved the storage temperature to the Absolute Maximum Ratings table                          | 4         |

| • | Added test conditions to the output supply voltage parameter in the Recommended Operating Co | onditions |

|   | table                                                                                        | 5         |

| С | hanges from Revision * (December 2013) to Revision A (October 2014)                          | Page      |

| • | 添加、更新或重命名了以下各个部分:器件信息表、应用和实施;电源建议;布局;器件和文档支<br>封装和可订购信息                                      |           |

| • | Changed from 1 MHz to 12 kHz in <i>Electrical Characteristics</i>                            | 5         |

| • | Deleted "The additive jitter The additive RMS jitter was approximated "                      |           |

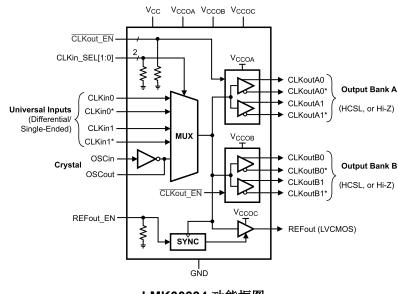

## **5** Pin Configuration and Functions

#### 图 5-1. RTV Package 32-Pin WQFN Top View

#### 表 5-1. Pin Functions<sup>(3)</sup>

| PIN        |             | I/O | DESCRIPTION                                                                                                                                                                |  |  |  |

|------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.         | 1/0 | DESCRIPTION                                                                                                                                                                |  |  |  |

| DAP        | DAP         | GND | Die Attach Pad. Connect to the PCB ground plane for heat dissipation.                                                                                                      |  |  |  |

| CLKin_SEL0 | 13          | I   | Clock input selection pins <sup>(2)</sup>                                                                                                                                  |  |  |  |

| CLKin_SEL1 | 16          | I   | Clock input selection pins <sup>(2)</sup>                                                                                                                                  |  |  |  |

| CLKin0     | 14          | I   | Jniversal clock input 0 (differential/single-ended)                                                                                                                        |  |  |  |

| CLKin0*    | 15          | I   | Universal clock input 0 (differential/single-ended)                                                                                                                        |  |  |  |

| CLKin1     | 27          | I   | Universal clock input 1 (differential/single-ended)                                                                                                                        |  |  |  |

| CLKin1*    | 26          | I   | Universal clock input 1 (differential/single-ended)                                                                                                                        |  |  |  |

| CLKout_EN  | 9           | I   | Bank A and Bank B low active output buffer enable. <sup>(2)</sup>                                                                                                          |  |  |  |

| CLKoutA0   | 3           | 0   | Differential clock output A0.                                                                                                                                              |  |  |  |

| CLKoutA0*  | 4           | 0   | Differential clock output A0.                                                                                                                                              |  |  |  |

| CLKoutA1   | 6           | 0   | Differential clock output A1.                                                                                                                                              |  |  |  |

| CLKoutA1*  | 7           | 0   | Differential clock output A1.                                                                                                                                              |  |  |  |

| CLKoutB1   | 19          | 0   | Differential clock output B1.                                                                                                                                              |  |  |  |

| CLKoutB1*  | 18          | 0   | Differential clock output B1.                                                                                                                                              |  |  |  |

| CLKoutB0   | 22          | 0   | Differential clock output B0.                                                                                                                                              |  |  |  |

| CLKoutB0*  | 21          | 0   | Differential clock output B0.                                                                                                                                              |  |  |  |

| GND        | 1, 8 17, 24 | GND | Ground                                                                                                                                                                     |  |  |  |

| NC         | 25          | _   | Not connected internally. Pin may be floated, grounded, or otherwise tied to any potential within the Supply Voltage range stated in the <i>Absolute Maximum Ratings</i> . |  |  |  |

| OSCin      | 11          | I   | Input for crystal. Can also be driven by a XO, TCXO, or other external single-ended clock.                                                                                 |  |  |  |

| OSCout     | 12          | 0   | Output for crystal. Leave OSCout floating if OSCin is driven by a single-ended clock.                                                                                      |  |  |  |

| REFout     | 29          | 0   | LVCMOS reference output. Enable output by pulling REFout_EN pin high.                                                                                                      |  |  |  |

| REFout_EN  | 31          | I   | REFout enable input. Enable signal is internally synchronized to selected clock input. <sup>(2)</sup>                                                                      |  |  |  |

#### 表 5-1. Pin Functions<sup>(3)</sup> (continued)

| PIN               |            | I/O | DESCRIPTION                                                                                                                                                                                                                                                   |  |  |

|-------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME              | NO.        |     | DESCRIPTION                                                                                                                                                                                                                                                   |  |  |

| V <sub>CC</sub>   | 10, 28, 32 | PWR | Power supply for Core and Input Buffer blocks. The V <sub>CC</sub> supply operates from 3.3 V. Bypass with a 0.1- $\mu$ F, low-ESR capacitor placed very close to each V <sub>CC</sub> pin.                                                                   |  |  |

| V <sub>CCOA</sub> | 2, 5       | PWR | Power supply for Bank A Output buffers. V <sub>CCOA</sub> operates from 3.3 V or 2.5 V. The V <sub>CCOA</sub> pins are internally tied together. Bypass with a 0.1- $\mu$ F, low-ESR capacitor placed very close to each V <sub>CCO</sub> pin. <sup>(1)</sup> |  |  |

| V <sub>CCOB</sub> | 20, 23     | PWR | Power supply for Bank B Output buffers. V <sub>CCOB</sub> operates from 3.3 V or 2.5 V. The V <sub>CCOB</sub> pins are internally tied together. Bypass with a 0.1- $\mu$ F, low-ESR capacitor placed very close to each V <sub>CCO</sub> pin. <sup>(1)</sup> |  |  |

| V <sub>ccoc</sub> | 30         | PWR | Power supply for REFout buffer. V <sub>CCOC</sub> operates from 3.3 V or 2.5 V. Bypass with a 0.1- $\mu$ F, low-ESR capacitor placed very close to each V <sub>CCO</sub> pin. <sup>(1)</sup>                                                                  |  |  |

(1) The output supply voltages or pins (V<sub>CCOA</sub>, V<sub>CCOB</sub>, and V<sub>CCOC</sub>) will be called V<sub>CCO</sub> in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

(2) CMOS control input with internal pulldown resistor.

(3) Any unused output pins should be left floating with minimum copper length (see note in *Clock Outputs*), or properly terminated if connected to a transmission line, or disabled/Hi-Z if possible. See *Clock Outputs* for output configuration and *Termination and Use of Clock Drivers* for output interface and termination techniques.

# **6** Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1) (2)

|                   |                               | MIN   | MAX                     | UNIT |

|-------------------|-------------------------------|-------|-------------------------|------|

| $V_{CC}, V_{CCO}$ | Supply voltages               | - 0.3 | 3.6                     | V    |

| V <sub>IN</sub>   | Input voltage                 | - 0.3 | (V <sub>CC</sub> + 0.3) | V    |

| TL                | Lead temperature (solder 4 s) |       | 260                     | °C   |

| TJ                | Junction temperature          |       | 150                     | °C   |

| T <sub>stg</sub>  | Storage temperature           | - 65  | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

## 6.2 ESD Ratings

|                 |                             |                                                                                | VALUE | UNIT |

|-----------------|-----------------------------|--------------------------------------------------------------------------------|-------|------|

|                 |                             | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(E</sub> | (D) Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

|                 |                             | Machine model (MM)                                                             | ±150  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                          |             |      | MIN      | TYP  | MAX      | UNIT |

|------------------|------------------------------------------|-------------|------|----------|------|----------|------|

| T <sub>A</sub>   | T <sub>A</sub> Ambient temperature       |             |      | - 40     | 25   | 85       | °C   |

| TJ               | Junction temperature                     |             |      |          |      | 125      | °C   |

| V <sub>CC</sub>  | Core supply voltage                      |             | 3.15 | 3.3      | 3.45 | V        |      |

| V <sub>cco</sub> | Output supply voltage <sup>(1)</sup> (2) | 3.3-V range |      | 3.3 - 5% | 3.3  | 3.3 + 5% | V    |

|                  |                                          | 2.5-V range |      | 2.5 - 5% | 2.5  | 2.5 + 5% | v    |

(1) The output supply voltages or pins (V<sub>CCOA</sub>, V<sub>CCOB</sub>, and V<sub>CCOC</sub>) will be called V<sub>CCO</sub> in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

(2)  $V_{CCO}$  for any output bank should be less than or equal to  $V_{CC}$  ( $V_{CCO} \le V_{CC}$ ).

### 6.4 Thermal Information

|                        |                                              | LMK00334 <sup>(2)</sup> |      |

|------------------------|----------------------------------------------|-------------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTV (WQFN)              | UNIT |

|                        |                                              | 32 PINS                 |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 38.1                    | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 7.2                     | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 12                      | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.4                     | °C/W |

| ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 11.9                    | °C/W |

| R <sub>0 JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.5                     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Specification assumes 5 thermal vias connect the die attach pad (DAP) to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the package. TI recommends using the maximum number of vias in the board layout.

## **6.5 Electrical Characteristics**

Unless otherwise specified: V<sub>CC</sub> = 3.3 V ± 5%, V<sub>CCO</sub> = 3.3 V ± 5%, 2.5 V ± 5%,  $-40^{\circ}$ C  $\leq T_A \leq 85^{\circ}$ C, CLKin driven differentially, input slew rate  $\geq 3$  V/ns. Typical values represent the most likely parametric norms at V<sub>CC</sub> = 3.3 V, V<sub>CCO</sub> = 3.3 V, T<sub>A</sub> = 25°C, and at the Recommended Operation Conditions at the time of product characterization; because of this, typical values are not ensured. <sup>(1)</sup>

| PARAMETER  |                                                       | TEST CONDITIONS                                                                                      |                              | MIN | TYP  | MAX  | UNIT |  |  |  |

|------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------|-----|------|------|------|--|--|--|

| CURRENT CO | CURRENT CONSUMPTION (1)                               |                                                                                                      |                              |     |      |      |      |  |  |  |

| ICC CORE   | Core supply current, all outputs                      | CLKinX selected                                                                                      |                              |     | 8.5  | 10.5 | mA   |  |  |  |

| ICC_CORE   | disabled                                              | OSCin selected                                                                                       |                              |     | 10   | 13.5 | mA   |  |  |  |

| ICC_HCSL   | CC_HCSL                                               |                                                                                                      |                              | 50  | 58.5 | mA   |      |  |  |  |

| ICC_CMOS   |                                                       |                                                                                                      |                              |     | 3.5  | 5.5  | mA   |  |  |  |

| ICCO_HCSL  | Additive output supply current,<br>HCSL banks enabled | Includes output bank bias and load currents for both banks, $R_{\rm T}$ = 50 $\Omega$ on all outputs |                              |     | 65   | 81.5 | mA   |  |  |  |

| ICCO_CMOS  | Additive output supply current,                       | 200 MHz, C <sub>1</sub> = 5 pF                                                                       | V <sub>CCO</sub> = 3.3 V ±5% |     | 9    | 10   | mA   |  |  |  |

|            | LVCMOS output enabled                                 | 200 Mi iz, CL – 5 pr                                                                                 | V <sub>CCO</sub> = 2.5V ± 5% |     | 7    | 8    | mA   |  |  |  |

#### LMK00334 ZHCSCZ5E - DECEMBER 2013 - REVISED JANUARY 2022

Unless otherwise specified: V<sub>CC</sub> = 3.3 V ± 5%, V<sub>CCO</sub> = 3.3 V ± 5%, 2.5 V ± 5%, - 40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, CLKin driven differentially, input slew rate  $\geq$  3 V/ns. Typical values represent the most likely parametric norms at V<sub>CC</sub> = 3.3 V, V<sub>CCO</sub> = 3.3 V, T<sub>A</sub> = 25°C, and at the Recommended Operation Conditions at the time of product characterization; because of this, typical values are not ensured. <sup>(1)</sup>

|                      | PARAMETER                                       | TEST CC                                                                                      | MIN                            | TYP  | MAX                   | UNIT                  |        |  |  |  |  |

|----------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------|------|-----------------------|-----------------------|--------|--|--|--|--|

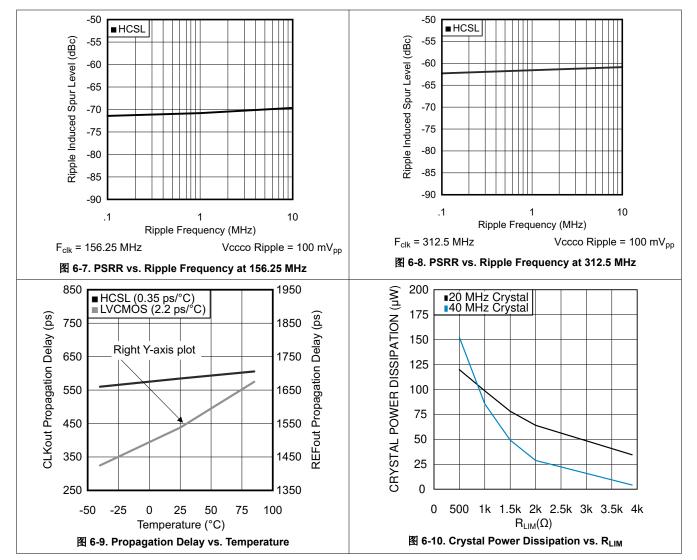

| POWER SUP            | PPLY RIPPLE REJECTION (PSRR)                    |                                                                                              | I                              |      |                       |                       |        |  |  |  |  |

|                      | Ripple-induced phase spur level <sup>(2)</sup>  | 156.25 MHz                                                                                   |                                |      | - 72                  |                       |        |  |  |  |  |

| PSRR <sub>HCSL</sub> | Differential HCSL Output                        | 312.5 MHz                                                                                    | 312.5 MHz                      |      | - 63                  |                       | dBc    |  |  |  |  |

| CMOS CON             | FROL INPUTS (CLKin_SELn, CLKout                 | <br>TYPEn, REFout_EN)                                                                        |                                |      | 1.                    |                       |        |  |  |  |  |

| V <sub>IH</sub>      | High-level input voltage                        |                                                                                              |                                | 1.6  |                       | V <sub>CC</sub>       | V      |  |  |  |  |

| V <sub>IL</sub>      | Low-level input voltage                         |                                                                                              |                                | GND  |                       | 0.4                   | V      |  |  |  |  |

| I <sub>IH</sub>      | High-level input current                        | V <sub>IH</sub> = V <sub>CC</sub> , internal pu                                              | Idown resistor                 |      |                       | 50                    | μA     |  |  |  |  |

| IIL                  | Low-level input current                         | V <sub>IL</sub> = 0 V, internal pull                                                         | down resistor                  | - 5  | 0.1                   |                       | μA     |  |  |  |  |

|                      | JTS (CLKin0/CLKin0*, CLKin1/CLKin               | 1*)                                                                                          |                                |      |                       |                       |        |  |  |  |  |

| f <sub>CLKin</sub>   | Input frequency range <sup>(8)</sup>            | Functional up to 400 M<br>Output frequency rang<br>per output type (refer<br>specifications) | ge and timing specified        | DC   |                       | 400                   | MHz    |  |  |  |  |

| V <sub>IHD</sub>     | Differential input high voltage                 |                                                                                              |                                |      |                       | Vcc                   | V      |  |  |  |  |

| V <sub>ILD</sub>     | Differential input low voltage                  | CLKin driven different                                                                       | GND                            |      |                       | V                     |        |  |  |  |  |

| V <sub>ID</sub>      | Differential input voltage swing <sup>(3)</sup> |                                                                                              | 0.15                           |      | 1.3                   | V                     |        |  |  |  |  |

|                      |                                                 | V <sub>ID</sub> = 150 mV                                                                     |                                | 0.25 |                       | V <sub>CC</sub> - 1.2 |        |  |  |  |  |

| V <sub>CMD</sub>     | Differential input CMD common-<br>mode voltage  | V <sub>ID</sub> = 350 mV                                                                     |                                | 0.25 |                       | V <sub>CC</sub> - 1.1 | V      |  |  |  |  |

|                      |                                                 | V <sub>ID</sub> = 800 mV                                                                     | 0.25                           |      | V <sub>CC</sub> - 0.9 |                       |        |  |  |  |  |

| V <sub>IH</sub>      | Single-ended input IH high voltage              |                                                                                              |                                |      |                       | V <sub>CC</sub>       | V      |  |  |  |  |

| V <sub>IL</sub>      | Single-ended input IL low voltage               | CLKinX driven single-                                                                        | ended (AC- or DC-              | GND  |                       |                       | V      |  |  |  |  |

| V <sub>I_SE</sub>    | Single-ended input voltage swing <sup>(8)</sup> | coupled), CLKinX*AC                                                                          | -coupled to GND or             | 0.3  |                       | 2                     | Vpp    |  |  |  |  |

| V <sub>CM</sub>      | Single-ended input CM common-<br>mode voltage   | externally biased with                                                                       | n v <sub>cm</sub> range        | 0.25 |                       | V <sub>CC</sub> - 1.2 | V      |  |  |  |  |

|                      |                                                 |                                                                                              | f <sub>CLKin0</sub> = 100 MHz  |      | - 84                  |                       |        |  |  |  |  |

| 100                  |                                                 | f <sub>OFFSET</sub> > 50 kHz,                                                                | f <sub>CLKin0</sub> = 200 MHz  |      | - 82                  |                       |        |  |  |  |  |

| ISO <sub>MUX</sub>   | Mux isolation, CLKin0 to CLKin1                 | $P_{CLKinX} = 0 \text{ dBm}$                                                                 | f <sub>CLKin0</sub> = 500 MHz  |      | - 71                  |                       | dBc    |  |  |  |  |

|                      |                                                 |                                                                                              | f <sub>CLKin0</sub> = 1000 MHz |      | - 65                  |                       | $\neg$ |  |  |  |  |

| CRYSTAL IN           | TERFACE (OSCin, OSCout)                         |                                                                                              |                                |      |                       |                       |        |  |  |  |  |

| F <sub>CLK</sub>     | External clock frequency range <sup>(8)</sup>   | OSCin driven single-e                                                                        | nded, OSCout floating          |      |                       | 250                   | MHz    |  |  |  |  |

| F <sub>XTAL</sub>    | Crystal frequency range                         | Fundamental mode cr<br>to 30 MHz) ESR ≤ 12                                                   |                                | 40   | MHz                   |                       |        |  |  |  |  |

| C <sub>IN</sub>      | OSCin input capacitance                         |                                                                                              |                                |      | 1                     |                       | pF     |  |  |  |  |

Unless otherwise specified:  $V_{CC}$  = 3.3 V ± 5%,  $V_{CCO}$  = 3.3 V ± 5%, 2.5 V ± 5%,  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3$  V/ns. Typical values represent the most likely parametric norms at  $V_{CC}$  = 3.3 V,  $V_{CCO}$  = 3.3 V,  $T_A$  = 25°C, and at the Recommended Operation Conditions at the time of product characterization; because of this, typical values are not ensured. <sup>(1)</sup>

|                            | PARAMETER                                                                 | TEST CO                                                                     | MIN                                      | ТҮР                       | MAX     | UNIT |        |

|----------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------|---------------------------|---------|------|--------|

| HCSL OUTPL                 | ITS (CLKoutAn/CLKoutAn*, CLKout                                           | Bn/CLKoutBn*)                                                               |                                          |                           |         |      |        |

| f <sub>CLKout</sub>        | Output frequency range <sup>(8)</sup>                                     | $R_L = 50 \Omega$ to GND, $C_L$                                             | $\leq$ 5 pF                              | DC                        |         | 400  | MHz    |

| Jitter <sub>ADD_PCle</sub> | Additive RMS phase jitter for PCIe $5.0^{(8)}$                            | PCle Gen 5 filter                                                           | CLKin: 100 MHz, slew rate $\ge 0.5$ V/ns |                           | 0.015   | 0.03 | ps     |

| Jitter <sub>ADD_PCle</sub> | Additive RMS phase jitter for PCIe $4.0^{(8)}$                            | PCIe Gen 4,<br>PLL BW = 2 - 5 MHz,<br>CDR = 10 MHz                          | CLKin: 100 MHz,<br>slew rate ≥ 1.8 V/ns  |                           | 0.03    | 0.05 | ps     |

| Jitter <sub>ADD_PCle</sub> | Additive RMS phase jitter for PCIe 3.0 <sup>(8)</sup>                     | PCIe Gen 3,<br>PLL BW = 2 - 5 MHz,<br>CDR = 10 MHz                          | CLKin: 100 MHz,<br>slew rate ≥ 0.6 V/ns  |                           | 0.03    | 0.15 | ps     |

| Jitter <sub>ADD</sub>      | Additive RMS jitter integration bandwidth 12 MHz to 20 MHz <sup>(5)</sup> | $V_{CCO}$ = 3.3 V,<br>R <sub>T</sub> = 50 $\Omega$ to GND                   | CLKin: 100 MHz, slew rate $\ge$ 3 V/ns   |                           | 77      |      | fs     |

| Noise Floor                | Noise floor $f_{OFFSET} \ge 10 \text{ MHz}^{(6)}$ (7)                     | $V_{CCO}$ = 3.3 V,<br>R <sub>T</sub> = 50 $\Omega$ to GND                   | CLKin: 100 MHz,<br>slew rate ≥ 3 V/ns    |                           | - 161.3 |      | dBc/Hz |

| DUTY                       | Duty cycle <sup>(8)</sup>                                                 | 50% input clock duty c                                                      | ycle                                     | 45%                       |         | 55%  |        |

| V <sub>OH</sub>            | Output high voltage                                                       | T <sub>A</sub> = 25°C, DC measur                                            | ement,                                   | 520                       | 810     | 920  | mV     |

| V <sub>OL</sub>            | Output low voltage                                                        | $R_T = 50 \Omega$ to GND                                                    | - 150                                    | 0.5                       | 150     | mV   |        |

| V <sub>CROSS</sub>         | Absolute crossing voltage <sup>(8) (9)</sup>                              |                                                                             | 250                                      | 350                       | 460     | mV   |        |

| $\Delta V_{CROSS}$         | Total variation of V <sub>CROSS</sub> <sup>(8)</sup> <sup>(9)</sup>       | $R_L = 50 \Omega$ to GND, $C_L$                                             | ≤ 5 pF                                   |                           |         | 140  | mV     |

| t <sub>R</sub>             | Output rise time 20% to 80% <sup>(9)</sup> (12)                           | 250 MHz, uniform trans                                                      |                                          | 225                       | 400     | ps   |        |

| t <sub>F</sub>             | Output fall time 80% to $20\%^{(9)}$ (12)                                 | in. with 50- $\Omega$ character 50 $\Omega$ to GND, C <sub>L</sub> $\leq$ 5 |                                          | 225                       | 400     | ps   |        |

| LVCMOS OUT                 | IPUT (REFout)                                                             |                                                                             |                                          |                           |         |      |        |

| f <sub>CLKout</sub>        | Output frequency range <sup>(8)</sup>                                     | $C_L \le 5  pF$                                                             |                                          | DC                        |         | 250  | MHz    |

| Jitter <sub>ADD</sub>      | Additive RMS jitter integration bandwidth 1 MHz to 20 MHz <sup>(5)</sup>  | $V_{CCO}$ = 3.3 V,<br>$C_L \le 5 \text{ pF}$                                | 100 MHz, input slew rate $\geq$ 3 V/ns   |                           | 95      |      | fs     |

| Noise Floor                | Noise floor $f_{OFFSET} \ge 10 \text{ MHz}^{(6)}$ (7)                     | $V_{CCO}$ = 3.3 V,<br>$C_L \le 5 \text{ pF}$                                | 100 MHz, input slew rate $\geq$ 3 V/ns   |                           | - 159.3 |      | dBc/Hz |

| DUTY                       | Duty cycle <sup>(8)</sup>                                                 | 50% input clock duty c                                                      | ycle                                     | 45%                       |         | 55%  |        |

| V <sub>OH</sub>            | Output high voltage                                                       | 1-mA load                                                                   |                                          | V <sub>CCO</sub><br>- 0.1 |         |      | V      |

| V <sub>OL</sub>            | Output low voltage                                                        |                                                                             |                                          |                           |         | 0.1  | V      |

| I <sub>OH</sub>            | Output high current (source)                                              |                                                                             | V <sub>CCO</sub> = 3.3 V                 |                           | 28      |      | mA     |

|                            |                                                                           | $V_{a} = V_{aaa} / 2$                                                       | V <sub>CCO</sub> = 2.5 V                 |                           | 20      |      | ШA     |

| I <sub>OL</sub>            | Output low current (sink)                                                 | $V_0 = V_{CCO} / 2$                                                         | V <sub>CCO</sub> = 3.3 V                 |                           | 28      |      | mA     |

|                            |                                                                           | V <sub>CCO</sub> = 2.5 V                                                    |                                          |                           | 20      |      |        |

| t <sub>R</sub>             | Output rise time 20% to 80% <sup>(9)</sup> (12)                           | 250 MHz, uniform trans                                                      | •                                        |                           | 225     | 400  | ps     |

| t <sub>F</sub>             | Output fall time 80% to 20% <sup>(10)</sup> (12)                          | in. with 50- $\Omega$ character 50 $\Omega$ to GND, C <sub>L</sub> $\leq$ 5 |                                          |                           | 225     | 400  | ps     |

| t <sub>EN</sub>            | Output enable time <sup>(10)</sup>                                        | - C <sub>L</sub> ≤ 5 pF                                                     |                                          |                           |         | 3    | cycles |

| t <sub>DIS</sub>           | Output disable time <sup>(10)</sup>                                       |                                                                             |                                          |                           |         | 3    | cycles |

(1) See *Power Supply Recommendations* and *Thermal Management* for more information on current consumption and power dissipation calculations.

(2) Power supply ripple rejection, or PSRR, is defined as the single-sideband phase spur level (in dBc) modulated onto the clock output when a single-tone sinusoidal signal (ripple) is injected onto the V<sub>CCO</sub> supply. Assuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows: DJ (ps pk-pk) = [ (2 × 10(<sup>PSRR</sup> / 20)) / ( π × f<sub>CLK</sub>) ] × 1E12

(3) See *Differential Voltage Measurement Terminology* for definition of V<sub>ID</sub> and V<sub>OD</sub> voltages.

- (4) The ESR requirements stated must be met to ensure that the oscillator circuitry has no start-up issues. However, lower ESR values for the crystal may be necessary to stay below the maximum power dissipation (drive level) specification of the crystal. Refer to Crystal Interface for crystal drive level considerations.

- (5) For the 100-MHz and 156.25-MHz clock input conditions, Additive RMS Jitter ( $J_{ADD}$ ) is calculated using Method #1:  $J_{ADD}$  = SQRT( $J_{OUT}$  <sup>2</sup>  $J_{SOURCE}$ <sup>2</sup>), where  $J_{OUT}$  is the total RMS jitter measured at the output driver and  $J_{SOURCE}$  is the RMS jitter of the clock source applied to CLKin. For the 625-MHz clock input condition, Additive RMS Jitter is approximated using Method #2:  $J_{ADD}$  = SQRT(2 ×  $10^{dBc/10}$ ) / (2 ×  $\pi$  × f<sub>CLK</sub>), where dBc is the phase noise power of the Output Noise Floor integrated from 12-kHz to 20-MHz bandwidth. The phase noise power can be calculated as: dBc = Noise Floor + 10 × log<sub>10</sub>(20 MHz 12 kHz).

- (6) The noise floor of the output buffer is measured as the far-out phase noise of the buffer. Typically this offset is ≥ 10 MHz, but for lower frequencies this measurement offset can be as low as 5 MHz due to measurement equipment limitations.

- (7) Phase noise floor will degrade as the clock input slew rate is reduced. Compared to a single-ended clock, a differential clock input (LVPECL, LVDS) will be less susceptible to degradation in noise floor at lower slew rates due to its common-mode noise rejection. However, TI recommends using the highest possible input slew rate for differential clocks to achieve optimal noise floor performance at the device outputs.

- (8) Specification is ensured by characterization and is not tested in production.

- (9) AC timing parameters for HCSL or CMOS are dependent on output capacitive loading.

- (10) Output Enable Time is the number of input clock cycles it takes for the output to be enabled after REFout\_EN is pulled high. Similarly, Output Disable Time is the number of input clock cycles it takes for the output to be disabled after REFout\_EN is pulled low. The REFout\_EN signal should have an edge transition much faster than that of the input clock period for accurate measurement.

- (11) Output skew is the propagation delay difference between any two outputs with identical output buffer type and equal loading while operating at the same supply voltage and temperature conditions.

- (12) Parameter is specified by design, not tested in production.

## 6.6 Timing Requirements, Propagation Delay, and Output Skew

|                      |                                                               |                        |                                          | MIN  | TYP  | MAX  | UNIT |

|----------------------|---------------------------------------------------------------|------------------------|------------------------------------------|------|------|------|------|

| t <sub>PD_HCSL</sub> | Propagation delay CLKin-to-HCSL <sup>(1)</sup> <sup>(2)</sup> | $R_T = 50 \Omega$ to G | ND, $C_L \leqslant 5 \text{ pF}$         | 295  | 590  | 885  | ps   |

| t <sub>PD_CMOS</sub> | Propagation delay CLKin-to-LVCMOS <sup>(1)</sup> (2)          | $C_{I} \leq 5  pF$     | V <sub>CCO</sub> = 3.3 V                 | 900  | 1475 | 2300 | 200  |

|                      |                                                               | CL ≪ 5 pr              | V <sub>CCO</sub> = 2.5 V                 | 1000 | 1550 | 2700 | ps   |

| t <sub>SK(O)</sub>   | Output skew <sup>(11) (9) (4)</sup>                           |                        | between any two CLKouts.                 |      | 30   | 50   | ps   |

| t <sub>SK(PP)</sub>  | Part-to-part output skew <sup>(1) (2) (3)</sup>               |                        | s are the same as<br>lay specifications. |      | 80   | 120  | ps   |

(1) AC timing parameters for HCSL or CMOS are dependent on output capacitive loading.

(2) Parameter is specified by design, not tested in production.

(3) Output skew is the propagation delay difference between any two outputs with identical output buffer type and equal loading while operating at the same supply voltage and temperature conditions.

(4) Specification is ensured by characterization and is not tested in production.

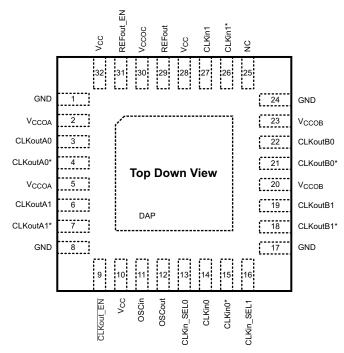

## 6.7 Typical Characteristics

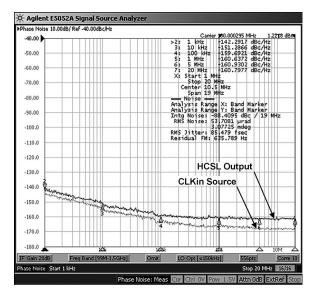

Unless otherwise specified: V<sub>CC</sub> = 3.3 V, V<sub>CCO</sub> = 3.3 V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\ge$  3 V/ns.

## 6.7 Typical Characteristics (continued)

Unless otherwise specified: V<sub>CC</sub> = 3.3 V, V<sub>CCO</sub> = 3.3 V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\ge$  3 V/ns.

# 6.7 Typical Characteristics (continued)

Unless otherwise specified: V<sub>CC</sub> = 3.3 V, V<sub>CCO</sub> = 3.3 V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\ge$  3 V/ns.

## 7 Parameter Measurement Information

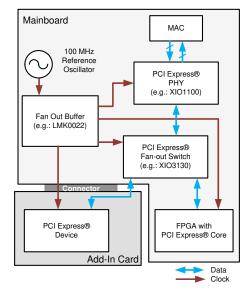

### 7.1 Differential Voltage Measurement Terminology

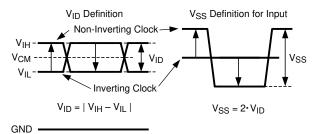

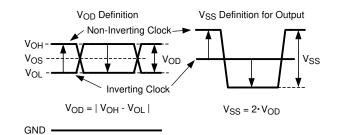

The differential voltage of a differential signal can be described by two different definitions, causing confusion when reading data sheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to understand and discern between the two different definitions when used.

The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and noninverting signal. The symbol for this first measurement is typically  $V_{ID}$  or  $V_{OD}$  depending on if an input or output voltage is being described.

The second definition used to describe a differential signal is to measure the potential of the noninverting signal with respect to the inverting signal. The symbol for this second measurement is  $V_{SS}$  and is a calculated parameter. Nowhere in the IC does this signal exist with respect to ground; it only exists in reference to its differential pair.  $V_{SS}$  can be measured directly by oscilloscopes with floating references, otherwise this value can be calculated as twice the value of  $V_{OD}$  as described in the first description.

[m] 7-1 illustrates the two different definitions side-by-side for inputs and [m] 7-2 illustrates the two different definitions side-by-side for outputs. The V<sub>ID</sub> (or V<sub>OD</sub>) definition show the DC levels, V<sub>IH</sub> and V<sub>OL</sub> (or V<sub>OH</sub> and V<sub>OL</sub>), that the noninverting and inverting signals toggle between with respect to ground. V<sub>SS</sub> input and output definitions show that if the inverting signal is considered the voltage potential reference, the noninverting signal voltage potential is now increasing and decreasing above and below the noninverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.

$V_{ID}$  and  $V_{OD}$  are often defined as volts (V) and  $V_{SS}$  is often defined as volts peak-to-peak ( $V_{PP}$ ).

图 7-1. Two Different Definitions for Differential Input Signals

Refer to Common Data Transmission Parameters and their Definitions (SNLA036) for more information.

# 8 Detailed Description

## 8.1 Overview

The LMK00334 is a 4-output HCSL clock fanout buffer with low additive jitter that can operate up to 400 MHz. It features a 3:1 input multiplexer with an optional crystal oscillator input, two banks of two HCSL outputs, one LVCMOS output, and three independent output buffer supplies. The input selection and output buffer modes are controlled through pin strapping. The device is offered in a 32-pin WQFN package and leverages much of the high-speed, low-noise circuit design employed in the LMK04800 family of clock conditioners.

## 8.2 Functional Block Diagram

## 8.3 Feature Description 8.3.1 Crystal Power Dissipation vs. R<sub>LIM</sub>

For 8 6-10, the following applies:

- The typical RMS jitter values in the plots show the total output RMS jitter ( $J_{OUT}$ ) for each output buffer type and the source clock RMS jitter ( $J_{SOURCE}$ ). From these values, the Additive RMS Jitter can be calculated as:  $J_{ADD} = SQRT(J_{OUT}^2 - J_{SOURCE}^2)$ .

- 20-MHz crystal characteristics: Abracon ABL series, AT cut, C<sub>L</sub> = 18 pF, C<sub>0</sub> = 4.4 pF measured (7 pF maximum), ESR = 8.5 Ω measured (40 Ω maximum), and Drive Level = 1 mW maximum (100 µW typical).

- 40-MHz crystal characteristics: Abracon ABLS2 series, AT cut, C<sub>L</sub> = 18 pF, C<sub>0</sub> = 5 pF measured (7 pF maximum), ESR = 5 Ω measured (40 Ω maximum), and Drive Level = 1 mW maximum (100 µW typical).

#### 8.3.2 Clock Inputs

The input clock can be selected from CLKin0/CLKin0\*, CLKin1/CLKin1\*, or OSCin. Clock input selection is controlled using the CLKin\_SEL[1:0] inputs as shown in 表 8-1. Refer to *Driving the Clock Inputs* for clock input requirements. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator circuit will start up and its clock will be distributed to all outputs. Refer to *Crystal Interface* for more information. Alternatively, OSCin may be driven by a single-ended clock (up to 250 MHz) instead of a crystal.

| 衣 8-1. Input Selection |            |                 |  |  |  |  |  |  |  |

|------------------------|------------|-----------------|--|--|--|--|--|--|--|

| CLKin_SEL1             | CLKin_SEL0 | SELECTED INPUT  |  |  |  |  |  |  |  |

| 0                      | 0          | CLKin0, CLKin0* |  |  |  |  |  |  |  |

| 0                      | 1          | CLKin1, CLKin1* |  |  |  |  |  |  |  |

| 1                      | X          | OSCin           |  |  |  |  |  |  |  |

= 0 4 Innut Calentian

**8-2** shows the output logic state vs. input state when either CLKin0/CLKin0\* or CLKin1/CLKin1\* is selected. When OSCin is selected, the output state will be an inverted copy of the OSCin input state.

#### 表 8-2. CLKin Input vs. Output States

| STATE OF<br>SELECTED CLKin                 | STATE OF<br>ENABLED OUTPUTS |

|--------------------------------------------|-----------------------------|

| CLKinX and CLKinX* inputs floating         | Logic low                   |

| CLKinX and CLKinX* inputs shorted together | Logic low                   |

| CLKin logic low                            | Logic low                   |

| CLKin logic high                           | Logic high                  |

#### 8.3.3 Clock Outputs

The HCSL output buffer for both Bank A and B outputs are can be disabled to Hi-Z using the  $\overline{\text{CLKout}_{EN}}$  [1:0] as shown in  $\mathbb{R}$  8-3. For applications where all differential outputs are not needed, any unused output pin should be left floating with a minimum copper length (see note below) to minimize capacitance and potential coupling and reduce power consumption. If all differential outputs are not used, TI recommends disabling (Hi-Z) the banks to reduce power. Refer to *Termination and Use of Clock Drivers* for more information on output interface and termination techniques.

#### 备注

For best soldering practices, the minimum trace length for any unused pin should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow.

| 表 8-3. Differential Output Buffer Type Selection |                                       |  |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| CLKout_EN                                        | CLKoutX BUFFER TYPE<br>(BANK A AND B) |  |  |  |  |  |  |

| 0                                                | HCSL                                  |  |  |  |  |  |  |

| 1                                                | Disabled (Hi-Z)                       |  |  |  |  |  |  |

#### 8.3.3.1 Reference Output

The reference output (REFout) provides a LVCMOS copy of the selected input clock. The LVCMOS output high level is referenced to the  $V_{CCO}$  voltage. REFout can be enabled or disabled using the enable input pin, REFout EN, as shown in  $\frac{1}{8}$  8-4.

| 表 8-4. Reference Output Enable |                 |  |  |  |  |  |  |

|--------------------------------|-----------------|--|--|--|--|--|--|

| REFout_EN REFout STATE         |                 |  |  |  |  |  |  |

| 0                              | Disabled (Hi-Z) |  |  |  |  |  |  |

| 1                              | Enabled         |  |  |  |  |  |  |

The REFout\_EN input is internally synchronized with the selected input clock by the SYNC block. This synchronizing function prevents glitches and runt pulses from occurring on the REFout clock when enabled or disabled. REFout will be enabled within three cycles ( $t_{EN}$ ) of the input clock after REFout\_EN is toggled high. REFout will be disabled within three cycles ( $t_{DIS}$ ) of the input clock after REFout\_EN is toggled low.

When REFout is disabled, the use of a resistive loading can be used to set the output to a predetermined level. For example, if REFout is configured with a  $1-k\Omega$  load to ground, then the output will be pulled to low when disabled.

#### 8.4 Device Functional Modes

#### 8.4.1 V<sub>CC</sub> and V<sub>CCO</sub> Power Supplies

The LMK00334 has separate 3.3-V core supplies ( $V_{CC}$ ) and three independent 3.3-V or 2.5-V output power supplies ( $V_{CCOA}$ ,  $V_{CCOB}$ ,  $V_{CCOC}$ ). Output supply operation at 2.5 V enables lower power consumption and output-level compatibility with 2.5-V receiver devices. The output levels for HCSL are relatively constant over the specified  $V_{CCO}$  range. Refer to *Power Supply Recommendations* for additional supply related considerations, such as power dissipation, power supply bypassing, and power supply ripple rejection (PSRR).

Take care to ensure the  $V_{CCO}$  voltages do not exceed the  $V_{CC}$  voltage to prevent turning-on the internal ESD protection circuitry.

备注

## 9 Application and Implementation

备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

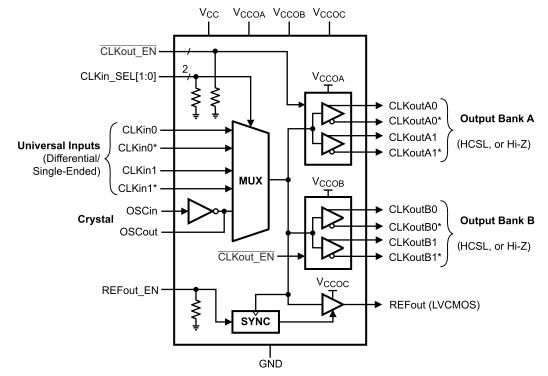

### 9.1 Application Information

A common PCIe application, such as a server card, consists of several building blocks, which all need a reference clock. In the mostly used Common RefClk architecture, the clock is distributed from a single source to both RX and TX. This requires either a Clock generator with high output count or a buffer like the LMK00334. The buffer simplifies the clocking tree and provides a cost and space optimized solution. While using a buffer to distribute the clock, the additive jitter must be considered. The LMK00334 is an ultra-low additive jitter PCIe clock buffer suitable for all current and future PCIe Generations.

### 9.2 Typical Application

图 9-1. Example PCI Express Application

#### 9.2.1 Design Requirements

#### 9.2.1.1 Driving the Clock Inputs

The LMK00334 has two universal inputs (CLKin0/CLKin0\* and CLKin1/CLKin1\*) that can accept DC-coupled, 3.3-V or 2.5-V LVPECL, LVDS, CML, SSTL, and other differential and single-ended signals that meet the input requirements specified in *Electrical Characteristics*. The device can accept a wide range of signals due to its wide input common-mode voltage range ( $V_{CM}$ ) and input voltage swing ( $V_{ID}$ ) / dynamic range. For 50% duty cycle and DC-balanced signals, AC coupling may also be employed to shift the input signal to within the  $V_{CM}$  range. Refer to *Termination and Use of Clock Drivers* for signal interfacing and termination techniques.

To achieve the best possible phase noise and jitter performance, it is mandatory for the input to have high slew rate of 3 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this reason, a differential signal input is recommended over single-ended because it typically provides higher slew rate and common-mode rejection. Refer to the *Noise Floor vs. CLKin Slew Rate* and *RMS Jitter vs. CLKin Slew Rate* plots in *Typical Characteristics*.

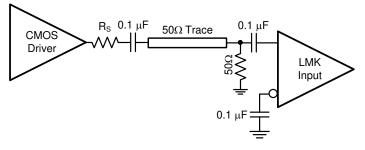

While TI recommends driving the CLKin/CLKin\* pair with a differential signal input, it is possible to drive it with a single-ended clock provided it conforms to the single-ended input specifications for CLKin pins listed in the *Electrical Characteristics*. For large single-ended input signals, such as 3.3-V or 2.5-V LVCMOS, a 50- $\Omega$  load resistor should be placed near the input for signal attenuation to prevent input overdrive as well as for line termination to minimize reflections. Again, the single-ended input slew rate should be as high as possible to minimize performance degradation. The CLKin input has an internal bias voltage of about 1.4 V, so the input can be AC coupled as shown in 8 9-2. The output impedance of the LVCMOS driver plus Rs should be close to 50  $\Omega$  to match the characteristic impedance of the transmission line and load termination.

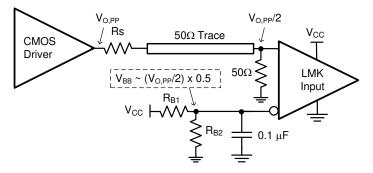

图 9-2. Single-Ended LVCMOS Input, AC Coupling

A single-ended clock may also be DC-coupled to CLKinX as shown in  $[\underline{R}]$  9-3. A 50- $\Omega$  load resistor should be placed near the CLKin input for signal attenuation and line termination. Because half of the single-ended swing of the driver (V<sub>O,PP</sub> / 2) drives CLKinX, CLKinX\* should be externally biased to the midpoint voltage of the attenuated input swing ((V<sub>O,PP</sub> / 2) × 0.5). The external bias voltage should be within the specified input common voltage (V<sub>CM</sub>) range. This can be achieved using external biasing resistors in the k $\Omega$  range (R<sub>B1</sub> and R<sub>B2</sub>) or another low-noise voltage reference. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.

图 9-3. Single-Ended LVCMOS Input, DC Coupling With Common-Mode Biasing

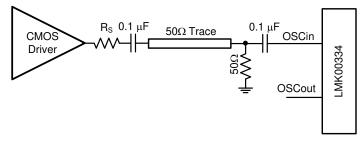

If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with an single-ended external clock as shown in 🛛 9-4. The input clock should be AC coupled to the OSCin pin, which has an internally-generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alternative input to multiplex an external clock, TI recommends using either universal input (CLKinX) because it offers higher operating frequency, better common-mode and power supply noise rejection, and greater performance over supply voltage and temperature variations.

图 9-4. Driving OSCin With a Single-Ended Input

#### 9.2.1.2 Crystal Interface

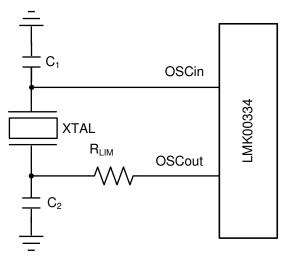

The LMK00334 has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal interface is shown in 🛽 9-5.

#### 图 9-5. Crystal Interface

The load capacitance (C<sub>L</sub>) is specific to the crystal, but usually on the order of 18 to 20 pF. While C<sub>L</sub> is specified for the crystal, the OSCin input capacitance (C<sub>IN</sub> = 1 pF typical) of the device and PCB stray capacitance (C<sub>STRAY</sub> is approximately around 1 to 3 pF) can affect the discrete load capacitor values, C<sub>1</sub> and C<sub>2</sub>.

For the parallel resonant circuit, the discrete capacitor values can be calculated as follows:

$$C_{L} = (C_{1} \times C_{2}) / (C_{1} + C_{2}) + C_{IN} + C_{STRAY}$$

(1)

Typically,  $C_1 = C_2$  for optimum symmetry, so  $5\pi R \ge 1$  can be rewritten in terms of  $C_1$  only:

$$C_{L} = C_{1}^{2} / (2 \times C_{1}) + C_{IN} + C_{STRAY}$$

(2)

Finally, solve for C<sub>1</sub>:

$$C_1 = (C_L - C_{IN} - C_{STRAY}) \times 2$$

(3)

(4)

*Electrical Characteristics* provides crystal interface specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer must ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause premature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start up and maintain steady-state operation.

The power dissipated in the crystal, P<sub>XTAL</sub>, can be computed by:

$$P_{XTAL} = I_{RMS}^{2} \times R_{ESR} \times (1 + C_0/C_L)^2$$

where

- I<sub>RMS</sub> is the RMS current through the crystal.

- R<sub>ESR</sub> is the maximum equivalent series resistance specified for the crystal

- C<sub>L</sub> is the load capacitance specified for the crystal

- C<sub>0</sub> is the minimum shunt capacitance specified for the crystal

I<sub>RMS</sub> can be measured using a current probe (Tektronix CT-6 or equivalent, for example) placed on the leg of the crystal connected to OSCout with the oscillation circuit active.

As shown in 🕅 9-5, an external resistor, R<sub>LIM</sub>, can be used to limit the crystal drive level, if necessary. If the power dissipated in the selected crystal is higher than the drive level specified for the crystal with R<sub>LIM</sub> shorted, then a larger resistor value is mandatory to avoid overdriving the crystal. However, if the power dissipated in the crystal is less than the drive level with R<sub>LIM</sub> shorted, then a zero value for R<sub>LIM</sub> can be used. As a starting point, a suggested value for R<sub>LIM</sub> is 1.5 kΩ.

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Termination and Use of Clock Drivers

When terminating clock drivers, keep these guidelines in mind for optimum phase noise and jitter performance:

- · Transmission line theory should be followed for good impedance matching to prevent reflections.

- Clock drivers should be presented with the proper loads.

- HCSL drivers are switched current outputs and require a DC path to ground through 50- $\Omega$  termination.

- Receivers should be presented with a signal biased to their specified DC bias level (common-mode voltage) for proper operation. Some receivers have self-biasing inputs that automatically bias to the proper voltage level; in this case, the signal should normally be AC coupled.

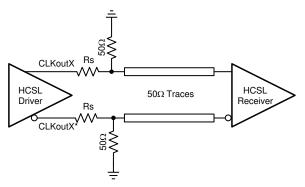

#### 9.2.2.2 Termination for DC-Coupled Differential Operation

For DC-coupled operation of an HCSL driver, terminate with 50  $\Omega$  to ground near the driver output as shown in  $\Im$  9-6. Series resistors, Rs, may be used to limit overshoot due to the fast transient current. Because HCSL drivers require a DC path to ground, AC coupling is not allowed between the output drivers and the 50- $\Omega$  termination resistors.

图 9-6. HCSL Operation, DC Coupling

#### 9.2.2.3 Termination for AC-Coupled Differential Operation

AC coupling allows for shifting the DC bias level (common-mode voltage) when driving different receiver standards. Because AC-coupling prevents the driver from providing a DC bias voltage at the receiver, it is important to ensure the receiver is biased to its ideal DC level.

#### 9.2.3 Application Curve

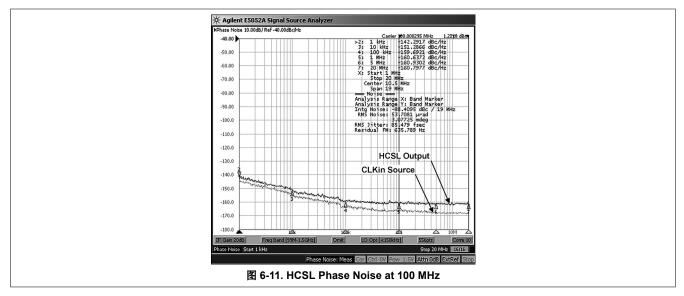

图 9-7. HCSL Phase Noise at 100 MHz

(5)

(6)

(8)

(9)

## 10 Power Supply Recommendations

### 10.1 Current Consumption and Power Dissipation Calculations

The current consumption values specified in *Electrical Characteristics* can be used to calculate the total power dissipation and IC power dissipation for any device configuration. The total  $V_{CC}$  core supply current ( $I_{CC_TOTAL}$ ) can be calculated using 5程式 5:

ICC\_TOTAL = ICC\_CORE + ICC\_BANKS + ICC\_CMOS

#### where

- I<sub>CC CORE</sub> is the V<sub>CC</sub> current for core logic and input blocks and depends on selected input (CLKinX or OSCin).

- I<sub>CC HCSL</sub> is the V<sub>CC</sub> current for Banks A and B

- I<sub>CC CMOS</sub> is the V<sub>CC</sub> current for the LVCMOS output (or 0 mA if REFout is disabled).

Because the output supplies ( $V_{CCOA}$ ,  $V_{CCOB}$ ,  $V_{CCOC}$ ) can be powered from three independent voltages, the respective output supply currents ( $I_{CCO}$  BANK A,  $I_{CCO}$  BANK B, and  $I_{CCO}$  CMOS) should be calculated separately.

$I_{CCO BANK} = I_{BANK BIAS} + (N \times I_{OUT LOAD})$

where

- I<sub>BANK BIAS</sub> is the output bank bias current (fixed value).

- I<sub>OUT LOAD</sub> is the DC load current per loaded output pair.

- N is the number of loaded output pairs (N = 0 to 2).

$\pm$  10-1 shows the typical I<sub>BANK BIAS</sub> values and I<sub>OUT LOAD</sub> expressions for HCSL.

#### 表 10-1. Typical Output Bank Bias and Load Currents

| CURRENT PARAMETER      | HCSL                            |  |  |  |  |

|------------------------|---------------------------------|--|--|--|--|

| I <sub>BANK_BIAS</sub> | 2.4 mA                          |  |  |  |  |

| lout_load              | V <sub>OH</sub> /R <sub>T</sub> |  |  |  |  |

Once the current consumption is known for each supply, the total power dissipation (P<sub>TOTAL</sub>) can be calculated by 方程式 7:

$$P_{\text{TOTAL}} = (V_{\text{CC}} \times I_{\text{CC} \text{ TOTAL}}) + (V_{\text{CCOA}} \times I_{\text{CCO} \text{ BANK}}) + (V_{\text{CCOB}} \times I_{\text{CCO} \text{ BANK}}) + (V_{\text{CCOC}} \times I_{\text{CCO} \text{ CMOS}})$$

(7)

If the device is configured with HCSL outputs, then it is also necessary to calculate the power dissipated in any termination resistors (P<sub>RT HCSL</sub>). The external power dissipation values can be calculated by 方程式 8:

$$P_{RT HCSL}$$

(per HCSL pair) =  $V_{OH}^2 / R_T$

Finally, the IC power dissipation (P<sub>DEVICE</sub>) can be computed by subtracting the external power dissipation values from P<sub>TOTAL</sub> as shown in 方程式 9:

$$P_{DEVICE} = P_{TOTAL} - N \times P_{RT_{HCSL}}$$

where

• N is the number of HCSL output pairs with termination resistors to GND.

#### 10.1.1 Power Dissipation Example: Worst-Case Dissipation

This example shows how to calculate IC power dissipation for a configuration to estimate **worst-case power dissipation**. In this case, the maximum supply voltage and supply current values specified in *Electrical Characteristics* are used:

- Max V<sub>CC</sub> = V<sub>CCO</sub> = 3.465 V. Max I<sub>CC</sub> and I<sub>CCO</sub> values.

- CLKin0/CLKin0\* input is selected.

- Banks A and B are enabled, and all outputs are terminated with 50  $\Omega$  to GND.

- REFout is enabled with 5-pF load.

- T<sub>A</sub> =85°C

Using the power calculations from the previous section and *maximum* supply current specifications, the user can compute  $P_{TOTAL}$  and  $P_{DEVICE}$ .

- From 方程式 5: I<sub>CC TOTAL</sub> = 10.5 mA + 58.5 mA + 5.5 mA = 74.5 mA

- From I<sub>CCO HCSL</sub> max spec: I<sub>CCO BANK</sub> = 50% of I<sub>CCO HCSL</sub> = 40.75 mA

- From 方程式 7: P<sub>TOTAL</sub> = (3.465 V × 74.5 mA) + (3.465 V × 40.75 mA) + (3.465 V × 40.75 mA) + (3.465 V × 10 mA) = 575.2 mW

- From 方程式 8: P<sub>RT HCSL</sub> = (0.92 V)<sup>2</sup> / 50 Ω = 16.9 mW (per output pair)

- From 方程式 9: P\_EVICE = 575.2 mW (4 × 16.9 mW) = 510.4 mW

In this worst-case example, the IC device will dissipate about 510.4 mW or 88.7% of the total power (575.2 mW), while the remaining 11.3% will be dissipated in the termination resistors (64.8 mW for 4 pairs). Based on R  $_{\theta JA}$  of 38.1°C/W, the estimate die junction temperature would be about 19.4°C above ambient, or 104.4°C when T<sub>A</sub> = 85°C.

## 10.2 Power Supply Bypassing

The V<sub>CC</sub> and V<sub>CCO</sub> power supplies should have a high-frequency bypass capacitor, such as 0.1  $\mu$ F or 0.01  $\mu$ F, placed very close to each supply pin. 1- $\mu$ F to 10- $\mu$ F decoupling capacitors should also be placed nearby the device between the supply and ground planes. All bypass and decoupling capacitors should have short connections to the supply and ground plane through a short trace or via to minimize series inductance.

#### 10.2.1 Power Supply Ripple Rejection

In practical system applications, power supply noise (ripple) can be generated from switching power supplies, digital ASICs or FPGAs, and so forth. While power supply bypassing will help filter out some of this noise, it is important to understand the effect of power supply ripple on the device performance. When a single-tone sinusoidal signal is applied to the power supply of a clock distribution device, such as LMK00334, it can produce narrow-band phase modulation as well as amplitude modulation on the clock output (carrier). In the single-side band phase noise spectrum, the ripple-induced phase modulation appears as a phase spur level relative to the carrier (measured in dBc).

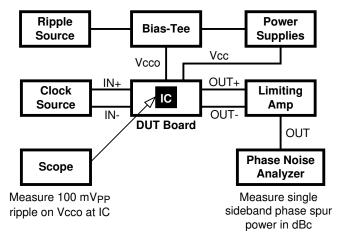

For the LMK00334, power supply ripple rejection, or PSRR, was measured as the single-sideband phase spur level (in dBc) modulated onto the clock output when a ripple signal was injected onto the V<sub>CCO</sub> supply. The PSRR test setup is shown in  $\boxtimes$  10-1.

图 10-1. PSRR Test Setup

A signal generator was used to inject a sinusoidal signal onto the  $V_{CCO}$  supply of the DUT board, and the peakto-peak ripple amplitude was measured at the  $V_{CCO}$  pins of the device. A limiting amplifier was used to remove amplitude modulation on the differential output clock and convert it to a single-ended signal for the phase noise analyzer. The phase spur level measurements were taken for clock frequencies of 156.25 MHz and 312.5 MHz under the following power supply ripple conditions:

- Ripple amplitude: 100 mVpp on  $V_{CCO}$  = 2.5 V

- Ripple frequencies: 100 kHz, 1 MHz, and 10 MHz

Assuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows:

DJ (ps pk-pk) = [

$$(2 \times 10^{(PSRR / 20)}) / (\pi \times f_{CLK})$$

] ×  $10^{12}$

The *PSRR vs. Ripple Frequency* plots in *Typical Characteristics* show the ripple-induced phase spur levels at 156.25 MHz and 312.5 MHz. The LMK00334 exhibits very good and well-behaved PSRR characteristics across the ripple frequency range. The phase spur levels for HCSL are below - 72 dBc at 156.25 MHz and below - 63 dBc at 312.5 MHz. Using 方程式 10, these phase spur levels translate to Deterministic Jitter values of 1.02 ps pk-pk at 156.25 MHz and 1.44 ps pk-pk at 312.5 MHz. Testing has shown that the PSRR performance of the device improves for V<sub>CCO</sub> = 3.3 V under the same ripple amplitude and frequency conditions.

(10)

# 11 Layout

## **11.1 Layout Guidelines**

For this device, consider the following guidelines:

- For DC-coupled operation of an HCSL driver, terminate with 50 Ω to ground near the driver output as shown in 图 11-1.

- Keep the connections between the bypass capacitors and the power supply on the device as short as possible.

- Ground the other side of the capacitor using a low impedance connection to the ground plane.

- If the capacitors are mounted on the back side, 0402 components can be employed. However, soldering to the Thermal Dissipation Pad can be difficult.

- For component side mounting, use 0201 body size capacitors to facilitate signal routing.

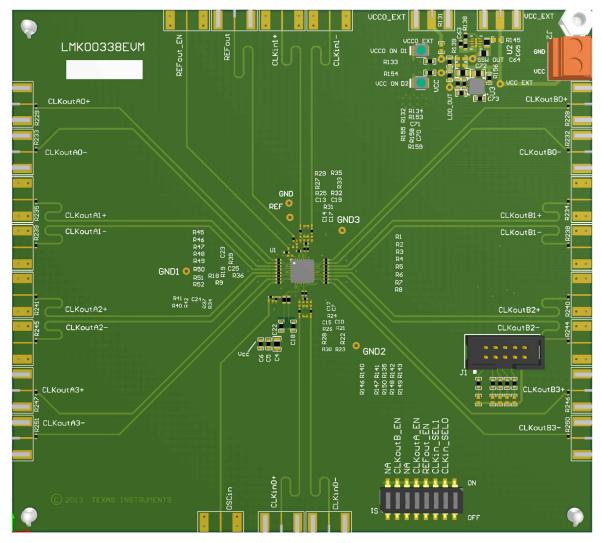

## 11.2 Layout Example

图 11-1. LMK00334 Layout Example

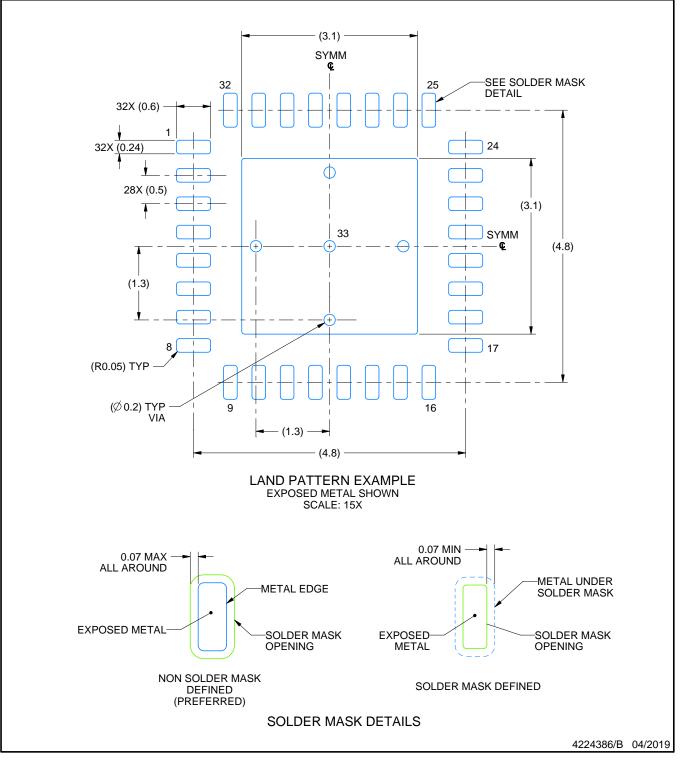

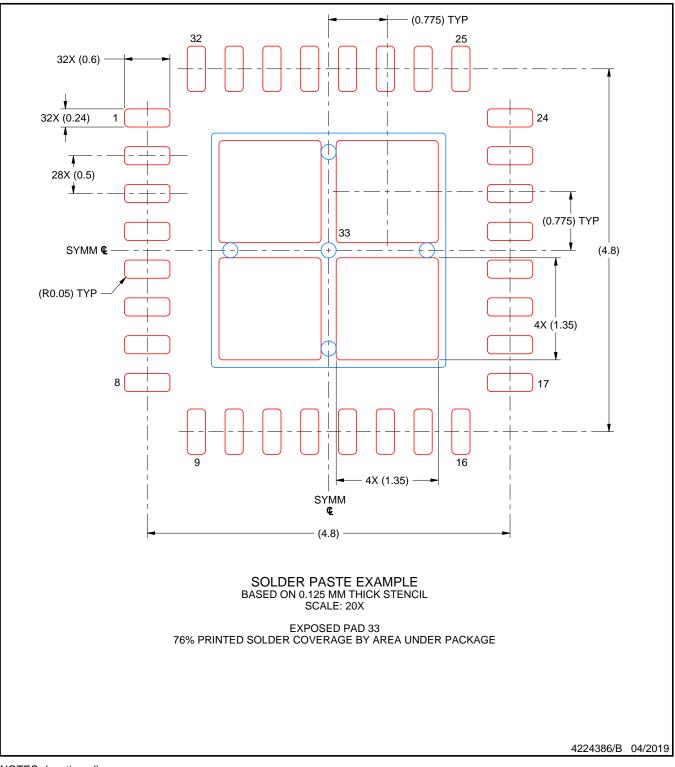

#### **11.3 Thermal Management**

Power dissipation in the LMK00334 device can be high enough to require attention to thermal management. For reliability and performance reasons the die temperature should be limited to a maximum of 125°C. That is, as an estimate,  $T_A$  (ambient temperature) plus device power dissipation times R  $_{\theta JA}$  should not exceed 125°C.

The package of the device has an exposed pad that provides the primary heat removal path as well as excellent electrical grounding to the printed-circuit board. To maximize the removal of heat from the package, a thermal land pattern including multiple vias to a ground plane must be incorporated on the PCB within the footprint of the package. The exposed pad must be soldered down to ensure adequate heat conduction out of the package.

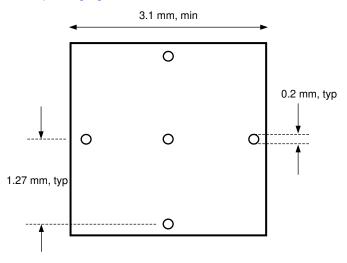

A recommended land and via pattern is shown in <u>11-2</u>. More information on soldering WQFN packages can be obtained at: <u>https://www.ti.com/packaging</u>.

图 11-2. Recommended Land and Via Pattern

To minimize junction temperature, TI recommends building a simple heat sink into the PCB (if the ground plane layer is not exposed). This is done by including a copper area of about 2 square inches on the opposite side of the PCB from the device. This copper area may be plated or solder coated to prevent corrosion but should not have conformal coating (if possible), which could provide thermal insulation. The vias shown in 图 11-2 should connect these top and bottom copper layers and to the ground layer. These vias act as *heat pipes* to carry the thermal energy away from the device side of the board to where it can be more effectively dissipated.

## 12 Device and Documentation Support

### **12.1 Documentation Support**

#### 12.1.1 Related Documentation

For related documents, see the following:

- Absolute Maximum Ratings for Soldering (SNOA549)

- Common Data Transmission Parameters and their Definitions (SNLA036)

- "How to Optimize Clock Distribution in PCIe Applications" on the Texas Instruments E2E community forum

- LMK00338EVM User's Guide (SNAU155)

- Semiconductor and IC Package Thermal Metrics (SPRA953).

### 12.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新*进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 12.3 支持资源

TI E2E<sup>™</sup> 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解 答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.6 术语表

TI 术语表 本术语表列出并解释了术语、首字母缩略词和定义。

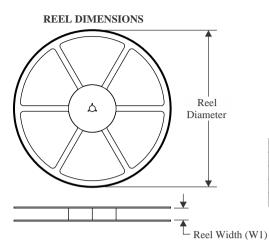

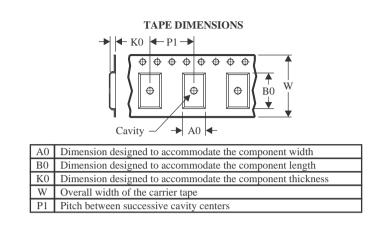

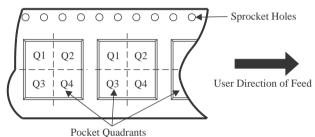

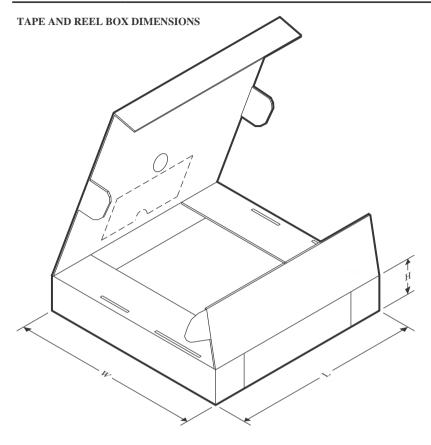

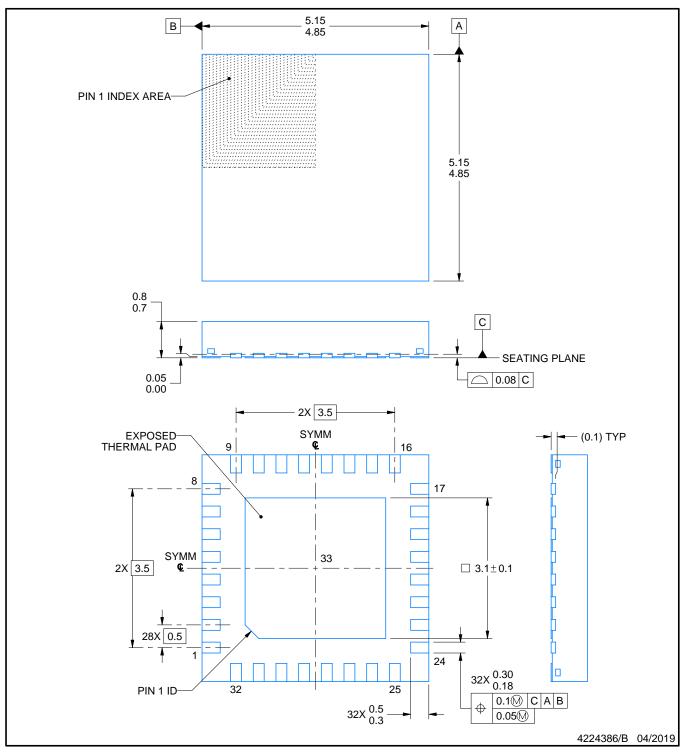

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|