ADC14X250

#### ZHCSEE8B-DECEMBER 2015-REVISED APRIL 2017

# ADC14X250 具有 5Gb/s JESD204B 输出的单通道 14 位 250MSPS ADC

## 1 特性

- 分辨率: 14 位

- 转换速率: 250MSPS

- 性能:

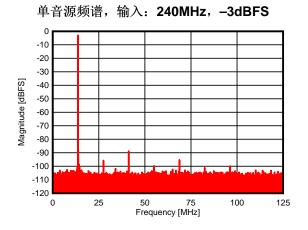

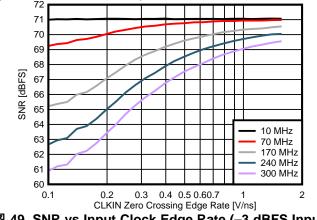

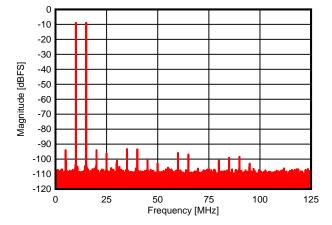

- 输入: 240MHz, -3dBFS

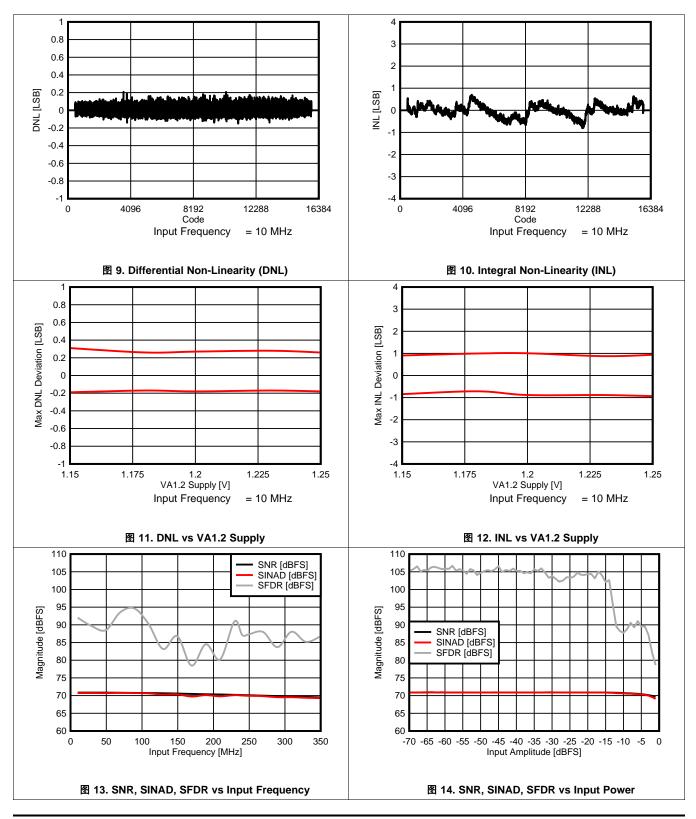

- 信噪比 (SNR): 70.1dBFS

- 噪声频谱密度: -151.1dBFS/Hz

- 无杂散动态范围 (SFDR): 87dBFS

- 非 HD2 和非 HD3 毛刺: -92dBFS

- 无输入 SNR: 71.1dBFS

- 功耗: 584mW

- 额定温度最高达 105°C (在散热焊盘处)

- JESD204B 通道速率高达 5Gb/s 的子类 1 单通道 串行数据接口

- 经缓冲的模拟输入

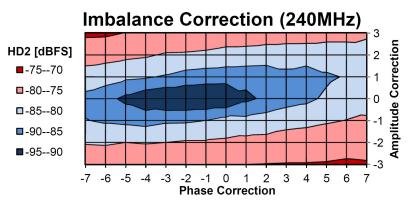

- 差分输入相位和幅值校正

- 输入采样时钟分频器(1分频、2分频、4分频、8 分频)

- 4 线制串行外设接口 (SPI)

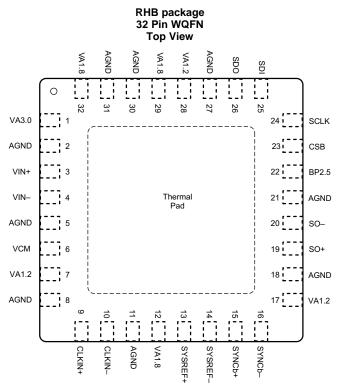

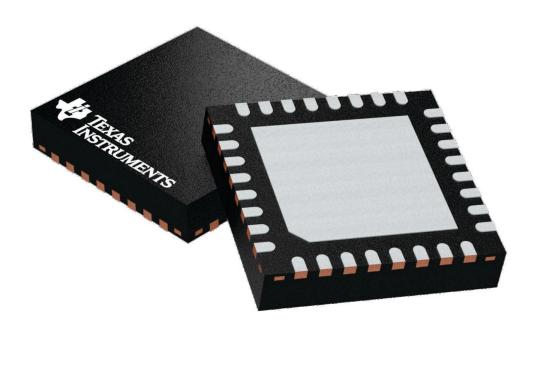

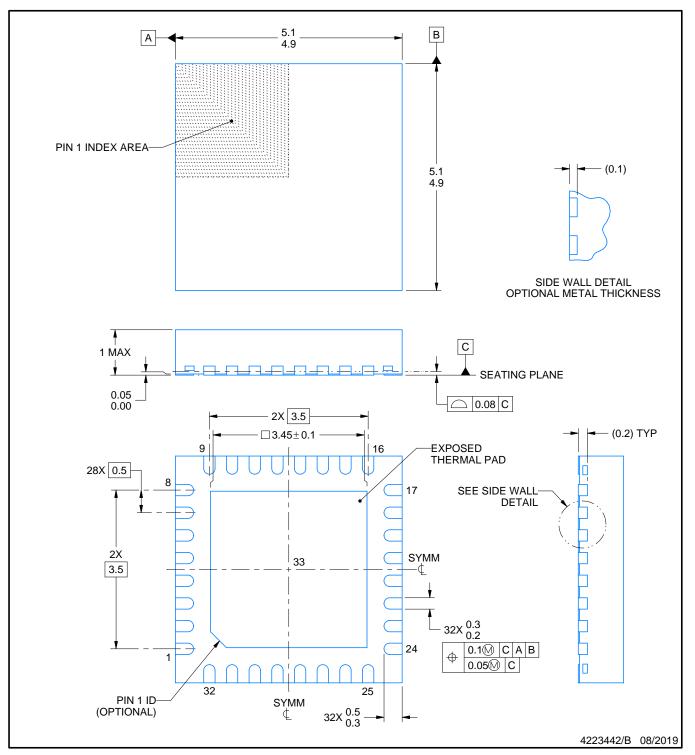

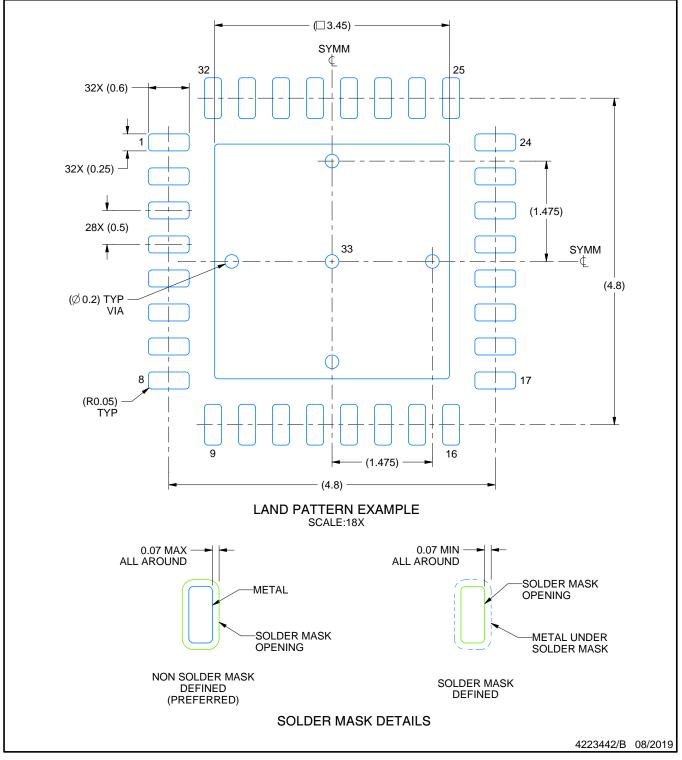

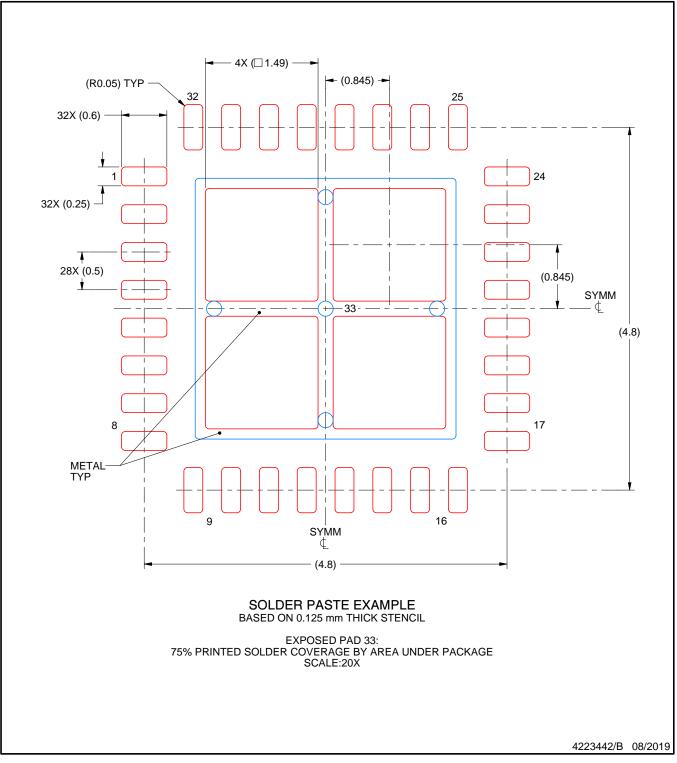

- 32 引脚超薄型四方扁平无引线 (WQFN) 封装 (5mm×5mm、0.5mm 间距)

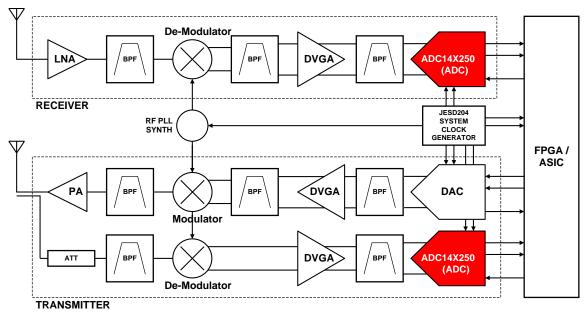

## 2 应用范围

- 高中频 (IF) 采样接收器

- 多载波基站接收器

- GSM/EDGE, CDMA2000, UMTS, LTE, Wi Max

- 多样性、多模式和多波段接收器

- 数字预失真

- 软件定义无线电 (SDR)

- 测试和测量设备

- 通信仪器仪表

- 雷达

- 便携式仪表

## 3 说明

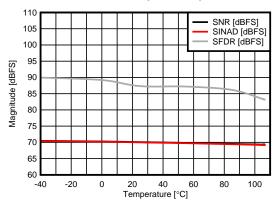

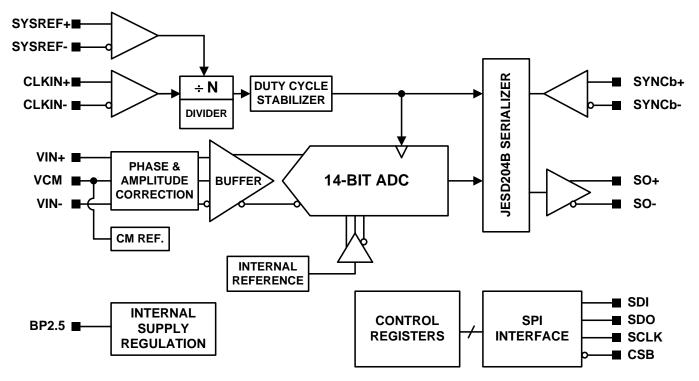

ADC14X250 器件是一款单片单通道高性能模数转换器,能够将模拟输入信号转换成 14 位数字字,采样速率达 250MSPS。该转换器采用差分流水线架构并集成有输入缓冲器,在 -40°C 至 105°C 的整个扩展温度范围内(在器件的印刷电路板 (PCB) 散热焊盘处测得)具有出色的动态性能和低功耗特性。

Support &

Community

22

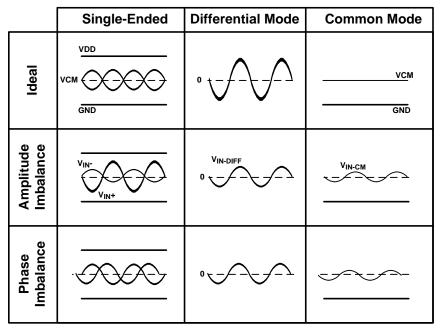

集成的输入缓冲器消除了来自内部开关电容采样电路的 电荷回馈噪声,并且简化了驱动放大器、抗混叠滤波器 以及阻抗匹配的系统级设计。此外,还可以对缓冲器进 行调整以校正差分输入信号路径的相位和幅值失衡,从 而改善偶数阶谐波失真。输入采样时钟分频器提供整数 分频比以简化系统时钟。该器件集成有低噪声电压基 准,无需使用外部去耦电容器,从而简化了电路板级设 计。数字输出数据通过采用 32 引脚 5mm × 5mm WQFN 封装的 JESD204B 子类 1 单通道接口提供。 ADC14X250 可在 1.2V、1.8V 和 3.0V 电源供电下工 作。可使用 SPI 来配置与 1.2V 至 3V 逻辑电路兼容的 器件。

#### 器件信息<sup>(1)</sup>

| 部件名称      | 封装        | 封装尺寸(标称值)       |  |  |

|-----------|-----------|-----------------|--|--|

| ADC14X250 | WQFN (32) | 5.00mm × 5.00mm |  |  |

(1) 要了解所有可用封装,请见产品说明书末尾的可订购产品附录。

Order I Now

整个温度范围内的 性能稳定性 (240MHz)

**EXAS**

NSTRUMENTS

|   | = |

|---|---|

| Ħ | 沤 |

|   |   |

| it he                                                            |    |

|------------------------------------------------------------------|----|

| 特性1                                                              | _  |

| 应用范围1                                                            | 8  |

| 说明1                                                              |    |

| 修订历史记录 3                                                         |    |

| Pin Configuration and Functions 4                                |    |

| Specifications                                                   |    |

| 6.1 Absolute Maximum Ratings 7                                   |    |

| 6.2 ESD Ratings                                                  | 9  |

| 6.3 Recommended Operating Conditions                             |    |

| 6.4 Thermal Information                                          |    |

| 6.5 Electrical Characteristics: Static Converter<br>Performance  | 10 |

| 6.6 Electrical Characteristics: Dynamic Converter<br>Performance | 11 |

| 6.7 Electrical Characteristics: Power Supply 11                  |    |

| 6.8 Electrical Characteristics: Analog Interface 11              | 12 |

| 6.9 Digital Input Characteristics 12                             |    |

| 6.10 Electrical Characteristics: Serial Data Output              |    |

| Interface 13                                                     |    |

| 6.11 Electrical Characteristics: Digital Input 13                |    |

| 6.12 Timing Requirements 14                                      |    |

| 6.13 Typical Characteristics 18                                  |    |

| Parameter Measurement Information 23                             | 13 |

|                                                                  |    |

|    | 7.1  | JESD204B Interface Functional Characteristics | 23   |

|----|------|-----------------------------------------------|------|

| 8  | Deta | iled Description                              | . 24 |

|    | 8.1  | Overview                                      | . 24 |

|    | 8.2  | Functional Block Diagram                      | . 24 |

|    | 8.3  | Feature Description                           | . 24 |

|    | 8.4  | Device Functional Modes                       | . 33 |

|    | 8.5  | Register Map                                  | . 34 |

| 9  | Appl | ication and Implementation                    |      |

|    | 9.1  | Application Information                       | . 41 |

|    | 9.2  | Typical Applications                          | . 55 |

| 10 |      | er Supply Recommendations                     |      |

|    | 10.1 |                                               |      |

|    | 10.2 | Decoupling                                    | . 60 |

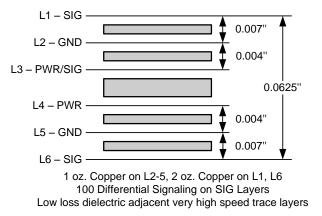

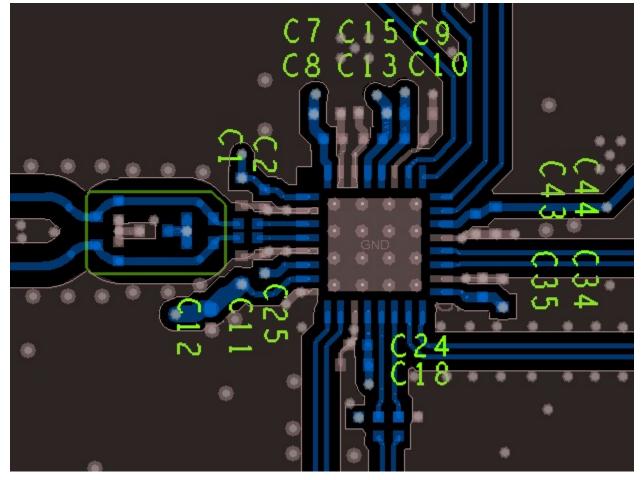

| 11 | Layo | out                                           | . 61 |

|    |      | Layout Guidelines                             |      |

| 12 |      | 和文档支持                                         |      |

|    | 12.1 | 器件支持                                          | . 63 |

|    | 12.2 | 接收文档更新通知                                      | . 64 |

|    | 12.3 | 社区资源                                          | . 64 |

|    | 12.4 | 商标                                            | . 64 |

|    | 12.5 | 静电放电警告                                        | . 64 |

|    | 12.6 | Glossary                                      | . 65 |

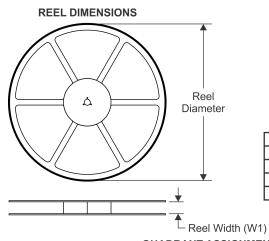

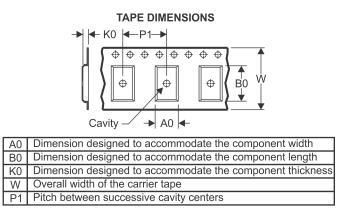

| 13 | 机械   | 、封装和可订购信息                                     |      |

|    |      |                                               |      |

# 4 修订历史记录

7

| С | Changes from Revision A (March 2017) to Revision B                                                                                                                              |      |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed V <sub>OH</sub> Test Conditions From: "Default V <sub>SPI</sub> = 1.8 V" To: "Default V <sub>SPI</sub> = 3 V" in <i>Electrical Characteristics: Digital Input</i> table | 13   |

| • | Changed text From: "output 1.8 V logic levels" To: "output 3 V logic levels" in section SPI                                                                                     | 32   |

| • | Changed text From: "output 1.8 V logic levels" To: "output 3 V logic levels" in section SPI                                                                                     | 55   |

|   |                                                                                                                                                                                 |      |

| 2 | hanges from Original (December 2015) to Revision A                                                                                                                              | Page |

|   |                                                              | -  |

|---|--------------------------------------------------------------|----|

| • | Changed 0.1: 1.8 V (default) to 0.1: 3.0 V (default) in 表 13 | 36 |

| • | Changed 11: 3.0 V To: 11: 1.8 V in 表 13                      | 36 |

## Page

## Dago

# ZHCSEE8B - DECEMBER 2015 - REVISED APRIL 2017

ADC14X250

# 5 Pin Configuration and Functions

Exposed pad on bottom of package

**Pin Functions**

| PIN    |                                    | TYPE OR DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO.                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| AGND   | 2, 5, 8, 11, 18,<br>21, 27, 30, 31 | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog ground<br>Must be connected to a solid ground reference plane<br>under the device.                                                                                                                                                                                                                                                                                                                            |  |

| BP2.5  | 22                                 | Bypass pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Capacitive bypassing pin for internally regulated 2.5-V supply<br>This pin must be decoupled to AGND with a $0.1$ - $\mu$ F and a $10$ - $\mu$ F capacitor located close to the pin.                                                                                                                                                                                                                                 |  |

| CLKIN+ | 9                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| CLKIN- | 10                                 | CLKIN+ $O$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A3,0}$<br>$V_{A$ | Differential device clock input pins<br>Each pin is internally terminated to a DC bias with a<br>$50-\Omega$ resistor for a $100-\Omega$ total internal differential<br>termination. AC coupling is required for coupling the<br>clock input to these pins if the clock driver cannot meet<br>the common-mode requirements. Sampling occurs on<br>the rising edge of the differential signal (CLKIN+) –<br>(CLKIN–). |  |

ADC14X250 ZHCSEE8B – DECEMBER 2015 – REVISED APRIL 2017

# Pin Functions (continued)

| PIN      |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO. |    | TYPE OR DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| CSB      | 23 | $\bigvee_{A3.0} \bigvee_{A1.2} \bigvee$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

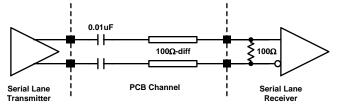

| SO+      | 19 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SO-      | 20 | VA3.0<br>VA3.0<br>VA3.0<br>S-<br>S-<br>AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Differential high speed serial data lane pins<br>These pins must be AC coupled to the receiving<br>device. The differential trace routing from these pins<br>must maintain a $100-\Omega$ characteristic impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

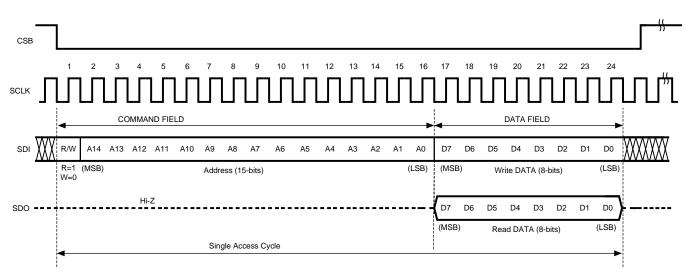

| SCLK     | 24 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPI serial clock pin<br>Serial data is shifted into and out of the device<br>synchronous with this clock signal. Compatible with<br>1.2- to 3-V CMOS logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SDI      | 25 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPI data input pin<br>Serial data is shifted into the device on this pin while<br>the CSB signal is asserted. Compatible with 1.2- to 3-V<br>CMOS logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

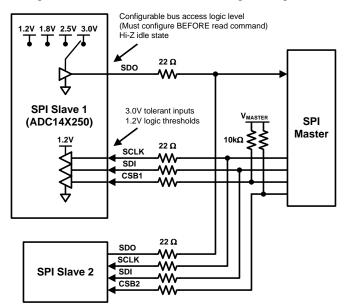

| SDO      | 26 | VA3.0<br>VA3.0<br>80Ω<br>80Ω<br>SDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SPI data output pin<br>Serial data is shifted out of the device on this pin<br>during a read command while CSB is asserted. The<br>output logic level is configurable as 1.2, 1.8, 2.5, or 3<br>V. The output level must be configured after power up<br>and before performing a read command. See the<br>Register Descriptions for configuration details.                                                                                                                                                                                                                                                                                                                   |  |

| SYNCb+   | 15 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SYNCb-   | 16 | $\begin{array}{c} V_{A3.0} \\ SYNC+ \\ \hline \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Differential SYNCb signal input pins<br>DC coupling is required for coupling the SYNCb signal<br>to these pins. Each pin is internally terminated to the<br>DC bias with a large resistor. An internal $100-\Omega$<br>differential termination is provided therefore an external<br>termination is not required. Additional resistive<br>components in the input structure give the SYNCb<br>input a wide input common-mode range. The SYNCb<br>signal is active low and therefore asserted when the<br>voltage at SYNCb+ is less than at SYNCb<br>If JESD204B sync~ signals are directed via SPI (with<br>SYNC_SEL=1), then SYNCb+ and SYNCb- may<br>remain not connected. |  |

ADC14X250 ZHCSEE8B-DECEMBER 2015-REVISED APRIL 2017

www.ti.com.cn

NSTRUMENTS

Texas

Pin Functions (continued)

| PIN          |            |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.     |            | TYPE OR DIAGRAM                                                                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

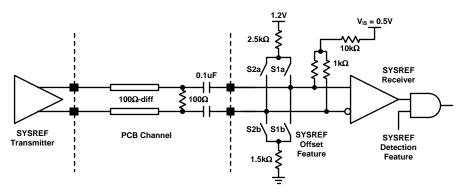

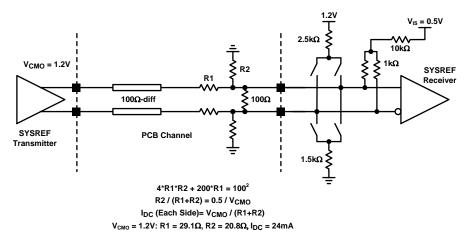

| SYSREF+      | 13         |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

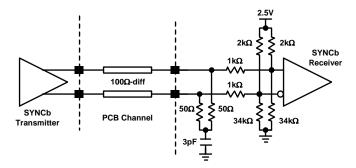

| SYSREF-      | 14         | SYSREF- O<br>SYSREF- O<br>AGND                                                       | Differential SYSREF signal input pins<br>Each pin is internally terminated to a DC bias with a 1- $k\Omega$ resistor. An external 100- $\Omega$ differential termination<br>must always be provided. AC coupling using capacitors<br>is required for coupling the SYSREF signal to these<br>pins if the clock driver cannot meet the common-mode<br>requirements. In the case of AC coupling, the external<br>termination must be placed on the source side of the<br>coupling capacitors.                                                                                                                                                                           |

| VA1.2        | 7, 17, 28  | Supply input pin                                                                     | 1.2-V analog power supply pins<br>These pins must be connected to a quiet source and<br>decoupled to AGND with a $0.1$ - $\mu$ F and $0.01$ - $\mu$ F<br>capacitor located close to each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VA1.8        | 12, 29, 32 | Supply input pin                                                                     | 1.8-V analog power supply pins<br>These pins must be connected to a quiet source and<br>decoupled to AGND with a $0.1$ - $\mu$ F and $0.01$ - $\mu$ F<br>capacitor located close to each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VA3.0        | 1          | Supply input pin                                                                     | 3-V analog power supply pin<br>This pin must be connected to a quiet source and<br>decoupled to AGND with a $0.1$ - $\mu$ F and $0.01$ - $\mu$ F<br>capacitor located close to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCM          | 6          |                                                                                      | Input interface common mode voltage<br>This pin must be bypassed to AGND with low<br>equivalent series inductance (ESL) 0.1- $\mu$ F capacitors.<br>One capacitor should be placed as close to the pin as<br>possible and additional capacitors placed at the bias<br>load points. 10- $\mu$ F capacitors should also be placed in<br>parallel. TI recommends to use VCM to provide the<br>common mode voltage for the differential analog<br>inputs. The input common mode bias is provided<br>internally for the ADC input; therefore, external use of<br>VCM is recommended, but not strictly required. The<br>recommended bypass capacitors are always required. |

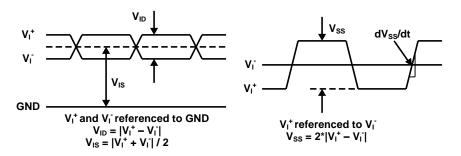

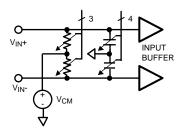

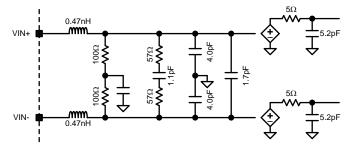

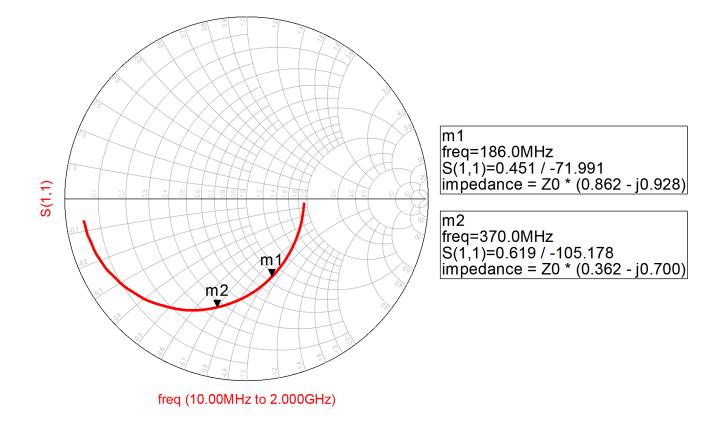

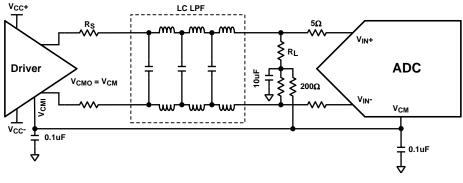

| VIN+<br>VIN- | 3          | V <sub>IN+</sub><br>V <sub>IN+</sub><br>V <sub>IN-</sub><br>V <sub>IN-</sub><br>AGND | Differential analog input pins<br>Each input pin is terminated to the internal common<br>mode reference with a resistor for an internal<br>differential termination. External resistors that terminate<br>to the common-mode voltage bias are recommended<br>but not strictly required. The total recommended<br>differential resistive termination (including the internal<br>200 $\Omega$ termination) is recommended to be between 50<br>$\Omega$ and 200 $\Omega$ .                                                                                                                                                                                              |

|              |            | Exposed thermal pad                                                                  | Exposed thermal pad<br>The exposed pad must be connected to the AGND<br>ground plane electrically and with good thermal<br>dissipation properties to achieve rated performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                      |                                               | MIN                   | MAX                                   | UNIT |

|----------------------|-----------------------------------------------|-----------------------|---------------------------------------|------|

| Supply Voltage       | V <sub>A3.0</sub>                             | -0.3                  | 4.2                                   | V    |

|                      | V <sub>A1.8</sub>                             | -0.3                  | 2.35                                  | V    |

|                      | V <sub>A1.2</sub>                             | -0.3                  | 1.55                                  | V    |

|                      | VIN+, VIN-                                    | $V_{CM} - 0.75^{(2)}$ | V <sub>CM</sub> + 0.75                | V    |

|                      | VCM                                           | -0.3                  | $V_{A3.0}$ + 0.3, not to exceed 4.2 V | V    |

|                      | SCLK, SDI, CSb                                | -0.3                  | $V_{A3.0}$ + 0.3, not to exceed 4.2 V | V    |

| Voltage at:          | SDO                                           | -0.3                  | $V_{SPI}$ + 0.3, not to exceed 4.2 V  | V    |

| Vollage al.          | CLKIN+, CLKIN-, SYSREF+, SYSREF-              | -0.3                  | 1.55                                  | V    |

|                      | SYNC+, SYNC-                                  | -0.3                  | V <sub>BP2.5</sub> + 0.3              | V    |

|                      | BP2.5                                         | -0.3                  | 3.2                                   | V    |

|                      | SO+, SO-                                      | -0.3                  | V <sub>BP2.5</sub> + 0.3              | V    |

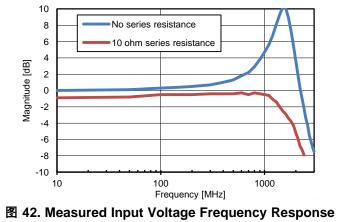

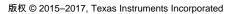

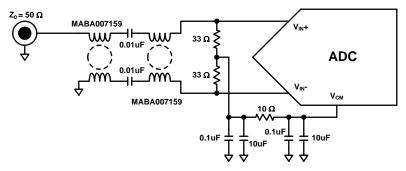

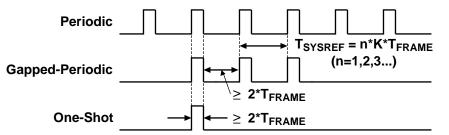

| Input current at any | pin <sup>(3)</sup>                            |                       | 5                                     | mA   |