# TUSB1106-Q1

ZHCS195-AUGUST 2011

16 V<sub>CC(5.0)</sub>

15 V<sub>reg(3.3)</sub>

14 VMO

13 VPO

12 D+

11 D-

10 SPEED

9 VCC(I/O)

**PW** 封装 (顶视图)

V<sub>pu(3.3)</sub>

SOFTCON 2

OE 3

RCV

VP 5

VM 6

SUSPND 7

GND

# 高级通用串行总线收发器

## 特性

- 符合汽车应用要求

- 与通用串行总线规范 2.0 版兼容

- 在全速 (12-Mbit/s) 和低速 (1.5-Mbit/s) 速率发送和 接收串行数据

- 集成 5-V 至 3.3-V 电压调节器用于通过 V<sub>BUS</sub>

- V<sub>BUS</sub> 通过 V<sub>P</sub> 和 V<sub>M</sub>的断开指示

- 用作USB设备收发器或者USB主机收发器

- 在SEO条件下的稳定RCV输出

- 2个具有滞后功能的单端接收器

- 是低功耗便携式设备的理想选择

- 支持 I/O 电压范围为 1.65 V 至 3.6 V

- 封装方式为超薄紧缩小型封装 [TSSOP (PW)]

## 说明

TUSB1106-Q1 通用串行总线 (USB) 收发器与通用串行总线规范版本 2.0 兼容。 在全速 (12-Mbit/s) 和低速 (1.5-Mbit/s) 数据速率下,此设备都能发送和接收串行数据。 TUSB1106-Q1 能被用作USB设备收发器或者USB主 机收发器。

此设备允许USB专用 IC (ASIC)和可编程逻辑设备 (PLD), 具有 1.65 V 至 3.6 V的电源供电电压, 到通用串行总线 的物理层接口。 它是集成的 5-V 至 3.3-V 电压调节器,用于通过USB电源VBUS进行直接供电。

TUSB1106-Q1 只允许差分输入模式,封装方式为PW封装。

TUSB1106-Q1 是便携式电子设备,例如手机、个人数字助理、信息装置和数码相机的理想选择。

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> <sup>(2)</sup> |              | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|---------------------------------------|--------------|-----------------------|------------------|--|

| –40°C to 85°C  | TSSOP – PW                            | Reel of 2000 | TUSB1106IPWRQ1        | TU1106I          |  |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

NSTRUMENTS

**EXAS**

#### ZHCS195-AUGUST 2011

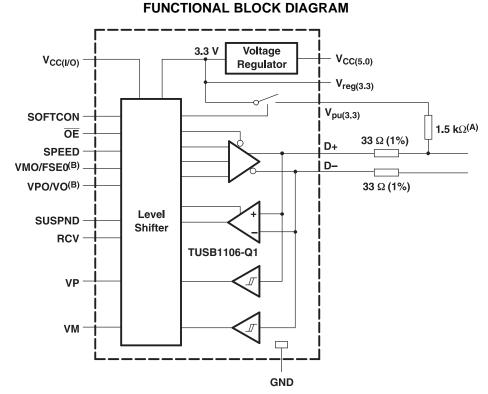

- A. Connect to D- for low-speed operation and to D+ for high-speed operation.

- B. Pin function depends on device type.

#### Copyright © 2011, Texas Instruments Incorporated

## TUSB1106-Q1

#### ZHCS195-AUGUST 2011

#### **TERMINAL FUNCTIONS**

| TERMINAL              |     |       | DECODIDION                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                  | NO. | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| ŌE                    | 3   | I     | Output enable (CMOS level with respect to $V_{CC(I/O)}$ , active LOW). Enables the transceiver to transmit data on the USB bus input pad. Push pull, CMOS.                                                                                                                                                                                              |  |  |  |

| RCV                   | 4   | 0     | Differential data receiver (CMOS level with respect to $V_{CC(I/O)}$ ). Driven LOW when input SUSPND is HIGH. The output state of RCV is preserved and stable during an SE0 condition output pad. Push pull, 4-mA output drive, CMOS.                                                                                                                   |  |  |  |

| VP                    | 5   | О     | Single-ended D+ receiver (CMOS level with respect to V). For external detection of single-ended zero (SE0), error conditions, speed of connected device. Driven HIGH when no supply voltage is connected to $V_{CC(5.0)}$ and $V_{reg(3.3)}$ output pad. Push pull, 4-mA output drive, CMOS.                                                            |  |  |  |

| VM                    | 6   | ο     | Single-ended D– receiver (CMOS level with respect to V <sub>CC(I/O)</sub> ). For external detection of single-ended zero (SE0), error conditions, speed of connected device. Driven HIGH when no supply voltage is connected to V <sub>CC(5.0)</sub> and V <sub>reg(3.3)</sub> output pad. Push pull, 4-mA output drive, CMOS.                          |  |  |  |

| SUSPND                | 7   | I     | Suspend (CMOS level with respect to $V_{CC(I/O)}$ ). A HIGH level enables low-power state while the USB bus is inactive and drives output RCV to a LOW-level input pad. Push pull, CMOS.                                                                                                                                                                |  |  |  |

| MODE                  |     | I     | Mode (CMOS level with respect to $V_{CC(I/O)}$ ). A HIGH level enables the differential input mode (VPO, VMO), whereas a LOW level enables a single-ended input mode (VO, FSE0). See Table 5 and Table 6 input pad. Push pull, CMOS.                                                                                                                    |  |  |  |

| GND                   | 8   |       | Ground supply                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| V <sub>CC(I/O)</sub>  | 9   |       | Supply voltage for digital I/O pins (1.65 to 3.6 V). When $V_{CC(I/O)}$ is not connected, the D+ and D– pins are in 3-state. This supply pin is independent of $V_{CC(5.0)}$ and $V_{reg(3.3)}$ and must never exceed the $V_{reg(3.3)}$ voltage.                                                                                                       |  |  |  |

| SPEED                 | 10  | I     | Speed selection (CMOS level with respect to $V_{CC(I/O)}$ ). Adjusts the slew rate of differential data outputs D+ and D- according to the transmission speed. Input pad, push pull, CMOS. LOW – low speed (1.5 Mbit/s) HIGH – full speed (12 Mbit/s)                                                                                                   |  |  |  |

| D-                    | 11  | AI/O  | Negative USB data bus connection (analog, differential). For low-speed mode, connect to pin $V_{pu(3.3)}$ via a 1.5-k $\Omega$ resistor.                                                                                                                                                                                                                |  |  |  |

| D+                    | 12  | AI/O  | Positive USB data bus connection (analog, differential). For full-speed mode, connect to pin $V_{pu(3.3)}$ via a 1.5-k $\Omega$ resistor.                                                                                                                                                                                                               |  |  |  |

| VPO/VO                |     | I     | Driver data (CMOS level with respect to V <sub>CC(I/O)</sub> , Schmitt trigger). See Driving Function table.                                                                                                                                                                                                                                            |  |  |  |

| VPO                   | 13  |       | Push pull, CMOS.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VMO/FSE0              |     | I     | Driver data (CMOS level with respect to V <sub>CC(I/O)</sub> , Schmitt trigger). See Driving Function table.                                                                                                                                                                                                                                            |  |  |  |

| VMO                   | 14  |       | Push pull, CMOS.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| V <sub>reg(3.3)</sub> | 15  |       | Internal regulator option. Regulated supply-voltage output (3 V to 3.6 V) during 5-V operation. A decoupling capacitor of at least 0.1 mF is required for the regulator bypass option. Used as a supply-voltage input for 3.3 V $\pm$ 10% operation.                                                                                                    |  |  |  |

| V <sub>CC(5.0)</sub>  | 16  |       | Internal regulator option. Supply-voltage input (4 V to 5.5 V). Can be connected directly to USB supply VBUS regulator bypass option. Connect to $V_{reg(3.3)}$ .                                                                                                                                                                                       |  |  |  |

| V <sub>pu(3.3)</sub>  | 1   |       | Pullup supply voltage (3.3 V ± 10%). Connect an external 1.5-kΩ resistor on D+ (full speed) or D– (low speed). Pin function is controlled by input SOFTCON.<br>SOFTCON = LOW – V <sub>pu(3.3)</sub> floating (high impedance), ensures zero pullup current SOFTCON = HIGH – V <sub>pu(3.3)</sub> = 3.3 V, internally connected to V <sub>reg(3.3)</sub> |  |  |  |

| SOFTCON               | 2   | I     | Software-controlled USB connection. A HIGH level applies 3.3 V to pin V <sub>pu(3.3)</sub> , which is connected to an external 1.5-k $\Omega$ pullup resistor. This allows USB connect/disconnect signaling to be controlled by software input pad. Push pull, CMOS.                                                                                    |  |  |  |

ZHCS195-AUGUST 2011

## FUNCTIONAL DESCRIPTION

## **Function Selection**

| FUNCTION TABLE |                                                          |                          |                         |        |                                                                        |  |  |

|----------------|----------------------------------------------------------|--------------------------|-------------------------|--------|------------------------------------------------------------------------|--|--|

| SUSPND         | SUSPND     OE     D+, D-     RCV     VP, VM     FUNCTION |                          |                         |        |                                                                        |  |  |

| L              | L                                                        | Driving and receiving    | Active                  | Active | Normal driving (differential receiver active)                          |  |  |

| L              | Η                                                        | Receiving <sup>(1)</sup> | Active                  | Active | Receiving                                                              |  |  |

| Н              | L                                                        | Driving                  | Inactive <sup>(2)</sup> | Active | Driving during suspend <sup>(3)</sup> (differential receiver inactive) |  |  |

| Н              | Н                                                        | High-Z <sup>(1)</sup>    | Inactive <sup>(2)</sup> | Active | Low-power state                                                        |  |  |

(1) Signal levels on D+ and D- are determined by other USB devices and external pullup/pulldown resistors.

(2) In suspend mode (SUSPND = HIGH) the differential receiver is inactive and output RCV is always LOW. Out of suspend (K), signaling is detected via the single-ended receivers VP and VM.

(3) During suspend, the slew-rate control circuit of low-speed operation is disabled. The D+ and D– lines are still driven to their intended states, without slew-rate control. This is permitted because driving during suspend is used to signal remote wakeup by driving a K signal (one transition from idle to K state) for a period of 1 ms to 15 ms.

## **Operating Functions**

| VMO VPO |     | DATA                 | DATA STATE |            |  |

|---------|-----|----------------------|------------|------------|--|

|         | VPU | DATA                 | LOW SPEED  | FULL SPEED |  |

| L       | L   | SE0                  | Х          | Х          |  |

| Н       | L   | Differential logic 0 | J          | К          |  |

| L       | Н   | Differential logic 1 | К          | J          |  |

| Н       | Н   | Illegal state        | Х          | Х          |  |

#### Driving Function (Pin OE = L) Using Differential Input Data Interface

|                      |                     |                   |                   | DATA STATE   |               |  |  |

|----------------------|---------------------|-------------------|-------------------|--------------|---------------|--|--|

| D+, D–               | RCV                 | VP <sup>(1)</sup> | VM <sup>(1)</sup> | LOW<br>SPEED | FULL<br>SPEED |  |  |

| Differential logic 0 | L                   | L                 | Н                 | J            | к             |  |  |

| Differential logic 1 | Н                   | н                 | L                 | К            | J             |  |  |

| SE0                  | RCV* <sup>(2)</sup> | L                 | L                 | Х            | Х             |  |  |

(1) VP = VM = H indicates the sharing mode (V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub> are disconnected).

RCV\* denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

## **Power-Supply Configurations**

The TUSB1106-Q1 can be used with different power-supply configurations, which can be dynamically changed. An overview is given in Table 3.

- Normal mode Both V<sub>CC(I/O)</sub> and V<sub>CC(5.0)</sub> or (V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub>) are connected. For 5-V operation, V<sub>CC(5.0)</sub> is connected to a 5-V source (4 V to 5.5 V). The internal voltage regulator then produces 3.3 V for the USB connections. For 3.3-V operation, both V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub> are connected to a 3.3-V source (3 V to 3.6 V). V<sub>CC(I/O)</sub> is independently connected to a voltage source (1.65 V to 3.6 V), depending on the supply voltage of the external circuit.

- Disable mode  $V_{CC(I/O)}$  is not connected,  $V_{CC(5.0)}$  or ( $V_{CC(5.0)}$  and  $V_{reg(3.3)}$ ) are connected. In this mode, the internal circuits of the TUSB1106-Q1 ensure that the D+ and D– pins are in 3-state and the power consumption drops to the low-power (suspended) state level. Some hysteresis is built into the detection of  $V_{CC(I/O)}$  lost.

- Sharing mode  $V_{CC(I/O)}$  is connected, ( $V_{CC(5.0)}$  and  $V_{reg(3.3)}$ ) are not connected. In this mode, the D+ and D- pins are made 3-state and the TUSB1106-Q1 allows external signals of up to 3.6 V to share the D+ and D-

lines. The internal circuits of the TUSB1106-Q1 ensure that virtually no current (maximum 10  $\mu$ A) is drawn via the D+ and D- lines. The power consumption through V<sub>CC(I/O)</sub> drops to the low-power (suspended) state level. Both the VP and VM pins are driven HIGH to indicate this mode. Pin RCV is made LOW. Some hysteresis is built into the detection of  $V_{reg(3.3)}$  lost.

| PINS                                                              | DISABLE-MODE STATE                              | SHARING-MODE STATE    |

|-------------------------------------------------------------------|-------------------------------------------------|-----------------------|

| V <sub>CC(5.0)</sub> /V <sub>reg(3.3)</sub>                       | 5-V input/3.3-V output, 3.3-V input/3.3-V input | Not present           |

| V <sub>CC(I/O)</sub>                                              | Not present                                     | 1.65-V to 3.6-V input |

| V <sub>pu(3.3)</sub>                                              | High impedance (off)                            | High impedance (off)  |

| D+, D–                                                            | High impedance                                  | High impedance        |

| VP, VM                                                            | Invalid <sup>(1)</sup>                          | н                     |

| RCV                                                               | Invalid <sup>(2)</sup>                          | L                     |

| Inputs (VO/VPO <u>, FS</u> E0/VMO, SPEED,<br>SUSPND, OE, SOFTCON) | High impedance                                  | High impedance        |

#### Table 2. Pin States in Disable or Sharing Mode

(1) High impedance or driven LOW

High impedance or driven LOW (2)

#### Table 3. Power-Supply Configuration Overview

| V <sub>CC(5.0)</sub> or V <sub>reg(3.3)</sub> | V <sub>CC(I/O)</sub> | CONFIGURATION | SPECIAL CHARACTERISTICS                                                                        |

|-----------------------------------------------|----------------------|---------------|------------------------------------------------------------------------------------------------|

| Connected                                     | Connected            | Normal mode   |                                                                                                |

| Connected                                     | Not connected        | Disable mode  | D+, D–, and $V_{pu(3.3)}$ are in high impedance. VP, VM, and RCV are invalid. <sup>(1)</sup>   |

| Not connected                                 | Connected            | Sharing mode  | D+, D–, and $V_{pu(3.3)}$ are in high impedance. VP and VM are driven HIGH. RCV is driven LOW. |

(1) High impedance or driven LOW

#### **Power-Supply Input Options**

The TUSB1106-Q1 has two power-supply input options.

- Internal regulator V<sub>CC(5.0)</sub> is connected to 4 V to 5.5 V. The internal regulator is used to supply the internal circuitry with 3.3 V (nominal).  $V_{reg(3.3)}$  becomes a 3.3-V output reference.

- Regulator bypass  $V_{CC(5.0)}$  and  $V_{reg(3.3)}$  are connected to the same supply. The internal regulator is bypassed and the internal circuitry is supplied directly from the  $V_{reg(3.3)}$  power supply. The voltage range is 3 V to 3.6 V to comply with the USB specification.

The supply-voltage range for each input option is specified in Table 4.

| Table 4. Power-Supply Input Op |

|--------------------------------|

|--------------------------------|

| INPUT OPTION V <sub>CC(5.0)</sub> |                                                                                              | V <sub>REG(3.3)</sub>                       | V <sub>CC(I/O)</sub>                                   |  |

|-----------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------|--|

| Internal regulator                | Supply input for internal regulator<br>(4 V to 5.5 V)                                        | Voltage-reference output<br>(3.3 V, 300 μA) | Supply input for digital I/O pins<br>(1.65 V to 3.6 V) |  |

| Regulator bypass                  | Connected to V <sub>reg(3.3)</sub> with<br>maximum voltage drop of 0.3 V<br>(2.7 V to 3.6 V) | Supply input<br>(3 V to 3.6 V)              | Supply input for digital I/O pins<br>(1.65 V to 3.6 V) |  |

www.ti.com.cn

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                         |                           |                         | MIN  | MAX                 | UNIT |

|-------------------------|---------------------------|-------------------------|------|---------------------|------|

| V <sub>CC(5.0)</sub>    | Supply voltage range      |                         | -0.5 | 6                   | V    |

| V <sub>I(I/O)</sub>     | Supply voltage range      |                         | -0.5 | 4.6                 | V    |

| V <sub>CCreg(3.3)</sub> | Regulated voltage range   |                         | -0.5 | 4.6                 | V    |

| VI                      | DC input voltage          |                         | -0.5 | $V_{CC(I/O)} + 0.5$ | V    |

| I <sub>IK</sub>         | Input clamp current       | $V_1 = -1.8 V$ to 5.4 V |      | 100                 | mA   |

| T <sub>stg</sub>        | Storage temperature range |                         | -40  | 125                 | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

|                         |                                           |                 | MIN  | NOM | MAX                  | UNIT |

|-------------------------|-------------------------------------------|-----------------|------|-----|----------------------|------|

| V <sub>CC(5.0)</sub>    | Supply voltage, internal regulator option | 5-V operation   | 4    | 5   | 5.5                  | V    |

| V <sub>CCreg(3.3)</sub> | Supply voltage, regulator bypass option   | 3.3-V operation | 3    | 3.3 | 3.6                  | V    |

| V <sub>CC(I/O)</sub>    | I/O supply voltage                        |                 | 1.65 |     | 3.6                  | V    |

| VI                      | I/O supply voltage                        |                 | 0    |     | V <sub>CC(I/O)</sub> | V    |

| V <sub>I/O</sub>        | Input voltage on analog I/O pins (D+, D–) |                 | 0    |     | 3.6                  | V    |

| T <sub>c</sub>          | Junction temperature                      |                 | -40  |     | 85                   | °C   |

www.ti.com.cn

### STATIC ELECTRICAL CHARACTERISTICS – SUPPLY PINS

over recommended ranges of operating free-air temperature and supply voltage (unless otherwise noted)

|                               | PARAMETER                                     | TEST CON                                                                                                                                                                                                              | DITIONS                                      | MIN | TYP  | MAX | UNIT |

|-------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|------|-----|------|

| V <sub>reg(3.3)</sub>         | Regulated<br>supply-voltage output            | Internal regulator option, $I_{load} \leq 300 \ \mu A^{(1)}$ <sup>(2)</sup>                                                                                                                                           |                                              |     | 3.3  | 3.6 | V    |

| I <sub>CC</sub>               | Operating supply current                      | Full-speed transmitting and re<br>C <sub>L</sub> = 50 pF on D+ and D- $^{(3)}$                                                                                                                                        |                                              | 6   | 8    | mA  |      |

| I <sub>CC(I/O)</sub>          | Operating I/O supply current                  | Full-speed transmitting and re                                                                                                                                                                                        |                                              | 2.3 | 2.5  | mA  |      |

| I <sub>CC(idle)</sub>         | Supply current during full-speed idle and SE0 | $ \begin{array}{l} \mbox{Full-speed idle:} \\ \mbox{V}_{D+} > 2.7 \ \mbox{V}, \ \mbox{V}_{D-} < 0.3 \ \mbox{V} \\ \mbox{SE0:} \\ \mbox{V}_{D+} < 0.3 \ \mbox{V}, \ \mbox{V}_{D-} < 0.3 \ \mbox{V}^{(4)} \end{array} $ |                                              |     | 500  | μA  |      |

| I <sub>CC(I/O)(static)</sub>  | Static I/O supply current                     | Full-speed idle, SE0 or suspe                                                                                                                                                                                         |                                              | 10  | 22   | μA  |      |

| I <sub>CC(susp)</sub>         | Suspend supply current                        | $SUSPND = HIGH^{(4)}$                                                                                                                                                                                                 |                                              | 10  | 22   | μA  |      |

| I <sub>CC(dis)</sub>          | Disable-mode supply current                   | V <sub>CC(I/O)</sub> not connected <sup>(4)</sup>                                                                                                                                                                     |                                              | 10  | 22   | μA  |      |

| I <sub>CC(I/O)(sharing)</sub> | Sharing-mode I/O<br>supply current            | $V_{CC(5.0)} \text{ or } V_{reg(3.3)} \text{ not connect}$                                                                                                                                                            |                                              | 10  | 22   | μA  |      |

| I <sub>Dx(sharing)</sub>      | Sharing-mode load current<br>on D+ and D–     | $V_{CC(5.0)}$ or $V_{reg(3.3)}$ not connect<br>SOFTCON = LOW, $V_{Dx}$ = 3.6                                                                                                                                          |                                              |     | 10   | μA  |      |

|                               | Regulated supply-voltage detection threshold  | $1.65 \text{ V} \leq \text{V}_{\text{CC(I/O)}} \leq \text{V}_{\text{reg}(3.3)},$                                                                                                                                      | Supply lost<br>during power down             |     |      | 0.8 | V    |

| V <sub>reg(3.3)th</sub>       |                                               | $2.7 \text{ V} \le \text{V}_{\text{reg}(3.3)} \le 3.6 \text{ V}$                                                                                                                                                      | Supply detect during power up <sup>(5)</sup> | 2.4 |      |     | V    |

| V <sub>reg(3.3)hys</sub>      | Regulated supply-voltage detection hysteresis | V <sub>CC(I/O)</sub> = 1.8 V                                                                                                                                                                                          |                                              |     | 0.45 |     | V    |

|                               | I/O supply-voltage                            |                                                                                                                                                                                                                       | Supply lost<br>during power down             |     |      |     | V    |

| V <sub>CC(I/O)th</sub>        | detection threshold                           | $V_{reg(3.3)} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                                                                                                                      | Supply detect<br>during power up             | 1.4 |      |     | V    |

| V <sub>CC(I/O)hys</sub>       | I/O supply-voltage detection hysteresis       | V <sub>reg(3.3)</sub> = 3.3 V                                                                                                                                                                                         |                                              |     | 0.45 |     | V    |

I<sub>load</sub> includes the pullup resistor current via V<sub>pu(3.3)</sub>.

In suspend mode, the typical voltage is 2.8 V.

Maximum value is characterized only, not tested in production.

Excluding any load current and V<sub>pu(3.3)</sub>/V<sub>sw</sub> source current to the 1.5-kΩ and 15-kΩ pullup and pulldown resistors (200 µA typ)

When V<sub>CC(I/O)</sub> < 2.7 V, the minimum value for V<sub>reg(3.3)th</sub> (present) is 2 V.

## STATIC ELECTRICAL CHARACTERISTICS - DIGITAL PINS

over recommended ranges of operating free-air temperature and supply voltage (unless otherwise noted)

|                 | PARAMETER                 | TEST CONDITIONS                        | V <sub>CC(I/O)</sub> | MIN                         | MAX                      | UNIT |

|-----------------|---------------------------|----------------------------------------|----------------------|-----------------------------|--------------------------|------|

| VIL             | LOW-level input voltage   |                                        | 1.65 V to 3.6 V      |                             | 0.3 V <sub>CC(I/O)</sub> | V    |

| VIH             | HIGH-level input voltage  |                                        | 1.65 V to 3.6 V      | 0.6 V <sub>CC(I/O)</sub>    |                          | V    |

|                 |                           | I <sub>OL</sub> = 100 μA               | 1.65 V to 3.6 V      |                             | 0.15                     |      |

|                 |                           | $I_{OL} = 2 \text{ mA}$                | 1.65 V to 3.6 V      |                             | 0.4                      |      |

|                 |                           | I <sub>OL</sub> = 100 μA               | 1.8 V ± 0.15 V       |                             | 0.15                     |      |

|                 |                           | $I_{OL} = 2 \text{ mA}$                | 1.8 V ± 0.15 V       |                             | 0.4                      | V    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 100 μA               | 2.5 V ± 0.2 V        |                             | 0.15                     | V    |

|                 |                           | $I_{OL} = 2 \text{ mA}$                | 2.5 V ± 0.2 V        |                             | 0.4                      |      |

|                 |                           | I <sub>OL</sub> = 100 μA 3.3 V ± 0.3 V | 0.15                 |                             |                          |      |

|                 |                           | $I_{OL} = 2 \text{ mA}$                | 3.3 V ± 0.3 V        |                             | 0.4                      |      |

|                 |                           | I <sub>OH</sub> = 100 μA               | 1.65 V to 3.6 V      | V <sub>CC(I/O)</sub> - 0.15 |                          |      |

|                 |                           | $I_{OH} = 2 \text{ mA}$                | 1.05 V 10 5.0 V      | $V_{CC(I/O)} - 0.4$         |                          |      |

|                 |                           | I <sub>OH</sub> = 100 μA               | 1.8 V ± 0.15 V       | 1.5                         |                          |      |

|                 | HIGH-level output voltage | $I_{OH} = 2 \text{ mA}$                | 1.6 V ± 0.15 V       | 1.25                        |                          | V    |

| V <sub>ОН</sub> | nigh-level output voltage | I <sub>OH</sub> = 100 μA               | 2.5 V ± 0.2 V        | 2.15                        |                          | v    |

|                 |                           | $I_{OH} = 2 \text{ mA}$                | 2.5 V ± 0.2 V        | 1.9                         |                          |      |

|                 |                           | I <sub>OH</sub> = 100 μA               | 3.3 V ± 0.3 V        | 2.85                        | 2.85                     |      |

|                 |                           | I <sub>OH</sub> = 2 mA                 | 3.3 V I U.3 V        | 2.6                         |                          |      |

| LI              | Input leakage current     |                                        |                      | -1                          | 1                        | μA   |

| C <sub>IN</sub> | Input capacitance         | Pin to GND                             |                      |                             | 3.5                      | pF   |

www.ti.com.cn

ZHCS195-AUGUST 2011

www.ti.com.cn

## **STATIC ELECTRICAL CHARACTERISTICS – ANALOG I/O PINS**

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$  (unless otherwise noted)

|                   | PARAMETER                                          | TEST CONDITIONS                                       | MIN                  | TYP | MAX | UNIT |

|-------------------|----------------------------------------------------|-------------------------------------------------------|----------------------|-----|-----|------|

| $V_{DI}$          | Differential input sensitivity                     | $ V_{I(D+)} - V_{I(D-)} $                             | 0.2                  |     |     | V    |

| V <sub>CM</sub>   | Differential common-mode voltage                   | Includes V <sub>DI</sub> range                        | 0.8                  |     | 2.5 | V    |

| V <sub>IL</sub>   | LOW-level input voltage, single-ended receiver     |                                                       | 2                    |     | 0.8 | V    |

| VIH               | HIGH-level input voltage, single-ended receiver    |                                                       | 0.4                  |     |     | V    |

| V <sub>hys</sub>  | Hysteresis voltage, single-ended receiver          |                                                       |                      |     | 0.7 | V    |

| V <sub>OL</sub>   | LOW-level output voltage                           | $R_L = 1.5 \text{ k}\Omega \text{ to } 3.6 \text{ V}$ |                      |     | 0.3 | V    |

| V <sub>OH</sub>   | HIGH-level output voltage                          | $R_L = 1.5 \text{ k}\Omega \text{ to GND}$            | 2.8 <sup>(1)</sup>   |     | 3.6 | V    |

| $I_{LZ}$          | OFF-state leakage current                          |                                                       |                      |     | 1   | μA   |

| CIN               | Transceiver capacitance                            | Pin to GND                                            |                      |     | 25  | pF   |

| Z <sub>DRV</sub>  | Driver output impedance                            | Steady-state drive                                    | 34 <sup>(2)</sup>    | 39  | 44  | Ω    |

| Z <sub>INP</sub>  | Input impedance                                    |                                                       | 10                   |     |     | MΩ   |

| $R_{SW}$          | Internal switch resistance at V <sub>pu(3.3)</sub> |                                                       |                      |     | 13  | Ω    |

| V <sub>TERM</sub> | Termination voltage for upstream port pullup (RPU) |                                                       | 3 <sup>(3) (4)</sup> |     | 3.6 | V    |

#### ZHCS195-AUGUST 2011

# DYNAMIC ELECTRICAL CHARACTERISTICS – ANALOG I/O PINS (D+, D–)<sup>(1) (2)</sup> Driver Characteristics, Full-Speed Mode

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{CC(I/O)} = 1.65 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}$ , see Table 10 for valid voltage level combinations,  $T_A = -40^{\circ}\text{C}$  to 85°C (unless otherwise noted)

|                  | PARAMETER                                              | TEST CONDITIONS                                                                                 | MIN | MAX   | UNIT |  |  |  |  |  |

|------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-------|------|--|--|--|--|--|

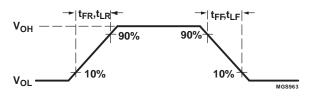

| t <sub>FR</sub>  | Rise time                                              | $C_{L} = 50 \text{ pF to } 125 \text{ pF},$<br>10% to 90% of $ V_{OH} - V_{OL} $ (see Figure 1) | 4   | 20    | ns   |  |  |  |  |  |

| t <sub>FF</sub>  | Fall time                                              | $C_{L} = 50 \text{ pF to } 125 \text{ pF},$<br>90% to 10% of $ V_{OH} - V_{OL} $ (see Figure 1) | 4   | 20    | ns   |  |  |  |  |  |

| FRFM             | Differential rise/fall time matching $(t_{FR}/t_{FF})$ | Excluding the first transition from idle state                                                  | 90  | 111.1 | %    |  |  |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage                        | Excluding the first transition from idle state (see Figure 10)                                  | 1.3 | 2     | V    |  |  |  |  |  |

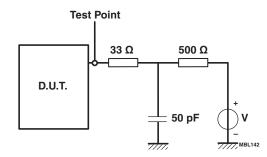

(1) Test circuit, see Figure 13

(2) Driver timing in low-speed mode is not specified. Low-speed delay timings are dominated by the slow rise/fall times t<sub>LR</sub> and t<sub>LF</sub>.

# DYNAMIC ELECTRICAL CHARACTERISTICS – ANALOG I/O PINS (D+, D–)<sup>(1) (2)</sup> Driver Characteristics, Low-Speed Mode

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{CC(I/O)} = 1.65 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}$ , see Table 10 for valid voltage level combinations,  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER        |                                                        | TEST CONDITIONS                                                                                | MIN | MAX | UNIT |

|------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-----|------|

| t <sub>LR</sub>  | Rise time                                              | $C_L$ = 200 pF to 600 pF,<br>10% to 90% of  V <sub>OH</sub> - V <sub>OL</sub>   (see Figure 1) | 75  | 300 | ns   |

| t <sub>LF</sub>  | Fall time                                              | $C_L = 200 \text{ pF to } 600 \text{ pF},$<br>90% to 10% of $ V_{OH} - V_{OL} $ (see Figure 1) | 75  | 300 | ns   |

| LRFM             | Differential rise/fall time matching $(t_{LR}/t_{LF})$ | Excluding the first transition from idle state                                                 | 80  | 125 | %    |

| V <sub>CRS</sub> | Output signal crossover voltage                        | Excluding the first transition from idle state (see Figure 10)                                 | 1.3 | 2   | V    |

(1) Test circuit, see Figure 13

(2) Driver timing in low-speed mode is not specified. Low-speed delay timings are dominated by the slow rise/fall times t<sub>LR</sub> and t<sub>LF</sub>.

#### DYNAMIC ELECTRICAL CHARACTERISTICS – ANALOG I/O PINS (D+, D–)<sup>(1) (2)</sup> Driver Timing, Full-Speed Mode

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{CC(I/O)} = 1.65 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}$ , see Table 10 for valid voltage level combinations,  $T_A = -40^{\circ}\text{C}$  to 85°C (unless otherwise noted)

|                       | PARAMETER                                                                                           | TEST CONDITIONS                                                 | MIN | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|------|

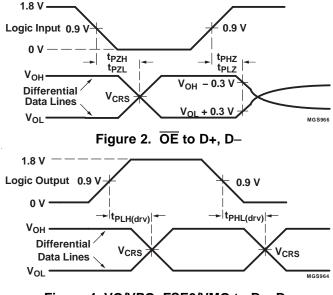

| t <sub>PLH(drv)</sub> | Driver propagation delay LOW to HIGH (see Figure 4)                                                 |                                                                 |     | 18  | 20   |

| t <sub>PHL(drv)</sub> | (VO/VPO, FSE0/VMO to D+, D-)                                                                        | HIGH to LOW (see Figure 4)                                      |     | 18  | ns   |

| t <sub>PHZ</sub>      | Driver disable delay ( $\overline{OE}$ to D+, D–)                                                   |                                                                 | 15  |     |      |

| t <sub>PLZ</sub>      | LOW to OFF (see Figure 2)                                                                           |                                                                 |     | 15  | ns   |

| t <sub>PZH</sub>      | $\mathbf{D}$ the problem of the problem ( $\overline{\mathbf{OE}}$ to $\mathbf{D}$ , $\mathbf{D}$ ) | OFF to HIGH (see Figure 2)                                      |     | 15  | ns   |

| t <sub>PZL</sub>      | Driver enable delay (OE to D+, D–)                                                                  | Driver enable delay (OE to D+, D–)<br>OFF to LOW (see Figure 2) |     |     |      |

(1) Test circuit, see Figure ?

(2) Driver timing in low-speed mode is not specified. Low-speed delay timings are dominated by the slow rise/fall times tLR and tLF.

#### ZHCS195-AUGUST 2011

#### DYNAMIC ELECTRICAL CHARACTERISTICS FOR ANALOG I/O PINS (D+, D–)<sup>(1)</sup> Receiver Timing, Full-Speed and Low-Speed Mode, Differential Receiver

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{CC(I/O)} = 1.65 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}$ , see Table 10 for valid voltage level combinations,  $T_A = -40^{\circ}$ C to 85°C (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS            | MIN MAX | UNIT |

|-----------------------|-----------------------------------|----------------------------|---------|------|

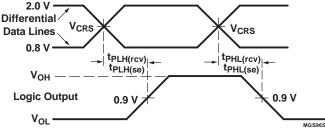

| t <sub>PLH(rcv)</sub> | Propagation delay (D. D. to PC)() | LOW to HIGH (see Figure 3) | 15      | 20   |

| t <sub>PHL(rcv)</sub> | Propagation delay (D+, D– to RCV) | HIGH to LOW (see Figure 3) | 15      | ns   |

(1) Test circuit, see Figure ?

#### DYNAMIC ELECTRICAL CHARACTERISTICS FOR ANALOG I/O PINS (D+, D–)<sup>(1)</sup> Receiver Timing, Full-Speed and Low-Speed Mode, Single-Ended Receiver

over recommended ranges of operating free-air temperature and supply voltage,  $V_{CC} = 4 \text{ V}$  to 5.5 V or  $V_{reg(3.3)} = 3 \text{ V}$  to 3.6 V,  $V_{CC(I/O)} = 1.65 \text{ V}$  to 3.6 V,  $V_{GND} = 0 \text{ V}$ , see Table 10 for valid voltage level combinations,  $T_A = -40^{\circ}$ C to 85°C (unless otherwise noted)

|                      | PARAMETER                              | TEST CONDITIONS            | MIN | MAX | UNIT |

|----------------------|----------------------------------------|----------------------------|-----|-----|------|

| t <sub>PLH(se)</sub> | Propagation dolory (D+ D, to )(D, )(M) | LOW to HIGH (see Figure 3) |     | 18  | ~~   |

| t <sub>PHL(se)</sub> | Propagation delay (D+, D– to VP, VM)   | HIGH to LOW (see Figure 3) |     | 18  | ns   |

(1) Test circuit, see Figure 13

Figure 1. Rise and Fall Times

Figure 3. D+, D- to RCV, VP, VM

Figure 4. VO/VPO, FSE0/VMO to D+, D-

www.ti.com.cn

#### **APPLICATION INFORMATION**

Figure 5. Load for Enable and Disable Times

- A. V = 0 V for  $t_{PZH}$ ,  $t_{PHZ}$

- $\mathsf{B}. \quad \mathsf{V} = \mathsf{V}_{\mathsf{reg}(3.3)} \text{ for } \mathsf{t}_{\mathsf{PZL}}, \, \mathsf{t}_{\mathsf{PLZ}}$

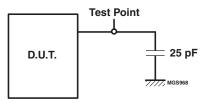

Figure 6. Load for VM, VP, and RCV

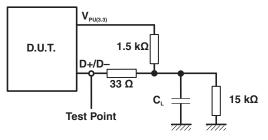

Figure 7. Load for D+, D-

- A. Full-speed mode: connected to D+

- B. Low-speed mode: Connected to D-

- C. Load capacitance:

- $C_L = 50 \text{ pF}$  or 125 pF (full-speed mode, minimum or maximum timing)

- $C_L = 200 \text{ pF}$  or 600 pF (low-speed mode, minimum or maximum timing)

## TUSB1106-Q1

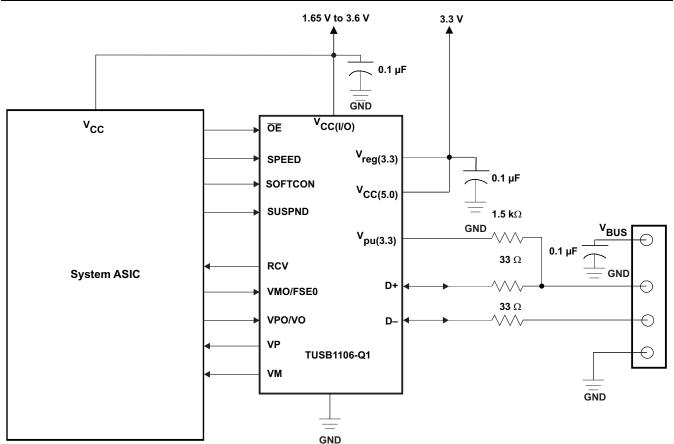

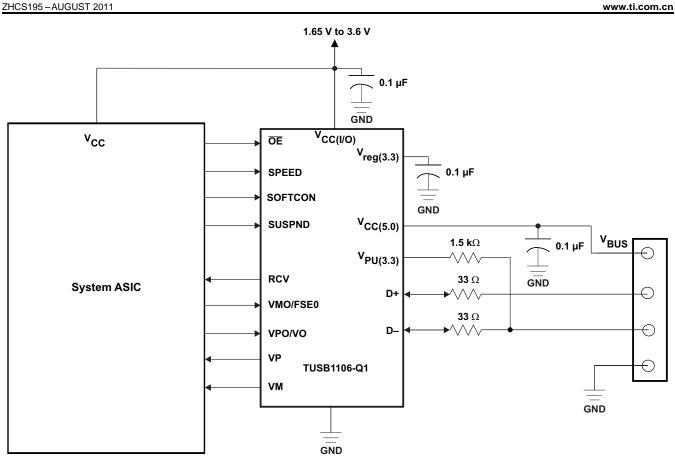

Figure 8. Peripheral-Side (Full-Speed) Regulator Bypass Mode

#### Peripheral-Side (Full-Speed) Regulator Bypass Mode

This mode is applicable when there is a 3.3-V supply already available on the board. The V<sub>BUS</sub> pin of the USB connector, if left unused at the peripheral side, should be terminated with a 0.1-µF capacitor. While operating at full speed, the 1.5-k $\Omega$  resistor must be connected between the D+ line and V<sub>PU(3.3)</sub> or an external 3.3-V supply. When the V<sub>CC(5.0)</sub> and the V<sub>reg(3.3)</sub> are connected together, the device operates at regulator bypass mode. This enables power savings since the regulator is turned off.

TEXAS INSTRUMENTS

ZHCS195-AUGUST 2011

www.ti.com.cn

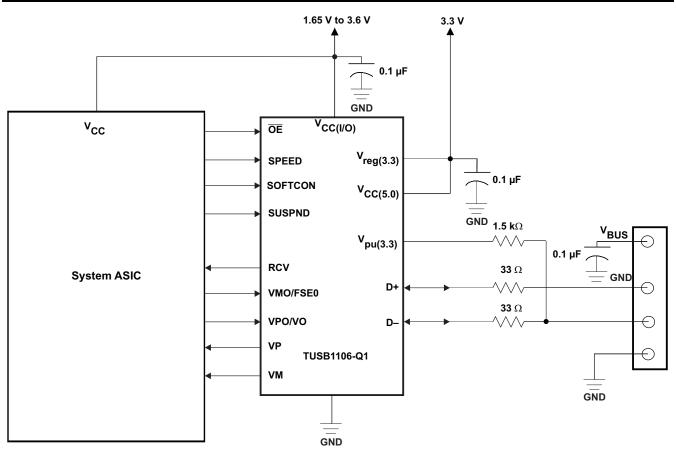

Figure 9. Peripheral-Side (Low-Speed) Regulator Bypass Mode

#### Peripheral-Side (Low-Speed) Regulator Bypass Mode

This mode is applicable when there is a 3.3-V supply already available on the board. The V<sub>BUS</sub> pin of the USB connector, if left unused at the peripheral side, should be terminated with a 0.1-µF capacitor. While operating at low speed, the 1.5-k $\Omega$  resistor must to be connected between the D– line and V<sub>PU(3.3)</sub> or an external 3.3-V supply. When the V<sub>CC(5.0)</sub> and the V<sub>reg(3.3)</sub> are connected together, the device operates at regulator bypass mode. This enables power savings since the regulator is turned off.

## TUSB1106-Q1

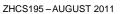

Figure 10. Peripheral-Side (Full-Speed) Internal Regulator Mode

#### Peripheral-Side (Full-Speed) Internal Regulator Mode

The USB side of the TUSB1106-Q1 can be powered from the V<sub>BUS</sub> line directly if a 3.3-V supply is not present on board. In this case, the internal regulator can be used to provide the 3.3-V supply for USB signaling. The V<sub>CC(5.0)</sub> is connected to the V<sub>BUS</sub>, which receives 5-V supply from the host, and generates the 3.3-V output at the V<sub>reg(3.3)</sub> pin. In this mode, it is important that both V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub> pins have individual bypass capacitors in the range of 0.1  $\mu$ F. Powering V<sub>CC(5.0)</sub> through the V<sub>BUS</sub> port of the USB connector realizes significant power saving for portable applications, such as cell phones, PDAs, etc. In this operating mode, the I<sub>CC(5.0)</sub> current is fed from the host. The USB-side power consumption, I<sub>CC(5.0)</sub> is 4 mA (with the regulator active), as opposed to logic-side I<sub>CC(10)</sub> of 1 mA under full-speed operation. While operating at full speed, the 1.5-k $\Omega$  resistor must be connected between the D+ line and the V<sub>PU(3.3)</sub> or an external 3.3-V supply.

NSTRUMENTS

FXAS

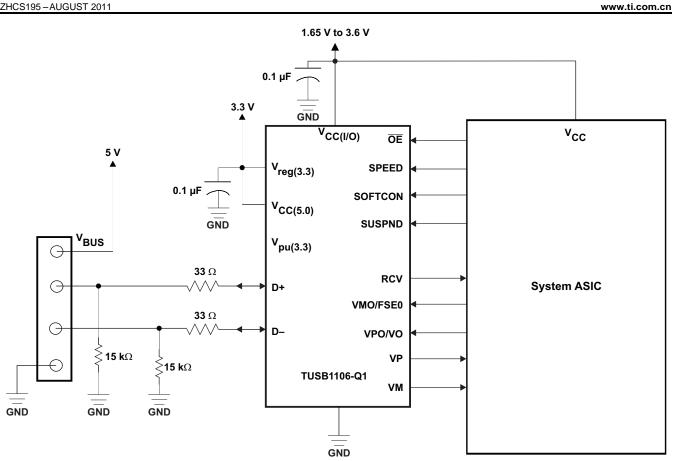

Figure 11. Peripheral-Side (Low-Speed) Internal Regulator Mode

## Peripheral-Side (Low-Speed) Internal Regulator Mode

The USB side of the TUSB1106-Q1 can be powered from the V<sub>BUS</sub> line directly if a 3.3-V supply is not present on board. In this case, the internal regulator can be used to provide the 3.3-V supply for the USB signaling. The V<sub>CC(5.0)</sub> is connected to the V<sub>BUS</sub>, which receives 5-V supply from the host, and generates the 3.3-V output at the V<sub>reg(3.3)</sub> pin. In this mode, it is important that both V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub> pins have individual bypass capacitors in the range of 0.1  $\mu$ F. Powering V<sub>CC(5.0)</sub> through the V<sub>BUS</sub> port of the USB connector realizes significant power saving for portable applications, such as cell phones, PDAs, etc. In this operating mode, the I<sub>CC(5.0)</sub> current is fed from the host side. The USB-side power consumption, I<sub>CC(5.0)</sub> is 4 mA (with the regulator active), as opposed to logic-side I<sub>CC(10)</sub> of 1 mA under full-speed operation. While operating at low speed, the 1.5-k $\Omega$  resistor must be connected between the D– line and the V<sub>PU(3.3)</sub> or an external 3.3-V supply.

ZHCS195-AUGUST 2011

www.ti.com.cn

#### 1.65 V to 3.6 V 0.1 μF GND V<sub>CC(I/O)</sub> v<sub>cc</sub> OE 5 V 5 V 0.1 µF V<sub>reg(3.3)</sub> SPEED GND SOFTCON V<sub>CC(5.0)</sub> SUSPND 0.1 µF v<sub>BUS</sub> V<sub>pu(3.3)</sub> θ GND **33** Ω RCV System ASIC Θ D+ VMO/FSE0 $\textbf{33}\,\Omega$ ( )D-VPO/VO ≥ 15 k $\Omega$ VP **15 k**Ω TUSB1106-Q1 VM GND GND GND GND

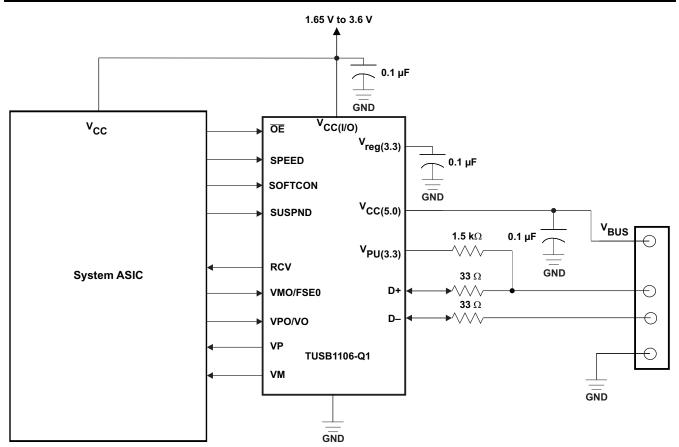

Figure 12. Host Side (V<sub>CC(5.0)</sub> Supplied From V<sub>BUS</sub> Pin)

## Host Side (V<sub>CC(5.0)</sub> Supplied From V<sub>BUS</sub> Pin)

If there is no 3.3-V supply on board, an external 5-V supply can support the USB-side power needs. When the  $V_{CC(5.0)}$  is connected to an external 5-V supply, the on-chip regulator generates the 3.3-V internal supply rail, which is used to drive the USB signaling levels at the USB side of the TUSB1106-Q1. The logic-side I/Os can operate at any voltage range from 1.65 V to 3.6 V.

ZHCS195-AUGUST 2011

Figure 13. Host-Side (3.3-V Supply Present) Internal Regulator Bypass Mode

### Host-Side (3.3-V Supply Present) Internal Regulator Bypass Mode

If a 3.3-V supply supports the USB-side power,  $V_{CC(5.0)}$  and  $V_{reg(3.3)}$  must to be tied together and connected to a 3.3-V supply. It also makes the regulator inactive.

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| TUSB1106IPWRQ1   | ACTIVE        | TSSOP        | PW                 | 16   | 2000           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM   | -40 to 85    | TU1106I                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

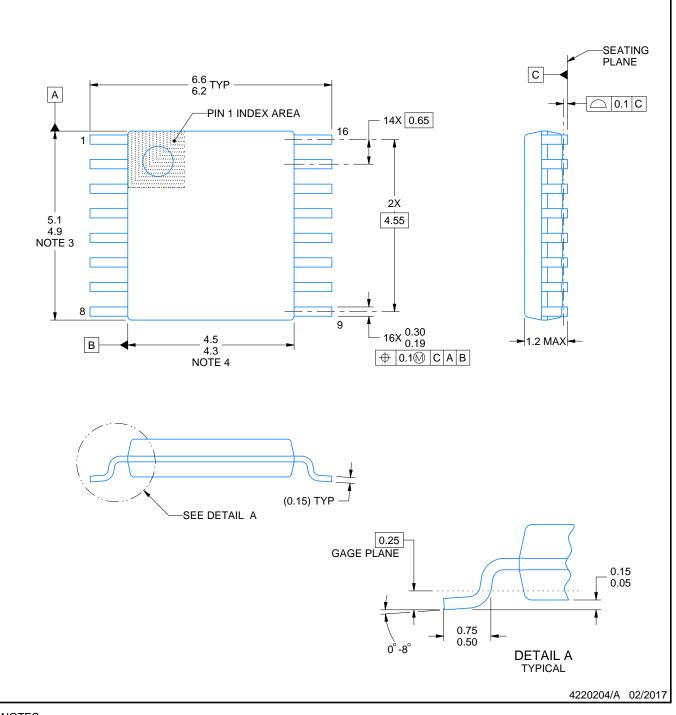

# **PW0016A**

# **PACKAGE OUTLINE**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

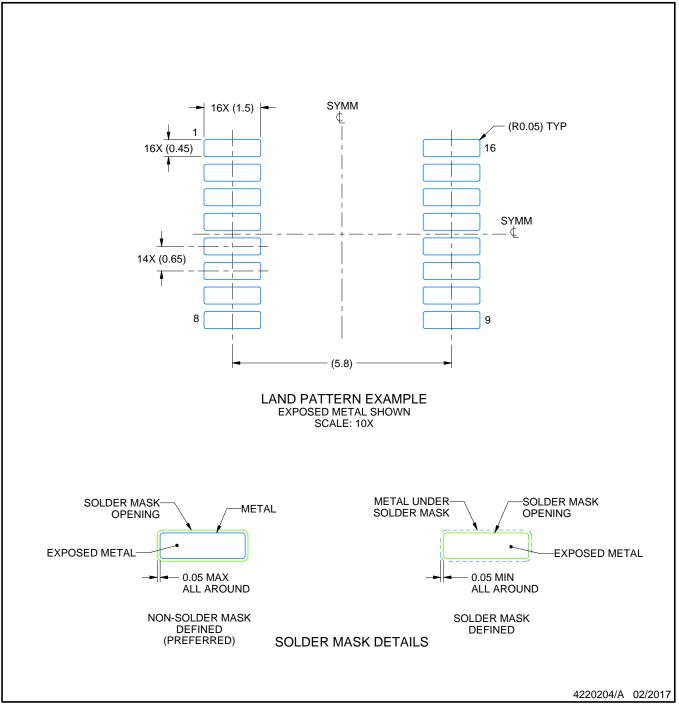

# PW0016A

# **EXAMPLE BOARD LAYOUT**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

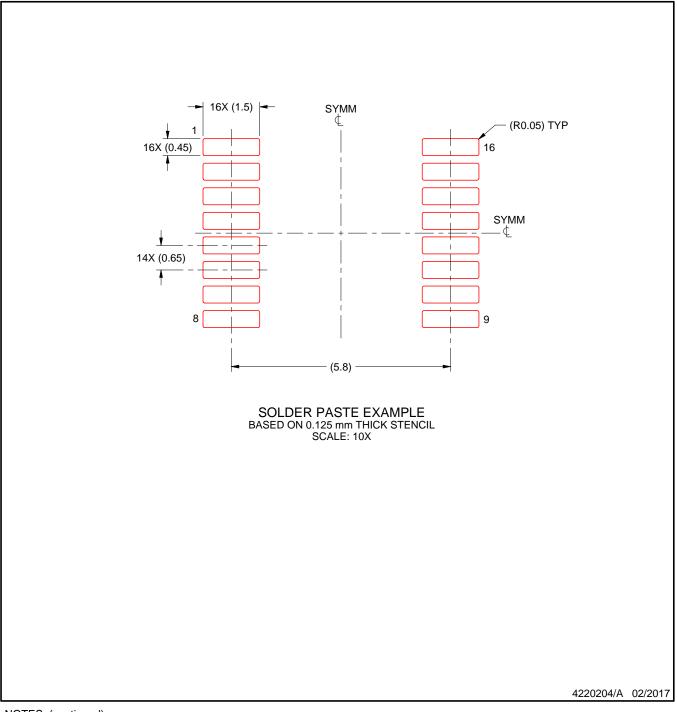

# PW0016A

# **EXAMPLE STENCIL DESIGN**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

Ⅱ 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、 验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用 所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权 许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司