# 16-BIT, 800 MSPS 2x-8x INTERPOLATING DUAL-CHANNEL DIGITAL-TO-ANALOG CONVERTER (DAC)

Check for Samples: DAC5689

# **FEATURES**

- Dual, 16-Bit, 800 MSPS DACs

- Dual, 16-Bit, 250 MSPS CMOS Input Data

- 16 Sample Input FIFO

- Flexible Input Data Bus Options

- High Performance

- 81 dBc ACLR WCDMA TM1 at 70 MHz

- Selectable 2x–8x Interpolation Filters

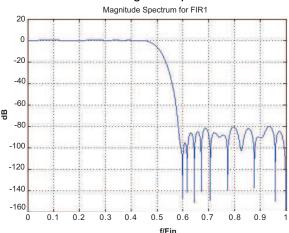

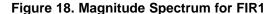

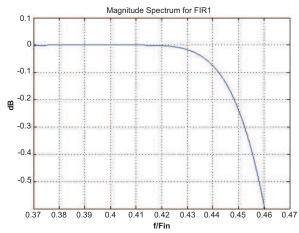

- Stop-band Attenuation > 80 dB

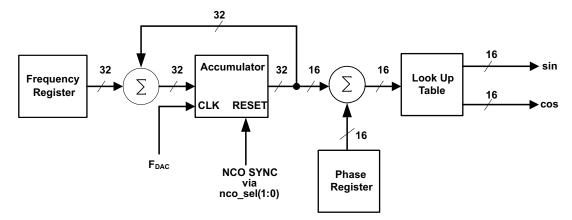

- Complex Mixer with 32-Bit NCO

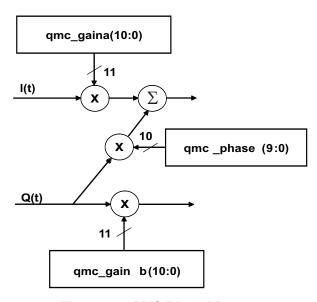

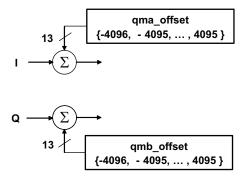

- Digital Quadrature Modulator Correction

- Gain, Phase and Offset Correction

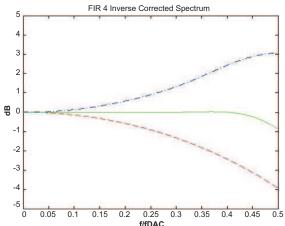

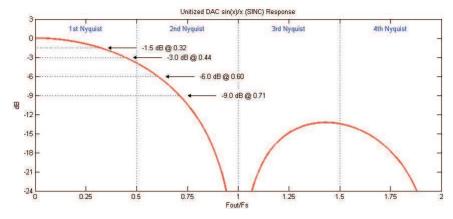

- Digital Inverse SINC Filter

- 3- or 4-Wire Serial Control Interface

- On Chip 1.2-V Reference

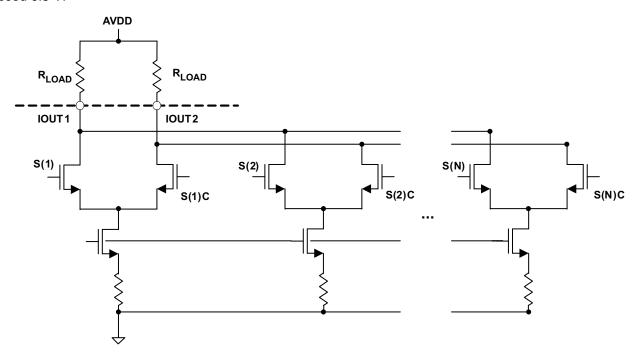

- Differential Scalable Output: 2 to 20 mA

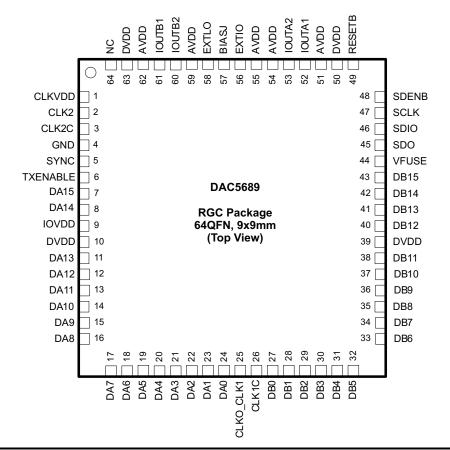

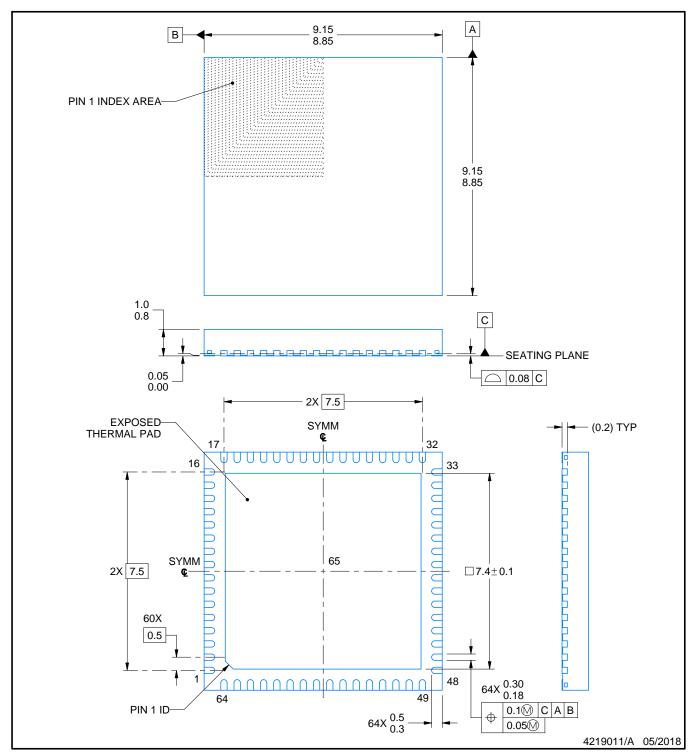

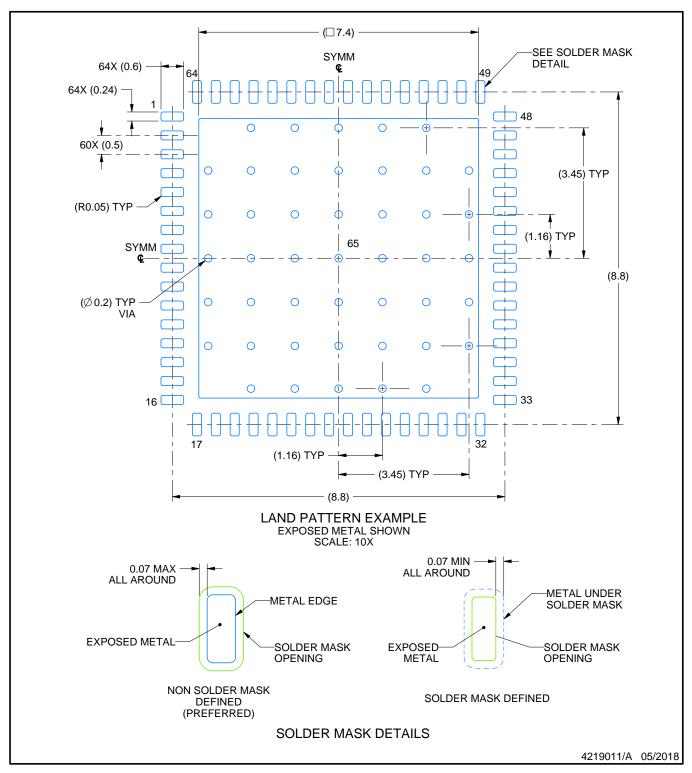

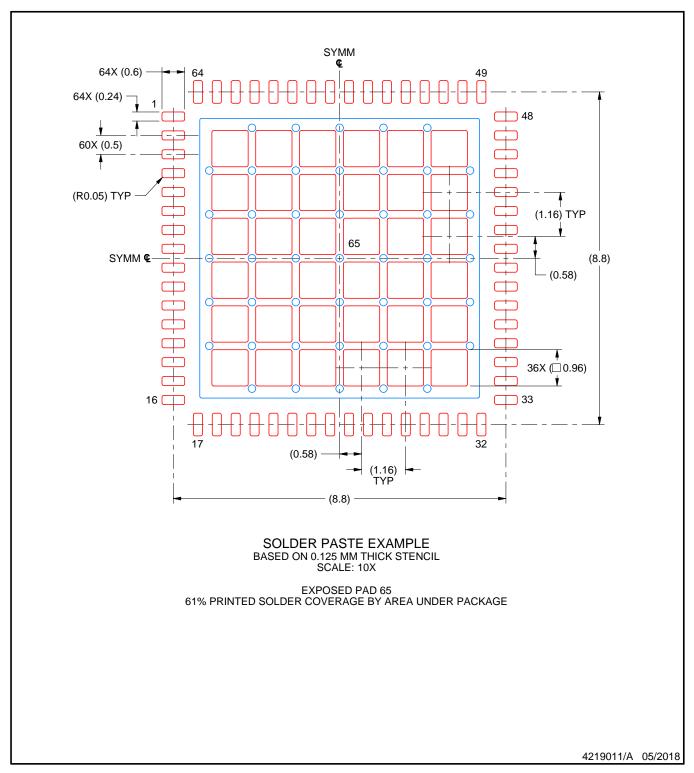

- Package: 64-pin 9×9mm QFN

#### **APPLICATIONS**

- Cellular Base Stations

- Broadband Wireless Access (BWA)

- WiMAX 802.16

- · Fixed Wireless Backhaul

- Cable Modem Termination System (CMTS)

#### DESCRIPTION

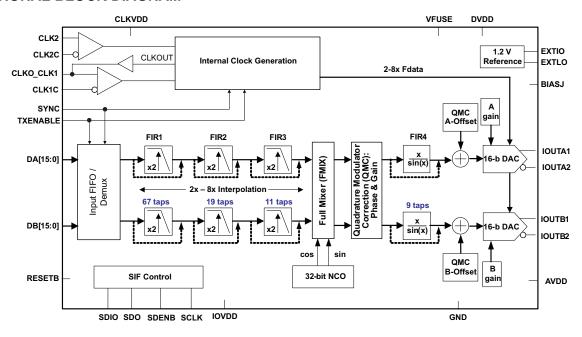

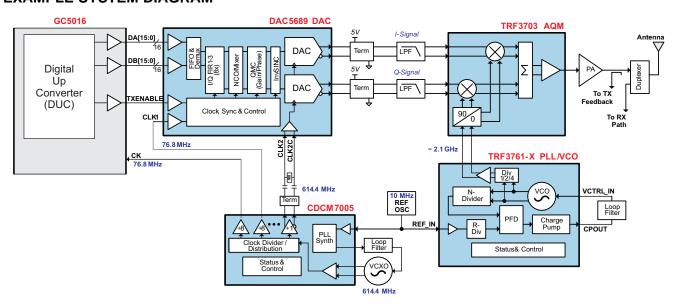

The DAC5689 is a dual-channel 16-bit 800 MSPS digital-to-analog converter (DAC) with dual CMOS digital data bus, integrated 2x-8x interpolation filters, a fine frequency mixer with 32-bit complex numerically controlled oscillator (NCO). compensation. and internal voltage reference. Different modes of operation enable or bypass various signal processing blocks. The DAC5689 offers superior linearity, noise and crosstalk performance.

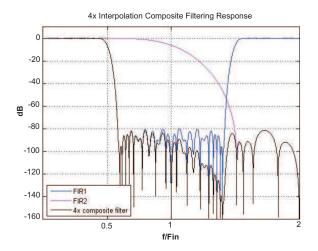

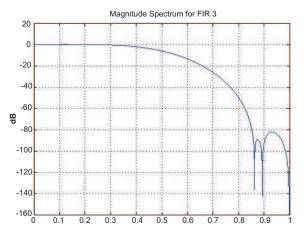

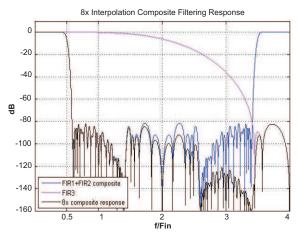

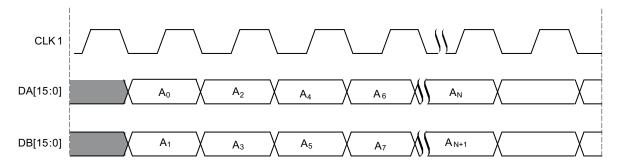

The DAC5689 dual CMOS data bus provides 250 MSPS input data transfer per DAC channel. Several input data options are available: dual-bus data, single-bus interleaved data, even and odd multiplexing at half-rate, and an input FIFO with either external or internal clock to ease interface timing. Input data can be interpolated 2x, 4x or 8x by on-board digital interpolating FIR filters with over 80 dB of stop-band attenuation.

The DAC5689 allows both complex or real output. An optional 32-bit NCO/mixer in complex mode provides frequency upconversion and the dual DAC output produces a complex Hilbert Transform pair. A digital Inverse SINC filter compensates for the natural DAC sin(x)/x frequency roll-off. The digital Quadrature Modulator Correction (QMC) feature allows IQ compensation of phase, gain and offset to maximize sideband rejection and minimize LO feed-through of an external quadrature modulator performing the final single sideband RF up-conversion.

The DAC5689 is pin upgradeable to the DAC5688 which includes a clock multiplying PLL. The DAC5689 is characterized for operation over the industrial temperature range of -40°C to 85°C and is available in a 64-pin 9x9mm QFN package.

# ORDERING INFORMATION(1) (2)

| ORDER CODE<br>T <sub>A</sub> = -40°C to 85°C | PACKAGE QTY<br>TAPE AND REEL FORMAT | PACKAGE<br>DRAWING/TYPE <sup>(3)</sup> (4) |  |  |

|----------------------------------------------|-------------------------------------|--------------------------------------------|--|--|

| DAC5689IRGCT                                 | 250                                 | RGC / 64QFN                                |  |  |

| DAC5689IRGCR                                 | 2000                                | Quad FlatpackNo-Lead                       |  |  |

- (1) For correct DAC5689 operation, bits [1:0] in register CONFIG26 need to be set to "10" at device startup (see Recommended Startup Sequence).

- (2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (3) Thermal Pad Size: 7,4 mm × 7,4 mm

- (4) MSL Peak Temperature: Level-3-260C-168 HR

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **FUNCTIONAL BLOCK DIAGRAM**

#### **PINOUT**

Submit Documentation Feedback

Copyright © 2009–2010, Texas Instruments Incorporated

# **TERMINAL FUNCTIONS**

| TERM      | IINAL                 |     | TERMINAL FUNCTIONS                                                                                                                                                                                                                                                                                                                                          |

|-----------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

| AVDD      | 51, 54, 55,<br>59, 62 | ı   | Analog supply voltage. (3.3V)                                                                                                                                                                                                                                                                                                                               |

| BIASJ     | 57                    | 0   | Full-scale output current bias. For 20mA full-scale output current, connect a 960 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                 |

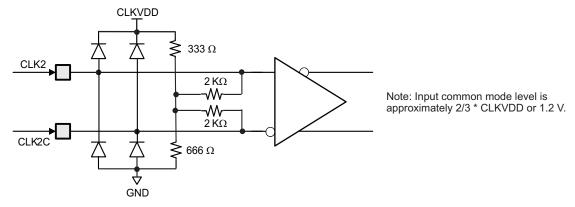

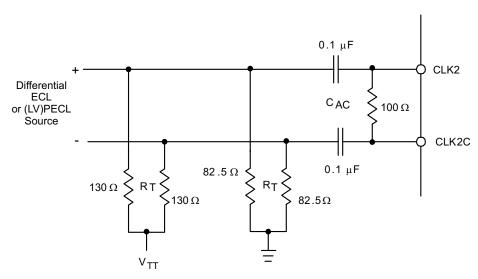

| CLK2      | 2                     | ı   | Positive DAC clock input. Accepts frequencies up to 800MHz.                                                                                                                                                                                                                                                                                                 |

| CLK2C     | 3                     | ı   | Complementary CLK2 input.                                                                                                                                                                                                                                                                                                                                   |

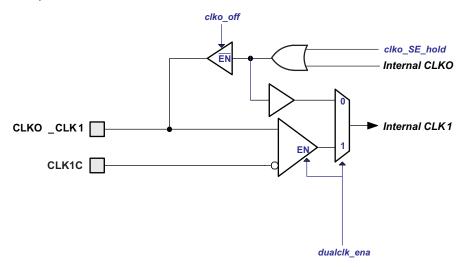

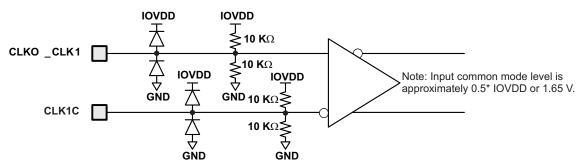

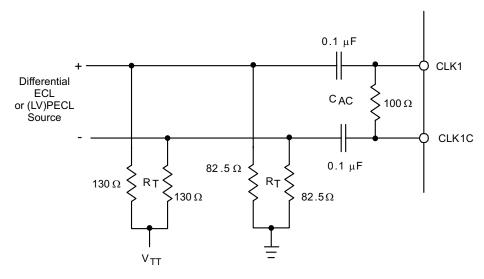

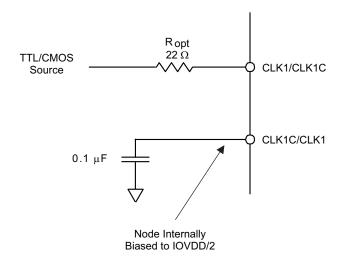

| CLKO_CLK1 | 25                    | I/O | In Dual Clock Mode can be used to provide the lower frequency input clock. The lower frequency clock can be differential or single-ended. If single-ended CLK1 can be used as the clock input. CLK1C must be AC coupled to GND in this case. Optionally provides (CLKO) output for data bus source. Internal pull-down.                                     |

| CLK1C     | 26                    | I/O | In Dual Clock Mode can be used to provide the lower frequency input clock. The lower frequency clock can be differential or single-ended. If differential, CLK1C is the complementary clock input. If single-ended it can be used as the clock input. CLKO_CLK1 must be AC coupled to GND in this case. Internal pull-down.                                 |

| CLKVDD    | 1                     | I   | Internal clock buffer supply voltage. (1.8V) It is recommended to isolate this supply from DVDD.                                                                                                                                                                                                                                                            |

| DA[150]   | 7, 8, 11–24           | I   | A-Channel Data Bits 0 through 15.  DA15 is most significant data bit (MSB) – pin 7  DA0 is least significant data bit (LSB) – pin 24  Internal pull-down. The order of bus can be reversed via CONFIG4 <b>reva</b> bit.                                                                                                                                     |

| DB[150]   | 40–43,<br>27–38       | I   | B-Channel Data Bits 0 through 15.  DB15 is most significant data bit (MSB) – pin 43  DB0 is least significant data bit (LSB) – pin 27  Internal pull-down. The order of bus can be reversed via CONFIG4 <b>revb</b> bit.                                                                                                                                    |

| DVDD      | 10, 39, 50,<br>63     | ı   | Digital supply voltage. (1.8V) For best performance it is recommended to isolate pins 10 and 39 from all other 1.8V supplies.                                                                                                                                                                                                                               |

| EXTIO     | 56                    | I/O | Used as external reference input when internal reference is disabled (i.e., EXTLO connected to AVDD). Used as internal reference output when EXTLO = GND, requires a 0.1µF decoupling capacitor to GND when used as reference output                                                                                                                        |

| EXTLO     | 58                    | 0   | Connect to GND for internal reference, or AVDD for external reference.                                                                                                                                                                                                                                                                                      |

| GND       | 4,<br>Thermal<br>Pad  | ı   | Pin 4 and the Thermal Pad located on the bottom of the QFN package is ground for AVDD, DVDD and IOVDD supplies.                                                                                                                                                                                                                                             |

| IOUTA1    | 52                    | 0   | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current sink and the least positive voltage on the IOUTA1 pin. Similarly, a 0xFFFF data input results in a 0 mA current sink and the most positive voltage on the IOUTA1 pin. In single DAC mode, outputs appear on the IOUTA1/A2 pair only. |

| IOUTA2    | 53                    | 0   | A-Channel DAC complementary current output. The IOUTA2 has the opposite behavior of the IOUTA1 described above. An input data value of 0x0000 results in a 0mA sink and the most positive voltage on the IOUTA2 pin.                                                                                                                                        |

| IOUTB1    | 61                    | 0   | B-Channel DAC current output. Refer to IOUTA1 description above.                                                                                                                                                                                                                                                                                            |

| IOUTB2    | 60                    | 0   | B-Channel DAC complementary current output. Refer to IOUTA2 description above.                                                                                                                                                                                                                                                                              |

| IOVDD     | 9                     | I   | 3.3V supply voltage for all digital I/O. Note: This supply input should remain at 3.3V regardless of the 1.8V or 3.3V selectable digital input switching thresholds via CONFIG26 <b>io_1p8_3p3</b> .                                                                                                                                                        |

| NC        | 64                    | I   | No connect. Leave open for proper operation.                                                                                                                                                                                                                                                                                                                |

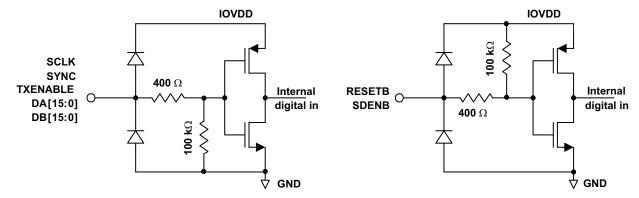

| SYNC      | 5                     | I   | Optional SYNC input for internal clock dividers, FIFO, NCO and QMC blocks. Internal pull-down.                                                                                                                                                                                                                                                              |

| RESETB    | 49                    | ı   | Resets the chip when low. Internal pull-up.                                                                                                                                                                                                                                                                                                                 |

| SCLK      | 47                    | ı   | Serial interface clock. Internal pull-down.                                                                                                                                                                                                                                                                                                                 |

| SDENB     | 48                    | I   | Active low serial data enable, always an input to the DAC5689. Internal pull-up.                                                                                                                                                                                                                                                                            |

| SDIO      | 46                    | I/O | Bi-directional serial data in 3-pin mode (default). In 4-pin interface mode (CONFIG5 <b>sif4</b> ), the SDIO pin is an input only. Internal pull-down.                                                                                                                                                                                                      |

| SDO       | 45                    | 0   | Uni-directional serial interface data in 4-pin mode (CONFIG5 <b>sif4</b> ). The SDO pin is 3-stated in 3-pin interface mode (default). Internal pull-down.                                                                                                                                                                                                  |

| TXENABLE  | 6                     | I   | Transmit enable input. Internal pull-down. TXENABLE must be high for the DATA to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data is ignored.                                                                                                                                                  |

# **TERMINAL FUNCTIONS (continued)**

| TERM  | INAL | 1/0 | DESCRIPTION                                                                                                                                 |  |

|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NO.  | 1/0 | DESCRIPTION                                                                                                                                 |  |

| VFUSE | 44   | I   | Digital supply voltage. (1.8V) This supply pin is also used for factory fuse programming. <b>Connect to DVDD pins for normal operation.</b> |  |

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                     |                                       | VALUE                | UNIT |

|-------------------------------------|---------------------------------------|----------------------|------|

| Supply voltage range                | DVDD <sup>(2)</sup>                   | -0.5 to 2.3          | V    |

|                                     | VFUSE <sup>(2)</sup>                  | -0.5 to 2.3          | V    |

|                                     | CLKVDD <sup>(2)</sup>                 | -0.5 to 2.3          | V    |

|                                     | AVDD <sup>(2)</sup>                   | -0.5 to 4            | V    |

|                                     | IOVDD <sup>(2)</sup>                  | -0.5 to 4            | V    |

| Supply voltage range                | AVDD to DVDD                          | -2 to 2.6            | V    |

|                                     | CLKVDD to DVDD                        | -0.5 to 0.5          | V    |

|                                     | IOVDD to AVDD                         | -0.5 to 0.5          | V    |

|                                     | CLK2, CLK2C <sup>(2)</sup>            | -0.5 to CLKVDD + 0.5 | V    |

|                                     | CLKO_CLK1, CLK1C, SLEEP, TXENABLE (2) | -0.5 to IOVDD + 0.5  | V    |

|                                     | DA[150] ,DB[150] <sup>(2)</sup>       | -0.5 to IOVDD + 0.5  | V    |

|                                     | SDO, SDIO, SCLK, SDENB, RESETB (2)    | -0.5 to IOVDD + 0.5  | V    |

|                                     | IOUTA1/B1, IOUTA2/B2 (2)              | -0.5 to AVDD + 0.5   | V    |

|                                     | EXTIO, EXTLO, BIASJ (2)               | -0.5 to AVDD + 0.5   | V    |

| Peak input current (any input)      | ·                                     | 20 mA                | mA   |

| Peak total input current (all input | ts)                                   | –30 mA               | mA   |

| Operating free-air temperature r    | ange, T <sub>A</sub> : DAC5689I       | -40 to 85            | °C   |

| Storage temperature range           |                                       | -65 to 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

over operating free-air temperature range (unless otherwise noted)

|                   |                                       | DAC5689 |       |

|-------------------|---------------------------------------|---------|-------|

|                   | THERMAL METRIC                        | RGC     | UNITS |

|                   |                                       | 64 LEAD |       |

| 0                 | Theta junction-to-ambient (still air) | 22      | 0000  |

| $\theta_{\sf JA}$ | Theta junction-to-ambient (150 lfm)   | 15      | °C/W  |

| $\theta_{JB}$     | Theta junction-to-board               | 3.5     | °C/W  |

| TJ                | Maximum junction temperature (1) (2)  | 125     | °C    |

| ΨЈТ               | Psi junction-to-top of package        | 0.2     | °C/W  |

<sup>(1)</sup> Air flow or heat sinking reduces  $\theta_{JA}$  and may be required for sustained operation at 85°C under maximum operating conditions. (2) It is strongly recommended to solder the device thermal pad to the board ground plane.

Measured with respect to GND.

# **ELECTRICAL CHARACTERISTICS (DC Specifications)**

over recommended operating free-air temperature range, AVDD, IOVDD = 3.3 V, DVDD, CLKVDD = 1.8 V, lout<sub>FS</sub> = 20 mA

|                    | PARAMETER                              | TEST CONDITIONS                                                                                                    | MIN            | TYP    | MAX            | UNIT             |

|--------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|--------|----------------|------------------|

| RESOL              | UTION                                  |                                                                                                                    | 16             |        |                | Bits             |

| DC AC              | CURACY                                 |                                                                                                                    |                |        |                |                  |

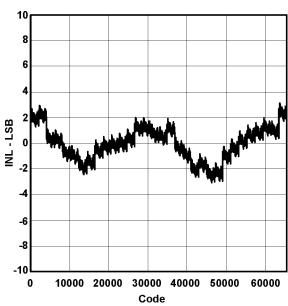

| INL                | Integral nonlinearity                  | 1 LSB = $IOUT_{FS}/2^{16}$                                                                                         |                | ±4     |                | LSB              |

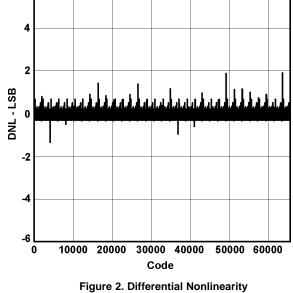

| DNL                | Differential nonlinearity              |                                                                                                                    |                | ±2     |                | LSB              |

| ANALO              | G OUTPUT                               |                                                                                                                    |                |        |                |                  |

|                    | Coarse gain linearity                  |                                                                                                                    |                | ± 0.04 |                | LSB              |

|                    | Offset error mid code offset           |                                                                                                                    |                | 0.01   |                | %FSR             |

|                    | Gain error                             | With external reference                                                                                            |                | 1      |                | %FSR             |

|                    |                                        | With internal reference                                                                                            |                | 0.7    |                | %FSR             |

| -                  | Gain mismatch                          | With internal reference, dual DAC mode                                                                             | -2             |        | 2              | %FSR             |

| -                  | Minimum full scale output current      | Nominal full-scale current, IOUT <sub>FS</sub> = 16 x IBIAS current.                                               |                | 2      |                | _                |

|                    | Maximum full scale output current      |                                                                                                                    |                | 20     |                | mA               |

|                    | Output compliance range <sup>(1)</sup> | IOUT <sub>FS</sub> = 20 mA                                                                                         | AVDD<br>- 0.5V |        | AVDD<br>+ 0.5V | V                |

|                    | Output resistance                      |                                                                                                                    |                | 300    |                | kΩ               |

|                    | Output capacitance                     |                                                                                                                    |                | 5      |                | pF               |

| REFER              | ENCE OUTPUT                            |                                                                                                                    |                |        |                |                  |

| $V_{REF}$          | Reference output voltage               | Internal Reference Mode                                                                                            | 1.14           | 1.2    | 1.26           | V                |

|                    | Reference output current (2)           |                                                                                                                    |                | 100    |                | nA               |

| REFER              | ENCE INPUT                             |                                                                                                                    | *              |        |                |                  |

| V <sub>EXTIO</sub> | Input voltage range                    | External Reference Mode                                                                                            | 0.1            |        | 1.25           | V                |

| EXTIG              | Input resistance                       |                                                                                                                    |                | 1      |                | ΜΩ               |

|                    |                                        | CONFIG26: isbiaslpf_a and isbiaslpf_b = 0                                                                          |                | 95     |                |                  |

|                    | Small signal bandwidth                 | CONFIG26: isbiaslpf_a and isbiaslpf_b = 1                                                                          |                | 472    |                | kHz              |

|                    | Input capacitance                      |                                                                                                                    |                | 100    |                | pF               |

| TEMPE              | RATURE COEFFICIENTS                    |                                                                                                                    |                |        |                |                  |

|                    | Offset drift                           |                                                                                                                    |                | ±1     |                |                  |

|                    |                                        | With external reference                                                                                            |                | ±15    |                | ppm of<br>FSR/°C |

|                    | Gain drift                             | With internal reference                                                                                            |                | ±30    |                | F3R/ C           |

|                    | Reference voltage drift                |                                                                                                                    |                | ±8     |                | ppm/°C           |

| POWER              | SUPPLY                                 |                                                                                                                    |                |        |                |                  |

|                    | AVDD, IOVDD                            |                                                                                                                    | 3.0            | 3.3    | 3.6            | V                |

|                    | DVDD, CLKVDD                           |                                                                                                                    | 1.7            | 1.8    | 1.9            | V                |

| PSRR               | Power supply rejection ratio           | DC tested                                                                                                          | -0.2           |        | 0.2            | %FSR/V           |

|                    | AVDD + IOVDD current, 3.3V             | Mode 1: x8 Interp, QMC = off, ISINC = off,                                                                         |                | 140    |                | mA               |

|                    | DVDD + CLKVDD current, 1.8V            | DAC A+B on, F <sub>IN</sub> = 5 MHz Tone, NCO = 145 MHz,<br>F <sub>OUT</sub> = 150 MHz, F <sub>DAC</sub> = 500 MHz |                | 430    |                | mA               |

|                    | Power Dissipation                      | 1 OUT = 130 WI12, 1 DAC = 300 WI12                                                                                 |                | 1240   |                | mW               |

|                    | AVDD + IOVDD current, 3.3V             | Mode 2: x8 Interp, QMC = on, ISINC = on,                                                                           |                | 140    |                | mA               |

|                    | DVDD + CLKVDD current, 1.8V            | DAC A+B on, F <sub>IN</sub> = 5 MHz Tone, NCO = 91 MHz                                                             |                | 520    |                | mA               |

|                    | Power dissipation                      | F <sub>OUT</sub> = 96 MHz, F <sub>DAC</sub> = 614.4 MHz                                                            |                | 1400   |                | mW               |

| Р                  | AVDD + IOVDD current, 3.3V             | Mode 3 (Max): x4 Interp, QMC = on, ISINC = on,                                                                     |                | 140    |                | mA               |

|                    | DVDD + CLKVDD current, 1.8V            | DAC A+B on, F <sub>IN</sub> = 5 MHz Tone, NCO = 135 MHz,                                                           |                | 680    |                | mA               |

|                    | Power dissipation                      | F <sub>OUT</sub> = 140 MHz, F <sub>DAC</sub> = 800 MHz                                                             |                | 1690   | 1950           | mW               |

|                    | AVDD + IOVDD current, 3.3V             | Mode 4 (Sleep): x8 Interp, QMC = off, ISINC = off,                                                                 |                | 12     |                | mA               |

|                    | DVDD + CLKVDD current, 1.8V            | DAC A+B off, F <sub>IN</sub> = 5 MHz Tone, NCO = off,                                                              |                | 15     |                | mA               |

|                    | Power dissipation                      | $F_{OUT} = off, F_{DAC} = 800 MHz,$                                                                                |                | 65     | 100            | mW               |

<sup>(1)</sup> The upper limit of the output compliance is determined by the CMOS process. Exceeding this limit may result in transistor breakdown, resulting in reduced reliability of the DAC5689 device. The lower limit of the output compliance is determined by the load resistors and full-scale output current. Exceeding the upper limit adversely affects distortion performance and integral nonlinearity.

<sup>(2)</sup> Use an external buffer amplifier with high impedance input to drive any external load.

# **ELECTRICAL CHARACTERISTICS (AC Specifications)**

Over recommended operating free-air temperature range, AVDD, IOVDD = 3.3 V, DVDD, CLKVDD = 1.8 V, IOUT<sub>FS</sub> = 20 mA

|                      | PARAMETER                                                    | DITIONS                                                                                                                                 | MIN                                          | TYP    | MAX  | UNIT |        |  |

|----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------|------|------|--------|--|

| ANALO                | G OUTPUT <sup>(1)</sup>                                      |                                                                                                                                         |                                              |        |      | ļ    |        |  |

| f <sub>DAC</sub>     | Maximum output update rate                                   |                                                                                                                                         |                                              | 800    |      |      | MSPS   |  |

| t <sub>s(DAC)</sub>  | Output settling time to 0.1%                                 | Transition: Code 0x0000 to 0xFFFF                                                                                                       |                                              |        | 10.4 |      | ns     |  |

| t <sub>pd</sub>      | Output propagation delay                                     | DAC outputs are updated on falling edge of Does not include Digital Latency (see below)                                                 |                                              |        | 2    |      | ns     |  |

| t <sub>r(IOUT)</sub> | Output rise time                                             | 10% to 90%                                                                                                                              |                                              |        | 220  |      | ps     |  |

| t <sub>f(IOUT)</sub> | Output fall time                                             | 90% to 10%                                                                                                                              |                                              |        | 220  |      | ps     |  |

|                      |                                                              | No Interp, NCO off, QMC off, ISINC = off                                                                                                |                                              |        | 109  |      |        |  |

|                      |                                                              | x2 Interpolation, NCO off, QMC off, ISINC =                                                                                             | off                                          |        | 172  |      |        |  |

|                      |                                                              | x4 Interpolation, NCO off, QMC off, ISINC =                                                                                             | off                                          |        | 276  |      | DAC    |  |

|                      | Digital latency                                              | x8 Interpolation, NCO off, QMC off, ISINC =                                                                                             | off                                          |        | 488  |      | clock  |  |

|                      |                                                              | x8 Interpolation, NCO on, QMC off, ISINC =                                                                                              | off                                          |        | 512  |      | cycles |  |

|                      |                                                              | x8 Interpolation, NCO on, QMC on, ISINC =                                                                                               | off                                          |        | 528  |      |        |  |

|                      |                                                              | x8 Interpolation, NCO on, QMC on, ISINC =                                                                                               |                                              | 548    |      |      |        |  |

| AC PER               | RFORMANCE (2)                                                |                                                                                                                                         |                                              |        |      |      |        |  |

|                      |                                                              | x4 Interp, CLK2 = 800 MHz,                                                                                                              | F <sub>OUT</sub> = 10.1 MHz                  |        | 83   |      |        |  |

| SFDR                 | Spurious free dynamic range                                  | DAC A+B on,<br>0 dBFS Single tone, F <sub>OUT</sub> = F <sub>IN</sub><br>First Nyquist Zone < f <sub>DATA</sub> /2                      | F <sub>OUT</sub> = 20.1 MHz                  |        | 79   |      | dBc    |  |

|                      |                                                              | x4 Interp, CLK2 = 800 MHz,                                                                                                              | NCO= 10 MHz, F <sub>OUT</sub> = 20.1 MHz     |        | 72   |      |        |  |

| SNR                  | Signal to noise ratio                                        | DAC A+B on,<br>0 dBFS Single tone, $F_{IN} = 10.1$ MHz,<br>$F_{OUT} = F_{IN} + NCO$                                                     | NCO= 60 MHz, F <sub>OUT</sub> = 70.1 MHz     |        | 68   |      | dBc    |  |

| SINK                 | Signal-to-noise ratio                                        |                                                                                                                                         | NCO= 140 MHz, F <sub>OUT</sub> = 150.1 MHz   |        | 64   |      | UBC    |  |

|                      |                                                              |                                                                                                                                         | NCO= 290 MHz, F <sub>OUT</sub> = 300.1 MHz   |        | 57   |      |        |  |

|                      | Third-order                                                  | x4 Interp, CLK2 = 800 MHz,                                                                                                              | NCO= 40 MHz, F <sub>OUT</sub> = 51±0.5 MHz   |        | 85   |      |        |  |

| IMD3                 | Two-Tone intermodulation                                     | DAC A+B on,<br>F <sub>IN</sub> = 10.5 and 11. 5 MHz,                                                                                    | NCO= 60 MHz, $F_{OUT}$ = 71±0.5 MHz          |        | 83   |      | dBc    |  |

|                      | (Each tone at –6 dBFS)                                       | F <sub>OUT</sub> = F <sub>IN</sub> + NCO                                                                                                |                                              |        |      |      |        |  |

| IMD                  | Four-tone Intermodulation to Nyquist (Each tone at –12 dBFS) | $\times 4$ Interp, CLK2 = 800 MHz, DAC A+B on, $F_{IN}$ = 9.8, 10.4, 11.6 and 12.2 MHz (600kHz $F_{OUT}$ = $F_{IN}$ + NCO = 140±1.2 MHz | spacing), NCO = 129 MHz,                     |        | 73   |      | dBc    |  |

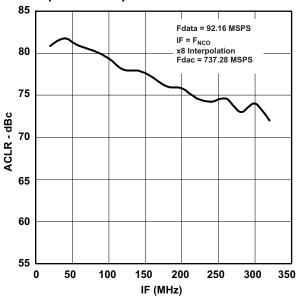

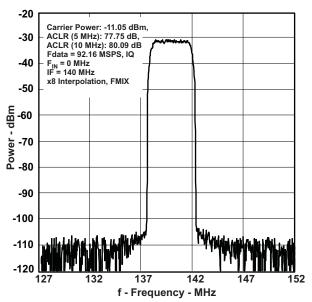

|                      |                                                              | x8 Interp, CLK2 = 737.28 MHz,<br>DAC A+B on, F <sub>IN</sub> = 23 .04 MHz, NCO = off                                                    | Single Carrier, F <sub>OUT</sub> = 23.04 MHz |        | 81   |      |        |  |

| ACLR                 | Adjacent channel                                             | x8 Interp, CLK2 = 737.28 MHz,                                                                                                           | Single Carrier, F <sub>OUT</sub> = 70MHz     |        | 81   |      | dBc    |  |

| (-)                  | leakage ratio                                                | DAC A+B on, $F_{IN}$ = Baseband I/Q, $F_{OUT}$ = NCO                                                                                    | Single Carrier, F <sub>OUT</sub> = 140MHz    |        | 78   |      |        |  |

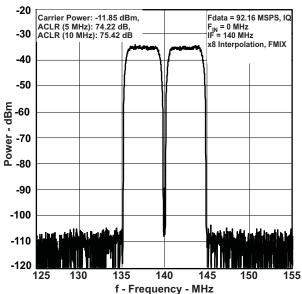

|                      |                                                              |                                                                                                                                         | Four Carrier, F <sub>OUT</sub> = 140MHz      | MHz 70 |      |      |        |  |

|                      | Noise fleer                                                  | x8 Interp, CLK2 = 737.28 MHz,                                                                                                           | Single Carrier Noise Floor                   |        | 101  |      | dBm    |  |

|                      | Noise floor,<br>noise spectral density                       | DAC A+B on,<br>F <sub>IN</sub> = F <sub>OUT</sub> = Baseband I/Q,                                                                       | Single Carrier NSD in 1 MHz BW               |        | 161  |      | dBm/Hz |  |

|                      | (NSD)                                                        | 50 MHz offset, 1 MHz BW                                                                                                                 | Four Carrier Noise Floor                     |        | 101  |      | dBm    |  |

|                      | • •                                                          |                                                                                                                                         | Four Carrier NSD in 1 MHz BW                 |        | 161  |      | dBm/Hz |  |

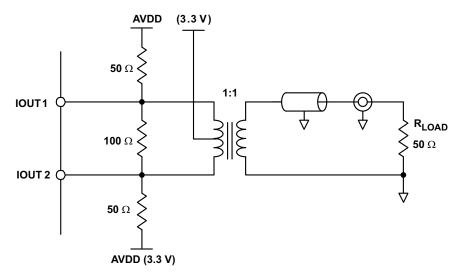

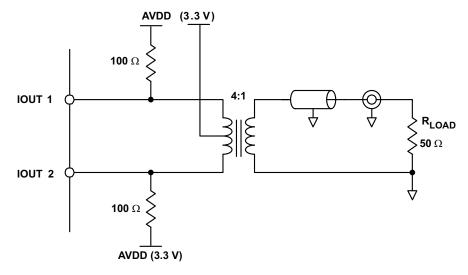

<sup>(1)</sup> Measured differential across IOUTA1 and IOUTA2 or IOUTB1 and IOUTB2 with 25  $\Omega$  each to AVDD. (2) 4:1 transformer output termination,  $50\Omega$  doubly terminated load (3) W-CDMA with 3.84 MHz BW, 5-MHz spacing, centered at IF. TESTMODEL 1, 10 ms

# **ELECTRICAL CHARACTERISTICS (Digital Specifications)**

Over recommended operating free-air temperature range, AVDD, IOVDD = 3.3V, DVDD, CLKVDD = 1.8V, lout<sub>ES</sub> = 20 mA

|                       | PARAMETER                                            | TEST CONDITIONS                                                              | MIN                                 | TYP      | MAX      | UNIT |

|-----------------------|------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|----------|----------|------|

| CMOS IN               | TERFACE: SDO, SDIO, SCLK, SDENB, RESETB              | , DA[15:0], DB[15:0], SYNC, TXENABLE, C                                      | LKO_CLK1                            |          |          |      |

| \ /                   | I link level in a track of                           | CONFIG26 io_1p8_3p3 = 0 (3.3V levels)                                        | 2.30                                |          |          | W    |

| V <sub>IH</sub>       | High-level input voltage                             | CONFIG26 io_1p8_3p3 = 1 (1.8V levels)                                        | 1.25                                |          |          | V    |

|                       | Law law Law Arabana                                  | CONFIG26 io_1p8_3p3 = 0 (3.3V levels)                                        |                                     |          | 1.00     | W    |

| $V_{IL}$              | Low-level input voltage                              | CONFIG26 io_1p8_3p3 = 1 (1.8V levels)                                        |                                     |          | 0.54     | V    |

| I <sub>IH</sub>       | High-level input current                             |                                                                              |                                     | ±20      |          | μА   |

| I <sub>IL</sub>       | Low-level input current                              |                                                                              |                                     | ±20      |          | μА   |

| Cı                    | CMOS Input capacitance                               |                                                                              |                                     | 2        |          | pF   |

| .,                    | SDO, SDIO, CLKO                                      | I <sub>LOAD</sub> = -100 μA                                                  | IOVDD –<br>0.2                      |          |          |      |

| V <sub>OH</sub>       | SDO, SDIO, CLKO                                      | I <sub>LOAD</sub> = -2 mA                                                    | 0.8 ×<br>IOVDD                      |          |          | V    |

|                       | SDO, SDIO, CLKO                                      | I <sub>LOAD</sub> = 100 μA                                                   |                                     |          | 0.2      | .,   |

| V <sub>OL</sub>       | SDO, SDIO, CLKO                                      | I <sub>LOAD</sub> = 2 mA                                                     |                                     |          | 0.5      | V    |

|                       | Input data rate                                      |                                                                              | 0                                   |          | 250      | MSPS |

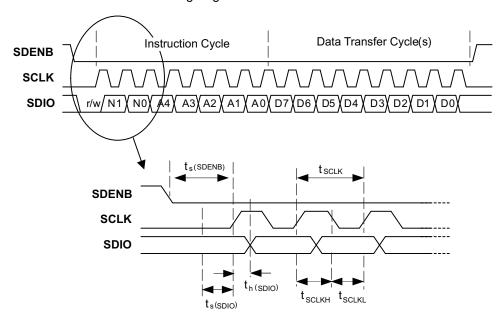

| t <sub>s(SDENB)</sub> | Setup time, SDENB to rising edge of SCLK             |                                                                              | 20                                  |          |          | ns   |

| t <sub>s(SDIO)</sub>  | Setup time, SDIO valid to rising edge of SCLK        |                                                                              | 10                                  |          |          | ns   |

| t <sub>h(SDIO)</sub>  | Hold time, SDIO valid to rising edge of SCLK         |                                                                              | 5                                   |          |          | ns   |

| t <sub>SCLK</sub>     | Period of SCLK                                       |                                                                              | 100                                 |          |          | ns   |

| t <sub>SCLKH</sub>    | High time of SCLK                                    |                                                                              | 40                                  |          |          | ns   |

| t <sub>SCLK</sub>     | Low time of SCLK                                     |                                                                              | 40                                  |          |          | ns   |

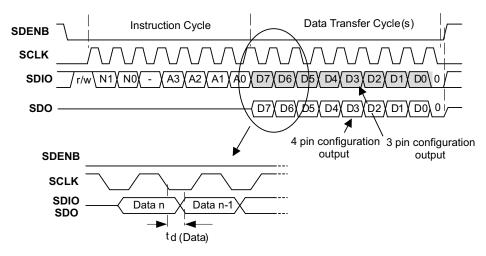

| t <sub>d(Data)</sub>  | Data output delay after falling edge of SCLK         |                                                                              |                                     | 10       |          | ns   |

| t <sub>RESET</sub>    | Minimum RESETB pulse width                           |                                                                              |                                     | 25       |          | ns   |

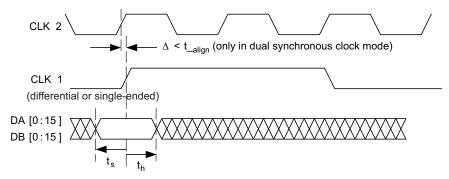

|                       | PARALLEL DATA INPUT TO CLK1/C (DUAL CLO              | CK and DUAL SYNCHRONOUS CLOCK M                                              | DDES: Figure 28)                    |          | <u> </u> |      |

| t <sub>s</sub>        | Setup time                                           |                                                                              | 1                                   |          |          | ns   |

| t <sub>h</sub>        | Hold time                                            | CLK1/C = input                                                               | 1                                   |          |          | ns   |

| t_align               | Max timing offset between CLK1 and CLK2 rising edges | DUAL SYNCHRONOUS BUS MODE only (Typical characteristic)                      | $\frac{1}{2f_{\text{CLK2}}} - 0.55$ |          |          | ns   |

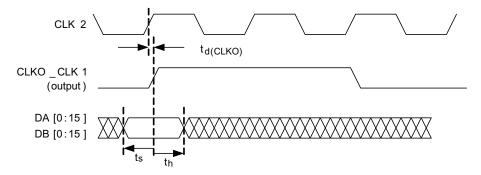

| TIMING P              | PARALLEL DATA INPUT TO CLKO (EXTERNAL                | CLOCK MODE: Figure 29)                                                       |                                     |          |          |      |

| ts                    | Setup time                                           |                                                                              | 1                                   |          |          | ns   |

| t <sub>h</sub>        | Hold time                                            | CLKO_CLK1 = output. Note: Delay time increases with higher capacitive loads. | 1                                   |          |          | ns   |

| t <sub>d(CLKO)</sub>  | Delay time                                           | Thereases with higher capacitive loads.                                      |                                     | 4.5      |          | ns   |

| CLOCK II              | NPUT (CLK2/CLK2C)                                    |                                                                              |                                     |          |          |      |

|                       | CLK2/C Duty cycle                                    |                                                                              | 40%                                 |          | 60%      |      |

|                       | CLK2/C Differential voltage <sup>(1)</sup>           |                                                                              | 0.4                                 | 1        |          | V    |

|                       | CLK2/C Input common mode                             |                                                                              | 2/3                                 | × CLKVDD |          | V    |

|                       | CLK2C Input Frequency                                |                                                                              |                                     |          | 800      | MHz  |

| CLOCK II              | NPUT (CLK1/CLK1C)                                    |                                                                              | 1                                   |          |          |      |

|                       | CLK1/C Duty cycle                                    |                                                                              | 40%                                 |          | 60%      |      |

|                       | CLK1/C Differential voltage                          |                                                                              | 0.4                                 | 1.0      |          | V    |

|                       | CLK1/C Input common mode                             |                                                                              | IC                                  | OVDD / 2 |          | V    |

|                       | CLK1/C Input Frequency                               |                                                                              |                                     |          | 250      | MHz  |

| CLOCK C               | DUTPUT (CLKO)                                        | I                                                                            | I.                                  |          |          |      |

|                       | CLKO Output frequency (2)                            | with 10pF load                                                               |                                     |          | 185      | MHz  |

|                       | CLKO Output frequency (2)                            | with 10pf load                                                               |                                     |          | 185      |      |

<sup>(1)</sup> Driving the clock input with a differential voltage lower than 1V will result in degraded performance.

<sup>(2)</sup> Specified by design and simulation. Not production tested. It is recommended to buffer CLKO.

# **TYPICAL CHARACTERISTICS**

Figure 1. Integral Nonlinearity

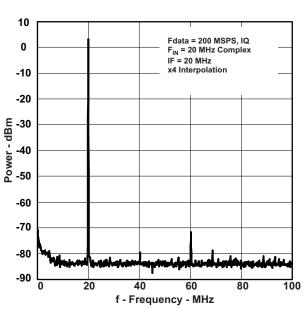

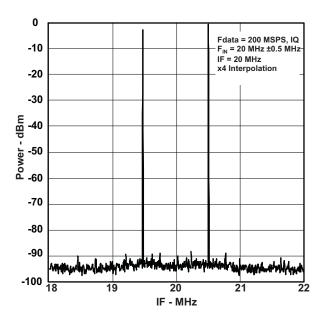

Figure 3. Single Tone Spectral Plot

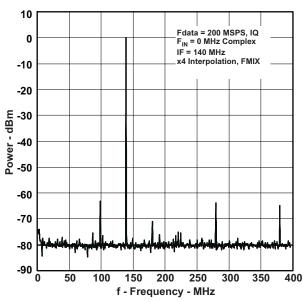

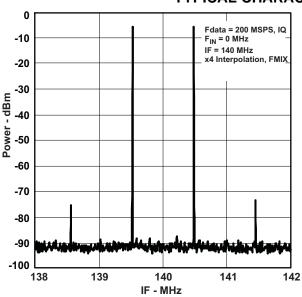

Figure 4. Single Tone Spectral Plot

# **TYPICAL CHARACTERISTICS (continued)**

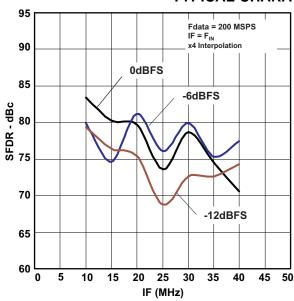

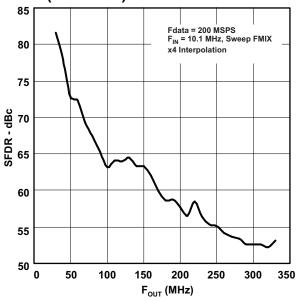

Figure 5. In-Band SFDR vs. Intermediate Frequency

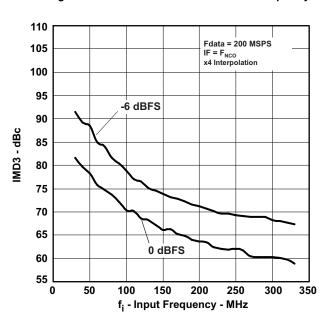

Figure 7. Two Tone IMD vs Intermediate Frequency

Figure 6. Out-Of-Band SFDR vs Intermediate Frequency

Figure 8. Two Tone IMD Spectral Plot

# **TYPICAL CHARACTERISTICS (continued)**

Figure 9. Two Tone IMD Spectral Plot

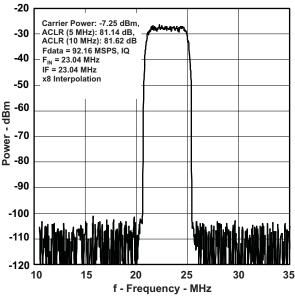

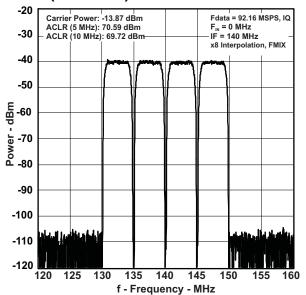

Figure 11. WCDMA TM1:Single Carrier

Figure 10. WCDMA ACLR vs Intermediate Frequency

Figure 12. WCDMA TM1:Single Carrier

# TYPICAL CHARACTERISTICS (continued)

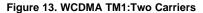

Figure 14. WCDMA TM1:Four Carriers

#### TEST METHODOLOGY

Typical AC specifications were characterized with the DAC5689EVM. A sinusoidal master clock frequency is generated by an HP8665B signal generator which drives an Agilent 8133A pulse generator to generate a square wave output clock for the TSW3100 Pattern Generator and EVM input clock. On the EVM, the input clock is driven by an CDCM7005 clock distribution chip that is configured to simply buffer the external clock or divide it down for necessary test configurations.

The DAC5689 output is characterized with a Rohde and Schwarz FSU spectrum analyzer. For WCDMA signal characterization, it is important to use a spectrum analyzer with high IP3 and noise subtraction capability so that the spectrum analyzer does not limit the ACPR measurement.

# **DEFINITION OF SPECIFICATIONS**

**Adjacent Carrier Leakage Ratio (ACLR):** Defined for a 3.84Mcps 3GPP W-CDMA input signal measured in a 3.84MHz bandwidth at a 5MHz offset from the carrier with a 12dB peak-to-average ratio.

Analog and Digital Power Supply Rejection Ratio (APSRR, DPSRR): Defined as the percentage error in the ratio of the delta IOUT and delta supply voltage normalized with respect to the ideal IOUT current.

**Differential Nonlinearity (DNL):** Defined as the variation in analog output associated with an ideal 1 LSB change in the digital input code.

**Gain Drift:** Defined as the maximum change in gain, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

**Gain Error:** Defined as the percentage error (in FSR%) for the ratio between the measured full-scale output current and the ideal full-scale output current.

**Integral Nonlinearity (INL):** Defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

**Intermodulation Distortion (IMD3, IMD):** The two-tone IMD3 or four-tone IMD is defined as the ratio (in dBc) of the worst 3rd-order (or higher) intermodulation distortion product to either fundamental output tone.

Offset Drift: Defined as the maximum change in DC offset, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

**Offset Error:** Defined as the percentage error (in FSR%) for the ratio of the differential output current (IOUT1-IOUT2) and the mid-scale output current.

**Output Compliance Range:** Defined as the minimum and maximum allowable voltage at the output of the current-output DAC. Exceeding this limit may result reduced reliability of the device or adversely affecting distortion performance.

**Reference Voltage Drift:** Defined as the maximum change of the reference voltage in ppm per degree Celsius from value at ambient (25°C) to values over the full operating temperature range.

**Spurious Free Dynamic Range (SFDR):** Defined as the difference (in dBc) between the peak amplitude of the output signal and the peak spurious signal.

**Signal to Noise Ratio (SNR):** Defined as the ratio of the RMS value of the fundamental output signal to the RMS sum of all other spectral components below the Nyquist frequency, including noise, but excluding the first six harmonics and dc.

# **REGISTER DESCRIPTIONS**

# **REGISTER MAP**

# Table 1. Register Map

| Name     | Address | Default | Bit 7<br>(MSB)       | Bit 6        | Bit 5               | Bit 4               | Bit 3       | Bit 2              | Bit 1           | Bit 0<br>(LSB) |

|----------|---------|---------|----------------------|--------------|---------------------|---------------------|-------------|--------------------|-----------------|----------------|

| STATUS0  | 0x00    | 0x03    | Reserved             | Unused       | Unused              | device_ID(2:0)      |             |                    | versio          | n(1:0)         |

| CONFIG1  | 0x01    | 0x0B    | insel_m              | ode(1:0)     | Unused              | synchr_clkin        | twos        | inv_inclk          | interp_va       | alue(1:0)      |

| CONFIG2  | 0x02    | 0xE1    | dualclk_ena          | clko_off     | Reserved            | clko_SE_hold        | fir4_ena    | qmc_offset_<br>ena | qmc_corr_ena    | mixer_ena      |

| CONFIG3  | 0x03    | 0x00    | diffclk_             | dly(1:0)     | clko_c              | dly(1:0)            |             | Res                | erved           |                |

| CONFIG4  | 0x04    | 0x00    | ser_dac_data_<br>ena | output_c     | delay(1:0)          | B_equals_A          | A_equals_B  | Unused             | reva            | revb           |

| CONFIG5  | 0x05    | 0x22    | sif4                 | sif_sync_sig | clkdiv_sync_<br>ena | clkdiv_sync_<br>sel | Reserved    | clkdiv_shift       | mixer_gain      | Unused         |

| CONFIG6  | 0x06    | 0x00    |                      |              |                     | phaseof             | fset(7:0)   |                    |                 |                |

| CONFIG7  | 0x07    | 0x00    |                      |              |                     | phaseoff            | set(15:8)   |                    |                 |                |

| CONFIG8  | 0x08    | 0x00    |                      |              |                     | phasea              | dd(7:0)     |                    |                 |                |

| CONFIG9  | 0x09    | 0x00    |                      |              |                     | phasea              | dd(15:8)    |                    |                 |                |

| CONFIG10 | 0x0A    | 0x00    |                      |              |                     | phasead             | d(23:16)    |                    |                 |                |

| CONFIG11 | 0x0B    | 0x00    |                      |              |                     | phasead             | d(31:24)    |                    |                 |                |

| CONFIG12 | 0x0C    | 0x00    |                      |              |                     | qmc_ga              | ina(7:0)    |                    |                 |                |

| CONFIG13 | 0x0D    | 0x00    |                      |              |                     | qmc_ga              | inb(7:0)    |                    |                 |                |

| CONFIG14 | 0x0E    | 0x00    |                      |              |                     | qmc_ph              | ase(7:0)    |                    |                 |                |

| CONFIG15 | 0x0F    | 0x24    | qmc_ph               | ase(9:8)     |                     | qmc_gaina(10:8)     |             |                    | qmc_gainb(10:8) |                |

| CONFIG16 | 0x10    | 0x00    |                      |              |                     | qmc_offs            | seta(7:0)   |                    |                 |                |

| CONFIG17 | 0x11    | 0x00    |                      |              |                     | qmc_offs            | setb(7:0)   |                    |                 |                |

| CONFIG18 | 0x12    | 0x00    |                      |              | qmc_offseta(12:8    | 3)                  |             | Unused             | Unused          | Unused         |

| CONFIG19 | 0x13    | 0x00    |                      |              | qmc_offsetb(12:8    | 3)                  |             | Unused             | Unused          | Unused         |

| CONFIG20 | 0x14    | 0x00    |                      |              |                     | ser_dac_            | data(7:0)   |                    |                 |                |

| CONFIG21 | 0x15    | 0x00    |                      |              |                     | ser_dac_o           | data(15:8)  |                    |                 |                |

| CONFIG22 | 0x16    | 0x15    | nco_s                | el(1:0)      | nco_reg             | _sel(1:0)           | qmcorr_re   | eg_sel(1:0)        | qmoffset_re     | eg_sel(1:0)    |

| CONFIG23 | 0x17    | 0x15    | Unused               | Unused       |                     | fifo_sel(2:0)       |             | aflag_sel          | Unused          | Unused         |

| CONFIG24 | 0x18    | 0x80    |                      | fifo_sync    | c_strt(3:0)         |                     | Unused      | Unused             | Unused          | Unused         |

| CONFIG25 | 0x19    | 0x00    | Unused               | Unused       | Unused              | Unused              | Unused      | Unused             | Unused          | Unused         |

| CONFIG26 | 0x1A    | 0x0E    | io_1p8_3p3           | Unused       | sleepb              | sleepa              | isbiaslpf_a | isbiaslpf_b        | Reserved        | Reserved       |

| CONFIG27 | 0x1B    | 0xFF    |                      | coarse_      | daca(3:0)           |                     |             | coarse_            | dacb(3:0)       |                |

| CONFIG28 | 0x1C    | 0x00    |                      |              |                     | Rese                | erved       |                    |                 |                |

| CONFIG29 | 0x1D    | 0x00    |                      | Reserved     |                     |                     |             |                    |                 |                |

| CONFIG30 | 0x1E    | 0x00    |                      |              |                     | Rese                | erved       |                    |                 |                |

# Table 2. Register name: STATUS0 - Address: 0x00, Default 0x03

| Bit 7    | Bit 6  | Bit 5  | Bit 4           | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|----------|--------|--------|-----------------|-------|-------|--------|--------|

| Reserved | Unused | Unused | device_ID (2:0) |       |       | versio | n(1:0) |

| 0        | 0      | 0      | 0               | 0     | 0     | 1      | 1      |

device\_ID(2:0) : Returns '000' for DAC5689. (Read Only)

version(1:0) : A hardwired register that contains the version of the chip. (Read Only)

#### Table 3. Register name: CONFIG1 Address: 0x01, Default 0x0B

| Bit 7    | Bit 6     | Bit 5  | Bit 4        | Bit 3 | Bit 2     | Bit 1     | Bit 0      |

|----------|-----------|--------|--------------|-------|-----------|-----------|------------|

| insel_mo | ode (1:0) | Unused | synchr_clkin | twos  | inv_inclk | interp_va | alule(1:0) |

| 0        | 0         | 0      | 0            | 1     | 0         | 1         | 1          |

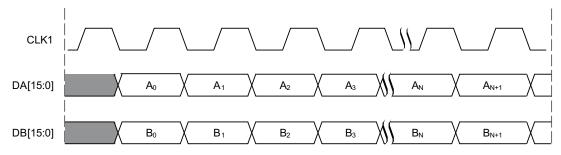

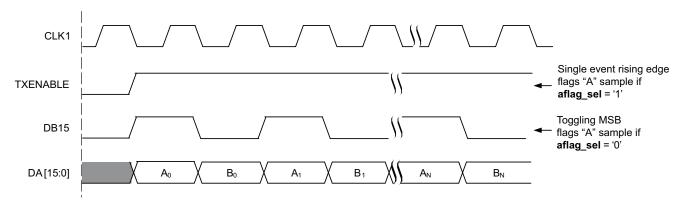

insel\_mode(1:0) : Controls the expected format of the input data. For the interleaved modes, TXENABLE or the MSB of the port

that does not have data can be used to tell the chip which sample is the A sample. For TXENABLE the sample aligned with the rising edge is A. For the MSB, it is presumed that this signal will toggle with A and B. The MSB

should be '1' for A and '0' for B. (\*\*\* See CONFIG23 \*\*\*)

| insel_mode | Function                                                                                                          |

|------------|-------------------------------------------------------------------------------------------------------------------|

| 00         | Normal input on A and B.                                                                                          |

| 01         | Interleaved input on A, which is de-interleaved and placed on both A and B data paths. (*** See CONFIG23 ***)     |

| 10         | Interleaved input on B, which is de-interleaved and placed on both A and B data paths. (*** See CONFIG23 ***)     |

| 11         | Half rate data on A and B inputs. This data is merge together to form a single stream of data on the A data path. |

synchr\_clkin : This turns on the synchronous mode of the dual-clock in mode. In this mode, the CLK2/C and CLK1/C must be

synchronous in phase since the slower clock is used to synchronize dividers in the clock distribution circuit.

twos : When set (default), the input data format is expected to be 2's complement. When cleared, the input is

expected to be offset-binary.

inv\_inclk : This allows the input clock, the clock driving the input side of the FIFO to be inverted. This allows easier

registering of the data (more setup/hold time) in the single-clock mode of the device

interp\_value(1:0)

: These bits define the interpolation factor:

| interp_value | Interpolation Factor |

|--------------|----------------------|

| 00           | 1X                   |

| 01           | 2X                   |

| 10           | 4X                   |

| 11           | 8X                   |

# Table 4. Register name: CONFIG2 Address: 0x02, Default 0xE1

| Bit 7       | Bit 6    | Bit 5    | Bit 4        | Bit 3     | Bit 2           | Bit 1         | Bit 0     |

|-------------|----------|----------|--------------|-----------|-----------------|---------------|-----------|

| dualclk_ena | clko_off | Reserved | clko_SE_hold | fir4_ ena | qmc_ offset_ena | qmc_ corr_ena | mixer_ena |

| 1           | 1        | 1        | 0            | 0         | 0               | 0             | 1         |

dualclk\_ena : When set (default), the device is in dual clock mode. A single-ended or differential clock at the data rate

frequency must be input to CLK1/CLK1C. Otherwise, the device is in external clock mode.

clko\_off : When cleared, the pin is configured to output an internally generated CLKO as a clock signal for the input data.

Must be set (default) in dual clock mode.

clko\_SE\_hold : When set, the single ended (SE) clock is held to a value of '1' so that the signal doesn't toggle when using the

differential clock input.

fir4\_ena : When set, the FIR4 Inverse SINC filter is enabled. Otherwise it is bypassed

qmc\_offset\_ena : When set, the digital Quadrature Modulator Correction (QMC) offset correction circuitry is enabled.

qmc\_corr\_enaWhen set, the QMC phase and gain correction circuitry is enabled.mixer\_enaWhen set, the Full Mixer (FMIX) is enabled. Otherwise it is bypassed.

#### Table 5. Register name: CONFIG3 Address: 0x03, Default 0x00

|                  | Bit 7 | Bit 6         | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------|-------|---------------|-------|----------|-------|-------|-------|-------|

| diffclk_dly(1:0) |       | clko_dly(1:0) |       | Reserved |       |       |       |       |

|                  | 0     | 0             | 0     | 0        | 0     | 0     | 0     | 0     |

diffclk\_dly(1:0) : To allow for a wider range of interfacing, the differential input clock has programmable delay added to its tree.

| diffclk_dly | Approximate additional delay |  |  |  |  |

|-------------|------------------------------|--|--|--|--|

| 00          | 0                            |  |  |  |  |

| 01          | 1.0 ns                       |  |  |  |  |

| 10          | 2.0 ns                       |  |  |  |  |

| 11          | 3.0 ns                       |  |  |  |  |

clko\_dly(1:0) : Same as above except these bits effect the single ended or internally generated clock

# Table 6. Register name: CONFIG4 Address: 0x04, Default 0x00

| Bit 7             | Bit 6    | Bit 5      | Bit 4      | Bit 3      | Bit 2  | Bit 1 | Bit 0 |

|-------------------|----------|------------|------------|------------|--------|-------|-------|

| ser_dac_ data_ena | output_c | delay(1:0) | B_equals_A | A_equals_B | Unused | reva  | revb  |

| 0                 | 0        | 0          | 0          | 0          | 0      | 0     | 0     |

ser\_dac\_data\_ena:Muxes the ser\_dac\_data(15:0) to both DACs when asserted.output\_delay(1:0):Delays the output to both DACs from 0 to 3 DAC clock cyclesB\_equals\_A:When set, the DACA data is driving the DACB output.A\_equals\_B:When set, the DACB data is driving the DACA output.

| Bit 4<br>B_equals_A | Bit 3<br>A_equals_B | DACB<br>Output | DACA<br>Output | Description                |

|---------------------|---------------------|----------------|----------------|----------------------------|

| 0                   | 0                   | B data         | A data         | Normal Output              |

| 0                   | 1                   | B data         | B data         | Both DACs driven by B data |

| 1                   | 0                   | A data         | A data         | Both DACs driven by A data |

| 1                   | 1                   | A data         | B data         | Swapped Output             |

reva : Reverse the input bits of the A input port. MSB becomes LSB.

revb : Reverse the input bits of the B input port. MSB becomes LSB

# Table 7. Register name: CONFIG5 Address: 0x05, Default 0x22

| Bit 7 | Bit 6         | Bit 5           | Bit 4           | Bit 3    | Bit 2        | Bit 1      | Bit 0  |

|-------|---------------|-----------------|-----------------|----------|--------------|------------|--------|

| sif4  | sif_ sync_sig | clkdiv_sync_ena | clkdiv_sync_sel | Reserved | clkdiv_shift | mixer_gain | Unused |

| 0     | 0             | 1               | 0               | 0        | 0            | 1          | 0      |

sif4 : When set, the serial interface (SIF) is a 4 bit interface, otherwise it is a 3 bit interface.

sif\_sync\_sig : SIF created sync signal. Set to '1' to cause a sync and then clear to '0' to remove it.

clkdiv\_sync\_ena : Enables syncing of the clock divider using the sync or TXENABLE pins when the bit is asserted.

clkdiv\_sync\_sel : Selects the input pin to sync the clock dividers. (0 = SYNC, 1 = TXENABLE)

clkdiv\_shift : When set, a rising edge on the selected sync (see clkdiv\_sync\_sel) for the clock dividers will cause a slip in the

synchronous counter by 1T and is useful for multi-DAC time alignment.

mixer\_gain : When set, adds 6dB to the mixer gain output.

#### Table 8. Register name: CONFIG6 Address: 0x06, Default 0x00 (Synced)

|               | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|------------------|-------|-------|-------|-------|-------|-------|-------|

|               | phaseoffset(7:0) |       |       |       |       |       |       |       |

| 0 0 0 0 0 0 0 |                  |       |       |       |       |       |       | 0     |

phaseoffset(7:0) : See CONFIG7 below.

# Table 9. Register name: CONFIG7 Address: 0x07, Default 0x00 (Synced)

|               | Bit 7             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------------|-------|-------|-------|-------|-------|-------|-------|

|               | phaseoffset(15:8) |       |       |       |       |       |       |       |

| 0 0 0 0 0 0 0 |                   |       |       |       |       |       |       | 0     |

phaseoffset(15:8)

This is the phase offset added to the NCO accumulator just before generation of the SIN and COS values. The phase offset is added to the upper 16bits of the NCO accumulator results and these 16 bits are used in the sin/cosine lookup tables.

# Table 10. Register name: CONFIG8 Address: 0x08, Default 0x00 (Synced)

|               | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|---------------|-------|-------|-------|-------|-------|-------|-------|

|               | phaseadd(7:0) |       |       |       |       |       |       |       |

| 0 0 0 0 0 0 0 |               |       |       |       |       | 0     |       |       |

phaseadd(7:0) : See CONFIG11 below.

# Table 11. Register name: CONFIG9 Address: 0x09, Default 0x00 (Synced)

| Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| phaseadd(15:8) |       |       |       |       |       |       |       |  |

| 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

phaseadd(15:8) : See CONFIG11 below.

# Table 12. Register name: CONFIG10 Address: 0x0A, Default 0x00 (Synced)

| Bit 7         | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------------|-----------------|-------|-------|-------|-------|-------|-------|--|

|               | phaseadd(23:16) |       |       |       |       |       |       |  |

| 0 0 0 0 0 0 0 |                 |       |       |       |       |       |       |  |

phaseadd(23:16) : See CONFIG11 below.

# Table 13. Register name: CONFIG11 Address: 0x0B, Default 0x00 (Synced)

| Bit 7 | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|-----------------|-------|-------|-------|-------|-------|-------|--|--|

|       | phaseadd(31:24) |       |       |       |       |       |       |  |  |

| 0     | 0 0 0 0 0 0 0   |       |       |       |       |       |       |  |  |

phaseadd(31:24) : The Phaseadd(31:0) value is used to determine the frequency of the NCO. The two's complement formatted value can be positive or negative and the LSB is equal to Fs/(2^32).

# Table 14. Register name: CONFIG12 Address: 0x0C, Default 0x00 (Synced)

| Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| qmc_gaina(7:0) |       |       |       |       |       |       |       |  |  |

| 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

qmc\_gaina(7:0)

: Lower 8 bits of the 11-bit Quadrature Modulator Correction (QMC) gain word for DACA. The upper 3 bits are in the CONFIG15 register. The full 11-bit qmc\_gaina(10:0) word is formatted as UNSIGNED with a range of 0 to 1.9990 and the default gain is 1.0000. The implied decimal point for the multiplication is between bit 9 and bit 10. Refer to formatting reference below.

| qmc_gaina(10:0)<br>[Binary] | qmc_gaina(10:0)<br>[Decimal] | Format          | Gain Value |

|-----------------------------|------------------------------|-----------------|------------|

| 0000000000                  | 0                            | 0 + 0/1024 =    | 0.0000000  |

| 0000000001                  | 1                            | 0 + 1/1024 =    | 0.0009766  |

|                             |                              |                 |            |

| 0111111111                  | 1023                         | 0 + 1023/1024 = | 0.9990234  |

| 1000000000                  | [Default] 1024               | 1 + 0/1024 =    | 1.0000000  |

| 1000000001                  | 1025                         | 1 + 1/1024 =    | 1.0009766  |

|                             |                              |                 |            |

| 1111111111                  | 2047                         | 1 + 1023/1024 = | 1.9990234  |

# Table 15. Register name: CONFIG13 Address: 0x0D, Default 0x00 (Synced)

| Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| qmc_gainb(7:0) |       |       |       |       |       |       |       |  |  |

| 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |