# NS4890C 2.4W Mono Class AB audio amplifier

#### 1 Features

- Voltage range:3.0V-5.0V

- Output power:  $1.56W@R_L=8\Omega/THD+N=10\%$

- Leakage current in shutdown mode:1uA(typical)

- The  $\overline{\mathrm{SD}}$  pin is used for low level control to enter shutdown mode.

- Stable unity gain.

- External feedback resistor and input resistor, adjustable gain.

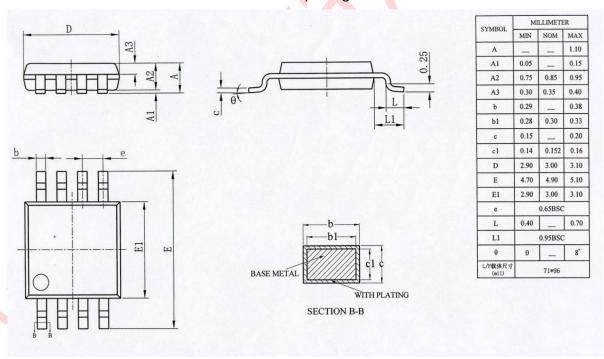

- MSOP8 package.

## 2 Application

- Smart wear

- Automobile data recorder

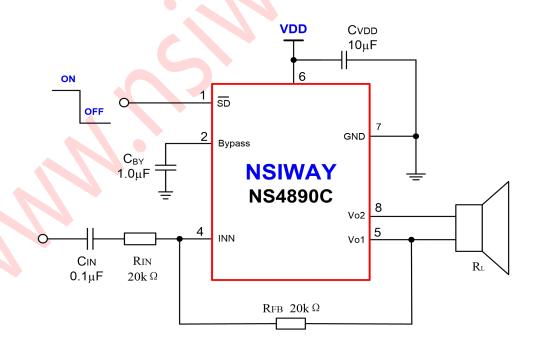

## 4 Typical application circuit

### 3 Description

NS4890C is a class AB bridge output audio amplifier. Its application circuit is simple and only a few peripheral devices are needed. The output does not require external coupling capacitors or lifting capacitors and buffering networks, it is more suitable for portable systems.

NS4890C can reduce power consumption by controlling the  $\overline{\rm SD}$  pin to enter low power shutdown mode. The voltage gain of the amplifier can be adjusted by configuring the peripheral resistor for easy application.

NS4890C is available in MSOP8 package and is rated for operating temperatures ranging from -40  $^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  .

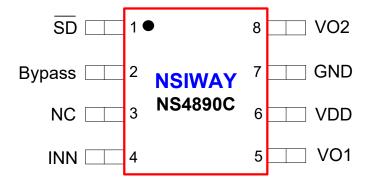

# 5 Pin configuration

The pin diagram of MSOP8 is shown below.

| No. | pin name | description                                         |  |  |  |

|-----|----------|-----------------------------------------------------|--|--|--|

| 1   | SD       | The device enters in shutdown mode when a low       |  |  |  |

|     |          | level is applied on this pin                        |  |  |  |

| 2   | Bypass   | Bypass capacitor pin which provides the common      |  |  |  |

|     |          | mode voltage                                        |  |  |  |

| 3   | NC       | -                                                   |  |  |  |

| 4   | INN      | Negative input of the first amplifier, receives the |  |  |  |

|     |          | audio input signal                                  |  |  |  |

| 5   | VO1      | Negative output                                     |  |  |  |

| 6   | VDD      | Positive power supply pin                           |  |  |  |

| 7   | GND      | Power ground                                        |  |  |  |

| 8   | VO2      | Positive output                                     |  |  |  |

# **6 Limit operating parameters**

| Name                         | Parameter       |  |  |  |  |

|------------------------------|-----------------|--|--|--|--|

| Input Voltage                | 2.8V ~ 5.5V     |  |  |  |  |

| ESD Susceptibility           | 2kV-HBM         |  |  |  |  |

| Storage Temperature          | −65°C to +150°C |  |  |  |  |

| Operating Temperature        | −40°C to +85°C  |  |  |  |  |

| Junction Temperature         | 150°C           |  |  |  |  |

| Lead Temp(Soldering, in 10s) | 260°C           |  |  |  |  |

| Thermal Resistance           |                 |  |  |  |  |

| θЈА                          | 140°C/W         |  |  |  |  |

| θЈС                          | 35°C/W          |  |  |  |  |

Note: Exceeding the limit operating parameters above may cause permanent damage to the chip. Prolonged exposure to any of these limiting conditions may affect the reliability and longevity of the chip.

# **7 Electrical characteristics**

Operating conditions (unless otherwise stated) : T=25  $^{\circ}$ C,  $V_{DD}$ =5V.

| symbol          | parameter                         | testing conditions         | Min. | standard | Max. | unit |

|-----------------|-----------------------------------|----------------------------|------|----------|------|------|

| V <sub>DD</sub> | Supply voltage                    |                            | 3.0  |          | 5.5  | ٧    |

| I <sub>DD</sub> | Quiescent Power Supply<br>Current | V <sub>IN</sub> =0V, Io=0A |      | 6        | 10   | mA   |

| I <sub>SD</sub> | Shutdown Current                  |                            |      | 1        | 20   | μΑ   |

| Vos             | Output offset voltage             |                            |      | 5.7      | 50   | mV   |

| Ro              | Output resistor                   |                            | 7    | 8.5      | 10   | ΚΩ   |

| P <sub>0</sub>  |                                   | THD+N=1%,f=1KHz            |      |          |      |      |

|                 | Output power                      | RL=4Ω                      |      | 1.8      |      | W    |

|                 |                                   | RL=8Ω                      |      | 1.3      |      |      |

|                 |                                   | THD+N=10%,f=1KHz           |      |          |      |      |

|                 |                                   | RL=4Ω                      |      | 2. 36    |      | W    |

|                 |                                   | RL=8Ω                      |      | 1.56     |      |      |

| THD+N           | Total distortion+Noise            | AVD=2, 20Hz≤f≤20KHz        |      |          |      | %    |

|                 |                                   | RL=8Ω,PO=0.5W              |      | 0.15     |      |      |

| PSRR            | Power supply rejection ratio      |                            | 65   | 80       |      | dB   |

| SNR             | Signal-to-noise ratio             | $RL=4\Omega$ ,Po=1W        |      | 78       |      | dB   |

| V <sub>IH</sub> | SD input at high level            |                            | 1.4  |          | VDD  | V    |

| V <sub>IL</sub> | SD input at low level             |                            | 0    |          | 0.5  | V    |

| Tst             | Start up time                     | Bypass=1uf                 |      | 180      |      | ms   |

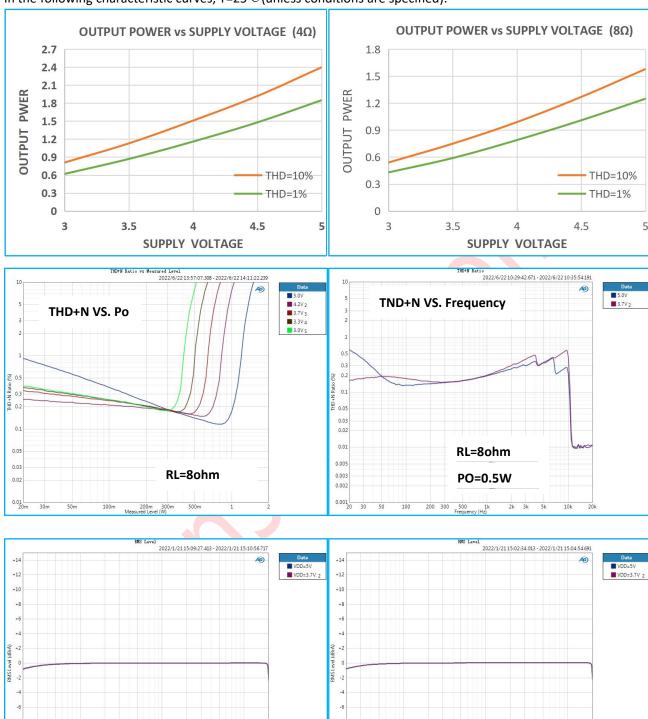

### 8 Typical characteristic curves

-10

-12

-14

RL=4ohm

200 300 500 1k Frequency (Hz)

In the following characteristic curves, T=25 °C (unless conditions are specified).

-10

-12

-14

RL=8ohm

### 9 Application specifications

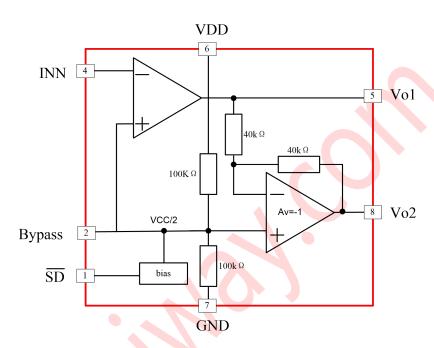

#### 9.1 Basic structure description

NS4890C is a class AB audio amplifier with bridge output. Two operational amplifiers are integrated internally. The gain of the first amplifier can be set by feedback resistance, and the second amplifier is followed by voltage inverting, forming an amplifier driving circuit with gain configurable differential output. Its principle block diagram is shown below.

## 9.2 External resistance configuration

As shown in the application drawing,the gain of the operational amplifier is determined by the external resistors  $R_{FB}$  and  $R_{IN}$ . The gain calculation formula is as follows:  $AV=2\cdot\frac{R_{FB}}{R_{IN}}$  . The chip is output to the load through V<sub>O1</sub> and V<sub>O2</sub>, which the bridge connection method is used.

#### 9.3 External capacitance configuration

In fact,in many applications, the speaker cannot reproduce low frequency speech below 100Hz. The input coupling capacitance  $C_{IN}$  (  $C_{IN}$  and  $R_{IN}$  form a first-order high-pass filter) determines the low-frequency response, the calculation formula is:  $fc = \frac{1}{2\pi \cdot R_{IN} \cdot C_{IN}}$ . In practice, large input capacitance can not improve the low frequency performance of the system. In addition to considering the performance of the system, the suppression performance of on-off/switching noise is affected by capacitance. If the coupling capacitance is large, the delay of the feedback network is large, resulting in pop noise. A small coupling capacitance can reduce the

noise.

#### 9.4 Power bypass

In amplifier applications, power bypass design is very important, especially for noise performance and power supply voltage suppression performance. In the design, the bypass capacitor should be as close as possible to the chip and power pin. Typical capacitance is an electrolytic capacitor of 10 uF with a ceramic capacitor of 0.1 uF.

In the NS4890C application circuit, another capacitor  $C_{BY}$  (connected to  $B_{YP}$  pin) is also critical, affecting PSRR and on-off/switching noise performance. Generally, a ceramic capacitor of  $0.1 uF \sim 1 uF$  is selected.

#### 9.5 Shutdown mode

NS4890C is provided with  $\overline{SD}$  control pin, through which the customer can control whether the amplifier is working. When the  $\overline{SD}$  pin is high, the audio amplifier is in operation mode. When the  $\overline{SD}$  pin is low, the chip enters the shut down mode. At this time, the chip shuts off the current of 1uA, to achieve the purpose of power saving.

### 10 Package information

### MSOP8 package

## 11 Revision history

Statement: Nsiway company has the right to modify the product information and specifications at any time without notice. Nsiway company reserves the right to interpret this manual and is responsible for the final interpretation.