TPS59632-Q1

ZHCSKX0-FEBRUARY 2020

# 适用于汽车 ADAS 应用的 TPS59632-Q1 2.5V 至 24V、三相/两相/单相降 压无驱动器控制器

#### 1 特性

- 符合面向汽车 应用的 AEC-Q100 标准

- 温度等级 1: -40°C 至 125°C

- 人体放电模型 ESD 分类等级 H2

- 带电器件模型 ESD 分类等级 C3B

- 可选相位数: 3、2或1

- 转换电压范围: 2.5V 至 24V (相位数、开关频率和 最大输出电压限制适用)

- 7位 DAC 电压范围: 0.50V 至 1.52V

- 支持预设引导, DAC 电压 0.800V

- 精确、可调节的直流负载线(压降)或零斜率负载 线

- D-CAP+™控制,可实现快速瞬态响应

- 已获专利的 AutoBalance™相位均衡技术

- 8 种开关频率设置(300kHz 至 1MHz)

- 8级独立的输出电压过冲衰减 (OSR) 和下冲衰减 (USR)

- 可选8级电流限制

- 负载电流监视器(模拟和数字)

- 可选8级电压压摆率

- 优化了轻负载和重负载条件下的效率

- I<sup>2</sup>C 接口适用于 VID 控制、相位管理和遥测(具有8 个器件地址)

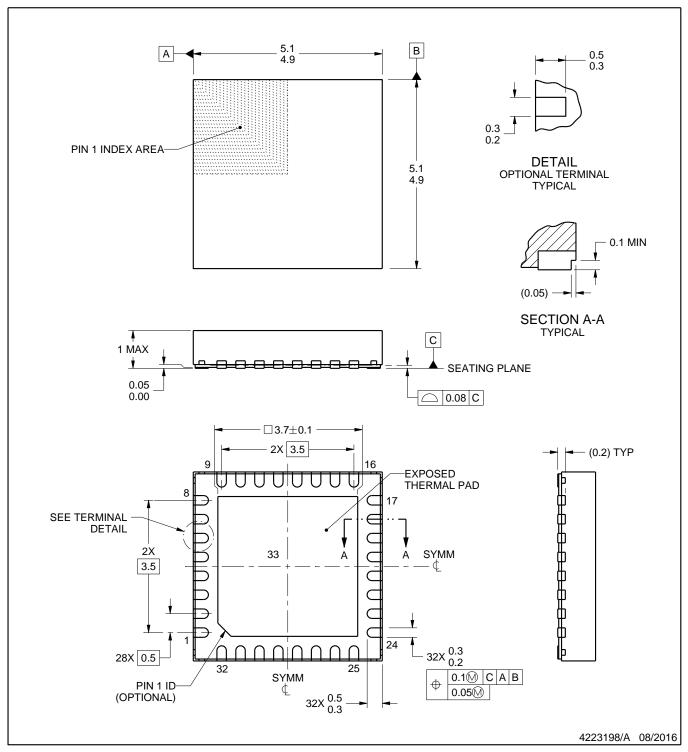

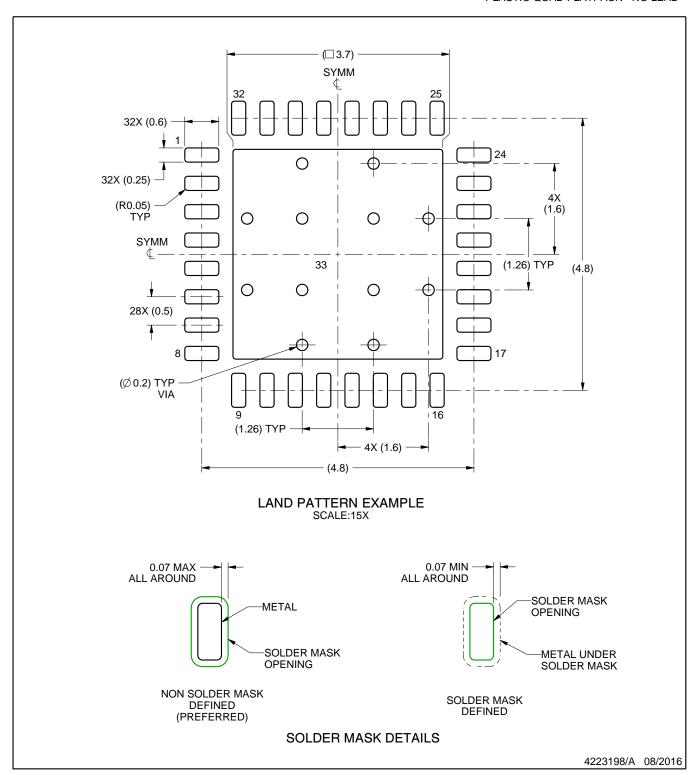

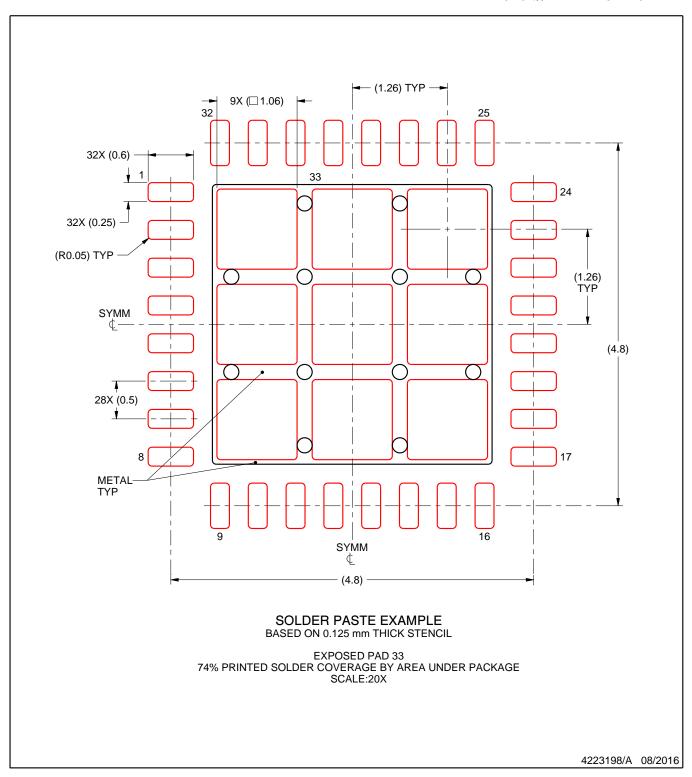

- 采用 5mm x 5mm、32 引脚、间距为 0.5mm 的 QFN 封装(具有电源板和可湿性侧面)

#### 2 应用

- 高级驾驶辅助系统 (ADAS)

- 条件式自动驱动控制器

- 汽车信息娱乐系统和仪表组

#### 3 说明

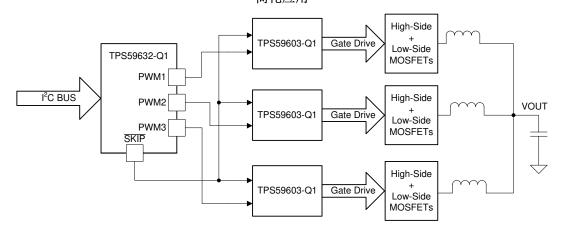

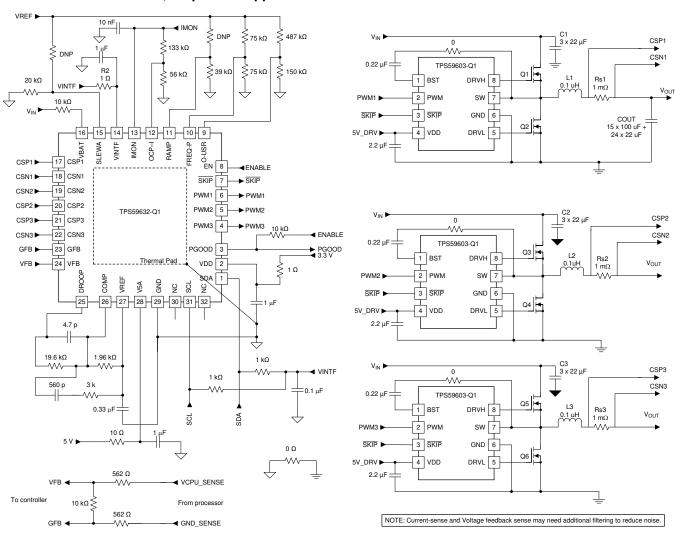

TPS59632-Q1 器件是一款三相降压无驱动器控制器,具有许多高级 功能 ,例如具有输出电压过冲衰减 (OSR) 和下冲衰减 (USR) 功能的 D-CAP+™控制架构,可实现极快的瞬态响应、超低的输出电容和高效率。该器件支持 I²C 接口,能够实现输出电压动态控制、可优化效率的相位管理以及电流监控器遥测。TPS59603-Q1 MOSFET 栅极驱动器专用于与此控制器配合工作,以驱动同步降压转换器功率级MOSFET。TPS59632-Q1 器件采用节省空间的 5mm×5mm、热增强型 32 引脚 QFN 封装(间距为0.5mm),额定工作温度范围为 -40°C 至 125°C。

#### 器件信息<sup>(1)</sup>

| 器件型号        | 封装        | 封装尺寸 (标称值) |

|-------------|-----------|------------|

| TPS59632-Q1 | VQFN (32) | 5mm × 5mm  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

#### 简化应用

## 目录

| 1 | 特性                                       |       | 8.1 Application Information         | 29 |

|---|------------------------------------------|-------|-------------------------------------|----|

| 2 | 应用 1                                     |       | 8.2 Typical Application             |    |

| 3 |                                          | 9     | Power Supply Recommendations        |    |

| 4 | 修订历史记录                                   | 10    | Layout                              |    |

| 5 | Pin Configuration and Functions3         |       | 10.1 Layout Guidelines              | 39 |

| 6 | Specifications                           |       | 10.2 Layout Example                 | 39 |

| • | 6.1 Absolute Maximum Ratings 5           |       | 10.3 Current Sensing Lines          | 40 |

|   | 6.2 ESD Ratings                          |       | 10.4 Feedback Voltage Sensing Lines | 40 |

|   | 6.3 Recommended Operating Conditions     |       | 10.5 PWM And SKIP Lines             | 40 |

|   | 6.4 Thermal Information                  |       | 10.6 Power Chain Symmetry           | 40 |

|   | 6.5 Electrical Characteristics 6         |       | 10.7 Component Location             | 40 |

|   |                                          |       | 10.8 Grounding Recommendations      | 41 |

|   | 6.6 Timing Requirements                  |       | 10.9 Decoupling Recommendations     |    |

|   | 6.7 Switching Characteristics            |       | 10.10 Conductor Widths              |    |

| _ | 6.8 Typical Characteristics              | 11    | 器件和文档支持                             |    |

| 7 | Detailed Description 13                  | • • • | 11.1 文档支持                           |    |

|   | 7.1 Overview 13                          |       | 11.2 商标                             |    |

|   | 7.2 Functional Block Diagram 14          |       |                                     |    |

|   | 7.3 Feature Description                  |       | 11.3 静电放电警告                         |    |

|   | 7.4 User Selections                      |       | 11.4 Glossary                       |    |

|   | 7.5 I <sup>2</sup> C Interface Operation | 12    | 机械、封装和可订购信息                         |    |

|   | 7.6 I <sup>2</sup> C Register Maps       | 13    | Package Option Addendum             | 44 |

| 8 | Applications and Implementation 29       |       | 13.1 Packaging Information          | 44 |

|   | , , , , , , , , , , , , , , , , , , , ,  |       | 13.2 Tape And Reel Information      | 45 |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期         | 修订版本 | 说明    |

|------------|------|-------|

| 2020 年 2 月 | *    | 初始发行版 |

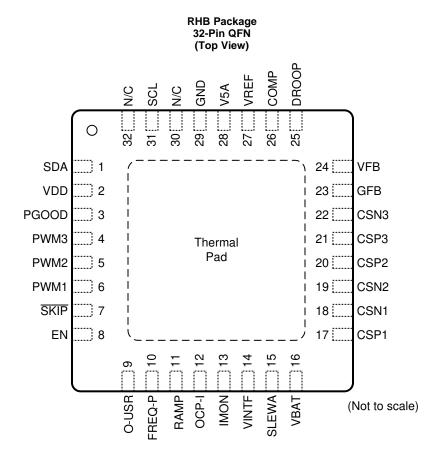

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN    |     | .,, | DESCRIPTION                                                                                                                                                                                                   |  |  |

|--------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                   |  |  |

| COMP   | 26  | ı   | Error amplifier summing node. Resistors from VREF to COMP ( $R_{COMP}$ ) and COMP to DROOP ( $R_{DROOP}$ ) set the droop gain.                                                                                |  |  |

| CSP1   | 17  |     |                                                                                                                                                                                                               |  |  |

| CSP2   | 20  | - 1 | Positive current sense inputs. Connect to the most positive node of current sense resistor or inductor DCR sense network. Tie CSP3, CSP2, or CSP1 (in that order) to 3.3 V to disable the phase.              |  |  |

| CSP3   | 21  |     | Solide Hetheria. The earlier, earlier, or earlier (in that order) to elect the disease the phase.                                                                                                             |  |  |

| CSN1   | 18  |     |                                                                                                                                                                                                               |  |  |

| CSN2   | 19  | ı   | Negative current sense inputs. Connect to the most negative node of current sense resistor or inductor DCR sense network. CSN1 has a secondary OVP comparator and includes the soft-stop pulldown transistor. |  |  |

| CSN3   | 22  |     | Solid Helwork. Convinues a Secondary CVI Comparator and includes the Solt Stop pullbown translator.                                                                                                           |  |  |

| DROOP  | 25  | 0   | Error amplifier output. A resistor pair from VREF to COMP to DROOP sets the droop gain. $A_{DROOP} = 1 + R_{DROOP} / R_{COMP}$ .                                                                              |  |  |

| EN     | 8   | ı   | Enable; 100-ns de-bounce. Regulator enters low-power mode, but retains start-up settings when brought low.                                                                                                    |  |  |

| FREQ-P | 10  | ı   | R to GND sets the per phase switching frequency. MUST connect a resistor to VREF to ensure this pin voltage is above 0.8 V for proper operation.                                                              |  |  |

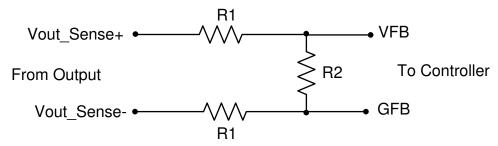

| GFB    | 23  | I   | Voltage sense return. Tie to GND on PCB with a 10- $\Omega$ resistor to provide feedback when $\mu P$ is not populated.                                                                                       |  |  |

| GND    | 29  | -   | Analog circuit reference; tie to a quiet point on the ground plane.                                                                                                                                           |  |  |

| IMON   | 13  | 0   | Analog current monitor output. $V_{IMON} = \sum V_{ISENSE} \times (1 + R_{IMON} / R_{OCP})$ .                                                                                                                 |  |  |

| OCP-I  | 12  | I/O | Voltage divider to IMON. Resistor ratio sets the IMON gain (see IMON pin). R to GND (R <sub>OCP</sub> ) selects 1 of 8 OCP levels (per phase, latched at start-up).                                           |  |  |

## Pin Functions (continued)

| PIN              |          |     |                                                                                                                                                                                                                                                  |

|------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                      |

| O-USR            | 9        | I   | Voltage divider to the VREG pin. Connect a resistor to GND to select the pulse-truncation level and OSR level. Voltage at O-USR selects the USR level.                                                                                           |

| PU               | 9        | I   | Provides pullup resistance to VREF through 10-kΩ resistor.                                                                                                                                                                                       |

| PAD              | GND      | -   | Thermal pad; tie to the ground plane with multiple vias.                                                                                                                                                                                         |

| PGOOD            | 3        | 0   | Power Good output; Open-drain. PGOOD can be configured to go low when the current reaches 70% of the OCP setting value.                                                                                                                          |

| PWM1             | 6        |     |                                                                                                                                                                                                                                                  |

| PWM2 5<br>PWM3 4 |          | 0   | PWM controls for the external driver; 5-V logic level. Controller forces signal to the 3-state level when needed.                                                                                                                                |

|                  |          |     | necueu.                                                                                                                                                                                                                                          |

| RAMP             | 11       | ı   | Voltage divider to VREF. Connect a resistor to GND to set the ramp setting voltage. The RAMP setting can override the factory ramp setting.                                                                                                      |

| NC -             | 30<br>32 | NC  | No connect. Leave pins floating.                                                                                                                                                                                                                 |

| SCL              | 31       | I   | I <sup>2</sup> C digital clock line.                                                                                                                                                                                                             |

| SDA              | 1        | I/O | I <sup>2</sup> C digital data line.                                                                                                                                                                                                              |

| SKIP             | 7        | 0   | This pin is active high to operate synchronous buck MOSFETs in Forced Continuous Conduction Mode (FCCM) active low for skip mode operation. This pin must be connected to the corresponding pin of the drivers for this function.                |

| SLEWA            | 15       | ı   | The voltage sets the 3 LSBs of the I <sup>2</sup> C address. The resistance to GND selects 1 of 8 slew rates. The start-up slew rate (EN transitions high) is SLEWRATE / 2. The ADDRESS and SLEWRATE values are latched at start-up.             |

| VINTF            | 14       | I   | Input voltage to power I <sup>2</sup> C interface logic. Can be tied to VDD if 3.3-V logic signals are needed.                                                                                                                                   |

| V5A              | 28       | ı   | 5-V power input for analog circuits; connect through resistor to 5-V plane and bypass to GND with ≥ 1-μF ceramic capacitor                                                                                                                       |

| VBAT             | 16       | I   | 10-k $\Omega$ resistor to VBAT provides VBAT information to the on-time circuits for both converters.                                                                                                                                            |

| VDD              | 2        | I   | 3.3-V digital power input; bypass to GND with ≥ 1-µF capacitor.                                                                                                                                                                                  |

| VFB              | 24       | ı   | Voltage sense line. Tie directly to $V_{OUT}$ sense point of processor. Tie to $V_{OUT}$ on PCB with a 10- $\Omega$ resistor to provide feedback when the microprocessor is not populated. The resistance between VFB and GFB is > 1 $M\Omega$ . |

| VREF             | 27       | 0   | 1.7-V, 500-μA reference. Bypass to GND with a 0.22-μF ceramic capacitor.                                                                                                                                                                         |

### 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                            |                                                                                                          | MIN  | MAX | UNIT |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|

|                                            | V5A                                                                                                      | -0.3 | 6.0 |      |

|                                            | VDD, O-USR, RAMP, OCP-I, VFB, CSP1, CSP2, CSP3, CSN1, CSN2, CSN3, VINTF, SDA, SCL, FREQ-P, SLEWA, EN, NC | -0.3 | 3.6 |      |

| Input voltage                              | VBAT                                                                                                     | -0.3 | 30  | V    |

|                                            | COMP                                                                                                     | -0.3 | 3.6 |      |

|                                            | GFB                                                                                                      | -0.2 | 0.2 |      |

| Output valtage                             | PGOOD, IMON, VREF, DROOP                                                                                 | -0.3 | 3.6 | V    |

| Output voltage                             | PWM3, PWM2, PWM1, SKIP                                                                                   | -0.3 | 6.0 | V    |

| lunction temperature range, T <sub>J</sub> |                                                                                                          | -40  | 150 | °C   |

| Storage Temperatu                          | re T <sub>stg</sub>                                                                                      | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|        |                         |                                                                   | VALUE | UNIT     |

|--------|-------------------------|-------------------------------------------------------------------|-------|----------|

| V      | Electrostatia Discharge | Human body model (HBM), per AEC-Q100 Classification Level H2      | ±2000 |          |

| V(ESD) |                         | Charged device model (CDM), per AEC-Q100 Classification Level C3B | ±750  | <b>v</b> |

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                        |                                                                                                          | MIN  | MAX | UNIT |

|------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|

|                        | V5A                                                                                                      | -0.1 | 5.5 |      |

|                        | VDD, O-USR, RAMP, OCP-I, VFB, CSP1, CSP2, CSP3, CSN1, CSN2, CSN3, VINTF, SDA, SCL, FREQ-P, SLEWA, EN, NC | -0.1 | 3.5 |      |

| Input voltage          | VBAT                                                                                                     | -0.1 | 28  | V    |

|                        | COMP                                                                                                     | -0.1 | 3.5 |      |

|                        | GFB                                                                                                      | -0.1 | 0.1 |      |

| Output valtage         | PGOOD, IMON, VREF, DROOP                                                                                 | -0.1 | 3.5 | V    |

| Output voltage         | PWM3, PWM2, PWM1, SKIP                                                                                   | -0.1 | 5.5 | V    |

| Operating junction ter | mperature, T <sub>J</sub>                                                                                | -40  | 125 | °C   |

#### 6.4 Thermal Information

|                    |                                              | TPS59632-Q1 |       |

|--------------------|----------------------------------------------|-------------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | RSM (VQFN)  | UNITS |

|                    |                                              | 32 PINS     |       |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 37.2        |       |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 31.9        |       |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 8.1         | 9000  |

| ΨЈТ                | Junction-to-top characterization parameter   | 0.4         | °C/W  |

| ΨЈВ                | Junction-to-board characterization parameter | 7.9         |       |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.2         |       |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report

#### 6.5 Electrical Characteristics

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>OUT</sub>, 0.7 < VFREQ-P  $\leq$  V<sub>VREF</sub> (unless otherwise noted).

| POWER SUPPLY: I <sub>V5-3P</sub>                      | PARAMETER  CURRENTS, UVLO AND POWER  V5A supply current, 3-phase |                                                                                                                                                         | MIN  | TYP            | MAX  | UNIT |

|-------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|------|

| I <sub>V5-3P</sub>                                    |                                                                  |                                                                                                                                                         |      |                |      |      |

|                                                       | voa supply current, 3-phase                                      |                                                                                                                                                         |      | 3.6            | 6.0  |      |

| VDD-3P                                                | VDD supply surrent 2 phase                                       | $V_{VDAC} < V_{VFB} < (V_{VDAC} + 100 \text{ mV}), \text{ EN = 'HI'}$<br>$V_{VDAC} < V_{VFB} < (V_{VDAC} + 100 \text{ mV}), \text{ EN = 'HI'; digital}$ |      |                |      |      |

|                                                       | VDD supply current, 3-phase                                      | buses idle                                                                                                                                              |      | 0.2            | 0.8  | mA   |

| I <sub>V5-1P</sub>                                    | V5A supply current, 1-phase                                      | $VDAC < VFB < (V_{VDAC} + 100 \text{ mV}) EN = 'HI'$                                                                                                    |      | 3.5            | 6.0  |      |

| I <sub>VDD-1P</sub>                                   | VDD supply current, 1-phase                                      | VDAC < VFB < (V <sub>VDAC</sub> + 100 mV), EN = 'HI'; digital buses idle                                                                                |      | 0.2            | 0.8  |      |

| I <sub>V5STBY</sub>                                   | V5A standby current                                              | EN = 'LO'                                                                                                                                               |      | 125            | 200  |      |

| I <sub>VDDSTBY</sub>                                  | VDD standby current                                              | EN = 'LO'                                                                                                                                               |      | 23             | 40   | μΑ   |

| I <sub>VINTF</sub>                                    | VINTF supply current                                             | All conditions; digital buses idle                                                                                                                      |      | 1.7            | 5.0  |      |

| V <sub>UVLOH</sub>                                    | V5A UVLO 'OK' threshold                                          | V <sub>VFB</sub> < 200 mV. Ramp up; V <sub>VDD</sub> > 3 V; EN = 'HI'; Switching begins.                                                                | 4.2  | 4.4            | 4.52 |      |

| V <sub>UVLOL</sub>                                    | V5A UVLO fault threshold                                         | Ramp down; EN = 'HI'; V <sub>VDD</sub> > 3 V; V <sub>VFB</sub> = 100 mV. Switching stops                                                                | 4.00 | 4.2            | 4.35 |      |

| V <sub>5POR</sub>                                     | V5A fault latch reset threshold                                  | Ramp down. EN = 'HI'; V <sub>VDD</sub> > 3 V. Can restart if V5A rises to V <sub>UVLOH</sub> , and no other faults present.                             | 1.2  | 1.9            | 2.5  |      |

| V <sub>3UVLOH</sub>                                   | VDD UVLO 'OK' threshold                                          | V <sub>VFB</sub> < 200 mV. Ramp up; V <sub>V5A</sub> > 4.5 V; EN = 'HI'; Switching begins.                                                              | 2.5  | 2.8            | 3.0  |      |

| V <sub>3UVLOL</sub>                                   | Fault threshold                                                  | Ramp down; EN = 'HI'; V5A > 4.5 V; VFB = 100 mV. Switching stops.                                                                                       | 2.4  | 2.6            | 2.8  | V    |

| V <sub>3POR</sub>                                     | VDD fault latch                                                  | Ramp down. EN = 'HI'; V5A > 4.5 V. Can restart if VDD goes up to V <sub>3UVLOH</sub> , and no other faults present.                                     | 1.2  | 1.9            | 2.5  |      |

| V <sub>INTFUVLOH</sub>                                | VINTF UVLO OK                                                    | Ramp up; EN = 'HI'; V5A > 4.5 V; VFB = 100 mV.                                                                                                          | 1.4  | 1.5            | 1.6  |      |

| V <sub>INTFUVLOL</sub>                                | VINTF UVLO falling                                               | Ramp down; EN = 'HI'; V5A > 4.5 V; VFB = 100 mV.                                                                                                        | 1.3  | 1.4            | 1.5  |      |

| REFERENCES: V                                         | DAC, VREF, BOOT Voltage                                          |                                                                                                                                                         |      |                | "    |      |

| V <sub>VIDSTP</sub>                                   | VID step size                                                    | Change VID0 HI to LO to HI                                                                                                                              |      | 10             |      |      |

| V <sub>DAC1</sub>                                     |                                                                  | 1.36 V ≤ V <sub>VFB</sub> ≤ 1.52 V, I <sub>OUT</sub> = 0 A                                                                                              | -9   |                | 9    | .,   |

| V <sub>DAC2</sub>                                     | VFB tolerance                                                    | 1.0 V ≤ V <sub>VFB</sub> ≤ 1.35 V; I <sub>OUT</sub> = 0 A                                                                                               | -8   |                | 8    | mV   |

| V <sub>DAC3</sub>                                     |                                                                  | $0.5 \text{ V} \le \text{V}_{VFB} \le 0.99 \text{ V}; I_{OUT} = 0 \text{ A}$                                                                            | -7   |                | 7    |      |

| $V_{VREF}$                                            | VREF output                                                      | VREF output 4.5 V ≤ V <sub>V5A</sub> ≤ 5.5 V, I <sub>VREF</sub> = 0 A                                                                                   | 1.66 | 1.700          | 1.74 | V    |

| V <sub>VREFSRC</sub>                                  | VREF output source                                               | 0 A ≤ I <sub>REF</sub> ≤ 500 μA, HP-2                                                                                                                   | -4   | -3             |      |      |

| V <sub>VREFSNK</sub>                                  | VREF output sink                                                 | -500 A ≤ I <sub>REF</sub> ≤ 0 A, HP-2                                                                                                                   |      | 3              | 4    | mV   |

| $V_{VBOOT}$                                           | Internal VFB initial boot voltage                                | Initial DAC boot voltage                                                                                                                                |      | 0.8            |      | V    |

|                                                       | OLTAGE SENSE: VFB AND GFB                                        |                                                                                                                                                         |      |                |      |      |

| R <sub>VFB</sub>                                      | VFB/GFB Input resistance                                         | Not in fault, disable, or UVLO, V <sub>VFB</sub> = V <sub>DAC</sub> = 1.5 V<br>V <sub>GFB</sub> = 0 V, measure from VFB to GFB                          |      | 50             |      | ΜΩ   |

| V <sub>DELGND</sub>                                   | GFB Differential                                                 | GND to GFB                                                                                                                                              |      | ±100           |      | mV   |

|                                                       | ER, CURRENT AMPLIFIER, CURR                                      |                                                                                                                                                         |      | =:00           |      |      |

| A <sub>V-EA</sub>                                     | Error amplifier total voltage                                    | VFB to DROOP                                                                                                                                            | 80   |                |      | dB   |

| I <sub>EA_SR</sub>                                    | Error amplifier source current                                   | $I_{DROOP}$ , $V_{VFB} = V_{DAC} + 50 \text{ mV}$ , $R_{COMP} = 1 \text{ k}\Omega$                                                                      |      | 1              |      | mA   |

| _,oi\                                                 | Error amplifier sink current                                     | $I_{DROOP}$ , $V_{VFB} = V_{DAC} - 50 \text{ mV}$ , $R_{COMP} = 1 \text{ k}\Omega$                                                                      |      | <u>·</u><br>_1 |      |      |

| IFA SK                                                |                                                                  |                                                                                                                                                         | -500 | 0.2            | 500  | nA   |

| I <sub>EA_SK</sub>                                    | CS pin input bias current                                        | CSPX and CSNX                                                                                                                                           |      |                |      |      |

| I <sub>EA_SK</sub> I <sub>CS</sub> A <sub>CSINT</sub> | CS pin input bias current Internal current sense gain            | CSPx and CSNx  Gain from CSPx – CSNx to PWM comparator,  RSKIP = Open                                                                                   | 5.8  | 6.0            | 6.2  | V/V  |

<sup>(1)</sup> Specified by design. Not production tested.

### **Electrical Characteristics (continued)**

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>OUT</sub>, 0.7 < VFREQ-P  $\leq$  V<sub>VREF</sub> (unless otherwise noted).

|                     | PARAMETER                                                              | CONDITIONS                                      | MIN TYP | MAX | UNIT     |

|---------------------|------------------------------------------------------------------------|-------------------------------------------------|---------|-----|----------|

| RAMP SETTII         | NGS                                                                    |                                                 |         |     |          |

|                     |                                                                        | $R_{RAMP} = 20 \text{ k}\Omega + -1\%$          | 20      |     | ·        |

| .,                  | 0 "                                                                    | $R_{RAMP} = 30 \text{ k}\Omega + /-1\%$         | 60      |     |          |

| JNDERSHOOD          | Compensation ramp amplitude                                            | $R_{RAMP} = 39 \text{ k}\Omega + /-1\%$         | 100     |     | mV       |

|                     |                                                                        | $R_{RAMP} \ge 150 \text{ k}\Omega + /- 1\%$     | 40      |     |          |

| SLEW SETTI          | NGS                                                                    |                                                 | 1       |     |          |

|                     |                                                                        | $R_{SLEW} = 20 \text{ k}\Omega + /-1\%$         | 6       | 10  |          |

| SL <sub>START</sub> | Slew rate setting for VID                                              | $R_{SLEW} = 24 \text{ k}\Omega + /-1\%$         | 12      | 20  |          |

| SL <sub>SET</sub>   | change                                                                 | $R_{SLEW} = 30 \text{ k}\Omega + /- 1\%$        | 18      | 30  | mV/μs    |

|                     |                                                                        | $R_{SLEW} = 39 \text{ k}\Omega + /- 1\%$        | 24      | 40  |          |

| SL <sub>START</sub> | Slew rate setting for start-up (2)                                     | EN goes high, R <sub>SLEW</sub> = 20 kΩ         | 3       | 5   | mV/μs    |

| ADDRESS SE          |                                                                        |                                                 |         |     |          |

|                     |                                                                        | V <sub>SLEWA</sub> ≤ 0.25 V                     | 000b    |     |          |

|                     |                                                                        | 0.35 V ≤ V <sub>SLEWA</sub> ≤ 0.45 V            | 001b    |     |          |

|                     | Address setting 3 LSB of I <sup>2</sup> C<br>Address (ADDR = 100 0xxx) | 0.55 V ≤ V <sub>SLEWA</sub> ≤ 0.65 V            | 010b    |     |          |

|                     |                                                                        | 0.75 V ≤ V <sub>SLEWA</sub> ≤ 0.85 V            | 011b    |     |          |

| ADDR                |                                                                        | 0.95 V ≤ V <sub>SLEWA</sub> ≤ 1.05 V            | 100b    |     |          |

|                     |                                                                        | 1.15 V ≤ V <sub>SLEWA</sub> ≤ 1.25 V            | 101b    |     |          |

|                     |                                                                        | 1.35 V ≤ V <sub>SLEWA</sub> ≤ 1.45 V            | 110b    |     |          |

|                     |                                                                        | 1.55 V ≤ V <sub>SLEWA</sub> ≤ V <sub>VREF</sub> | 111b    |     |          |

| OVERSHOOT           | REDUCTION (OSR) SETTINGS                                               |                                                 |         |     |          |

|                     |                                                                        | $R_{O-USR} = 20 \text{ k}\Omega + /- 1\%$       | 100     |     | <u> </u> |

|                     |                                                                        | $R_{O-USR} = 24 \text{ k}\Omega + /- 1\%$       | 150     |     |          |

| OVERSHOOT           |                                                                        | $R_{O-USR} = 30 \text{ k}\Omega + /- 1\%$       | 200     |     |          |

|                     | Overshoot Reduction (OSR)                                              | $R_{O-USR} = 39 \text{ k}\Omega + /- 1\%$       | 250     |     |          |

| V <sub>OSR</sub>    | Voltage set (3)                                                        | $R_{O-USR} = 56 \text{ k}\Omega + /- 1\%$       | 300     |     | mV       |

|                     |                                                                        | $R_{O-USR} = 75 \text{ k}\Omega + /- 1\%$       | 400     |     |          |

|                     |                                                                        | $R_{O-USR} = 100 \text{ k}\Omega + /- 1\%$      | 500     |     |          |

|                     |                                                                        | $R_{O-USR} = 150 \text{ k}\Omega + /- 1\%$      | OFF     |     |          |

| UNDERSHOO           | OT REDUCTION (USR) SETTINGS                                            |                                                 | 1       |     |          |

|                     |                                                                        | V <sub>O-USR</sub> < 0.25 V                     | 40      |     | ·        |

|                     |                                                                        | 0.35 < V <sub>O-USR</sub> < 0.45 V              | 60      |     |          |

|                     |                                                                        | 0.55 < V <sub>O-USR</sub> < 0.65 V              | 80      |     |          |

| .,                  | Undershoot Reduction (USR)                                             | 0.75 < V <sub>O-USR</sub> < 0.85 V              | 120     |     |          |

| V <sub>USR</sub>    | Voltage set (4)                                                        | 0.95 < V <sub>O-USR</sub> < 1.05 V              | 160     |     | mV       |

|                     |                                                                        | 1.15 < V <sub>O-USR</sub> < 1.25 V              | 200     |     |          |

|                     |                                                                        | 1.35 < V <sub>O-USR</sub> < 1.45 V              | 240     |     |          |

|                     |                                                                        | 1.55 < V <sub>O-USR</sub> < V <sub>VREF</sub>   | OFF     |     |          |

| OVER CUPPE          | ENT PROTECTION (OCP) SETTINGS                                          |                                                 |         |     |          |

<sup>(2)</sup> Specified by design. Not production tested.

<sup>3)</sup> Specified by design. Not production tested.

<sup>(4)</sup> Specified by design. Not production tested.

## **Electrical Characteristics (continued)**

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>OUT</sub>, 0.7 < VFREQ-P  $\leq$  V<sub>VREF</sub> (unless otherwise noted).

|                  | PARAMETER                                         | CONDITIONS                                 | MIN  | TYP  | MAX  | UNIT |

|------------------|---------------------------------------------------|--------------------------------------------|------|------|------|------|

|                  |                                                   | $R_{OCP-I} = 20 \text{ k}\Omega + /- 1\%$  | 5.0  | 7.0  | 9.0  | mV   |

|                  |                                                   | $R_{OCP-I} = 24 \text{ k}\Omega + /- 1\%$  | 7.0  | 10.0 | 13.0 |      |

|                  | OCP voltage (valley current limit at CSPx – CSNx) | $R_{OCP-I} = 30 \text{ k}\Omega + /- 1\%$  | 10.0 | 14.0 | 18.0 |      |

| V                |                                                   | $R_{OCP-I} = 39 \text{ k}\Omega + /- 1\%$  | 15.0 | 19.0 | 23.0 |      |

| V <sub>OCP</sub> |                                                   | $R_{OCP-I} = 56 \text{ k}\Omega + /- 1\%$  | 21.0 | 25.0 | 29.0 |      |

|                  |                                                   | $R_{OCP-I} = 75 \text{ k}\Omega + /- 1\%$  | 28.0 | 32.0 | 36.0 |      |

|                  |                                                   | $R_{OCP-I} = 100 \text{ k}\Omega + /- 1\%$ | 36.0 | 40.0 | 44.0 |      |

|                  |                                                   | $R_{OCP-I} = 150 \text{ k}\Omega + /- 1\%$ | 45.0 | 49.0 | 53.0 |      |

## **Electrical Characteristics (continued)**

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>OUT</sub>, 0.7 < VFREQ-P  $\leq$  V<sub>VREF</sub> (unless otherwise noted).

|                      | PARAMETER                       | CONDITIONS                                                           | MIN  | TYP  | MAX      | UNIT |  |

|----------------------|---------------------------------|----------------------------------------------------------------------|------|------|----------|------|--|

| CURRENT MO           | ONITOR (IMON)                   |                                                                      |      |      |          |      |  |

|                      |                                 | $\Sigma \Delta CS = 0 \text{ mV}, A_{\text{IMON}} = 3.867$           | 00h  | 00h  | 03h      |      |  |

| \/AI                 | IMON ARG. A. A.                 | $\Sigma \Delta CS = 4.5 \text{ mV}, A_{IMON} = 3.867$                | 12h  | 19h  | 20h      |      |  |

| VAL <sub>ADC</sub>   | IMON ADC output                 | $\Sigma \Delta CS = 22 \text{ mV}, A_{\text{IMON}} = 3.867$          | 79h  | 80h  | 87h      |      |  |

|                      |                                 | $\Sigma \Delta CS = 44 \text{ mV}, A_{\text{IMON}} = 3.867$          | FAh  | FFh  | FFh      |      |  |

| LR <sub>IMON</sub>   | IMON linear range               | Each phase, CSPx – CSNx                                              | 50   |      |          | mV   |  |

| PROTECTION           | I: OVP, UVP, PGOOD              |                                                                      |      |      | <u>'</u> |      |  |

| V <sub>OVPH</sub>    | Fixed OVP voltage               | V <sub>CSN1</sub> > V <sub>OVPH</sub> for 1 μs                       | 1.60 | 1.70 | 1.80     | V    |  |

| R <sub>SFTSTP</sub>  | Soft-stop transistor resistance | Connected to CSN1                                                    |      | 100  | 200      | Ω    |  |

| $V_{PGDH}$           | PGOOD high threshold            | Measured at the VFB pin with respect to VID code, device latches OFF | 185  |      | 245      | \/   |  |

| $V_{PGDL}$           | PGOOD low threshold             | Measured at the VFB pin with respect to VID code, device latches OFF | -348 | -348 |          | mV   |  |

| PWM AND SH           | (IP OUTPUTS: I/O VOLTAGE AND CU | IRRENT                                                               |      |      | <u>'</u> |      |  |

| $V_{P-S\_L}$         | PWMx / SKIP – Low               | $I_{LOAD} = \pm 1 \text{ mA}$                                        |      | 0.15 | 0.3      |      |  |

| V <sub>P-S_H</sub>   | PWMx / SKIP – High              | $I_{LOAD} = \pm 1 \text{ mA}$                                        | 4.2  |      |          | V    |  |

| V <sub>PW-SKLK</sub> | PWMx / SKIP 3-state             | $I_{LOAD} = \pm 100 \mu A$                                           | 1.6  | 1.7  | 1.8      |      |  |

| LOGIC INTER          | FACE: VOLTAGE AND CURRENT       |                                                                      |      |      |          |      |  |

| R <sub>VRTTL</sub>   | Dull-desses assistants          | SDA, V = 0.31 V                                                      | 4    |      | 15       | 0    |  |

| R <sub>VRPG</sub>    | Pulldown resistance             | PGOOD, V = 0.31 V                                                    |      | 36   | 50       | Ω    |  |

| I <sub>VRTTLK</sub>  | Logic leakage current           | SDA, SCL = 1.8 V, PGOOD = 3.3 V                                      | -2   | 0.2  | 2        | μA   |  |

| V <sub>IL,I2C</sub>  | Low-level input voltage         | COL CDA VINTE 4 0 V                                                  |      |      | 0.6      |      |  |

| V <sub>IH,I2C</sub>  | High-level input voltage        | SCL, SDA, VINTF = 1.8 V                                              | 1.2  |      |          | V    |  |

| $V_{IL,EN}$          | EN Low-level input voltage      |                                                                      |      |      | 0.5      |      |  |

| V <sub>IH,EN</sub>   | EN High-level input voltage     |                                                                      | 1.3  |      |          | V    |  |

| I <sub>ENH</sub>     | I/O leakage, EN                 | Leakage current , V <sub>EN</sub> = 1.8 V                            |      | 24   | 40       | μΑ   |  |

| VBAT INPUT           | RESISTANCE                      |                                                                      |      |      |          |      |  |

| <b>D</b>             | VDAT                            | EN = HI                                                              |      | 550  |          | kΩ   |  |

| R <sub>VBAT</sub>    | VBAT resistance                 | EN = LOW                                                             |      | 50   |          | ΜΩ   |  |

#### 6.6 Timing Requirements

The device, TPS59632Q1, requires the ENABLE signal on Pin 8 to go from low to high only after the V5A (5-V supply), the VDD (3.3-V supply) and the VBAT rails have gone high.

#### 6.7 Switching Characteristics

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>CORE</sub> (unless otherwise noted).

|                       | PARAMETER                                    | CONDITIONS                                                                                   | MIN | TYP | MAX | UNIT |  |

|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| TIMERS: STA           | TIMERS: START-UP, PWM ON-TIME AND I/O TIMING |                                                                                              |     |     |     |      |  |

| t <sub>START-CB</sub> | Cold boot time                               | $V_{BOOT}$ > 0V , EN = high, time from UVLO to VOUT ramp, $C_{REF}$ = 0.33 $\mu F$           |     |     | 1.2 | ms   |  |

| t <sub>STBY-E</sub>   | STBY exit time                               | Time from EN assertion until PGOOD goes high. $V_{VID}$ = 1.28 V, $R_{SLEW}$ = 39 k $\Omega$ |     |     | 250 | μs   |  |

| t <sub>PGDDGLTO</sub> | PGOOD deglitch time                          | Time from VFB out of 250 mV VDAC boundary to PGOOD low.                                      |     | 1   |     |      |  |

| t <sub>PGDDGLTU</sub> | PGOOD deglitch time                          | Time from VFB out of –300 mV VDAC boundary to PGOOD low.                                     |     | 31  |     | μs   |  |

## **Switching Characteristics (continued)**

Over recommended temperature range, 4.5 V  $\leq$  V<sub>V5A</sub>  $\leq$  5.5 V, 3.0 V  $\leq$  V<sub>VDD</sub>  $\leq$  3.6 V, V<sub>GFB</sub> = GND, V<sub>VFB</sub> = V<sub>CORE</sub> (unless otherwise noted).

|                      | PARAMETER                               | CONDITIONS                                                                                  | MIN                                                                | TYP | MAX | UNIT |

|----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------|

|                      |                                         | $R_F = 24 \text{ k}\Omega, V_{BAT} = 12 \text{ V}, V_{VFB} = 1 \text{ V} (400 \text{ kHz})$ |                                                                    | 230 |     |      |

|                      | PWM ON-time                             | $R_F = 39 \text{ k}\Omega, V_{BAT} = 12 \text{ V}, V_{VFB} = 1 \text{ V} (600 \text{ kHz})$ |                                                                    | 164 |     |      |

| ton                  | PWW ON-time                             | $R_F = 75 \text{ k}\Omega, V_{BAT} = 12 \text{ V}, V_{VFB} = 1 \text{ V} (800 \text{ kHz})$ |                                                                    | 140 |     | ns   |

|                      |                                         |                                                                                             | $R_F$ = 150 k $\Omega$ , $V_{BAT}$ = 12 V, $V_{VFB}$ = 1 V (1 MHz) |     | 122 |      |

| t <sub>OFF_MIN</sub> | Controller minimum OFF time             | Fixed value                                                                                 | 20                                                                 |     |     |      |

| t <sub>ON_MIN</sub>  | Controller minimum ON time              | $R_{CF} = 150 \text{ k}\Omega, V_{BAT} = 20 \text{ V}, V_{VFB} = 0 \text{ V}$               | 20                                                                 |     |     | ns   |

| t <sub>VCCVID</sub>  | VID change to VFB change <sup>(1)</sup> | ACK of VID change command to start of voltage ramp                                          |                                                                    |     | 1   | μs   |

| t <sub>PG2</sub>     | PGOOD low after enable goes low         | Low-state time after EN goes low.                                                           | 225                                                                | 250 | 275 | μs   |

| PWM OUTPU            | TS: I/O VOLTAGE AND CURRENT             |                                                                                             |                                                                    |     |     |      |

| t <sub>P-S_H-L</sub> | PWMx H-L transition time                | 10 to 90%, both edges                                                                       |                                                                    | 7   | 20  |      |

| t <sub>P-S_TRI</sub> | PWMx 3-state transition                 | 10 or 90% to 3-state level, both edges                                                      | 5 20                                                               |     | 20  | ns   |

<sup>(1)</sup> Specified by design. Not production tested.

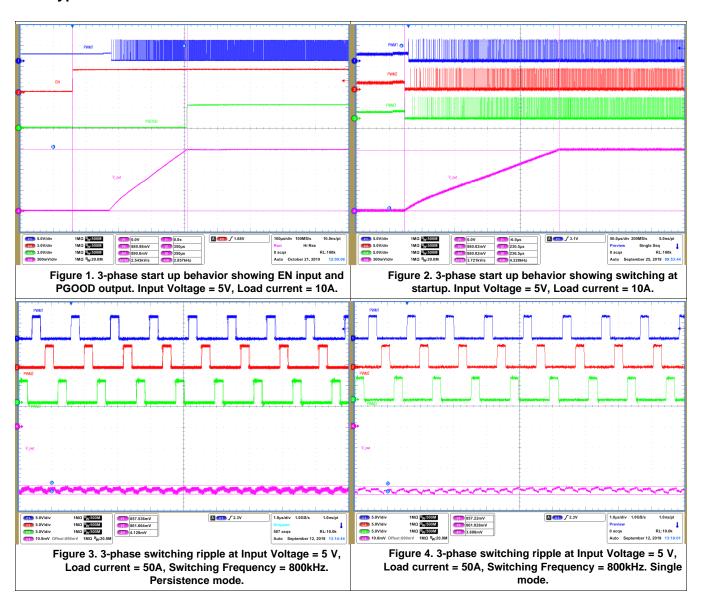

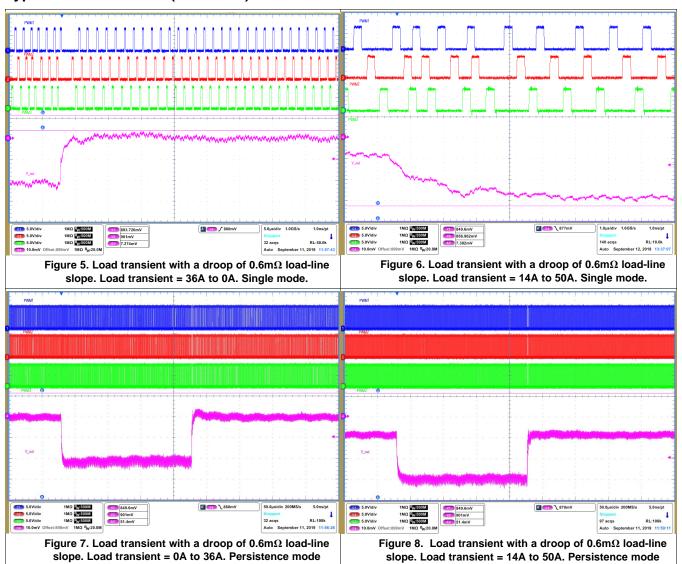

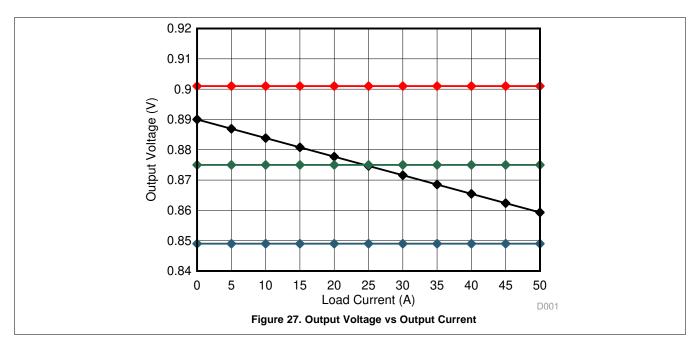

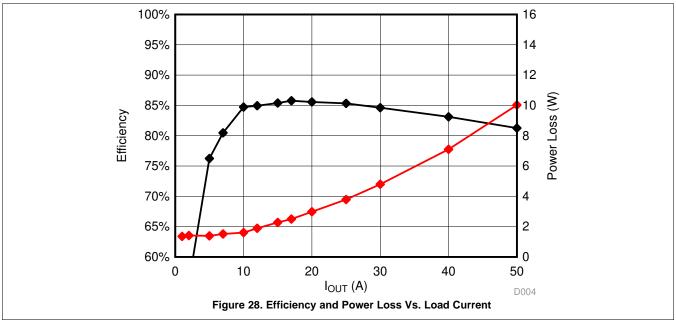

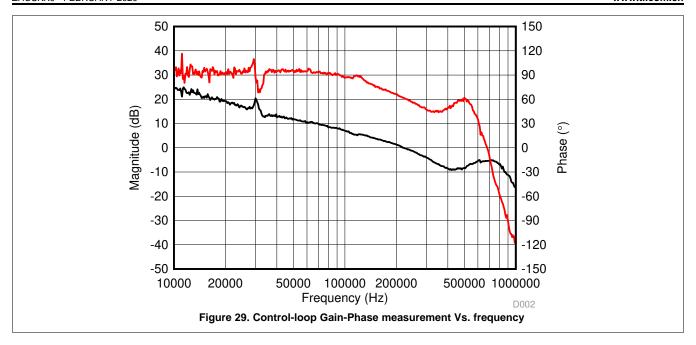

#### 6.8 Typical Characteristics

#### **Typical Characteristics (continued)**

www.ti.com.cn ZHCSKX0 – FEBRUARY 2020

### 7 Detailed Description

#### 7.1 Overview

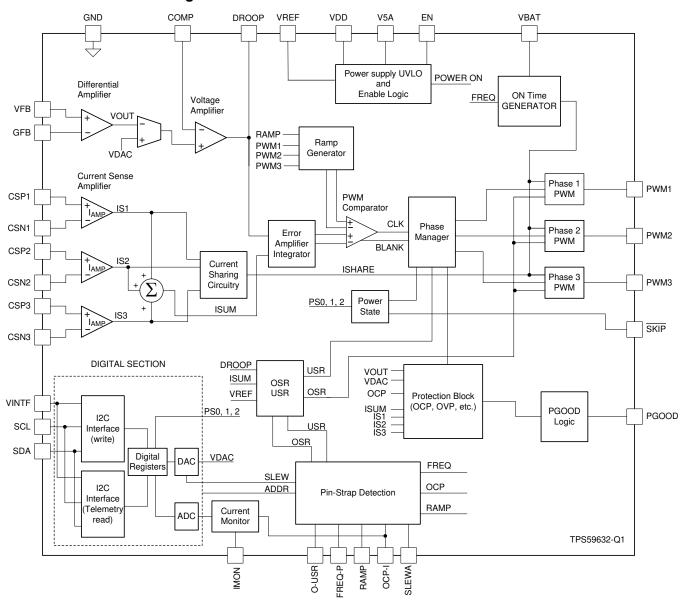

The TPS59632-Q1 device is a DCAP+ mode adaptive on-time controller. The DAC outputs a reference in accordance with the 8-bit VID code, as defined in Table 3. This DAC sets the output voltage.

In adaptive on-time converters, the controller varies the on-time as a function of input and output voltage to maintain a nearly constant frequency during steady-state conditions. With conventional voltage-mode constant on-time converters, each cycle begins when the output voltage crosses to a fixed reference level. However, in the TPS59632-Q1 device, the cycle begins when the current feedback reaches an error voltage level, which corresponds to the amplified difference between the DAC voltage and the feedback output voltage. In the case of 2-phase or 3-phase operation, the device sums the current feedback from all the phases at the output of the internal current-sense amplifiers.

This approach has two advantages:

- The amplifier DC gain sets an accurate linear load-line slope, which is required for CPU core applications.

- The device filters the error voltage input to the PWM comparator to improve the noise performance.

In addition, the difference between the DAC-to-output voltage and the current feedback goes through an integrator to give an approximately linear load-line slope even at light loads where the inductor current is in discontinuous conduction mode (DCM).

During a steady-state condition, the phases of the TPS59632-Q1 device switch 180° phase-displacement for 2-phase mode and 120° phase-displacement for 3-phase mode. The phase displacement is maintained both by the architecture and current ripple. The architecture does not allow the high-side gate drive outputs of more than one phase to be ON in any condition except transients. The current ripple forces the pulses to be spaced equally. The controller forces current-sharing adjusting the ON time of each phase. Current balancing requires no user intervention, compensation, or extra components.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

### 7.3.1 PWM Operation

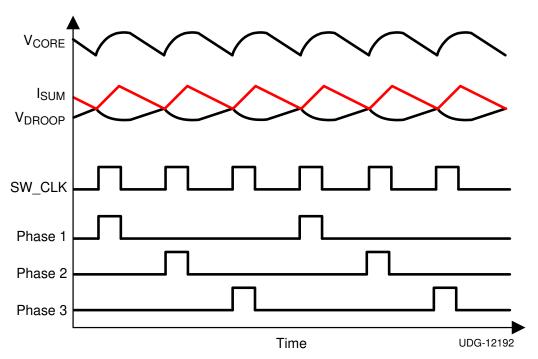

The functional block diagram and Figure 9 shows how the converter operates in CCM.

#### **Feature Description (continued)**

Figure 9. D-Cap+ Mode Basic Waveforms

Starting with the condition that the high-side FETs are off and the low-side FETs are on, the summed current feedback ( $I_{SUM}$ ) is higher than the error amplifier output ( $V_{DROOP}$ ).  $I_{SUM}$  falls until it hits  $V_{DROOP}$ , which contains a component of the output ripple voltage. The PWM comparator senses where the two waveforms cross and triggers the on-time generator, which generates the internal SW\_CLK signal. Each SW\_CLK signal corresponds to one switching ON pulse for one phase.

During single-phase operation, every SW\_CLK signal generates a switching pulse on the same phase. Also, I<sub>SUM</sub> voltage corresponds to a single-phase inductor current only.

During multi-phase operation, the controller distributes the SW\_CLK signal to each of the phases in a cycle. Using the summed inductor current and cyclically distributing the ON pulses to each phase automatically gives the required interleaving of 360 / n, where n is the number of phases.

#### 7.3.2 Current Sensing

The TPS59632-Q1 provides independent channels of current feedback for every phase, to increase the system accuracy and reduce the dependence of circuit performance on layout compared to an externally summed architecture. The design can use *inductor DCR sensing* to yield the best efficiency or *resistor current sensing* to yield the most accuracy across wide temperature ranges. As inductor DCR sensing is not suitable for automotive applications due to wide variation in current sensing across temperature, resistor sensing is recommended. This sense resistor must be connected in series with the inductor and requires Kelvin sensing terminals for improved current sense accuracy.

The pins CSP1, CSN1, CSP2, CSN2, CSP3, and CSN3 are the inductor current sensing pins for the each of the three phases of the converter.

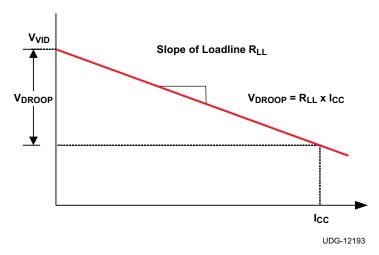

#### 7.3.3 Load-line (Droop)

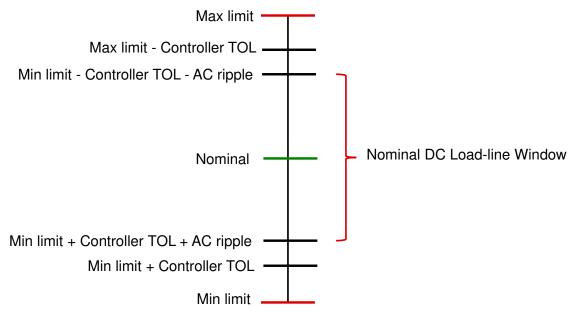

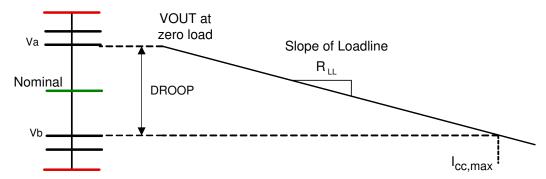

The TPS59632-Q1 features programmable droop enabling significant reduction of output capacitors. Figure 10 shows the output voltage droop with increasing load current.

## TEXAS INSTRUMENTS

#### **Feature Description (continued)**

Figure 10. Load-Line Slope

$$V_{DROOP} = R_{LL} \times I_{CC} = \frac{R_{CS(eff)} \times A_{CS} \times I_{CC}}{A_{DROOP}}$$

where

- R<sub>CS(eff)</sub> is the effective current sense resistance, when using either a sense resistor or inductor DCR

- · A<sub>CS</sub> is the gain of the current sense amplifier

- I<sub>CC</sub> is the load current

$$A_{DROOP} = 1 + \left(\frac{R_{DROOP}}{R_{COMP}}\right)$$

where

- $\bullet \quad$  resistor,  $R_{\text{DROOP}}$  is connected between the DROOP pin and the COMP pin

- resistor R<sub>COMP</sub> is connected between the COMP pin and the VREF pin

This load-line aids in the transient performance as discussed in the following section.

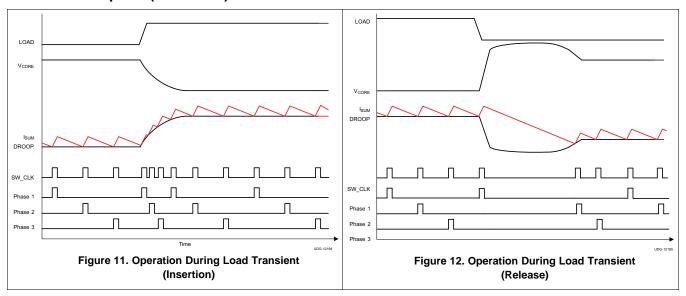

#### 7.3.4 Load Transients

When the load increases suddenly, the output voltage immediately drops. This voltage drop is reflected as a rising voltage on the DROOP pin. This rising voltage forces the PWM to pulse sooner and more frequently, which causes the inductor current to rapidly increase. As the inductor current reaches the new load current, a steady-state operating condition is reached and the PWM switching resumes the steady-state frequency. Similarly, when the load releases suddenly, the output voltage rises. This rise is reflected as a falling voltage on the DROOP pin. This rising voltage forces a delay in the PWM pulses until the inductor current reaches the new load current, when the switching resumes and steady-state switching continues.

For simplicity, neither Figure 11 or Figure 12 show the ripple on the output  $V_{\text{CORE}}$  nor the DROOP waveform.

#### **Feature Description (continued)**

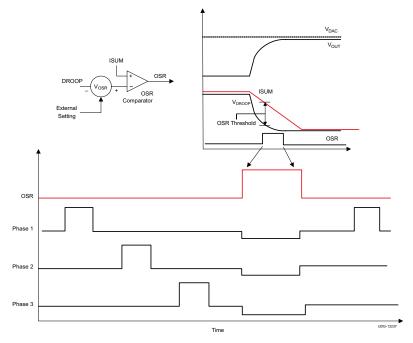

#### 7.3.5 Overshoot Reduction (OSR)

The problem of overshoot in synchronous buck converters results from the output inductor having a small voltage  $(V_{OLIT})$  with which to respond to a transient load release.

With overshoot reduction feature enabled, when the output voltage increases beyond a value that corresponds to a voltage difference between the ISUM voltage and the DROOP pin voltage exceeding the specified OSR voltage (as specified in the Electrical Characteristics table), at the instant that the low-side drivers are turned OFF. When the low-side driver is turned OFF, the energy in the inductor is partially dissipated by the body diodes. As the overshoot reduces, the low-side drivers are turned ON again. Figure 13 shows overshoot reduction by turning off the low-side MOSFET during load transient release.

Figure 13. Overshoot Reduction

## TEXAS INSTRUMENTS

#### **Feature Description (continued)**

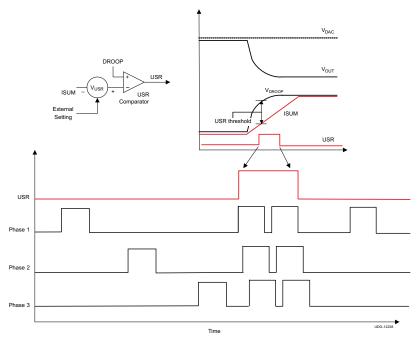

#### 7.3.6 Undershoot Reduction (USR)

When the transient load increase becomes quite large, it is difficult to meet the energy demanded by the load especially at lower input voltages. Then it is necessary to quickly increase the energy in the inductors during the transient load increase. This increase is achieved by enabling pulse overlapping. In order to maintain the interleaving of the multi-phase configuration while maintaining pulse-overlapping during load-insertion, the undershoot reduction (USR) mode is entered only when necessary. This device enters this mode is when the difference between DROOP voltage and ISUM voltage exceeds the USR voltage level specified in the Electrical Characteristics table.

Figure 14 shows the undershoot reduction operation. This feature allows for the use of reduced output capacitance while continuing to meet the specification. The device achieves undershoot reduction by overlapping of pulses on all the phases.

Figure 14. Undershoot Reduction

When the transient condition is completed, the interleaving of the phases is resumed.

It should be noted that single-phase mode there is no USR mode of operation.

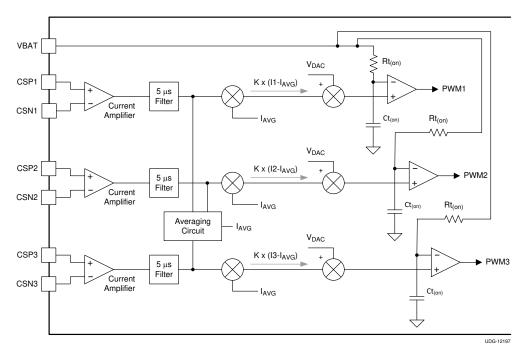

#### 7.3.7 Autobalance Current Sharing

The basic mechanism for current sharing is to sense the average phase current, then adjust the pulse width of each phase to equalize the current in each phase.

The PWM comparator (not shown) starts a pulse when the feedback voltage equals the reference voltage. The VBAT voltage charges  $C_{t(on)}$  through the resistor  $R_{t(on)}$ . The pulse is terminated when the voltage at capacitor  $C_{t(on)}$  matches the on-time  $(t_{ON})$  reference, usually the DAC voltage  $(V_{DAC})$ .

A current sharing circuit is shown in Figure 15. For example, assume that the 5- $\mu$ s-averaged value of I1 = I2 = I3. In this case, the PWM modulator terminates at  $V_{DAC}$ , and the typical pulse width is delivered to the system. If instead, I1 > I<sub>AVG</sub>, then an offset is subtracted from  $V_{DAC}$ , and the pulse width for phase one is shortened, reducing the current in phase one to compensate. If I1 < I<sub>AVG</sub>, then a longer pulse is produced, again compensating on a pulse-by-pulse basis.

#### **Feature Description (continued)**

Figure 15. Autobalance Current Sharing

#### 7.3.8 PWM And SKIP Signals

The PWM and SKIP signals are outputs of the controller and serve as input to the MOSFET gate driver or DrMOS-type devices. Both signals are 5-V logic signals. The PWM signals are logic high to allow the high-side drive of the external gate driver to turn ON. The PWM signal must be low for the low-side drive of the external gate driver to turn ON. To drive both the signals are OFF, the PWM is set to tri-state. The SKIP signal is active low to set all the phases in Continuous Conduction Mode (CCM) of operation. If SKIP signal is high then the external gate driver turns OFF the Low-side drive to operate in the boundary of CCM and Discontinuous Conduction Mode (DCM).

#### 7.3.9 Bias Power (V5A, VDD, And VINTF) UVLO

The TPS59632-Q1 device continuously monitors the voltage on the V5A, VDD, and VINTF pin to ensure a value high enough to bias the device properly and provide sufficient gate drive potential to maintain high efficiency. The converter starts with approximately 4.4 V and has a nominal 200 mV of hysteresis. Once the 5VA,VDD, or VINTF goes below the  $V_{\rm UVIOL}$ , the corresponding voltage must fall below  $V_{\rm POR}$  (1.5 V) to reset the device.

The input ( $V_{BAT}$ ) does not include a UVLO function, so the circuit runs with power inputs as low as approximately  $3 \times V_{OUT}$ .

#### 7.3.10 Start-Up Sequence

The TPS59632-Q1 device initializes when all of the supplies rise above the UVLO thresholds. This function is also know as a *cold boot*. The device then reads all of the various settings (such as frequency and overcurrent protection). This process takes less than 1.2 ms. During this time, the VSR initializes to the BOOT voltage. The output voltage rises to the VSR level when the EN pin (enable) goes high. Once the BOOT sequence completes, PGOOD is HIGH and the I<sup>2</sup>C interface can be used to change the voltage select register (VSR). The current VSR value is held when EN goes low and returns to a high state This function is also known as a *warm boot*.

## TEXAS INSTRUMENTS

#### **Feature Description (continued)**

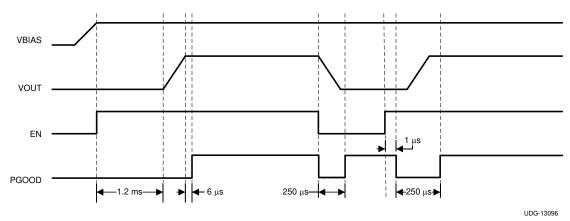

#### 7.3.11 Power Good Operation

PGOOD is an open-drain output pin that is designed to be pulled-up with an external resistor to a voltage 3.6 V or less. Normal PGOOD operation (exclusive of activation of any faults) is shown in Figure 16. On initial power-up PGOOD happens within 6 μs of the DAC reaching its target value. When EN is brought low, PGOOD is also brought low for 250 μs, then is allowed to float. The TPS59632-Q1 device pulls down the PGOOD signal when the EN signal subsequently goes high and returns high again within 6 μs of the end of the DAC ramp. The delay period between EN going high and PGOOD going low in this case is less than 1 μs. Figure 16 shows the power good operation at initial start-up and with falling and rising EN.

For applications where it is undesirable to have PGOOD high when EN is low, an alternate method of pulling up the open-drain PGOOD signal is possible. In this method, the PGOOD is pulled up to EN logic signal. This ensures that the PGOOD is low when EN goes low.

Figure 16. Power Good Operation

#### 7.3.12 Analog Current Monitor, IMON, And Corresponding Digital Output Current

The TPS59632-Q1 device includes a current monitor function. The current monitor supplies an analog voltage, proportional to the load current, on the IMON pin.

The current monitor function is related to the OCP selection resistors. The R<sub>OCP</sub> is the resistor between the OCP-I pin and GND and R<sub>CIMON</sub> is the resistor between the IMON pin to the OCP-I pin that sets the current monitor gain. Equation 3 shows the calculation for the current monitor gain.

$$V_{IMON} = 10 \times 1 + \frac{(R_{IMON})}{(R_{OCP})} \times \sum V_{CSn} \xrightarrow{yields} V$$

where

Σ V<sub>CS</sub> is the sum of the DC voltages at the inputs to the current sense amplifiers

To ensure stable current monitor operation, and at the same time, provide a fast dynamic response, connect a 4.7-nF to 10-nF capacitor from the IMON pin to GND. Connecting higher capacitance will reduce the response

time accordingly.

The analog current monitor should be set so that at the maximum processor current ( $I_{CC(max)}$ ) the IMON voltage

The analog current monitor should be set so that at the maximum processor current (I<sub>CC(max)</sub>) the IMON voltage should be 1.7 V. This setting corresponds to a digital output current value of 'FF' in the telemetry register 03H through I2C. For any other IMON voltage output in the range of 0 to 1.7 V, the digital output varies linearly.

#### 7.3.13 Fault Behavior

TPS59632-Q1 device has a complete suite of fault detection and protection functions, including input undervoltage lockout on all power inputs, over voltage and over current limiting, and output under voltage detection. The protection limits are given in the tables above. The converter suspends switching when the limits are exceeded and PGOOD goes low. In this state, the fault register 14h can be read. To exit fault protection mode, the bias power (V5A, VDD and VINTF) must be cycled as described in Bias Power (V5A, VDD, And VINTF) UVLO.

(3)

#### **Feature Description (continued)**

#### 7.3.14 Output Under Voltage Protection (UVP)

Output undervoltage protection works in conjunction with the current protection described in the Over Current Protection (OCP) section. If V<sub>OUT</sub> drops below the low PGOOD voltage threshold, then the PWM is tri-stated. The device stays off until the V5A, VDD or VINTF power is cycled and EN goes high.

#### 7.3.15 Output Over Voltage Protection (OVP)

An OVP condition is detected when the output voltage is greater than the PGDH voltage, and greater than VDAC.  $V_{OUT} > + V_{PGDH}$  greater than VDAC. In this case, the controller device sets PGOOD inactive, and keeps all the PWM signals low so as to keep the low-side driver ON at the converter. The converter remains in this state until the controller device is reset by cycling V5A, VDD or VINTF. This is the first level of OVP. This first level of OVP is inactive during VID transitions. There is a second OVP level fixed at  $V_{OVPH}$  which is always active. If the fixed OVP condition is detected, the PGOOD is forced inactive and the PWM signals are kept low and the operation is similar to the first level of OVP detection

#### 7.3.16 Over Current Protection (OCP)

The TPS59632-Q1 device uses a inductor valley current limiting scheme, so the ripple current must be considered. The DC current value at OCP is the OCP limit value plus half of the ripple current. Current limiting occurs on a phase-by-phase and pulse-by-pulse basis. Generally, the current is sensed using the sense resistor in series with the inductor for automotive applications giving a voltage between the CSPx and CSNx pins. If this sensed voltage is above the OCP limit, the converter delays the next ON pulse until that voltage difference drops below the OCP limit.

In OCP mode, the voltage drops until the UVP limit is reached. When UVP limit is reached the operation follows as described in the Output Under Voltage Protection (UVP).

#### 7.3.17 Over Current Warning

$I^2$ C programming enables this function. The TPS59632-Q1 device pulls down the voltage on the PGOOD pin whenever the valley current reaches 70% of the OCP value (or higher). PGOOD resumes normal function when the value falls below 65% of the OCP value.

#### 7.3.18 Input Voltage Limits

The minimum input voltage is limited by the number of input phases, the switching frequency and the output voltage. The minimum input voltage increases with required maximum output voltage and switching frequency. See Table 1 for limits in 3-phase operating mode and Table 2 for limits in 2-phase operating mode. In 1-phase mode, the operation is limited by controller's capability to 2.5 V for all output voltages and switching frequency.

Table 1. Minimum Input Voltage ( $V_{IN,\ MIN}$ ) Limits Versus Switching Frequency ( $F_{SW}$ ) and Maximum Output Voltage ( $V_{OUT,\ MAX}$ ) in 3-phase operation

| V <sub>OUT,MAX</sub> (V) | F <sub>SW</sub> (kHz) | V <sub>IN, MIN</sub> (V) |

|--------------------------|-----------------------|--------------------------|

| 0.9                      | 800                   | 3.6                      |

| 0.8                      | 1000                  | 4.0                      |

| 0.9                      | 800                   | 4.0                      |

|                          | 1000                  | 4.5                      |

| 1.0                      | 800                   | 4.5                      |

| 1.0                      | 1000                  | 5.0                      |

Table 2. Minimum Input Voltage ( $V_{IN,\ MIN}$ ) Limits Versus Switching Frequency ( $F_{SW}$ ) and Maximum Output Voltage ( $V_{OUT,\ MAX}$ ) in 2-phase operation

| V <sub>OUT,MAX</sub> (V) | F <sub>SW</sub> (kHz) | V <sub>IN, MIN</sub> (V) |

|--------------------------|-----------------------|--------------------------|

| 0.8                      | 1000                  | 2.5                      |

| 0.9                      | 1000                  | 2.5                      |

| 1.0                      | 1000                  | 2.8                      |

## TEXAS INSTRUMENTS

#### 7.3.19 VID Table

The Table 3 shows the VID table for all the programmable DAC voltage levels.

#### Table 3. TPS59632-Q1 VID Table

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | VOLTAGE |

|------|------|------|------|------|------|------|-----|---------|

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 19  | 0.5000  |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1A  | 0.5100  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1B  | 0.5200  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1C  | 0.5300  |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1D  | 0.5400  |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1E  | 0.5500  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1F  | 0.5600  |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 20  | 0.5700  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 21  | 0.5800  |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 22  | 0.5900  |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 23  | 0.6000  |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 24  | 0.6100  |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 25  | 0.6200  |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 26  | 0.6300  |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 27  | 0.6400  |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 28  | 0.6500  |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 29  | 0.6600  |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 2A  | 0.6700  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 2B  | 0.6800  |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 2C  | 0.6900  |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 2D  | 0.7000  |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 2E  | 0.7100  |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 2F  | 0.7200  |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 30  | 0.7300  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 31  | 0.7400  |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 32  | 0.7500  |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 33  | 0.7600  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 34  | 0.7700  |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 35  | 0.7800  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 36  | 0.7900  |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 37  | 0.8000  |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 38  | 0.8100  |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 39  | 0.8200  |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | ЗА  | 0.8300  |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 3B  | 0.8400  |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 3C  | 0.8500  |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 3D  | 0.8600  |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 3E  | 0.8700  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 3F  | 0.8800  |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 40  | 0.8900  |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 41  | 0.9000  |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 42  | 0.9100  |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 43  | 0.9200  |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 44  | 0.9300  |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 45  | 0.9400  |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 46  | 0.9500  |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 47  | 0.9600  |

## Table 3. TPS59632-Q1 VID Table (continued)

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | VOLTAGE |

|------|------|------|------|------|------|------|-----|---------|

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 48  | 0.9700  |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 49  | 0.9800  |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 4A  | 0.9900  |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 4B  | 1.0000  |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 4C  | 1.0100  |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 4D  | 1.0200  |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 4E  | 1.0300  |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 4F  | 1.0400  |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 50  | 1.0500  |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 51  | 1.0600  |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 52  | 1.0700  |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 53  | 1.0800  |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 54  | 1.0900  |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 55  | 1.1000  |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 56  | 1.1100  |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 57  | 1.1200  |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 58  | 1.1300  |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 59  | 1.1400  |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 5A  | 1.1500  |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 5B  | 1.1600  |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 5C  | 1.1700  |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 5D  | 1.1800  |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 5E  | 1.1900  |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 5F  | 1.2000  |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 60  | 1.2100  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 61  | 1.2200  |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 62  | 1.2300  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 63  | 1.2400  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 64  | 1.2500  |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 65  | 1.2600  |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 66  | 1.2700  |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 67  | 1.2800  |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 68  | 1.2900  |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 69  | 1.3000  |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 6A  | 1.3100  |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 6B  | 1.3200  |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 6C  | 1.3300  |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 6D  | 1.3400  |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 6E  | 1.3500  |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 6F  | 1.3600  |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 70  | 1.3700  |