## DAC101C081, DAC101C081Q, DAC101C085

ZHCSEO3B - APRIL 2012 - REVISED JANUARY 2016

# **DAC101C08xx 10** 位微功耗 数模转换器,具有 **I**<sup>2</sup>**C** 兼容接口

#### 1 特性

- 确保单调性达 10 位

- 低功耗运行: 3.3V 时的最大电流为 156µA

- 扩展的电源范围(2.7V至5.5V)

- I<sup>2</sup>C 兼容双线接口,支持标准 (100kHz)、快速 (400kHz) 和高速 (3.4MHz) 三种模式

- 轨到轨电压输出

- 超小型封装

- DAC101C081Q 采用汽车级流程制造,符合 AEC-Q100 1 级标准

- 分辨率: 10 位

- 积分非线性 (INL): ±2 最低有效位 (LSB) (最大值)

- 差分非线性 (DNL): +0.3/-0.2 最低有效位 (LSB) (最大值)

- 稳定时间: 6µs(最大值)

- 零码误差: +10mV(最大值)

- 满量程误差: -0.7 %FS (最大值)

- 电源(正常工作): 380μW (3V)/730μW (5V) (典型值)

- 电源(省电模式): 0.5μW (3V)/0.9μW (5V)(典型 値)

#### 2 应用

- 工业过程控制

- 便携式仪器

- 数字增益和偏移调整

- 可编程电压源和电流源

- 测试设备

- 汽车

## 3 说明

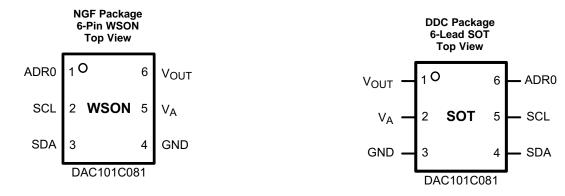

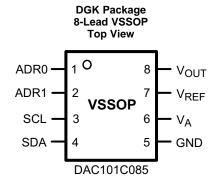

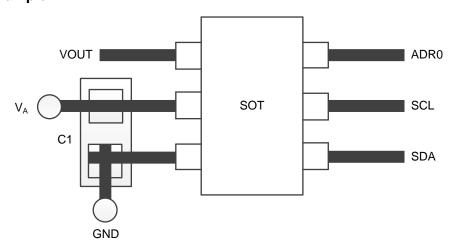

DAC101C081 器件是一款 10 位、单通道、电压输出数模转换器 (DAC),工作电源范围为 2.7V 至 5.5V。输出放大器支持轨到轨输出摆幅,并且具有 6μs 的稳定时间。DAC101C081 使用电源作为基准以提供最宽的动态输出范围,在 5.0V 电压下工作时通常仅消耗 132μA 电流。该器件采用 6 引脚小外形尺寸晶体管(SOT)和晶圆级小外形无引线 (WSON) 封装,并且提供三种地址选项(可通过引脚选择)。

DAC101C085 是一款替代产品,提供有 9 种 I<sup>2</sup>C™寻址选项且使用外部基准。该器件采用 8 引脚超薄小外形尺寸封装 (VSSOP) 封装,并且与 DAC101C081 具有相同的性能和稳定时间。

DAC101C081 和 DAC101C085 采用双线 I<sup>2</sup>C 兼容串行接口,支持包括高速模式 (3.4MHz) 在内的全部三种速度模式。凭借外部地址选择引脚,每条双线总线上最多可连接 3 个 DAC101C081 或 9 个 DAC101C085 器件。此外,还提供有与 DAC101C081 引脚兼容的替代产品,可提供更多的地址选项。

器件信息(1)

| WILLIAM.    |           |                 |  |  |  |  |  |

|-------------|-----------|-----------------|--|--|--|--|--|

| 器件型号        | 封装        | 封装尺寸 (标称值)      |  |  |  |  |  |

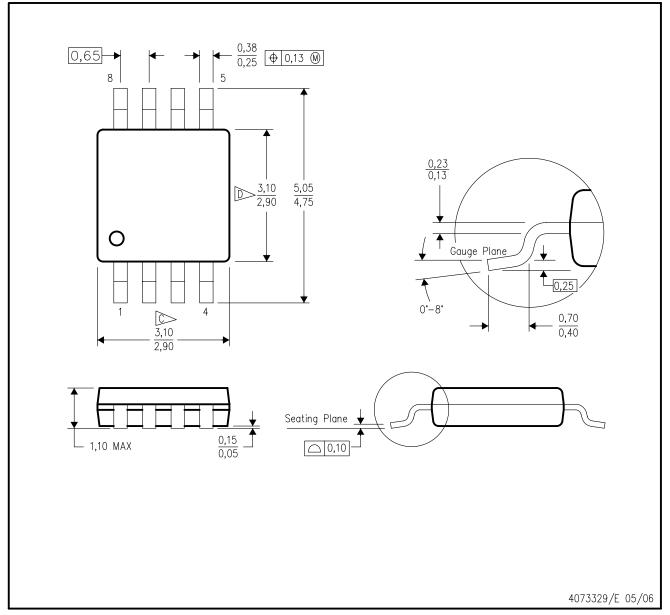

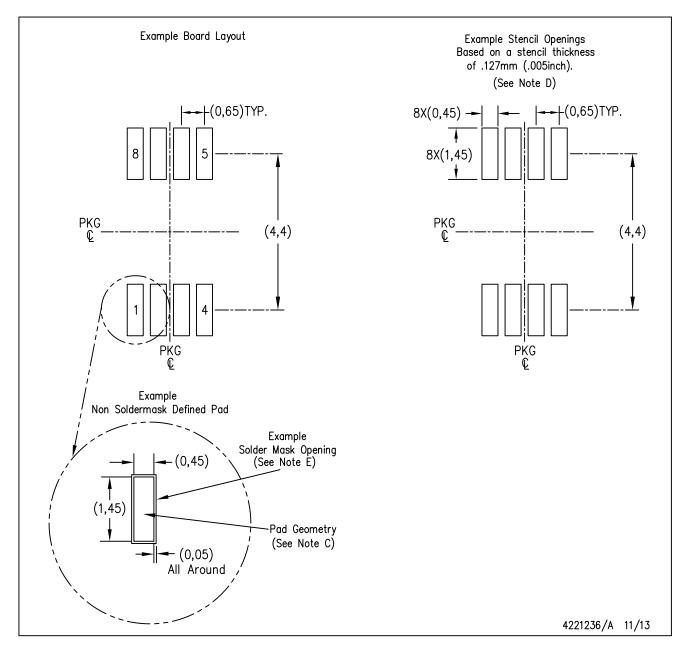

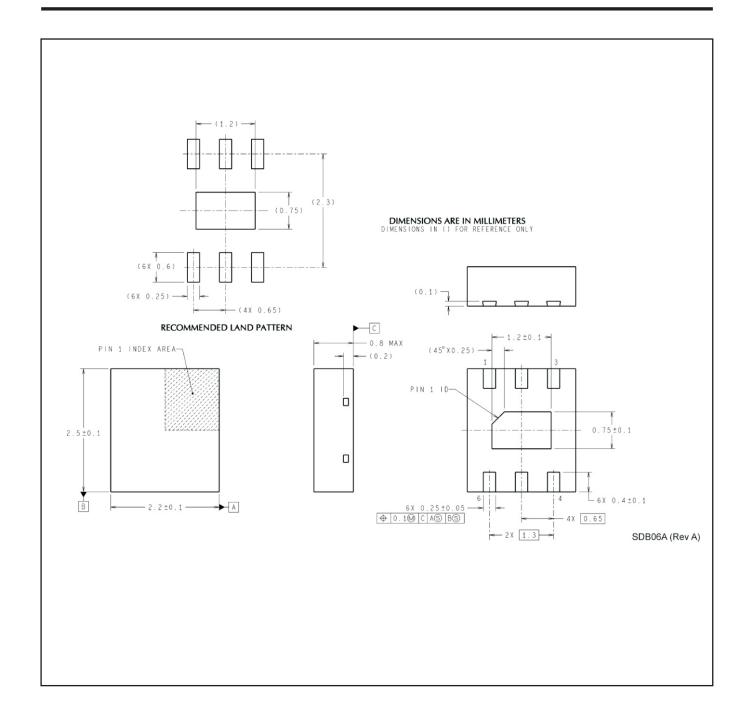

| DAC404C004  | WSON (6)  | 2.20mm x 2.50mm |  |  |  |  |  |

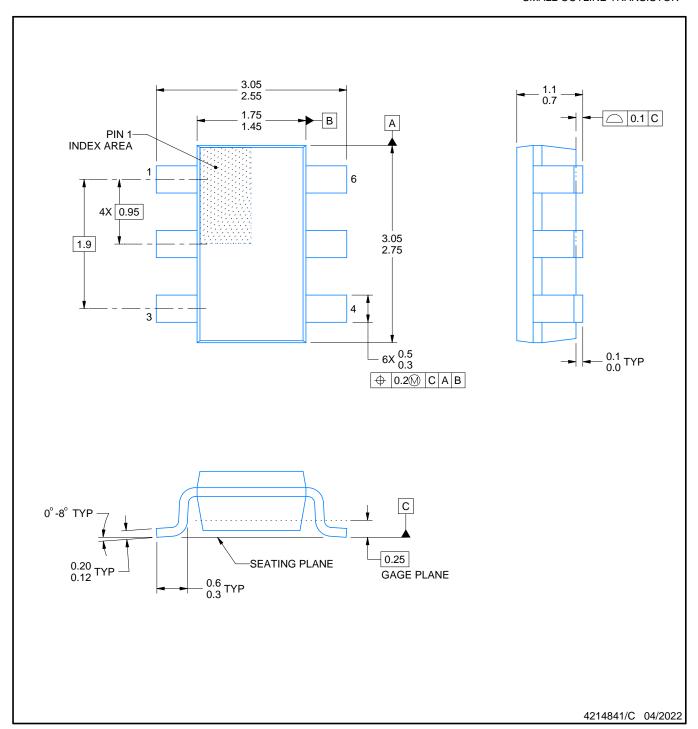

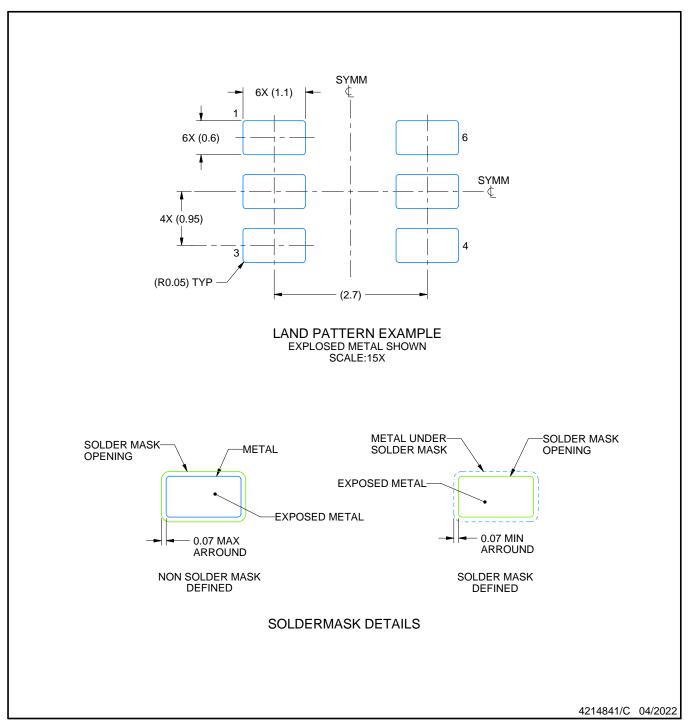

| DAC101C081  | SOT (6)   | 1.60mm x 2.90mm |  |  |  |  |  |

| DAC101C085  | VSSOP (8) | 3.00mm × 3.00mm |  |  |  |  |  |

| DAC101C081Q | WSON (6)  | 2.20mm x 2.50mm |  |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

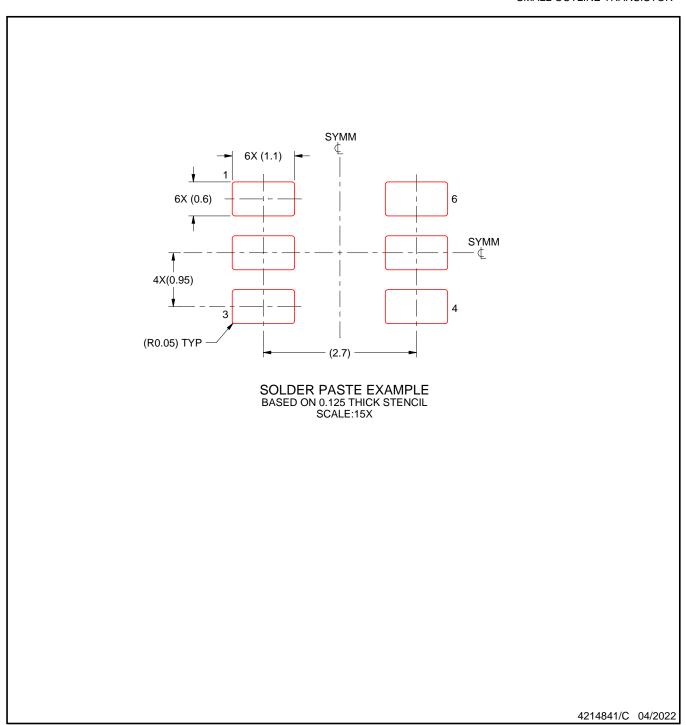

14 机械、封装和可订购信息......30

|   |                                      | 日求 |    |                                         |                |

|---|--------------------------------------|----|----|-----------------------------------------|----------------|

| 1 | 特性                                   | 1  |    | 9.4 Device Functional Modes             | 10             |

| 2 | 应用                                   | 1  |    | 9.5 Programming                         | 17             |

| 3 | 说明                                   | 1  |    | 9.6 Registers                           | 20             |

| 4 | 修订历史记录                               |    | 10 | Application and Implementation          | 2 <sup>,</sup> |

| 5 | 说明 (续)                               |    |    | 10.1 Application Information            | 2              |

| 6 | Device Comparison Table              |    |    | 10.2 Typical Application                | 2              |

| 7 | Pin Configuration and Functions      |    | 11 | Power Supply Recommendations            | 2              |

| 8 | Specifications                       |    |    | 11.1 Using References as Power Supplies | 2              |

| O | •                                    |    | 12 | Layout                                  | 28             |

|   | 8.1 Absolute Maximum Ratings         |    |    | 12.1 Layout Guidelines                  | 28             |

|   | 8.2 ESD Ratings                      |    |    | 12.2 Layout Example                     |                |

|   | 8.3 Recommended Operating Conditions |    | 13 | 器件和文档支持                                 |                |

|   | 8.4 Thermal Information              | 0  |    | 13.1 器件支持                               |                |

|   | 8.5 Electrical Characteristics       |    |    | 13.2 相关链接                               |                |

|   | 8.6 AC and Timing Characteristics    |    |    | 13.3 社区资源                               |                |

|   | 8.7 Typical Characteristics          | 1  |    |                                         |                |

| 9 | Detailed Description 14              | 4  |    | 13.4 商标                                 |                |

|   | 9.1 Overview                         | 4  |    | 13.5 静电放电警告                             | 30             |

$\neg$

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

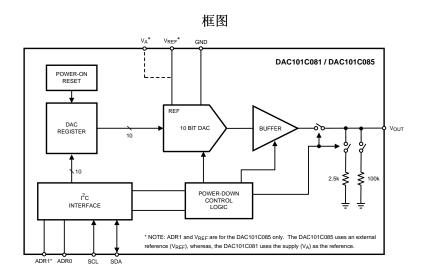

9.2 Functional Block Diagram ...... 14

| Cł       | hanges from Revision A (March 2013) to Revision B                                  | Page |

|----------|------------------------------------------------------------------------------------|------|

| •        | 已添加 <i>ESD</i> 额定值表,特性 描述部分,器件功能模式,应用和实施部分,电源相关建议部分,布局部分,器件和文档支持部分以及机械、封装和可订购信息部分。 |      |

| <u>.</u> | Added addresses that the DAC responds to on the I2C bus.                           | 19   |

| Cł       | hanges from Original (March 2013) to Revision A                                    | Page |

| •        | Changed layout of National Data Sheet to TI format                                 | 28   |

#### 5 说明 (续)

DAC101C081 和 DAC101C085 均具有一个 16 位寄存器,用于控制工作模式、省电条件和输出电压。上电复位电路可确保 DAC 输出电压在上电时达到 0V。省电特性可使器件功耗降至 1 微瓦以下。低功耗及小型封装特性使得这两款 DAC 成为了电池供电类设备的绝佳选择。每款 DAC 均在 -40°C 至 +125°C 的扩展工业级温度范围内运行。

DAC101C081 和 DAC101C085 所属系列均提供有 12 位和 8 位分辨率的引脚兼容 DAC。12 位 DAC 分别为 DAC121C081 和 DAC121C085。8 位 DAC 分别为 DAC081C081 和 DAC081C085。

## 6 Device Comparison Table<sup>(1)</sup>

| Resolution | SOT-6 and WSON-6 Packages | VSSOP-8 Package w/ External Reference |

|------------|---------------------------|---------------------------------------|

| 12-bit     | DAC121C081                | DAC121C085                            |

| 10-bit     | DAC101C081                | DAC101C085                            |

| 8-bit      | DAC081C081                | DAC081C085                            |

<sup>(1)</sup> All devices are fully pin and function compatible.

## 7 Pin Configuration and Functions

#### **Pin Functions**

| PIN              |      |     |       | TYPE                           | EQUIVALENT               | DESCRIPTION                                                                                                                                                                                                                                                |

|------------------|------|-----|-------|--------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | WSON | SOT | VSSOP | ITPE                           | CIRCUIT                  | DESCRIPTION                                                                                                                                                                                                                                                |

| ADR0             | 1    | 6   | 1     | Digital Input,<br>three levels | PIN Snap D1 2.1k \$41.5k | Tri-state Address Selection Input. Sets the two Least Significant Bits (A1 and A0) of the 7-bit slave address. (see Table 1)                                                                                                                               |

| ADR1             | _    | l   | 2     | Digital Input,<br>three levels | GND 41.5K                | Tri-State Address Selection Input. Sets Bits A6 and A3 of the 7-bit slave address. (see Table 1)                                                                                                                                                           |

| GND              | 4    | 3   | 5     | Ground                         |                          | Ground for all on-chip circuitry                                                                                                                                                                                                                           |

| PAD              | PAD  |     | _     | Ground                         |                          | Exposed die attach pad can be connected to ground or left floating. Soldering the pad to the PCB offers optimal thermal performance and enhances package self-alignment during reflow.                                                                     |

| SCL              | 2    | 5   | 3     | Digital Input                  | PIN                      | Serial Clock Input. SCL is used together with SDA to control the transfer of data in and out of the device.                                                                                                                                                |

| SDA              | 3    | 4   | 4     | Digital<br>Input/Output        | Snap<br>Back             | Serial Data bi-directional connection. Data is clocked into or out of the internal 16-bit register relative to the clock edges of SCL. This is an open drain data line that must be pulled to the supply (V <sub>A</sub> ) by an external pullup resistor. |

| V <sub>A</sub>   | 5    | 2   | 6     | Supply                         |                          | Power supply input. For the SOT and WSON versions, this supply is used as the reference. Must be decoupled to GND.                                                                                                                                         |

| V <sub>OUT</sub> | 6    | 1   | 8     | Analog Output                  |                          | Analog Output Voltage                                                                                                                                                                                                                                      |

| V <sub>REF</sub> | _    |     | 7     | Supply                         |                          | Unbufferred reference voltage. For the VSSOP-8, this supply is used as the reference. V <sub>REF</sub> must be free of noise and decoupled to GND.                                                                                                         |

## 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                            | MIN  | MAX | UNIT |

|--------------------------------------------|------|-----|------|

| Supply voltage, V <sub>A</sub>             | -0.3 | 6.5 | V    |

| Voltage on any input pin                   | -0.3 | 6.5 | V    |

| Input current at any pin <sup>(4)</sup>    |      | ±10 | mA   |

| Package input current <sup>(4)</sup>       |      | ±20 | mA   |

| Power consumption at T <sub>A</sub> = 25°C | See  | (5) |      |

| Operating junction temperature             |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub>      | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

- (4) When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two.

- (5) The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula P<sub>D</sub>MAX = (T<sub>J</sub>max T<sub>A</sub>) / θ<sub>JA</sub>. The values for maximum power dissipation will be reached only when the device is operated in a severe fault condition (e.g., when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed).

#### 8.2 ESD Ratings

|             |                         |                                                                             |                         | VALUE | UNIT |

|-------------|-------------------------|-----------------------------------------------------------------------------|-------------------------|-------|------|

| DAC081      | C081 in NGF Package     |                                                                             |                         |       |      |

|             |                         | Human-body model (HBM), per                                                 | All pins except 2 and 3 | ±2500 |      |

|             |                         | ANSI/ESDA/JEDEC JS-001                                                      | Pins 2 and 3            | ±5000 |      |

| V           | Clastrostatia diasharas | Charged-device model (CDM), per JEDEC                                       | All pins except 2 and 3 | ±1000 | V    |

| $V_{(ESD)}$ | Electrostatic discharge | specification JESD22-C101                                                   | Pins 2 and 3            | ±1000 | V    |

|             |                         | Machine model (MM)                                                          | All pins except 2 and 3 | ±250  |      |

|             |                         | Machine model (MM)                                                          | Pins 2 and 3            | ±350  |      |

| DAC081      | C081 in DDC Package     |                                                                             |                         |       |      |

|             |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001  All pins except 4 and 5 | All pins except 4 and 5 | ±2500 | V    |

|             |                         |                                                                             | Pins 4 and 5            | ±5000 |      |

| V           | Electrostatic discharge | Charged-device model (CDM), per JEDEC                                       | All pins except 4 and 5 | ±1000 |      |

| $V_{(ESD)}$ |                         | specification JESD22-C101                                                   | Pins 4 and 5            | ±1000 |      |

|             |                         | Machine model (MM)                                                          | All pins except 4 and 5 | ±250  |      |

|             |                         | Machine model (MM)                                                          | Pins 4 and 5            | ±350  |      |

| DAC081      | C085 in DGK Package     |                                                                             |                         |       |      |

|             |                         | Human-body model (HBM), per                                                 | All pins except 3 and 4 | ±2500 |      |

|             |                         | ANSI/ESDA/JEDEC JS-001                                                      | Pins 3 and 4            | ±5000 |      |

| \ <i>/</i>  | Clastrostatia diasharas | Charged-device model (CDM), per JEDEC                                       | All pins except 3 and 4 | ±1000 | V    |

| $V_{(ESD)}$ | Electrostatic discharge | specification JESD22-C101                                                   | Pins 3 and 4            | ±1000 | V    |

|             |                         | Machine model (MM)                                                          | All pins except 3 and 4 | ±250  |      |

|             |                         | Machine model (MM)                                                          | Pins 3 and 4            | ±350  |      |

<sup>(3)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

#### 8.3 Recommended Operating Conditions

See (1)

|                                         | MIN | NOM            | MAX            | UNIT |

|-----------------------------------------|-----|----------------|----------------|------|

| Operating temperature range             | -40 | T <sub>A</sub> | 125            | °C   |

| Supply voltage, V <sub>A</sub>          | 2.7 |                | 5.5            | V    |

| Reference voltage, V <sub>REFIN</sub>   | 1   |                | V <sub>A</sub> | V    |

| Digital input voltage <sup>(2)(3)</sup> | 0   |                | 5.5            | V    |

| Output load                             | 0   |                | 1500           | pF   |

1) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

#### 8.4 Thermal Information

| (4)(2)(2)                                               | DAC101C081 | DAC101C081,<br>DAC101C081Q | DAC101C085  |      |

|---------------------------------------------------------|------------|----------------------------|-------------|------|

| THERMAL METRIC <sup>(1)(2)(3)</sup>                     | DDC (SOT)  | NGF (WSON)                 | DGK (VSSOP) | UNIT |

|                                                         | 6 PINS     | 6 PINS                     | 8 PINS      |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 250        | 190                        | 240         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 8.5 Electrical Characteristics

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $C_L = 200 \text{ pF}$  to GND, input code range 12 to 1011. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise specified).

|        | PARAMETER                           | TEST CONDITIONS                                 | MIN  | TYP <sup>(1)</sup> | MAX <sup>(1)</sup> | UNIT          |

|--------|-------------------------------------|-------------------------------------------------|------|--------------------|--------------------|---------------|

| STATIC | PERFORMANCE                         |                                                 |      |                    |                    |               |

|        | Resolution                          |                                                 | 10   |                    |                    | Bits          |

|        | Monotonicity                        |                                                 | 10   |                    |                    | Bits          |

| INL    | Integral non linearity              |                                                 |      | +0.6               | +2                 | LSB           |

| IINL   | Integral non-linearity              |                                                 | -2   | -0.4               |                    | LSB           |

| DNL    | Differential non-linearity          |                                                 |      | +0.12              | +0.3               | LSB           |

| DINL   | Differential non-linearity          |                                                 | -0.2 | -0.04              |                    | LSB           |

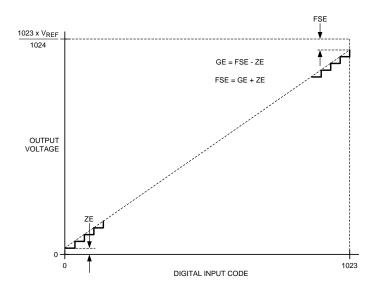

| ZE     | Zero code error                     | I <sub>OUT</sub> = 0                            |      | +1.1               | +10                | mV            |

| FSE    | Full-scale error                    | I <sub>OUT</sub> = 0                            |      | -0.1               | -0.7               | %FSR          |

| GE     | Gain error                          | All ones loaded to DAC register                 |      | -0.2               | -0.7               | %FSR          |

| ZCED   | Zero code error drift               |                                                 |      | -20                |                    | μV/°C         |

| TC GE  | Cain array tampaa                   | V <sub>A</sub> = 3 V                            |      | -0.7               |                    | ppm<br>FSR/°C |

| IC GE  | Gain error tempco                   | V <sub>A</sub> = 5 V                            |      | -1                 |                    | ppm<br>FSR/°C |

| ANALOG | OUTPUT CHARACTERISTIC               | CS (V <sub>OUT</sub> )                          |      |                    |                    |               |

|        | Output voltage range <sup>(2)</sup> | DAC101C085                                      | 0    |                    | $V_{REF}$          | V             |

|        | Output voltage range                | DAC101C081                                      | 0    |                    | $V_{A}$            | V             |

| 700    | Zoro codo output                    | $V_A = 3 \text{ V}, I_{OUT} = 200 \mu\text{A}$  |      | 1.3                |                    | mV            |

| ZCO    | Zero code output                    | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 200 μA |      | 7.0                |                    | mV            |

| F80    | Full cools sustaint                 | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 200 μA |      | 2.984              |                    | V             |

| FSO    | Full scale output                   | $V_A = 5 \text{ V}, I_{OUT} = 200 \mu\text{A}$  |      | 4.989              |                    | V             |

Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

<sup>(2)</sup> The inputs are protected as shown below. Input voltage magnitudes up to 5.5 V, regardless of V<sub>A</sub>, will not cause errors in the conversion result. For example, if V<sub>A</sub> is 3 V, the digital input pins can be driven with a 5 V logic device.

<sup>(3)</sup> To ensure accuracy, it is required that  $V_A$  and  $V_{REF}$  be well bypassed.

<sup>(2)</sup> Soldering process must comply with Reflow Temperature Profile specifications. Refer to www.ti.com/packaging.

<sup>(3)</sup> Reflow temperature profiles are different for lead-free packages.

<sup>2)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

## **Electrical Characteristics (continued)**

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $C_L = 200 \text{ pF}$  to GND, input code range 12 to 1011. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise specified).

|                   | ·                                                                    | T <sub>MIN</sub> = T <sub>A</sub> = T <sub>MAX</sub> and an Typical in | The are at 1 <sub>A</sub> =e |                    |                      | p = = |

|-------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------|--------------------|----------------------|-------|

|                   | PARAMETER                                                            | TEST CONDITIONS                                                        | MIN                          | TYP <sup>(1)</sup> | MAX <sup>(1)</sup>   | UNIT  |

| laa.              | Output short circuit current                                         | $V_A = 3 \text{ V}, V_{OUT} = 0 \text{ V},$<br>Input code = FFFh.      |                              | 56                 |                      | mA    |

| I <sub>OS</sub>   | (I <sub>SOURCE</sub> )                                               | $V_A = 5 \text{ V}, V_{OUT} = 0 \text{ V},$<br>Input code = FFFh.      |                              | 69                 |                      | mA    |

| la a              | Output short circuit current                                         | $V_A = 3 \text{ V}, V_{OUT} = 3 \text{ V},$<br>Input code = 000h.      |                              | <b>-</b> 52        |                      | mA    |

| los               | (I <sub>SINK</sub> )                                                 | $V_A = 5 \text{ V}, V_{OUT} = 5 \text{ V},$<br>Input code = 000h.      |                              | <b>-</b> 75        |                      | mA    |

| l <sub>o</sub>    | Continuous output current (2)                                        | Available on the DAC output                                            |                              |                    | 11                   | mA    |

| C                 | Maximum load capacitance                                             | R <sub>L</sub> = ∞                                                     |                              | 1500               |                      | pF    |

| C <sub>L</sub>    | Maximum load capacitance                                             | $R_L = 2 k\Omega$                                                      |                              | 1500               |                      | pF    |

| Z <sub>OUT</sub>  | DC output impedance                                                  |                                                                        |                              | 7.5                |                      | Ω     |

| REFERE            | NCE INPUT CHARACTERISTICS                                            | · (DAC101C085 only)                                                    |                              |                    |                      |       |

|                   | Input range inimum                                                   |                                                                        | 1                            | 0.2                |                      | V     |

| $V_{REF}$         | Input range maximum                                                  |                                                                        |                              |                    | $V_{A}$              | V     |

|                   | Input impedance                                                      |                                                                        |                              | 120                |                      | kΩ    |

| LOGIC IN          | IPUT CHARACTERISTICS (SCL,                                           | SDA)                                                                   | ı                            |                    | •                    |       |

| V <sub>IH</sub>   | Input high voltage                                                   |                                                                        | 0.7 × V <sub>A</sub>         |                    |                      | V     |

| V <sub>IL</sub>   | Input low voltage                                                    |                                                                        |                              |                    | 0.3 × V <sub>A</sub> | V     |

| IN                | Input current                                                        |                                                                        |                              |                    | ±1                   | μA    |

| C <sub>IN</sub>   | Input pin capacitance <sup>(2)</sup>                                 |                                                                        |                              |                    | 3                    | pF    |

| V <sub>HYST</sub> | Input hysteresis                                                     |                                                                        | 0.1 × V <sub>A</sub>         |                    |                      | V     |

|                   | IPUT CHARACTERISTICS (ADRO                                           | ), ADR1)                                                               |                              |                    | <u>I</u>             |       |

| V <sub>IH</sub>   | Input high voltage                                                   |                                                                        | V <sub>A</sub> - 0.5         |                    |                      | V     |

| V <sub>IL</sub>   | Input low voltage                                                    |                                                                        |                              |                    | 0.5                  | V     |

| I <sub>IN</sub>   | Input current                                                        |                                                                        |                              |                    | ±1                   | μA    |

|                   | UTPUT CHARACTERISTICS (SD                                            | A)                                                                     |                              |                    |                      |       |

|                   |                                                                      | I <sub>SINK</sub> = 3 mA                                               |                              |                    | 0.4                  | V     |

| $V_{OL}$          | Output low voltage                                                   | I <sub>SINK</sub> = 6 mA                                               |                              |                    | 0.6                  | V     |

| I <sub>OZ</sub>   | High-impedence output leakage current                                | SINK SIII.                                                             |                              |                    | ±1                   | μA    |

| POWER I           | REQUIREMENTS                                                         |                                                                        |                              |                    | +                    |       |

|                   | Supply voltage minimum                                               |                                                                        | 2.7                          |                    |                      | V     |

| $V_A$             | Supply voltage maximum                                               |                                                                        |                              |                    | 5.5                  | V     |

| Normal            |                                                                      | face quiet (SCL = SDA = $V_A$ ). (output                               | unloaded)                    |                    |                      |       |

|                   |                                                                      | V <sub>A</sub> = 2.7 V to 3.6 V                                        |                              | 105                | 156                  | μΑ    |

| ST_VA-1           | V <sub>A</sub> DAC101C081 supply current                             | V <sub>A</sub> = 4.5 V to 5.5 V                                        |                              | 132                | 214                  | μA    |

|                   |                                                                      | V <sub>A</sub> = 2.7 V to 3.6 V                                        |                              | 86                 | 118                  | μA    |

| ST_VA-5           | V <sub>A</sub> DAC101C085 supply current                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$                                |                              | 98                 | 152                  | μΑ    |

|                   | V supply current                                                     | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$                                |                              | 37                 | 43                   | μA    |

| ST_VREF           | V <sub>REF</sub> supply current (DAC101C085 only)                    | V <sub>A</sub> = 4.5 V to 5.5 V                                        |                              | 53                 | 61                   | μΑ    |

|                   |                                                                      | V <sub>A</sub> = 3 V                                                   |                              | 380                | 01                   | μW    |

| P <sub>ST</sub>   | Power consumption (V <sub>A</sub> & V <sub>REF</sub> for DAC101C085) | $V_A = 5 \text{ V}$                                                    |                              | 730                |                      | μW    |

|                   |                                                                      | ively addressing the DAC and writing                                   | to the DAC 11111             |                    |                      | μνν   |

## **Electrical Characteristics (continued)**

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $C_L = 200 \text{ pF}$  to GND, input code range 12 to 1011. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise specified).

|                      | PARAMETER                                                         | TEST CON                        |                                    | MIN                     | TYP <sup>(1)</sup> | MAX <sup>(1)</sup> | UNIT |

|----------------------|-------------------------------------------------------------------|---------------------------------|------------------------------------|-------------------------|--------------------|--------------------|------|

|                      |                                                                   | f <sub>SCL</sub> = 400 kHz      | V <sub>A</sub> = 2.7 V to 3.6 V    |                         | 134                | 220                | μΑ   |

|                      | V DAC404C004 oupply ourrent                                       | I <sub>SCL</sub> = 400 kHz      | $V_A = 4.5 \text{ V to} $ 5.5 V    |                         | 192                | 300                | μΑ   |

| I <sub>CO_VA-1</sub> | V <sub>A</sub> DAC101C081 supply current                          | £ 2.4 MH=                       | V <sub>A</sub> = 2.7 V to<br>3.6 V |                         | 225                | 320                | μΑ   |

|                      |                                                                   | $f_{SCL} = 3.4 \text{ MHz}$     | $V_A = 4.5 \text{ V to} $ 5.5 V    |                         | 374                | 500                | μΑ   |

|                      |                                                                   | f _ 400 kHz                     | $V_A = 2.7 \text{ V to}$ 3.6 V     |                         | 101                | 155                | μΑ   |

|                      | V DAC404C00E gupply gurrant                                       | $f_{SCL} = 400 \text{ kHz}$     | $V_A = 4.5 \text{ V to} $ 5.5 V    |                         | 142                | 220                | μΑ   |

| I <sub>CO_VA-5</sub> | V <sub>A</sub> DAC101C085 supply current                          | f <sub>SCL</sub> = 3.4 MHz      | $V_A = 2.7 \text{ V to}$ 3.6 V     |                         | 193                | 235                | μΑ   |

|                      |                                                                   |                                 | $V_A = 4.5 \text{ V to}$ 5.5 V     |                         | 325                | 410                | μΑ   |

|                      | V <sub>REF</sub> supply current<br>(DAC101C085 only)              |                                 | V <sub>A</sub> = 2.7 V to<br>3.6 V |                         | 33.5               | 55                 | μΑ   |

| I <sub>CO_VREF</sub> |                                                                   |                                 | V <sub>A</sub> = 4.5 V to 5.5 V    |                         | 49.5               | 71.4               | μΑ   |

|                      |                                                                   | f <sub>SCL</sub> = 400 kHz      | V <sub>A</sub> = 3 V               |                         | 480                |                    | μW   |

| D                    | Power consumption                                                 |                                 | $V_A = 5 V$                        |                         | 1.06               |                    | mW   |

| $P_{CO}$             | (V <sub>A</sub> & V <sub>REF</sub> for DAC101C085)                |                                 | V <sub>A</sub> = 3 V               |                         | 810                |                    | μW   |

|                      |                                                                   | $f_{SCL} = 3.4 \text{ MHz}$     | $V_A = 5 V$                        |                         | 2.06               |                    | mW   |

| Power Do             | wn 2-wire interface quiet (SCL =                                  | SDA = V <sub>A</sub> ) after Pl | D mode written to                  | DAC register. (output u | unloaded)          |                    |      |

| I <sub>PD</sub>      | Supply current (V <sub>A</sub> & V <sub>REF</sub> for DAC101C085) | All power-down                  | V <sub>A</sub> = 2.7 V to<br>3.6 V |                         | 0.13               | 1.52               | μΑ   |

|                      |                                                                   |                                 | V <sub>A</sub> = 4.5 V to 5.5 V    |                         | 0.15               | 3.25               | μΑ   |

| D                    | Power consumption                                                 | All power-down                  | V <sub>A</sub> = 3 V               | _                       | 0.5                |                    | μW   |

| $P_{PD}$             | (V <sub>A</sub> & V <sub>REF</sub> for DAC101C085)                | modes                           | V <sub>A</sub> = 5 V               |                         | 0.9                |                    | μW   |

|                      |                                                                   |                                 |                                    |                         |                    |                    |      |

#### 8.6 AC and Timing Characteristics

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $R_L = Infinity$ ,  $C_L = 200 \text{ pF}$  to GND. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise specified).

|                | PARAMETER                                | TEST CONDITIONS <sup>(1)</sup>                                              | MIN | TYP <sup>(2)</sup> | MAX <sup>(1)(3)</sup> | UNIT   |

|----------------|------------------------------------------|-----------------------------------------------------------------------------|-----|--------------------|-----------------------|--------|

| t <sub>s</sub> | Output voltage settling time (4)         | 100h to 300h code change $R_L = 2 \text{ k}\Omega$ , $C_L = 200 \text{ pF}$ |     | 4.5                | 6                     | μs     |

| SR             | Output slew rate                         |                                                                             |     | 1                  |                       | V/µs   |

|                | Glitch impulse                           | Code change from 200h to 1FFh                                               |     | 12                 |                       | nV-sec |

|                | Digital feedthrough                      |                                                                             |     | 0.5                |                       | nV-sec |

|                | Multiplying bandwidth (5)                | V <sub>REF</sub> = 2.5 V ± 0.1 Vpp                                          |     | 160                |                       | kHz    |

|                | Total harmonic distortion <sup>(5)</sup> | V <sub>REF</sub> = 2.5 V ± 0.1 Vpp<br>input frequency = 10 kHz              |     | 70                 |                       | dB     |

<sup>(1)</sup>  $C_b$  refers to the capacitance of one bus line.  $C_b$  is expressed in pF units.

<sup>(2)</sup> Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

<sup>(3)</sup> Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

<sup>(4)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

<sup>(5)</sup> Applies to the Multiplying DAC configuration. In this configuration, the reference is used as the analog input. The value loaded in the DAC Register will digitally attenuate the signal at Vout.

## **AC and Timing Characteristics (continued)**

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF}$  =  $V_A$ ,  $R_L$  = Infinity,  $C_L$  = 200 pF to GND. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A$  = 25°C (unless otherwise specified).

|                                    | PARAMETER                                        | TEST CONDITIONS <sup>(1)</sup>                                                     | MIN                    | TYP <sup>(2)</sup> MAX <sup>(1)</sup> | )(3) | UNIT     |  |

|------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------|------------------------|---------------------------------------|------|----------|--|

|                                    | Waka un tima                                     | V <sub>A</sub> = 3 V                                                               |                        | 0.8                                   |      | µsec     |  |

| WU                                 | Wake-up time                                     | V <sub>A</sub> = 5 V                                                               |                        | 0.5                                   |      | µsec     |  |

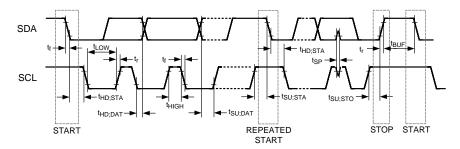

| DIGITA                             | L TIMING SPECS (SCL, SDA)                        |                                                                                    |                        |                                       |      |          |  |

|                                    |                                                  | Standard mode                                                                      |                        | 1                                     | 00   |          |  |

|                                    | Operiod also de françois est                     | Fast mode                                                                          |                        | 4                                     | 100  | kHz      |  |

| fscl                               | Serial clock frequency                           | High speed mode, C <sub>b</sub> = 100 pF                                           |                        | ;                                     | 3.4  | N 41 1-  |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           |                        |                                       | 1.7  | MHz      |  |

|                                    |                                                  | Standard mode                                                                      | 4.7                    |                                       |      |          |  |

|                                    | 001.1                                            | Fast mode                                                                          | 1.3                    |                                       |      | μs       |  |

| LOW                                | SCL low time                                     | High speed mode, C <sub>b</sub> = 100 pF                                           | 160                    |                                       |      |          |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           | 320                    |                                       |      | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 4                      |                                       |      |          |  |

|                                    |                                                  | Fast mode                                                                          | 0.6                    |                                       |      | μs       |  |

| HIGH                               | SCL high time                                    | High speed mode, C <sub>b</sub> = 100 pF                                           |                        |                                       |      |          |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           | 120                    |                                       |      | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 250                    |                                       |      |          |  |

| SU:DAT                             | Data set-up time                                 | Fast mode                                                                          | 100                    |                                       |      | ns       |  |

| 00,27                              | •                                                | High speed mode                                                                    | 10                     |                                       |      |          |  |

| i <sub>HD;DAT</sub> Data hold time |                                                  | Standard mode                                                                      | 0                      | 3.                                    | .45  |          |  |

|                                    |                                                  | Fast mode                                                                          | 0                      |                                       | 0.9  | μs       |  |

|                                    | Data hold time                                   | High speed mode, C <sub>b</sub> = 100 pF                                           | 0                      |                                       | 70   |          |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           | 0                      |                                       | 50   | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 4.7                    |                                       |      |          |  |

| SU;STA                             | Set-up time for a start or a                     | Fast mode                                                                          | 0.6                    |                                       |      | μs       |  |

| 50;51A                             | repeated start condition                         | High speed mode                                                                    | 160                    |                                       |      | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 4                      |                                       |      | 110      |  |

| LID.OTA                            | Hold time for a start or a                       | Fast mode                                                                          | 0.6                    |                                       |      | μs       |  |

| HD;STA                             | repeated start condition                         | High speed mode                                                                    | 160                    |                                       |      | ns       |  |

|                                    | Due free time between a stan                     | Standard mode                                                                      | 4.7                    |                                       |      | 110      |  |

| BUF                                | Bus free time between a stop and start condition | Fast mode                                                                          | 1.3                    |                                       |      | μs       |  |

|                                    |                                                  | Standard mode                                                                      | 4                      |                                       |      |          |  |

| ·                                  | Set-up time for a stop condition                 | Fast mode                                                                          | 0.6                    |                                       |      | μs       |  |

| SU;STO                             | Set-up time for a stop condition                 | High speed mode                                                                    | 160                    |                                       |      | ne       |  |

|                                    |                                                  | Standard mode                                                                      | 100                    | 10                                    | 000  | ns<br>ns |  |

|                                    |                                                  | Fast mode                                                                          | 20 + 0.1C <sub>b</sub> |                                       | 800  |          |  |

| rDA                                | Rise time of SDA signal                          | High speed mode, C <sub>b</sub> = 100 pF                                           | 20 + 0.10 <sub>b</sub> |                                       | 80   | ns       |  |

|                                    |                                                  | High speed mode, $C_b = 100 \text{ pF}$<br>High speed mode, $C_b = 400 \text{ pF}$ | 20                     |                                       | 60   | ns       |  |

|                                    |                                                  |                                                                                    | 20                     |                                       |      | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 20 + 0.10              |                                       | 250  | ns       |  |

| fDA                                | Fall time of SDA signal                          | Fast mode                                                                          | 20 + 0.1C <sub>b</sub> |                                       | 250  | ns       |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 100 pF                                           | 10                     |                                       | 80   | ns       |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           | 20                     |                                       | 60   | ns       |  |

|                                    |                                                  | Standard mode                                                                      | 00 0:0                 |                                       | 000  | ns       |  |

| rCL                                | Rise time of SCL signal                          | Fast mode                                                                          | 20 + 0.1C <sub>b</sub> |                                       | 300  | ns       |  |

| -                                  | -                                                | High speed mode, C <sub>b</sub> = 100 pF                                           | 10                     |                                       | 40   | ns       |  |

|                                    |                                                  | High speed mode, C <sub>b</sub> = 400 pF                                           | 20                     |                                       | 80   | ns       |  |

## **AC and Timing Characteristics (continued)**

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF}$  =  $V_A$ ,  $R_L$  = Infinity,  $C_L$  = 200 pF to GND. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A$  = 25°C (unless otherwise specified).

|                   | PARAMETER                                                                              | TEST CONDITIONS <sup>(1)</sup>           | MIN           | TYP <sup>(2)</sup> | MAX <sup>(1)(3)</sup> | UNIT |

|-------------------|----------------------------------------------------------------------------------------|------------------------------------------|---------------|--------------------|-----------------------|------|

|                   |                                                                                        | Standard mode                            |               |                    | 1000                  | ns   |

|                   | Rise time of SCL signal after a repeated start condition and after an acknowledge bit. | Fast mode                                | $20 + 0.1C_b$ |                    | 300                   | ns   |

| <sup>t</sup> rCL1 |                                                                                        | High speed mode, C <sub>b</sub> = 100 pF | 10            |                    | 80                    | ns   |

|                   |                                                                                        | High speed mode, C <sub>b</sub> = 400 pF | 20            |                    | 160                   | ns   |

|                   | t <sub>fCL</sub> Fall time of a SCL signal                                             | Standard mode                            |               |                    | 300                   | ns   |

|                   |                                                                                        | Fast mode                                | $20 + 0.1C_b$ |                    | 300                   | ns   |

| <sup>l</sup> fCL  |                                                                                        | High speed mode, C <sub>b</sub> = 100 pF | 10            |                    | 40                    | ns   |

|                   |                                                                                        | High speed mode, C <sub>b</sub> = 400 pF | 20            |                    | 80                    | ns   |

| C <sub>b</sub>    | Capacitive load for each bus line (SCL and SDA)                                        |                                          |               |                    | 400                   | pF   |

|                   | Pulse width of spike                                                                   | Fast mode                                |               |                    | 50                    |      |

| ISP               | t <sub>SP</sub> suppressed (6)(4)                                                      | High speed mode                          |               |                    | 10                    | ns   |

|                   | SDA output delay (see Section                                                          | Fast mode                                |               | 87                 | 270                   |      |

| t <sub>outz</sub> | 1.9)                                                                                   | High speed mode 38                       |               | 60                 | ns                    |      |

(6) Spike suppression filtering on SCL and SDA will supress spikes that are less than 50ns for standard-fast mode and less than 10ns for hs-mode.

Figure 1. Input / Output Transfer Characteristic

Figure 2. Serial Timing Diagram

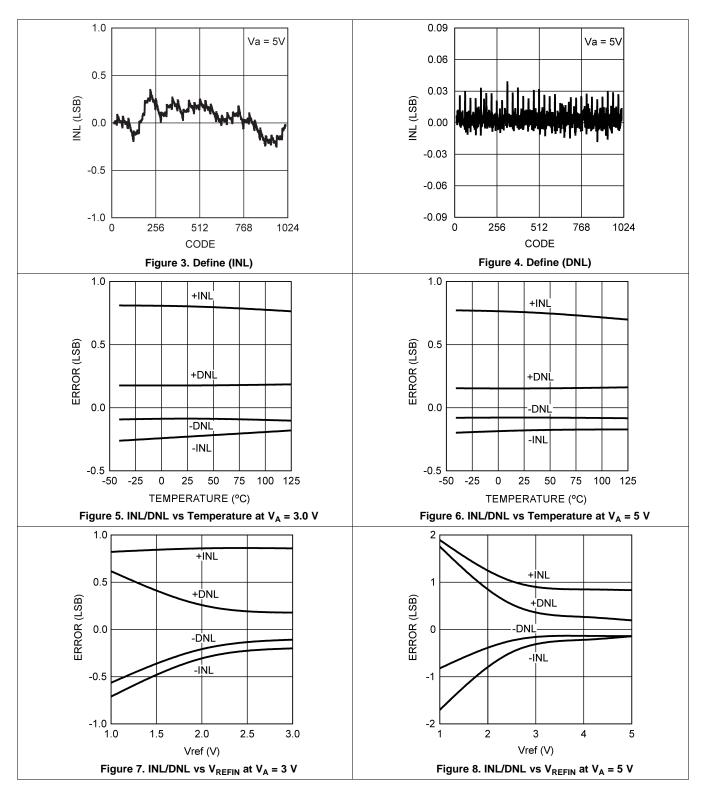

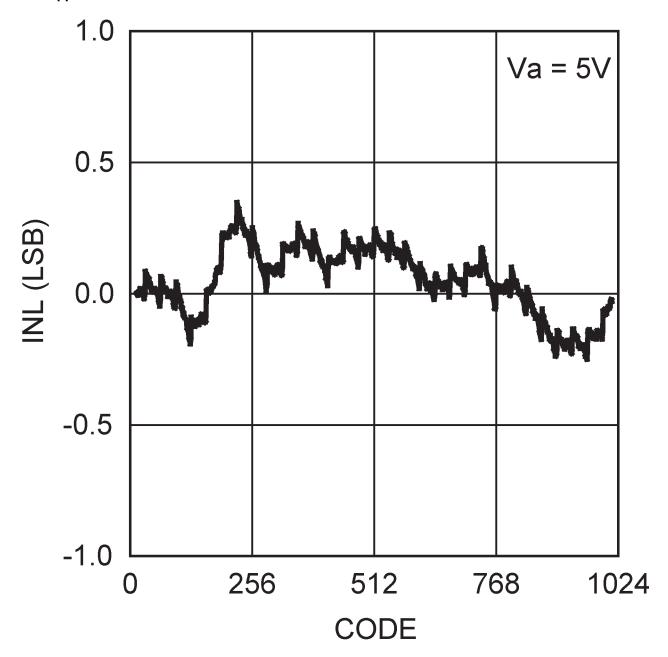

## 8.7 Typical Characteristics

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, input code range 12 to 1011 (unless otherwise stated).

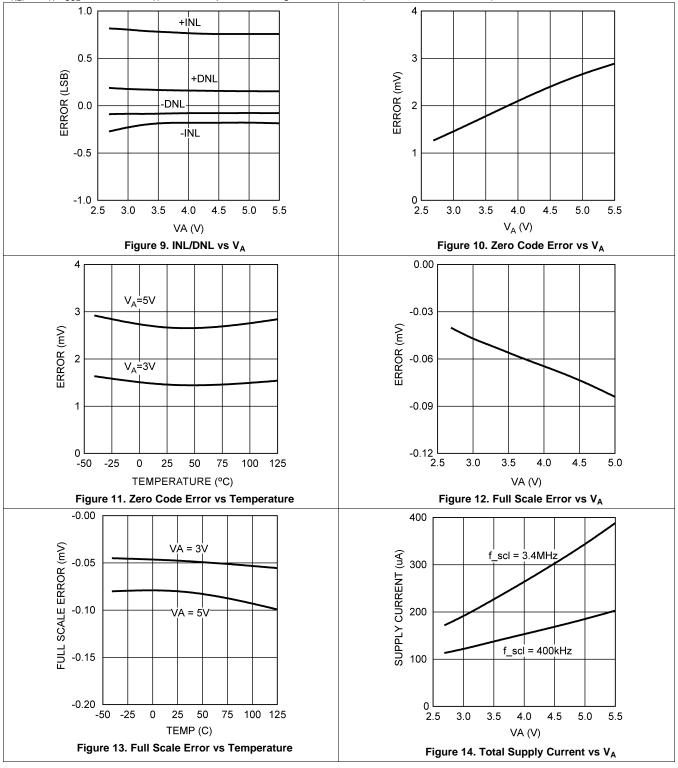

## **Typical Characteristics (continued)**

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, input code range 12 to 1011 (unless otherwise stated).

## **Typical Characteristics (continued)**

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, input code range 12 to 1011 (unless otherwise stated).

Figure 19. Power-On Reset

#### 9 Detailed Description

#### 9.1 Overview

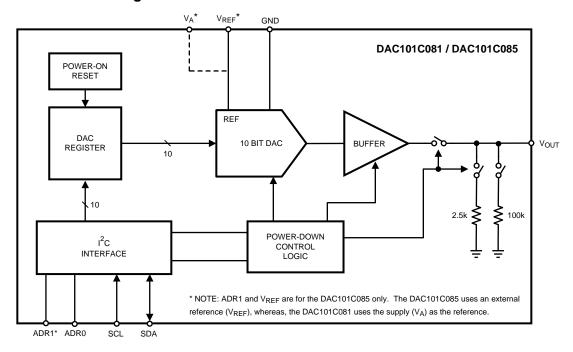

The DAC101C081 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer.

#### 9.2 Functional Block Diagram

## 9.3 Feature Description

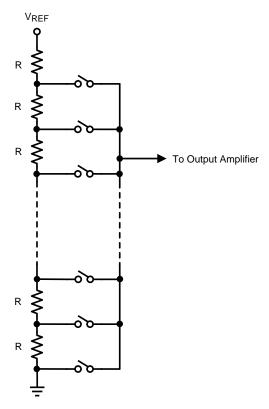

#### 9.3.1 DAC Section

For simplicity, a single resistor string is shown in Figure 20. This string consists of 1024 equal valued resistors with a switch at each junction of two resistors, plus a switch to ground. The code loaded into the DAC register determines which switch is closed, connecting the proper node to the amplifier. The input coding is straight binary with an ideal output voltage of:

$$V_{OUT} = V_{REF} \times (D / 1024)$$

where D is the decimal equivalent of the binary code that is loaded into the DAC register. D can take on any integer value between 0 and 1023. This configuration ensures that the DAC is monotonic. (1)

#### **Feature Description (continued)**

Figure 20. DAC Resistor String

## 9.3.2 Output Amplifier

The output amplifier is rail-to-rail, providing an output voltage range of 0 V to  $V_A$  when the reference is  $V_A$ . All amplifiers, even rail-to-rail types, exhibit a loss of linearity as the output approaches the supply rails (0 V and  $V_A$ , in this case). For this reason, linearity is specified over less than the full output range of the DAC. However, if the reference is less than  $V_A$ , there is only a loss in linearity in the lowest codes. The output capabilities of the amplifier are described in the *Electrical Characteristics* table.

The output amplifiers are capable of driving a load of  $2-k\Omega$  in parallel with 1500 pF to ground or to  $V_A$ . The zero-code and full-scale outputs for given load currents are available in the *Electrical Characteristics* table.

#### 9.3.3 Reference Voltage

The DAC101C081 uses the supply  $(V_A)$  as the reference. With that said,  $V_A$  must be treated as a reference. The Analog output will only be as clean as the reference  $(V_A)$ . It is recommended that the reference be driven by a voltage source with low output impedance.

The DAC101C085 comes with an external reference supply pin ( $V_{REF}$ ). For the DAC101C085, it is important that  $V_{REF}$  be kept as clean as possible.

The Applications Information section describes a handful of ways to drive the reference appropriately. Refer to Using References as Power Supplies for details.

#### 9.3.4 Power-On Reset

The power-on reset circuit controls the output voltage of the DAC during power-up. Upon application of power, the DAC register is filled with zeros and the output voltage is 0 Volts. The output remains at 0 V until a valid write sequence is made to the DAC.

#### **Feature Description (continued)**

When resetting the device, it is crutial that the  $V_A$  supply be lowered to a maximum of 200mV before the supply is raised again to power-up the device. Dropping the supply to within 200mV of GND during a reset will ensure the ADC performs as specified.

#### 9.3.5 Simultaneous Reset

The broadcast address allows the  $I^2C^{TM}$  master to write a single word to multiple DACs simultaneously. Provided that all of the DACs exist on a single  $I^2C^{TM}$  bus, every DAC will update when the broadcast address is used to address the bus. This feature allows the master to reset all of the DACs on a shared  $I^2C^{TM}$  bus to a specific digital code. For instance, if the master writes a power-down code to the bus with the broadcast address, all of the DACs will power-down simultaneously.

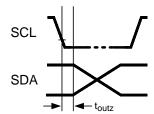

## 9.3.6 Additional Timing Information: toutz

The  $t_{outz}$  specification is provided to aid the design of the  $I^2C$  bus. After the SCL bus is driven low by the  $I^2C^{TM}$  master, the SDA bus will be held for a short time by the DAC101C081. This time is referred to as  $t_{outz}$ . The following figure illustrates the relationship between the fall of SCL, at the 30% threshold, to the time when the DAC begins to transition the SDA bus. The  $t_{outz}$  specification only applies when the DAC is in control of the SDA bus. The DAC is only in control of the bus during an ACK by the DAC101C081 or a data byte read from the DAC (see Figure 25).

Figure 21. Data Output Timing

The t<sub>outz</sub> specification is typically 87nsec in Standard-Fast Mode and 38nsec in Hs-Mode.

#### 9.4 Device Functional Modes

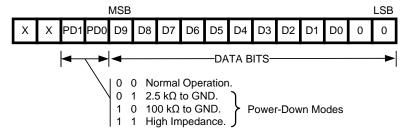

#### 9.4.1 Power-Down Modes

The DAC101C081 has three power-down modes. In power-down mode, the supply current drops to  $0.13\mu A$  at 3 V and  $0.15\mu A$  at 5 V (typ). The DAC101C081 is put into power-down mode by writing a one to PD1 and/or PD0. The outputs can be set to high impedance, terminated by  $2.5~k\Omega$  to GND, or terminated by  $100~k\Omega$  to GND (see Figure 26).

The bias generator, output amplifier, resistor string, and other linear circuitry are all shut down in any of the power-down modes. When the DAC101C081 is powered down, the value written to the DAC register, including the power-down bits, is saved. While the DAC is in power-down, the saved DAC register contents can be read back. When the DAC is brought out of power-down mode, the DAC register contents will be overwritten and  $V_{OUT}$  will be updated with the new 10-bit data value.

The time to exit power-down (Wake-Up Time) is typically 0.8µsec at 3 V and 0.5µsec at 5 V.

#### 9.5 Programming

#### 9.5.1 Serial Interface

The I<sup>2</sup>C<sup>TM</sup>-compatible interface operates in all three speed modes. Standard mode (100kHz) and Fast mode (400 kHz) are functionally the same and will be referred to as Standard-Fast mode in this document. High-Speed mode (3.4 MHz) is an extension of Standard-Fast mode and will be referred to as Hs-mode in this document. The following diagrams describe the timing relationships of the clock (SCL) and data (SDA) signals. Pullup resistors or current sources are required on the SCL and SDA busses to pull them high when they are not being driven low. A logic zero is transmitted by driving the output low. A logic high is transmitted by releasing the output and allowing it to be pulled-up externally. The appropriate pullup resistor values will depend upon the total bus capacitance and operating speed.

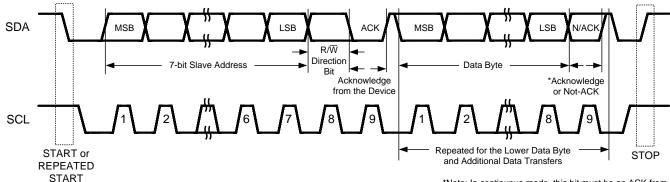

#### 9.5.2 Basic I<sup>2</sup>C™ Protocol

The I<sup>2</sup>C<sup>TM</sup> interface is bi-directional and allows multiple devices to operate on the same bus. To facilitate this bus configuration, each device has a unique hardware address which is referred to as the "slave address." To communicate with a particular device on the bus, the controller (master) sends the slave address and listens for a response from the slave. This response is referred to as an acknowledge bit. If a slave on the bus is addressed correctly, it Acknowledges (ACKs) the master by driving the SDA bus low. If the address doesn't match a device's slave address, it Not-acknowledges (NACKs) the master by letting SDA be pulled high. ACKs also occur on the bus when data is being transmitted. When the master is writing data, the slave ACKs after every data byte is successfully received. When the master is reading data, the master ACKs after every data byte is received to let the slave know it wants to receive another data byte. When the master wants to stop reading, it NACKs after the last data byte and creates a Stop condition on the bus.

All communication on the bus begins with either a Start condition or a Repeated Start condition. The protocol for starting the bus varies between Standard-Fast mode and Hs-mode. In Standard-Fast mode, the master generates a Start condition by driving SDA from high to low while SCL is high. In Hs-mode, starting the bus is more complicated. Please refer to *High-Speed (Hs) Mode* for the full details of a Hs-mode Start condition. A Repeated Start is generated to either address a different device, or switch between read and write modes. The master generates a Repeated Start condition by driving SDA low while SCL is high. Following the Repeated Start, the master sends out the slave address and a read/write bit as shown in Figure 22. The bus continues to operate in the same speed mode as before the Repeated Start condition.

All communication on the bus ends with a Stop condition. In either Standard-Fast mode or Hs-Mode, a Stop condition occurs when SDA is pulled from low to high while SCL is high. After a Stop condition, the bus remains idle until a master generates a Start condition.

Please refer to the Philipsl<sup>2</sup>C<sup>™</sup> Specification (Version 2.1 Jan, 2000) for a detailed description of the serial interface.

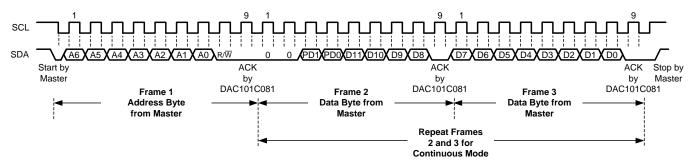

\*Note: In continuous mode, this bit must be an ACK from the data receiver. Immediately preceding a STOP condition, this bit must be a NACK from the master.

Figure 22. Basic Operation

#### **Programming (continued)**

#### 9.5.3 Standard-Fast Mode

In Standard-Fast mode, the master generates a start condition by driving SDA from high to low while SCL is high. The Start condition is always followed by a 7-bit slave address and a Read/Write bit. After these eight bits have been transmitted by the master, SDA is released by the master and the DAC101C081 either ACKs or NACKs the address. If the slave address matches, the DAC101C081 ACKs the master. If the address doesn't match, the DAC101C081 NACKs the master.

For a **write** operation, the master follows the ACK by sending the upper eight data bits to the DAC101C081. Then the DAC101C081 ACKs the transfer by driving SDA low. Next, the lower eight data bits are sent by the master. The DAC101C081 then ACKs the transfer. At this point, the DAC output updates to reflect the contents of the 16-bit DAC register. Next, the master either sends another pair of data bytes, generates a Stop condition to end communication, or generates a Repeated Start condition to communicate with another device on the bus.

For a **read** operation, the DAC101C081 sends out the upper eight data bits of the DAC register. This is followed by an ACK by the master. Next, the lower eight data bits of the DAC register are sent to the master. The master then produces a NACK by letting SDA be pulled high. The NACK is followed by a master-generated Stop condition to end communication on the bus, or a Repeated Start to communicate with another device on the bus.

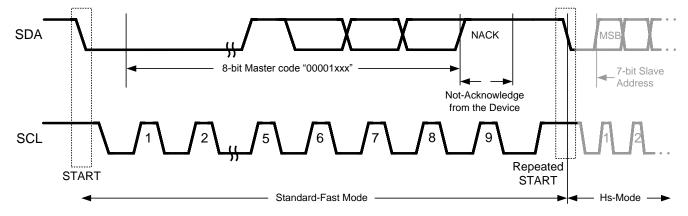

#### 9.5.4 High-Speed (Hs) Mode

For Hs-mode, the sequence of events to begin communication differ slightly from Standard-Fast mode. Figure 23 describes this in further detail. Initially, the bus begins running in Standard-Fast mode. The master generates a Start condition and sends the 8-bit Hs master code (00001XXX) to the DAC101C081. Next, the DAC101C081 responds with a NACK. Once the SCL line has been pulled to a high level, the master switches to Hs-mode by increasing the bus speed and generating a Repeated Start condition (driving SDA low while SCL is pulled high). At this point, the master sends the slave address to the DAC101C081, and communication continues as shown above in the "Basic Operation" Diagram (see Figure 22).

When the master generates a Repeated Start condition while in Hs-mode, the bus stays in Hs-mode awaiting the slave address from the master. The bus continues to run in Hs-mode until a Stop condition is generated by the master. When the master generates a Stop condition on the bus, the bus must be started in Standard-Fast mode again before increasing the bus speed and switching to Hs-mode.

Figure 23. Beginning Hs-Mode Communication

#### **Programming (continued)**

#### 9.5.5 I<sup>2</sup>C Slave (Hardware) Address

The DAC has a seven-bit  $I^2C^{TM}$  slave address. For the VSSOP-8 version of the DAC, this address is configured by the ADR0 and ADR1 address selection inputs. For the DAC101C081, the address is configured by the ADR0 address selection input. ADR0 and ADR1 can be grounded, left floating, or tied to  $V_A$ . If desired, the address selection inputs can be set to  $V_A/2$  rather than left floating. The state of these inputs sets the address the DAC responds to on the  $I^2C^{TM}$  bus (see Table 1). In addition to the selectable slave address, there is also a broadcast address (1001000) for all DAC101C081's and DAC101C085's on the 2-wire bus. When the bus is addressed by the broadcast address, all the DAC101C081's and DAC101C085's will respond and update synchronously. Figure 24 and Figure 25 describe how the master device should address the DAC via the  $I^2C^{TM}$ -Compatible interface.

Keep in mind that the address selection inputs (ADR0 and ADR1) are only sampled until the DAC is correctly addressed with a non-broadcast address. At this point, the ADR0 and ADR1 inputs Tri-State and the slave address is "locked". Changes to ADR0 and ADR1 will not update the selected slave address until the device is power-cycled.

| SLAVE ADDRESS    | DAC101C08      | DAC101C081 (SOT & WSON) <sup>(1)</sup> |                |

|------------------|----------------|----------------------------------------|----------------|

| [A6 - A0]        | ADR1           | ADR0                                   | ADR0           |

| 0001100, 1000110 | Floating       | Floating                               | Floating       |

| 0001101, 1000110 | Floating       | GND                                    | GND            |

| 0001110, 1000111 | Floating       | $V_{A}$                                | V <sub>A</sub> |

| 0001000, 1000100 | GND            | Floating                               | _              |

| 0001001, 1000100 | GND            | GND                                    | _              |

| 0001010, 1000101 | GND            | V <sub>A</sub>                         | _              |

| 1001100, 1100110 | V <sub>A</sub> | Floating                               | _              |

| 1001101, 1100110 | $V_{A}$        | GND                                    | _              |

| 1001110, 1100111 | V <sub>A</sub> | V <sub>A</sub>                         | _              |

| 1001000, 1100100 |                |                                        |                |

**Table 1. Slave Addresses**

#### 9.5.6 Writing to the DAC Register

To write to the DAC, the master addresses the part with the correct slave address (A6-A0) and writes a "zero" to the read/write bit. If addressed correctly, the DAC returns an ACK to the master. The master then sends out the upper data byte. The DAC responds by sending an ACK to the master. Next, the master sends the lower data byte to the DAC. The DAC responds by sending an ACK again. At this point, the master either sends the upper byte of the next data word to be converted by the DAC, generates a Stop condition to end communication, or generates a Repeated Start condition to begin communication with another device on the bus. Until generating a Stop condition, the master can continuously write the upper and lower data bytes to the DAC register. This allows for a maximum DAC conversion rate of 188.9 kilo-conversions per second in Hs-mode.

Figure 24. Typical Write to the DAC Register

<sup>(1)</sup> Pin-compatible alternatives to the DAC101C081 options are available with additional address options.

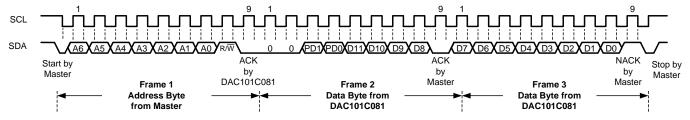

#### 9.5.7 Reading from the DAC Register

To read from the DAC register, the master addresses the part with the correct slave address (A6-A0) and writes a "one" to the read/write bit. If addressed correctly, the DAC returns an ACK to the master. Next, the DAC sends out the upper data byte. The master responds by sending an ACK to the DAC to indicate that it wants to receive another data byte. Then the DAC sends the lower data byte to the master. Assuming only one 16-bit data word is read, the master sends a NACK after receiving the lower data byte. At this point, the master either generates a Stop condition to end communication, or a Repeated Start condition to begin communication with another device on the bus.

Figure 25. Typical Read from the DAC Register

#### 9.6 Registers

#### 9.6.1 DAC Register

The DAC register, Figure 26, has sixteen bits. The first two bits are always zero. The next two bits determine the mode of operation (normal mode or one of three power-down modes). The final twelve bits of the shift register are the data bits. The data format is straight binary (MSB first, LSB last), with twelve 0's corresponding to an output of 0 V and twelve 1's corresponding to a full-scale output of  $V_A$  - 1 LSB. When writing to the DAC Register,  $V_{OUT}$  will update on the rising edge of the ACK following the lower data byte.

Figure 26. DAC Register Contents

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 10.1 Application Information

#### 10.1.1 Bipolar Operation

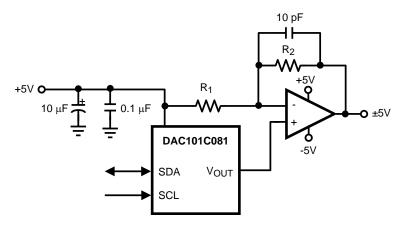

The DAC101C081 is designed for single supply operation and thus has a unipolar output. However, a bipolar output may be obtained with the circuit in Figure 27. This circuit will provide an output voltage range of ±5 Volts. A rail-to-rail amplifier should be used if the amplifier supplies are limited to ±5 V.

Figure 27. Bipolar Operation

The output voltage of this circuit for any code is found to be:

$$V_0 = (V_A \times (D / 1024) \times ((R1 + R2) / R1) - V_A \times R2 / R1)$$

where *D* is the input code in decimal form.

(2)

With  $V_A = 5 \text{ V}$  and R1 = R2,

$$V_0 = (10 \times D / 1024) - 5 V$$

(3)

A list of rail-to-rail amplifiers suitable for this application are indicated in Table 2.

Table 2. Some Rail-to-Rail Amplifiers

| AMP     | PKGS             | Typ V <sub>OS</sub> | Typ I <sub>SUPPLY</sub> |

|---------|------------------|---------------------|-------------------------|

| LMP7701 | SOT-23-5         | 37 uV               | 0.79 mA                 |

| LMV841  | SC70-5           | 50 uV               | 1 mA                    |

| LMC7111 | SOT-23-5         | 0.9 mV              | 25 μΑ                   |

| LM7301  | SO-8<br>SOT-23-5 | 0.03 mV             | 620 μΑ                  |

| LM8261  | SOT-23-5         | 0.7 mV              | 1 mA                    |

#### 10.1.2 DSP/Microprocessor Interfacing

Interfacing the DAC101C081 to microprocessors and DSPs is quite simple. The following guidelines are offered to simplify the design process.

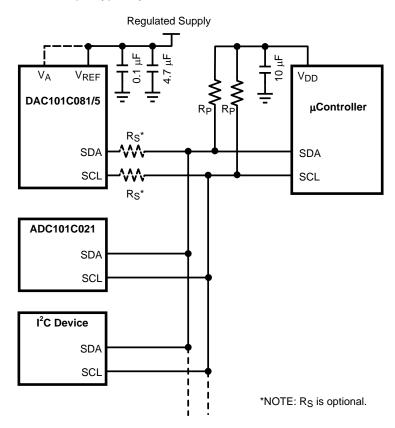

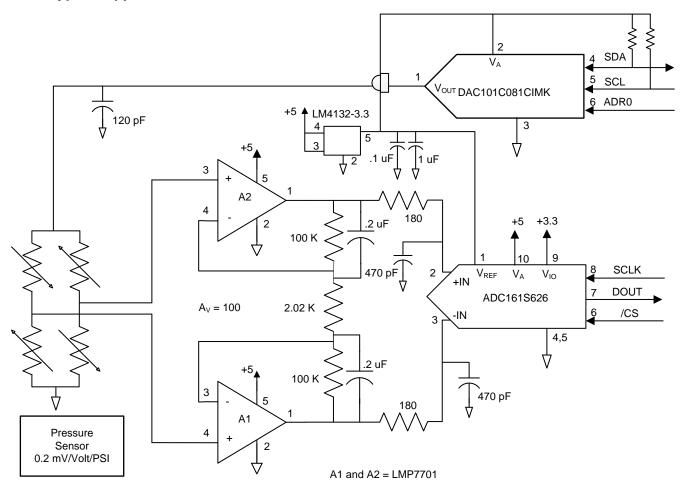

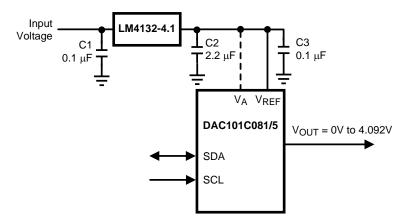

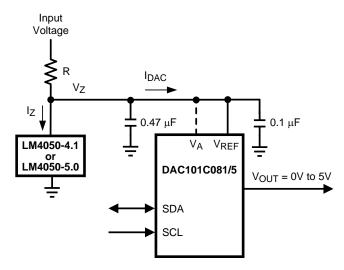

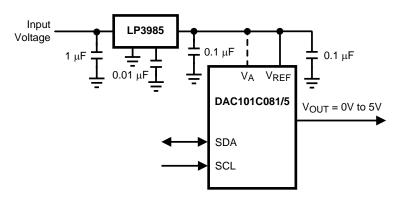

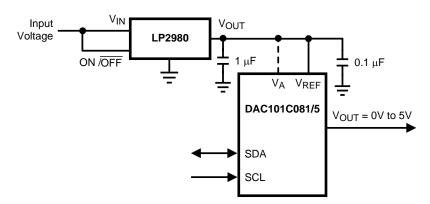

#### 10.1.2.1 Interfacing to the 2-wire Bus