# 八路同步采样 24 位模数转换器

查询样品: ADS1278-EP

### 特性

- 同时测量八个通道

- 高达 128kSPS 数据速率

- AC 性能:

62kHz 带宽

111dB 信噪比 (SNR)(高分辨率模式)

-108dB 总谐波失真 (THD)

- DC 精度:

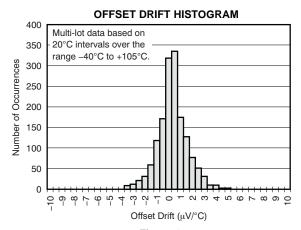

0.8-μV/°C 偏移漂移

1.3-ppm/°C 增益漂移

- 可选运行模式:

高速: 128kSPS, 106dB SNR

高分辨率: 52kSPS, 111dB SNR

低功耗: 52kSPS, 31mW/ch

低速: 10kSPS, 7mW/ch

- 线性相位数字滤波器

- SPI™ 或者帧同步串行接口

- 低采样孔径错误

- 调制器输出选项(数字滤波器旁通)

- 模拟电源:5V数字内核:1.8V

- I/O 电源: 1.8V 至 3.3V

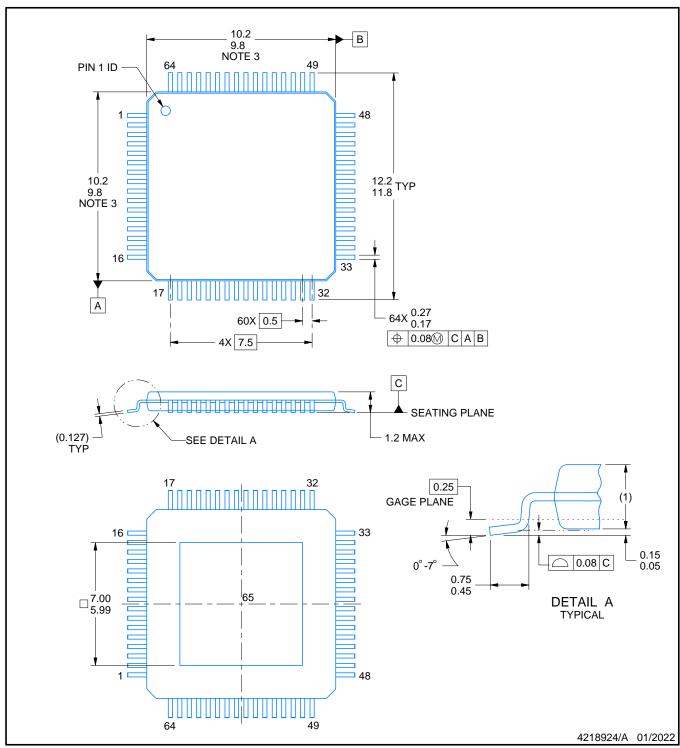

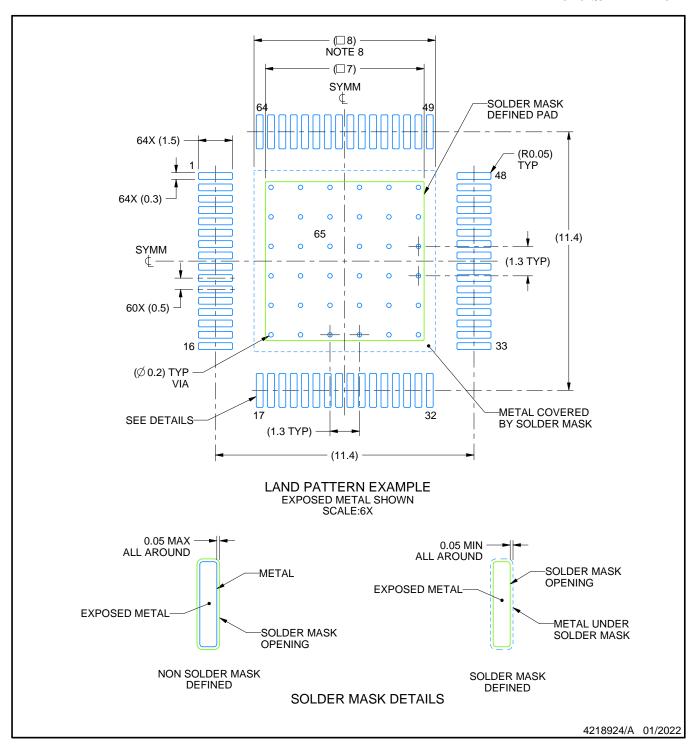

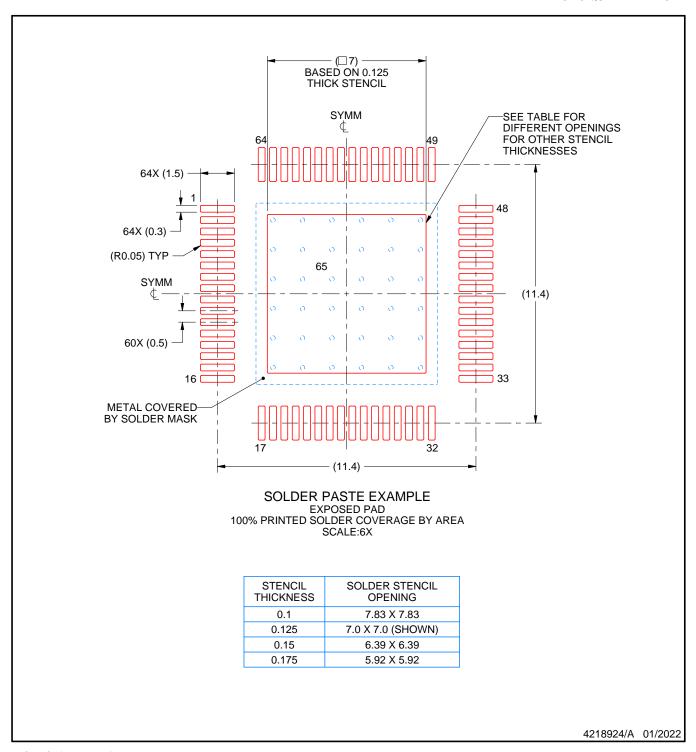

- 当前提供散热增强薄型四方扁平封装 (HTQFP)-64 封装 PowerPAD™ 封装

#### 支持国防、航空航天、和医疗应用

- 受控基线

- 一个组装/测试场所

- 一个制造场所

- 军用温度范围 (-55°C/125°C) 内可用 (1)

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

- (1) 可提供额外温度范围-请与厂家联系

#### 应用范围

- 振动/模式分析

- 多通道数据采集

- 声学/动态应变仪

- 压力传感器

### 说明

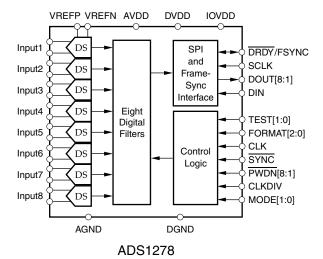

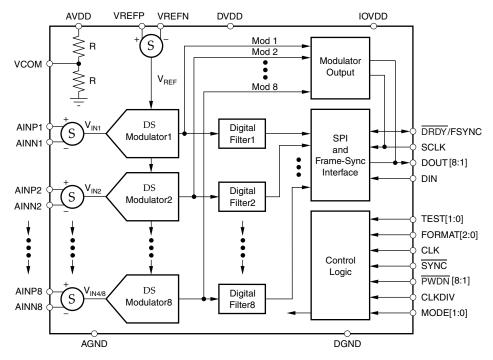

基于单通道ADS1271, ADS1278 (八通道) 是一款 24 位、三角积分 ( $\Delta\Sigma$ ) 模数转换器 (ADC), 其数据速率高达每秒 128k 次采样 (SPS), 从而可实现八通道同时采样。

传统上来讲,提供良好漂移性能的工业用三角积分 ADC 使用带有较大通带衰减的数字滤波器。 因此,它 们的信号带宽有限并且主要适合于 dc 测量。 音频应用中的高分辨 ADC 提供更大的可用带宽,但是与工业用 ADC 相比,它的偏移和漂移技术规格被大大削弱。 ADS1278 将三种类型的转换器组合在一起,从而实现带有出色 dc 和 ac 技术规格的高精度工业测量。

高阶、斩波稳定调制器在低带内噪声情况下实现极低漂移。 板载抽取滤波器抑制调制器和信号带外噪声。 这些 ADC 在纹波小于 0.005dB 的情况下提供高达那奎斯特速率 90% 的可用信号带宽。

四个运行模式可实现速度、分辨率和功率的优化。 所有操作直接由引脚控制;无需寄存器编程。 器件可在军用温度范围(-55°C 至 125°C)内运行并且采用HTQFP-64 PowerPAD 封装。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE    |             | PACKAGE ORDERABLE PART NUMBER |           | VID NUMBER     |  |

|----------------|------------|-------------|-------------------------------|-----------|----------------|--|

| –55°C to 125°C | TQFP - PAP | Reel of 250 | ADS1278MPAPTEP                | ADS1278EP | V62/12611-01XE |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

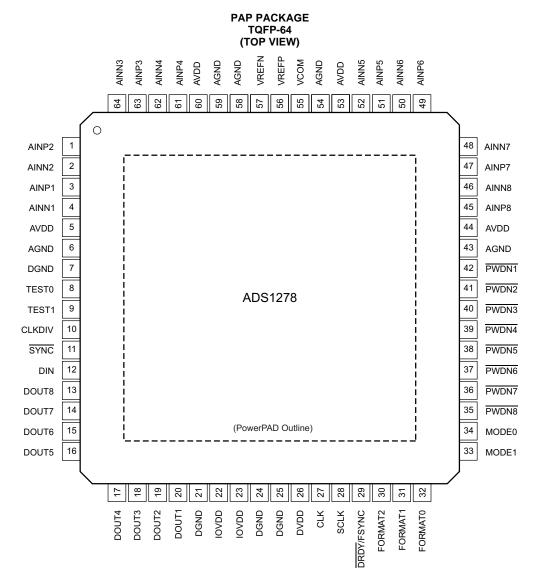

#### **PIN ASSIGNMENTS**

**Table 1. PIN DESCRIPTIONS**

| PIN   |                      |               |                                                        |

|-------|----------------------|---------------|--------------------------------------------------------|

| NAME  | NO.                  | FUNCTION      | DESCRIPTION                                            |

| AGND  | 6, 43, 54,<br>58, 59 | Analog ground | Analog ground; connect to DGND using a single plane.   |

| AINP1 | 3                    | Analog input  |                                                        |

| AINP2 | 1                    | Analog input  |                                                        |

| AINP3 | 63                   | Analog input  |                                                        |

| AINP4 | 61                   | Analog input  | AINP[8:1] Positive analog input, channels 8 through 1. |

| AINP5 | 51                   | Analog input  |                                                        |

| AINP6 | 49                   | Analog input  |                                                        |

| AINP7 | 47                   | Analog input  |                                                        |

| AINP8 | 45                   | Analog input  |                                                        |

# **Table 1. PIN DESCRIPTIONS (continued)**

| PIN            |               |                      |                                                                                                                                                    |

|----------------|---------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO.           | FUNCTION             | DESCRIPTION                                                                                                                                        |

| AINN1          | 4             | Analog input         |                                                                                                                                                    |

| AINN2          | 2             | Analog input         |                                                                                                                                                    |

| AINN3          | 64            | Analog input         |                                                                                                                                                    |

| AINN4          | 62            | Analog input         | AINN[8:1] Negative analog input, channels 8 through 1.                                                                                             |

| AINN5          | 52            | Analog input         |                                                                                                                                                    |

| AINN6          | 50            | Analog input         |                                                                                                                                                    |

| AINN7          | 48            | Analog input         |                                                                                                                                                    |

| AINN8          | 46            | Analog input         |                                                                                                                                                    |

| AVDD           | 5, 44, 53, 60 | Analog power supply  | Analog power supply (4.75V to 5.25V).                                                                                                              |

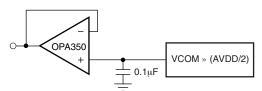

| VCOM           | 55            | Analog output        | AVDD/2 Unbuffered voltage output.                                                                                                                  |

| VREFN          | 57            | Analog input         | Negative reference input.                                                                                                                          |

| VREFP          | 56            | Analog input         | Positive reference input.                                                                                                                          |

| CLK            | 27            | Digital input        | Master clock input (f <sub>CLK</sub> ).                                                                                                            |

| CLKDIV         | 10            | Digital input        | CLK input divider control: 1 = 37MHz (High-Speed mode)/otherwise 27MHz 0 = 13.5MHz (low-power)/5.4MHz (low-speed)                                  |

| DGND           | 7, 21, 24, 25 | Digital ground       | Digital ground power supply.                                                                                                                       |

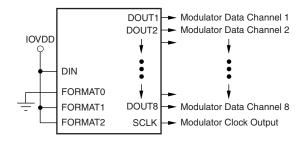

| DIN            | 12            | Digital input        | Daisy-chain data input.                                                                                                                            |

| DOUT1          | 20            | Digital output       | DOUT1 is TDM data output (TDM mode).                                                                                                               |

| DOUT2          | 19            | Digital output       |                                                                                                                                                    |

| DOUT3          | 18            | Digital output       |                                                                                                                                                    |

| DOUT4          | 17            | Digital output       | DOUT[8:1] Data output for channels 8 through 1.                                                                                                    |

| DOUT5          | 16            | Digital output       |                                                                                                                                                    |

| DOUT6          | 15            | Digital output       |                                                                                                                                                    |

| DOUT7          | 14            | Digital output       |                                                                                                                                                    |

| DOUT8          | 13            | Digital output       |                                                                                                                                                    |

| DRDY/<br>FSYNC | 29            | Digital input/output | Frame-Sync protocol: frame clock input; SPI protocol: data ready output.                                                                           |

| DVDD           | 26            | Digital power supply | Digital core power supply.                                                                                                                         |

| FORMAT0        | 32            | Digital input        |                                                                                                                                                    |

| FORMAT1        | 31            | Digital input        | FORMAT[2:0] Selects Frame-Sync/SPI protocol, TDM/discrete data outputs, fixed/dynamic position TDM data, and modulator mode/normal operating mode. |

| FORMAT2        | 30            | Digital input        | mica synamo position 12 m cata, and modulate model model operating model                                                                           |

| IOVDD          | 22, 23        | Digital power supply | I/O power supply (+1.65V to +3.6V).                                                                                                                |

| MODE0          | 34            | Digital input        | MODE[1:0] Selects High-Speed, High-Resolution, Low-Power, or Low-Speed                                                                             |

| MODE1          | 33            | Digital input        | mode operation.                                                                                                                                    |

| PWDN1          | 42            | Digital input        |                                                                                                                                                    |

| PWDN2          | 41            | Digital input        |                                                                                                                                                    |

| PWDN3          | 40            | Digital input        |                                                                                                                                                    |

| PWDN4          | 39            | Digital input        | PWDN[8:1] Power-down control for channels 8 through 1.                                                                                             |

| PWDN5          | 38            | Digital input        |                                                                                                                                                    |

| PWDN6          | 37            | Digital input        |                                                                                                                                                    |

| PWDN7          | 36            | Digital input        |                                                                                                                                                    |

| PWDN8          | 35            | Digital input        |                                                                                                                                                    |

| SCLK           | 28            | Digital input/output | Serial clock input, Modulator clock output.                                                                                                        |

| SYNC           | 11            | Digital input        | Synchronize input (all channels).                                                                                                                  |

| TEST0          | 8             | Digital input        | TEST[1:0] Test mode select: 00 = Normal operation 01 = Do not use                                                                                  |

| TEST1          | 9             | Digital input        | 11 = Test mode 10 = Do not use                                                                                                                     |

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range, unless otherwise noted(1)

|                                              |            |                    | UNIT |

|----------------------------------------------|------------|--------------------|------|

| AVDD to AGND                                 |            | -0.3 to 6.0        | V    |

| DVDD, IOVDD to DGND                          |            | -0.3 to 3.6        | V    |

| AGND to DGND                                 |            | -0.3 to 0.3        | V    |

| Lament accommend                             | Momentary  | 100                | mA   |

| Input current                                | Continuous | 10                 | mA   |

| Analog input to AGND                         |            | -0.3 to AVDD + 0.3 | V    |

| Digital input or output to DGND              | )          | -0.3 to DVDD + 0.3 | V    |

| Maximum junction temperature, T <sub>J</sub> |            | 150                | °C   |

| Storage temperature range                    |            | -60 to 150         | °C   |

Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### THERMAL INFORMATION

|               |                                                       | ADS1278 |       |

|---------------|-------------------------------------------------------|---------|-------|

|               | THERMAL METRIC <sup>(1)</sup>                         | PAP     | UNITS |

|               |                                                       | 64 PINS |       |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance <sup>(2)</sup> | 33.1    |       |

| $\theta_{JC}$ | Junction-to-case thermal resistance                   | 6.2     |       |

| $\theta_{JB}$ | Junction-to-board thermal resistance <sup>(3)</sup>   | 7.9     | °C/W  |

| $\Psi_{JT}$   | Junction-to-top characterization parameter (4)        | 0.2     |       |

| ΨЈВ           | Junction-to-board characterization parameter (5)      | 7.8     |       |

- 有关传统和新的热 度量的更多信息,请参阅*IC 封装热度量*应用报告, SPRA953。 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环

- 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。 结至顶部特征参数, ψ<sub>JT</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参 数以便获得 θ<sub>JA</sub>。

- 结至电路板特征参数, Ψ<sub>JB</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该 参数以便获得  $\theta_{JA}$  。

#### **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = -55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ , AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| P.                                             | ARAMETER                 | TEST CONDITIONS                            | MIN        | TYP                     | MAX        | UNIT                 |

|------------------------------------------------|--------------------------|--------------------------------------------|------------|-------------------------|------------|----------------------|

| Operating temperature range, T <sub>A</sub>    |                          |                                            | -55        |                         | 125        | °C                   |

| Analog Inputs                                  |                          |                                            |            |                         |            |                      |

| Full-scale input voltage                       | (FSR <sup>(1)</sup> )    | $V_{IN} = (AINP - AINN)$                   |            | ±V <sub>REF</sub>       |            | V                    |

| Absolute input voltage                         |                          | AINP or AINN to AGND                       | AGND - 0.1 |                         | AVDD + 0.1 | V                    |

| Common-mode input vo                           | Itage (V <sub>CM</sub> ) | V <sub>CM</sub> = (AINP + AINN)/2          |            | 2.5                     |            | V                    |

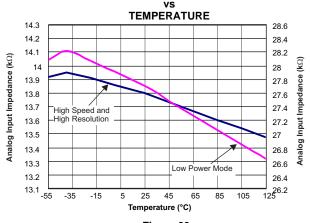

|                                                | High-Speed mode          |                                            |            | 14                      |            | kΩ                   |

| Differential input                             | High-Resolution mode     |                                            |            | 14                      |            | kΩ                   |

| impedance                                      | Low-Power mode           |                                            |            | 28                      |            | kΩ                   |

|                                                | Low-Speed mode           |                                            |            | 140                     |            | kΩ                   |

| DC Performance                                 | 1                        | ,                                          |            |                         |            |                      |

| Resolution                                     |                          | No missing codes                           | 24         |                         |            | Bits                 |

|                                                |                          | $f_{CLK} = 32.768MHz^{(2)}$                |            | 128,000                 |            | SPS                  |

|                                                | High-Speed mode          | f <sub>CLK</sub> = 27MHz                   |            | 105,469                 |            | SPS <sup>(3)</sup>   |

| Data rate (f <sub>DATA</sub> )                 | High-Resolution mode     |                                            |            | 52,734                  |            | SPS                  |

|                                                | Low-Power mode           |                                            |            | 52,734                  |            | SPS                  |

|                                                | Low-Speed mode           |                                            |            | 10,547                  |            | SPS                  |

| Integral nonlinearity (INL                     | )(4)                     | Differential input, V <sub>CM</sub> = 2.5V |            | ±0.0003                 | ±0.0014    | % FSR <sup>(1)</sup> |

| Offset error                                   |                          |                                            |            | 0.25                    | 2          | mV                   |

| Offset drift                                   |                          |                                            |            | 0.8                     |            | μV/°C                |

| Gain error                                     |                          |                                            |            | 0.1                     | 0.5        | % FSR                |

| Gain drift                                     |                          |                                            |            | 1.3                     |            | ppm/°C               |

|                                                | High-Speed mode          | Shorted input                              |            | 8.5                     | 68         | μV, rms              |

|                                                | High-Resolution mode     | Shorted input                              |            | 5.5                     | 13         | μV, rms              |

| Noise                                          | Low-Power mode           | Shorted input                              |            | 8.5                     | 21         | μV, rms              |

|                                                | Low-Speed mode           | Shorted input                              |            | 8.0                     | 21         | μV, rms              |

| Common-mode rejection                          | 1                        | f <sub>CM</sub> = 60Hz                     | 90         | 108                     |            | dB                   |

|                                                | AVDD                     |                                            |            | 80                      |            | dB                   |

| Power-supply rejection                         | DVDD                     | f <sub>PS</sub> = 60Hz                     |            | 85                      |            | dB                   |

|                                                | IOVDD                    |                                            |            | 105                     |            | dB                   |

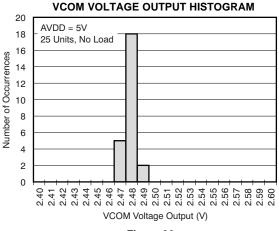

| V <sub>COM</sub> output voltage                |                          | No load                                    |            | AVDD/2                  |            | V                    |

| AC Performance                                 |                          | 1                                          | ı          |                         |            |                      |

| Crosstalk                                      |                          | $f = 1kHz, -0.5dBFS^{(5)}$                 |            | -107                    |            | dB                   |

|                                                | High-Speed mode          | -                                          | 88.3       | 106                     |            | dB                   |

|                                                |                          | V <sub>REF</sub> = 2.5V                    | 101        | 110                     |            | dB                   |

| Signal-to-noise ratio                          | High-Resolution mode     | V <sub>REF</sub> = 3V                      |            | 111                     |            | dB                   |

| (SNR) <sup>(6)</sup> (unweighted)              | Low-Power mode           | - 151                                      | 98         | 106                     |            | dB                   |

|                                                | Low-Speed mode           |                                            | 98         | 107                     |            | dB                   |

| Total harmonic distortion (THD) <sup>(7)</sup> |                          | V <sub>IN</sub> = 1kHz, -0.5dBFS           |            | -108                    | -96        | dB                   |

| Spurious-free dynamic r                        |                          | ,                                          |            | 109                     |            | dB                   |

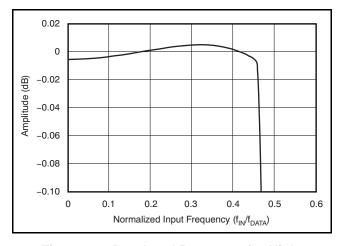

| Passband ripple                                | ·                        |                                            |            | ±0.005                  |            | dB                   |

| Passband                                       |                          |                                            |            | 0.453 f <sub>DATA</sub> |            | Hz                   |

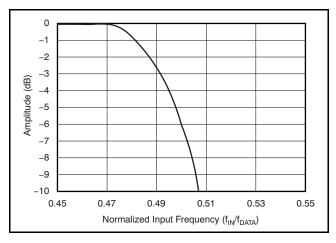

| -3dB Bandwidth                                 |                          |                                            |            | 0.49 f <sub>DATA</sub>  |            | Hz                   |

<sup>(1)</sup> FSR = full-scale range = 2V<sub>REF</sub>.

(2) f<sub>CLK</sub> = 32.768MHz max for High-Speed mode, and 27MHz max for all other modes. When f<sub>CLK</sub> > 27MHz, operation is limited to Frame-Sync mode and V<sub>REF</sub> ≤ 2.6V.

(3) SPS = samples per second.

Best fit method.

Worst-case channel crosstalk between one or more channels. (5)

Minimum SNR is ensured by the limit of the DC noise specification.

THD includes the first nine harmonics of the input signal; Low-Speed mode includes the first five harmonics. (7)

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = -55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ , AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| F                                     | PARAMETER            | TEST CONDITIONS                             | MIN                     | TYP                  | MAX                          | UNIT |

|---------------------------------------|----------------------|---------------------------------------------|-------------------------|----------------------|------------------------------|------|

| Stop band attenuation                 | High-Resolution mode |                                             | 95                      |                      |                              | dB   |

| Stop band attendation                 | All other modes      |                                             | 100                     |                      |                              |      |

| Stop band                             | High-Resolution mode |                                             | 0.547 f <sub>DATA</sub> |                      | 127.453<br>f <sub>DATA</sub> | Hz   |

| Stop Bana                             | All other modes      |                                             | 0.547 f <sub>DATA</sub> |                      | 63.453<br>f <sub>DATA</sub>  | Hz   |

| Croup dolov                           | High-Resolution mode |                                             |                         | 39/f <sub>DATA</sub> |                              | s    |

| Group delay                           | All other modes      |                                             |                         | 38/f <sub>DATA</sub> |                              | S    |

| Cattling time (lateray)               | High-Resolution mode | Complete settling                           |                         | 78/f <sub>DATA</sub> |                              | S    |

| Settling time (latency)               | All other modes      | Complete settling                           |                         | 76/f <sub>DATA</sub> |                              | S    |

| Voltage Reference Inp                 | uts                  |                                             |                         |                      |                              |      |

| Reference input voltage               | (V <sub>REE</sub> )  | f <sub>CLK</sub> = 27MHz                    | 0.5                     | 2.5                  | 3.1                          | V    |

| (V <sub>REF</sub> = VREFP – VREF      |                      | f <sub>CLK</sub> = 32.768MHz <sup>(2)</sup> | 0.5                     | 2.5                  | 2.6                          | V    |

| Negative reference inpu               | ut (VREFN)           |                                             | AGND - 0.1              |                      | AGND +<br>0.1                | V    |

| Positive reference input              | (VREFP)              |                                             | VREFN + 0.5             |                      | AVDD +<br>0.1                | V    |

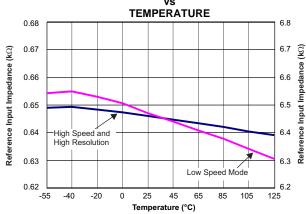

|                                       | High-Speed mode      |                                             |                         | 0.65                 |                              | kΩ   |

| Reference Input                       | High-Resolution mode |                                             |                         | 0.65                 |                              | kΩ   |

| impedance                             | Low-Power mode       |                                             |                         | 1.3                  |                              | kΩ   |

|                                       | Low-Speed mode       |                                             |                         | 6.5                  |                              | kΩ   |

| Digital Input/Output (I               | OVDD = 1.8V to 3.6V) |                                             |                         |                      | '                            |      |

| V <sub>IH</sub>                       |                      |                                             | 0.7 IOVDD               |                      | IOVDD                        | V    |

| V <sub>IL</sub>                       |                      |                                             | DGND                    |                      | 0.3<br>IOVDD                 | V    |

| V <sub>OH</sub>                       |                      | I <sub>OH</sub> = 4mA                       | 0.8 IOVDD               |                      | IOVDD                        | V    |

| V <sub>OL</sub>                       |                      | I <sub>OL</sub> = 4mA                       | DGND                    |                      | 0.2<br>IOVDD                 | V    |

| Input leakage                         |                      | 0 < V <sub>IN DIGITAL</sub> < IOVDD         |                         |                      | ±10                          | μA   |

|                                       |                      | High-Speed mode <sup>(8)</sup>              | 0.1                     |                      | 32.768                       | MHz  |

| Master clock rate (f <sub>CLK</sub> ) |                      | Other modes                                 | 0.1                     |                      | 27                           | MHz  |

| Power Supply                          |                      |                                             |                         |                      | "                            |      |

| AVDD                                  |                      |                                             | 4.75                    | 5                    | 5.25                         | V    |

| DVDD                                  |                      |                                             | 1.65                    | 1.8                  | 1.95                         | V    |

| IOVDD                                 |                      |                                             | 1.65                    |                      | 3.6                          | V    |

|                                       | AVDD                 |                                             |                         | 1                    | 10                           | μA   |

| Power-down current                    | DVDD                 |                                             |                         | 1                    | 50                           | μA   |

|                                       | IOVDD                |                                             |                         | 1                    | 11                           | μA   |

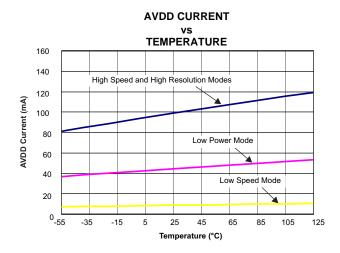

|                                       | High-Speed mode      |                                             |                         | 97                   | 145                          | mA   |

|                                       | High-Resolution mode |                                             |                         | 97                   | 145                          | mA   |

| AVDD current                          | Low-Power mode       |                                             |                         | 44                   | 64                           | mA   |

|                                       | Low-Speed mode       |                                             |                         | 9                    | 14                           | mA   |

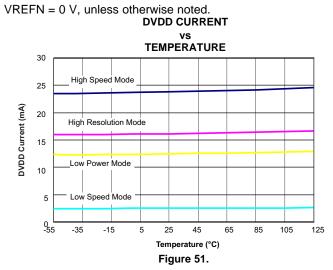

|                                       | High-Speed mode      |                                             |                         | 23                   | 30                           | mA   |

|                                       | High-Resolution mode |                                             |                         | 16                   | 20                           | mA   |

| OVDD current                          | Low-Power mode       |                                             |                         | 12                   | 17                           | mA   |

|                                       | Low-Speed mode       |                                             |                         | 2.5                  | 4.5                          | mA   |

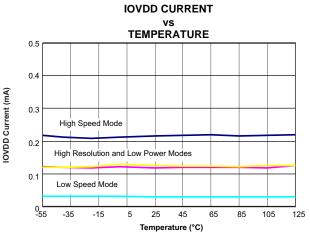

|                                       | High-Speed mode      |                                             |                         | 0.25                 | 1                            | mA   |

|                                       | High-Resolution mode |                                             |                         | 0.125                | 0.6                          | mA   |

| IOVDD current                         | Low-Power mode       |                                             |                         | 0.125                | 0.6                          | mA   |

|                                       |                      |                                             |                         |                      |                              |      |

<sup>(8)</sup>  $f_{CLK} = 32.768 MHz$  max for High-Speed mode, and 27MHz max for all other modes. When  $f_{CLK} > 27 MHz$ , operation is limited to Frame-Sync mode and  $V_{REF} \le 2.6 V$ .

**ISTRUMENTS**

ZHCSAC0-AUGUST 2012 www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = -55$ °C to 125°C, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, VREFN = 0 V, and all channels active, unless otherwise noted.

| PARAMETER         |                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|----------------------|-----------------|-----|-----|-----|------|

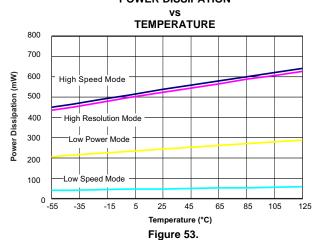

|                   | High-Speed mode      |                 |     | 530 | 785 | mW   |

| Power dissipation | High-Resolution mode |                 |     | 515 | 765 | mW   |

| rower dissipation | Low-Power mode       |                 |     | 245 | 355 | mW   |

|                   | Low-Speed mode       |                 |     | 50  | 80  | mW   |

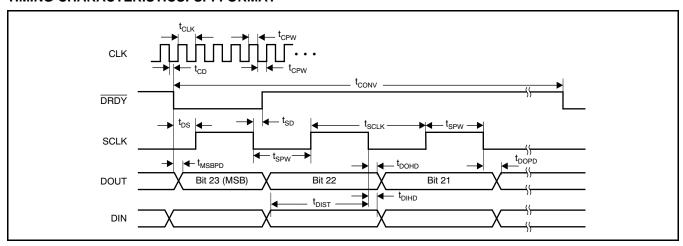

#### **TIMING CHARACTERISTICS: SPI FORMAT**

#### TIMING REQUIREMENTS: SPI FORMAT

For  $T_A = -40$ °C to 125°C, IOVDD = 1.65 V to 3.6 V, and DVDD = 1.65 V to 1.95 V.

| SYMBOL                       | PARAMETER                                                          | MIN | TYP | MAX    | UNIT             |

|------------------------------|--------------------------------------------------------------------|-----|-----|--------|------------------|

| t <sub>CLK</sub>             | CLK period (1/f <sub>CLK</sub> ) <sup>(1)</sup>                    | 37  |     | 10,000 | ns               |

| t <sub>CPW</sub>             | CLK positive or negative pulse width                               | 15  |     |        | ns               |

| t <sub>CONV</sub>            | Conversion period (1/f <sub>DATA</sub> ) <sup>(2)</sup>            | 256 |     | 2560   | t <sub>CLK</sub> |

| t <sub>CD</sub> (3)          | Falling edge of CLK to falling edge of DRDY                        |     | 22  |        | ns               |

| t <sub>DS</sub> (3)          | Falling edge of DRDY to rising edge of first SCLK to retrieve data | 1   |     |        | t <sub>CLK</sub> |

| t <sub>MSBPD</sub>           | DRDY falling edge to DOUT MSB valid (propagation delay)            |     |     | 16     | ns               |

| t <sub>SD</sub> (3)          | Falling edge of SCLK to rising edge of DRDY                        |     | 18  |        | ns               |

| t <sub>SCLK</sub> (4)        | SCLK period                                                        | 1   |     |        | t <sub>CLK</sub> |

| t <sub>SPW</sub>             | SCLK positive or negative pulse width                              | 0.4 |     |        | t <sub>CLK</sub> |

| t <sub>DOHD</sub> (5)(3) (6) | SCLK falling edge to new DOUT invalid (hold time)                  | 10  |     |        | ns               |

| t <sub>DOPD</sub> (5)(3)     | SCLK falling edge to new DOUT valid (propagation delay)            |     |     | 32     | ns               |

| t <sub>DIST</sub>            | New DIN valid to falling edge of SCLK (setup time)                 | 6   |     |        | ns               |

| t <sub>DIHD</sub> (6)        | Old DIN valid to falling edge of SCLK (hold time)                  | 6   |     |        | ns               |

- $f_{CLK}=27 MHz$  maximum. Depends on MODE[1:0] and CLKDIV selection. See Table 7 (f<sub>CLK</sub>/f<sub>DATA</sub>). Load on  $\overline{DRDY}$  and DOUT = 20pF.

- For best performance, limit  $f_{SCLK}/f_{CLK}$  to ratios of 1, 1/2, 1/4, 1/8, etc.

- Timing parameters are characerized or guranteed by design for specified temperature but not production tested. (5)

- t<sub>DOHD</sub> (DOUT hold time) and t<sub>DIHD</sub> (DIN hold time) are specified under opposite worst-case conditions (digital supply voltage and ambient temperature). Under equal conditions, with DOUT connected directly to DIN, the timing margin is >4ns.

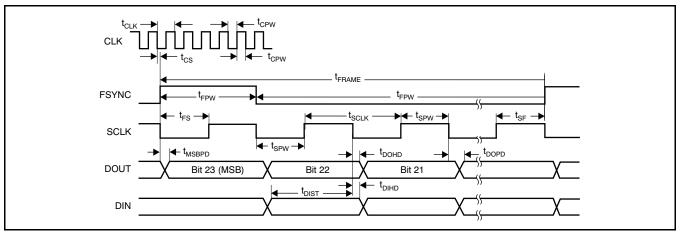

Figure 1. TIMING CHARACTERISTICS: FRAME-SYNC FORMAT

# TIMING REQUIREMENTS: FRAME-SYNC FORMAT(1)

For  $T_A = -40$ °C to 125°C, IOVDD = 1.65 V to 3.6 V, and DVDD = 1.65 V to 1.95 V.

| SYMBOL                           | PARAMETER                                               |                                             | MIN   | TYP | MAX    | UNIT              |

|----------------------------------|---------------------------------------------------------|---------------------------------------------|-------|-----|--------|-------------------|

|                                  | CLIV paried (4/6                                        | All modes                                   | 37    |     | 10,000 | ns                |

| t <sub>CLK</sub>                 | CLK period (1/f <sub>CLK</sub> )                        | High-Speed mode only                        | 30.5  |     |        | ns                |

| t <sub>CPW</sub>                 | CLK positive or negative pulse wi                       | dth                                         | 12    |     |        | ns                |

| t <sub>CS</sub>                  | Falling edge of CLK to falling edg                      | e of SCLK                                   | -0.25 |     | 0.25   | t <sub>CLK</sub>  |

| t <sub>FRAME</sub>               | Frame period (1/f <sub>DATA</sub> ) <sup>(2)</sup>      |                                             | 256   |     | 2560   | t <sub>CLK</sub>  |

| t <sub>FPW</sub>                 | FSYNC positive or negative pulse                        | FSYNC positive or negative pulse width      |       |     |        | t <sub>SCLK</sub> |

| t <sub>FS</sub>                  | Rising edge of FSYNC to rising edge of SCLK             |                                             | 5     |     |        | ns                |

| t <sub>SF</sub>                  | Rising edge of SCLK to rising edge                      | Rising edge of SCLK to rising edge of FSYNC |       |     |        | ns                |

| t <sub>SCLK</sub>                | SCLK period <sup>(3)</sup>                              |                                             | 1     |     |        | t <sub>CLK</sub>  |

| t <sub>SPW</sub>                 | SCLK positive or negative pulse v                       | width                                       | 0.4   |     |        | t <sub>CLK</sub>  |

| t <sub>DOHD</sub> (4)(5) (6)     | SCLK falling edge to old DOUT in                        | nvalid (hold time)                          | 10    |     |        | ns                |

| t <sub>DOPD</sub> (4)(6)         | SCLK falling edge to new DOUT                           | valid (propagation delay)                   |       |     | 31     | ns                |

| t <sub>MSBPD</sub> (4)           | FSYNC rising edge to DOUT MSB valid (propagation delay) |                                             |       |     | 31     | ns                |

| t <sub>DIST</sub>                | New DIN valid to falling edge of SCLK (setup time)      |                                             | 6     |     |        | ns                |

| t <sub>DIHD</sub> <sup>(5)</sup> | Old DIN valid to falling edge of S0                     | CLK (hold time)                             | 6     |     |        | ns                |

- Timing parameters are characerized or guranteed by design for specified temperature but not production tested. Depends on MODE[1:0] and CLKDIV selection. See Table 7 ( $f_{CLK}/f_{DATA}$ ). SCLK must be continuously running and limited to ratios of 1, 1/2, 1/4, and 1/8 of  $f_{CLK}$ . Timing parameters are characerized or guranteed by design for specified temperature but not production tested.

- (3)

- (4)

- $t_{DOHD}$  (DOUT hold time) and  $t_{DIHD}$  (DIN hold time) are specified under opposite worst-case conditions (digital supply voltage and ambient temperature). Under equal conditions, with DOUT connected directly to DIN, the timing margin is >4 ns.

- Load on DOUT = 20 pF.

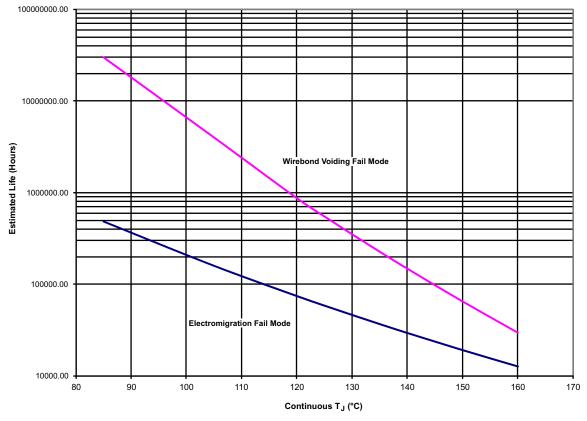

Figure 2. ADS1278 Operating Life Derating and Wirebond Voiding Fail Mode Chart

#### Notes:

- 1. See datasheet for absolute maximum and minimum recommended operating conditions.

- 2. Sillicon operating life design goal is 10 years at 110°C junction temperature.

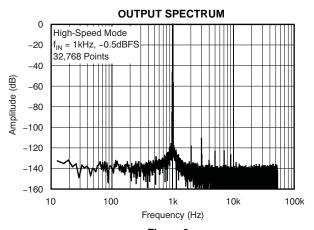

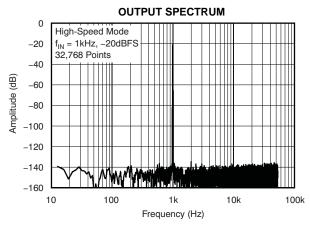

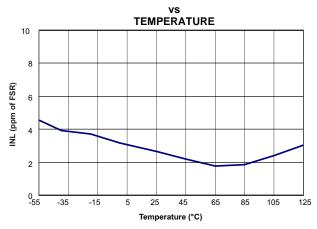

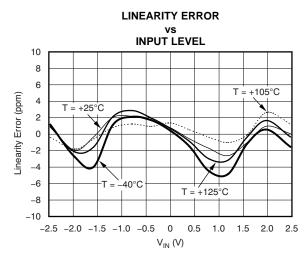

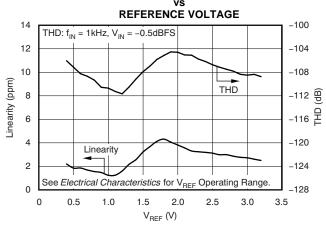

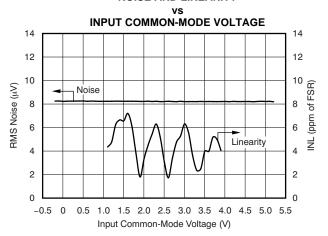

#### TYPICAL CHARACTERISTICS

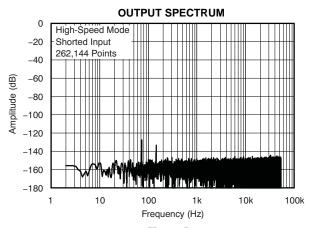

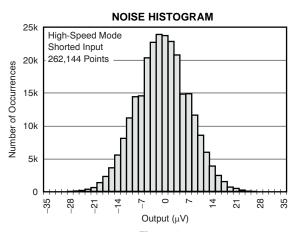

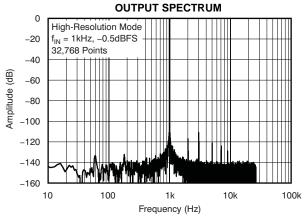

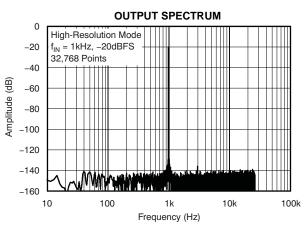

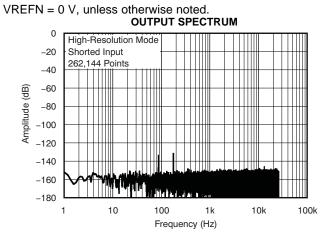

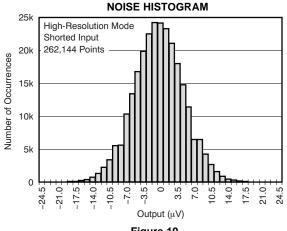

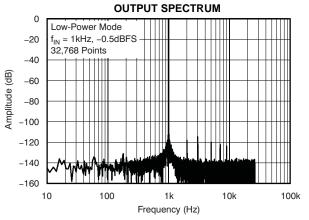

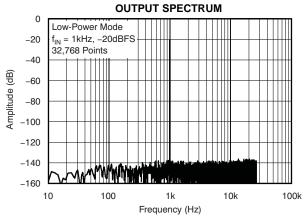

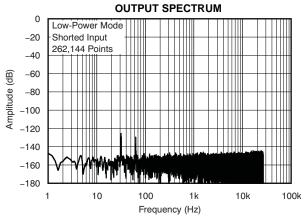

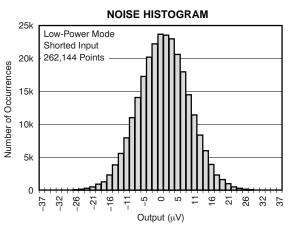

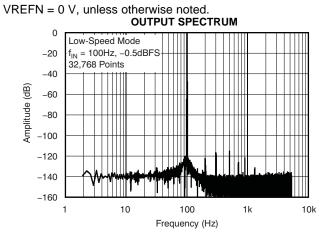

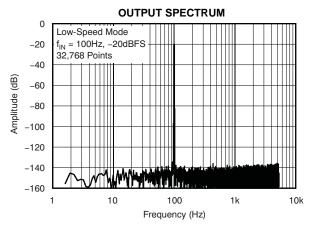

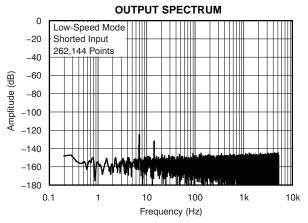

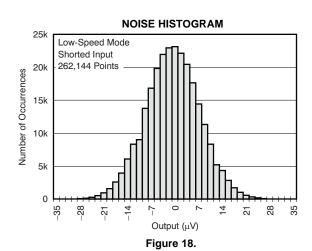

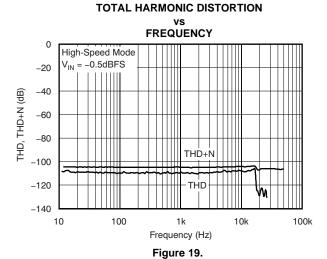

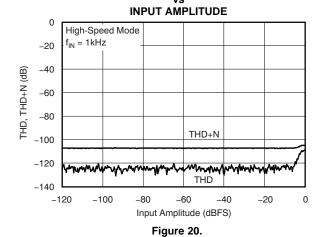

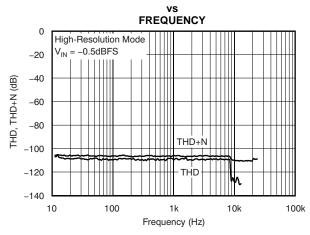

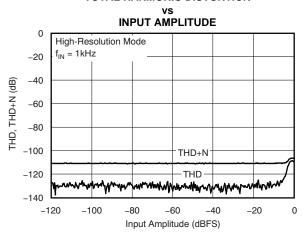

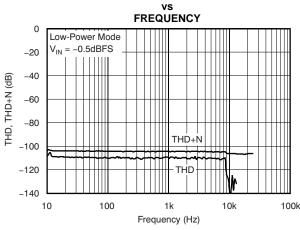

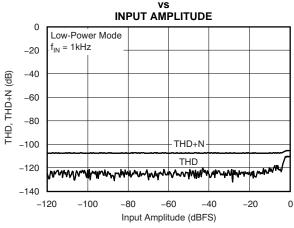

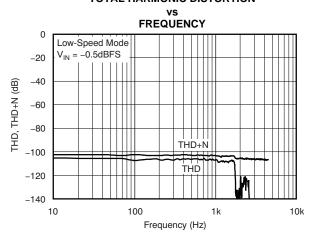

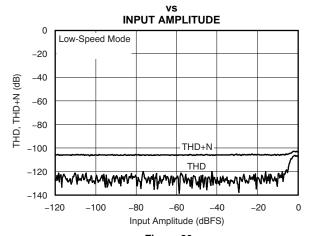

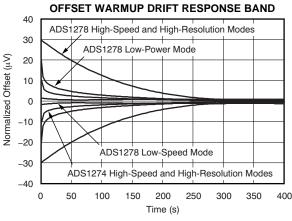

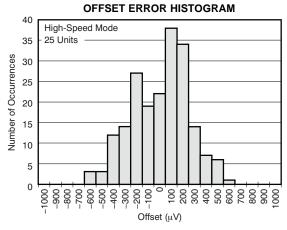

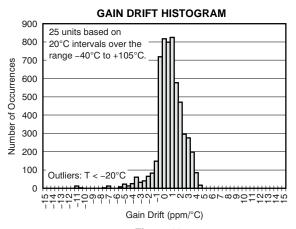

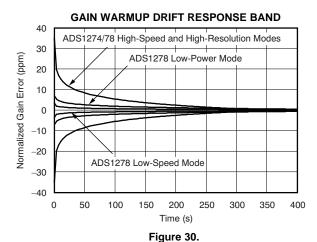

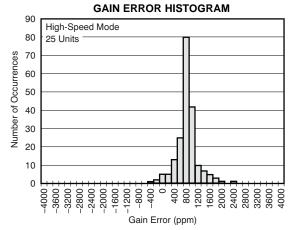

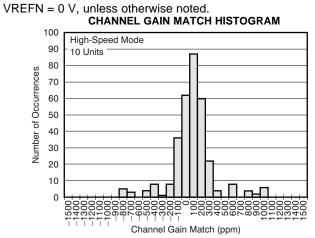

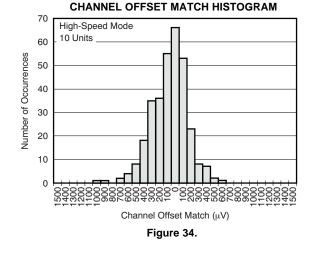

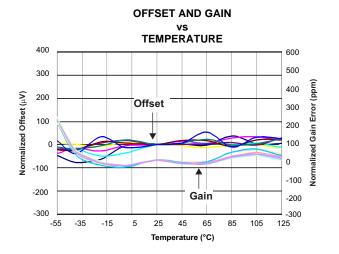

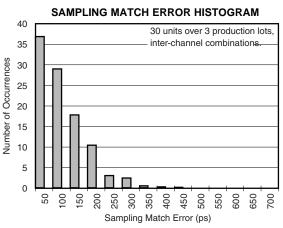

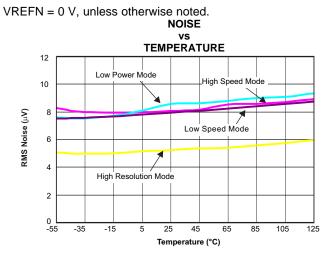

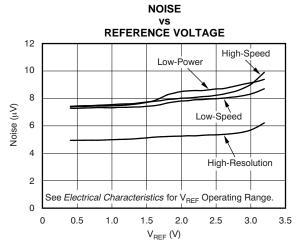

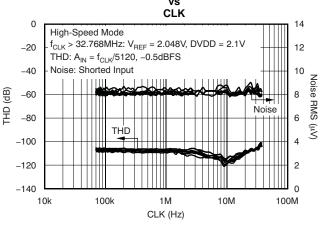

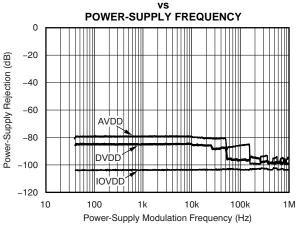

At  $T_A$  = 25°C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK}$  = 27 MHz, VREFP = 2.5 V, and VREFN = 0 V, unless otherwise noted.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

Figure 9.

**NSTRUMENTS**

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

Figure 15.

Figure 16.

Figure 17.

TOTAL HARMONIC DISTORTION

Copyright © 2012, Texas Instruments Incorporated

## TYPICAL CHARACTERISTICS (continued)

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

VREFN = 0 V, unless otherwise noted.

TOTAL HARMONIC DISTORTION

Figure 21.

#### TOTAL HARMONIC DISTORTION

NSTRUMENTS

Figure 22.

#### **TOTAL HARMONIC DISTORTION**

Figure 23.

#### TOTAL HARMONIC DISTORTION

Figure 24.

## **TOTAL HARMONIC DISTORTION**

Figure 25.

#### **TOTAL HARMONIC DISTORTION**

Figure 26.

#### TYPICAL CHARACTERISTICS (continued)

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and VREFN = 0 V, unless otherwise noted.

Figure 27.

Figure 29.

Figure 31.

Figure 28.

•

Figure 32.

# TYPICAL CHARACTERISTICS (continued)

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

Figure 33.

NSTRUMENTS

Figure 35.

Figure 36.

Figure 37.

# REFERENCE INPUT DIFFERENTIAL **IMPEDANCE**

Figure 38.

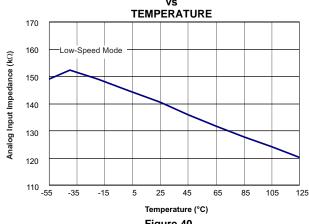

# TYPICAL CHARACTERISTICS (continued)

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and VREFN = 0 V, unless otherwise noted.

#### **ANALOG INPUT DIFFERENTIAL IMPEDANCE**

Figure 39.

# **ANALOG INPUT DIFFERENTIAL IMPEDANCE**

Figure 40.

#### INTEGRAL NONLINEARITY

Figure 41.

Figure 42.

#### LINEARITY AND TOTAL HARMONIC DISTORTION

Figure 43.

#### **NOISE AND LINEARITY**

Figure 44.

# TYPICAL CHARACTERISTICS (continued)

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

Figure 45.

**ISTRUMENTS**

Figure 46.

#### **TOTAL HARMONIC DISTORTION AND NOISE**

Figure 47.

Figure 48.

#### **POWER-SUPPLY REJECTION**

Figure 49.

Figure 50.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = 25$ °C, High-Speed mode, AVDD = 5 V, DVDD = 1.8 V, IOVDD = 3.3 V,  $f_{CLK} = 27$  MHz, VREFP = 2.5 V, and

Figure 52.

#### **POWER DISSIPATION**

#### OVERVIEW

The ADS1278 is an octal 24-bit, delta-sigma ADC based on the single-channel ADS1271. It offers the combination of outstanding dc accuracy and superior ac performance. Figure 54 shows the block diagram. The converter is comprised of eight advanced, 6th-order, chopper-stabilized, delta-sigma modulators followed by low-ripple, linear phase FIR filters. The modulators measure the differential input signal,  $V_{IN} = (AINP - AINN)$ , against the differential reference,  $V_{REF} = (VREFP - VREFN)$ . The digital filters receive the modulator signal and provide a low-noise digital output. To allow tradeoffs among speed, resolution, and power, four operating modes are supported:

High-Speed, High-Resolution, Low-Power, and Low-Speed. Table 2 summarizes the performance of each mode.

In High-Speed mode, the maximum data rate is 128 kSPS (when operating at 128 kSPS, Frame-Sync format must be used). In High-Resolution mode, the SNR = 111dB ( $V_{REF} = 3.0 \text{ V}$ ); in Low-Power mode, the power dissipation is 31 mW/channel; and in Low-Speed mode, the power dissipation is only 7 mW/channel at 10.5 kSPS. The digital filters can be bypassed, enabling direct access to the modulator output.

The ADS1278 is configured by simply setting the appropriate I/O pins—there are no registers to program. Data are retrieved over a serial interface that supports both SPI and Frame-Sync formats. The ADS1278 has a daisy-chainable output and the ability to synchronize externally, so it can be used conveniently in systems requiring more than eight channels.

Figure 54. Block Diagram

**Table 2. Operating Mode Performance Summary**

| MODE            | MAX DATA RATE (SPS) | PASSBAND (kHz) | SNR (dB) | NOISE (μV <sub>RMS</sub> ) | POWER/CHANNEL (mW) |

|-----------------|---------------------|----------------|----------|----------------------------|--------------------|

| High-Speed      | 128,000             | 57,984         | 106      | 8.5                        | 70                 |

| High-Resolution | 52,734              | 23,889         | 110      | 5.5                        | 64                 |

| Low-Power       | 52,734              | 23,889         | 106      | 8.5                        | 31                 |

| Low-Speed       | 10,547              | 4,798          | 107      | 8.0                        | 7                  |

#### **FUNCTIONAL DESCRIPTION**

The ADS1278 is a delta-sigma ADC consisting of eight independent converters that digitize eight input signals in parallel.

The converter is composed of two main functional blocks to perform the ADC conversions: the modulator and the digital filter. The modulator samples the input signal together with sampling the reference voltage to produce a 1s density output stream. The density of the output stream is proportional to the analog input level relative to the reference voltage. The pulse stream is filtered by the internal digital filter where the output conversion result is produced.

In operation, the input signal is sampled by the modulator at a high rate (typically 64x higher than the final output data rate). The quantization noise of the modulator is moved to a higher frequency range where the internal digital filter removes it. Oversampling results in very low levels of noise within the signal passband.

Since the input signal is sampled at a very high rate, input signal aliasing does not occur until the input signal frequency is at the modulator sampling rate. This architecture greatly relaxes the requirement of external antialiasing filters because of the high modulator sampling rate.

#### SAMPLING APERTURE MATCHING

The ADS1278 converter operates from the same CLK input. The CLK input controls the timing of the modulator sampling instant. The converter is designed such that the sampling skew, or modulator sampling aperture match between channels, is controlled. Furthermore, the digital filters are synchronized to start the convolution phase at the same modulator clock cycle. This design results in excellent phase match among the ADS1278 channels.

Figure 37 shows the inter-device channel sample matching for the ADS1278.

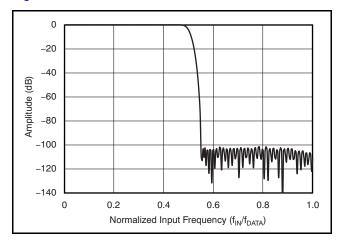

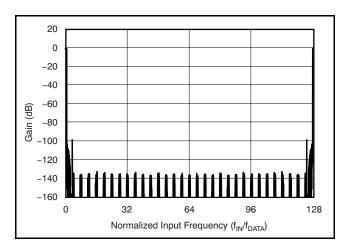

#### FREQUENCY RESPONSE

The digital filter sets the overall frequency response. The filter uses a multi-stage FIR topology to provide linear phase with minimal passband ripple and high stop band attenuation. The filter coefficients are identical to the coefficients used in the ADS1271. The oversampling ratio of the digital filter (that is, the ratio of the modulator sampling to the output data rate, or  $f_{\text{MOD}}/f_{\text{DATA}}$ ) is a function of the selected mode, as shown in Table 3.

**Table 3. Oversampling Ratio versus Mode**

| MODE SELECTION  | OVERSAMPLING RATIO (f <sub>MOD</sub> /f <sub>DATA</sub> ) |

|-----------------|-----------------------------------------------------------|

| High-Speed      | 64                                                        |

| High-Resolution | 128                                                       |

| Low-Power       | 64                                                        |

| Low-Speed       | 64                                                        |

# TEXAS INSTRUMENTS

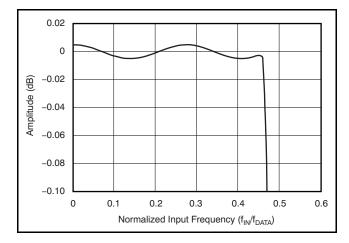

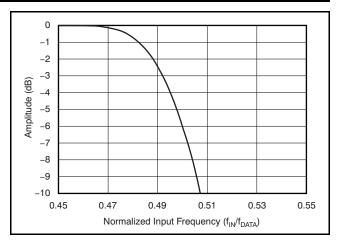

#### High-Speed, Low-Power, and Low-Speed Modes

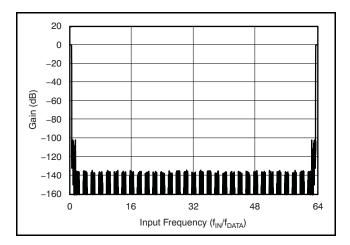

The digital filter configuration is the same in High-Speed, Low-Power, and Low-Speed modes with the oversampling ratio set to 64. Figure 55 shows the frequency response in High-Speed, Low-Power, and Low-Speed modes normalized to  $f_{DATA}$ . Figure 56 shows the passband ripple. The transition from passband to stop band is shown in Figure 57. The overall frequency response repeats at 64x multiples of the modulator frequency  $f_{MOD}$ , as shown in Figure 58.

Figure 55. Frequency Response for High-Speed, Low-Power, and Low-Speed Modes

Figure 56. Passband Response for High-Speed, Low-Power, and Low-Speed Modes

Figure 57. Transition Band Response for High-Speed, Low-Power, and Low-Speed Modes

Figure 58. Frequency Response Out to  $f_{\text{MOD}}$  for High-Speed, Low-Power, and Low-Speed Modes

These image frequencies, if present in the signal and not externally filtered, will fold back (or alias) into the passband, causing errors. The stop band of the ADS1278 provides 100 dB attenuation of frequencies that begin just beyond the passband and continue out to  $f_{\text{MOD}}$ . Placing an antialiasing, low-pass filter in front of the ADS1278 inputs is recommended to limit possible high-amplitude, out-of-band signals and noise. Often, a simple RC filter is sufficient. Table 4 lists the image rejection versus external filter order.

Table 4. Antialiasing Filter Order Image Rejection

| ANTIALIASING | IMAGE REJECTION (dB)<br>(f <sub>-3dB</sub> at f <sub>DATA</sub> ) |     |  |

|--------------|-------------------------------------------------------------------|-----|--|

| FILTER ORDER | HS, LP, LS                                                        | HR  |  |

| 1            | 39                                                                | 45  |  |

| 2            | 75                                                                | 87  |  |

| 3            | 111                                                               | 129 |  |

#### **High-Resolution Mode**

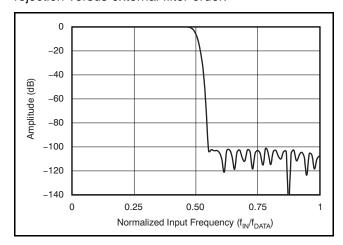

The oversampling ratio is 128 in High-Resolution mode. Figure 59 shows the frequency response in High-Resolution mode normalized to  $f_{DATA}.$  Figure 60 shows the passband ripple, and the transition from passband to stop band is shown in Figure 61. The overall frequency response repeats at multiples of the modulator frequency  $f_{MOD}$  (128 ×  $f_{DATA}$ ), as shown in Figure 62. The stop band of the ADS1278 provides 100 dB attenuation of frequencies that begin just beyond the passband and continue out to  $f_{MOD}.$  Placing an antialiasing, low-pass filter in front of the ADS1278 inputs is recommended to limit possible high-amplitude out-of-band signals and noise. Often, a simple RC filter is sufficient. Table 4 lists the image rejection versus external filter order.

Figure 59. Frequency Response for High-Resolution Mode

Figure 60. Passband Response for High-Resolution Mode

Figure 61. Transition Band Response for High-Resolution mode

Figure 62. Frequency Response Out to f<sub>MOD</sub> for High-Resolution Mode

TEXAS INSTRUMENTS

ZHCSAC0 – AUGUST 2012 www.ti.com.cn

#### PHASE RESPONSE

The ADS1278 incorporates a multiple stage, linear phase digital filter. Linear phase filters exhibit constant delay time versus input frequency (constant group delay). This characteristic means the time delay from any instant of the input signal to the same instant of the output data is constant and is independent of input signal frequency. This behavior results in essentially zero phase errors when analyzing multi-tone signals.

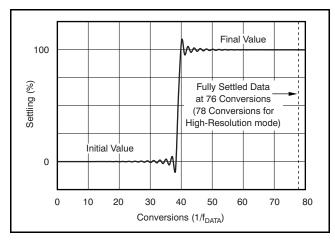

#### **SETTLING TIME**

As with frequency and phase response, the digital filter also determines settling time. Figure 63 shows the output settling behavior after a step change on the analog inputs normalized to conversion periods. The X-axis is given in units of conversion. Note that after the step change on the input occurs, the output data change very little prior to 30 conversion periods. The output data are fully settled after 76 conversion periods for High-Speed and Low-Power modes, and 78 conversion periods for High-Resolution mode.

Figure 63. Step Response

#### **DATA FORMAT**

The ADS1278 outputs 24 bits of data in twos complement format.

A positive full-scale input produces an ideal output code of 7FFFFFh, and the negative full-scale input produces an ideal output code of 800000h. The output clips at these codes for signals exceeding full-scale. Table 5 summarizes the ideal output codes for different input signals.

Table 5. Ideal Output Code versus Input Signal

| INPUT SIGNAL V <sub>IN</sub><br>(AINP – AINN)            | IDEAL OUTPUT CODE(1) |

|----------------------------------------------------------|----------------------|

| ≥ +V <sub>REF</sub>                                      | 7FFFFh               |

| $\frac{+ V_{REF}}{2^{23} - 1}$                           | 000001h              |

| 0                                                        | 000000h              |

| $\frac{-V_{REF}}{2^{23}-1}$                              | FFFFFFh              |

| $\leq -V_{REF} \left( \frac{2^{23}}{2^{23} - 1} \right)$ | 800000h              |

(1) Excludes effects of noise, INL, offset, and gain errors.

# **ANALOG INPUTS (AINP, AINN)**

The ADS1278 measures each differential input signal  $V_{IN} = (AINP - AINN)$  against the common differential reference  $V_{REF} = (VREFP - VREFN)$ . The most positive measurable differential input is  $+V_{REF}$ , which produces the most positive digital output code of 7FFFFh. Likewise, the most negative measurable differential input is  $-V_{REF}$ , which produces the most negative digital output code of 800000h.

For optimum performance, the inputs of the ADS1278 are intended to be driven differentially. For single-ended applications, one of the inputs (AINP or AINN) can be driven while the other input is fixed (typically to AGND or 2.5 V). Fixing the input to 2.5 V permits bipolar operation, thereby allowing full use of the entire converter range.

While the ADS1278 measures the differential input signal, the absolute input voltage is also important. This value is the voltage on either input (AINP or AINN) with respect to AGND. The range for this voltage is:

$$-0.1 \text{ V} < (AINN \text{ or AINP}) < AVDD + 0.1 \text{ V}$$

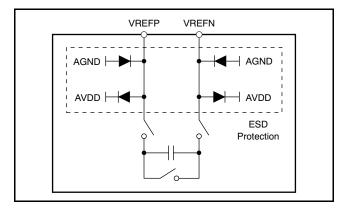

If either input is taken below -0.4 V or above (AVDD + 0.4 V), ESD protection diodes on the inputs may turn on. If these conditions are possible, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings table).

The ADS1278 is a very high-performance ADC. For optimum performance, it is critical that the appropriate circuitry be used to drive the ADS1278 inputs. See the *Application Information* section for several recommended circuits.

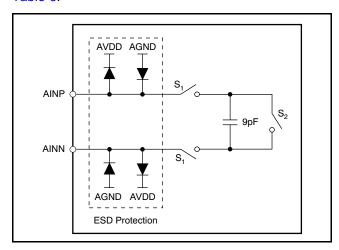

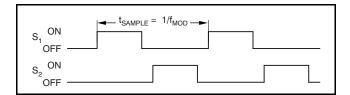

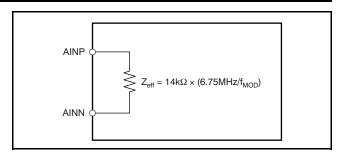

The ADS1278 uses switched-capacitor circuitry to measure the input voltage. Internal capacitors are charged by the inputs and then discharged. Figure 64 shows a conceptual diagram of these circuits. Switch  $S_2$  represents the net effect of the modulator circuitry in discharging the sampling capacitor; the actual implementation is different. The timing for switches  $S_1$  and  $S_2$  is shown in Figure 65. The sampling time ( $t_{SAMPLE}$ ) is the inverse of modulator sampling frequency ( $t_{MOD}$ ) and is a function of the mode, the CLKDIV input, and CLK frequency, as shown in Table 6.

Figure 64. Equivalent Analog Input Circuitry

Figure 65. S<sub>1</sub> and S<sub>2</sub> Switch Timing for Figure 64

Table 6. Modulator Frequency (f<sub>MOD</sub>) Mode Selection

| MODE SELECTION  | CLKDIV | f <sub>MOD</sub>     |

|-----------------|--------|----------------------|

| High-Speed      | 1      | f <sub>CLK</sub> /4  |

| High-Resolution | 1      | f <sub>CLK</sub> /4  |

| Laux Bassas     | 1      | f <sub>CLK</sub> /8  |

| Low-Power       | 0      | f <sub>CLK</sub> /4  |

| Low Chood       | 1      | f <sub>CLK</sub> /40 |

| Low-Speed       | 0      | f <sub>CLK</sub> /8  |

The average load presented by the switched capacitor input can be modeled with an effective differential impedance, as shown in Figure 66. Note that the effective impedance is a function of  $f_{\text{MOD}}$ .

Figure 66. Effective Input Impedances

# VOLTAGE REFERENCE INPUTS (VREFP, VREFN)

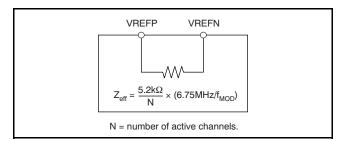

The voltage reference for the ADS1278 ADC is the differential voltage between VREFP and VREFN:  $V_{RFF} = (VREFP - VREFN)$ . The voltage reference is common to all channels. The reference inputs use a structure similar to that of the analog inputs with the equivalent circuitry on the reference inputs shown in Figure 67. As with the analog inputs, the load presented by the switched capacitor can be modeled with an effective impedance, as shown in Figure 68. However, the reference input impedance depends on the number of active (enabled) channels in addition to f<sub>MOD</sub>. As a result of the change of reference input impedance caused by enabling and disabling channels, the regulation and setting time of the external reference should be noted, so as not to affect the readings.

Figure 67. Equivalent Reference Input Circuitry

Figure 68. Effective Reference Impedance

**NSTRUMENTS**

ZHCSAC0 – AUGUST 2012 www.ti.com.cn

ESD diodes protect the reference inputs. To keep these diodes from turning on, make sure the voltages on the reference pins do not go below AGND by more than 0.4 V, and likewise do not exceed AVDD by 0.4 V. If these conditions are possible, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings table).

Note that the valid operating range of the reference inputs is limited to the following parameters:

$-0.1 \text{ V} \leq \text{VREFN} \leq +0.1 \text{ V}$

$VREFN + 0.5 V \le VREFP \le AVDD + 0.1 V$

# **CLOCK INPUT (CLK)**

The ADS1278 requires a clock input for operation. The individual converters of the ADS1278 operate from the same clock input. At the maximum data rate, the clock input can be either 27 MHz or 13.5 MHz for Low-Power mode, or 2 7MHz or 5.4 MHz for Low-Speed mode, determined by the setting of the CLKDIV input. For High-Speed mode, the maximum CLK input frequency is 32.768 MHz. For High-Resolution mode, the maximum CLK input frequency is 27 MHz. The selection of the external clock frequency (f<sub>CLK</sub>) does not affect the resolution of the ADS1278. Use of a slower f<sub>CLK</sub> can reduce the power consumption of an external clock buffer. The output data rate scales with clock frequency, down to a minimum clock frequency of f<sub>CLK</sub> = 100 kHz. Table 7 summarizes the ratio of the clock input frequency (f<sub>CLK</sub>) to data rate (f<sub>DATA</sub>), maximum data rate and corresponding maximum clock input for the four operating modes.

As with any high-speed data converter, a high-quality, low-jitter clock is essential for optimum performance. Crystal clock oscillators are the recommended clock source. Make sure to avoid excess ringing on the clock input; keeping the clock trace as short as possible, and using a  $50-\Omega$  series resistor placed close to the source end, often helps.

**Table 7. Clock Input Options**

| MODE<br>SELECTION | MAX f <sub>CLK</sub><br>(MHz) | CLKDIV | f <sub>CLK</sub> /f <sub>DATA</sub> | DATA RATE<br>(SPS) |  |

|-------------------|-------------------------------|--------|-------------------------------------|--------------------|--|

| High-Speed        | 32.768                        | 1      | 256                                 | 128,000            |  |

| High-Resolution   | 27                            | 1      | 512                                 | 52,734             |  |

|                   | 27                            | 1      | 512                                 | 50.704             |  |

| Low-Power         | 13.5                          | 0      | 256                                 | 52,734             |  |

| Law Casad         | 27                            | 1      | 2,560                               | 10.547             |  |

| Low-Speed         | 5.4                           | 0      | 512                                 | 10,547             |  |

# **MODE SELECTION (MODE)**

The ADS1278 supports four modes of operation: High-Speed, High-Resolution, Low-Power, and Low-Speed. The modes offer optimization of speed, resolution, and power. Mode selection is determined by the status of the digital input MODE[1:0] pins, as shown in Table 8. The ADS1278 continually monitors the status of the MODE pin during operation.

**Table 8. Mode Selection**

| MODE[1:0] | MODE SELECTION  | MAX f <sub>DATA</sub> <sup>(1)</sup> |

|-----------|-----------------|--------------------------------------|

| 00        | High-Speed      | 128,000                              |

| 01        | High-Resolution | 52,734                               |

| 10        | Low-Power       | 52,734                               |

| 11        | Low-Speed       | 10,547                               |

(1) f<sub>CLK</sub> = 27 MHz max (32.768MHz max in High-Speed mode).

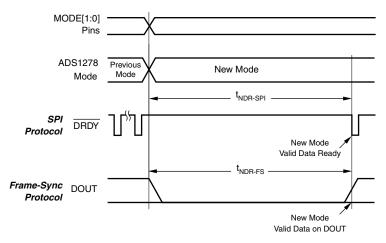

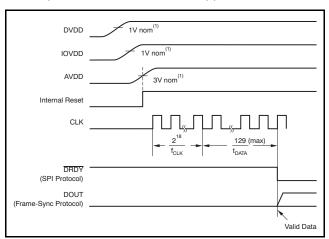

When using the SPI protocol,  $\overline{DRDY}$  is held high after a mode change occurs until settled (or valid) data are ready; see Figure 69 and Table 9.

In Frame-Sync protocol, the DOUT pins are held low after a mode change occurs until settled data are ready; see Figure 69 and Table 9. Data can be read from the device to detect when DOUT changes to logic 1, indicating that the data are valid.

Figure 69. Mode Change Timing

**Table 9. New Data After Mode Change**

| SYMBOL               | DESCRIPTION                                | MIN | TYP | MAX | UNITS                              |

|----------------------|--------------------------------------------|-----|-----|-----|------------------------------------|

| t <sub>NDR-SPI</sub> | Time for new data to be ready (SPI)        |     |     | 129 | Conversions (1/f <sub>DATA</sub> ) |

| t <sub>NDR-FS</sub>  | Time for new data to be ready (Frame-Sync) | 127 |     | 128 | Conversions (1/f <sub>DATA</sub> ) |

# **SYNCHRONIZATION (SYNC)**

The ADS1278 can be synchronized by pulsing the SYNC pin low and then returning the pin high. When the pin goes low, the conversion process stops, and the internal counters used by the digital filter are reset. When the SYNC pin returns high, the conversion process restarts. Synchronization allows the conversion to be aligned with an external event, such as the changing of an external multiplexer on the analog inputs, or by a reference timing pulse.

Because the ADS1278 converters operate in parallel from the same master clock and use the same SYNC input control, they are always in synchronization with each other. The aperture match among internal channels is typically less than 500 ps. However, the synchronization of multiple devices is somewhat different. At device power-on, variations in internal reset thresholds from device to device may result in uncertainty in conversion timing.

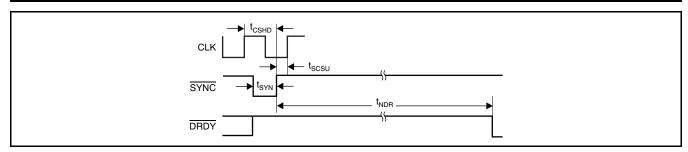

The SYNC pin can be used to synchronize multiple devices to within the same CLK cycle. Figure 70 illustrates the timing requirement of SYNC and CLK in SPI format.

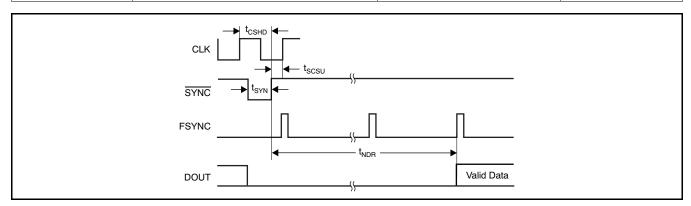

See Figure 71 for the Frame-Sync format timing requirement.

After synchronization, indication of valid data depends on whether SPI or Frame-Sync format was used.

In the SPI format, DRDY goes high as soon as SYNC is taken low; see Figure 70. After SYNC is returned high, DRDY stays high while the digital filter is settling. Once valid data are ready for retrieval, DRDY goes low.

In the Frame-Sync format, DOUT goes low as soon as SYNC is taken low; see Figure 71. After SYNC is returned high, DOUT stays low while the digital filter is settling. Once valid data are ready for retrieval, DOUT begins to output valid data. For proper synchronization, FSYNC, SCLK, and CLK must be established before taking SYNC high, and must then remain running. If the clock inputs (CLK, FSYNC or SCLK) are subsequently interrupted or reset, reassert the SYNC pin.

For consistent performance, re-assert SYNC after device power-on when data first appear.

Figure 70. Synchronization Timing (SPI Protocol)

# **Table 10. SPI Protocol**

| SYMBOL            | DESCRIPTION                   | MIN | TYP | MAX | UNITS                              |

|-------------------|-------------------------------|-----|-----|-----|------------------------------------|

| t <sub>CSHD</sub> | CLK to SYNC hold time         | 10  |     |     | ns                                 |

| t <sub>SCSU</sub> | SYNC to CLK setup time        | 5   |     |     | ns                                 |

| t <sub>SYN</sub>  | Synchronize pulse width       | 1   |     |     | CLK periods                        |

| t <sub>NDR</sub>  | Time for new data to be ready |     |     | 129 | Conversions (1/f <sub>DATA</sub> ) |

Figure 71. Synchronization Timing (Frame-Sync Protocol)

# **Table 11. Frame-Sync Protocol**

| SYMBOL            | DESCRIPTION                   | MIN | TYP | MAX | UNITS                              |

|-------------------|-------------------------------|-----|-----|-----|------------------------------------|

| t <sub>CSHD</sub> | CLK to SYNC hold time         | 10  |     |     | ns                                 |

| t <sub>SCSU</sub> | SYNC to CLK setup time        | 5   |     |     | ns                                 |

| t <sub>SYN</sub>  | Synchronize pulse width       | 1   |     |     | CLK periods                        |

| t <sub>NDR</sub>  | Time for new data to be ready | 127 |     | 128 | Conversions (1/f <sub>DATA</sub> ) |

# POWER-DOWN (PWDN)

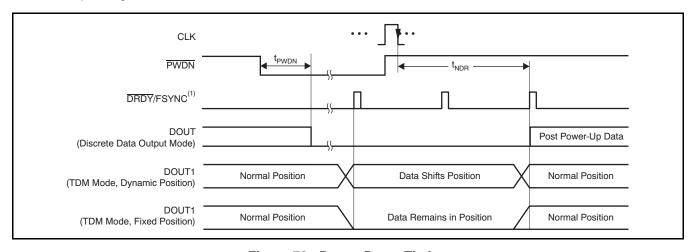

The channels of the ADS1278 can be independently powered down by use of the  $\overline{PWDN}$  inputs. To enter the power-down mode, hold the respective  $\overline{PWDN}$  pin low for at least two CLK cycles. To exit power-down, return the corresponding  $\overline{PWDN}$  pin high. Note that when all channels are powered down, the ADS1278 enters a microwatt (µW) power state where all internal biasing is disabled. In this state, the TEST[1:0] input pins must be driven; all other input pins can float. The ADS1278 outputs remain driven.

As shown in Figure 72 and Table 12, a maximum of 130 conversion cycles must elapse for SPI interface, and 129 conversion cycles must elapse for Frame-Sync, before reading data after exiting power-down. Data from channels already running are not affected. The user software can perform the required delay time in any of the following ways:

- Count the <u>number</u> of data conversions after taking the <u>PWDN</u> pin high.

- Delay 129/f<sub>DATA</sub> or 130/f<sub>DATA</sub> after taking the PWDN pins high, then read data.

Detect for non-zero data in the powered-up channel.

After powering up one or more channels, the channels are synchronized to each other. It is not necessary to use the SYNC pin to synchronize them.

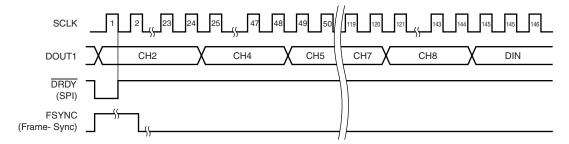

When a channel is powered down in TDM data format, the data for that channel are either forced to zero (fixed-position TDM data mode) or replaced by shifting the data from the next channel into the vacated data position (dynamic-position TDM data mode).

In Discrete data format, the data are always forced to zero. When powering-up a channel in dynamic-position TDM data format mode, the channel data remain packed until the data are ready, at which time the data frame is expanded to include the just-powered channel data. See the *Data Format* section for details.

Figure 72. Power-Down Timing

Table 12. Power-Down Timing

| SYMBOL            | DESCRIPTION                               | MIN | TYP | MAX | UNITS                              |

|-------------------|-------------------------------------------|-----|-----|-----|------------------------------------|

| t <sub>PWDN</sub> | PWDN pulse width to enter Power-Down mode | 2   |     |     | CLK periods                        |

| t <sub>NDR</sub>  | Time for new data ready (SPI)             | 129 |     | 130 | Conversions (1/f <sub>DATA</sub> ) |

| t <sub>NDR</sub>  | Time for new data ready (Frame-Sync)      | 128 |     | 129 | Conversions (1/f <sub>DATA</sub> ) |

TEXAS INSTRUMENTS

ZHCSAC0 – AUGUST 2012 www.ti.com.cn

## FORMAT[2:0]

Data can be read from the ADS1278 with two interface protocols (SPI or Frame-Sync) and several options of data formats (TDM/Discrete and Fixed/Dynamic data positions). The FORMAT[2:0] inputs are used to select among the options. Table 13 lists the available options. See the *DOUT Modes* section for details of the DOUT Mode and Data Position.

**Table 13. Data Output Format**

| FORMAT[2:0] | INTERFACE<br>PROTOCOL | DOUT<br>MODE | DATA<br>POSITION |

|-------------|-----------------------|--------------|------------------|

| 000         | SPI                   | TDM          | Dynamic          |

| 001         | SPI                   | TDM          | Fixed            |

| 010         | SPI                   | Discrete     | _                |

| 011         | Frame-Sync            | TDM          | Dynamic          |

| 100         | Frame-Sync            | TDM          | Fixed            |

| 101         | Frame-Sync            | Discrete     | _                |

| 110         | Modulator Mode        | _            | _                |

#### SERIAL INTERFACE PROTOCOLS

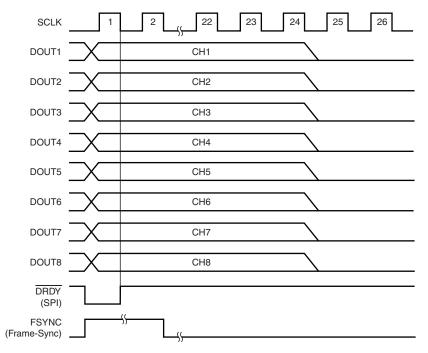

Data are retrieved from the ADS1278 using the serial interface. Two protocols are available: SPI and Frame-Sync. The <u>same</u> pins are used for both interfaces: SCLK, <u>DRDY/FSYNC</u>, <u>DOUT[8:1]</u>, and DIN. The FORMAT[2:0] pins select the desired interface protocol.

#### **SPI SERIAL INTERFACE**

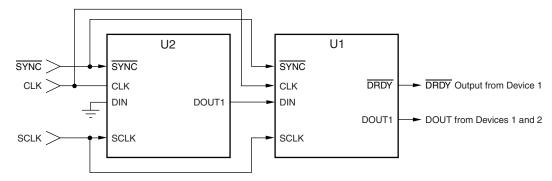

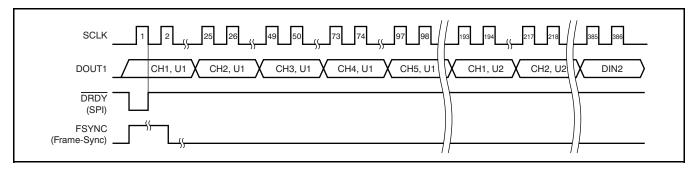

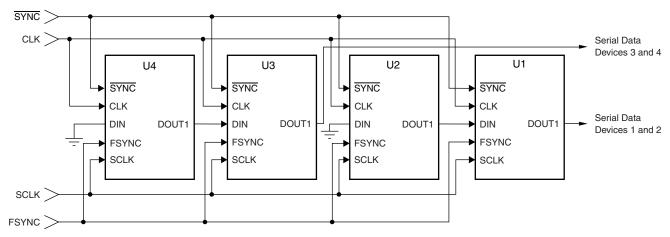

The SPI-compatible format is a read-only interface. Data ready for retrieval are indicated by the falling DRDY output and are shifted out on the falling edge of SCLK, MSB first. The interface can be daisy-chained using the DIN input when using multiple devices. See the Daisy-Chaining section for more information.

NOTE: The SPI format is limited to a CLK input frequency of 27 MHz, maximum. For CLK input operation above 27 MHz (High-Speed mode only), use Frame-Sync format.

#### **SCLK**

The serial clock (SCLK) features a Schmitt-triggered input and shifts out data on DOUT on the falling edge. It also shifts in data on the falling edge on DIN when this pin is being used for daisy-chaining. The device shifts data out on the falling edge and the user normally shifts this data in on the rising edge.

Even though the SCLK input has hysteresis, it is recommended to keep SCLK as clean as possible to prevent glitches from accidentally shifting the data.

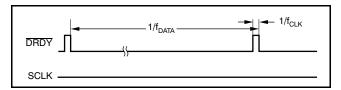

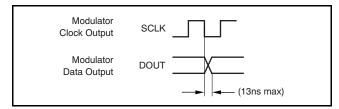

SCLK may be run as fast as the CLK frequency. SCLK may be either in free-running or stop-clock operation between conversions. Note that one  $f_{CLK}$  is required after the falling edge of  $\overline{DRDY}$  until the first rising edge of SCLK. For best performance, limit  $f_{SCLK}/f_{CLK}$  to ratios of 1, 1/2, 1/4, 1/8, etc. When the device is configured for modulator output, SCLK becomes the modulator clock output (see the *Modulator Output* section).

#### **DRDY/FSYNC (SPI Format)**

In the SPI format, this pin functions as the DRDY output. It goes low when data are ready for retrieval and then returns high on the falling edge of the first subsequent SCLK. If data are not retrieved (that is, SCLK is held low), DRDY pulses high just before the next conversion data are ready, as shown in Figure 73. The new data are loaded within one CLK cycle before DRDY goes low. All data must be shifted out before this time to avoid being overwritten.

Figure 73. DRDY Timing with No Readback

#### **DOUT**

The conversion data are output on DOUT[8:1]. The MSB data are valid on DOUT[8:1] after DRDY goes low. Subsequent bits are shifted out with each falling edge of SCLK. If daisy-chaining, the data shifted in using DIN appear on DOUT after all channel data have been shifted out. When the device is configured for modulator output, DOUT[8:1] becomes the modulator data output for each channel (see the *Modulator Output* section).

#### DIN

This input is used when multiple ADS1278s are to be daisy-chained together. The DOUT1 pin of the first device connects to the DIN pin of the next, etc. It can be used with either the SPI or Frame-Sync formats. Data are shifted in on the falling edge of SCLK. When using only one ADS1278, tie DIN low. See the *Daisy-Chaining* section for more information.

#### FRAME-SYNC SERIAL INTERFACE

Frame-Sync format is similar to the interface often used on audio ADCs. It operates in slave fashion—the user must supply framing signal FSYNC (similar to the *left/right clock* on stereo audio ADCs) and the serial clock SCLK (similar to the *bit clock* on audio ADCs). The data are output MSB first or *left-justified* on the rising edge of FSYNC. When using Frame-Sync format, the FSYNC and SCLK inputs must be continuously running with the relationships shown in the Frame-Sync Timing Requirements.

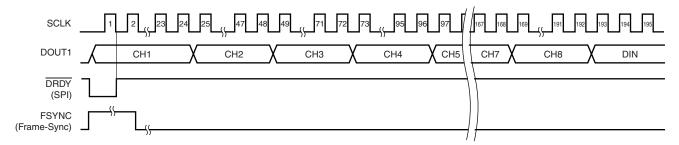

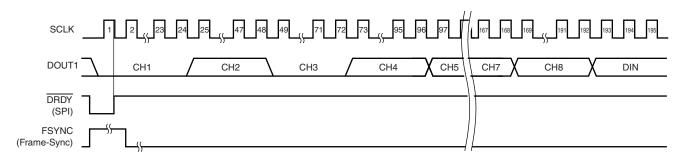

#### **SCLK**