LMX2582

ZHCSEK4E - DECEMBER 2015 - REVISED AUGUST 2022

# 集成了 VCO 的 LMX2582 高性能宽带 PLLatinum™ 射频合成器

# 1 特性

- 输出频率范围为 20 至 5500MHz

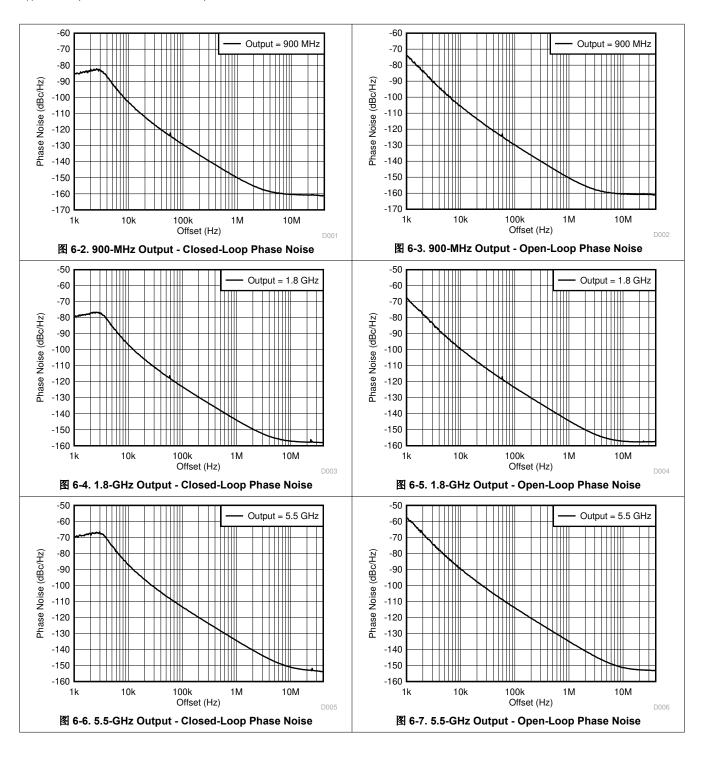

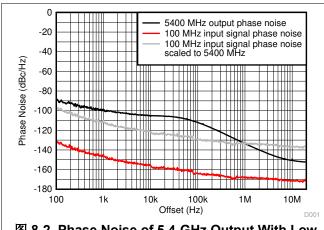

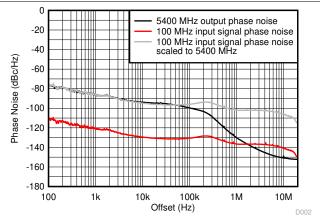

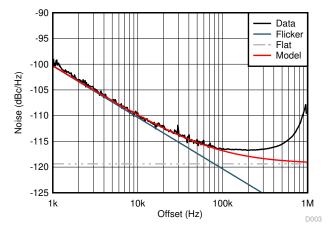

- 相位噪声性能行业领先

- VCO 相位噪声: 在输出为 1.8GHz 且偏移为 1MHz 时为 - 144.5dBc/Hz

- 归一化 PLL 本底噪声: -231dBc/Hz

- 归一化 PLL 闪烁噪声: -126dBc/Hz

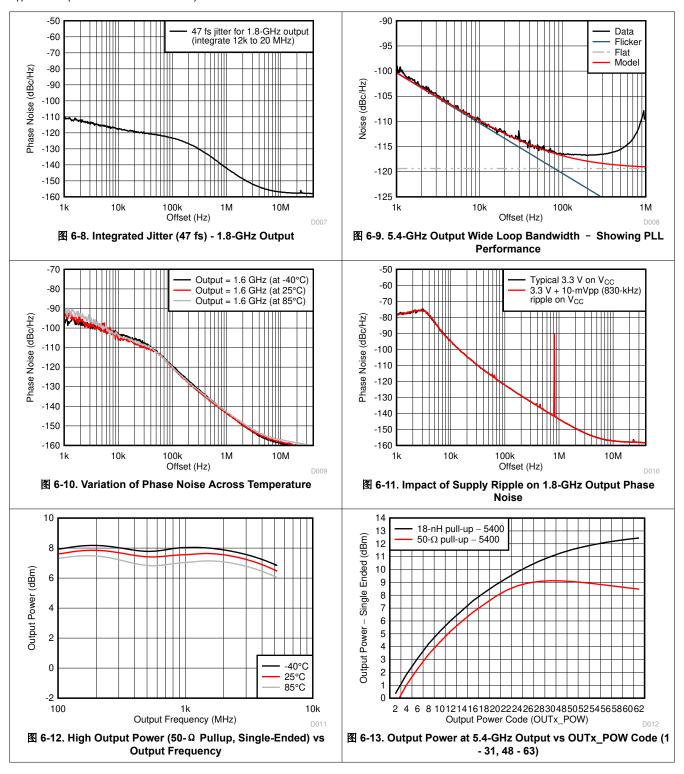

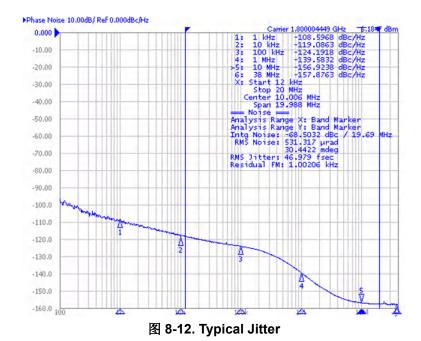

- 47fs RMS 抖动 (12kHz 至 20MHz ) (对于 1.8GHz 输出)

- 输入时钟频率高达 1400MHz

- 相位检测器频率高达 200MHz, 且在整数 N 模式中高达 400MHz

- 支持分数 N 和整数 N 模式

- 双差分输出

- 减少毛刺的创新型解决方案

- 可编程相位调整

- 可编程电荷泵电流

- 可编程输出功率水平

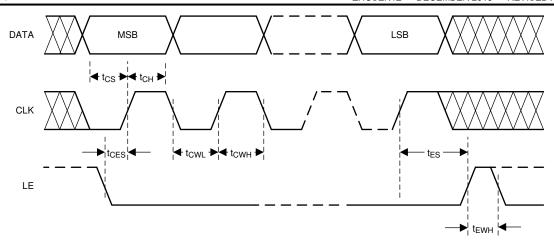

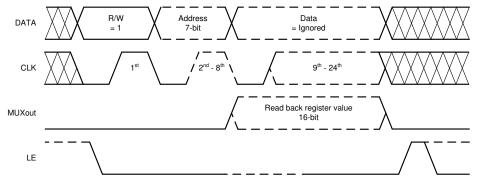

- 串行外设接口 (SPI) 或 uWire ( 4 线制串行接口 )

- 单电源运行: 3.3V

# 2 应用

- 测试和测量设备

- 蜂窝基站

- 微波回程

- 高速数据转换器的高性能时钟源

- 由软件定义的无线电

## 3 说明

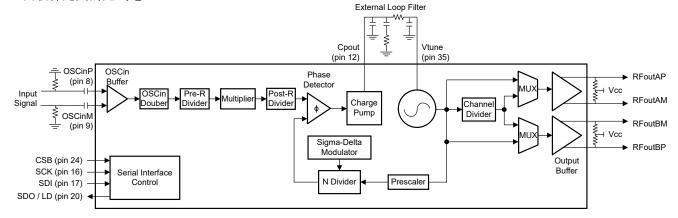

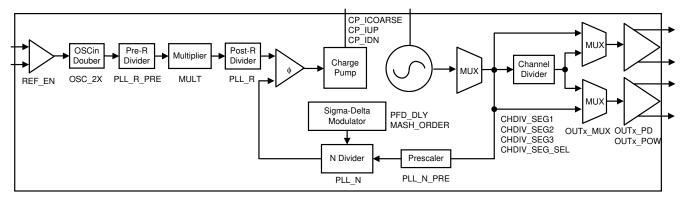

LMX2582 是一款集成了 VCO 的低噪声宽带射频 PLL,支持的频率范围为 20MHz 至 5.5GHz。该器件 支持分数 N 和整数 N 模式,具有一个 32 位分数分频 器,支持选择合适的频率。其积分噪声为 47fs (对于 1.8GHz 输出),是理想的低噪声源。该器件融入了一 流的 PLL 和 VCO 积分噪声与集成的低压线性稳压器 (LDO),从而无需高性能系统中的多个分立器件。

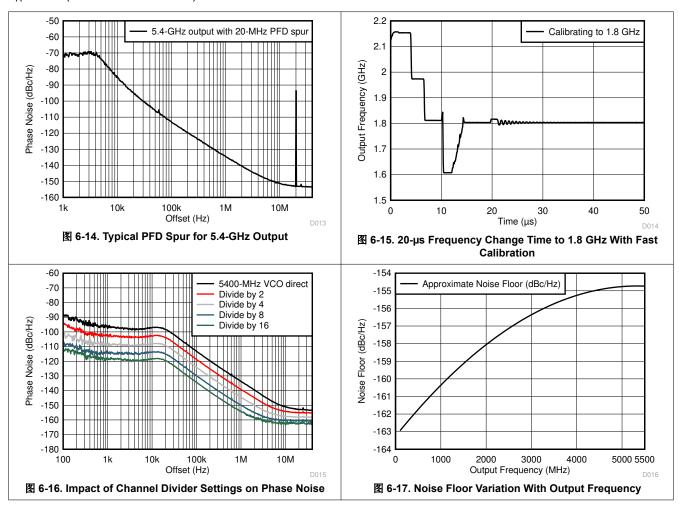

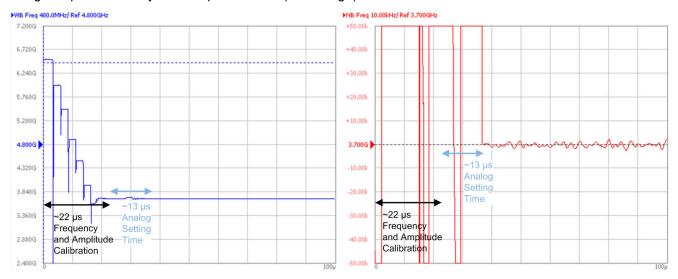

该器件可接受高达 1.4GHz 的输入频率,与分频器及可 编程低噪声乘法器相结合,可灵活设置频率。附加的可 编程低噪声乘法器可帮助用户减轻整数边界杂散的影 响。在分数 N 模式下,该器件可将输出相位调整 32 位 分辨率。对于需要快速频率变化的应用,该器件支持耗 时小于 25us 的快速校准选项。

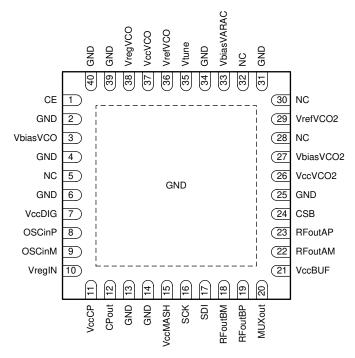

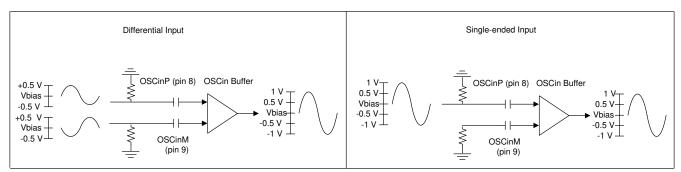

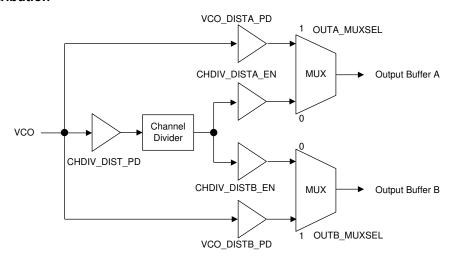

使用一个 3.3V 电源即可能实现此性能。该器件支持 2 个差分输出,这两个输出也可灵活配置为单端输出。用 户可选择将其中一个编程为从 VCO 输出,另一个从通 道分配器输出。若不想使用,可分别禁用每个输出。

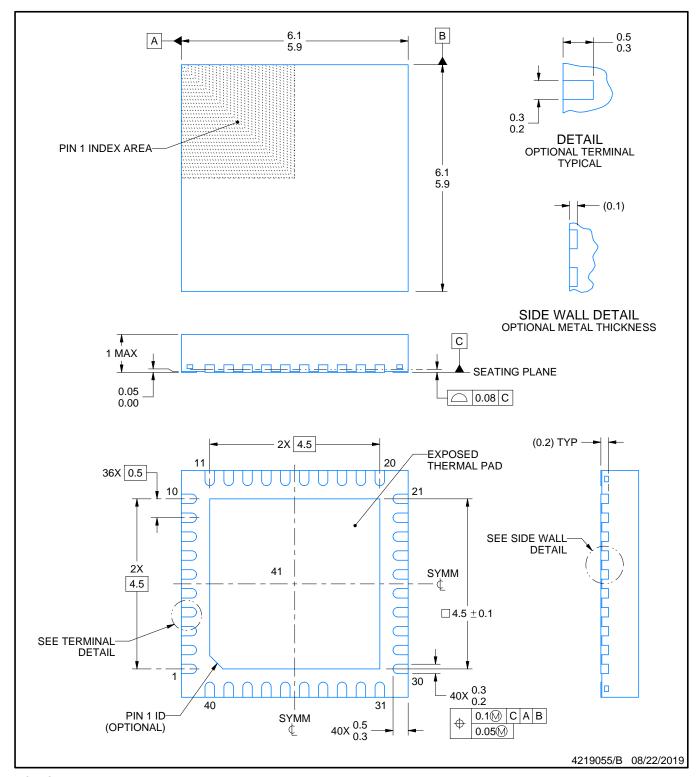

# 封装信息<sup>(1)</sup>

| 器件型号                       | 说明        | 封装尺寸(标称值)       |

|----------------------------|-----------|-----------------|

| LMX2582RHAT<br>LMX2582RHAR | VQFN (40) | 6.00mm × 6.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

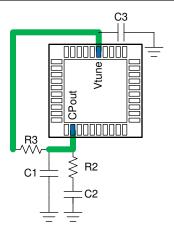

简化版原理图

| Table o                                                                                                                                                                                                                                                                                                                                                                                                    | of Contents            |                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------|

| 1 特性 2 应用 3 说明 4 Revision History 5 Pin Configuration and Functions 6 Specifications 6.1 Absolute Maximum Ratings 6.2 ESD Ratings 6.3 Recommended Operating Conditions 6.4 Thermal Information 6.5 Electrical Characteristics 6.6 Timing Requirements 6.7 Typical Characteristics 17 Detailed Description 7.1 Overview 7.2 Functional Block Diagram 7.3 Functional Description 7.4 Device Functional Modes | 7.6 Register Maps      | .18<br>.29<br>.36<br>.37<br>.38<br>.39<br>.39<br>.39<br>.39<br>.39 |

| <ul> <li>Added a new requirement to Vtune pin description</li> </ul>                                                                                                                                                                                                                                                                                                                                       | ion E (August 2022) Pa | 1                                                                  |

| Changes from Revision D (October 2017) to Revision E (August 2022)                                      | Page |

|---------------------------------------------------------------------------------------------------------|------|

| <ul> <li>将封装说明从 WQFN 更改为 VQFN</li> </ul>                                                                |      |

| Added a new requirement to Vtune pin description                                                        |      |

| Removed sentence: The CLK signal should not be high when LE transitions to low                          |      |

| Changed the Channel Divider requirement                                                                 |      |

| Added a new register field, VTUNE_ADJ, in register R30                                                  |      |

| Changed the position of register field, PFD_CTL, in register R13                                        |      |

| Added read only register R68, R69 and R70                                                               |      |

| • Added additional requirement for register CP_ICOARSE in 表 7-16                                        |      |

| • Added additional information for register MUXOUT_HDRV in 表 7-44                                       |      |

| • Added a new register field, VTUNE_ADJ, in 表 7-25                                                      |      |

| Changed the register R0 FCAL_LPFD_ADJ configurable values                                               |      |

| Changed the register R13 PFD_CTL position                                                               |      |

| Added the R68, R69 and R70 register field descriptions                                                  |      |

| Added External Loop Filter section                                                                      |      |

| <ul> <li>Moved the Power Supply Recommendations and Layout sections to the Application and I</li> </ul> |      |

| section                                                                                                 |      |

| Changes from Revision C (July 2017) to Revision D (October 2017)                                        | Page |

| Switched the RFoutBP and RFoutBM pins in the pinout diagram                                             | 4    |

| Changed register 0, 7, 30, and 46 descriptions                                                          |      |

| Changes from Revision B (February 2017) to Revision C (July 2017)                                       | Page |

| Changed Channel Divider Setting as a Function of the Desired Output Frequency table                     | 15   |

| Changes from Revision A (December 2015) to Revision B (February 2017)                                   | Page |

| • 从 <i>特性</i> 中删除了 < 25µs 快速校准模式项目                                                                      | 1    |

| • 根据最新文档和翻译标准更新了数据表文本                                                                                   |      |

| Changed pin 30 name from: Rext to: NC                                                                   | 4    |

#### www.ti.com.cn

| Changed CDM value from: ±1250 V to: ±750 V                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changed parameter name from: Maximum reference input frequency to: reference input frequency           | <mark>7</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Removed charge pump current TYP range '0 to 12' and split range into MIN (0) and MAX (12) column       | s <mark>7</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Added 10 kHz test conditions for the PN <sub>open loop</sub> parameter                                 | <mark>7</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Changed the high level input voltage minimum value of from: 1.8 to: 1.4                                | <mark>7</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Moved all typical values in the <i>Timing Requirements</i> table to minimum column                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Changed text from: the shift registers to an actual counter to: the shift registers to a register bank | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Changed high input value from: 700 to: 200                                                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Added content to the Voltage Controlled Oscillator section                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

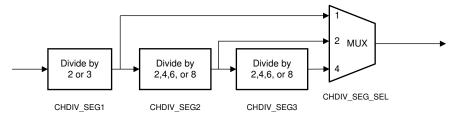

| Changed text from: output dividers to: channel dividers                                                | 1 <mark>5</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Changed Channel Divider Setting as a Function of the Desired Output Frequency table                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Changed VCO frequency from: 7200 to: 7100                                                              | 1 <mark>5</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Changed Phase shift (degrees) from: 360 × MASH_SEED / PLL_N_DEN / [Channel divider value] to:          | 360 x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MASH_SEED x PLL_N_PRE / PLL_N_DEN / [Channel divider value]"                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Changed register 7, 8, 19, 23, 32, 33, 34, 46, and 64 descriptions                                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Added registers 20, 22, 25, 59, and 61                                                                 | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Added registers 2, 4, and 62 to Register Table                                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Changed register 38 in Register Table                                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Changed register descriptions from: Program to default to: Program to Register Map default values      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Added R2 Register Field Descriptions                                                                   | <mark>20</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Added R4 Register Field Descriptions                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Added R62 Register Field Descriptions                                                                  | <mark>20</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Updated content in the Decreasing Lock Time section                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

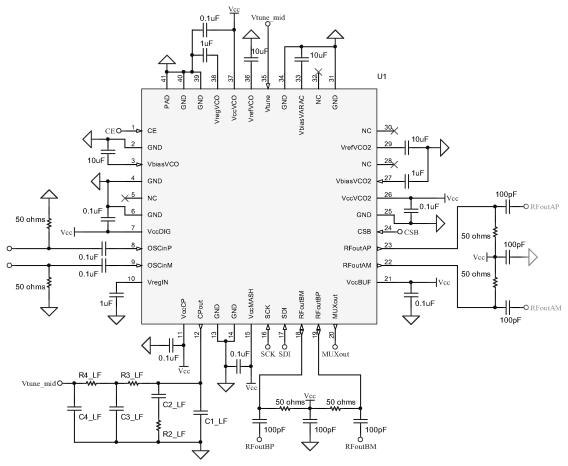

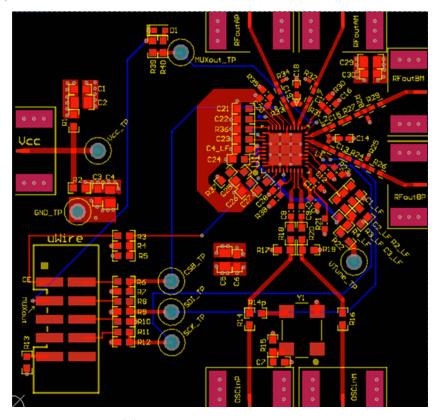

| Changed typical application image                                                                      | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Changed R2 value from: 0.068 to: 68                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| nanges from Revision * (December 2015) to Revision A (December 2015)                                   | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |